armv8架构与指令集.整理.初稿

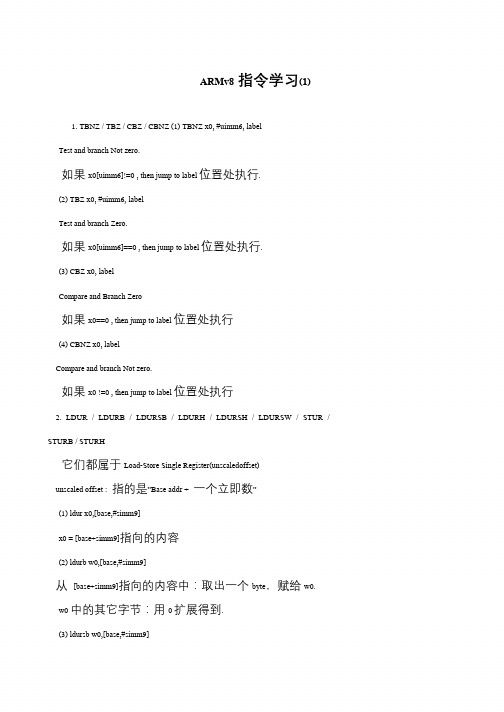

ARMv8指令学习(1)

如果x0 !=0 , then jumpto label位置处执行

LDUR/LDURB/LDURSB/LDURH/LDURSH/LDURSW/STUR/

STURB / STURH

它们都属于Load-StoreSingle Register(unscaledoffset)

unscaledoffset :指的是”Baseaddr+一个立即数”

w0中的其它字节:用此byte的符号位扩展得到.

(4) ldurh

类似ldurb,不过:这次取halfword(2 bytes)

(5) ldursh

类似ldursb,不过:这次取halfword(2 bytes)

(6) ldursw

类似ldursb,不过:这次取word(4 bytes)

(7) sturx0,[base,#simm9]

把x0保存到[base+#simm9]指向的内存位置

(8) sturb x0,[base,#simm9]

把x0中的一个byte,保存到[base+#simm9]指向的内存位置

(9) sturh x0,[base,#simm9]

把x0中的一个half-word(2 bytes),保存到[base+#simm9]指向的内存位置

(1) ldur x0,[base,#simm9]

x0 = [base+simm9]指向的内容

(2) ldurb w0,[base,#simm9]

从[base+simm9]指向的内容中:取出一个byte,赋给w0.

w0中的其它字节:用0扩展得到.

(3) ldursbw0,[base,#simm9]

ARM体系结构与指令集

ARM技术简介

采用RISC架构的ARM微处理器一般具有如下特点: ① 体积小、低功耗、低成本、高性能。 ② 支持Thumb(16位)/ARM(32位)双指令集,

能很好的兼容8/16位器件。 ③ 大量使用寄存器,指令执行速度更快。 ④ 大多数数据操作都在寄存器中完成。 ⑤ 寻址方式灵活简单,执行效率高。 ⑥ 指令长度固定。

OS等主流嵌入式操作系统。 ⑤ MPU支持实时操作系统。 ⑥ 支持数据Cache和指令Cache,具有更高的指令

和数据处理能力。

ARM处理器内核系列

ARM9E系列微处理器的主要特点如下: ① 支持DSP指令集,适合于需要高速数字信号处理的场合。 ② 5级整数流水线,指令执行效率更高。 ③ 支持32位ARM指令集和16位Thumb指令集。 ④ 支持32位的高速AMBA总线接口。 ⑤ 支持VFP9浮点处理协处理器。 ⑥ 全性能MMU,支持Windows CE、Linux、Palm OS等主

体系架构分类

(1)复杂指令集和精简指令集

微处理器的架构根据指令结构可以分为复杂指令集 (Complex Instruction Set Computer,CISC)架 构和精简指令集(Reduced Instruction Set Computer,RISC)架构,CISC架构采用庞大的指 令集,可以减少编程所需要的代码行数,减轻程式 师的负担,RISC采用精简指令集,包含了简单、基 本的指令,透过这些简单、基本的指令,就可以组 合成复杂指令,二者各有优缺点。CISC在桌面电脑 和服务器中应用广泛,而RISC在嵌入式微处理器中 则占有较大的市场份额。

产品。 ③ 能够提供0.9MIPS/MHz的三级流水线结构。 ④ 代码密度高并兼容16位的Thuws CE、Linux、

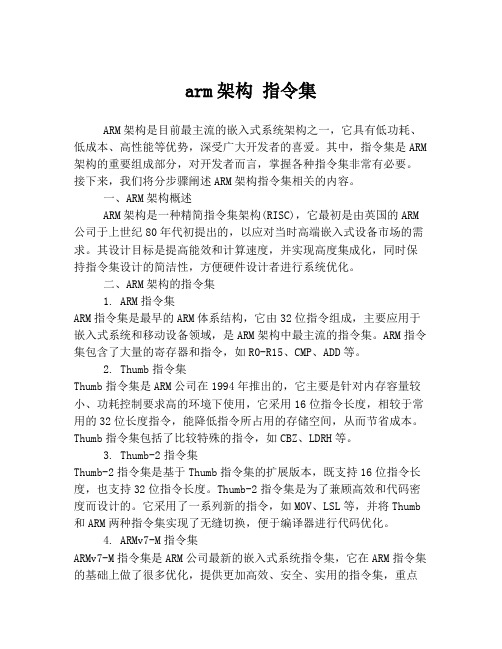

arm架构 指令集

arm架构指令集ARM架构是目前最主流的嵌入式系统架构之一,它具有低功耗、低成本、高性能等优势,深受广大开发者的喜爱。

其中,指令集是ARM 架构的重要组成部分,对开发者而言,掌握各种指令集非常有必要。

接下来,我们将分步骤阐述ARM架构指令集相关的内容。

一、ARM架构概述ARM架构是一种精简指令集架构(RISC),它最初是由英国的ARM 公司于上世纪80年代初提出的,以应对当时高端嵌入式设备市场的需求。

其设计目标是提高能效和计算速度,并实现高度集成化,同时保持指令集设计的简洁性,方便硬件设计者进行系统优化。

二、ARM架构的指令集1. ARM指令集ARM指令集是最早的ARM体系结构,它由32位指令组成,主要应用于嵌入式系统和移动设备领域,是ARM架构中最主流的指令集。

ARM指令集包含了大量的寄存器和指令,如R0-R15、CMP、ADD等。

2. Thumb指令集Thumb指令集是ARM公司在1994年推出的,它主要是针对内存容量较小、功耗控制要求高的环境下使用,它采用16位指令长度,相较于常用的32位长度指令,能降低指令所占用的存储空间,从而节省成本。

Thumb指令集包括了比较特殊的指令,如CBZ、LDRH等。

3. Thumb-2指令集Thumb-2指令集是基于Thumb指令集的扩展版本,既支持16位指令长度,也支持32位指令长度。

Thumb-2指令集是为了兼顾高效和代码密度而设计的。

它采用了一系列新的指令,如MOV、LSL等,并将Thumb 和ARM两种指令集实现了无缝切换,便于编译器进行代码优化。

4. ARMv7-M指令集ARMv7-M指令集是ARM公司最新的嵌入式系统指令集,它在ARM指令集的基础上做了很多优化,提供更加高效、安全、实用的指令集,重点支持通用数学、位操作、存储器、DMA控制等指令。

它可以运行在更加高效的Cortex-M内核上,提供更加强大的性能和更佳的功耗控制。

三、总结在开发嵌入式系统和移动设备时,深入掌握各种指令集是非常有必要的,不同的指令集具有各自的优势和适用场景,开发者应该根据需求进行选择。

03_ARMv8指令集介绍加载与存储指令

03_ARMv8指令集介绍加载与存储指令Github地址:ARMv8指令集介绍A64指令集只能运⾏在aarch64所有A64汇编都是32 bits宽的关注指令的使⽤、有什么limitationA64能访问的地址数据是64位宽的A64⽀持全部的⼤写或者⼩写⽅式ARM官⽅⼤写应⽤使⽤⼩写寄存器命名Wn表⽰32bits宽的寄存器Xn表⽰64bits宽的寄存器WZR表⽰32位内容全为0的寄存器XZR表⽰64位内容全为0的寄存器...LDR指令LDR Xd, [Xn, $offset]【释义】:将Xn寄存器中存储的地址+offset地址偏移存组成⼀个新的地址,把这个地址⾥⾯存储的值放在Xd寄存器中。

[]有取地址内存储的数值的含义。

【⽰例】:S1: 使⽤MOV指令把0x80000加载到X1寄存器:MOV x1, 0x80000(如果是⼀个数,⽽⾮#0x80000, 则是⼀个地址)S2: 使⽤MOV指令把16数值加载到X3寄存器:MOV x3, 16S3: 使⽤LDR指令读取X1地址⾥⾯存储的值,存储到X0中: LDR x0,[x1] , 这个不允许->LDR x2,[0x80000]S4:使⽤LDR指令读取X1 + 8地址⾥⾯存储的值,存储到X2中:LDR x2,[x1, #8]S5:使⽤LDR指令读取(X1 + X3)地址⾥⾯存储的值,存储到X4中:LDR x4,[x1, x3]S6: 使⽤LDR指令读取(X1+(X3<<3))地址⾥⾯存储的值,存储到X5中:LDR x5,[x1,x3,lsl #3]【注意】:给的数不加任何标志的视为地址需要给⽴即数的场景⽽⾮地址的值,使⽤#[]有取地址值的意思LDR lsl扩展指令,只⽀持1和3LDR x2,[x1, #8] x1的值不会被更新为0x80008【变基模式】:前变基模式 pre-index:先更新偏移地址,后访问地址(注意有叹号!表⽰)LDR x6, [x1, #8]! : 将x1⾥⾯的地址增加偏移#8并赋给x1,最后将新的x1寄存器内的地址的值给x6寄存器后变基模式 post-index:先访问内存地址,再更新偏移地址LDR x6, [x1], #8 : 将x1寄存器内的地址的值赋给x6寄存器,并将x1地址偏移+8。

ARMv8指令学习(2)

Wd = Wn

else

Wd = Wn

同时:设置Wd中的其它bit位为0

4. Bitfield insertand extract指令(1) BFI : Bitfield insert

BFI Wd, Wn,#lsb, #width

等同于

BFM Wd,Wn,#((32-lsb)&31) , #(width-1)

即:

widthbitsinWd,startingatlsb,arereplacedbywidthbitsfromWn,startingat

bit[0].

Other bitsin Rd are unchanged

BFI指令,不会更改PSTATE中的flags

(2) BFXIL : Bitfield extract and insert low

BFXIL Wd, Wn,#lsb,#width等同于BFM Wd,Wn,#lsb,#(lsb+width-1)

(3)SBFIZ:Signedbitfieldinsertinzero(4)SBFX:Signedbitfieldextract(5)

UBFIZ : Unsigned bitfield insert in zero (6) UBFX : Unsigned bitfield extract

else

Wd = Wn

同时:保持Wd中的其它bit不变(2)SBFM: Signedbitfieldmove

SBFM Wd,Wn,#r,#s

if (s>=r)

Wd = Wn

else

Wd = Wn

并扩展相应的符号位.

(3)UBFM:Unsignedbitfield move

arm指令集发展史

ARM指令集是一种用于处理器架构的指令集体系结构。

它最初由英国公司ARM Holdings开发,并广泛应用于各种嵌入式系统、移动设备和低功耗应用中。

以下是ARM指令集的发展史:1. ARM1:ARM指令集最早出现在1985年的ARM1处理器上。

ARM1是一款32位处理器,采用精简指令集(RISC)设计理念,具有较低的能耗和成本。

2. ARM2:ARM2处理器于1987年发布,增加了对乘法指令的支持,并引入了缓存技术来提高性能。

3. ARMv3:ARMv3指令集体系结构于1992年推出,支持更多的指令和功能,如虚拟内存管理单元(VMMU)和协处理器。

4. ARMv4:ARMv4指令集体系结构于1995年发布,引入了Thumb指令集,可以以压缩的形式执行16位指令,提高了代码密度和节能效果。

5. ARMv5:ARMv5指令集体系结构于1997年推出,引入了Jazelle技术,使处理器能够直接执行Java字节码。

6. ARMv6:ARMv6指令集体系结构于2002年发布,引入了Thumb-2技术,将16位Thumb指令和32位ARM指令混合使用,提高了代码密度和性能。

7. ARMv7:ARMv7指令集体系结构于2004年发布,引入了NEON SIMD(单指令多数据)扩展指令集,提供更高的并行计算能力。

8. ARMv8:ARMv8指令集体系结构于2011年推出,是一个重要的里程碑,引入了64位处理器架构(AArch64),并保持了与之前32位指令集的向后兼容性。

9. ARMv9:目前(2024年)尚未发布,但ARM Holdings已经透露正在研发ARMv9指令集体系结构。

ARMv9预计将进一步提升性能、安全性和AI加速能力。

上述是ARM指令集的主要发展历程,每个版本都带来了新的功能和改进,使ARM成为全球最受欢迎的处理器架构之一,并广泛应用于各个领域。

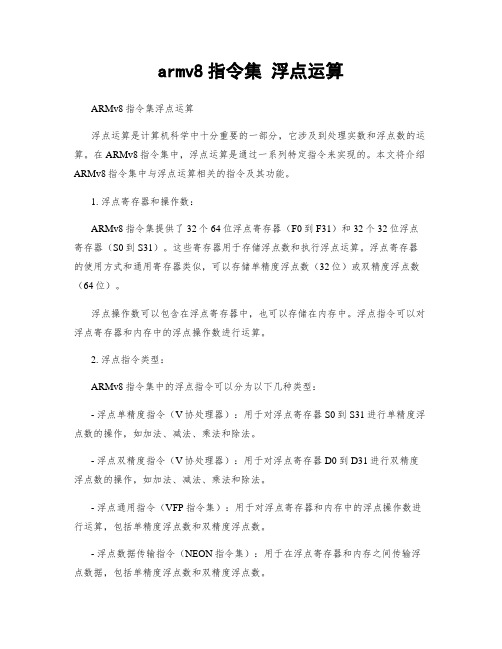

armv8指令集 浮点运算

armv8指令集浮点运算ARMv8指令集浮点运算浮点运算是计算机科学中十分重要的一部分,它涉及到处理实数和浮点数的运算。

在ARMv8指令集中,浮点运算是通过一系列特定指令来实现的。

本文将介绍ARMv8指令集中与浮点运算相关的指令及其功能。

1. 浮点寄存器和操作数:ARMv8指令集提供了32个64位浮点寄存器(F0到F31)和32个32位浮点寄存器(S0到S31)。

这些寄存器用于存储浮点数和执行浮点运算。

浮点寄存器的使用方式和通用寄存器类似,可以存储单精度浮点数(32位)或双精度浮点数(64位)。

浮点操作数可以包含在浮点寄存器中,也可以存储在内存中。

浮点指令可以对浮点寄存器和内存中的浮点操作数进行运算。

2. 浮点指令类型:ARMv8指令集中的浮点指令可以分为以下几种类型:- 浮点单精度指令(V协处理器):用于对浮点寄存器S0到S31进行单精度浮点数的操作,如加法、减法、乘法和除法。

- 浮点双精度指令(V协处理器):用于对浮点寄存器D0到D31进行双精度浮点数的操作,如加法、减法、乘法和除法。

- 浮点通用指令(VFP指令集):用于对浮点寄存器和内存中的浮点操作数进行运算,包括单精度浮点数和双精度浮点数。

- 浮点数据传输指令(NEON指令集):用于在浮点寄存器和内存之间传输浮点数据,包括单精度浮点数和双精度浮点数。

3. 浮点指令示例:下面是一些ARMv8指令集中常用的浮点指令的示例:- FADD:这个指令用于将两个单精度浮点数相加,并将结果存储在指定的浮点寄存器中。

- FSUB:这个指令用于将两个单精度浮点数相减,并将结果存储在指定的浮点寄存器中。

- FMUL:这个指令用于将两个单精度浮点数相乘,并将结果存储在指定的浮点寄存器中。

- FDIV:这个指令用于将两个单精度浮点数相除,并将结果存储在指定的浮点寄存器中。

类似地,对于双精度浮点数,可以使用相应的指令,如DADD、DSUB、DMUL和DDIV。

此外,ARMv8指令集还提供了其他一些常用的浮点指令,如比较指令(FCMP、FCMPE)、转换指令(FCVT)、取整指令(FRINT)、开平方指令(FSQRT)和求平均指令(FABD)等。

ARM指令集详解--汇编

ARM指令集详解--汇编1. 汇编1.1. 通⽤通⽤寄存器37个寄存器,31个通⽤寄存器,6个状态寄存器,R13指针sp,R14返回指针,R15为PC指针, cpsr_c代表的是这32位中的低8位,也就是控制位CPSR有4个8位区域:标志域(F)、状态域(S)、扩展域(X)、控制域(C)MSR - Load specified fields of the CPSR or SPSR with an immediate constant, orfrom the contents of a general-purpose register. Syntax: MSR{cond} _, #immed_8rMSR{cond} _, Rm where: cond is an optional condition code. is either CPSR orSPSR. specifies the field or fields to be moved. can be one or more of: ccontrol field mask byte (PSR[7:0]) x extension field mask byte (PSR[15:8]) sstatus field mask byte (PSR[23:16) f flags field mask byte (PSR[31:24]).immed_8r is an expression evaluating to a numeric constant. The constant mustcorrespond to an 8-bit pattern rotated by an even number of bits within a32-bit word. Rm is the source register.C 控制域屏蔽字节(psr[7:0])X 扩展域屏蔽字节(psr[15:8])S 状态域屏蔽字节(psr[23:16])F 标志域屏蔽字节(psr[31:24])CPSR寄存器FIQ和IRQ的区别?MODE(以下为⼆进制)10000⽤户模式PC,CPSR,R0~R1410001FIQ PC,CPSR,SPSR_fiq,R14_fiq~R8_fiq,R7~R010010IRQ PC,CPSR,SPSR_irq,R14_irq~R13_irq,R12~R010011管理模式(svc)PC,CPSR,SPSR_svc,R14_svc~R13_svc,R12~R010111终⽌模式PC,CPSR,SPSR_abt,R14_abt~R13_abt,R12~R011011未定义PC,CPSR,SPSR_und,R14_und~R13_und,R2~R011111系统模式(sys)PC,CPSR,R14 ~R01.2. 指令格式1) 基本格式<opcode>{<cond>}{S} <Rd>,<Rn>{,<opcode2>}其中,<>内的项是必须的,{}内的项是可选的,如<opcode>是指令助记符,是必须的,⽽{<cond>}为指令执⾏条件,是可选的,如果不写则使⽤默认条件AL(⽆条件执⾏)。

到底什么是Cortex、ARMv8、arm架构、ARM指令集、soc?一文帮你梳理基础概念【科普】

到底什么是Cortex、ARMv8、arm架构、ARM指令集、soc?⼀⽂帮你梳理基础概念【科普】前⾔有粉丝问我到底什么是ARM,搞不清楚Cortex、arm内核、arm架构、ARM指令集、soc这些概念都是什么关系,下⾯⼀⼝君给⼤家整理⼀下关于ARM相关的⼀些概念。

1、ARM既可以认为是⼀个公司的名字,也可以认为是对⼀类微处理器的通称,还可以认为是⼀种技术的名字。

2、ARM公司是专门从事基于RISC技术芯⽚设计开发的公司,作为知识产权供应商,本⾝不直接从事芯⽚⽣产,⽽是转让设计许可,由合作公司⽣产各具特⾊的芯⽚。

3、ARM处理器的内核是统⼀的,由ARM公司提供,⽽⽚内部件则是多样的,由各⼤半导体公司设计,这使得ARM设计嵌⼊式系统的时候,可以基于同样的核⼼,使⽤不同的⽚内外设,从⽽具有很⼤的优势。

下⾯我们针对这些概念,给⼤家逐⼀介绍。

ARM公司ARM⾸先是⼀个公司,即Advanced RISC Machines的缩写。

但是他本来并不叫这个名字,来看看ARM公司的成长历史。

1978年,⼀个名叫Hermann Hauser的奥地利籍物理学博⼠,还有他的朋友,⼀个名叫Chris Curry的英国⼯程师成⽴了⼀家名字叫“CPU”的公司。

这家CPU公司的全称,是Cambridge Processor Unit,字⾯意思是“剑桥处理器单元”。

CPU公司成⽴之后,主要从事电⼦设备设计和制造的业务。

他们接到的第⼀份订单,是制造赌博机的微控制器系统。

这个微控制器系统被开发出来后,称之为Acorn System 1。

之所以叫Acorn,就是因为他们想在电话黄页⾥排在Apple(苹果)公司的前⾯。

在Acorn System 1之后,他们⼜陆续开发了System 2、3、4,还有⾯向消费者的盒式计算机——Acorn Atom。

到了1981年,公司迎来了⼀个难得的机遇——英国⼴播公司BBC打算在整个英国播放⼀套提⾼电脑普及⽔平的节⽬,他们希望Acorn能⽣产⼀款与之配套的电脑。

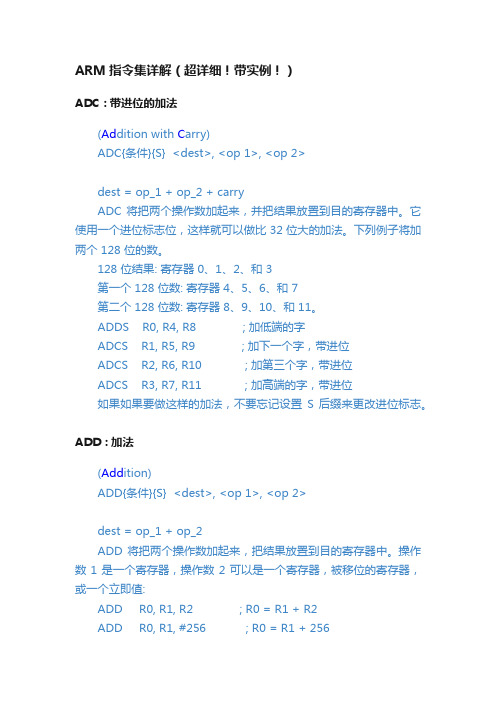

ARM指令集详解(超详细!带实例!)

ARM指令集详解(超详细!带实例!)ADC : 带进位的加法(Ad dition with C arry)ADC{条件}{S} <dest>, <op 1>, <op 2>dest = op_1 + op_2 + carryADC 将把两个操作数加起来,并把结果放置到目的寄存器中。

它使用一个进位标志位,这样就可以做比 32 位大的加法。

下列例子将加两个 128 位的数。

128 位结果: 寄存器 0、1、2、和 3第一个 128 位数: 寄存器 4、5、6、和 7第二个 128 位数: 寄存器 8、9、10、和 11。

ADDS R0, R4, R8 ; 加低端的字ADCS R1, R5, R9 ; 加下一个字,带进位ADCS R2, R6, R10 ; 加第三个字,带进位ADCS R3, R7, R11 ; 加高端的字,带进位如果如果要做这样的加法,不要忘记设置S 后缀来更改进位标志。

ADD : 加法(Add ition)ADD{条件}{S} <dest>, <op 1>, <op 2>dest = op_1 + op_2ADD 将把两个操作数加起来,把结果放置到目的寄存器中。

操作数 1 是一个寄存器,操作数 2 可以是一个寄存器,被移位的寄存器,或一个立即值:ADD R0, R1, R2 ; R0 = R1 + R2ADD R0, R1, #256 ; R0 = R1 + 256ADD R0, R2, R3,LSL#1 ; R0 = R2 + (R3 << 1)加法可以在有符号和无符号数上进行。

AND : 逻辑与(logical AND)AND{条件}{S} <dest>, <op 1>, <op 2>dest = op_1 AND op_2AND 将在两个操作数上进行逻辑与,把结果放置到目的寄存器中;对屏蔽你要在上面工作的位很有用。

ARMv8的学习笔记

ARMv8的学习笔记0. 状态执⾏态: AARCH64, AARCH32最⾼异常等级只能⼯作在Aarch64,其他EL可以⼯作在Aarch64或者Aarch32.SCR_EL3.RW, HCR_EL2.RW和PSTATE控制执⾏状态。

Security态: Security 和 non-SecuritySCR_EL3.NS 控制security状态1. 寄存器共31个64bit GPR寄存器X0~X30 ,X29做为FP, X30作为LR。

另外还有PC,SPs(SPEL0~SPEL3), ELRs(exception link register)。

32个128bit 浮点寄存器V0~V31PSTATE:处理器状态,pstate不是⼀个寄存器,由⼏个寄存器组成(条件寄存器:NZCV, 异常mask寄存器:DAIF, SP选择寄存器:SPSEL. 异常等级寄存器: CurrentEL)SPSRs:当异常发⽣时,PSTATE在SPSRs⾥⾯保存。

M[3:2] Encodes the Exception level, 0-3. M[1] ReservedM[0] Selects the SP:0 SP_EL01 SP_ELx2. 指令集A64指令集, 寄存器位宽 w-32位, x-64位寻址:寄存器索引寻址,PC相对寻址,Load/Store寻址3. 异常模型异常分为同步异常和异步异常。

同步异常有如下特点:a.由直接执⾏或者试图执⾏⼀条指令产品b.精确的(能保证给出正确的pc)异步异常也就是中断,包括SError,IRQ,FIQ。

ARMv8异常模型,Exception Level 从EL0到EL3. EL3权限最⼤EL0 Applications.EL1 OS kernel and associated functionsthat are typically described as privileged.EL2 Hypervisor.EL3 Secure monitor.异常基址寄存器:VBAR_ELx,要求1k字节对齐。

ARM指令集

MOV R1, Operand // R1 = Operand MVN R1, Operand // R1 = ~Operand

算术逻辑运算指令

算术运算 ADD、SUB、RSB、MUL、MLA

ADD R1, R2, Operand // R1 = R2 + Operand SUB R1, R2, Operand // R1 = R2 - Operand RSB R1, R2, Operand // R1 = R3 - Operand

3. 处理器内核自自动对LR进行行调整,即:LR = LR - 4

指令格式:<Opcond>{<cond>}{S} Rd, Rn {, Operand}

Operand

立立即数

收到合法性的限制

寄存器

R0~R15

寄存器移位

Rm, LSL #0x3 Rm, LSL Rx

数据处理指令

数据搬移指令 MOV、MVN

LDR R1, [R2, #8] //读取地址为R2+8处存储器中的内容至至寄存器R1中 STR R1, [R2, #8] //将寄存器R1中的值保存到地址为R2+8处的存储器中

块数据传送

<LDM|STM>{<cond>}<addressing_mode> Rb{!}, <寄存器 list> LDMxx/STMxx R1!, [R2, R3, R4]

ARM指令集(基础)

分支支跳转指令

跳转范围受到限制 PC +/- 32MB

指令格式:B{条件} label BL{条件} label

B指令

B label ,将l标号label处的地址 赋给PC,实现程序的跳转

ARM体系结构与指令集(PPT152页)

19

2.Q标志位

在带DSP指令扩展的ARM v5及更高版本中, bit[27]被指定用于指示增强的DAP指令是否发 生了溢出,因此也就被称为Q标志位。同样, 在SPSR中bit[27]也被称为Q标志位,用于在异 常中断发生时保存和恢复CPSR中的Q标志位。

20

(7)如果把Thumb指令集也当作ARM体系 结构的一部分,那么还可以加上:在Thumb体 系结构中以高密度16位压缩形式表示指令集。

6

2.2 ARM处理器工作模式

表2-1

ARM处理器的工作模式

处理器工作模式

简写

描述

用户模式(User)

usr 正常程序执行模式,大部分任务执行在这种模式下

快速中断模式(FIQ)

15

(2)当异常中断发生时,该异常模式特 定的物理寄存器R14被设置成该异常模式的返 回地址,对于有些模式R14的值可能与返回地 址有一个常数的偏移量(如数据异常使用SUB PC,LR,#8返回)。

R14也可以被用做通用寄存器使用。

16

2.3.2 状态寄存器

当前程序状态寄存器(Current Program Status Register,CPSR)可以在任何处理器 模式下被访问,它包含下列内容:

(1)R13_<mode> (2)R14_<mode>

其中,<mode>可以是以下几种模式之一: usr、svc、abt、und、irp及fiq。

14

寄存器R14又被称为连接寄存器(Link Register,LR),在ARM体系结构中具有下面 两种特殊的作用。

(1)每一种处理器模式用自己的R14存放 当前子程序的返回地址。

ARMv8内存管理架构.学习笔记

ARMv8内存管理架构.学习笔记⽬录第1章分级存储架构. 21.1基础认识 (2)1.1.1从数据通路描述. 21.1.2从数据交换单位描述. 21.1.3 Cache数据⼀致性拓扑结构. 31.2 系统层内存模型 (3)1.2.1内存属性. 31.2.2地址空间. 41.2.3字节编码⽀持. 4第2章虚拟内存系统架构(VMSA) 52.1 VMSAv8-64. 52.1.1地址转换系统. 52.1.2 内存转换粒度. 62.1.3 Address Translation Stage 82.1.4 描述符格式(descriptor format) 92.1.5 描述符内存属性. 112.2 VMSAv8-32. 112.2.1地址转换系统. 112.2.2转换表⽀持. 122.2.3描述符格式. 122.2.4 描述符内存属性. 132.3 TTW(地址转换流程). 142.3.1 VMSAv8-64 142.3.2 VMSAv8-32 16第3章 MMU Fault 193.1故障类型 (19)3.2 Kernel如何处理读取空指针? (19)3.2.1 ARM发⽣了什么?. 193.2.1 Kernel如何处理?. 20第4章 Vmalloc 224.1简介 (22)4.2基本流程 (22)4.3 代码实现分析 (23)第5章 Linux虚拟内存布局. 275.1 User内存布局 (27)5.1.1 Mem mapping内存分配⽅式(64位) 285.2 Kernel内存布局 (29)5.2.1 ARM64内核内存布局. 295.3 各内存域和物理内存映射关系 (31)第1章分级存储架构1.1基础认识通常为了保证计算机的整体性能,内存和CPU之间的通信需保证很⾼的传输速率,然⽽这受限制于内存的⼤⼩和昂贵的硬件实现,传输速率和内存容量⼤⼩的关系遵循“Smaller is faster”原则,使⽤更⼤容量的内存势必会增加传输延迟降低性能。

ARM指令集详解(超详细!带实例!)

ARM指令集详解(超详细!带实例!)算术和逻辑指令ADC : 带进位的加法(Ad dition with C arry)ADC{条件}{S} <dest>, <op 1>, <op 2>dest = op_1 + op_2 + carryADC 将把两个操作数加起来,并把结果放置到⽬的寄存器中。

它使⽤⼀个进位标志位,这样就可以做⽐ 32 位⼤的加法。

下列例⼦将加两个 128 位的数。

128 位结果: 寄存器 0、1、2、和 3第⼀个 128 位数: 寄存器 4、5、6、和 7第⼆个 128 位数: 寄存器 8、9、10、和 11。

ADDS R0, R4, R8 ; 加低端的字ADCS R1, R5, R9 ; 加下⼀个字,带进位ADCS R2, R6, R10 ; 加第三个字,带进位ADCS R3, R7, R11 ; 加⾼端的字,带进位如果如果要做这样的加法,不要忘记设置 S 后缀来更改进位标志。

这两个指令与普通指令在对操作数的限制上有所不同:1. 给出的所有操作数、和⽬的寄存器必须为简单的寄存器。

2. 你不能对操作数 2 使⽤⽴即值或被移位的寄存器。

3. ⽬的寄存器和操作数 1 必须是不同的寄存器。

4. 最后,你不能指定 R15 为⽬的寄存器。

译注:CMP 和 CMP 是算术指令,TEQ 和 TST 是逻辑指令。

把它们归⼊⼀类的原因是它们的 S 位总是设置的,就是说,它们总是影响标志位。

CMN : ⽐较取负的值(C o m pare N egative)CMN{条件}{P} <op 1>, <op 2>status = op_1 - (- op_2)CMN 同于 CMP,但它允许你与⼩负值(操作数 2 的取负的值)进⾏⽐较,⽐如难于⽤其他⽅法实现的⽤于结束列表的 -1。

这样与 -1 ⽐较将使⽤:CMN R0, #1 ; 把 R0 与 -1 进⾏⽐较详情参照 CMP 指令。

arm汇编指令集汇编入门第一篇小白也能看懂

arm汇编指令集汇编入门第一篇小白也能看懂如今,计算机科学与技术领域发展迅猛,其中包括一门被广泛应用的指令集架构—— ARM(Advanced RISC Machines)汇编指令集。

本文将从小白角度出发,向读者介绍ARM汇编指令集的基本概念和入门知识。

1. ARM汇编简介ARM汇编指令集是一种低级程序设计语言,用于在ARM微处理器上进行编程。

它不同于高级语言如C++或Java,具有较为底层的特性。

掌握ARM汇编指令集可以让开发者更深入地理解计算机内部运行原理,并能进行更加灵活和高效的编程。

2. ARM寄存器ARM汇编指令集使用一组寄存器来存储和处理数据。

其中,常用的寄存器有13个通用寄存器(R0-R12)、程序计数器(PC)、堆栈指针(SP)和链接寄存器(LR),另外还有一些特殊用途的寄存器。

这些寄存器提供了一种基于寄存器的计算模型,使得ARM汇编具有高效处理数据的能力。

3. 指令格式ARM汇编指令集的指令格式一般包括操作码和操作数。

操作码表示具体的操作,如加法、乘法等,而操作数则指定操作所需的寄存器和立即数等。

4. 数据处理指令ARM汇编指令集提供了一系列的数据处理指令,用于对寄存器中的数据进行处理。

这些指令包括基本的算术运算、逻辑运算以及移位操作等,可以实现各种数据处理需求。

5. 分支指令分支指令是ARM汇编指令集中常用的一类指令,用于根据条件进行跳转。

跳转指令可以在程序执行过程中改变程序执行的顺序,实现条件判断和循环等功能。

6. 存储器访问指令存储器访问指令用于在ARM汇编中对内存进行读写操作。

通过这些指令,可以将数据从寄存器中存储到内存中,或者将内存中的数据加载到寄存器中进行处理。

7. 输入输出指令输入输出指令用于实现与外部设备的交互。

例如,通过输入指令可以从键盘或其他输入设备中获取用户输入的数据,而通过输出指令可以将数据输出到显示器或其他输出设备中。

8. 常用例程ARM汇编指令集中有一些常用的例程,可以用于处理常见的编程任务。

armv8架构与指令集.整理.初稿

目 录第1章 ARMV8简介 (3)1.1基础认识 (3)1.2相关专业名词解释 (3)第2章 EXECUTION STATE (4)2.1提供两种E XECUTION S TATE (4)2.2决定E XECUTION S TATE的条件 (4)第3章 EXCEPTION LEVEL (5)3.1E XCEPTION L EVEL 与S ECURITY (5)3.1.1 EL3使用AArch64、AArch32的对比 (5)3.2EL X 和E XECUTION S TATE 组合 (7)3.3路由控制 (7)3.3.1 路由规则 (7)3.3.2 IRQ/FIQ/SError路由流程图 (9)第4章 ARMV8寄存器 (10)4.1AA RCH32重要寄存器 (10)4.1.1 A32状态下寄存器组织 (11)4.1.1 T32状态下寄存器组织 (11)4.2AA RCH64重要寄存器 (11)4.364、32位寄存器的映射关系 (12)第5章 异常模型 (13)5.1异常类型描述 (13)5.1.1 AArch32异常类型 (13)5.1.2 AArch64异常类型 (13)5.2异常处理逻辑 (14)5.2.1 寄存器操作 (14)5.2.2 路由控制 (15)5.3流程图对比 (15)5.3.1 IRQ 流程图 (16)5.3.2 Data Abort 流程图 (19)5.4源代码异常入口 (21)5.4.1 C函数入口 (21)5.4.2 上报流程图 (21)5.4.3 异常进入压栈准备 (22)5.4.4 栈布局 (22)第6章 ARMV8指令集 (23)6.1概况 (23)6.1.1 指令基本格式 (23)6.1.2 指令分类 (23)6.2指令详解 (23)6.2.1 跳转指令 (23)6.2.2 异常产生、返回指令 (24)6.2.3 系统寄存器指令 (24)6.2.4 数据处理指令 (24)6.2.5 load/store内存操作指令 (25)6.3指令编码 (26)6.4机器码分析 (26)第7章 流水线 (27)7.1简介 (27)7.1.1 简单三级流水线 (27)7.1.2 经典五级流水线 (27)7.2流水线冲突 (28)7.3指令并行 (28)第1章 ARMv8简介1.1基础认识ARMv8的架构继承以往ARMv7与之前处理器技术的基础,除了现有的16/32bit的Thumb2指令支持外,也向前兼容现有的A32(ARM 32bit)指令集,基于64bit的AArch64架构,除了新增A64(ARM 64bit)指令集外,也扩充了现有的A32(ARM 32bit)和T32(Thumb2 32bit)指令集,另外还新增加了CRYPTO(加密)模块支持。

ARMv8指令学习(1)

(1) ldur x0,[base,#simm9]

x0 = [base+simm9]指向的内容

(2) ldurb w0,[base,#simm9]

从[base+simm9]指向的内容中:取出一个byte,赋给w0.

w0 中的其它字节:用0 扩展得到.

ARMv8指令学习(1)

ARMv8指令学习(1)

1. TBNZ / TBZ / CBZ / CBNZ (1) TBNZ x0, #uimm6, label

Test and nch Not zero.

如果x0[uimm6]!=0 , then jump to label 位置处执行.

(2) TBZ x0, #uimm6, label

(3) ldursb w0,[base,#simm9]

Test and branch Zero.

如果x0[uimm6]==0 , then jump to label 位置处执行.

(3) CBZ x0, label

Compare and Branch Zero

如果x0==0 , then jump to label 位置处执行

(4) CBNZ x0, label

Compare and branch Not zero.

如果x0 !=0 , then jump to label 位置处执行

2. LDUR / LDURB / LDURSB / LDURH / LDURSH / LDURSW / STUR / STURB / STURH

它们都属于Load-Store Single Register(unscaledoffset)

armv8指令集 浮点运算 -回复

armv8指令集浮点运算-回复Armv8指令集中的浮点运算是指基于ARM处理器架构的第8版本指令集中用于进行浮点数计算的指令集。

本文将逐步回答关于Armv8指令集的浮点运算方面的内容。

第一部分:Armv8指令集简介ARMv8指令集是由ARM公司推出的一套先进的处理器架构指令集,用于基于ARM架构的各种处理器芯片。

该指令集提供了一系列指令,可实现高效的浮点数计算。

第二部分:浮点数表示在进行浮点数计算之前,我们需要了解浮点数的表示方式。

在Armv8指令集中,浮点数采用IEEE 754标准进行表示。

IEEE 754标准定义了单精度浮点数和双精度浮点数的表示方式,其中单精度浮点数占用32位,双精度浮点数占用64位。

第三部分:浮点数指令集Armv8指令集中提供了一套完整的浮点指令集,用于进行浮点数计算。

这些指令包括浮点数加法、减法、乘法和除法等基本操作,以及一些高级操作,如平方根、对数和三角函数等。

第四部分:浮点加法指令浮点加法是浮点数计算中最基本的操作之一。

在Armv8指令集中,可以使用add.f32指令进行单精度浮点数的加法运算,使用add.f64指令进行双精度浮点数的加法运算。

这些指令将两个浮点数相加,并将结果存储到目标寄存器中。

第五部分:浮点乘法指令浮点乘法是另一个常见的浮点数计算操作。

在Armv8指令集中,可以使用mul.f32指令进行单精度浮点数的乘法运算,使用mul.f64指令进行双精度浮点数的乘法运算。

这些指令将两个浮点数相乘,并将结果存储到目标寄存器中。

第六部分:浮点除法指令除法是浮点数计算中的重要操作之一。

在Armv8指令集中,可以使用div.f32指令进行单精度浮点数的除法运算,使用div.f64指令进行双精度浮点数的除法运算。

这些指令将两个浮点数相除,并将结果存储到目标寄存器中。

第七部分:高级浮点操作除了基本的浮点运算之外,Armv8指令集还提供了一些高级的浮点操作指令。

例如,sqrt.f32指令用于计算单精度浮点数的平方根,sqrt.f64指令用于计算双精度浮点数的平方根。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

目 录第1章 ARMV8简介 (3)1.1基础认识 (3)1.2相关专业名词解释 (3)第2章 EXECUTION STATE (4)2.1提供两种E XECUTION S TATE (4)2.2决定E XECUTION S TATE的条件 (4)第3章 EXCEPTION LEVEL (5)3.1E XCEPTION L EVEL 与S ECURITY (5)3.1.1 EL3使用AArch64、AArch32的对比 (5)3.2EL X 和E XECUTION S TATE 组合 (7)3.3路由控制 (7)3.3.1 路由规则 (7)3.3.2 IRQ/FIQ/SError路由流程图 (9)第4章 ARMV8寄存器 (10)4.1AA RCH32重要寄存器 (10)4.1.1 A32状态下寄存器组织 (11)4.1.1 T32状态下寄存器组织 (11)4.2AA RCH64重要寄存器 (11)4.364、32位寄存器的映射关系 (12)第5章 异常模型 (13)5.1异常类型描述 (13)5.1.1 AArch32异常类型 (13)5.1.2 AArch64异常类型 (13)5.2异常处理逻辑 (14)5.2.1 寄存器操作 (14)5.2.2 路由控制 (15)5.3流程图对比 (15)5.3.1 IRQ 流程图 (16)5.3.2 Data Abort 流程图 (19)5.4源代码异常入口 (21)5.4.1 C函数入口 (21)5.4.2 上报流程图 (21)5.4.3 异常进入压栈准备 (22)5.4.4 栈布局 (22)第6章 ARMV8指令集 (23)6.1概况 (23)6.1.1 指令基本格式 (23)6.1.2 指令分类 (23)6.2指令详解 (23)6.2.1 跳转指令 (23)6.2.2 异常产生、返回指令 (24)6.2.3 系统寄存器指令 (24)6.2.4 数据处理指令 (24)6.2.5 load/store内存操作指令 (25)6.3指令编码 (26)6.4机器码分析 (26)第7章 流水线 (27)7.1简介 (27)7.1.1 简单三级流水线 (27)7.1.2 经典五级流水线 (27)7.2流水线冲突 (28)7.3指令并行 (28)第1章 ARMv8简介1.1基础认识ARMv8的架构继承以往ARMv7与之前处理器技术的基础,除了现有的16/32bit的Thumb2指令支持外,也向前兼容现有的A32(ARM 32bit)指令集,基于64bit的AArch64架构,除了新增A64(ARM 64bit)指令集外,也扩充了现有的A32(ARM 32bit)和T32(Thumb2 32bit)指令集,另外还新增加了CRYPTO(加密)模块支持。

1.2 相关专业名词解释AArch32 描述32bit Execution StateAArch64 描述64bit Execution StateA32、T32 AArch32 ISA (Instruction Architecture)A64 AArch64 ISA (Instruction Architecture)Interprocessing 描述AArch32和AArch64两种执行状态之间的切换SIMD Single-Instruction, Multiple-Data (单指令多数据)2.1 提供两种Execution State•ARMv8 提供AArch32 state和 AArch64 state 两种Execution State,下面是两种Execution State对比.Execution State NoteAArch32 提供13个32bit通用寄存器R0-R12,一个32bit PC指针 (R15)、堆栈指针SP (R13)、链接寄存器LR (R14)提供一个32bit异常链接寄存器ELR, 用于Hyp mode下的异常返回提供32个64bit SIMD向量和标量floating-point支持提供两个指令集A32(32bit)、T32(16/32bit)兼容ARMv7的异常模型AArch64 提供31个64bit通用寄存器X0-X30(W0-W30),其中X30是程序链接寄存器LR提供一个64bit PC指针、堆栈指针SPx 、异常链接寄存器ELRx提供32个128bit SIMD向量和标量floating-point支持定义ARMv8异常等级ELx(x<4),x越大等级越高,权限越大定义一组PE state寄存器PSTATE(NZCV/DAIF/CurrentEL/SPSel等),用于保存PE当前的状态信息2.2 决定Execution State的条件只有通过复位或者发生异常这两种方式才可以改变Execution State SPSR_EL1.M[4] 决定EL0的执行状态,为0 =>64bit ,否则=>32bit HCR_EL2.RW 决定EL1的执行状态,为1 =>64bit ,否则=>32bitSCR_EL3.RW确定EL2 or EL1的执行状态,为1 =>64bit ,否则=>32bit•ARMv8定义EL0-EL3共 4个Exception Level来控制PE的行为. ELx(x<4),x越大等级越高,执行特权越高执行在EL0称为非特权执行EL2 没有Secure state,只有Non-secure stateEL3 只有Secure state,实现EL0/EL1的Secure 和Non-secure之间的切换 EL0 & EL1 必须要实现,EL2/EL3则是可选实现3.1 Exception Level 与SecurityEL0 ApplicationEL1 Linux kernel- OSEL2 Hypervisor (可以理解为上面跑多个虚拟OS)EL3 Secure Monitor (ARM Trusted Firmware)3.1.1 EL3使用AArch64、AArch32的对比NoteCommon User mode 只执行在Non- Secure EL0 or Secure ELOSCR_EL3.NS决定的是low level EL的secure/non-secure状态,不是绝对自身的EL2只有Non-secure stateEL0 既有Non-secure state 也有Secure stateEL3 AArch64 若EL1使用AArch32,那么Non- Secure {SYS/FIQ/IRQ/SVC/ABORT/UND} 模式执行在Non-secure EL1,Secure {SYS/FIQ/IRQ/SVC/ABORT/UND}模式执行在Secure EL1若 SCR_EL3.NS == 0,则切换到Secure EL0/EL1状态,否则切换到Non-secure ELO/EL1状态Secure state 只有Secure EL0/EL1/EL3EL3 AArch32 User mode 只执行在Non- Secure EL0 or Secure ELO若EL1使用AArch32,那么Non- Secure {SYS/FIQ/IRQ/SVC/ABORT/UND} 模式执行在Non-secure EL1,Secure {SYS/FIQ/IRQ/SVC/ABORT/UND}模式执行在EL3Secure state只有Secure EL0/EL3,没有Secure EL1,要注意和上面的情况不同•当EL3使用AArch64时,有如下结构组合:•当EL3使用AArch32时,有如下结构组合:3.2 ELx 和 Execution State 组合•假设EL0-EL3都已经实现,那么将会有如下组合五类组合EL0/EL1/EL2/EL3 => AArch64 此两类组合不存在64bit –> 32bit之间的所谓Interprocessing 切换EL0/EL1/EL2/EL3 => AArch32EL0 => AARCH32,EL1/EL2/EL3 => AArch64 此三类组合存在64bit –> 32bit之间的所谓Interprocessing 切换EL0/EL1 => AArch32,EL2/EL3 => AArch64EL0/EL1/EL2 => AArch32,EL3 => AArch64组合规则字宽(ELx)<=字宽(EL(x+1)) { x=0,1,2 } 原则:上层字宽不能大于底层字宽• 五类经典组合图示3.3路由控制•如果EL3使用AArch64,则有如下异常路由控制3.3.1 路由规则•路由规则如下图所示(from ARMv8 Datasheet):•规则小结如下:若SPSR_EL1.M[4] == 0,则决定ELO使用AArch64,否则AArch32若SCR_EL3.RW == 1,则决定 EL2/EL1 是使用AArch64,否则AArch32若SCR_EL3.{EA, FIQ, IRQ} == 1,则所有相应的SError\FIQ\IRQ 中断都被路由到EL3若HCR_EL2.RW == 1,则决定EL1使用AArch64,否则使用AArch32若HCR_EL2.{AMO, IMO, FMO} == 1,则EL1/EL0所有对应的SError\FIQ\IRQ中断都被路由到EL2,同时使能对应的虚拟中断VSE,VI,VF若HCR_EL2.TGE == 1,那么会忽略HCR_EL2.{AMO, IMO, FMO}的具体值,直接当成1处理,则EL1/EL0所有对应的SError\FIQ\IRQ中断都被路由到EL2,同时禁止所有虚拟中断注意: SCR_EL3.{EA, FIQ, IRQ}bit的优先级高于HCR_EL2.{AMO, IMO, FMO} bit优先级,路由优先考虑SCR_EL33.3.2 IRQ/FIQ/SError路由流程图第4章 ARMv8寄存器4.1 AArch32重要寄存器寄存器类型 Bit 描述R0-R14 32bit 通用寄存器,但是ARM不建议使用有特殊功能的R13,R14,R15当做通用寄存器使用. SP_x 32bit 通常称R13为堆栈指针,除了User和Sys模式外,其他各种模式下都有对应的SP_x寄存器:x ={ und/svc/abt/irq/fiq/hyp/mon}LR_x 32bit 称R14为链接寄存器,除了User和Sys模式外,其他各种模式下都有对应的SP_x寄存器:x ={ und/svc/abt/svc/irq/fiq/mon},用于保存程序返回链接信息地址,AArch32环境下,也用于保存异常返回地址,也就说LR和ELR是公用一个,AArch64下是独立的. ELR_hyp 32bit Hyp mode下特有的异常链接寄存器,保存异常进入Hyp mode时的异常地址PC 32bit 通常称R15为程序计算器PC指针,AArch32 中PC指向取指地址,是执行指令地址+8,AArch64中PC读取时指向当前指令地址.CPSR 32bit 记录当前PE的运行状态数据,CPSR.M[4:0]记录运行模式,AArch64下使用PSTATE代替 APSR 32bit 应用程序状态寄存器,EL0下可以使用APSR访问部分PSTATE值SPSR_x 32bit 是CPSR的备份,除了User和Sys模式外,其他各种模式下都有对应的SPSR_x寄存器:x ={ und/svc/abt/irq/fiq/hpy/mon},注意:这些模式只适用于32bit运行环境HCR 32bit EL2特有,HCR.{TEG,AMO,IMO,FMO,RW}控制EL0/EL1的异常路由SCR 32bit EL3特有,SCR.{EA,IRQ,FIQ,RW}控制EL0/EL1/EL2的异常路由,注意EL3始终不会路由 VBAR 32bit 保存任意异常进入非Hyp mode & 非Monitor mode的跳转向量基地址HVBAR 32bit 保存任意异常进入Hyp mode的跳转向量基地址MVBAR 32bit 保存任意异常进入Monitor mode的跳转向量基地址ESR_ELx 32bit 保存异常进入ELx时的异常综合信息,包含异常类型EC等,可以通过EC值判断异常class PSTATE 不是一个寄存器,是保存当前PE状态的一组寄存器统称,其中可访问寄存器有:PSTATE.{NZCV,DAIF,CurrentEL,SPSel},属于ARMv8新增内容,主要用于64bit环境下4.1.1 A32状态下寄存器组织4.1.1 T32状态下寄存器组织A32 T32 R0 R0 R1R1 R2 R2 R3 R3 R4 R4 R5 R5 R6 R6 R7 R7R8 并不是说T32下没有R8~R12,而是有限的指令才能访问到 R9 R10 R11 R12SP (R13) SP (R13) LR (R14) LR (R14) PC (R15) PC (R15) CPSR CPSR SPSRSPSR4.2 AArch64重要寄存器寄存器类型 Bit描述X0-X30 64bit 通用寄存器,如果有需要可以当做32bit使用:WO-W30LR (X30) 64bit 通常称X30为程序链接寄存器,保存跳转返回信息地址SP_ELx 64bit 若PSTATE.M[0] ==1,则每个ELx选择SP_ELx,否则选择同一个SP_EL0ELR_ELx 64bit 异常链接寄存器,保存异常进入ELx的异常地址(x={0,1,2,3})PC 64bit 程序计数器,俗称PC指针,总是指向即将要执行的下一条指令SPSR_ELx 32bit 寄存器,保存进入ELx的PSTATE状态信息NZCV 32bit 允许访问的符号标志位DIAF 32bit 中断使能位:D-Debug,I-IRQ,A-SError,F-FIQ ,逻辑0允许CurrentEL 32bit 记录当前处于哪个Exception levelSPSel 32bit记录当前使用SP_EL0还是SP_ELx,x= {1,2,3}HCR_EL2 32bit HCR_EL2.{TEG,AMO,IMO,FMO,RW}控制EL0/EL1的异常路由 逻辑1允许SCR_EL3 32bit SCR_EL3.{EA,IRQ,FIQ,RW}控制EL0/EL1/EL2的异常路由 逻辑1允许ESR_ELx 32bit 保存异常进入ELx时的异常综合信息,包含异常类型EC等.VBAR_ELx 64bit 保存任意异常进入ELx的跳转向量基地址 x={0,1,2,3}PSTATE 不是一个寄存器,是保存当前PE状态的一组寄存器统称,其中可访问寄存器有:PSTATE.{NZCV,DAIF,CurrentEL,SPSel},属于ARMv8新增内容,64bit下代替CPSR 4.3 64、32位寄存器的映射关系64-bit 32-bit64-bit OSRuningAArch32 App 64-bit 32-bitX0 R0 X20 LR_adt X1 R1 X21 SP_abt X2 R2 X22 LR_und X3 R3 X23 SP_und X4 R4 X24 R8_fiq X5 R5 X25 R9_fiq X6 R6 X26 R10_fiq X7 R7 X27 R11_fiq X8 R8_usr X28 R12_fiq X9 R9_usr X29 SP_fiq X10 R10_usr X30(LR) LR_fiq X11 R11_usr SCR_EL3 SCR X12 R12_usr HCR_EL2 HCR X13 SP_usr VBAR_EL1 VBAR X14 LR_usr VBAR_EL2 HVBAR X15 SP_hyp VBAR_EL3 MVBAR X16 LR_irq ESR_EL1 DFSR X17 SP_irq ESR_EL2 HSR X18 LR_svcX19 SP_svc第5章 异常模型5.1 异常类型描述5.1.1 AArch32异常类型异常类型 描述 默认捕获模式 向量地址偏移 Undefined Instruction 未定义指令 Und mode 0x04 Supervisor Call SVC调用 Svc mode 0x08 Hypervisor Call HVC调用 Hyp mode 0x08Secure Monitor Call SMC调用 Mon mode 0x08Prefetch abort 预取指令终止 Abt mode 0x0cData abort 数据终止 Abt mode 0x10IRQ interrupt IRQ中断 IRQ mode 0x18FIQ interrupt FIQ中断 FIQ mode 0x1cHyp Trap exception Hyp捕获异常 Hyp mode 0x14Monitor Trap exception Mon捕获异常 Mon mode 0x045.1.2 AArch64异常类型可分为同步异常 & 异步异常两大类,如下表描述:Synchronous(同步异常)异常类型 描述Undefined Instruction 未定义指令异常Illegal Execution State 非常执行状态异常System Call 系统调用指令异常(SVC/HVC/SMC)Misaligned PC/SP PC/SP未对齐异常Instruction Abort 指令终止异常Data Abort 数据终止异常Debug exception 软件断点指令/断点/观察点/向量捕获/软件单步 等Debug异常Asynchronous(异步异常)类型 描述SError or vSError 系统错误类型,包括外部数据终止IRQ or vIRQ 外部中断 or 虚拟外部中断FIQ or vFIQ 快速中断 or 虚拟快速中断异常进入满足以下条件向量地址偏移表Synchronous(同步异常)IRQ|| vIRQFIQ|| vFIQSError|| vSErrorSP => SP_EL0&& 从Current EL来0x000 0x080 0x100 0x180SP => SP_ELx&& 从Current EL来0x200 0x280 0x300 0x38064bit => 64bit&& 从Low level EL来0x400 0x480 0x500 0x58032bit => 64bit&& 从Low level EL来0x600 0x680 0x700 0x780•SP => SP_EL0,表示使用SP_EL0堆栈指针,由PSTATE.SP == 0决定,PSTATE.SP == 1 则SP_ELx; •32bit => 64bit 是指发生异常时PE从AArch32切换到AArch64的情况;5.2异常处理逻辑5.2.1 寄存器操作AArch32 state异常模式x = {und/svc/abt/irq/fiq/hyp/mon} 32位系统对应的7大异常模式PE根据异常类型跳转到对应的异常模式x 跳转到哪一种模式通常由路由关系决定保存异常返回地址到LR_x,用于异常返回用 LR也是对应模式的R[14]_x寄存器,32位系统下LR和ELR是同一个寄存器,而64位是独立的 备份PSTATE 数据到SPSR_x 异常返回时需要从SPSR_x恢复PSTATEPSTATE.M[4:0]设置为异常模式x PSTATE.{A,I,F} = 1PSTATE.T = 1,强制进入A32模式 PSTATE.IT[7:2] = “00000” PSTATE.M[4]只是对32位系统有效,64为下是保留的,因为64位下没有各种mode的概念.异常处理都要切换到ARM下进行;进入异常时需要暂时关闭A,I,F中断;根据异常模式x的向量偏移跳转到进入异常处理 各个mode有对应的Vector base addr + offsetAArch64 stateELx, x = {1,2,3} 代表目标EL1\EL2\EL3, EL0不能作为目标EL 保存PSTATE 数据到SPSR_ELx 异常返回时需要从SPSR_ELx中恢复PSTATE保存异常进入地址到ELR_ELx,同步异常(und/abt等)是当前地址,异步异常(irq/fiq等)是下一条指令地址 64位架构LR和ELR是独立分开的,这点和32位架构有所差别保存异常原因信息到ESR_ELx ESR_ELx.EC代表Exception Class,关注这个bitPE根据目标EL的异常向量表中定义的异常地址强制跳转到异常处理程序 跳转到哪个EL使用哪个向量偏移地址又路由关系决定堆栈指针SP的使用由目标EL决定 (SPSR_ELx.M[0] == 1) ? h(ELx): t(EL0)5.2.2 路由控制Execution State 异步异常(中断)路由控制位、优先级排列. 1允许 0禁止AArch32Asynchronous Data Abort (异步数据终止) SCR.EA HCR.TGEHCR.AMOIRQ or vIRQSCR.IRQ HCR.TGE HCR.IMO FIQ or vFIQSCR.FIQ HCR.TGE HCR.FMOAArch64SError or vSErrorSCR_EL3.EA HCR_EL2.TGE HCR_EL2.AMO IRQ or vIRQSCR_EL3.IRQ HCR_EL2.TGE HCR_EL2.IMO FIQ or vFIQSCR_EL3.FIQ HCR_EL2.TGE HCR_EL2.FMO• 若HCR_EL2.TGE ==1所有的虚拟中断将被禁止,HCR.{AMO,IMO,FMO} HCR_EL2.{AMO,IMO,FMO}被当成1处理.5.3流程图对比AArch32、AArch64架构下IRQ 和Data Abort 异常处理流程图对比.Data-abort-AArch32.jpgData-abort-AArch64.jpgIRQ-AArch32.jpgIRQ-AARCH64-1.jpg5.3.1 IRQ 流程图 5.3.1.1 AArch325.3.1.2 AArch645.3.2 Data Abort 流程图 5.3.2.1 AArch325.3.2.2 AArch645.4 源代码异常入口 5.4.1 C函数入口异常类型AArch32 State AArch64 State所在文件 C 函数 所在文件 C 函数Und arm/kernel/traps.c do_undefinstr Arm64/kernel/traps.c do_undefinstr Data Abort arm/mm/fault.c do_DataAbort arm64/mm/fault.c do_mem_abort IRQ arm/kernel/irq.c asm_do_IRQ arm64/kernel/irq.c handle_IRQ FIQSystem Call5.4.2 上报流程图例举Data Abort 和 IRQ中断的入口流程图5.4.2.1 Data Abort 上报5.4.2.2 IRQ上报5.4.3 异常进入压栈准备分析64位kernel_entry 压栈代码逻辑(代码路径:kernel/arch/arm64/kernel/entry.S)• sp指向 #S_LR – #S_FRAME_SIZE 位置 #S_FRAME_SIZE是pt_regs结构图的size• 依次把x28-x29 … x0-x1 成对压入栈内 每压入一对寄存器,sp指针就移动 -16 =((64/8)*2)字节长度,栈是向地址减少方向增长的. • 保存sp+#S_FRAME_SIZE数据到x21 add x21, sp, #SP_FRAME_SIZE• 保存elr_el1到x22 mrs x22, elr_el1• 保存spsr_el1到x23 mrs x23, spsr_el1• 把lr、x21写入sp+#S_LR地址内存 保存lr和x21的数据到指定栈内存位置• 把x22、x23写入sp+#S_PC地址内存 保存elr,spsr数据到指定栈内存位置5.4.4 栈布局第6章 ARMv8指令集6.1 概况6.1.1 指令基本格式<Opcode> {<Cond>} {S} <Rd> , <Rn> { , <Opcode2> }(其中尖括号是必须的,花括号是可选的).标识符 Note 是否必须 Opcode 操作码,也就是助记符,说明指令需要执行的操作类型 YES Cond 指令执行条件码,在编码中占4bit,0b0000 -0b1110 NOS 条件码设置项,决定本次指令执行是否影响PSTATE寄存器响应状态位值 NO Rd 目标寄存器,ARM指令可以选择R0-R14,Thumb指令大部分只能选择RO-R7 YES Rn 第一个操作数的寄存器,和Rd一样,不同指令有不同要求 YES Opcode2 第二个操作数,可以是立即数,寄存器Rm和寄存器移位方式(Rm,#shit)NO6.1.2 指令分类指令类型 例举1、跳转指令 B.cond\B\BL\BX\BLX2、异常产生指令 SVC\HVC\SMC\ERET\BRK3、系统寄存器指令 MRS\MSR4、数据处理指令 MOV\MVN\ADD\SUB\AND\EOR\BIC\ADC5、load/store 内存操作指令 STP\LDR6、协处理指令6.2 指令详解6.2.1 跳转指令Opcode NoteB 条件跳转BL 跳转前会把当前指令的下一条指令保存到R14 (lr)BX 只能用于寄存器寻址,寄存器最低位值用于切换ARM/Thumb工作状态,ARM/Thumb的切换只能通过跳转实现,不能通过直接write register方式实现.BLX BL & BX的交集CBNZ 比较非0跳转CBZ 比较为0跳转TBNZ 测试位比较非0跳转TBZ 测试位比较0跳转BLR 带返回的寄存器跳转BR 跳转到寄存器RET 返回到子程序6.2.2 异常产生、返回指令Opcode NoteBRK 软件断点指令SVC 系统调用产生SVC异常,目标在EL1HVC 系统调用产生HVC异常,目标在EL2SMC 系统调用产生SMC异常,目标在EL3ERET 异常返回使用Current ELR & SPSR6.2.3 系统寄存器指令Opcode NoteMRS 数据传输: 通用寄存器 <= 系统寄存器,可以记忆为: S => RMSR 数据传输: 系统寄存器 <= 通用寄存器, 可以记忆为: R => S6.2.4 数据处理指令Opcode Note数据传输指令MOV 将待传输数据传输给目标寄存器MVN 先将待传输数据按位取反运算,再传送到目标寄存器数据比较指令CMP 数据比较指令,结果不保证但是影像PSTATE标志位CMN 先将数据按位取反运算,然后执行CMP的操作TST 用于一个寄存器内容和另外一个寄存器内容进行按位与运算,根据结果更新PSTAT标志位,用于检测是否设置了特定的bitTEQ 用于一个寄存器内容和另外一个寄存器内容进行按位异或运算,逻辑运算指令AND 逻辑与运算ORR 逻辑或运算EOR 逻辑异或运算BIC 逻辑清零,如:BIC R1, R1, #0X0F // 将R1的低四位清零,其他位不变算术运算指令ADD 算术求和ADC 带进位算术求和SUB 算术求差SBC 是将操作数1减去操作数2,再减去标志位C的取反值,结果送到目的寄存器RSB 逆向减法,操作数2 –操作数1,结果RdRSC 带借位的逆向减法指令,将操作数2减去操作数1,再减去标志位C的取反值,结果送Rd乘法和乘加指令MUL 操作数1 × 操作数2 ,结果送RdMLASMULLSMLALUMULLUMLAL6.2.5 load/store内存操作指令Opcode Note单个加载存储LDR LDR {条件} 目的寄存器, <存储器地址>, 从内存地址中读取数据传送到RdSTR STR {条件} 源寄存器, <存储器地址>, 把源寄存器中的数据存到目标内存地址批量加载存储LDM LDM {条件} {类型} 基址寄存器{!} ,寄存器列表{^}从内存中加载批量数据到寄存器堆STM STM {条件} {类型} 基址寄存器{!} ,寄存器列表{^}把寄存器堆中批量数据存储到指定内存地址其中{类型含义}:{类型} NoteIA 每次操作后,地址加4IB 每次操作前,地址加4DA 每次操作后,地址减4DB 每次操作前,地址减4FD 满递减堆栈ED 空递减堆栈FA 满递增堆栈EA 空递增堆栈6.3 指令编码 6.4 机器码分析第7章 流水线7.1 简介1、不能减少单指令的响应时间,和single-cycle指令的响应时间是相同的2、多指令同时使用不同资源,可提升整体单cycle内的指令吞吐量,极大提高指令执行效率3、指令执行速率被最慢的流水线级所限制,执行效率被依赖关系限制影响7.1.1 简单三级流水线IF Instruction fetch 取指ID Instruction decode & register file read 译码 & 读取寄存器堆数据 EX Execution or address calculation 执行 or 地址计算图示:7.1.2 经典五级流水线IF Instruction fetch 取指ID Instruction decode & register file read 译码 & 读取寄存器堆数据 EX Execution or address calculation 执行 or 地址计算MEM Data memeory access 读写内存数据WB Write back 数据写回到寄存器堆图示:7.2 流水线冲突类型 Note 解决方法结构冲突 不同指令同时占用问储器资源冲突,早期处理器程序、数据存储器混合设计产生的问题。