NPN BJT制备工艺流程

BJT简介

BJT工作原理BJT即Bipolar Juncti ON Transistor的缩写,译为双极结型晶体管。

实际上就是我们通常所说的三极管,BJT是通过一定的工艺将两个PN结结合在一起的器件,有PNP和NPN两种组合结构。

BJT的原理BJT是由2块N型半导体中间夹着一块P型半导体所组成,发射区与基区之间形成的PN结称为发射结,而集电区与基区形成的PN结称为集电结,三条引线分别称为发射极e、基极b和集电极。

当b点电位高于e点电位零点几伏时,发射结处于正偏状态,而C点电位高于b点电位几伏时,集电结处于反偏状态,集电极电源Ec要高于基极电源Ebo。

在制造BJT时,有意识地使发射区的多数载流子浓度大于基区的,同时基区做得很薄,而且,要严格控制杂质含量,这样,一旦接通电源后,由于发射结正确,发射区的多数载流子(电子)极基区的多数载流子(控穴)很容易地截越过发射结构互相向反方各扩散,但因前者的浓度基大于后者,所以通过发射结的电流基本上是电子流,这股电子流称为发射极电流Ie。

由于基区很薄,加上集电结的反偏,注入基区的电子大部分越过集电结进入集电区而形成集电集电流Ic,只剩下很少(1-10[%])的电子在基区的空穴进行复合,被复合掉的基区空穴由基极电源Eb重新补纪念给,从而形成了基极电流Ibo根据电流连续性原理得:Ie=Ib+Ic这就是说,在基极补充一个很小的Ib,就可以在集电极上得到一个较大的Ic,这就是所谓电流放大作用,Ic与Ib是维持一定的比例关系,即:β1=Ic/Ib式中:β--称为直流放大倍数,集电极电流的变化量△Ic与基极电流的变化量△Ib之比为:β=△Ic/△Ib式中β--称为交流电流放大倍数,由于低频时β1和β的数值相差不大,所以有时为了方便起见,对两者不作严格区分,β值约为几十至一百多。

BJT作为电流放大器件,在实际使用中常常利用其电流放大作用,通过电阻转变为电压放大作用。

NPN硅管的电流放大原理对于NPN管,它是由2块N型半导体中间夹着一块P型半导体所组成,发射区与基区之间形成的 PN结称为发射结,而集电区与基区形成的PN结称为集电结,三条引线分别称为发射极e、基极b和集电极c。

第二章_双极型晶体三极管(BJT)

传输到集电极的电流 发射区注入的电流

ICn

Rb

IE

IC ICBO IC

EB

IE

IE

一般要求 ICn 在 IE 中占的比例尽量大

ICBO IB

b IBn

c

IC

ICn

IEn e IE 一般可达 0.95 ~ 0.99

Rc EC

13

(2) i与C 的i关B 系

输入

b

+

cUCE 输出

e

V 回路UCE

回路

V

UBE

电流,UCE是输出电压;

VCC

25

1、共射输入特性曲线

I B f (U BE ) UCE 常数

(1) UCE = 0 时的输入特性曲线

Rb IB b c

VBB

+e

UBE _

IB/A

UCE 0

类似为PN结正偏时的伏安特性曲线。

O

U BE / V

IE = IC + IB IC IE ICBO

IB=IBn-ICBO

当IE=0时,IC=ICBO

IC ( IC IB ) ICBO

1

IC 1 IB 1 ICBO

IC IB (1 )ICBO

= IB ICEO

穿透电流。

其中:

1

共射直流电流放大 系数。

14

IC IB ICEO

• 直流参数

– 直流电流放大系数 和

– 极间反向电流 和ICBO ICEO

• 交流参数

– 交流电流放大系数 和

– 频率参数 和 f

fT

• 极限参数

集电极最大允许电流ICmax 集电极最大允许功耗PCmax 反向击穿电压

BJT直流参数测试

BJT、MOS直流参数测试实验顺序及注意事项1、复习指导书2、熟悉仪器(不开机)3、将功耗电阻调至合适位置,一般1k左右即可。

将集电极电压档调回到最小的档位.4、根据晶体管类型,设置正常工作状态下的偏置电压。

5、仪器调零(将基区零点、集电区零点分别在显示屏上显示,然后将之调至相同位置,注意,非调x、y轴位置旋钮——>这同时“等幅度"调整了两者显示位置,故为非调零)6、先调出正确的输出特性曲线,完成此步骤后,再测试指导书中的各项实验内容.为有效调出输出特性曲线时,注意:A.各极的正负偏置最重要(理论上自己分析正负)B、然后才是所施加电压大小C、没有输出特性曲线,可能偏置错误,也可能是管子尚未开启.此外,常见导致问题包括:1). 测试击穿电压或击穿电流时,因击穿电流较大,此时应“及时回调”,否则热击穿的话,需重新测试所有数据。

2)。

所用晶体管管脚易断,实验时管脚需要弯曲的话,应使其“弯曲点"远离封的装壳。

3)。

实验中若旋钮旋不动,则表明已调到最大或最小量程。

此时,“若”因旋钮指示的位置和面板上标示的最大/最小位置对不上,仍表明其所在位置为最大/最小量程档,此时,切勿“继续"用力用力旋拧,否则将导致旋钮故障进而无法继续实验!4). I C要保证较小,因所测对象是小功率管,一般1mA以下足够,勿太高(某些同学毫无概念甚至调到几百mA),这样很容易烧掉导致数据作废。

5). 实验中,切换量程时(尤其是集电极电压换量程时),务必注意需先将旋钮旋到最小,再换量程,经常的错误是直接换量程,导致的问题是:1)、电流过大,器件部分烧坏(现场检查或实验报告检查时,特性曲线与记录不一致,影响成绩); 2)、器件完全烧毁(如此数据全部作废);3)、更严重情况是仪器烧毁(成绩零)。

该情况试验中经常出现,特别提醒注意。

6).所测电流较大时,注意功耗电阻要增加,否则易烧.7).实验完毕,将各电阻调到最大,量程档调至最小,关机。

BJT-清华大学半导体物理与器件

Bipolar JunctionTransistors双极型晶体管14集成电路中的npn-BJT杂质分布特点:•两头大,中间小•发射区掺杂浓度比基区高很多•四层结构•A E < A C本征晶体管非本征晶体管•埋层•隔离:采用pn 结5双极晶体管的四个工作区9正向有源区(正向放大模式,有源模式)——发射结正偏,集电结反偏9反向有源区(反向放大模式)——发射结反偏,集电结正偏SaturationCutoffActive InvertedV CB (pnp )V BC (npn )V EB (pnp ) V BE (npn )9截止区——两个结都反偏9饱和区——两个结都正偏双极型晶体管使用时,有共基极、共发射极和共集电极三种接法。

BJT的电流方向67理想npn-BJT ( 原型BJT )8•发射结正偏•集电结反偏910处于正向有源区BJT 的内部少子分布示意图162. 杂质任意分布的晶体管理论BJT 的晶体管作用主要发生在基区,研究基区的特性是获得BJT 电流电压关系的关键。

•缓变基区——基区杂质分布为任意形式•通过缓变基区的研究,将获得BJT 的基区电场分布、载流子分布以及电流分布的公式•介绍BJT 的一个重要的参数——基区渡越时间常数182.1 基区电流求基区非平衡少子(电子) 分布及电流密度分布——Moll-Ross方法推导前提是6个基本假定:1)少子在基区中的运动是一维的2)基区宽度大于载流子的平均自由程3)基区中准中性近似成立4)载流子的迁移率等于常数(可以引入平均迁移率)5)基区处于小注入状态6)忽略基区复合(对于现代高β-BJT是成立的)1922问题:分析基区电流的漂移流成分与扩散流成分归一化基区非平衡少子浓度分布2.3 重掺杂发射区为了获得高增益,发射结要求高注入比,即I pE(–x E) << I nB(0) ,因此发射区要求重掺杂1) 禁带变窄•重掺杂会导致电子在杂质原子之间进行共有化运动。

双极集成电路中的BJT

双极集成电路中的BJT微电子学院贾新章2010年12月复习:集成电路工艺基本流程1. 实现选择性掺杂的三道基本工序(1) 氧化Si+O2=SiO2复习:集成电路工艺基本流程1. 实现选择性掺杂的三道基本工序(2) 光刻:与常规的洗像原理相同。

复习:集成电路工艺基本流程1. 实现选择性掺杂的三道基本工序(3) 扩散掺杂:扩散是一种常见的自然现象。

在IC 生产中,扩散的同时进行氧化。

复习:集成电路工艺基本流程2. 分立NPN晶体管管芯制备的工艺流程(1) 基区氧化:原始材料为N型硅片,将作为最终NPN晶体管的集电区。

复习:集成电路工艺基本流程2.分立NPN晶体管管芯制备的工艺流程(2) 基区光刻复习:集成电路工艺基本流程2.分立NPN晶体管管芯制备的工艺流程(3) 基区掺杂:采用扩散技术,掺入P型杂质,通过补偿,使衬底的一部分区域变为P型区,成为晶体管的基区。

同时表面又生成一层SiO2复习:集成电路工艺基本流程2.分立NPN晶体管管芯制备的工艺流程(4) 发射区光刻:在基区范围内的SiO2层上光刻出一个小窗口,确定发射区的范围。

复习:集成电路工艺基本流程2.分立NPN晶体管管芯制备的工艺流程(5) 发射区掺杂:采用扩散掺杂技术,掺入N型杂质,通过补偿,使一部分P型基区转变为N型,成为晶体管的发射区。

同时表面上又生成一层SiO2复习:集成电路工艺基本流程2.分立NPN晶体管管芯制备的工艺流程(6) 引线孔光刻:在基区和发射区范围内分别刻出窗口,用于制备电极。

复习:集成电路工艺基本流程2.分立NPN晶体管管芯制备的工艺流程(7) 淀积金属:将用于形成电极。

复习:集成电路工艺基本流程2.分立NPN晶体管管芯制备的工艺流程(8) “反刻”:采用光刻技术,将用作为E电极和B电极的金属保留,刻蚀掉其余部分。

硅片背面通过金属化形成C极。

构成晶体管管芯。

复习:集成电路工艺基本流程2.分立NPN晶体管管芯制备的工艺流程复习:集成电路工艺基本流程3.分立NPN晶体管版图:基本结构晶体管版图包括4层基区(Base)发射区(Emitter)引线孔(Contact)电极(Metallization)复习:集成电路工艺基本流程4. IC管芯中的特殊问题(1) 隔离(2) NPN晶体管集电区埋层的引入(3) 元器件之间的互连(4) 集成电路中的其他元器件复习:集成电路工艺基本流程4. IC管芯中的特殊问题(1) 隔离问题:采用常规NPN工艺,硅片衬底即为集电区,同一硅片上制作的多个NPN晶体管,集电区连在一起,显然不会与电路中元器件连接关系相一致。

芯片工艺bjt器件-概述说明以及解释

芯片工艺bjt器件-概述说明以及解释1.引言1.1 概述BJT器件是一种重要的半导体器件,广泛应用于电子电路中。

它是由三个掺杂不同类型的半导体材料组成的结构,包括发射极、基极和集电极。

BJT器件具有放大、开关和稳定电流的功能,是现代电子器件中不可或缺的一部分。

本文将重点介绍芯片工艺对BJT器件性能的影响。

芯片工艺是制造半导体器件的关键步骤,直接影响到器件的性能和稳定性。

了解芯片工艺对BJT器件的影响,有助于提高器件的工作效率和可靠性。

通过对BJT器件的基本原理、芯片工艺对性能的影响以及制造过程的详细介绍,本文旨在帮助读者更深入地了解BJT器件,为相关领域的研究和应用提供参考和指导。

文章结构部分的内容如下:1.2 文章结构本文分为三个部分来探讨芯片工艺对BJT器件的影响。

首先,我们将介绍BJT器件的基本原理,包括其结构和工作原理。

接着,我们将详细讨论芯片工艺对BJT器件性能的影响,分析不同工艺参数对器件性能的影响。

最后,我们将深入探讨BJT器件的制造过程,介绍制造过程中的关键步骤和技术。

通过本文的探讨,读者将了解到芯片工艺在BJT器件中的重要性,以及不同工艺对器件性能的影响,从而为相关领域的研究和应用提供参考依据。

1.3 目的:本文旨在探讨芯片工艺对BJT器件性能的影响,通过介绍BJT器件的基本原理和制造过程,分析芯片工艺在BJT器件中的应用及优化方向。

通过研究芯片工艺对BJT器件性能的影响,可以更好地了解器件的工作原理和性能特点,为进一步提升器件性能和研发更先进的电子器件提供参考。

同时,本文也将展望BJT器件在未来的发展趋势,为相关领域的研究和应用提供参考。

2.正文2.1 BJT器件的基本原理BJT(双极型晶体管)是一种三端元件,通常由P型半导体和N型半导体层叠而成。

它由两个PN结组成,分别称为发射结和集电结。

三个端子分别为发射极(E)、基极(B)和集电极(C)。

BJT工作的基本原理是基区的控制作用。

NPN BJT双极晶体管制备工艺流程

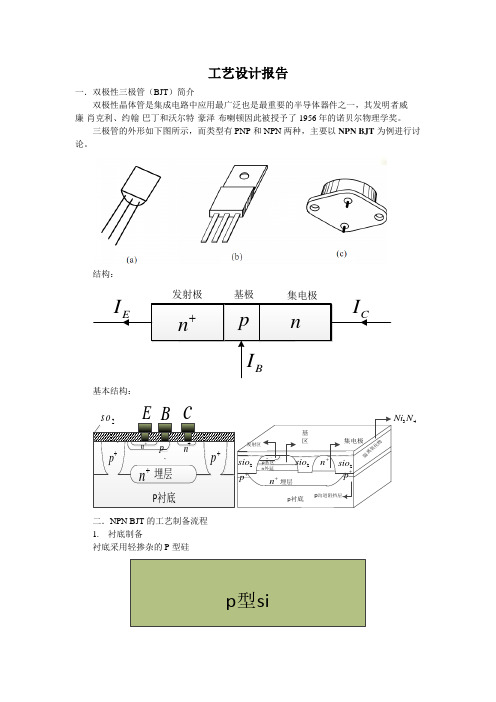

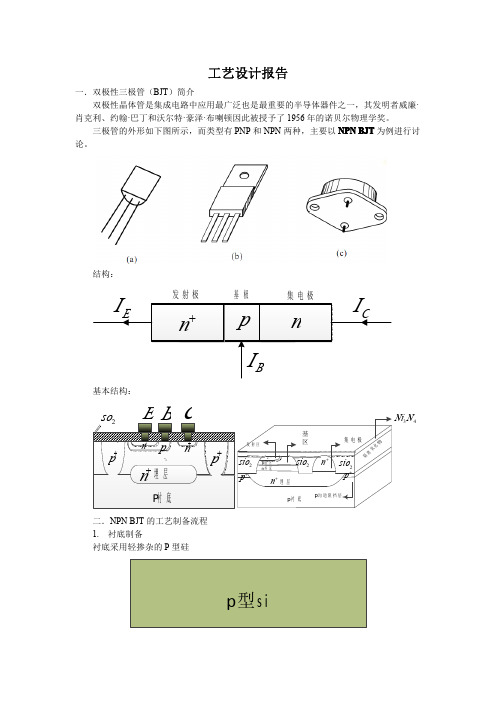

工艺设计报告一.双极性三极管(BJT )简介双极性晶体管是集成电路中应用最广泛也是最重要的半导体器件之一,其发明者威廉·肖克利、约翰·巴丁和沃尔特·豪泽·布喇顿因此被授予了1956年的诺贝尔物理学奖。

三极管的外形如下图所示,而类型有PNP 和NPN 两种,主要以NPN BJT 为例进行讨论。

结构:n+p nEI BI CI 发射极基极集电极基本结构:埋层n +P 衬底p+p +pn +n+2so E Bcp 衬底集电极2sio 2sio p +p +2sio n +埋层p 基区n 外延p 沟道阻挡层发射区n +基区n34Ni N 隔离氧化物二.NPN BJT 的工艺制备流程 1. 衬底制备衬底采用轻掺杂的P 型硅p 型si2. 埋层制备为了减小集电区的串联电阻,并减小寄生PNP管的影响,在集电区的外延层和衬底间通常要制作N+埋层。

首先在衬底上生长一层二氧化硅,并进行一次光刻,刻蚀出埋层区域,然后注入N型杂质(如磷、砷等),再退火(激活)杂质。

埋层材料选择标准是杂质在硅中的固溶度要大,以降低集电区的串联电阻;在高温下,杂质在硅中的扩散系数要小,以减少制作外延层时的杂质扩散效应;杂质元素与硅衬底的晶格匹配要好以减小应力,最好是采用砷。

3.外延层去除全部二氧化硅后,外延生长一层轻掺杂的硅。

此外延层作为集电区。

整个双极型集成电路便制作在这一外延层上。

外延生长主要考虑电阻率和厚度。

为减少结电容,提高击穿电压,降低后续工艺过程中的扩散效应,电阻率应尽量高一些;但为了降低集电区串联电阻,又希望它小一些。

4. 形成隔离区先生长一层二氧化硅,然后进行二次光刻,刻蚀出隔离区,接着预淀积硼(或者采用离子注入),并退火使杂质推进到一定距离,形成P 型隔离区。

这样器件之间的电绝缘就形成了。

5. 深集电极接触的制备这里的“深”指集电极接触深入到了N型外延层的内部。

为降低集电极串联电阻,需要制备重掺杂的N 型接触,进行第三次光刻,刻蚀出集电极,再注入(或扩散)磷并退火。

丁辛醇生产工艺

丁辛醇的生产工艺有两种路线,一种是以乙醛为原料,巴豆醛缩合加氢法;另一种是以丙烯、合成气为原料的低压羰基合成法,该法是当今国际上最为先进的技术之一,目前世界丁辛醇70%是由丙烯羰基化法生产的。

它以丙烯、合成气为原料,经低压羰基合成生产粗丁醛,再经丁醛处理、缩合、加氢反应制得丁辛醇。

低压羰基合成法生产丁辛醇典型的流程包括:原料净化、羰基合成、丁醛精制、缩合、加氢、粗醇精馏等工序。

丁醛精制是指粗丁醛除去轻组分后在异构塔内精馏分离得正丁醛和异丁醛。

缩合是指正丁醛脱去重组分后进入缩合系统,在NaOH存在、120℃和0.4MPa条件下,进行醛醛缩合生成辛烯醛(EPA)。

加氢一般是指正、异丁醛或混合丁醛或辛烯醛加氢生产相应的醇。

但是不论采用那一种方法,都必须经过丁烯醛/丁醛、辛烯醛加氢来制取丁醇和辛醇。

醛加氢是丁辛醇生产过程的重要组成部分,对丁辛醇的产品质量和生产过程的经济性都有很大的影响。

1丁辛醇加氢工艺路线丁醛加氢制备丁醇和辛烯醛加氢制备辛醇的工业化工艺路线主要有气相法和液相法两种。

液相加氢反应采用多段绝热固定床反应器,由于液相热容量较大,反应器内不用设置换热器。

根据反应条件,段间设置换热器移走反应热,防止醛的缩合反应。

BASF公司曾经采用过高压液相加氢,加氢的压力为25.33MPa。

高压加氢的唯一优点是氢气耗量较少,所用的液相加氢催化剂为70%Ni、25%Cu、5%Mn,该催化剂要求氢气分压不低于3.5MPa,所以总高压时,尾气的氢气浓度可降低,氢耗少。

但采用该高压工艺,原料氢气必须高压压缩,电耗大、设备费用大,目前已经被淘汰。

BASF公司和三菱化成工艺中醛的加氢采用中压液相加氢工艺,加氢压力为4.0-5.0MPa,加氢反应器形式采用填充床,反应温度为60-190℃。

气相加氢法由于操作压力相对较低,工艺设备简单而被广泛应用。

目前,工业上丁辛醇装置上大多采用铜系催化剂气相加氢工艺。

如U.D.J联合工艺中采用低压气相加氢,压力为0.59-0.69MPa。

npn bjt工艺设计报告

npn bjt工艺设计报告NPBjt工艺设计报告一、引言双极性晶体管(双晶管)是一种广泛使用的晶体管类型,被广泛应用于模拟电路和数字电路中。

本报告介绍了一个n-p-n型双晶体管的工艺流程,包括制造步骤和步骤的主要参数,同时讨论了属性和性能的影响。

实验的目的是使学生能够更深入地理解双晶体管的制造过程和结构原理,并获得从实验中获得的知识和技能,为以后的工作打下基础。

二、实验材料1.硅片:n - 型硅片。

2.蒸发器:电子束或热蒸发器,用于沉积n型和p型受控薄膜层。

3.掩模:用于控制n型和p型受控区的形状和大小。

4.反应室:用于在高温下形成薄膜层。

5.化学液:硝酸、氢氟酸和去离子水。

6.光刻胶:用于保护受控区域和刻蚀非受控区。

7.显影液:用于去除化学图形。

8.磨光机:用于去除硅片表面的杂质和平整表面。

9.染色液:用于染色控制n型和p型受控区域。

10.微探针:用于测量双晶体管的电学性能。

三、制造步骤1.准备硅片表面:将硅片用去离子水清洗并在高温条件下挥发硅表面的杂质。

2.沉积n型受控薄膜层:在反应室中,使用蒸发器将n型材料沉积在硅表面,同时使用掩模控制受控区的形状和大小。

3.沉积p型受控薄膜层:在上述过程之后,再次使用蒸发器将p型材料沉积在硅表面,控制受控区的形状和大小以及n型受控区的定位。

4.光学保护:使用光刻胶覆盖所有区域,并仅保留需要的n型和p型受控区域。

5.刻蚀非受控区:在上述过程中沉积上了光刻胶后,使用反应室中的化学液刻蚀未保护的区域。

6.显影:使用显影液去除上述过程所沉积的光刻胶。

7.染色:使用染色液,将受控区域区分成n型和p型。

8.测量电学特性:使用微探针测量受控区的电阻和电容等电学参数。

四、参数和工艺影响在制造双晶体管时,有几个关键参数和工艺步骤对结果有重要影响。

1.掩膜的质量:掩口的质量对受控区域定位的准确性十分重要。

低质量的掩膜可能导致受控区域的失效。

2.沉积温度:沉积温度会影响薄膜厚度和光刻胶的形状和大小,因此需要仔细控制。

NPN硅双极结型晶体管

缓变基区晶体管:基区掺杂浓度随位置变化。低注入下基区少子的运动形式既有扩散也有漂移。

5,心得体会

通过这次的课程设计,使我了解到工艺参数对器件的设计起到关键性的作用。一开始的时候根本就不知道怎么做这个课程设计,不知道从何入手,只有大量的上网查找各种资料,以及通过课本的参阅来帮助自己来完成这个设计。这个准备的过程我就花了3天半的时间。但 这个过程是必不可少的,俗话说的好磨刀不误砍柴工,工欲善其事,必先利其器,但做了大量的准备工作之后,完成这个课程设计 就顺利多了,通过这次课程设计的报告的研究探讨,让我感受到了课堂知识应用于实践的欣慰!

电子09--1

0906040106

李瑞雪

发射区、基区和集电区的典型掺杂浓度为1019,1017,1015 cm-3

BJT是非对称器件。

集电极电流:

假定:基区电子线性分布集电极电流为扩散电流

结论:集电极电流由基极和发射极之间的电压控制,这就是晶体管的工作原理

发射极电流:

一是由从发射区注入到基区的电子电流形成的(iE1);二是由基区的多子空穴越过B-E结注入到发射区(iE2),它也是正偏电流,表达形式同iE1

本次,我们主要研究设计NPN轨双极结型晶体管

3.方案设计与分析

3.1 NPN晶体管基本结构分析

如上图所示,由两个相距很近的PN结组成,基区宽度远远小于少子扩散长度,以上是NPN形式。

双极型晶体管基区中的电流传输过程与杂质分布形式有极密切的关系。

均匀基区晶体管:基区杂质浓度为常数。低注入下基区少子的运动形式为扩散。

C结反偏饱和,饱和时集电极电流不受控于VBE!

3.4假设:(采用一维理想模型)

三聚氰胺的工艺

三聚氰胺的工艺

三聚氰胺的生产工艺通常包括以下步骤:

1. 合成氰氨:氰化铵和氨气在高温高压条件下反应,生成氰氨。

2. 氰氨聚合:将氰氨与酚醛树脂(例如尿素甲醛树脂)混合,通过酸性催化剂催化反应,产生三聚氰胺。

3. 结晶和干燥:将产生的三聚氰胺溶液进行结晶、过滤和干燥,得到成品三聚氰胺产品。

这些步骤可以根据生产厂家的具体工艺进行微调,以确保产品质量和产量的稳定。

同时,生产过程中也需要严格控制各项参数,如温度、压力、催化剂的使用量等,以保证产品的质量和安全性。

硅平面NPN三极管设计与制作

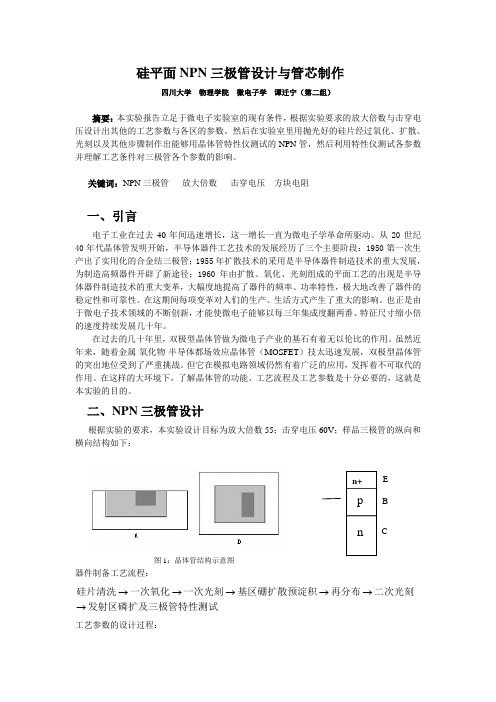

硅平面NPN 三极管设计与管芯制作四川大学 物理学院 微电子学 谭迁宁(第二组)摘要:本实验报告立足于微电子实验室的现有条件,根据实验要求的放大倍数与击穿电压设计出其他的工艺参数与各区的参数。

然后在实验室里用抛光好的硅片经过氧化、扩散、光刻以及其他步骤制作出能够用晶体管特性仪测试的NPN 管,然后利用特性仪测试各参数并理解工艺条件对三极管各个参数的影响。

关键词:NPN 三极管 放大倍数 击穿电压 方块电阻一、引言电子工业在过去40年间迅速增长,这一增长一直为微电子学革命所驱动。

从20世纪40年代晶体管发明开始,半导体器件工艺技术的发展经历了三个主要阶段:1950第一次生产出了实用化的合金结三极管;1955年扩散技术的采用是半导体器件制造技术的重大发展,为制造高频器件开辟了新途径;1960年由扩散、氧化、光刻组成的平面工艺的出现是半导体器件制造技术的重大变革,大幅度地提高了器件的频率、功率特性,极大地改善了器件的稳定性和可靠性。

在这期间每项变革对人们的生产、生活方式产生了重大的影响。

也正是由于微电子技术领域的不断创新,才能使微电子能够以每三年集成度翻两番、特征尺寸缩小倍的速度持续发展几十年。

在过去的几十年里,双极型晶体管做为微电子产业的基石有着无以伦比的作用。

虽然近年来,随着金属-氧化物-半导体都场效应晶体管(MOSFET )技太迅速发展,双极型晶体管的突出地位受到了严重挑战。

但它在模拟电路领域仍然有着广泛的应用,发挥着不可取代的作用。

在这样的大环境下,了解晶体管的功能、工艺流程及工艺参数是十分必要的,这就是本实验的目的。

二、NPN 三极管设计根据实验的要求,本实验设计目标为放大倍数55;击穿电压60V ;样品三极管的纵向和横向结构如下:图1:晶体管结构示意图 器件制备工艺流程:→→→→→→硅片清洗一次氧化一次光刻基区硼扩散预淀积再分布二次光刻发射区磷扩及三极管特性测试工艺参数的设计过程:E BC一)晶体管参数设计在实验室里,硅片的衬底电阻率为3-6Ω·CM ,查表一得所对应的Nc=1510厘米-3。

si npn 晶体管芯片工艺流程

si npn 晶体管芯片工艺流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor.I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!硅NPN晶体管芯片的制造工艺流程详解在现代电子技术中,硅基NPN晶体管是一种至关重要的组件,广泛应用于各种电路设计中,如放大器、开关和逻辑门等。

NPN BJT制备工艺流程

p型 si

4. 形成隔离区 先生长一层二氧化硅,然后进行二次光刻,刻蚀出隔离区,接着预淀积硼(或者 采用离子注入),并退火使杂质推进到一定距离,形成 P 型隔离区。这样器件之 间的电绝缘就形成了。

n外 延 层

p+

n+ n + 埋n 外层延 层

沟p+

沟p +

道

道

阻 挡

n外 延 层

阻 挡

层

工艺设计报告

一.双极性三极管(BJT)简介 双极性晶体管是集成电路中应用最广泛也是最重要的半导体器件之一,其发明者威廉·

肖克利、约翰·巴丁和沃尔特·豪泽·布喇顿因此被授予了 1956 年的诺贝尔物理学奖。 三极管的外形如下图所示,而类型有 PNP 和 NPN 两种,主要以 NPN BJT 为例进行讨

n+

n外 延 层

p+

n+埋层

Ni3 N4

p+

沟 道 阻 挡 层

n+

p+

p 基区

n外 延 层

n+

p+

沟

道

阻

挡

层

n+埋层

p型s i

n+

p+

p+

沟

p 基区

道 阻

挡

层

n外 延 层

n+

p+

沟

道

阻

挡

层

n+埋层

p型s i

9. 形成金属互联线 进行第七次光刻,形成互联金属布线。 10. 后续工序 测试、键合、封装等。

论。

结构:

IE

发射极

npj工艺的工艺过程

npj工艺的工艺过程1. 引言npj工艺是一种先进的制造工艺,它通过使用纳米粒子和纳米材料来实现高效、精确的加工和制造。

该工艺可以应用于多个领域,如电子、医疗、能源等,具有许多优点,如高精度、高效率和低成本。

本文将详细介绍npj工艺的工艺过程。

2. npj工艺的原理npj工艺是基于纳米粒子的加工技术,它利用了纳米尺度下材料的特殊性质。

纳米尺度下,物质的电子、光学和磁学性质会发生显著改变,因此可以实现更精确和高效的加工过程。

npj工艺主要包括以下几个步骤:2.1 纳米材料制备在npj工艺中,首先需要制备纳米材料。

常见的方法包括溶胶-凝胶法、气相沉积法和机械合成法等。

这些方法可以控制纳米材料的大小、形状和结构,以满足具体应用需求。

2.2 粘结剂的选择在npj工艺中,粘结剂起着连接纳米材料的作用。

粘结剂的选择对最终产品的性能和稳定性至关重要。

常见的粘结剂包括有机胶水、高分子材料和金属粉末等。

2.3 纳米材料的加工纳米材料的加工是npj工艺中最关键的步骤之一。

常见的加工方法包括喷射、沉积和压制等。

这些方法可以将纳米材料制备成所需形状,并实现高度精确和高效率的加工过程。

2.4 表面处理在npj工艺中,表面处理是提高产品性能和稳定性的重要步骤之一。

常见的表面处理方法包括氧化、镀金和涂层等。

这些方法可以改变纳米材料表面的化学和物理性质,以满足具体应用需求。

3. npj工艺在不同领域中的应用npj工艺可以应用于多个领域,以下是几个典型的应用案例:3.1 电子领域在电子领域,npj工艺可以用于制备高性能晶体管、显示器和传感器等。

通过控制纳米材料的尺寸和结构,可以实现更高的电子迁移率和更快的响应速度,从而提高电子产品的性能。

3.2 医疗领域在医疗领域,npj工艺可以用于制备纳米药物载体和生物传感器等。

纳米材料具有较大的比表面积和高度可调控性,可以实现药物的精确释放和生物分子的灵敏检测,从而提高医疗治疗效果。

3.3 能源领域在能源领域,npj工艺可以用于制备高效能源存储器件和太阳能电池等。

晶体管工艺流程

晶体管工艺流程1引言晶体管是现代电子技术中非常重要的一种器件,无论是计算机、手机、电视还是汽车、航天器等电子设备中,都离不开晶体管。

它是数字电路、模拟电路、功率电路等各个领域中非常基础的器件。

那么,晶体管是如何制造出来的呢?本文将详细介绍晶体管的工艺流程。

2晶体管的结构和原理在探讨晶体管的制造工艺之前,先了解一下晶体管的结构和原理。

晶体管主要由三部分组成:发射极(Emitter)、基极(Base)和集电极(Collector)。

其中,基极在正常情况下是没有电流流经的,收到发射极和集电极之间通过基极的电流控制。

晶体管的原理是在PN结的基础上加以改进和扩展的,比二极管的原理更为复杂。

晶体管是由一块受特殊工艺处理的半导体材料,如硅或锗制成。

基本工作原理是利用外加电场的控制作用,将产生在发射极和集电极之间的电流作微小的变化,从而可以实现放大、开关、正弦波和方波等多种不同形式的信号放大和处理。

3工艺流程的要点晶体管的制造工艺涉及到许多细致复杂的步骤,其中一些主要要点如下:3.1基片制备晶体管的制造是从基片加工开始的。

基片是一个非常薄的硅片,通常厚度约为0.5毫米至1毫米。

它的表面必须非常光滑、均匀,且没有任何瑕疵和杂质。

制作基片的主要步骤包括选择高纯度硅材料、高质量的制造工艺和表面处理技术。

3.2薄膜制备晶体管制造过程中需要用到许多不同材料的薄膜,例如金属导线、氧化物等。

这些薄膜经过特殊的工艺加工,可以使它们在晶体片上形成精密的结构,以便进行电路连接和器件控制等操作。

3.3沉淀沉淀是制造晶体管的核心工艺,也是整个流程中最为重要的步骤。

它是将原始材料在高温、高压、无氧净化环境下反应制得高纯度单晶芯片的过程。

在晶体制作过程中,常用的沉淀方法有CZ法、FZ法等。

3.4光刻和蚀刻光刻和蚀刻是在薄膜上刻画精确电路结构的关键步骤。

在光刻过程中,具体操作是将电路结构投射到光刻胶上,然后通过化学或物理方法将图案传递到硅基片表面。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

层

n +埋 层

p型 si

6. 基区的形成 先进行第四次光刻,刻蚀出基区,然后注入硼并退火,使其扩散形成基区。由于 基区掺杂元素及其分布直接影响器件电流增益、截止频率等特性,因此注入硼的 剂量和能量要特别加以控制。

n外 延 层

p+

n+ n +埋 层

n

p+

沟 道 阻 挡 层

集电极

p+ p基 区

n外 延 层

层

n +埋 层

p型 si

5. 深集电极接触的制备 这里的“深”指集电极接触深入到了 N 型外延层的内部。 为降低集电极串联电阻,需要制备重掺杂的 N 型接触,进行第三次光刻,刻蚀 出集电极,再注入(或扩散)磷并退火。

n外 延 层

n+

p+

n +埋 层

集电极

p+

沟

n+

p+

沟

道

道

阻 挡

n外 延 层

阻 挡

层

论。

结构:

IE

发射极

基极

n+

p

集电极

n

IC

IB

基本结构:

c so2 E B

Ni3 N 4

基

p+

n+ p n+

n+ 埋 层

发射区

区

集电极

物

化

氧

p+

n+

sio2

p基 区 n外 延

离 隔

sio2 n+ sio2

p+

n+ 埋 层

p+

P衬 底

p衬 底

p沟 道 阻 挡 层

二.NPN BJT 的工艺制备流程 1. 衬底制备 衬底采用轻掺杂的 P 型硅

p型s i

2. 埋层制备 为了减小集电区的串联电阻,并减小寄生 PNP 管的影响,在集电区的外延层和衬 底间通常要制作 N+埋层。首先在衬底上生长一层二氧化硅,并进行一次光刻,刻 蚀出埋层区域,然后注入 N 型杂质(如磷、砷等),再退火(激活)杂质。埋层 材料选择标准是杂质在硅中的固溶度要大,以降低集电区的串联电阻;在高温下, 杂质在硅中的扩散系数要小,以减少制作外延层时的杂质扩散效应;杂质元素与 硅衬底的晶格匹配要好以减小应力,最好是采用砷。

n+

p+

沟

道

阻

挡

层

n +埋 层

p型 si

7. 发射区形成 在基区上生长一层氧化物,进行第五次光刻,刻蚀出发射区,进行磷或砷注入(或 扩散),并退火形成发射区。

n外 延 层

n+

p+

n +埋 层

+

集电极

n+

p+

n+

p+

沟

p基 区

p+

沟

道

道

阻 挡

阻 挡

层

层

n外 延 层

n +埋 层

ห้องสมุดไป่ตู้

p型 si

8. 金属接触 淀积二氧化硅后,进行第六次光刻,刻蚀出接触也窗口,用于引出电极线。接触 孔中温江溅射金属铝形成欧姆接触。

n+埋 层

p型 si

3.外延层 去除全部二氧化硅后,外延生长一层轻掺杂的硅。此外延层作为集电区。整个双极型集 成电路便制作在这一外延层上。外延生长主要考虑电阻率和厚度。为减少结电容,提高击穿 电压,降低后续工艺过程中的扩散效应,电阻率应尽量高一些;但为了降低集电区串联电阻, 又希望它小一些。

n外 延 层

n +埋 层

p型 si

4. 形成隔离区 先生长一层二氧化硅,然后进行二次光刻,刻蚀出隔离区,接着预淀积硼(或者 采用离子注入),并退火使杂质推进到一定距离,形成 P 型隔离区。这样器件之 间的电绝缘就形成了。

n外 延 层

p+

n+ n + 埋n 外层延 层

沟p+

沟p +

道

道

阻 挡

n外 延 层

阻 挡

层

n+

n外 延 层

p+

n+埋层

Ni3 N4

p+

沟 道 阻 挡 层

n+

p+

p 基区

n外 延 层

n+

p+

沟

道

阻

挡

层

n+埋层

p型s i

n+

p+

p+

沟

p 基区

道 阻

挡

层

n外 延 层

n+

p+

沟

道

阻

挡

层

n+埋层

p型s i

9. 形成金属互联线 进行第七次光刻,形成互联金属布线。 10. 后续工序 测试、键合、封装等。

工艺设计报告

一.双极性三极管(BJT)简介 双极性晶体管是集成电路中应用最广泛也是最重要的半导体器件之一,其发明者威廉·

肖克利、约翰·巴丁和沃尔特·豪泽·布喇顿因此被授予了 1956 年的诺贝尔物理学奖。 三极管的外形如下图所示,而类型有 PNP 和 NPN 两种,主要以 NPN BJT 为例进行讨