DSP指令解释

DSP代码释义

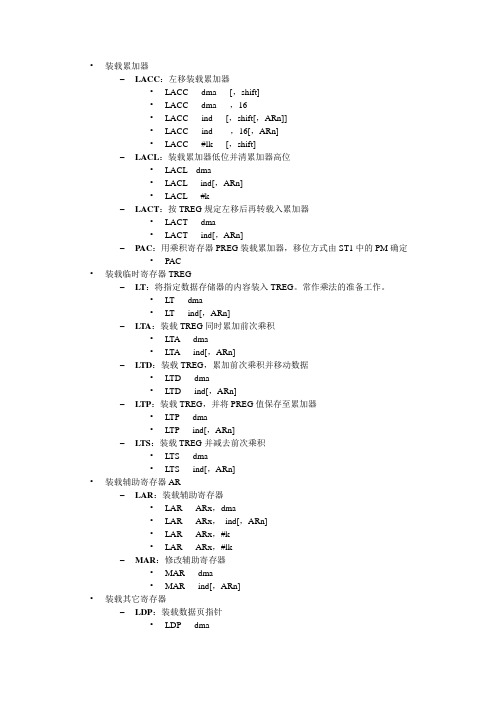

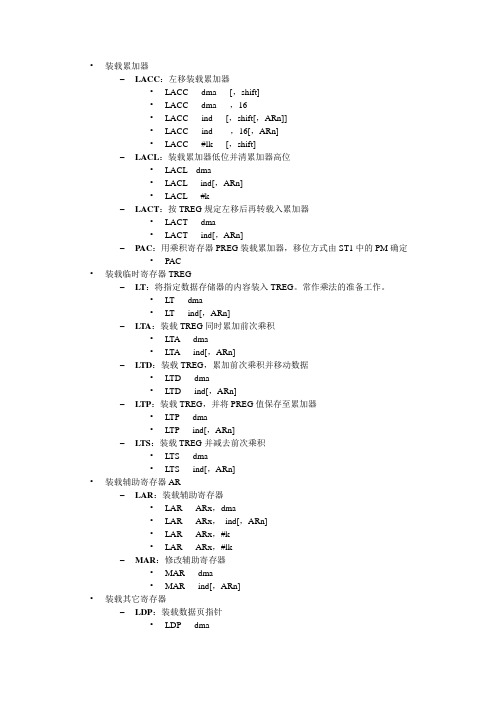

•装载累加器–LACC:左移装载累加器•LACC dma [,shift]•LACC dma ,16•LACC ind [,shift[,ARn]]•LACC ind ,16[,ARn]•LACC #lk [,shift]–LACL:装载累加器低位并清累加器高位•LACL dma•LACL ind[,ARn]•LACL #k–LACT:按TREG规定左移后再转载入累加器•LACT dma•LACT ind[,ARn]–PAC:用乘积寄存器PREG装载累加器,移位方式由ST1中的PM确定•PAC•装载临时寄存器TREG–LT:将指定数据存储器的内容装入TREG。

常作乘法的准备工作。

•LT dma•LT ind[,ARn]–LTA:装载TREG同时累加前次乘积•LTA dma•LTA ind[,ARn]–LTD:装载TREG,累加前次乘积并移动数据•LTD dma•LTD ind[,ARn]–LTP:装载TREG,并将PREG值保存至累加器•LTP dma•LTP ind[,ARn]–LTS:装载TREG并减去前次乘积•LTS dma•LTS ind[,ARn]•装载辅助寄存器AR–LAR:装载辅助寄存器•LAR ARx,dma•LAR ARx,ind[,ARn]•LAR ARx,#k•LAR ARx,#lk–MAR:修改辅助寄存器•MAR dma•MAR ind[,ARn]•装载其它寄存器–LDP:装载数据页指针•LDP dma•LDP ind[,ARn]•LDP #k–LPH:装载乘积寄存器高位字•LPH dma•LPH ind[,ARn]–LST:装载状态寄存器•LST #m,dma•LST #m,ind[,ARn]存储寄存器值•保存AR值(SAR)–SAR ARx, dma–SAR ARx, ind[, ARn] •保存PREG高位字(SPH)–SPH dma–SPH ind[, ARn]•保存PREG低位字(SPL)–SPL dma–SPL ind[, ARn]•保存状态寄存器ST0和ST1(SST)–SST #m, dma–SAR #m, ind[, ARn]堆栈操作•出栈至ACC低位字(POP )–POP•ACC低位字入栈(PUSH )–PUSH•出栈至数据存储器(POPD )–POPD dma–POPD, ind[, ARn]•数据存储器值入栈(PSHD )–PSHD dma–PSHD ind[, ARn]读写数据或程序存储器•数据存储器至数据存储器的块移动(BLDD )–BLDD #lk,dma–BLDD #lk,ind[, ARn]–BLDD dma ,#lk–BLDD ind ,#lk[, ARn] •程序存储器至数据存储器的块移动(BLPD )–BLPD #pma, dma–BLPD #pma, ind[, ARn] •片内数据存储器中的数据传送(DMOV )–DMOV dma–DMOV ind[, ARn]•长立即数写入数据存储器(SPLK )–SPLK #lk, dma–SPLK #lk, ind[, ARn]•读程序存储器(表读)(TBLR )–TBLR dma–TBLR ind[, ARn]•写程序存储器(表写)(TBLW )–TBLW dma–TBLW ind[, ARn]读写I/O单元•读I/O单元(IN )–IN dma, PA–IN ind, PA[, ARn]•写I/O单元(OUT )–OUT dma, PA–OUT ind, PA[, ARn]加法•左移加至ACC(ADD)–ADD dma [,shift]–ADD dma ,16–ADD ind [,shift[,ARn]]–ADD ind ,16[,ARn]–ADD #k–ADD #lk [,shift]•带进位位加至ACC (ADDC)–ADDC dma–ADDC ind [,ARn]•抑制符号扩展加至ACC (ADDS)–ADDS dma–ADDS ind [,ARn]•按TREG低4位规定左移加至ACC (ADDT)–ADDT dma–ADDT ind [,ARn]•加短立即数至当前AR(ADRK)–ADRK #k减法•左移后从ACC中减去(SUB)–SUB dma [,shift]–SUB dma ,16–SUB ind [,shift[,ARn]]–SUB ind ,16[,ARn]–SUB #k–SUB #lk [,shift]•带借位从ACC中减去(SUBB)–SUBB ind [,ARn]•条件减(SUBC):常用来实现除法–SUBC dma–SUBC ind [,ARn]•抑制符号扩展减(SUBS)–SUBS dma–SUBS ind [,ARn]•按TREG低4位左移后从ACC中减去(SUBT)–SUBT dma–SUBT ind [,ARn]•当前AR减去短立即数(SBRK)–SBRK #k•ACC减去PREG(SPAC)–SPAC•SUBC实现16位数除法的步骤–被除数(必须为正)置于累加器低位字中,且最高位放在bit15中,累加器高位字清零;–除数(必须大于0)放入数据存储单元中;–执行SUBC指令16次;–除的结果:商在累加器低位字;余数在累加器高位字。

第五章 DSP的汇编指令..

第五章 TMS320C55x系列DSP的汇编指令

(2) 用户自定义的双指令的并行

这两条指令的并行是通过用户或C编译器定义的。两条指令 同时执行两个操作,用并行符“||”区分并行执行的两条指令。 例:

MPYM *AR1+, *CDP, AC1 ;D单元的一个MAC来完成

||XOR AR2,T1

;A单元的ALU来完成

第五章 TMS320C55x系列DSP的汇编指令

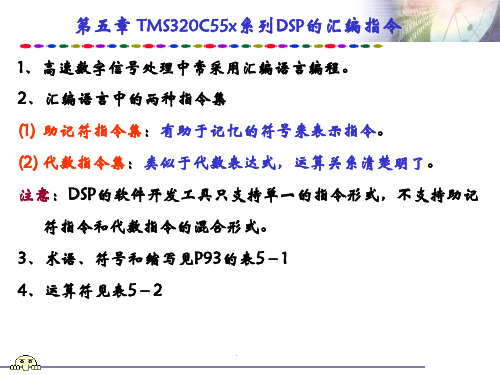

1、高速数字信号处理中常采用汇编语言编程。 2、汇编语言中的两种指令集 (1) 助记符指令集:有助于记忆的符号来表示指令。 (2) 代数指令集:类似于代数表达式,运算关系清楚明了。 注意:DSP的软件开发工具只支持单一的指令形式,不支持助记

符指令和代数指令的混合形式。 3、术语、符号和缩写见P93的表5-1 4、运算符见表5-2

令执行的条件:

TCx(测试/控制标志为1) !TCx(测试/控制标志为0)

TC1&TC2 TC1&!TC2 TC1|TC2 TC1|!TC2 TC1^TC2 TC1^!TC2

!TC1&TC2 !TC1&!TC2 !TC1|TC2 !TC1|!TC2 !TC1^TC2 !TC1^!TC2

第五章 TMS320C55x系列DSP的汇编指令

4、双16比特算术指令: [(1)语法、(2)操作数、(3)状态位] 在D单元中利用其ALU的双16比特模式,同时执行(并行)两个16

比特算术运算,包括加-减、减-加、两个加和两个减运算。

例:

说明: NO:不能并行执行 3:指令的长度为3字节 1:周期为1 X:在X(执行)流水线阶段处理

D – ALU:在D单元ALU执行。 执行结果:AC0=(*AR3)+CARRY+AC1 状态位: Affected by CARRY,C54CM,M40等

dsp汇编指令系统介绍(精)

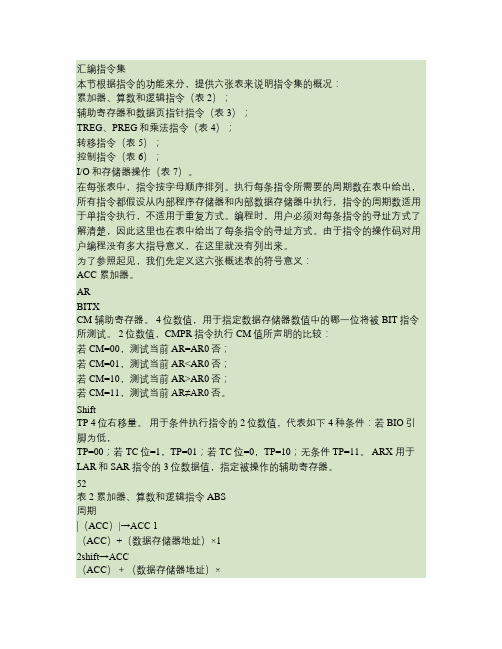

汇编指令集本节根据指令的功能来分,提供六张表来说明指令集的概况:累加器、算数和逻辑指令(表2);辅助寄存器和数据页指针指令(表3);TREG、PREG和乘法指令(表4);转移指令(表5);控制指令(表6);I/O和存储器操作(表7)。

在每张表中,指令按字母顺序排列。

执行每条指令所需要的周期数在表中给出,所有指令都假设从内部程序存储器和内部数据存储器中执行,指令的周期数适用于单指令执行,不适用于重复方式。

编程时,用户必须对每条指令的寻址方式了解清楚,因此这里也在表中给出了每条指令的寻址方式。

由于指令的操作码对用户编程没有多大指导意义,在这里就没有列出来。

为了参照起见,我们先定义这六张概述表的符号意义:ACC 累加器。

ARBITXCM 辅助寄存器。

4位数值,用于指定数据存储器数值中的哪一位将被BIT指令所测试。

2位数值,CMPR指令执行CM值所声明的比较:若CM=00,测试当前AR=AR0否;若CM=01,测试当前AR<AR0否;若CM=10,测试当前AR>AR0否;若CM=11,测试当前AR≠AR0否。

ShiftTP 4位右移量。

用于条件执行指令的2位数值,代表如下4种条件:若BIO引脚为低,TP=00;若TC位=1,TP=01;若TC位=0,TP=10;无条件TP=11。

ARX 用于LAR和SAR指令的3位数据值,指定被操作的辅助寄存器。

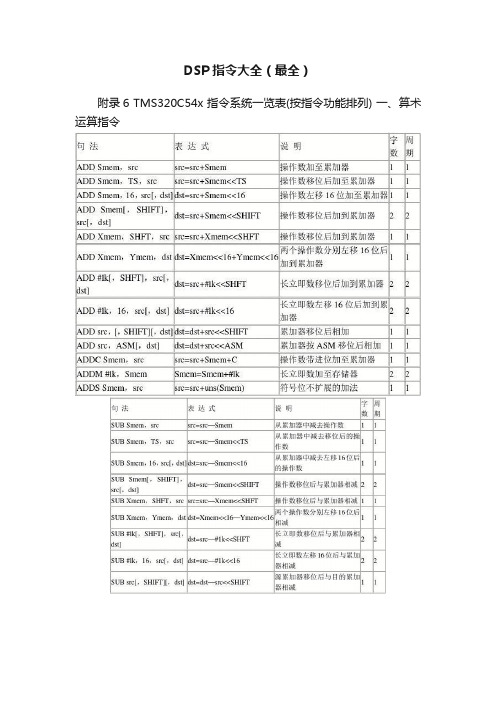

52表2 累加器、算数和逻辑指令 ABS周期|(ACC)|→ACC 1(ACC)+(数据存储器地址)×12shift→ACC(ACC)+(数据存储器地址)×216→ACC 1(ACC)+k→ACC 1shift(ACC)+lk×2→ACC 2指令功能(ACC)+(数据存储器地址)+(C)→ACC寻址方式直接/间接直接/间接短立即数长立即数指令说明ACC取绝对值移位时低位填0,若SXM=1,高位用符号扩展;若SXM=0,高位填0;结果存在ACC中,该指令使C=0。

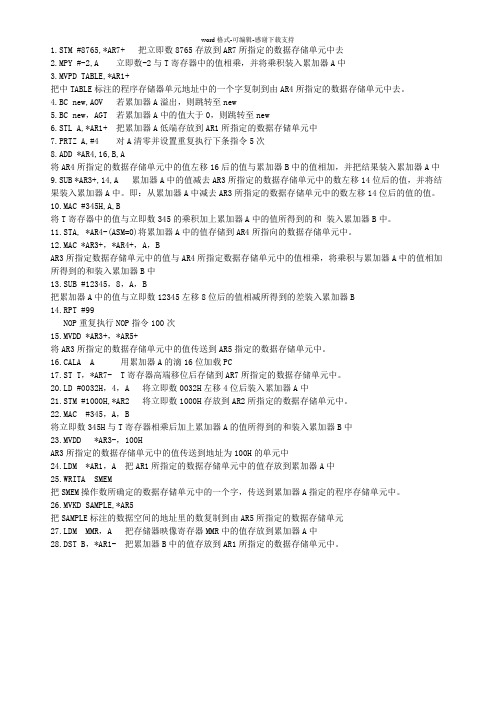

DSP指令大全(最全)

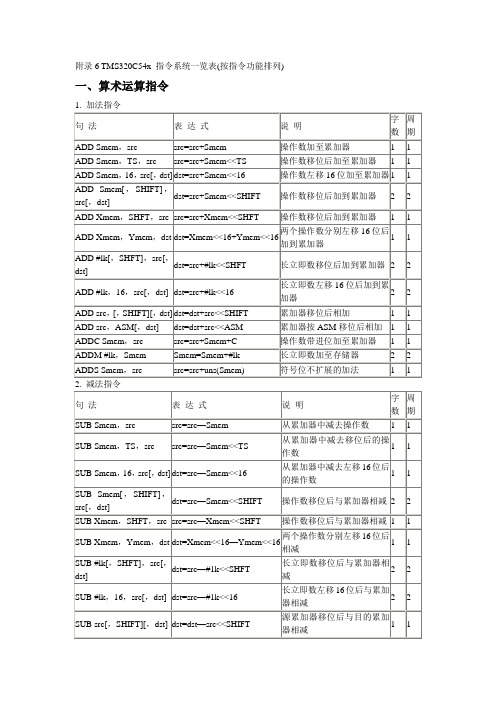

附录6 TMS320C54x 指令系统一览表(按指令功能排列) 一、算术运算指令二、逻辑运算指令三、程序控制指令6.注:?条件“真”,§条件“假”,※延迟指令。

四、加载和存储指令4.6.7.五.伪指令2.初始化常数(数据和存储器)的伪指令3.调整段程序计数器伪指令(SPC).align 把SPC调整到页边界.even 把SPC调整到偶数字边界4.控制输出列表格式化伪指令5.条件汇编伪指令.break [well-defined expression] 如果条件真结束.loop汇编,.break结构是可选项.else 如果.if条件为假,汇编代码块.else结构是可选项.elseif well-defined expression——如果if条件为假且.elseif条件为真,汇编代码块.else结构是可选项.endif 结束.if代码块.endloop 结束.1oop代码块.if well-defined expression 如果条件为真则汇编代码块.loop [well-defined expression] 开始代码块的重复汇编6. 汇编符号.asg [”] character string [”],substitution symbol——把字符串赋予替代的符号..endstruct 结束结构定义.equ 使值和符号相等.eval well-defined expression,substitution symbol 根据数字替代符号完成运算.newblock 取消局部标号.set 使数值和符号相等.struct 开始结构定义.tag 把结构属性赋予标号7.宏指令宏定义:Macname .macro[参数1],[…],[参数n]宏调用:[标号][:] macname [参数1],[…],[参数n]8.编译软件指令①汇编器:asm500.exeasm500[input file[object file [listing file] [-options]]-c—使汇编语言文件中大小没有区别。

DSP代码释义

•装载累加器–LACC:左移装载累加器•LACC dma [,shift]•LACC dma ,16•LACC ind [,shift[,ARn]]•LACC ind ,16[,ARn]•LACC #lk [,shift]–LACL:装载累加器低位并清累加器高位•LACL dma•LACL ind[,ARn]•LACL #k–LACT:按TREG规定左移后再转载入累加器•LACT dma•LACT ind[,ARn]–PAC:用乘积寄存器PREG装载累加器,移位方式由ST1中的PM确定•PAC•装载临时寄存器TREG–LT:将指定数据存储器的内容装入TREG。

常作乘法的准备工作。

•LT dma•LT ind[,ARn]–LTA:装载TREG同时累加前次乘积•LTA dma•LTA ind[,ARn]–LTD:装载TREG,累加前次乘积并移动数据•LTD dma•LTD ind[,ARn]–LTP:装载TREG,并将PREG值保存至累加器•LTP dma•LTP ind[,ARn]–LTS:装载TREG并减去前次乘积•LTS dma•LTS ind[,ARn]•装载辅助寄存器AR–LAR:装载辅助寄存器•LAR ARx,dma•LAR ARx,ind[,ARn]•LAR ARx,#k•LAR ARx,#lk–MAR:修改辅助寄存器•MAR dma•MAR ind[,ARn]•装载其它寄存器–LDP:装载数据页指针•LDP dma•LDP ind[,ARn]•LDP #k–LPH:装载乘积寄存器高位字•LPH dma•LPH ind[,ARn]–LST:装载状态寄存器•LST #m,dma•LST #m,ind[,ARn]存储寄存器值•保存AR值(SAR)–SAR ARx, dma–SAR ARx, ind[, ARn] •保存PREG高位字(SPH)–SPH dma–SPH ind[, ARn]•保存PREG低位字(SPL)–SPL dma–SPL ind[, ARn]•保存状态寄存器ST0和ST1(SST)–SST #m, dma–SAR #m, ind[, ARn]堆栈操作•出栈至ACC低位字(POP )–POP•ACC低位字入栈(PUSH )–PUSH•出栈至数据存储器(POPD )–POPD dma–POPD, ind[, ARn]•数据存储器值入栈(PSHD )–PSHD dma–PSHD ind[, ARn]读写数据或程序存储器•数据存储器至数据存储器的块移动(BLDD )–BLDD #lk,dma–BLDD #lk,ind[, ARn]–BLDD dma ,#lk–BLDD ind ,#lk[, ARn] •程序存储器至数据存储器的块移动(BLPD )–BLPD #pma, dma–BLPD #pma, ind[, ARn] •片内数据存储器中的数据传送(DMOV )–DMOV dma–DMOV ind[, ARn]•长立即数写入数据存储器(SPLK )–SPLK #lk, dma–SPLK #lk, ind[, ARn]•读程序存储器(表读)(TBLR )–TBLR dma–TBLR ind[, ARn]•写程序存储器(表写)(TBLW )–TBLW dma–TBLW ind[, ARn]读写I/O单元•读I/O单元(IN )–IN dma, PA–IN ind, PA[, ARn]•写I/O单元(OUT )–OUT dma, PA–OUT ind, PA[, ARn]加法•左移加至ACC(ADD)–ADD dma [,shift]–ADD dma ,16–ADD ind [,shift[,ARn]]–ADD ind ,16[,ARn]–ADD #k–ADD #lk [,shift]•带进位位加至ACC (ADDC)–ADDC dma–ADDC ind [,ARn]•抑制符号扩展加至ACC (ADDS)–ADDS dma–ADDS ind [,ARn]•按TREG低4位规定左移加至ACC (ADDT)–ADDT dma–ADDT ind [,ARn]•加短立即数至当前AR(ADRK)–ADRK #k减法•左移后从ACC中减去(SUB)–SUB dma [,shift]–SUB dma ,16–SUB ind [,shift[,ARn]]–SUB ind ,16[,ARn]–SUB #k–SUB #lk [,shift]•带借位从ACC中减去(SUBB)–SUBB ind [,ARn]•条件减(SUBC):常用来实现除法–SUBC dma–SUBC ind [,ARn]•抑制符号扩展减(SUBS)–SUBS dma–SUBS ind [,ARn]•按TREG低4位左移后从ACC中减去(SUBT)–SUBT dma–SUBT ind [,ARn]•当前AR减去短立即数(SBRK)–SBRK #k•ACC减去PREG(SPAC)–SPAC•SUBC实现16位数除法的步骤–被除数(必须为正)置于累加器低位字中,且最高位放在bit15中,累加器高位字清零;–除数(必须大于0)放入数据存储单元中;–执行SUBC指令16次;–除的结果:商在累加器低位字;余数在累加器高位字。

DSP术语

MIPS(Million Instructions Per Second):单字长定点指令平均执行速度Million Instructions Per Second的缩写,每秒处理的百万级的机器语言指令数。

这是衡量CPU速度的一个指标。

像是一个Intel 80386 电脑可以每秒处理3百万到5百万机器语言指令,即我们可以说80386是3到5MIPS的CPU。

MIPS只是衡量CPU性能的指标。

ROM是只读内存(Read-Only Memory)的简称,是一种只能读出事先所存数据的固态半导体存储器。

其特性是一旦储存资料就无法再将之改变或删除。

通常用在不需经常变更资料的电子或电脑系统中,资料并且不会因为电源关闭而消失。

RAM(random access memory)随机存储器。

存储单元的内容可按需随意取出或存入,且存取的速度与存储单元的位置无关的存储器。

这种存储器在断电时将丢失其存储内容,故主要用于存储短时间使用的程序。

按照存储信息的不同,随机存储器又分为静态随机存储器(Static RAM,SRAM)和动态随机存储器(Dynamic RAM,DRAM)。

PWM Channels:脉宽调制频率。

General-Purpose Timers:通用定时器。

外部存储器接口(EMIF),External Memory Interface,是TMS DSP器件上的一种接口。

一般来说,EMIF可实现DSP与不同类型存储器(SRAM、Flash RAM、DDR-RAM 等)的连接。

一般EMIF与FPGA相连,从而使FPGA平台充当一个协同处理器、高速数据处理器或高速数据传输接口。

watchdog timer:看门狗,是一个定时器电路, 一般有一个输入,叫喂狗,一个输出到MCU 的RST端,MCU正常工作的时候,每隔一段时间输出一个信号到喂狗端,给WDT 清零,如果超过规定时间不喂狗(一般在程序跑飞时),WDT 定时超过,就会给出一个复位信号到MCU,使MCU复位. 防止MCU死机. 看门狗的作用就是防止程序发生死循环或者说程序跑飞。

DSP常用汇编语言指令简介

5. 控制指令举例

Example1:BIT0h,15 ;(DP = 6)把内存地址=300h 单元内容的最低位(BIT0)送给TC。 Example2:LDP #0h;使用立即数方式装载 数据页,也可以采用直接寻址和间接寻址方式装 载。 Example3:PUSH ;把累加器的低16位压入堆 栈。 Example4:SETC C;置进位C=1,也可以设置 以下的控制位为1或者为0,例如:CNF、INTM、 OVM、SXM、TC和XF。类似的指令还有: CLRC。

2. 工作寄存器等指令举例

Example4:ADRK #80h ;把当前工作寄存器内容 加一个立即数80h(注意立即数范围:00~FFh)。类 似的指令还有SBRK。 Example5:BANZ指令使用举例。例: MAR *, AR0 ;当前ARP=AR0 LAR AR1, #03h ;AR1内容赋值为03h LAR AR0, #60h ;AR0内容赋值为60h ZAC ; 累加器ACC清零 loop: ADD *+, AR1 ;把当前工作寄存器AR0指向 的内存单元数值加到ACC,然后AR0内容加1,当前工 作寄存器指针指向AR1 BANZ loop, *-AR0 ;判断AR0是否为0,否则程序 转到loop,同时AR0的内容减1。 南航自动化学院DSP技术应用实验 返回到第10页 室

南航自动化学院DSP技术应用实验 室

1. 累加器等指令举例

Example 1:ADD 1,1;(假设DP = 6),把 第6个数据页的第一个内存单元内容左移一 位加到累加器 Example 2:LACC *,4; (与SXM有关) Example 3:ROL;把累加器内容循环左移 Example 4:SACL *,0,AR7 ;把当前工作寄 存器指示内容左移0位送入累加器的低8位 Example 5:RPT #15 SUBC * ;累加器减去当前寄存 器指的内容,连续减16次,结果存累加器

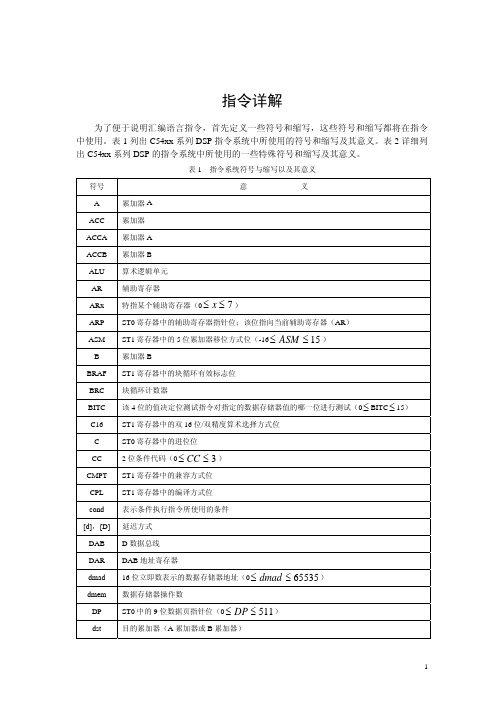

c54xx系列DSP汇编指令详解

意义 或运算 异或运算

减1 赋值于 表示一个立即数 x 的补码

|x|

x 的绝对值

0x

十六进制数据

>>

右移

<<

左移

×

乘法

*

指针指向的地址

TMS320C54xx 系列 DSP 的指令一共有 129 条,按功能分为如下几类:算术指令、逻 辑指令、程序控制指令、存储和装入指令以及循环指令。下面根据每种指令功能的不同,

目的累加器的反 if dst=A,then dst_=B if dst=B then dst_=A

E 地址总线 EAB 地址寄存器 23 位立即数表示的程序存储器地址 ST1 寄存器中的分数方式位 十六进制数据 十六进制数据 累加器 A 的高端(位 32~16) ST1 寄存器中的保持方式位 中断标志寄存器 ST1 寄存器中的中断屏蔽位 少于 9 位的短立即数

3 位立即数(0 ≤ k3 ≤ 7 ) 5 位立即数(-16 ≤ k5 ≤ 15 ) 9 位立即数(0 ≤ k9 ≤ 115 )

16 位长立即数 使用长字寻址 32 位单数据存储器操作数 存储器映射寄存器,AR0~AR7 或 SP

存储器映射寄存器,AR0~AR7 或 SP

紧跟 XC 指令的字数,n=1 或 2 指定在 RSBX、SSBX 和 XC 指令中修改的状态寄存器 N=0,状态寄存器 ST0 N=1,状态寄存器 ST1 ST0 寄存器中的累加器 A 的溢出标志 ST0 寄存器中的累加器 B 的溢出标志 目的累加器(A 或 B)的溢出标志 目的累加器反(A 或 B)的溢出标志 源累加器(A 或 B)的溢出标志 ST1 寄存器中的溢出方式位 16 位立即数表示的端口地址

③ 乘法指令

第三章DSP汇编指令

if 0≤ index+step < BK: index = index + step

else if index + step ≥ BK: index = index + step - BK

else if index + step< 0 index = index + step + BK

只有8条指令能使用存储器映射寄存器寻址:

LDM MMR, dst MVDM dmad, MMR MVMD MMR, dmad MVMM MMRx, MMRy POPM MMR PSHM MMR STLM src, MMR STM #lk, MMR

7. 堆栈寻址

系统堆栈用来在中断和子程序期间自动存放程序计数器。 它也能用来存放额外的数据项或传递数据值。处理器使用一 个16-bit的存储器映射寄存器—堆栈指针来对堆栈寻址,它 总是指向存放在堆栈中的最后一个元素。

2、调用与中断指令

3、返回指令

4、重复指令和堆栈操作指令

四、装入和存储指令

装入和存储指令包括:

一般的装入和存储指令 条件存储指令 并行装入和存储指令 并行装入和乘法指令 并行存储和加件乘指令 混合装入和存储指令

1、一般的装入指令

2、存贮指令

3 并行装入和存储指令 4、条件存储指令

共有四条使用堆栈寻址方பைடு நூலகம்访问堆栈的指令:

PSHD 把一个数据存储器的值压入堆栈。 PSHM 把 一 个 存 储 器 映 射 寄 存 器 的 值 压 入 堆 栈 。 POPD 把一个数据存储器的值弹出堆栈。 POPM 把一个存储器映射寄存器的值弹出堆栈。

§3-2 特殊寻址方式说明

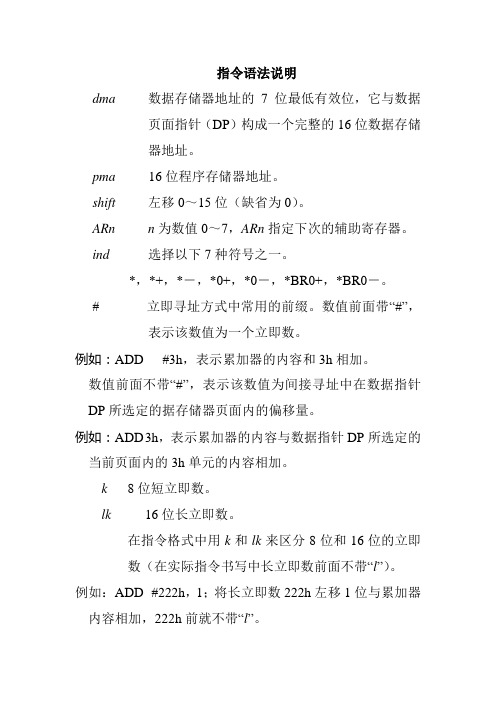

dsp指令语法说明

指令语法说明dma数据存储器地址的7位最低有效位,它与数据页面指针(DP)构成一个完整的16位数据存储器地址。

pma 16位程序存储器地址。

shift左移0~15位(缺省为0)。

ARn n为数值0~7,ARn指定下次的辅助寄存器。

ind选择以下7种符号之一。

*,*+,*-,*0+,*0-,*BR0+,*BR0-。

# 立即寻址方式中常用的前缀。

数值前面带“#”,表示该数值为一个立即数。

例如:ADD #3h,表示累加器的内容和3h相加。

数值前面不带“#”,表示该数值为间接寻址中在数据指针DP所选定的据存储器页面内的偏移量。

例如:ADD 3h,表示累加器的内容与数据指针DP所选定的当前页面内的3h单元的内容相加。

k8位短立即数。

lk16位长立即数。

在指令格式中用k和lk来区分8位和16位的立即数(在实际指令书写中长立即数前面不带“l”)。

例如:ADD #222h,1;将长立即数222h左移1位与累加器内容相加,222h前就不带“l”。

[, x]操作数x是可选项。

[x1[, x2]] 操作数x1和x2是可选项,如果若不写x1,也就不能写x2。

例如指令ADD ind[, shift[, ARn]]中必须提供ind,而shift和ARn可以缺省,* 但若没有shift,就不能写ARn。

如ADD *+ 还可以包括可选项shift,如ADD *+, 5。

** 如果希望包含ARn,即使不移位,也必须写上shift,如ADD *+,0,AR2操作数0表示不移位,但必须写。

ADD *+,AR2是错误指令。

DSP汇编指令总结

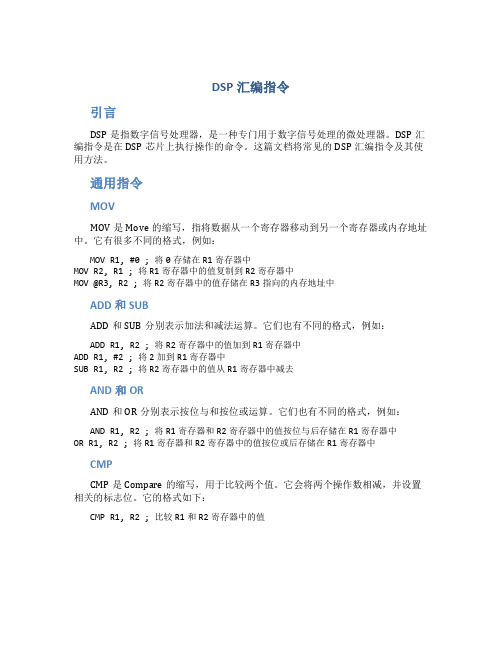

DSP汇编指令引言DSP是指数字信号处理器,是一种专门用于数字信号处理的微处理器。

DSP汇编指令是在DSP芯片上执行操作的命令。

这篇文档将常见的DSP汇编指令及其使用方法。

通用指令MOVMOV是Move的缩写,指将数据从一个寄存器移动到另一个寄存器或内存地址中。

它有很多不同的格式,例如:MOV R1, #0 ; 将0存储在R1寄存器中MOV R2, R1 ; 将R1寄存器中的值复制到R2寄存器中MOV @R3, R2 ; 将R2寄存器中的值存储在R3指向的内存地址中ADD和SUBADD和SUB分别表示加法和减法运算。

它们也有不同的格式,例如:ADD R1, R2 ; 将R2寄存器中的值加到R1寄存器中ADD R1, #2 ; 将2加到R1寄存器中SUB R1, R2 ; 将R2寄存器中的值从R1寄存器中减去AND和ORAND和OR分别表示按位与和按位或运算。

它们也有不同的格式,例如:AND R1, R2 ; 将R1寄存器和R2寄存器中的值按位与后存储在R1寄存器中OR R1, R2 ; 将R1寄存器和R2寄存器中的值按位或后存储在R1寄存器中CMPCMP是Compare的缩写,用于比较两个值。

它会将两个操作数相减,并设置相关的标志位。

它的格式如下:CMP R1, R2 ; 比较R1和R2寄存器中的值跳转指令JMPJMP是Jump的缩写,用于无条件跳转到目标地址。

它的格式如下:JMP label ; 跳转到标签为label的位置JNZ和JZJNZ和JZ分别表示如果结果不为零则跳转和如果结果为零则跳转。

它们的格式如下:JNZ label ; 如果前一条CMP指令比较结果不为零,则跳转到标签为label的位置JZ label ; 如果前一条CMP指令比较结果为零,则跳转到标签为label的位置JGE和JLEJGE和JLE分别表示如果大于或等于则跳转和如果小于或等于则跳转。

它们的格式如下:JGE label ; 如果前一条CMP指令比较结果大于或等于,则跳转到标签为label的位置JLE label ; 如果前一条CMP指令比较结果小于或等于,则跳转到标签为label的位置循环指令DJNZDJNZ是Decrement and Jump if Not Zero的缩写,表示如果操作数不为零则减1并跳转到目标地址。

第三章 DSP的指令系统

TC=1

CMPM Smem,#1K

CMPR CC , ARX

CC=2=10b, IF (AR4) > (AR0), TC=1, ELSE TC=0

程序控制指令

转

移指令

(B,BC);

调用指令 (CALL) 中断指令

(INTR,TRAP)

返回指令 (RET)

循环指令 (RPT) 堆栈操作指令 (FRAME,POP) 混合程序控制指令 (IDLE,NOP)

sth

利用SUBC实现除法

在‘C54X中没有提供专门的除法指令, 一般有两种方法来完成除法。一种是用 乘法来代替,除以某个数相当于乘以其 倒数,所以先求出其倒数,然后相乘。 这种方法对于除以常数特别适用。另一 种方法是使用SUBC指令,重复16次减法 完成除法运算。

利用SUBC完成Temp1/Temp2

FRCT Fractional mode bit in ST1 OVA Overflow flag for accumulator A in ST0 OVB Overflow flag for accumulator B in ST0 OVdst Overflow flag for the destination accumulator (A or B) OVdst_ Overflow flag for the opposite destination accumulator (A or B) OVsrc Overflow flag for the source accumulator (A or B) OVM Overflow mode bit in ST1 PA 16-bit port immediate address (0-65535) PAR Program address register SXM Sign-extension mode bit in ST1 T Temporary register C Carry bit in ST0 pmad 16-bit immediate program-memory address (0 Pmem Program-memory operand dmad 16-bit immediate data-memory address (0 Dmem Data-memory operand

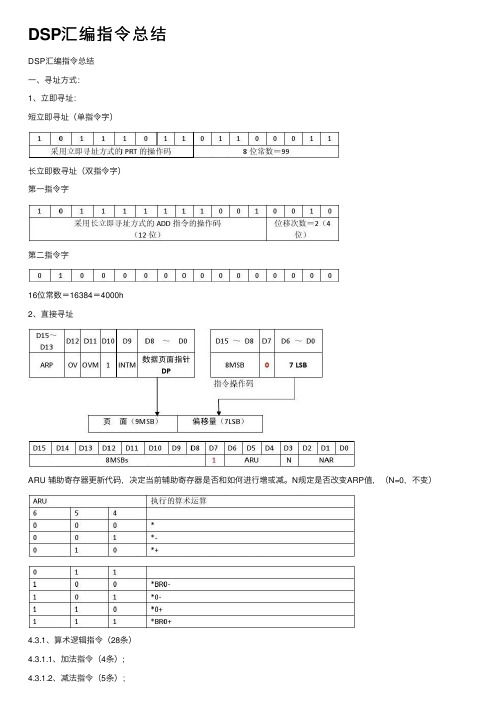

DSP汇编指令总结

DSP汇编指令总结DSP汇编指令总结⼀、寻址⽅式:1、⽴即寻址:短⽴即寻址(单指令字)长⽴即数寻址(双指令字)第⼀指令字第⼆指令字16位常数=16384=4000h2、直接寻址ARU 辅助寄存器更新代码,决定当前辅助寄存器是否和如何进⾏增或减。

N规定是否改变ARP值,(N=0,不变)4.3.1、算术逻辑指令(28条)4.3.1.1、加法指令(4条);4.3.1.2、减法指令(5条);4.3.1.3、乘法指令(2条);4.3.1.4、乘加与乘减指令(6条);4.3.1.5、其它算数指令(3条);4.3.1.6、移位和循环移位指令(4条);4.3.1.7、逻辑运算指令(4条);4.3.2、寄存器操作指令(35条)4.3.2.1、累加器操作指令(6条)4.3.2.2、临时寄存器指令(5条)4.3.2.3、乘积寄存器指令(6条)4.3.2.4、辅助寄存器指令(5条)4.3.2.5、状态寄存器指令(9条)4.3.2.6、堆栈操作指令(4条)4.3.3、存储器与I/O操作指令(8条)4.3.3.1、数据移动指令(4条)4.3.3.2、程序存储器读写指令(2条)4.3.3.3、I/O操作指令(2条)4.3.4、程序控制指令(15条)4.3.4.1、程序分⽀或调⽤指令(7条)4.3.4.2、中断指令(3条)4.3.4.3、返回指令(2条)4.3.4.4、其它控制指令(3条)4.3.1、算术逻辑指令(28条)4.3.1.1、加法指令(4条);▲ADD▲ADDC(带进位加法指令)▲ADDS(抑制符号扩展加法指令)▲ADDT(移位次数由TREG指定的加法指令)4.3.1.2、减法指令(5条);★SUB(带移位的减法指令)★SUBB(带借位的减法指令)★SUBC(条件减法指令)★SUBS(减法指令)★SUBT(带移位的减法指令,TREG决定移位次数)4.3.1.3、乘法指令(2条);★MPY(带符号乘法指令)★MPYU(⽆符号乘法指令)4.3.1.4、乘加与乘减指令(6条);★MAC(累加前次积并乘)(字数2,周期3)★MAC(累加前次积并乘)★MPYA(累加-乘指令)★MPYS(减-乘指令)★SQRA(累加平⽅值指令)★SQRS(累减并平⽅指令)4.3.1.5、其它算数指令(3条);★ABS(累加器取绝对值指令)★NEG(累加器取补码指令)★NORM(累加器规格化指令)返回4.3.1.6、移位和循环移位指令(4条);▲ SFL(累加器内容左移指令)▲ SFR(累加器内容右移指令)▲ROL(累加器内容循环左移指令)▲ROR(累加器内容循环右移指令)返回4.3.1.7、逻辑运算指令(4条);▲ AND(逻辑与指令)▲ OR(逻辑或指令)▲ XOR(逻辑异或指令)▲ CMPL(累加器取反指令)返回4.3.2、寄存器操作指令(35条)4.3.2.1、累加器操作指令(6条)▲ LACC(装载累加器指令)▲ LACT(装载累加器)*按TREG低4位指定的次数移位▲ LACL(装载累加器低16位指令)▲ ZALR(装载累加器指令)▲ SACL(移位并存储累加器低半部)▲ SACH(移位并存储累加器⾼半部)返回4.3.2.2、临时寄存器指令(5条)▲ LT(装载TREG指令)▲ LTA(装载TREG并累加上次乘积指令)▲ LTS (装载TREG并减去上次乘积指令)▲ LTD(装载TREG并累加上次乘积及数据移动指令)▲LTP(装载TREG和累加器指令)返回4.3.2.3、乘积寄存器指令(6条)▲ PAC (乘积寄存器内容载⼊累加器)▲ APAC (PREG与累加器相加)▲ SPAC(累加器和乘积寄存器相减)▲ LPH(装载PREG⾼16位指令)▲ SPL(存储PREG低16位指令)▲ SPH(存储PREG⾼16位指令)返回4.3.2.4、辅助寄存器指令(5条)★LAR(装载当前辅助寄存器AR)★SAR(存储辅助寄存器指令)★MAR(修改当前辅助寄存器)★SBRK(从当前辅助寄存器减去短⽴即数)返回4.3.2.5、状态寄存器指令(9条)★LST(装载状态寄存器)★SST(存储状态寄存器)★SETC(控制位置“1”指令)★SETC(控制位置“1”指令)★LDP(装载数据指针DP指令)★BIT(位测试指令)★BITT(测试由TREG指定bit code指令)★CMPR(⽐较当前辅助寄存器AR和AR0)返回4.3.2.6、堆栈操作指令(4条)★PUSH(累加器低16位进栈指令)★POP(栈顶内容弹出⾄累加器低16位指令)★POP(栈顶内容弹出⾄累加器低16位指令)★POPD(弹栈⾄数据存储器指令)返回4.3.3、存储器与I/O操作指令(8条)4.3.3.1、数据移动指令(4条)▲DMOV(数据存储器内部数据移动指令)▲SPLK(存储长⽴即数⾄数据存储器指令)▲BLDD(数据存储器内部的数据块移动)▲ BLPD(从程序存储器到数据存储器的数据块传送)4.3.3.2、程序存储器读写指令(2条)★TBLR(读程序存储器数据到数据存储器)★TBLW(写程序存储器)4.3.3.3、I/O操作指令(2条)★IN(数据输⼊指令)★OUT(数据输出指令)4.3.4、程序控制指令(15条)4.3.4.1、程序分⽀或调⽤指令(7条)★B(⽆条件转移指令)★BANZ(辅助寄存器内容不等于零转移)★CALL(⽆条件⼦程序调⽤指令)★BACC(按累加器内容转移指令)★CALA(由累加器指定地址的⼦程序调⽤指令)★CC(条件调⽤指令)4.3.4.2、中断指令(3条)★INTR(软中断指令)★TRAP(软件陷阱中断)★NMI(⾮屏蔽中断)4.3.4.3、返回指令(2条)★RET(⽆条件从⼦程序或中断返回)★RETC(条件返回指令)4.3.4.4、其它控制指令(3条)★RPT(重复执⾏下条指令)★NOP(空操作)★IDEL(暂停)返回。

DSP汇编伪指令集讲解

.usect执行之后的存储器分布示意图

8.2 .sect用法:

.sect

“段名”

定义初始化命名段。段名必须用引号引起。该段中可包括代码或者数据, 类似于.text和.data。 9 .set伪指令: 用法: 符号 .set 数值 .set定义的符号在符号表中,不能重复定义。在数值表达式中的符号必 需事先定义。用.def或.global可以使用由.set定义的符号被其他模块调用。 例: IMR .set 0004h ; Interrupt Mask Register IFR .set 0006h ; Interrupt Flag Register 10 .byte, .float , .bfloat, .int , .word, .long , .blong, .string, .field 10.1 .byte用法: [标号] .byte 数值1[,数值2,……] .byte指令将一个或者多个8位的值植入当前段的连续字中。数值可以是 常数,表达式,字符串。使用标号的时候,汇编器指向第一个.byte位置。每 个.byte指令可以定义100个设置,若有字符串,则总数值长度不超过200个字 符。例如: 0000 .space 100h*16 0100 strx .byte ”ab”,”c” 0101 … 后面几个指令用法也基本类似,但数据类型不同。

.align, .even;

4.输出列表格式伪指令:控制列表文件的格式。

.drlist, .drnolist, .list, .fcnolist, .length, .width,.list,

.nolist, .mlist, .mnolist, .opinion, .ssnolist, .tab, .title

DSP第五章 DSP的汇编指令

展和移位操作都以第31比特为准。

M40=1时,D单元按40位运算模式,因此累加器溢出,进位,符号扩

展和移位操作都以第39比特为准。

BCLR M40

; Clear M40

BSET M40

; Set M40

第五章 TMS320C55x系列DSP的汇编指令

2、累加器溢出状态(ACOVx)

当AC0~AC3寄存器溢出时,目的累加器的溢出状态位ACOV0~3被置1。 以下情况会清零ACOVx位

复位; CPU执行一个跳转,条件调用,条件返回或执行一条测试ACOVx的指令; 通过BCLR指令清除; 溢出位检测受ST1_55中的M40位影响,即:

第五章 TMS320C55x系列DSP的汇编指令

(3)内置并行指令与用户自定义并行指令的混合形式 在不引起资源冲突的情况下,将隐含并行的指令按用户自定义 方式与另一条指令并行执行。例:

MPY *AR0, *CDP, AC0 ;隐含的或内置的并行指令 :: MPY *AR1, *CDP, AC1 ||MOV #5, AR1

பைடு நூலகம்

在实际编程时,只要指令满足这三条基本规则,即可写成并行

方式,然后进行编译。如果编译有错,则可参照书上详细规则进 行检测。

第五章 TMS320C55x系列DSP的汇编指令 5.4 TMS320C55x DSP的汇编指令

TMS320C55x DSP的汇编指令按操作分为以下6类 算术运算指令 比特操作指令 一条指令的属性包括: 语法(Syntax) 执行的操作 操作数 相关的状态位 是否有并行使能位 长度(Size) 执行周期(Cycles) 在流水线(Pipeline)上的执行阶段 在哪个功能单元执行(Executed) 是否可以重复执行等

DSP指令解释

word格式-可编辑-感谢下载支持1.STM #8765,*AR7+ 把立即数8765存放到AR7所指定的数据存储单元中去2.MPY #-2,A 立即数-2与T寄存器中的值相乘,并将乘积装入累加器A中3.MVPD TABLE,*AR1+把中TABLE标注的程序存储器单元地址中的一个字复制到由AR4所指定的数据存储单元中去。

4.BC new,AOV 若累加器A溢出,则跳转至new5.BC new,AGT 若累加器A中的值大于0,则跳转至new6.STL A,*AR1+ 把累加器A低端存放到AR1所指定的数据存储单元中7.PRTZ A,#4 对A清零并设置重复执行下条指令5次8.ADD *AR4,16,B,A将AR4所指定的数据存储单元中的值左移16后的值与累加器B中的值相加,并把结果装入累加器A中9.SUB *AR3+,14,A 累加器A中的值减去AR3所指定的数据存储单元中的数左移14位后的值,并将结果装入累加器A中。

即:从累加器A中减去AR3所指定的数据存储单元中的数左移14位后的值的值。

10.MAC #345H,A,B将T寄存器中的值与立即数345的乘积加上累加器A中的值所得到的和装入累加器B中。

11.STA, *AR4-(ASM=0)将累加器A中的值存储到AR4所指向的数据存储单元中。

12.MAC *AR3+,*AR4+,A,BAR3所指定数据存储单元中的值与AR4所指定数据存储单元中的值相乘,将乘积与累加器A中的值相加所得到的和装入累加器B中13.SUB #12345,8,A,B把累加器A中的值与立即数12345左移8位后的值相减所得到的差装入累加器B14.RPT #99NOP重复执行NOP指令100次15.MVDD *AR3+,*AR5+将AR3所指定的数据存储单元中的值传送到AR5指定的数据存储单元中。

16.CALA A 用累加器A的滴16位加载PC17.ST T,*AR7- T寄存器高端移位后存储到AR7所指定的数据存储单元中。

DSP指令大全(最全)

DSP指令大全(最全)附录6 TMS320C54x 指令系统一览表(按指令功能排列) 一、算术运算指令二、逻辑运算指令三、程序控制指令6.注:?条件―真‖,§条件―假‖,※延迟指令。

四、加载和存储指令4.6.7.五.伪指令2.初始化常数(数据和存储器)的伪指令3.调整段程序计数器伪指令(SPC).align 把SPC调整到页边界.even 把SPC调整到偶数字边界4.控制输出列表格式化伪指令5.条件汇编伪指令.break [well-defined expression] 如果条件真结束.loop汇编,.break结构是可选项.else 如果.if条件为假,汇编代码块.else结构是可选项.elseif well-defined expression——如果if条件为假且.elseif 条件为真,汇编代码块.else结构是可选项.endif 结束.if代码块.endloop 结束.1oop代码块.if well-defined expression 如果条件为真则汇编代码块.loop [well-defined expression] 开始代码块的重复汇编6. 汇编符号.asg [”] character string [”],substitution symbol——把字符串赋予替代的符号..endstruct 结束结构定义.equ 使值和符号相等.eval well-defined expression,substitution symbol 根据数字替代符号完成运算.newblock 取消局部标号.set 使数值和符号相等.struct 开始结构定义.tag 把结构属性赋予标号7.宏指令宏定义:Macname .macro[参数1],[…],[参数n]宏调用:[标号][:] macname [参数1],[…],[参数n]8.编译软件指令①汇编器:asm500.exeasm500[input file[object file [listing file] [-options]]-c—使汇编语言文件中大小没有区别。

DSP常用语言指令简介

2. 工作寄存器等指令举例

z Example1:MAR

*+,AR1;把当前工作寄 存器的内容加1,然后再改变工作寄存器为 AR1。 z Example2:LAR AR4,#8123h;把AR4的 值改变为立即数。 LAR AR0,16;(DP=6)把 地址=310H的内存单元内容装入AR0。 z Example3:SAR AR0,*+;(如果当前工 作寄存器=AR1)把AR0的内容拷贝到AR1 南航自动化学院DSP技术应用实验 指向的内存单元。 室

南航自动化学院DSP技术应用实验 室

z Example1:BCND

xxx, LEQ, C ;如果累加 器<=0并且进位C=1,那么程序就跳转到标 号xxx处执行;否则,程序顺序执行。根据 累加器ACC的内容产生的转移条件如下表格 所示。类似的指令还有:CC xxx。 z Example2:BANZ。第七页举例。

南航自动化学院DSP技术应用实验 室

1. 累加器等指令举例

z Example

1:ADD 1,1;(假设DP = 6),把 第6个数据页的第一个内存单元内容左移一 位加到累加器 z Example 2:LACC *,4; (与SXM有关) z Example 3:ROL;把累加器内容循环左移 z Example 4:SACL *,0,AR7 ;把当前工作寄 存器指示内容左移0位送入累加器的低8位 z Example 5:RPT #15 SUBC * ;累加器减去当前寄存 器指的内容,连续减16次,结果存累加器

南航自动化学院DSP技术应用实验 室

1. 累加器等指令举例

Example 6: AND 16 ;(假设DP = 4),把地址 =210H的内存单元内容和ACC相逻辑“与”,结果存 入累加器。 z Example 7:SFL ;把整个的ACC内容左移一位,低 位填0,最高位送入进位位,不受SXM影响。 z Example 8:SFR ;把整个的ACC内容右移一位,高 位根据SXM进行符号位扩展。例如: 1.执行前ACC=B0001234h,SXM=0,执行后ACC= 5800091Ah; 2.执行前ACC=B0001234h,SXM=0,执行后ACC =5800091Ah;

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1.STM #8765,*AR7+ 把立即数8765存放到AR7所指定的数据存储单元中去

2.MPY #-2,A 立即数-2与T寄存器中的值相乘,并将乘积装入累加器A中

3.MVPD TABLE,*AR1+

把中TABLE标注的程序存储器单元地址中的一个字复制到由AR4所指定的数据存储单元中去。

4.BC new,AOV 若累加器A溢出,则跳转至new

5.BC new,AGT 若累加器A中的值大于0,则跳转至new

6.STL A,*AR1+ 把累加器A低端存放到AR1所指定的数据存储单元中

7.PRTZ A,#4 对A清零并设置重复执行下条指令5次

8.ADD *AR4,16,B,A

将AR4所指定的数据存储单元中的值左移16后的值与累加器B中的值相加,并把结果装入累加器A中

9.SUB *AR3+,14,A 累加器A中的值减去AR3所指定的数据存储单元中的数左移14位后的值,并将结果装入累加器A中。

即:从累加器A中减去AR3所指定的数据存储单元中的数左移14位后的值的值。

10.MAC #345H,A,B

将T寄存器中的值与立即数345的乘积加上累加器A中的值所得到的和装入累加器B中。

11.STA, *AR4-(ASM=0)将累加器A中的值存储到AR4所指向的数据存储单元中。

12.MAC *AR3+,*AR4+,A,B

AR3所指定数据存储单元中的值与AR4所指定数据存储单元中的值相乘,将乘积与累加器A 中的值相加所得到的和装入累加器B中

13.SUB #12345,8,A,B

把累加器A中的值与立即数12345左移8位后的值相减所得到的差装入累加器B

14.RPT #99

NOP重复执行NOP指令100次

15.MVDD *AR3+,*AR5+

将AR3所指定的数据存储单元中的值传送到AR5指定的数据存储单元中。

16.CALA A 用累加器A的滴16位加载PC

17.ST T,*AR7- T寄存器高端移位后存储到AR7所指定的数据存储单元中。

20.LD #0032H,4,A 将立即数0032H左移4位后装入累加器A中

21.STM #1000H,*AR2 将立即数1000H存放到AR2所指定的数据存储单元中。

22.MAC #345,A,B

将立即数345H与T寄存器相乘后加上累加器A的值所得到的和装入累加器B中

23.MVDD *AR3-,100H

AR3所指定的数据存储单元中的值传送到地址为100H的单元中

24.LDM *AR1,A 把AR1所指定的数据存储单元中的值存放到累加器A中

25.WRITA SMEM

把SMEM操作数所确定的数据存储单元中的一个字,传送到累加器A指定的程序存储单元中。

26.MVKD SAMPLE,*AR5

把SAMPLE标注的数据空间的地址里的数复制到由AR5所指定的数据存储单元

27.LDM MMR,A 把存储器映像寄存器MMR中的值存放到累加器A中

28.DST B,*AR1- 把累加器B中的值存放到AR1所指定的数据存储单元中。

1。