第五章 DSP的汇编指令..

第五章 DSP的汇编指令..

第五章 TMS320C55x系列DSP的汇编指令

(2) 用户自定义的双指令的并行

这两条指令的并行是通过用户或C编译器定义的。两条指令 同时执行两个操作,用并行符“||”区分并行执行的两条指令。 例:

MPYM *AR1+, *CDP, AC1 ;D单元的一个MAC来完成

||XOR AR2,T1

;A单元的ALU来完成

第五章 TMS320C55x系列DSP的汇编指令

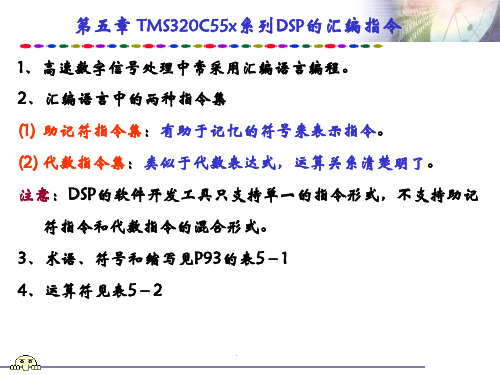

1、高速数字信号处理中常采用汇编语言编程。 2、汇编语言中的两种指令集 (1) 助记符指令集:有助于记忆的符号来表示指令。 (2) 代数指令集:类似于代数表达式,运算关系清楚明了。 注意:DSP的软件开发工具只支持单一的指令形式,不支持助记

符指令和代数指令的混合形式。 3、术语、符号和缩写见P93的表5-1 4、运算符见表5-2

令执行的条件:

TCx(测试/控制标志为1) !TCx(测试/控制标志为0)

TC1&TC2 TC1&!TC2 TC1|TC2 TC1|!TC2 TC1^TC2 TC1^!TC2

!TC1&TC2 !TC1&!TC2 !TC1|TC2 !TC1|!TC2 !TC1^TC2 !TC1^!TC2

第五章 TMS320C55x系列DSP的汇编指令

4、双16比特算术指令: [(1)语法、(2)操作数、(3)状态位] 在D单元中利用其ALU的双16比特模式,同时执行(并行)两个16

比特算术运算,包括加-减、减-加、两个加和两个减运算。

例:

说明: NO:不能并行执行 3:指令的长度为3字节 1:周期为1 X:在X(执行)流水线阶段处理

D – ALU:在D单元ALU执行。 执行结果:AC0=(*AR3)+CARRY+AC1 状态位: Affected by CARRY,C54CM,M40等

DSP指令大全(最全)

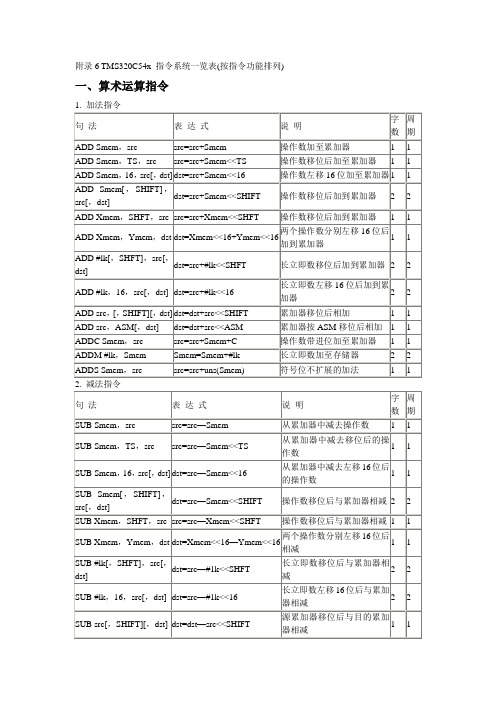

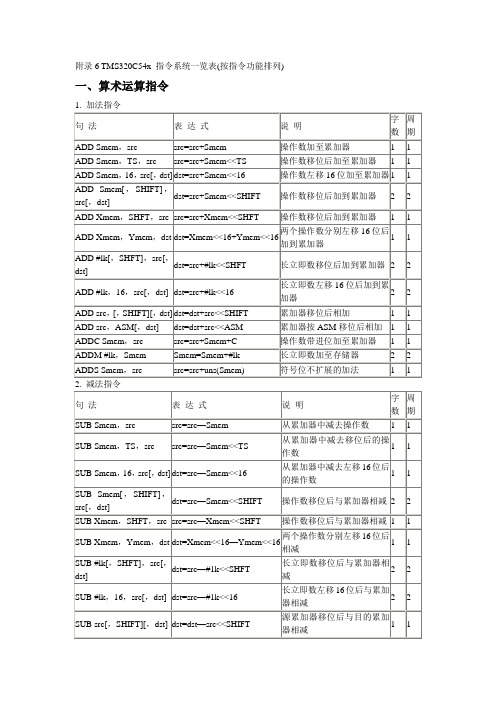

附录6 TMS320C54x 指令系统一览表(按指令功能排列) 一、算术运算指令二、逻辑运算指令三、程序控制指令6.注:?条件“真”,§条件“假”,※延迟指令。

四、加载和存储指令4.6.7.五.伪指令2.初始化常数(数据和存储器)的伪指令3.调整段程序计数器伪指令(SPC).align 把SPC调整到页边界.even 把SPC调整到偶数字边界4.控制输出列表格式化伪指令5.条件汇编伪指令.break [well-defined expression] 如果条件真结束.loop汇编,.break结构是可选项.else 如果.if条件为假,汇编代码块.else结构是可选项.elseif well-defined expression——如果if条件为假且.elseif条件为真,汇编代码块.else结构是可选项.endif 结束.if代码块.endloop 结束.1oop代码块.if well-defined expression 如果条件为真则汇编代码块.loop [well-defined expression] 开始代码块的重复汇编6. 汇编符号.asg [”] character string [”],substitution symbol——把字符串赋予替代的符号..endstruct 结束结构定义.equ 使值和符号相等.eval well-defined expression,substitution symbol 根据数字替代符号完成运算.newblock 取消局部标号.set 使数值和符号相等.struct 开始结构定义.tag 把结构属性赋予标号7.宏指令宏定义:Macname .macro[参数1],[…],[参数n]宏调用:[标号][:] macname [参数1],[…],[参数n]8.编译软件指令①汇编器:asm500.exeasm500[input file[object file [listing file] [-options]]-c—使汇编语言文件中大小没有区别。

DSP汇编编程及应用举例

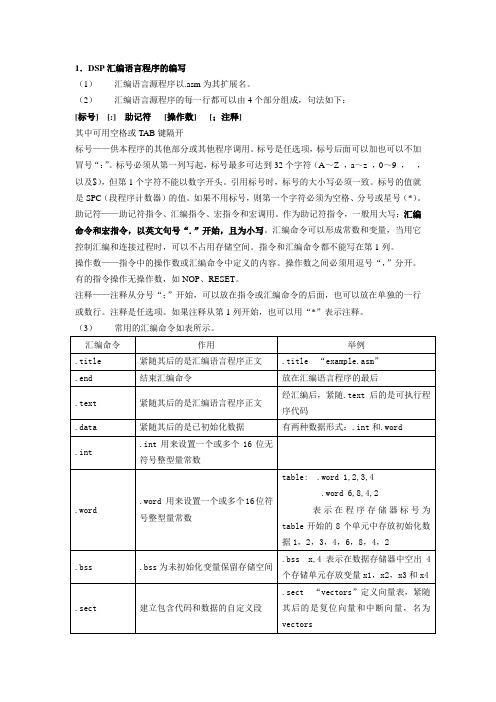

1.DSP汇编语言程序的编写(1)汇编语言源程序以.asm为其扩展名。

(2)汇编语言源程序的每一行都可以由4个部分组成,句法如下:[标号] [:] 助记符[操作数] [;注释]其中可用空格或TAB键隔开标号——供本程序的其他部分或其他程序调用。

标号是任选项,标号后面可以加也可以不加冒号“:”。

标号必须从第一列写起,标号最多可达到32个字符(A~Z ,a~z ,0~9 ,_ ,以及$),但第1个字符不能以数字开头。

引用标号时,标号的大小写必须一致。

标号的值就是SPC(段程序计数器)的值。

如果不用标号,则第一个字符必须为空格、分号或星号(*)。

助记符——助记符指令、汇编指令、宏指令和宏调用。

作为助记符指令,一般用大写;汇编命令和宏指令,以英文句号“.”开始,且为小写。

汇编命令可以形成常数和变量,当用它控制汇编和连接过程时,可以不占用存储空间。

指令和汇编命令都不能写在第1列。

操作数——指令中的操作数或汇编命令中定义的内容。

操作数之间必须用逗号“,”分开。

有的指令操作无操作数,如NOP、RESET。

注释——注释从分号“;”开始,可以放在指令或汇编命令的后面,也可以放在单独的一行或数行。

注释是任选项。

如果注释从第1列开始,也可以用“*”表示注释。

(3)常用的汇编命令如表所示。

(4)汇编语言程序中的数据形式如表所示2.程序2.1 程序一编程目的:了解DSP的输入和输出方法程序功能:求乘积之和y=a1*x1+a2*x2+a3*x3+a4*x4.title "mpy_add.asm".mmregs ;将存储映像寄存器导入列表STACK .usect "STACK",10h ;给堆栈段分配空间.bss a,4 ;将9个字空间分配给各个变量.bss x,4.bss y,1PA0 .set 0 ;将端口PA0全部置0.def start ;定义标号start.data ;定义数据代码段table: .word 4,4,4,4.word 4,4,4,4.text ;定义文本代码段start: STM #0,SWWSR ;将等待寄存器设为0,表示不等待STM #STACK+10h,SP ;设堆栈指针STM #a,AR1 ;将AR1指向变量a的地址RPT #7 ;从程序存储空间转移7+1个值到数据储存空间MVPD table,*AR1+CALL SUM ;调用SUM子程序end: B end ;循环等待SUM: STM #a,AR3 ;将AR3指向变量a的地址STM #x,AR4 ;将AR4指向变量x的地址RPTZ A,#3 ;将A清0,并重复执行下一条指令3+1次MAC *AR3+,*AR4+,ASTL A,@y ;将寄存器A中的低16位存入y地址空间PORTW @y,PA0 ;将y地址中的值输出到输出口RET ;子程序返回.end ;程序结束等待位的设置:C54x片内有一部件——软件可编程等待状态发生器,控制着外部总线的工作。

dsp汇编指令系统介绍(精)

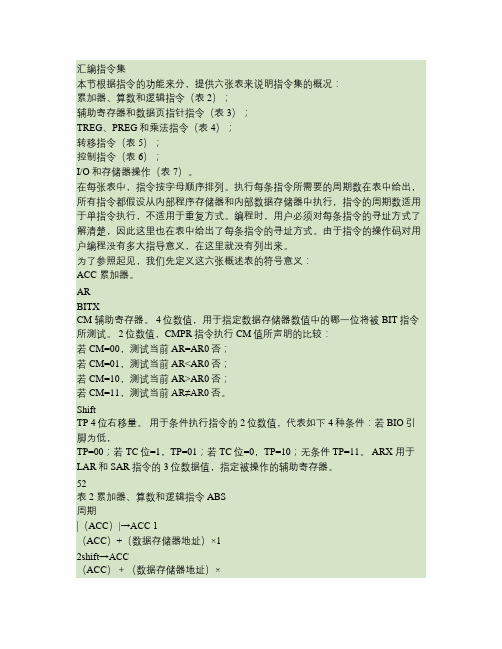

汇编指令集本节根据指令的功能来分,提供六张表来说明指令集的概况:累加器、算数和逻辑指令(表2);辅助寄存器和数据页指针指令(表3);TREG、PREG和乘法指令(表4);转移指令(表5);控制指令(表6);I/O和存储器操作(表7)。

在每张表中,指令按字母顺序排列。

执行每条指令所需要的周期数在表中给出,所有指令都假设从内部程序存储器和内部数据存储器中执行,指令的周期数适用于单指令执行,不适用于重复方式。

编程时,用户必须对每条指令的寻址方式了解清楚,因此这里也在表中给出了每条指令的寻址方式。

由于指令的操作码对用户编程没有多大指导意义,在这里就没有列出来。

为了参照起见,我们先定义这六张概述表的符号意义:ACC 累加器。

ARBITXCM 辅助寄存器。

4位数值,用于指定数据存储器数值中的哪一位将被BIT指令所测试。

2位数值,CMPR指令执行CM值所声明的比较:若CM=00,测试当前AR=AR0否;若CM=01,测试当前AR<AR0否;若CM=10,测试当前AR>AR0否;若CM=11,测试当前AR≠AR0否。

ShiftTP 4位右移量。

用于条件执行指令的2位数值,代表如下4种条件:若BIO引脚为低,TP=00;若TC位=1,TP=01;若TC位=0,TP=10;无条件TP=11。

ARX 用于LAR和SAR指令的3位数据值,指定被操作的辅助寄存器。

52表2 累加器、算数和逻辑指令 ABS周期|(ACC)|→ACC 1(ACC)+(数据存储器地址)×12shift→ACC(ACC)+(数据存储器地址)×216→ACC 1(ACC)+k→ACC 1shift(ACC)+lk×2→ACC 2指令功能(ACC)+(数据存储器地址)+(C)→ACC寻址方式直接/间接直接/间接短立即数长立即数指令说明ACC取绝对值移位时低位填0,若SXM=1,高位用符号扩展;若SXM=0,高位填0;结果存在ACC中,该指令使C=0。

DSP汇编指令缩写

DSP汇编指令缩写ABS Absolute value of AccumulatorADD add to accumulatorADDC add to accumulator with carryADDT add to accumulator with shift specified by TREGAND and with accumulatorCMPL complement accumulatorLACC load accumulator with shiftLACL load low accumulator and clear high accumulatorLACT load accumulator with shift specified by TREGNEG negate accumulatorNORM normalize contents of accumulatorOR or with accumulatorROL/ROR rotate accumulator left/rightSACH/SACL store high/low accumulator with shiftSFL/SFR shift accumulator left/rightSUB subtract from accumulatorSBUC conditional subtractSUBS subtract from accumulator with sign extension suppressed SUBT subtract from accumulator with shift specified by TREGXOR exclusive or with accumulatorZALR zero low accumulator and load high accumulator with rounding ADRK add short limmediate value to ARBANZ branch on AR not zeroCMPR compare AR with AR0LAR load ARMAR modify ARSTR store ARSBRK subtract short limmediateAPAC add PREG to accumulatorLPH load PREGLT load TREGLTA load TREG and ACC previous productLTD load TREG ACC previous product and move dateLTS load TREG and subtract previous productMAC multiply and accumulateMACD multiply and accumulate wit data moveMPY multiplyMPY A multiply and accumulate previous productMPYS multiply and subtract previous productMPYS multiply unsignPAC load accumulator with PREGSPAC subtract PREG from accumulatorSPH/SPL store high/low PREGSPM set PREG output shift modeSQRA/SQRS square value and accumulate/subtract previous product B branch unconditionallyBACC branch to location specified by ACCBANZ branch on AR not zeroBCND branch conditionallyCALA call subroutione at location specified by ACCCALL call unconditionallyCC call conditionallyINTR software interruptNMI nonmaskable interruptRET return from subroutineRETC return conditionallyTRAP software interruptBIT bit numberBITT test bit specified by TREGCLRC clear control bitIDEL idle until interruptLDP load data page pointerLST load status registerNOP no operationPOP pop top of stack to low ACCPOPD pop top of stack to data memoryPSHD push data-memory value onto stackPUSH push low ACC onto stackRPT repeat next instructionSETC set control bitSPM set PREG output shift modeSST store status registerBLDD block move from data memory to data memory BLPD block move from data memory to data memory DMOV data move in data memoryIN input data from portOUT output data to portSPLK store long immediate value to data memory TBLR table readTBLW table write。

DSP常用汇编语言指令简介

5. 控制指令举例

Example1:BIT0h,15 ;(DP = 6)把内存地址=300h 单元内容的最低位(BIT0)送给TC。 Example2:LDP #0h;使用立即数方式装载 数据页,也可以采用直接寻址和间接寻址方式装 载。 Example3:PUSH ;把累加器的低16位压入堆 栈。 Example4:SETC C;置进位C=1,也可以设置 以下的控制位为1或者为0,例如:CNF、INTM、 OVM、SXM、TC和XF。类似的指令还有: CLRC。

2. 工作寄存器等指令举例

Example4:ADRK #80h ;把当前工作寄存器内容 加一个立即数80h(注意立即数范围:00~FFh)。类 似的指令还有SBRK。 Example5:BANZ指令使用举例。例: MAR *, AR0 ;当前ARP=AR0 LAR AR1, #03h ;AR1内容赋值为03h LAR AR0, #60h ;AR0内容赋值为60h ZAC ; 累加器ACC清零 loop: ADD *+, AR1 ;把当前工作寄存器AR0指向 的内存单元数值加到ACC,然后AR0内容加1,当前工 作寄存器指针指向AR1 BANZ loop, *-AR0 ;判断AR0是否为0,否则程序 转到loop,同时AR0的内容减1。 南航自动化学院DSP技术应用实验 返回到第10页 室

南航自动化学院DSP技术应用实验 室

1. 累加器等指令举例

Example 1:ADD 1,1;(假设DP = 6),把 第6个数据页的第一个内存单元内容左移一 位加到累加器 Example 2:LACC *,4; (与SXM有关) Example 3:ROL;把累加器内容循环左移 Example 4:SACL *,0,AR7 ;把当前工作寄 存器指示内容左移0位送入累加器的低8位 Example 5:RPT #15 SUBC * ;累加器减去当前寄存 器指的内容,连续减16次,结果存累加器

dsp汇编指令

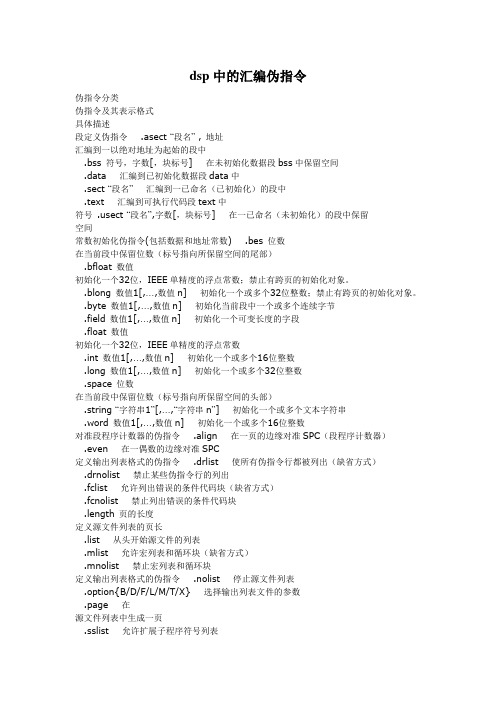

dsp中的汇编伪指令伪指令分类伪指令及其表示格式具体描述段定义伪指令 .asect “段名” , 地址汇编到一以绝对地址为起始的段中.bss 符号,字数[,块标号] 在未初始化数据段bss中保留空间.data 汇编到已初始化数据段data中.sect “段名”汇编到一已命名(已初始化)的段中.text 汇编到可执行代码段text中符号 .usect “段名”,字数[,块标号] 在一已命名(未初始化)的段中保留空间常数初始化伪指令(包括数据和地址常数) .bes 位数在当前段中保留位数(标号指向所保留空间的尾部).bfloat 数值初始化一个32位,IEEE单精度的浮点常数;禁止有跨页的初始化对象。

.blong 数值1[,…,数值n] 初始化一个或多个32位整数;禁止有跨页的初始化对象。

.byte 数值1[,…,数值n] 初始化当前段中一个或多个连续字节.field 数值1[,…,数值n] 初始化一个可变长度的字段.float 数值初始化一个32位,IEEE单精度的浮点常数.int 数值1[,…,数值n] 初始化一个或多个16位整数.long 数值1[,…,数值n] 初始化一个或多个32位整数.space 位数在当前段中保留位数(标号指向所保留空间的头部).string “字符串1”[,…,“字符串n”] 初始化一个或多个文本字符串.word 数值1[,…,数值n] 初始化一个或多个16位整数对准段程序计数器的伪指令 .align 在一页的边缘对准SPC(段程序计数器).even 在一偶数的边缘对准SPC定义输出列表格式的伪指令 .drlist 使所有伪指令行都被列出(缺省方式).drnolist 禁止某些伪指令行的列出.fclist 允许列出错误的条件代码块(缺省方式).fcnolist 禁止列出错误的条件代码块.length 页的长度定义源文件列表的页长.list 从头开始源文件的列表.mlist 允许宏列表和循环块(缺省方式).mnolist 禁止宏列表和循环块定义输出列表格式的伪指令 .nolist 停止源文件列表.option{B/D/F/L/M/T/X} 选择输出列表文件的参数.page 在源文件列表中生成一页.sslist 允许扩展子程序符号列表.ssnolist 禁止扩展子程序符号列表(缺省方式).tab 大小设置表的大小.title “字符串”在列表页头显示一个标题.width 页宽设置源文件列表的页宽外部文件定位的指伪令 .copy [“]文件名[”] 包含其他文件中的源语句.def 符号1[,…,符号n] 标明一个或多个在当前模块中定义而在其他模块中要用到的符号.global 符号1[,…,符号n] 标明一个或多个全局(外部)符号.include [“]文件名[”] 包含其他文件中的源语句.mlib [“]文件名[”] 定义宏定义库.ref符号1[,…,符号n] 标明一个或多个在另一模块中定义而在当前模块中要用到的符号条件汇编伪指令 .break [确切定义的表达式] 如果条件满足,就结束.loop汇编。

DSP指令大全(最全)

附录6 TMS320C54x 指令系统一览表(按指令功能排列) 一、算术运算指令二、逻辑运算指令三、程序控制指令6.注:?条件“真”,§条件“假”,※延迟指令。

四、加载和存储指令4.6.7.五.伪指令2.初始化常数(数据和存储器)的伪指令3.调整段程序计数器伪指令(SPC).align 把SPC调整到页边界.even 把SPC调整到偶数字边界4.控制输出列表格式化伪指令5.条件汇编伪指令.break [well-defined expression] 如果条件真结束.loop汇编,.break结构是可选项.else 如果.if条件为假,汇编代码块.else结构是可选项.elseif well-defined expression——如果if条件为假且.elseif条件为真,汇编代码块.else结构是可选项.endif 结束.if代码块.endloop 结束.1oop代码块.if well-defined expression 如果条件为真则汇编代码块.loop [well-defined expression] 开始代码块的重复汇编6. 汇编符号.asg [”] character string [”],substitution symbol——把字符串赋予替代的符号..endstruct 结束结构定义.equ 使值和符号相等.eval well-defined expression,substitution symbol 根据数字替代符号完成运算.newblock 取消局部标号.set 使数值和符号相等.struct 开始结构定义.tag 把结构属性赋予标号7.宏指令宏定义:Macname .macro[参数1],[…],[参数n]宏调用:[标号][:] macname [参数1],[…],[参数n]8.编译软件指令①汇编器:asm500.exeasm500[input file[object file [listing file] [-options]]-c—使汇编语言文件中大小没有区别。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

令执行的条件:

TCx(测试/控制标志为1) !TCx(测试/控制标志为0)

TC1&TC2 TC1&!TC2 TC1|TC2 TC1|!TC2 TC1^TC2 TC1^!TC2

!TC1&TC2 !TC1&!TC2 !TC1|TC2 !TC1|!TC2 !TC1^TC2 !TC1^!TC2

第五章 TMS320C55x系列DSP的汇编指令

4、双16比特算术指令: [(1)语法、(2)操作数、(3)状态位] 在D单元中利用其ALU的双16比特模式,同时执行(并行)两个16

比特算术运算,包括加-减、减-加、两个加和两个减运算。

例:

▪ M40=0时,D单元按32位运算模式,因此累加器溢出、进位、符号扩

展和移位操作都以第31比特为准。

▪ M40=1时,D单元按40位运算模式,因此累加器溢出,进位,符号扩

展和移位操作都以第39比特为准。

BCLR M40 ; Clear M40

BSET M40 ; Set M40

第五章 TMS320C55x系列DSP的汇编指令

第五章 TMS320C55x系列DSP的汇编指令

一、算术运算指令 用于完成加减乘除等运算,按照功能可分成以下几类:

▪ 加法指令 ▪ 减法指令:减法,条件减法,条件加/减 ▪ 乘法指令:乘法,乘加,乘减,双乘加/减 ▪ 双16比特算术指令 ▪ 比较运算指令:比较并求极值,最大/最小值,存储单元比较,寄存器比较 ▪ 移位指令:条件移位、带符号的移位。 ▪ 寄存器修改:辅助寄存器修改、堆栈指针SP修改 ▪ 隐含的并行指令 ▪ 专用指令:绝对值、归一化、有限冲激响应滤波FIR、最小均方LMS等

✓ M40=0时: 溢出位在第31位检测

✓ M40=1时: 溢出位在第39位检测

BCLR ACOV1 ;清零 BSET ACOV1 ;置位

第五章 TMS320C55x系列DSP的汇编指令

3、兼容模式(C54CM)

▪ C54CM=0:CPU工作于增强模式,只支持C55x的指令, ▪ C54CM=1: CPU工作于兼容模式,既支持C54x又支持C55x指令。 ✓ BCLR C54CM ; Clear C54CM (happens at run time) ✓ C54CM_off ; Tell assembler C54CM = 0 ✓ BSET C54CM ; Set C54CM (happens at run time) ✓ C54CM_on ; Tell the assembler C54CM = 1

*ARx<=#0

*ARx>#0

ACx<#0 ACx>=#0

*ARx<#0 *ARx>=#0

第五章 TMS320C55x系列DSP的汇编指令

(4)临时寄存器的值(4个临时寄存器T0~T3)

Tx==#0

Tx!=#0 Tx<#0

Tx<=#0

Tx>#0

Tx>=#0

(5) 测试/控制标志

两个测/控制标志的状态以及它们的逻辑组合可以作为指

第五章 TMS320C55x系列DSP的汇编指令

可以作为指令执行的条件有:

(1)累加器的值

ACx==#0

ACx!=#0

ACx<=#0

ACx>#0

(2)溢出标志和进位标志

overflow(ACx) !overflow(ACx)

CARRY

!CARRY

(3)辅助寄存器的值

*ARx==#0

*ARx!=#0

第五章 TMS320C55x系列DSP的汇编指令

4、进位标志(CARRY) CARRY表示是否有进位或借位发生

▪ CARRY=0时,没有借位或进位发生。

▪ CARRY=1时,有借位或进位发生。

▪ 位操作指令改变CARRY

✓ BCLR CARRY ; Clear CARRY ✓ BSET CARRY ; Set CARRY

5.3 C55x指令的并行执行 1、并行指令的分类

C55只支持有限的指令并行执行,能支持三种类型的指令并行。 (1) 隐含的或内置的单指令并行

一条指令同时执行两个不同的操作,用“::”来分隔指令的两 个部分。

MPY *AR0, *CDP, AC0 :: MPY *AR1, *CDP, AC1

这类指令是利用双MAC来实现的,C55x中,这视为一条单指令。

第五章 TMS320C55x系列DSP的汇编指令

1、加法指令 在D单元或A单元中执行加法运算。

▪ 当有一个目的操作数为累加器ACx时,在D-ALU中执行。 ▪ 当目的操作数为辅助或临时寄存器时,在A-ALU中执行 ▪ 当目的操作数为Smen时,在D-ALU中执行 ▪ 当移位位数不是立即数16时(移位指令),在D单元的移位器中执 行。 ▪(1)语法 ▪(2)操作数 ▪(3)状态位 举例:ADD uns(*AR3),CARRY,AC1,AC0

第五章 TMS320C55x系列DSP的汇编指令

1、高速数字信号处理中常采用汇编语言编程。 2、汇编语言中的两种指令集 (1) 助记符指令集:有助于记忆的符号来表示指令。 (2) 代数指令集:类似于代数表达式,运算关系清楚明了。 注意:DSP的软件开发工具只支持单一的指令形式,不支持助记

符指令和代数指令的混合形式。 3、术语、符号和缩写见P93的表5-1 4、运算符见表5-2

第五章 TMS320C55x系列DSP的汇编指令

2、减法指令 ▪ 常规减法:在D单元或A单元执行减法操作。 ▪ 条件减法:在D单元中执行,先执行减法,然后根据结果进行移位。 ▪ 条件加/减:在D单元根据TC1或TC2的状态执行加/减运算。 ▪(1)语法;(2)操作数;(3)状态位

例1(常规减法):

; Clear FRCT ; Set FRCT

第五章 TMS320C55x系列DSP的汇编指令

6、中断模式(INTM)

▪ INTM=0:允许所有可屏蔽中断 ▪ INTM=1:关闭所有可屏蔽中断

✓ BCLR INTM ✓ BSET INTM

; Clear INTM ; Set INTM

第五章 TMS320C55x系列DSP的汇编指令

第五章 TMS320C55xDSP的汇编指令

5.1状态比特和 执行条件

一条指令的执 行可能会受到某些 状态位的影响,也 可能会改变某些状 态位的值,这些状 态位都在状态寄存 器。

第五章 TMS320C55x DSP的汇编指令

1、40比特运算模式(M40)

用于控制D单元的运行模式,会影响累加器溢出、进位标志等。

寻址,不满足规则3,所以不能并行。

在实际编程时,只要指令满足这三条基本规则,即可写成并行 方式,然后进行编译。如果编译有错,则可参照pp.77-78的8条 详细规则进行检测。

第五章 TMS320C55x系列DSP的汇编指令

5.4 TMS320C55x DSP的汇编指令

TMS320C55x DSP的汇编指令按操作分为以下6类

;用户自定义并行

第五章 TMS320C55x系列DSP的汇编指令

2、指令并行的规则 只有满足以下三条基本规则,并行指令才可以使用,若非

法使用并行指令,可能会导致不可预测的执行结果。 规则1:指令长度要少于6个字节 受I单元指令译码器的限制,只有两条指令长度不超过6字节的,

才可以作为并行处理。[IBQ大小为64字节/译码器大小为6字节] 规则2:没有硬件资源冲突 如果两条指令不存在操作数、总线、内部交叉单元和寄存器

7 、测试/控制标志(TCx)

▪ 主要用于保存某些测试指令的结果; ▪ 可以作为指令执行的条件; ▪ 举例:CMP AC1 = = T1, TC1;;如果AC1 = T1,那么TC1=1。

BCLR TC1 ; Clear TC1 BSET TC1 ; Set TC1 BCLR TC2 ; Clear TC2 BSET TC2 ; Set TC2

3、乘法指令 [(1)语法、(2)操作数、(3)状态位]

▪ 常规乘法(MPY):在D单元的一个MAC中执行乘法运算。

▪ 乘加和乘减运算(MAC/MAS):在D单元的一个MAC中执行乘法,然 后执行加法或减法运算。

▪ 双乘加/减(Dual-MAC/S): 利用D单元的两个MAC同时执行两个乘法或

乘加/乘减运算。 例1(常规乘法)

▪ 算术运算指令 ▪ 比特操作指令 ▪ 扩展辅助寄存器操作指令 ▪ 逻辑操作指令 ▪ MOVE操作指令 ▪ 程序控制指令

一条指令的属性包括: ▪ 语法(Syntax) ▪ 执行的操作 ▪ 操作数 ▪ 相关的状态位 ▪ 是否有并行使能位 ▪ 长度(Size) ▪ 执行周期(Cycles) ▪ 在流水线(Pipeline)上的执行阶段 ▪ 在哪个功能单元执行(Executed) ▪ 是否可以重复执行等

之间的冲突,则可以并行。

第五章 TMS320C55x系列DSP的汇编指令

规则3:并行指令含有两个数据存储器访问时,必须使用间 接寻址模式。

以上三条规则是基本规则,缺一不可。

例如:

MOV *AR,AC1

;2个字节

||ADD @var,AR2 ;3个字节

两条指令访问两个数据存储单元,第二条指令没有使用间接

第五章 TMS320C55x系列DSP的汇编指令

(2) 用户自定义的双指令的并行

这两条指令的并行是通过用户或C编译器定义的。两条指令 同时执行两个操作,用并行符“||”区分并行执行的两条指令。 例:

MPYM *AR1+, *CDP, AC1 ;D单元的一个MAC来完成

||XOR AR2,T1

;A单元的ALU来完成

第五章 TMS320C55x系列DSP的汇编指令

例如: -----------------------------------------------------------------------------------| ADD uns(*AR3),CARRY,AC1,AC0 | No | 3 | 1 | X | D - ALU | ------------------------------------------------------------------------------------