DSP 汇编指令缩写

第五章 DSP的汇编指令..

第五章 TMS320C55x系列DSP的汇编指令

(2) 用户自定义的双指令的并行

这两条指令的并行是通过用户或C编译器定义的。两条指令 同时执行两个操作,用并行符“||”区分并行执行的两条指令。 例:

MPYM *AR1+, *CDP, AC1 ;D单元的一个MAC来完成

||XOR AR2,T1

;A单元的ALU来完成

第五章 TMS320C55x系列DSP的汇编指令

1、高速数字信号处理中常采用汇编语言编程。 2、汇编语言中的两种指令集 (1) 助记符指令集:有助于记忆的符号来表示指令。 (2) 代数指令集:类似于代数表达式,运算关系清楚明了。 注意:DSP的软件开发工具只支持单一的指令形式,不支持助记

符指令和代数指令的混合形式。 3、术语、符号和缩写见P93的表5-1 4、运算符见表5-2

令执行的条件:

TCx(测试/控制标志为1) !TCx(测试/控制标志为0)

TC1&TC2 TC1&!TC2 TC1|TC2 TC1|!TC2 TC1^TC2 TC1^!TC2

!TC1&TC2 !TC1&!TC2 !TC1|TC2 !TC1|!TC2 !TC1^TC2 !TC1^!TC2

第五章 TMS320C55x系列DSP的汇编指令

4、双16比特算术指令: [(1)语法、(2)操作数、(3)状态位] 在D单元中利用其ALU的双16比特模式,同时执行(并行)两个16

比特算术运算,包括加-减、减-加、两个加和两个减运算。

例:

说明: NO:不能并行执行 3:指令的长度为3字节 1:周期为1 X:在X(执行)流水线阶段处理

D – ALU:在D单元ALU执行。 执行结果:AC0=(*AR3)+CARRY+AC1 状态位: Affected by CARRY,C54CM,M40等

第五章 DSP的汇编指令..

令执行的条件:

TCx(测试/控制标志为1) !TCx(测试/控制标志为0)

TC1&TC2 TC1&!TC2 TC1|TC2 TC1|!TC2 TC1^TC2 TC1^!TC2

!TC1&TC2 !TC1&!TC2 !TC1|TC2 !TC1|!TC2 !TC1^TC2 !TC1^!TC2

第五章 TMS320C55x系列DSP的汇编指令

4、双16比特算术指令: [(1)语法、(2)操作数、(3)状态位] 在D单元中利用其ALU的双16比特模式,同时执行(并行)两个16

比特算术运算,包括加-减、减-加、两个加和两个减运算。

例:

▪ M40=0时,D单元按32位运算模式,因此累加器溢出、进位、符号扩

展和移位操作都以第31比特为准。

▪ M40=1时,D单元按40位运算模式,因此累加器溢出,进位,符号扩

展和移位操作都以第39比特为准。

BCLR M40 ; Clear M40

BSET M40 ; Set M40

第五章 TMS320C55x系列DSP的汇编指令

第五章 TMS320C55x系列DSP的汇编指令

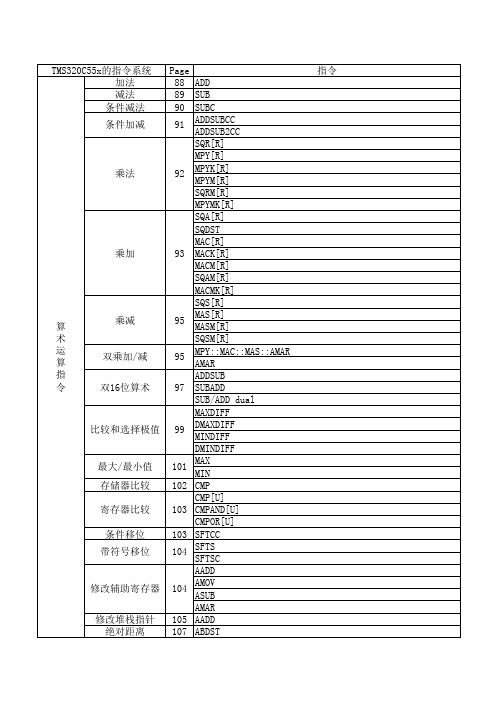

一、算术运算指令 用于完成加减乘除等运算,按照功能可分成以下几类:

▪ 加法指令 ▪ 减法指令:减法,条件减法,条件加/减 ▪ 乘法指令:乘法,乘加,乘减,双乘加/减 ▪ 双16比特算术指令 ▪ 比较运算指令:比较并求极值,最大/最小值,存储单元比较,寄存器比较 ▪ 移位指令:条件移位、带符号的移位。 ▪ 寄存器修改:辅助寄存器修改、堆栈指针SP修改 ▪ 隐含的并行指令 ▪ 专用指令:绝对值、归一化、有限冲激响应滤波FIR、最小均方LMS等

✓ M40=0时: 溢出位在第31位检测

第六章_DSP的汇编语法寻址及指令系统2

助记符方式汇编程序语法

[label][:] mnemonic [operand list] [;comment]

[标号][:] 助记符

[操作数]

[;注释]

汇编程序语法

1.所有的语句必须由语句标号、空格、*号或 ; 号开头。 2.语句标号不是必须的,如果用,就必须在第一 列。 3.语句中的各部分之间,由一个或多个空格分开。 4.注释不是必须的。注释可以从第一列的 * 号 或 ;号开头;如果不是从第一列开始,就必须 用 ;号开头。

MPY

乘法器

第六章 汇编语法,寻址及指令系统

• 1.汇编语法 • 2.寻址方式 • 3.指令系统

汇编程序语法

TMS320的汇编程序包含:

1. 汇 编 语 言 指 令 ( assembly language instructions)、 2. 汇编指令(伪指令,assembler directives)、 3. 宏指令(macro directives) 4. 注释(comments)。

片内DARAM配置位。该位用于确定x24x芯片内的可配置DARAM存储块的配置。当

XF

PM

1

符 号

名 称 累加器 辅助寄存器算术单元

说 明 一个32位寄存器.用来保存CALU计算结果,并为下一次CALU操作提供输入, 它具有移位和循环操作功能 一个无符号、16位算术单元间接寻址时,用辅助寄存器算数单元来计算辅 助寄存器地址 这些16位寄存器可用作指针,指向数据存储空间范围内的任何地址。它们 面向ARAU单元操作,由辅助寄存器指针(ARP)选定。AR0可用来作为更新 ARx(x为1~7)参考值,也可作为ARx的比较值 寄存器进位位由CALU输出,C被反馈到CALU单元,用于扩展运算操作。C位 位于状态寄存器(ST1),其状态可通过条件指令测试。C位也可用于累加器 移位和循环 TMS320C2xx核的32位主要算术逻辑单元。CALU在一个单机器周期内执行32 位操作。它对来自ISCALE或PSCALE的数据和来自ACC的数据进行运算,并将 运算后的状态结果存于PCTRL单元 如果片内RAM配置控制位(CNF)被设置为0,那么可配置的双口RAM(DARAM)块 BO被映射到数据存储空间;否则,BO被映射列程序存储空间。块B1和B2分 别映射到地址分别为0300h~03FFh和0060h—007Fh的数据存储器空间。块0 和1的容量为256宇,而块2的容量为32字 9位DP寄存器与一个指令字的低7位(LSBs)一起形成一个16位的直接寻址地 址。DP值可由LST和LDP指令改变 GREG指定全局数据存储器的空间大小。由于F240x器件没有使用全局。存储 器空间,这个寄存器被保留下来 MR寄存器的各位分别屏蔽或使能对应的7个中断 IFR的7位分别指示TMS320C2xx已进入7个可屏蔽的中断中的任意一个中断 一个16~32位的桶式左向移位器。ISCALE能将输入的16位数据的0~16位在 本周期内,向左移位以得到32位输出,因此输入定标移位操作不需要额外 的周期 经过16X16位乘法运算得到一个32位的乘积。MPY可在一个单周期内完成乘

DSP汇编指令索引

指令

指令

隐含并行

105

算 术 运 算 指 令

绝对值 FIR滤波 最小均方 补码 归一化 饱和和舍入 平方距离 位域比较 位域抽取 位域扩展

107 108 109 109 109 110 110 111 111 111

位 操 作 指 令

存储器位操作

112

寄存器位操作

113

状态位设置 扩展辅助 寄存器操 作指令 按位与/或 /异或/取反 位计数 逻辑移位 循环移位

114

115 116 117 118

逻辑运 算指令

TMS320C55x的指令系统 Page 累加器、辅助寄 MOV 存器或临时寄存 SWAP 119 器装载、存储、 SWAPP 移 移动、和交换 SWAP4 动 存储单元间的移 DELAY 122 指 动及初始化 MOV 令 POP 入栈和出栈 122 PSH CPU寄存器装载、 124 MOV 存储和移动 B 跳转 127 BCC CALL CALLCC 调用与返回 128 RET RETCC INTR 程 中断与返回 128 TRAP 序 RETI 控 PRT 制 PRTADD 指 PRTSUB 重复 128 令 PRTCC PRTB PRTBLOCAL XCC 条件执行 XCCPART 129 IDLE 空闲 空操作 NOP 软件复位 RESET

指令

TMS320C55x的指令系统

Page MPYM::MOV MACM::MOV MASM::MOV ADD::MOV SUB::MOV MOV::MOV ABS FIRSADD FIRSSUB LMS NEG MANT ::NEXP EXP SAT ROUND SQDST BAND BFXTR BFXPA BTST BNOT BCLR BSET BTSTSET BTSTCLR BTSTNOT BTST BNOT BCLR BSET BTSTP BCLR BSET MOV AMAR AMOV POPBOTH PSHBOTH NOT AND/OR/XOR BCNT SFTL ROL

DSP汇编指令缩写

DSP汇编指令缩写ABS Absolute value of AccumulatorADD add to accumulatorADDC add to accumulator with carryADDT add to accumulator with shift specified by TREGAND and with accumulatorCMPL complement accumulatorLACC load accumulator with shiftLACL load low accumulator and clear high accumulatorLACT load accumulator with shift specified by TREGNEG negate accumulatorNORM normalize contents of accumulatorOR or with accumulatorROL/ROR rotate accumulator left/rightSACH/SACL store high/low accumulator with shiftSFL/SFR shift accumulator left/rightSUB subtract from accumulatorSBUC conditional subtractSUBS subtract from accumulator with sign extension suppressed SUBT subtract from accumulator with shift specified by TREGXOR exclusive or with accumulatorZALR zero low accumulator and load high accumulator with rounding ADRK add short limmediate value to ARBANZ branch on AR not zeroCMPR compare AR with AR0LAR load ARMAR modify ARSTR store ARSBRK subtract short limmediateAPAC add PREG to accumulatorLPH load PREGLT load TREGLTA load TREG and ACC previous productLTD load TREG ACC previous product and move dateLTS load TREG and subtract previous productMAC multiply and accumulateMACD multiply and accumulate wit data moveMPY multiplyMPY A multiply and accumulate previous productMPYS multiply and subtract previous productMPYS multiply unsignPAC load accumulator with PREGSPAC subtract PREG from accumulatorSPH/SPL store high/low PREGSPM set PREG output shift modeSQRA/SQRS square value and accumulate/subtract previous product B branch unconditionallyBACC branch to location specified by ACCBANZ branch on AR not zeroBCND branch conditionallyCALA call subroutione at location specified by ACCCALL call unconditionallyCC call conditionallyINTR software interruptNMI nonmaskable interruptRET return from subroutineRETC return conditionallyTRAP software interruptBIT bit numberBITT test bit specified by TREGCLRC clear control bitIDEL idle until interruptLDP load data page pointerLST load status registerNOP no operationPOP pop top of stack to low ACCPOPD pop top of stack to data memoryPSHD push data-memory value onto stackPUSH push low ACC onto stackRPT repeat next instructionSETC set control bitSPM set PREG output shift modeSST store status registerBLDD block move from data memory to data memory BLPD block move from data memory to data memory DMOV data move in data memoryIN input data from portOUT output data to portSPLK store long immediate value to data memory TBLR table readTBLW table write。

DSP中的EALLOW和EDIS

DSP中的EALLOW和EDIS

F2812中有⼀些配置寄存器是受保护的,⽆法直接操作。

在对这些寄存器进⾏修改之前,需要先去掉保护功能。

⽽保护状态是由状态寄存器中EALLOW标志来指⽰的。

汇编指令“EALLOW”就是将该标志位置位,允许对受保护的寄存器操作。

EALLOW(Edit allow)⼀般和EDIS(Edit disable)配套使⽤,在对受保护的寄存器操作之后,⽤EDIS恢复寄存器的被保护状态。

F280x器件上的⼏个控制寄存器受EALLOW 保护机制保护以防⽌虚假的CPU 写⼊。

在复位时EALLOW位被清除以启⽤EALLOW 保护。

在受保护时,CPU 对受保护寄存器进⾏的所有写⼊被忽略且只允许CPU读取、JTAG读取和JTAG写⼊。

如果设置了此位,则通过执⾏EALLOW指令可以允许CPU⾃由写⼊受保护的寄存器。

在修改寄存器之后,可以通过执⾏EDIS指令清除EALLOW位使它们再次受保护。

以下列寄存器受EALLOW保护:

· 器件仿真寄存器

· 闪存寄存器

· CSM 寄存器

· PIE ⽮量表

· 系统控制寄存器

· GPIO MUX 寄存器

· 某些eCAN 寄存器

eg:

// Enable EALLOW

EALLOW;

// Setting PWM1-6 as primary output pins

GpioMuxRegs.GPAMUX.all |= 0x003F;

// Disable EALLOW

EDIS;。

DSP缩略词整理

DSP缩略词整理DSP digital signal processing 数字信号处理的理论和方法SUB subtract from accumulator 带累加器减法SBUC conditional subtract from accumulator 有条件带累加器减法SUBS subtract from accumulator with sign extension suppressed 抑制符号带累加器减法STR store AR 存储到ARMAR modify AR 修改ARLAR load AR 加载ARCMPR compare AR with AR0 比较AR和AR0XOR exclusive or with accumulator 特殊与或累加器ZALR zero low accumulator and load high accumulator with rounding 低位取零高位取整BANZ branch on AR not zero 不分配AR 0SBRK subtract short limmediate 减去短的立即数APAC add PREG to accumulator 把PREG加到累加器LPH load PREG 加载PREGLT load TREG 加载TREGLTA load TREG and ACC previous product 加载TREG和ACC之前的输出LTD load TREG ACC previous product and move date 加载TREG ACC之前的输出和移动日期LTS load TREG and subtract previous product 加载TREG和减去以前的输出MAC multiply and accumulate 乘法和积累MACD multiply and accumulate wit data move 带数据移动的乘加运算MPY A multiply and accumulate previous product 乘加之前的输出 MPYS multiply and subtract previous product 乘减之前的输出TI Texas Instrumens 美国德州仪器公司ASIC Application Specific Intergrated Circuit 专用集成电路BS Barrel Shifter 桶形移位寄存器AU Addressing Unit 寻址单元PAGEN Program Address Generation Logic 逻辑发生程序地址DAGEN Data Address Generation Logic 数据地址产生单元PLL Phase Locked Loops 锁相环电路IFR Interrupt Flag Register 中断标志寄存器IMR Interrrupt Mask Register 中断屏蔽寄存器TIM Timer Register 定时器寄存器PRD Timer Period Register 定时器周期寄存器TCR Timer Control Register 定时器控制寄存器TDDR Timer Divide Down Ration 定时器分频系数TSS Timer Stop Status 定时器停止状态位TRB Timer Reload 定时器重新加载位PSC Timer Prescaler Counter 定时器预定标计数器HPI Host Port Interface 主机接口SPI Serial Port Interface 标准同步串行BSP Buffered Serial Port 缓冲串行口TDM Time Division Multiplexed 时分多路复用串行接口IDE Intergrated Development Environment 集成开发环境ABS Absolute value of Accumulator 累加器绝对值ADD add to accumulator 累加器值相加ADDC add toaccumulator with carry 带进位加法运算LACC load accumulator with shift 加载移位累加器LACL load low accumulator and clear high accumulator 加载到累加器低位字和清除累加器高位字LACT load accumulator with shift specified by TREG 通过TREG 特殊移位加载到累加器NEG negate accumulator 否定累加器NORM normalize contents of accumulator 正规化累加器ROL/ROR rotate accumulator left/right 左/右旋转累加器SACH/SACL store high/low accumulator with shift 高/低位存储移位累加器SFL/SFR shift accumulator left/right 左/右移位累加器SPAC subtract PREG from accumulator 从累加器减去PREG MELP Mixed Excitation LPC Vocoder 混合激励线性预测编码器FBTC Flashburn Target Component 下载用具CCS Code Composer Studio TI 公司的DSP软件编译环境GEL General Eextension Language 类似于C语言的解释性语言RF3 Reference Frmework level 3 应用程序使用多通道和多算法API Application Program Interface 应用程序编程接口EMIF External Memory Interface 外部存储器界面RAM random access memory 随机存储器SDRAM Synchronous Dynamic Random Access Memory 同步动态随机存储器ALU Arithmetic-Logic Unit 算术逻辑单元ARP Address Resolution Protocol 辅助寄存器指针ROM Read-Only Memory 只读存储器PCB Printed circuit board 电路板HPI Hardware Platform Interface 主机接口。

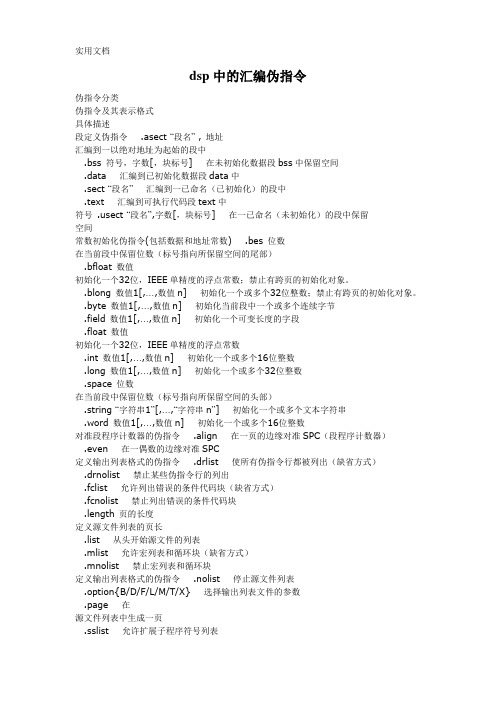

dsp汇编指令

dsp中的汇编伪指令伪指令分类伪指令及其表示格式具体描述段定义伪指令 .asect “段名” , 地址汇编到一以绝对地址为起始的段中.bss 符号,字数[,块标号] 在未初始化数据段bss中保留空间.data 汇编到已初始化数据段data中.sect “段名”汇编到一已命名(已初始化)的段中.text 汇编到可执行代码段text中符号 .usect “段名”,字数[,块标号] 在一已命名(未初始化)的段中保留空间常数初始化伪指令(包括数据和地址常数) .bes 位数在当前段中保留位数(标号指向所保留空间的尾部).bfloat 数值初始化一个32位,IEEE单精度的浮点常数;禁止有跨页的初始化对象。

.blong 数值1[,…,数值n] 初始化一个或多个32位整数;禁止有跨页的初始化对象。

.byte 数值1[,…,数值n] 初始化当前段中一个或多个连续字节.field 数值1[,…,数值n] 初始化一个可变长度的字段.float 数值初始化一个32位,IEEE单精度的浮点常数.int 数值1[,…,数值n] 初始化一个或多个16位整数.long 数值1[,…,数值n] 初始化一个或多个32位整数.space 位数在当前段中保留位数(标号指向所保留空间的头部).string “字符串1”[,…,“字符串n”] 初始化一个或多个文本字符串.word 数值1[,…,数值n] 初始化一个或多个16位整数对准段程序计数器的伪指令 .align 在一页的边缘对准SPC(段程序计数器).even 在一偶数的边缘对准SPC定义输出列表格式的伪指令 .drlist 使所有伪指令行都被列出(缺省方式).drnolist 禁止某些伪指令行的列出.fclist 允许列出错误的条件代码块(缺省方式).fcnolist 禁止列出错误的条件代码块.length 页的长度定义源文件列表的页长.list 从头开始源文件的列表.mlist 允许宏列表和循环块(缺省方式).mnolist 禁止宏列表和循环块定义输出列表格式的伪指令 .nolist 停止源文件列表.option{B/D/F/L/M/T/X} 选择输出列表文件的参数.page 在源文件列表中生成一页.sslist 允许扩展子程序符号列表.ssnolist 禁止扩展子程序符号列表(缺省方式).tab 大小设置表的大小.title “字符串”在列表页头显示一个标题.width 页宽设置源文件列表的页宽外部文件定位的指伪令 .copy [“]文件名[”] 包含其他文件中的源语句.def 符号1[,…,符号n] 标明一个或多个在当前模块中定义而在其他模块中要用到的符号.global 符号1[,…,符号n] 标明一个或多个全局(外部)符号.include [“]文件名[”] 包含其他文件中的源语句.mlib [“]文件名[”] 定义宏定义库.ref符号1[,…,符号n] 标明一个或多个在另一模块中定义而在当前模块中要用到的符号条件汇编伪指令.break [确切定义的表达式] 如果条件满足,就结束.loop汇编。

DSP常用汇编语言指令简介

5. 控制指令举例

Example1:BIT0h,15 ;(DP = 6)把内存地址=300h 单元内容的最低位(BIT0)送给TC。 Example2:LDP #0h;使用立即数方式装载 数据页,也可以采用直接寻址和间接寻址方式装 载。 Example3:PUSH ;把累加器的低16位压入堆 栈。 Example4:SETC C;置进位C=1,也可以设置 以下的控制位为1或者为0,例如:CNF、INTM、 OVM、SXM、TC和XF。类似的指令还有: CLRC。

2. 工作寄存器等指令举例

Example4:ADRK #80h ;把当前工作寄存器内容 加一个立即数80h(注意立即数范围:00~FFh)。类 似的指令还有SBRK。 Example5:BANZ指令使用举例。例: MAR *, AR0 ;当前ARP=AR0 LAR AR1, #03h ;AR1内容赋值为03h LAR AR0, #60h ;AR0内容赋值为60h ZAC ; 累加器ACC清零 loop: ADD *+, AR1 ;把当前工作寄存器AR0指向 的内存单元数值加到ACC,然后AR0内容加1,当前工 作寄存器指针指向AR1 BANZ loop, *-AR0 ;判断AR0是否为0,否则程序 转到loop,同时AR0的内容减1。 南航自动化学院DSP技术应用实验 返回到第10页 室

南航自动化学院DSP技术应用实验 室

1. 累加器等指令举例

Example 1:ADD 1,1;(假设DP = 6),把 第6个数据页的第一个内存单元内容左移一 位加到累加器 Example 2:LACC *,4; (与SXM有关) Example 3:ROL;把累加器内容循环左移 Example 4:SACL *,0,AR7 ;把当前工作寄 存器指示内容左移0位送入累加器的低8位 Example 5:RPT #15 SUBC * ;累加器减去当前寄存 器指的内容,连续减16次,结果存累加器

第三章DSP汇编指令

if 0≤ index+step < BK: index = index + step

else if index + step ≥ BK: index = index + step - BK

else if index + step< 0 index = index + step + BK

只有8条指令能使用存储器映射寄存器寻址:

LDM MMR, dst MVDM dmad, MMR MVMD MMR, dmad MVMM MMRx, MMRy POPM MMR PSHM MMR STLM src, MMR STM #lk, MMR

7. 堆栈寻址

系统堆栈用来在中断和子程序期间自动存放程序计数器。 它也能用来存放额外的数据项或传递数据值。处理器使用一 个16-bit的存储器映射寄存器—堆栈指针来对堆栈寻址,它 总是指向存放在堆栈中的最后一个元素。

2、调用与中断指令

3、返回指令

4、重复指令和堆栈操作指令

四、装入和存储指令

装入和存储指令包括:

一般的装入和存储指令 条件存储指令 并行装入和存储指令 并行装入和乘法指令 并行存储和加件乘指令 混合装入和存储指令

1、一般的装入指令

2、存贮指令

3 并行装入和存储指令 4、条件存储指令

共有四条使用堆栈寻址方பைடு நூலகம்访问堆栈的指令:

PSHD 把一个数据存储器的值压入堆栈。 PSHM 把 一 个 存 储 器 映 射 寄 存 器 的 值 压 入 堆 栈 。 POPD 把一个数据存储器的值弹出堆栈。 POPM 把一个存储器映射寄存器的值弹出堆栈。

§3-2 特殊寻址方式说明

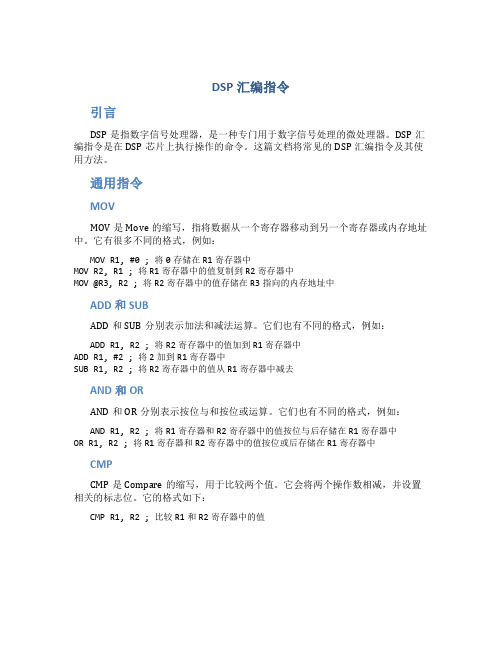

DSP汇编指令总结

DSP汇编指令引言DSP是指数字信号处理器,是一种专门用于数字信号处理的微处理器。

DSP汇编指令是在DSP芯片上执行操作的命令。

这篇文档将常见的DSP汇编指令及其使用方法。

通用指令MOVMOV是Move的缩写,指将数据从一个寄存器移动到另一个寄存器或内存地址中。

它有很多不同的格式,例如:MOV R1, #0 ; 将0存储在R1寄存器中MOV R2, R1 ; 将R1寄存器中的值复制到R2寄存器中MOV @R3, R2 ; 将R2寄存器中的值存储在R3指向的内存地址中ADD和SUBADD和SUB分别表示加法和减法运算。

它们也有不同的格式,例如:ADD R1, R2 ; 将R2寄存器中的值加到R1寄存器中ADD R1, #2 ; 将2加到R1寄存器中SUB R1, R2 ; 将R2寄存器中的值从R1寄存器中减去AND和ORAND和OR分别表示按位与和按位或运算。

它们也有不同的格式,例如:AND R1, R2 ; 将R1寄存器和R2寄存器中的值按位与后存储在R1寄存器中OR R1, R2 ; 将R1寄存器和R2寄存器中的值按位或后存储在R1寄存器中CMPCMP是Compare的缩写,用于比较两个值。

它会将两个操作数相减,并设置相关的标志位。

它的格式如下:CMP R1, R2 ; 比较R1和R2寄存器中的值跳转指令JMPJMP是Jump的缩写,用于无条件跳转到目标地址。

它的格式如下:JMP label ; 跳转到标签为label的位置JNZ和JZJNZ和JZ分别表示如果结果不为零则跳转和如果结果为零则跳转。

它们的格式如下:JNZ label ; 如果前一条CMP指令比较结果不为零,则跳转到标签为label的位置JZ label ; 如果前一条CMP指令比较结果为零,则跳转到标签为label的位置JGE和JLEJGE和JLE分别表示如果大于或等于则跳转和如果小于或等于则跳转。

它们的格式如下:JGE label ; 如果前一条CMP指令比较结果大于或等于,则跳转到标签为label的位置JLE label ; 如果前一条CMP指令比较结果小于或等于,则跳转到标签为label的位置循环指令DJNZDJNZ是Decrement and Jump if Not Zero的缩写,表示如果操作数不为零则减1并跳转到目标地址。

汇编语言指令及标志位状态英文缩写

DEC---->decrease 1

NEC---->negative

CMP---->compare

AAS---->ASCII adjust on subtract

DAS---->decimal adjust on subtract

MUL---->multiplication

JBE---->jump when below or equal

JNA---->jump when not above

JG---->jump when greater

JNLE---->jump when not less or equal

JGE---->jump when greater or equal

2>条件转移指令(短转移,-128到+127的距离内)

JAE---->jump when above or equal

JNB---->jump when not below

JB---->jump when below

JNAE---->jump when notபைடு நூலகம்above or equal

XADD---->exchange and add

XLAT---->translate

2.输入输出端口传送指令.

IN---->input

OUT---->output

3.目的地址传送指令.

LEA---->load effective address

c54xx系列DSP汇编指令详解

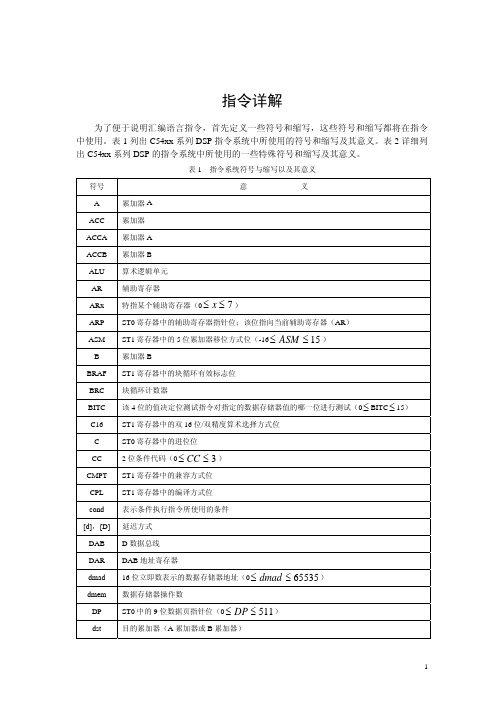

为了便于说明汇编语言指令,首先定义一些符号和缩写,这些符号和缩写都将在指令 中使用。表 1 列出 C54xx 系列 DSP 指令系统中所使用的符号和缩写及其意义。表 2 详细列 出 C54xx 系列 DSP 的指令系统中所使用的一些特殊符号和缩写及其意义。

表 1 指令系统符号与缩写以及其意义

dst = src – #lk <<16

从 src 中减去长立即数移动 16 位后的值,结果存到 dst 中

dst = dst – src << SHIFT

从 dst 中减去 src 移动 SHIFT 位后的值

dst = dst – src << ASM

从 dst 中减去 src 移动 ASM 位 后的值

② 减法指令

语法 SUB Smem, src

SUB Smem, TS, src SUB Smem, 16, src [, dst] SUB Smem [, SHIFT], src [, dst] SUB Xmem, SHFT, src

SUB Xmem, Ymem, dst

SUB # lk [, SHFT], src [, dst]

目的累加器的反 if dst=A,then dst_=B if dst=B then dst_=A

E 地址总线 EAB 地址寄存器 23 位立即数表示的程序存储器地址 ST1 寄存器中的分数方式位 十六进制数据 十六进制数据 累加器 A 的高端(位 32~16) ST1 寄存器中的保持方式位 中断标志寄存器 ST1 寄存器中的中断屏蔽位 少于 9 位的短立即数

表达式 dst = T * Smem

dst = rnd(T * Smem)

dst = Xmem * Ymem, T = Xmem

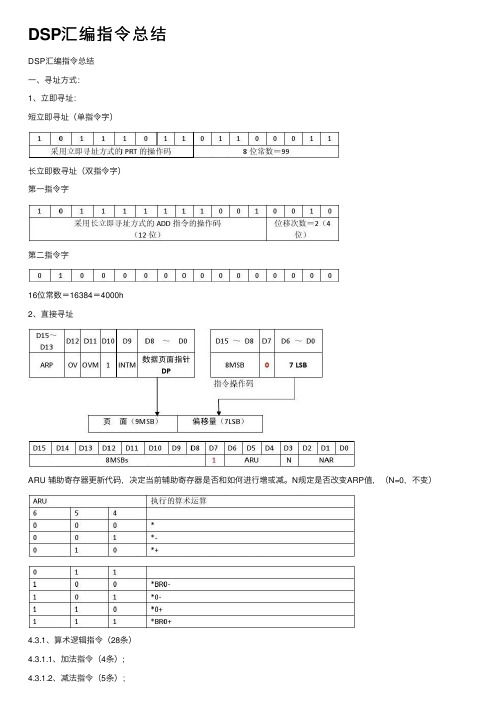

DSP汇编指令总结

DSP汇编指令总结DSP汇编指令总结⼀、寻址⽅式:1、⽴即寻址:短⽴即寻址(单指令字)长⽴即数寻址(双指令字)第⼀指令字第⼆指令字16位常数=16384=4000h2、直接寻址ARU 辅助寄存器更新代码,决定当前辅助寄存器是否和如何进⾏增或减。

N规定是否改变ARP值,(N=0,不变)4.3.1、算术逻辑指令(28条)4.3.1.1、加法指令(4条);4.3.1.2、减法指令(5条);4.3.1.3、乘法指令(2条);4.3.1.4、乘加与乘减指令(6条);4.3.1.5、其它算数指令(3条);4.3.1.6、移位和循环移位指令(4条);4.3.1.7、逻辑运算指令(4条);4.3.2、寄存器操作指令(35条)4.3.2.1、累加器操作指令(6条)4.3.2.2、临时寄存器指令(5条)4.3.2.3、乘积寄存器指令(6条)4.3.2.4、辅助寄存器指令(5条)4.3.2.5、状态寄存器指令(9条)4.3.2.6、堆栈操作指令(4条)4.3.3、存储器与I/O操作指令(8条)4.3.3.1、数据移动指令(4条)4.3.3.2、程序存储器读写指令(2条)4.3.3.3、I/O操作指令(2条)4.3.4、程序控制指令(15条)4.3.4.1、程序分⽀或调⽤指令(7条)4.3.4.2、中断指令(3条)4.3.4.3、返回指令(2条)4.3.4.4、其它控制指令(3条)4.3.1、算术逻辑指令(28条)4.3.1.1、加法指令(4条);▲ADD▲ADDC(带进位加法指令)▲ADDS(抑制符号扩展加法指令)▲ADDT(移位次数由TREG指定的加法指令)4.3.1.2、减法指令(5条);★SUB(带移位的减法指令)★SUBB(带借位的减法指令)★SUBC(条件减法指令)★SUBS(减法指令)★SUBT(带移位的减法指令,TREG决定移位次数)4.3.1.3、乘法指令(2条);★MPY(带符号乘法指令)★MPYU(⽆符号乘法指令)4.3.1.4、乘加与乘减指令(6条);★MAC(累加前次积并乘)(字数2,周期3)★MAC(累加前次积并乘)★MPYA(累加-乘指令)★MPYS(减-乘指令)★SQRA(累加平⽅值指令)★SQRS(累减并平⽅指令)4.3.1.5、其它算数指令(3条);★ABS(累加器取绝对值指令)★NEG(累加器取补码指令)★NORM(累加器规格化指令)返回4.3.1.6、移位和循环移位指令(4条);▲ SFL(累加器内容左移指令)▲ SFR(累加器内容右移指令)▲ROL(累加器内容循环左移指令)▲ROR(累加器内容循环右移指令)返回4.3.1.7、逻辑运算指令(4条);▲ AND(逻辑与指令)▲ OR(逻辑或指令)▲ XOR(逻辑异或指令)▲ CMPL(累加器取反指令)返回4.3.2、寄存器操作指令(35条)4.3.2.1、累加器操作指令(6条)▲ LACC(装载累加器指令)▲ LACT(装载累加器)*按TREG低4位指定的次数移位▲ LACL(装载累加器低16位指令)▲ ZALR(装载累加器指令)▲ SACL(移位并存储累加器低半部)▲ SACH(移位并存储累加器⾼半部)返回4.3.2.2、临时寄存器指令(5条)▲ LT(装载TREG指令)▲ LTA(装载TREG并累加上次乘积指令)▲ LTS (装载TREG并减去上次乘积指令)▲ LTD(装载TREG并累加上次乘积及数据移动指令)▲LTP(装载TREG和累加器指令)返回4.3.2.3、乘积寄存器指令(6条)▲ PAC (乘积寄存器内容载⼊累加器)▲ APAC (PREG与累加器相加)▲ SPAC(累加器和乘积寄存器相减)▲ LPH(装载PREG⾼16位指令)▲ SPL(存储PREG低16位指令)▲ SPH(存储PREG⾼16位指令)返回4.3.2.4、辅助寄存器指令(5条)★LAR(装载当前辅助寄存器AR)★SAR(存储辅助寄存器指令)★MAR(修改当前辅助寄存器)★SBRK(从当前辅助寄存器减去短⽴即数)返回4.3.2.5、状态寄存器指令(9条)★LST(装载状态寄存器)★SST(存储状态寄存器)★SETC(控制位置“1”指令)★SETC(控制位置“1”指令)★LDP(装载数据指针DP指令)★BIT(位测试指令)★BITT(测试由TREG指定bit code指令)★CMPR(⽐较当前辅助寄存器AR和AR0)返回4.3.2.6、堆栈操作指令(4条)★PUSH(累加器低16位进栈指令)★POP(栈顶内容弹出⾄累加器低16位指令)★POP(栈顶内容弹出⾄累加器低16位指令)★POPD(弹栈⾄数据存储器指令)返回4.3.3、存储器与I/O操作指令(8条)4.3.3.1、数据移动指令(4条)▲DMOV(数据存储器内部数据移动指令)▲SPLK(存储长⽴即数⾄数据存储器指令)▲BLDD(数据存储器内部的数据块移动)▲ BLPD(从程序存储器到数据存储器的数据块传送)4.3.3.2、程序存储器读写指令(2条)★TBLR(读程序存储器数据到数据存储器)★TBLW(写程序存储器)4.3.3.3、I/O操作指令(2条)★IN(数据输⼊指令)★OUT(数据输出指令)4.3.4、程序控制指令(15条)4.3.4.1、程序分⽀或调⽤指令(7条)★B(⽆条件转移指令)★BANZ(辅助寄存器内容不等于零转移)★CALL(⽆条件⼦程序调⽤指令)★BACC(按累加器内容转移指令)★CALA(由累加器指定地址的⼦程序调⽤指令)★CC(条件调⽤指令)4.3.4.2、中断指令(3条)★INTR(软中断指令)★TRAP(软件陷阱中断)★NMI(⾮屏蔽中断)4.3.4.3、返回指令(2条)★RET(⽆条件从⼦程序或中断返回)★RETC(条件返回指令)4.3.4.4、其它控制指令(3条)★RPT(重复执⾏下条指令)★NOP(空操作)★IDEL(暂停)返回。

DSP第五章 DSP的汇编指令

展和移位操作都以第31比特为准。

M40=1时,D单元按40位运算模式,因此累加器溢出,进位,符号扩

展和移位操作都以第39比特为准。

BCLR M40

; Clear M40

BSET M40

; Set M40

第五章 TMS320C55x系列DSP的汇编指令

2、累加器溢出状态(ACOVx)

当AC0~AC3寄存器溢出时,目的累加器的溢出状态位ACOV0~3被置1。 以下情况会清零ACOVx位

复位; CPU执行一个跳转,条件调用,条件返回或执行一条测试ACOVx的指令; 通过BCLR指令清除; 溢出位检测受ST1_55中的M40位影响,即:

第五章 TMS320C55x系列DSP的汇编指令

(3)内置并行指令与用户自定义并行指令的混合形式 在不引起资源冲突的情况下,将隐含并行的指令按用户自定义 方式与另一条指令并行执行。例:

MPY *AR0, *CDP, AC0 ;隐含的或内置的并行指令 :: MPY *AR1, *CDP, AC1 ||MOV #5, AR1

பைடு நூலகம்

在实际编程时,只要指令满足这三条基本规则,即可写成并行

方式,然后进行编译。如果编译有错,则可参照书上详细规则进 行检测。

第五章 TMS320C55x系列DSP的汇编指令 5.4 TMS320C55x DSP的汇编指令

TMS320C55x DSP的汇编指令按操作分为以下6类 算术运算指令 比特操作指令 一条指令的属性包括: 语法(Syntax) 执行的操作 操作数 相关的状态位 是否有并行使能位 长度(Size) 执行周期(Cycles) 在流水线(Pipeline)上的执行阶段 在哪个功能单元执行(Executed) 是否可以重复执行等

DSP缩略词总结

DSP缩略词总结一Signal Processing 信号处理classification 分类variable 变量vector 矢量scalar 标量multichannel 多通道multidimensional 多维的,多面的amplitude 幅度waveform 波形continuous-time 连续时间discrete-time 离散时间analog signal 模拟信号digital signal 数字信号normalize 使恢复正常deterministic signal 确定信号random signal 随机信号sample 抽样numerical 数字的quantized 量子化的(数字elementary 基本的implement 实现amplification 放大scaling 加权delay 延时addition 相加gain 增益attenuation 衰减advance 超前product 乘积integration 积分differentiation 微分filter 滤波器lowpass filter 低通滤波器highpass filter 高通滤波器bandpass filter 带通滤波器bandstop filter 带阻滤波器转化)time-domain 时域frequency-doblock 屏蔽passband 通带stopband 阻带quantized boxcar signal 量化阶梯信号main 频域inear 线性time-invariant 时不变cutoff-frequency 截止频率二algorithm 算法horizontal 水平面vertical 垂直面consecutive samples 相邻样本 sampling interval 抽样间隔sampling period 抽样周期sampling frequency 抽样频率real/complex sequence 实数/虚数序列conjugate 共轭analog-to-digital converter 模数转换器sample-and-hold circuit 采样保持电路equivalent 等效的infinite/finite 无限的/有限的finite/infinite-length 有限/无限长finite-extent 有限范围finite-duration 有限时宽causal/anticausal sequence 因果序列/非因果序列reversal 反转even/odd sequence 偶/奇序列conjugate-symmetric/ conjugate-antisymmetric 共轭对称/共轭非对称periodic/aperiodic 周期性的/非周期性的energy signal 能量信号power signal 功率信号average power 平均功率appending with zeros 补零bounded 有界的bounded-input,bounded-output 有界输入有界输出(BIBO)left-sided/right-sided/two-sided sequence 左边/右边/双边序列time-shifting operation 时移delaying operation 延时运算advancing operation 超前运算unit delay 单位延时time-reversal operation 时间反转运算unit sample sequence 单位抽样序列unit step sequence 单位阶跃序列exponential sequence 指数序列complex exponential sequence 复指数序列discrete-time impulse 离散时间冲激in-phase component 同相分量quadrature component 正交分量real sinusoidal sequence 实正弦序列sinusoidal envelope 正弦包络angular frequency 角频率decomposition 分解phase 相位radian 弧度exponential sequence 指数序列fundamental period 基本周期arbitrary sequence 任意序列Shift-Invariant System 时不变系统Impulse Response 冲激响应Step Response 阶跃响应Linear system 线性系统Stable system 稳定系统三Discrete-Time-Fourier Transform 离散时间傅里叶变换Fourier integral 傅里叶积分Finite discontinuities 有限个不连续点spectrum 谱magnitude/phase spectrum 幅度/相位谱 finite interval 有限区间absolutely integrable 绝对可积Energy Density Spectrum 能量密度谱Parseval’s relation 帕斯瓦尔定理Principal value 主值Frequency response 频率响应magnitude/phase response 幅度/相位响应gain/attenuation/loss function 增益/衰减/损耗函数 band-limited 带限 bandwidth 带宽 integer 整数periodic impulse train 周期脉冲序列 Frequency-Shifting 频移 Modulation 调制eigenfunctions 特征值 digital filer 数字滤波器四Digital Processing of Continuous-Time Signals 连续时间信号的数字化处理aliasing 混叠anti-aliasing 反混叠reconstruction 重建sampling process 抽样过程Mathematical representation 数学表示ideal sampling model 理想抽样模型folding frequency 折叠频率recovery 恢复oversampling 过抽样undersampling 欠抽样critical sampling 临界抽样aliasing distortion 混叠失真passband 通带stopband 阻带passband edge frequency 通带截止频率stopband edge frequency 阻带截止频率五Finite-Length Discrete Transforms 有限长离散变换Discrete Fourier transform 离散傅里叶变换Basis sequences 基本序列Inverse discrete Fourier transform 离散傅里叶逆变换frequency samples 频率样本circular Shift 圆周(循环)移位circular time-shifting operation 圆周时移运算circular frequency-shifting operation 圆周频移运算circular time-reversal operation 圆周时间反转运算modulo operation 模运算circular convolution 圆周(循环)卷积N-point circular convolution N点圆周(循环)卷积circulant matrix 圆周矩阵六z-Transform Z变换unit circle 单位圆region of convergence(ROC)收敛域Rational z-transform 有理z变换Polynomial 多项式zero point 零点pole point 极点Inverse z-Transform z反变换Partial-Fraction Expansion 部分分式展开法residue 留数transfer function 传输函数system function 系统函数circular convolution 圆周(循环)卷积N-point circular convolution N点圆周(循环)卷积 circulant matrix 圆周矩阵七z-Transform Z变换 unit circle 单位圆region of convergence(ROC)收敛域 Rational z-transform 有理z变换 Polynomial 多项式 zero point 零点 pole point 极点Inverse z-Transform z反变换 Partial-Fraction Expansion 部分分式展开法 residue 留数transfer function 传输函数 system function 系统函数八Digital Filter Structures 数字滤波器的结构IIR: Infinite Impulse Response 无限冲激响应FIR: Finite Impulse Response 有限冲激响应Block Diagram Representation 方框图表示Basic Building Blocks 基本结构单元Analysis of Block Diagrams 方框图的分析Delay-Free Loop 无延时回路Signal Flow-Graph 信号流图node 节点 branch 支路addition 加法器multiplication 乘法器(增益)unit delay 单位延时Equivalent Structures 等效结构transpose operation 转置运算direct form 直接型cascade realizations 级联型parallel realizations 并联型linear-phase FIR structures 线性相位FIR滤波器结构九IIR Digital Filter Design IIR数字滤波器设计Digital Filter Specifications 数字滤波器指标passband 通带stopband 阻带transition band 过渡带passband edge frequency 通带截止频率stopband edge frequency 阻带截止频率peak ripple values 峰波纹值peak passband ripple 峰值通带波纹minimum stopband attenuation 最小阻带衰减maximum passband attenuation 最大通带衰减selection of the Filter Type 滤波器类型的选择First-Order Butterworth lowpass filter 一阶巴特沃斯低通滤波器 magnitude-squared response 幅度平方函数Scaling the Digital Transfer Function 缩放数字传输函数Bilinear Transformation method 双线性变换法Frequency warping 频率畸变Spectral Transformation 谱变换十IIR Digital Filter Design IIR数字滤波器设计Digital Filter Specifications 数字滤波器指标passband 通带stopband 阻带transition band 过渡带passband edge frequency 通带截止频率stopband edge frequency 阻带截止频率peak ripple values 峰波纹值peak passband ripple 峰值通带波纹minimum stopband attenuation 最小阻带衰减maximum passband attenuation 最大通带衰减selection of the Filter Type 滤波器类型的选择First-Order Butterworth lowpass filter 一阶巴特沃斯低通滤波器 magnitude-squared response 幅度平方函数Scaling the Digital Transfer Function 缩放数字传输函数Bilinear Transformation method 双线性变换法Frequency warping 频率畸变Spectral Transformation 谱变换十一FIR Digital Filter Design FIR数字滤波器设计filter order 滤波器阶数window-based method 窗函数法lowpass filter 低通滤波器highpass filter 高通滤波器bandpass filter 带通滤波器bandstop filter 带阻滤波器differentiator 差分器Gibbs phenomenon 吉布斯效应rectangular window 矩形窗fixed window function 固定窗函数main lobe width 主瓣宽度relative sidelobe level 相对旁瓣级minimum-phase 最小相位十二DFT Algorithm Implementation DSP算法实现computation 计算fast Fourier transform(FFT) algorithms 快速傅里叶变换算法complex multiplications 复乘complex additions 复加Decimation-in-Time(DIT) FFT Algorithm 按时间抽取FFT算法butterfly computation 蝶形运算decomposition 分解in-place computation 同址计算(原位计算)twiddle factor 旋转因子bit-reversed order 倒位序Decimation-in-Frequency(DIF) FFT Algorithm 按频率抽取FFT算法Inverse DFT Computation 离散傅里叶逆变换计算。

DSP常用语言指令简介

2. 工作寄存器等指令举例

z Example1:MAR

*+,AR1;把当前工作寄 存器的内容加1,然后再改变工作寄存器为 AR1。 z Example2:LAR AR4,#8123h;把AR4的 值改变为立即数。 LAR AR0,16;(DP=6)把 地址=310H的内存单元内容装入AR0。 z Example3:SAR AR0,*+;(如果当前工 作寄存器=AR1)把AR0的内容拷贝到AR1 南航自动化学院DSP技术应用实验 指向的内存单元。 室

南航自动化学院DSP技术应用实验 室

z Example1:BCND

xxx, LEQ, C ;如果累加 器<=0并且进位C=1,那么程序就跳转到标 号xxx处执行;否则,程序顺序执行。根据 累加器ACC的内容产生的转移条件如下表格 所示。类似的指令还有:CC xxx。 z Example2:BANZ。第七页举例。

南航自动化学院DSP技术应用实验 室

1. 累加器等指令举例

z Example

1:ADD 1,1;(假设DP = 6),把 第6个数据页的第一个内存单元内容左移一 位加到累加器 z Example 2:LACC *,4; (与SXM有关) z Example 3:ROL;把累加器内容循环左移 z Example 4:SACL *,0,AR7 ;把当前工作寄 存器指示内容左移0位送入累加器的低8位 z Example 5:RPT #15 SUBC * ;累加器减去当前寄存 器指的内容,连续减16次,结果存累加器

南航自动化学院DSP技术应用实验 室

1. 累加器等指令举例

Example 6: AND 16 ;(假设DP = 4),把地址 =210H的内存单元内容和ACC相逻辑“与”,结果存 入累加器。 z Example 7:SFL ;把整个的ACC内容左移一位,低 位填0,最高位送入进位位,不受SXM影响。 z Example 8:SFR ;把整个的ACC内容右移一位,高 位根据SXM进行符号位扩展。例如: 1.执行前ACC=B0001234h,SXM=0,执行后ACC= 5800091Ah; 2.执行前ACC=B0001234h,SXM=0,执行后ACC =5800091Ah;

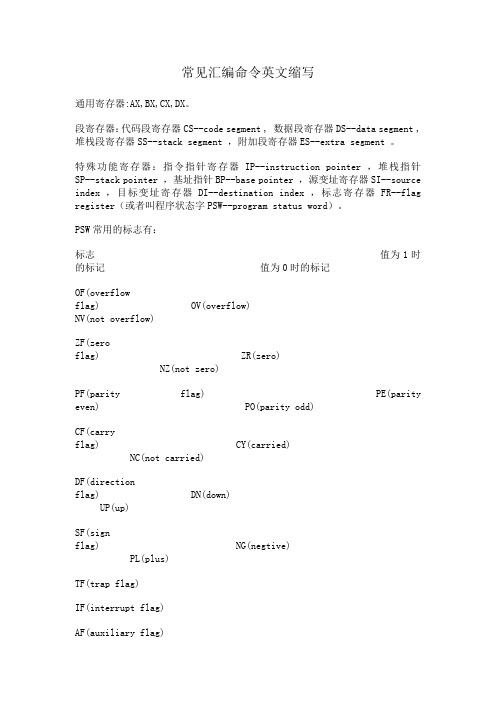

常见汇编命令英文缩写

常见汇编命令英文缩写通用寄存器:AX,BX,CX,DX。

段寄存器:代码段寄存器CS--code segment , 数据段寄存器DS--data segment , 堆栈段寄存器SS--stack segment ,附加段寄存器ES--extra segment 。

特殊功能寄存器:指令指针寄存器IP--instruction pointer ,堆栈指针SP--stack pointer ,基址指针BP--base pointer ,源变址寄存器SI--source index ,目标变址寄存器DI--destination index ,标志寄存器FR--flag register(或者叫程序状态字PSW--program status word)。

PSW常用的标志有:标志值为1时的标记值为0时的标记OF(overflow flag) OV(overflow) NV(not overflow)ZF(zero flag) ZR(zero) NZ(not zero)PF(parity flag) PE(parity even) PO(parity odd)CF(carry flag) CY(carried) NC(not carried)DF(direction flag) DN(down) UP(up)SF(sign flag) NG(negtive) PL(plus)TF(trap flag)IF(interrupt flag)AF(auxiliary flag)1.通用数据传送指令.MOV----> moveMOVSX---->extended move with sign dataMOVZX---->extended move with zero dataPUSH---->pushPOP---->popPUSHA---->push allPOPA---->pop allPUSHAD---->push all dataPOPAD---->pop all dataBSWAP---->byte swapXCHG---->exchangeCMPXCHG---->compare and changeXADD---->exchange and addXLAT---->translate2.输入输出端口传送指令.IN---->inputOUT---->output3.目的地址传送指令.LEA---->load effective addressLDS---->load DSLES---->load ESLFS---->load FSLGS---->load GSLSS---->load SS4.标志传送指令.LAHF---->load AH from flagSAHF---->save AH to flagPUSHF---->push flagPOPF---->pop flagPUSHD---->push dflagPOPD---->pop dflag二、算术运算指令ADD---->addADC---->add with carryINC---->increase 1AAA---->ascii add with adjustDAA---->decimal add with adjustSUB---->substractSBB---->substract with borrowDEC---->decrease 1NEC---->negativeCMP---->compareAAS---->ascii adjust on substractDAS---->decimal adjust on substract MUL---->multiplicationIMUL---->integer multiplicationAAM---->ascii adjust on multiplication DIV---->divideIDIV---->integer divideAAD---->ascii adjust on divideCBW---->change byte to wordCWD---->change word to double wordCWDE---->change word to double word with sign to EAXCDQ---->change double word to quadrate word三、逻辑运算指令———————————————————————————————————————AND---->andOR---->orXOR---->xorNOT---->notTEST---->testSHL---->shift leftSAL---->arithmatic shift leftSHR---->shift rightSAR---->arithmatic shift rightROL---->rotate leftROR---->rotate rightRCL---->rotate left with carryRCR---->rotate right with carry四、串指令———————————————————————————————————————MOVS---->move stringCMPS---->compare stringSCAS---->scan stringLODS---->load stringSTOS---->store stringREP---->repeatREPE---->repeat when equalREPZ---->repeat when zero flagREPNE---->repeat when not equalREPNZ---->repeat when zero flagREPC---->repeat when carry flagREPNC---->repeat when not carry flag五、程序转移指令———————————————————————————————————————1>无条件转移指令(长转移)JMP---->jumpCALL---->callRET---->returnRETF---->return far2>条件转移指令(短转移,-128到+127的距离内) JAE---->jump when above or equalJNB---->jump when not belowJB---->jump when belowJNAE---->jump when not above or equalJBE---->jump when below or equalJNA---->jump when not aboveJG---->jump when greaterJNLE---->jump when not less or equalJGE---->jump when greater or equalJNL---->jump when not lessJL---->jump when lessJNGE---->jump when not greater or equal JLE---->jump when less or equalJNG---->jump when not greaterJE---->jump when equalJZ---->jump when has zero flagJNE---->jump when not equalJNZ---->jump when not has zero flagJC---->jump when has carry flagJNC---->jump when not has carry flagJNO---->jump when not has overflow flag JNP---->jump when not has parity flagJPO---->jump when parity flag is oddJNS---->jump when not has sign flagJO---->jump when has overflow flagJP---->jump when has parity flagJPE---->jump when parity flag is evenJS---->jump when has sign flag3>循环控制指令(短转移)LOOP---->loopLOOPE---->loop equalLOOPZ---->loop zeroLOOPNE---->loop not equalLOOPNZ---->loop not zeroJCXZ---->jump when CX is zeroJECXZ---->jump when ECX is zero4>中断指令INT---->interruptINTO---->overflow interruptIRET---->interrupt return5>处理器控制指令HLT---->haltWAIT---->waitESC---->escapeLOCK---->lockNOP---->no operationSTC---->set carryCLC---->clear carryCMC---->carry make changeSTD---->set directionCLD---->clear directionSTI---->set interruptCLI---->clear interrupt六、伪指令—————————————————————————————————————DW---->definw wordPROC---->procedureENDP---->end of procedureSEGMENT---->segmentASSUME---->assumeENDS---->end segmentEND---->end。

dsp英文缩写含义

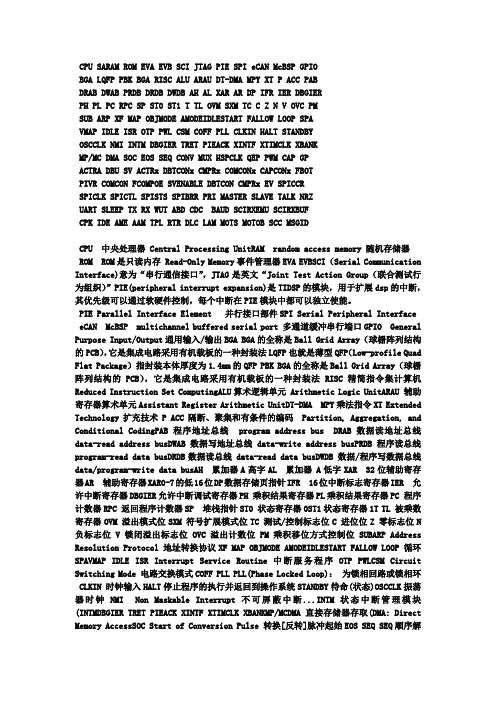

CPU SARAM ROM EVA EVB SCI JTAG PIE SPI eCAN McBSP GPIOBGA LQFP PBK BGA RISC ALU ARAU DT-DMA MPY XT P ACC PABDRAB DWAB PRDB DRDB DWDB AH AL XAR AR DP IFR IER DBGIERPH PL PC RPC SP ST0 ST1 T TL OVM SXM TC C Z N V OVC PMSUB ARP XF MAP OBJMODE AMODEIDLESTART FALLOW LOOP SPAVMAP IDLE ISR OTP PWL CSM COFF PLL CLKIN HALT STANDBYOSCCLK NMI INTM DBGIER TRET PIEACK XINTF XTIMCLK XBANKMP/MC DMA SOC EOS SEQ CONV MUX HSPCLK QEP PWM CAP GPACTRA DBU SV ACTRx DBTCONx CMPRx COMCONx CAPCONx FBOTPIVR COMCON FCOMPOE SVENABLE DBTCON CMPRx EV SPICCRSPICLK SPICTL SPISTS SPIBRR PRI MASTER SLAVE TALK NRZUART SLEEP TX RX WUT ABD CDC BAUD SCIRXEMU SCIRXBUFCPK IDE AME AAM TPL RTR DLC LAM MOTS MOTOB SCC MSGIDCPU 中央处理器 Central Processing UnitRAM random access memory 随机存储器ROM ROM是只读内存 Read-Only Memory事件管理器EVA EVBSCI(Serial Communication Interface)意为“串行通信接口”,JTAG是英文“Joint Test Action Group(联合测试行为组织)”PIE(peripheral interrupt expansion)是TIDSP的模块,用于扩展dsp的中断,其优先级可以通过软硬件控制,每个中断在PIE模块中都可以独立使能。

DSP缩略词

SUB subtract from accumulator 带累加器减法SBUC conditional subtract from accumulator 有条件带累加器减法SUBS subtract from accumulator with sign extension suppressed 抑制符号带累加器减法SUBT subtract from accumulator with shift specified by TREG 从累加器减去指定的寄存器内容XOR exclusive or with accumulator 特殊与或累加器ZALR zero low accumulator and load high accumulator with rounding 低位取零高位取整BANZ branch on AR not zero 不分配AR 0CMPR compare AR with AR0 比较AR和AR0LAR load AR 加载ARMAR modify AR 修改ARSTR store AR 存储到ARSBRK subtract short limmediate 减去短的立即数APAC add PREG to accumulator 把PREG加到累加器LPH load PREG 加载PREGLT load TREG 加载TREGLTA load TREG and ACC previous product 加载TREG和ACC之前的输出LTD load TREG ACC previous product and move date 加载TREG ACC之前的输出和移动日期LTS load TREG and subtract previous product 加载TREG和减去以前的输出MAC multiply and accumulate 乘法和积累MACD multiply and accumulate wit data move 带数据移动的乘加运算MPY A multiply and accumulate previous product 乘加之前的输出MPYS multiply and subtract previous product 乘减之前的输出TI Texas Instrumens 美国德州仪器公司ASIC Application Specific Intergrated Circuit 专用集成电路BS Barrel Shifter 桶形移位寄存器AU Addressing Unit 寻址单元PAGEN Program Address Generation Logic 逻辑发生程序地址DAGEN Data Address Generation Logic 数据地址产生单元PLL Phase Locked Loops 锁相环电路IFR Interrupt Flag Register 中断标志寄存器IMR Interrrupt Mask Register 中断屏蔽寄存器TIM Timer Register 定时器寄存器PRD Timer Period Register 定时器周期寄存器TCR Timer Control Register 定时器控制寄存器TDDR Timer Divide Down Ration 定时器分频系数TSS Timer Stop Status 定时器停止状态位TRB Timer Reload 定时器重新加载位PSC Timer Prescaler Counter 定时器预定标计数器HPI Host Port Interface 主机接口SPI Serial Port Interface 标准同步串行BSP Buffered Serial Port 缓冲串行口TDM Time Division Multiplexed 时分多路复用串行接口IDE Intergrated Development Environment 集成开发环境ABS Absolute value of Accumulator累加器绝对值ADD add to accumulator累加器值相加ADDC add toaccumulator with carry带进位加法运算ADDT add to accumulator with shift specified byAND and with accumulatorLACC load accumulator with shift加载移位累加器LACL load low accumulator and clear high accumulator加载到累加器低位字和清除累加器高位字LACT load accumulator with shift specified by TREG通过TREG特殊移位加载到累加器NEG negate accumulator否定累加器NORM normalize contents of accumulator正规化累加器ROL/RORrotate accumulator left/right左/右旋转累加器SACH/SACL store high/low accumulator with shift高/低位存储移位累加器SFL/SFR shift accumulator left/right左/右移位累加器PAC load accumulator with PREGSPAC subtract PREG from accumulatorSPH/SPL store high/low PREGSPM set PREG output shift modeSQRA/SQRS square value and accumulate/subtract previous productB branch unconditionallyBACC branch to location specified by ACCBANZ branch on AR not zeroBCND branch conditionallyCALA call subroutione at location specified by ACCCALL call unconditionallyCC call conditionallyINTR software interruptNMI nonmaskable interruptRET return from subroutineRETC return conditionallyTRAP software interruptBIT bit numberBITT test bit specified by TREGCLRC clear control bitIDEL idle until interruptLDP load data page pointerLST load status registerNOP no operationPOP pop top of stack to low ACCPOPD pop top of stack to data memoryPSHD push data-memory value onto stackPUSH push low ACC onto stackRPT repeat next instructionSETC set control bitSPM set PREG output shift modeSST store status registerBLDD block move from data memory to data memoryBLPD block move from data memory to data memoryDMOV data move in data memoryIN input data from portOUT output data to portSPLK store long immediate value to data memoryTBLR table readTBLW table writeMELP Mixed Excitation LPC V ocoder 混合激励线性预测编码器FBTC Flashburn Target Component 下载用具CCS Code Composer Studio TI公司的DSP软件编译环境DSP Digital Siginal Processor数字信号处理器LPC Linear Predictive Coding线性预测编码GEL General Eextension Language 类似于C语言的解释性语言RF3 Reference Frmework level 3应用程序使用多通道和多算法API Application Program Interface应用程序编程接口EMIF External Memory Interface外部存储器界面RAMrandom access memory随机存储器SDRAM Synchronous Dynamic Random Access Memory同步动态随机存储器biasing error 偏移误差rounding error 舍入误差matrix form 矩阵形式twiddle factor 旋转因子modulo-N 模Nperiodic extention 周期延拓computational cost 计算代价unitary matrix 酉阵merging 组合FFT (fast Fourier transform )快速傅立叶变换Decimation-in-time radix-2 FFT algorithm 按时间抽取的基二FFT算法butterfly merging equations蝶形组合公式shuffling 重排bit reversal 码位倒置fast convolution 快速卷积circular convolution 圆周卷积overlap-add methord 重叠相加法overlap-save methord 重叠保留法IDFT (inverse discrete Fourier transform ) 序列傅氏反变换IFFT (inverse fast Fourier transform)快速傅立叶反变换window method 窗口法linear phase 线性相位guarantee sability 保证稳定性lowpass 低通highpass 高通bandpass 带通bandstop 带阻transition band 过渡带passband 通带stopband 阻带differentiator 微分器Hilbert transformer 希尔伯特变换器double-sided 双边real 实部imaginary 虚部even 偶odd 奇truncate 截断cutoff frequency 截止频率transition band width 过渡带宽ripples 纹波symmetric 对称antisymmetric 反对称Bilinear transformation 双线性变换prewarping 预畸mapping 映射nonlinear 非线性first-order lowpass/highpass filter一阶低通/高通滤波器high-order filter 高阶滤波器second-order notching filter二阶陷波滤波器N-order Butterworth lowpass AFN阶巴特沃斯模拟低通滤波器magnitude response 幅度响应prototype 原型ALU Arithmetic-Logic Unit算术逻辑单元ARP Address Resolution Protocol 辅助寄存器指针ROM Read-Only Memory只读存储器PCB Printed circuit board 电路板HPI Hardware Platform Interface 主机接口。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ABS Absolute value of Accumulator

ADD add to accumulator

ADDC add to accumulator with carry

ADDT add to accumulator with shift specified by TREG

AND and with accumulator

CMPL complement accumulator

LACC load accumulator with shift

LACL load low accumulator and clear high accumulator

LACT load accumulator with shift specified by TREG

NEG negate accumulator

NORM normalize contents of accumulator

OR or with accumulator

ROL/ROR rotate accumulator left/right

SACH/SACL store high/low accumulator with shift

SFL/SFR shift accumulator left/right

SUB subtract from accumulator

SBUC conditional subtract

SUBS subtract from accumulator with sign extension suppressed SUBT subtract from accumulator with shift specified by TREG

XOR exclusive or with accumulator

ZALR zero low accumulator and load high accumulator with rounding ADRK add short limmediate value to AR

BANZ branch on AR not zero

CMPR compare AR with AR0

LAR load AR

MAR modify AR

STR store AR

SBRK subtract short limmediate

APAC add PREG to accumulator

LPH load PREG

LT load TREG

LTA load TREG and ACC previous product

LTD load TREG ACC previous product and move date

LTS load TREG and subtract previous product

MAC multiply and accumulate

MACD multiply and accumulate wit data move

MPY multiply

MPY A multiply and accumulate previous product

MPYS multiply and subtract previous product

MPYS multiply unsign

PAC load accumulator with PREG

SPAC subtract PREG from accumulator

SPH/SPL store high/low PREG

SPM set PREG output shift mode

SQRA/SQRS square value and accumulate/subtract previous product B branch unconditionally

BACC branch to location specified by ACC

BANZ branch on AR not zero

BCND branch conditionally

CALA call subroutione at location specified by ACC

CALL call unconditionally

CC call conditionally

INTR software interrupt

NMI nonmaskable interrupt

RET return from subroutine

RETC return conditionally

TRAP software interrupt

BIT bit number

BITT test bit specified by TREG

CLRC clear control bit

IDEL idle until interrupt

LDP load data page pointer

LST load status register

NOP no operation

POP pop top of stack to low ACC

POPD pop top of stack to data memory

PSHD push data-memory value onto stack

PUSH push low ACC onto stack

RPT repeat next instruction

SETC set control bit

SPM set PREG output shift mode

SST store status register

BLDD block move from data memory to data memory

BLPD block move from data memory to data memory

DMOV data move in data memory

IN input data from port

OUT output data to port

SPLK store long immediate value to data memory

TBLR table read

TBLW table write。