定点dsp与浮点dsp的比较

DSP面试常见问题

DSP常见问题1.DSP与普通的微处理器的不同?单周期指令:大多数DSP都拥有流水结构,即每条指令都由片内多个功能单元分别完成取指、译码、取数、执行等步骤,这样可以大大提高系统的执行效率。

它可以在一个时钟周期内执行一条语句。

快速乘法器:信号处理算法往往大量用到乘加(multiply-accumulate,MAC)运算。

DSP有专用的硬件乘法器,它可以在一个时钟周期内完成MAC运算。

硬件乘法器占用了DSP芯片面积的很大一部分。

(与之相反,通用微处理器采用一种较慢的、迭代的乘法技术,它可以在多个时钟周期内完成一次乘法运算,但是占用了较少了硅片资源)。

多总线:DSP有分开的代码和数据总线(一般用术语“哈佛结构”表示),这样在同一个时钟周期内可以进行多次存储器访问——这是因为数据总线也往往有好几组。

有了这种体系结构,DSP就可以在单个时钟周期内取出一条指令和一个或者两个(或者更多)的操作数。

地址发生器:DSP有专用的硬件地址发生单元,这样它可以支持许多信号处理算法所要求的特定数据地址模式。

这包括前(后)增(减)、环状数据缓冲的模地址以及FFT 的比特倒置地址。

地址发生器单元与主ALU和乘法器并行工作,这就进一步增加了DSP 可以在一个时钟周期内可以完成的工作量。

硬件辅助循环:信号处理算法常常需要执行紧密的指令循环。

对硬件辅助循环的支持,可以让DSP高效的循环执行代码块而无需让流水线停转或者让软件来测试循环终止条件。

数据格式:除了标准的整数型格式外,DSP一般支持定点和(或)浮点数。

对数据格式和精度的选择取决于应用程序所需,例如:16位定点DSP可以满足语音信号处理和控制所需24位和32位定点DSP可以满足高质量音频信号处理所需32位浮点DSP可以满足图形和图像处理所需1:DSP采用改进的Harvard结构,程序与数据存储空间分开,各有独立的地址总线和数据总线,取指和读数可以同时进行,而单片机多数采用的是冯•罗依曼结构,所有的操作都必须经过累加器A,很容易造成瓶颈效应。

DSP技术总结

DSP技术知识要点(电信)CHAP11、冯、诺依曼结构和哈佛结构的特点冯、诺依曼结构:该结构采用单存储空间,即程序指令和数据共用一个存储空间,使用单一的地址和数据总线,取指令和取操作数都是通过一条总线分时进行。

当进行高速运算时,不但不能同时进行取指令和取操作数,而且还会造成数据传输通道的瓶颈现象,其工作速度较慢。

哈佛结构:该结构采用双存储空间,程序存储器和数据存储器分开,有各自独立的程序总线和数据总线,可独立编址和独立访问,可对程序和数据进行独立传输,使取指令操作、指令执行操作、数据吞吐并行完成,大大地提高了数据处理能力和指令的执行速度,非常适合于实时的数字信号处理。

2、DSP芯片的特点(为何适合数据密集型应用)采用哈佛结构;采用多总线结构;采用流水线技术;配有专用的硬件乘法-累加器;快速的指令周期3、定点DSP芯片和浮点DSP芯片的区别及应用特点若数据以定点格式工作的——定点DSP芯片。

若数据以浮点格式工作的——浮点DSP芯片。

浮点DSP芯片,精度高、动态范围大,产品相对较少,复杂成本高。

但不必考虑溢出的问题。

用在精度要求较高的场合。

4、定点DSP的表示(Qm.n,精度和范围与m、n的关系)及其格式转换(1)数的总字长:m+n+11位符号位:最高位是符号位,0代表正数,1代表负数m表示数的2的补码的整数部分的位数n表示数的2的补码的小数部分的位数正数:补码=原码负数:补码=原码取反+1(2)m越小,n就越大,则数值范围越小,但精度越高;m越大,n就越小,则数值范围越大,但精度越低。

(3)十进制转换成Qm.n形式:先将数乘以2^n 变成整数,再将整数转换成相应的Qm.n形式不同Qm.n形式之间的转换:不同Qm.n形式的数进行加减运算时,通常将动态范围小的数据格式转换成动态范围大的数据格式。

即n大的数据格式向n小的数据格式转换。

方法:将n 大的数向右移相差的位数,这时原数低位被移出,高位则进行符号扩展。

定点。浮点dsp区别(Fixed...

定点。

浮点dsp区别(Fixed point. Difference between floatingpoint DSP)Since the introduction of floating point digital signal processor (DSP) more than 10 years ago, it has provided more advanced arithmetic options for real-time signal processing. However, fixed-point devices are still the pillar of the industry, of course, low cost is the main reason. Fixed point DSP has lower price per device, which is an important advantage for mass market applications.In comparison, floating point DSP can achieve more rapid and simple development, so it is the best choice for small scale applications which are more important than unit manufacturing cost.In recent years, high-density integration and support improvement have made the two kinds of DSP more convenient in use and cost. At present, the choice of device type is more and more decided by whether the application data set requires more calculation function of floating point format. As a result, developers who design mass production signal processing applications are beginning to discover more intrinsic value of floating-point formats. They focus on the areas outside the traditional fixed-point DSP development model, and explore the design opportunities brought by floating point DSP.Different digital formatsThe basic difference between fixed point and floating point DSP is that they differ in number representation of data. Fixedpoint hardware performs integer operations strictly, while floating-point DSP supports both integer operation and real number operation, and the latter is standardized by scientific counting method. The fixed-point DSP with 16 bit word length achieves (rovide) 64K precision with a signed integer range of -215 to 215-1.In contrast, floating-point DSP divides the data path into two parts: one can be used as integer value or the mantissa of real number base, and two is index. In the 32 bit floating-point DSP, which supports the single precision operation of the industry standard, the mantissa is 24 bits, and the index is 8 bits. Because of its longer length and exponentiation range, precision range of the device supports 16M, dynamic range that is much higher than the fixed point format can provide accuracy. The implementation of the industry standard double precision (64 bit, including a 53 bit mantissa and 11 bit index) device can achieve higher accuracy.Cost and ease of useFloating point DSP provides higher computing power, which is the biggest difference from its fixed point DSP function. But in the early 1990s, when floating point DSP was emerging, other factors often masked basic mathematical calculations. The floating point function requires more internal circuitry, and the 32 bit data path is twice as wide as the fixed point device available at that time. The chip area is greater, the more the number of pins, the package is larger, it will greatly improve the cost of the new floating point devices, so the digital voice and Telecommunications integrated card (concentration card)and other high yield applications still tend to use fixed-point devices with lower cost.At that time, ease of use offset the adverse effects of cost issues. Floating point devices are one of the earliest DSP supported C languages, while fixed point DSP still need to be programmed at the assembly code level. In addition, the floating point format, the real operations can be added directly through the hardware operation code, and fixed devices must be implemented indirectly through software to real operations, which increases the algorithm instruction and extend the development time. The floating point DSP is easy to be programmed, so its development was mainly used in the strength of a larger work, such as military system research and prototype development, image recognition, 3D image workstation accelerator and radar etc..Convergence graduallyAt present, the difference between cost and usability has been less obvious. In general, fixed point DSP still has a cost advantage, and floating point DSP still has advantages in ease of use, but the difference has narrowed a lot, so the above factors have no longer decided.Cost is increasingly becoming a problem of SOC integration and production, rather than the size of the DSP kernel itself. Ten years ago, only a single transistor space could be placed, and dozens of transistors could now be placed. At present,Most of the memory footprint is memory, not logic, and many DSPbased products make full use of the advantages of rescaling, which integrates more than one kernel for specific market requirements. Fixed DSP cost is still low, because of the mass market for application of high yield; however, if the mass production demand, so floating point devices will also benefit from the scale of benefits also reduce the cost of.Early differences in ease of use have also diminished. Efficient C compilers and tools have long been able to support fixed point DSP, bringing visibility to code execution. It is still advantageous to implement real number arithmetic directly using floating point hardware, but the advanced modeling tools, complete mathematical function library and off the shelf algorithm reduce the difficulty of developing complex applications for fixed point devices.Precision of floating pointAt present, the choice of fixed point DSP or floating point DSP is in the end whether the application data set needs floating-point arithmetic function. Overall, designers should address two questions: how high is the accuracy of the data set? What is the predictability of the data set?Three factors affect the intrinsic precision of floating point formats. First of all, the 24 bit I/O word length of floating-point DSP can achieve higher accuracy than integers in the 16 bit word length commonly used in fixed-point devices in integer and real numbers. Second, a substantial increase in the scope of application of dynamic power available, a large dynamic range of data sets and is expected to greatly facilitatethe scope of a data set is quite important. Third, the data representation in the floating-point hardware is more accurate than the fixed-point device, which ensures the accuracy of the final result is higher.The last point should be explained slightly. In the internal architecture of DSP, three data word lengths are very important and should be considered. The first is the word length of the I/O signal, which, as we've already said, is 24 bits for floating point, and usually 16 for fixed point DSP. Second is the coefficient word length for multiplication. Thefixed-point coefficient is 16 bits, the same as the signal data, but the floating point coefficient may be 24 bits or 53 bits, depending on whether the single width precision is used or the double width precision. If the index represents a meaningful zero, the accuracy will actually exceed the number above.Finally, the word length of the intermediate result of the iterative multiplication (MAC) operation is preserved, which is usually referred to as the register file. For a single 16 bit multiplied by 16 bit multiplication, it will require 32 bit multiplication; and for a single 24 bit multiplied by 24 bit mantissa multiplication, the product of 48 bits (the index has different data paths) is needed. However, iterative MAC requires additional bits for overflow headroom. In a 16 bit fixed point device, the overflow space is usually 8 bits, which makes the total intermediate result word length 40 bits (16 signals +16 coefficients +8 overflow).Integrating the same size of overflow space into floating point DSP requires 60 intermediate results bits (24 signals +24coefficients +12 overflow), which will exceed the accuracy requirements of most applications. But we will power, the standard, so that all 24 or 53 bits are valid, overflow is not necessary. TI's TMS320C67x series floating point DSP allows developers to optimize accuracy and performance in a dual precision, internal, and single precision I/O mode. As a result, the accuracy is much higher than that of fixed-point or single precision floating-point operations, but it does not produce periodic problems caused by fully double precision I/O.Video and audio data set requirementsComparing the requirements of video and audio applications, it is easy to see the advantages of using floating point formats. Video sampling rate is very high, and its pixel data sampling rate is equivalent to tens or even hundreds of megabits per second (Mbps), the specific value is applied. Pixel data is usually represented by short words from 8 to 12 bits,The red, green, and blue (RGB) planes of each image representing the image. The key mathematical operations of the industry standard MPEG video compression algorithms include discrete cosine transform (DCT) and quantization, and the filtering is limited. DCT and quantified by using integer arithmetic can effectively deal with it, and short data word combination makes the video applications become fixed-point DSP naturally, especially for those who have a large number of parallel data path design and on-chip video interface is more so.On the other hand, the data stream of audio is more limited, and the speed of 24 bit sampling and 48 thousand sampling (ksps)per second is about 1Mbps speed. The emerging sampling rate is 192 ksps, which is four times of the data rate, but the data stream is still much lower than the video stream. But audio data processing must be much more accurate than video. Eyes are easily deceived, especially when images are moving, but ears are hard to deceive. Therefore, audio requires larger word lengths provided by floating point hardware.Full 24 bit floating point I/O accuracy is used to perform sound sampling, which gives a dynamic range of 144 dB, which is far beyond the full amplitude range required for sound reproduction. In addition, the width of the audio and the accuracy of the intermediate results provide the reason for two. First of all, audio applications usually use a series of infinite impulse response filters (IIR) to achieve minimum delay and maximum performance. But each level of the serial filter will spread the error of the upper level. The longer the signal and the length of the system, the higher the accuracy, the less the impact of the propagation error.Second, the signal accuracy must be maintained at near zero to avoid harmonic distortion that can be distinguished by human ears. The floating point scheme essentially matches the sensitivity of the human ear because it becomes more accurate when the fraction approaches zero. On the contrary, the fixed point system takes approximate value equal to zero in the case of fractional minimum, which reduces the accuracy. All of the above floating point real number algorithms are crucial for true replication of audio signals.Despite the fact that fixed point devices have been used toimplement high fidelity audio in the past, they have now switched to higher precision floating point formats. Some floating point DSP integrated multi-channel audio serial port (McASP), which simplifies the design of audio system, which provides support for the above development trends. With the increasing popularity of the latest audio innovations in consumer electronics, the demand for floating point DSP will also rise, which helps to make the cost closer to fixed point DSP.Decision data setData sets of other types of applications can also benefit from floating-point accuracy. In the medical image recognition, signal input and higher accuracy can support many levels, including light, X rays, ultrasonic and other sources of input, all of them must be defined and processing, the output image to provide useful diagnostic information to generate the. Dynamic range is very important for radar, in this case, the system should be able to track in the range from zero to infinity, and only a small subset of the whole range for target acquisition and identification. Larger dynamic range also helps the robot deal with unforeseen situations, such as obstacles encountered in the normal range of motion of the robot. In contrast to the above applications, the fixed-point devices to provide better communication services market is huge, because most of the communication data are based on a eight byte serial transmission, followed by internal expansion of 16 bit processing based on integer arithmetic.In recent years, with the continuous development of digitalsignal processing field, DSP has also been promoted by applications. SOC integration means that more memory and different cores can be integrated into the same device with dedicated peripherals, which makes DSP products customized according to specific market requirements. In this environment, floating point functionality has become another element in the overall DSP product mix.There are still some differences between cost and usability in fixed point DSP and floating point DSP,But with the passage of time, the above differences are not big. The most important feature of the designer is that the floating-point format has higher arithmetic flexibility and accuracy. Floating point DSP is the best solution for high fidelity audio and other data sets that require real number operations, higher accuracy, and larger dynamic range.。

IQmath的应用

IQmath库的定点DSP算法设计引言DSP数字信号处理器DSP数字信号处理器是一个实时处理信号的微处理器,分为定点和浮点两种基本类型,它们之间最大差异在于浮点DSP比定点DSP具有更强大的计算能力和更大范围的动态精度。

浮点DSP内部设有专门支持浮点运算的硬件单元,对浮点格式的数据可以直接通过代码加入硬件运算中,因此运算速度很高。

而定点DSP没有定点运算单元,它对浮点格式的实数必须通过软件才能实现,这样就增加了指令代码,间接地使得定点DSP运算速度低于浮点DSP,典型的浮点处理器,如TI公司的C6000系列,几乎所有的嵌入式微控制器都为定点处理器,如TI公司的C2000系列。

因为浮点DSP的价格更加昂贵,因此定点DSP仍然有其巨大的优势。

但是任何算法都需要进行浮点运算,因此如何提高在定点DSP 上进行的浮点运算的速度和精度,就成为了用户开发时必须要考虑的关键问题。

TI公司专门为定点处理器TMS320C2000系列提供的IQmath库为解决上述问题提供了良好的实现方法。

数字信号处理(Digital Signal Processing,简称DSP)是一门涉及许多学科而又广泛应用于许多领域的新兴学科。

20世纪60年代以来,随着计算机和信息技术的飞速发展,数字信号处理技术应运而生并得到迅速的发展。

在过去的二十多年时间里,数字信号处理已经在通信等领域得到极为广泛的应用。

数字信号处理是利用计算机或专用处理设备,以数字形式对信号进行采集、变换、滤波、估值、增强、压缩、识别等处理,以得到符合人们需要的信号形式。

1 数的定标:Q格式有符号数的表示法,机器数(出现在电脑的二进位数值)有3个特点,无符号或符号转换成数值来表示,没有+10101这样的资料,而是以010101来表示,只表示单纯的整数或小数,小数点的位置预设在一定的位置而较少变动,它的长度受到电脑硬体的限制,而不能无限增长。

Q格式,就是将一个小数放大若干倍后,用整数来表示小数定点DSP不能直接处理小数,编程时处理小数有3种方法:①把变量定义成float类型。

DSP定点与浮点的区别

DSP定点与浮点的区别可能对于入门级的dsp开发者有所帮助。

本文关注定点dsp与浮点dsp的对比,主要从三个方面来分析。

感谢我所引用的资料的作者。

一般来说,定点dsp处理器具有速度快,功耗低,价格便宜的特点;而浮点dsp处理器则计算精确,动态范围大,速度快,易于编程,功耗大,价格高。

1、宏观上的区别从宏观上讲,浮点dsp比定点dsp的动态范围大得多。

定点运算中,程序员必须时刻关注溢出的发生,为了防止溢出,要么不断进行移位定标,要么做截尾。

前者耗费大量时间和空间,后者则带来精度的损失。

相反,浮点运算dsp扩大了动态范围,提高了精度,节省了运算时间和存储空间,因为大大减少了定标,移位和溢出检查。

举个例子(来自/s/blog_518dfe5b0100e17w.html)定点的计算不过是把一个数据当作整数来处理,通常AD采样来的都是整数,这个数相对于真实的模拟信号有一个刻度因子,大家都知道用一个16位的AD去采样一个0到5V的信号,那么AD输出的整数除以2^16再乘以5V就是对应的电压。

在定点DSP中是直接对这个16位的采样进行处理,并不将它转换成以小数表示的电压,因为定点DSP无法以足够的精度表示一个小数,它只能对整数进行计算。

而浮点DSP的优势在于它可以把这个采样得到的整数转换成小数表示的电压,并不损失精度(这个小数用科学记数法来表示),原因在于科学记数法可以表示很大的动态范围的一个信号,以IEEE754浮点数为例,单精度浮点格式: [31] 1位符号 [30-23]8位指数 [22-00]23位小数这样的能表示的最小的数是+-2^-149,最大的数是+-(2-2^23)*2^127.(这里不去研究这个最小最大范围是如何计算出来的)动态范围为20*log(最大的数/最小的数)=1667.6dB 这样大的动态范围使得我们在编程的时候几乎不必考虑乘法和累加的溢出,而如果使用定点处理器编程,对计算结果进行舍入和移位则是家常便饭,这在一定程度上会损失是精度。

DSP简介

DSP-起始篇数字信号处理(Digital Signal Processing,简称DSP)是一门涉及许多学科而又广泛应用于许多领域的新兴学科。

20世纪60年代以来,随着计算机和信息技术的飞速发展,数字信号处理技术应运而生并得到迅速的发展。

在过去的二十多年时间里,数字信号处理已经在通信等领域得到极为广泛的应用。

数字信号处理是利用计算机或专用处理设备,以数字形式对信号进行采集、变换、滤波、估值、增强、压缩、识别等处理,以得到符合人们需要的信号形式。

数字信号处理是围绕着数字信号处理的理论、实现和应用等几个方面发展起来的。

数字信号处理在理论上的发展推动了数字信号处理应用的发展。

反过来,数字信号处理的应用又促进了数字信号处理理论的提高。

而数字信号处理的实现则是理论和应用之间的桥梁。

数字信号处理是以众多学科为理论基础的,它所涉及的范围极其广泛。

例如,在数学领域,微积分、概率统计、随机过程、数值分析等都是数字信号处理的基本工具,与网络理论、信号与系统、控制论、通信理论、故障诊断等也密切相关。

近来新兴的一些学科,如人工智能、模式识别、神经网络等,都与数字信号处理密不可分。

可以说,数字信号处理是把许多经典的理论体系作为自己的理论基础,同时又使自己成为一系列新兴学科的理论基础。

世界上第一个单片DSP 芯片应当是1978年AMI公司发布的S2811,1979年美国Intel公司发布的商用可编程器件2920是DSP芯片的一个主要里程碑。

这两种芯片内部都没有现代DSP芯片所必须有的单周期乘法器。

1980 年,日本NEC 公司推出的μP D7720是第一个具有乘法器的商用DSP 芯片。

在这之后,最成功的DSP 芯片当数美国德州仪器公司(Texas Instruments,简称TI)的一系列产品。

TI 公司在1982年成功推出其第一代DSP 芯片TMS32010及其系列产品TMS32011、TMS320C10/C1 4/C15/C16/C17等,之后相继推出了第二代DSP芯片TMS32020、TMS320C25/C26/C28,第三代DSP 芯片TMS320C30/C31/C32,第四代DSP芯片TMS320C40/C44,第五代DSP 芯片TMS320C5X/C54 X,第二代DSP芯片的改进型TMS320C2XX,集多片DSP芯片于一体的高性能DSP芯片TMS320C8X 以及目前速度最快的第六代DSP芯片TMS320C62X/C67X等。

DSP学习笔记(二)——DSP中浮点数与定点数格式与运算处理

DSP学习笔记(⼆)——DSP中浮点数与定点数格式与运算处理DSP学习笔记(⼆)——DSP中浮点数与定点数格式与处理1 DSP中的数据表述DSP中数据通常是有定点数与表⽰,其中可以对字长进⾏相关定义,可以选取字长为16位、24位、32位不同字长使⽤。

⽽格式与字长决定了数据的精度与动态范围,同时也⼀定程度上决定了DSP处理器的功耗、成本与编程难度。

定点数:⼩数点位置为确定的。

浮点数:⼩数点位置可以改变。

定点运算的硬件实现较为简单,功耗较⼩,主要注意的是数据的定标、溢出以及误差。

器减结构较为复杂,但是精度较⾼,⾼级语⾔容易⽀持。

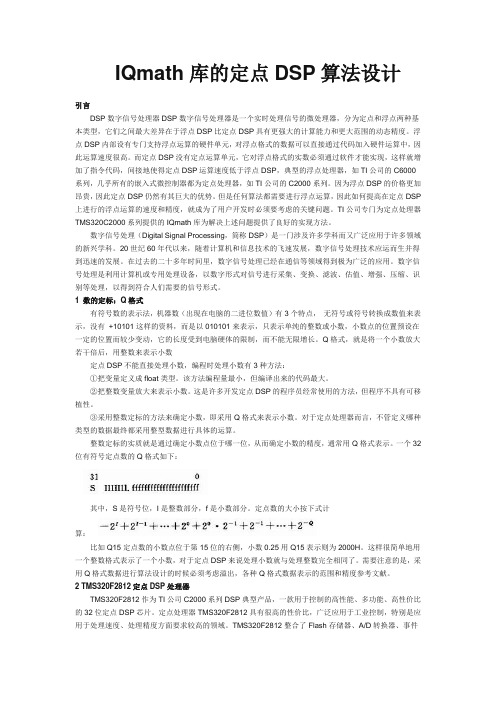

2 定点数的格式与相关运算2.1 定点数格式定点数格式:Q n 格式,n为⼩数位数。

即Q15 ,⼩数点右边有15个⼩数位,如果我们定义了⼀个长度为32位的数字,那么⼩数位为15,1位符号位,16位为整数位。

整数⼩数点固定在最后,定点数⼩数位固定使⽤上⽂的Q n 格式表⽰,两者都使⽤⼆进制补码形式表⽰。

例: Q4格式:01010011b=1·22+1·20+1·2-3+1·2-4=83/24=5.1875对于负数(最⾼位MSB为1),要先把它转化为⽆符号⼆进制数,再进⾏计算,最后加上负号。

图2-1 ⼆进制Q格式表⽰定点数与浮点数转化时需要使⽤2n 的关系进⾏转化。

转化关系如下图:图2-2 定点数与浮点数转化关系浮点数转换为定点数时,由于⼩数点后的位数有限,会产⽣截断误差。

2.2 数值范围与精度Qn 格式,字长为N数值范围: -2N-12n~2N-1-12n精度:12n由于符号位占1位,所以数据位为N-1,n越⼤范围越⼩,但精度越⾼。

图2-3 数值范围与精度2.3 动态范围数据格式中最⼤值与最⼩值之⽐即为动态范围。

N位定点数动态范围:分贝表⽰:dsp⼤多采⽤16位定点数,动态范围为90.3db。

Dsp⼤多采⽤16为定点数,运算硬件实现较为简单,更⼤动态范围应⽤可以使⽤拓展字长⽅式。

DSP-定点和浮点数格式解析

① 小数乘小数(n、m≠0,m≤ n) ② 整数乘小数(n≠0、m=0) ③ 整数乘整数(n=m=0)

① 小数乘小数(n、m≠0,m≤ n)

例:两个8位数相加,有溢出 进位位与最高位(MSB)不同 运算结果发生溢出,8位字长已不能正确地表示结果

10110000b( -80) + 10111111b( -65) 非饱和模式:101101111bቤተ መጻሕፍቲ ባይዱ-145)

00101001b( 41) + 01110011b(115) 非饱和模式:010011100b(156)

2)数值范围与精度

给定字长N,采用Qn格式表示小数

2 N 1 2 N 1 1 数值范围: n ~ 2 2n

精

度:

1

2n

16位字长Qn格式的数值范围与精度

Qn格式 Q15 数值范围 -1~0.999969482421875 精度 0.000030517578125

Q14

饱和模式:110000000b(-128)

饱和模式:001111111b(127)

溢出是由于字长有限,运算结果超出数值的表示范围引 起的

饱和模式

定点数减法运算的原理与加法运算相同

2)定点数的乘法运算

DSP处理器都有硬件乘法器和乘法指令,可实现单周期乘 法运算 二进制乘法运算包含一系列的移位和加法运算 定点数乘法运算不要求相乘数有相同的Qn格式 两个相乘数分别为Qn和Qm格式,字长为N,结果为 Q(n+m)格式,字长为2N 根据n和m的不同取值,定点数乘法运算可以分成三种情况

DSP 运算基础

• 1、 DSP的数据表示

• 2、定点数的格式与运算 • 3、浮点数的格式与运算

定点dsp与浮点dsp的比较

定点DSP与浮点DSP的比较定点运算DSP在应用中已取得了极大的成功,而且仍然是DSP应用的主体。

然而,随着对DSP处理速度与精度、存储器容量、编程的灵活性和方便性要求的不断提高、自80年代中后期以来,各DSP生产厂家陆续推出了各自的32bit浮点运算DSP。

和定点运算DSP相比,浮点运算DSP具有许多优越性:浮点运算DSP比定点运算DSP的动态范围要大很多。

定点DSP的字长每增加1bit,动态范围扩大6dB。

16bit字长的动态范围为96dB。

程序员必须时刻关注溢出的发生。

例如,在作图像处理时,图像作旋转、移动等,就很容易产生溢出。

这时,要么不断地移位定标,要么作截尾。

前者要耗费大量的程序空间和执行时间,后者则很快带来图像质量的劣化。

总之,是使整个系统的性能下降。

在处理低信噪比信号的场合,例如进行语音识别、雷达和声纳信号处理时,也会发生类似的问题。

而32bit浮点运算DSP的动态范围可以作到1536dB,这不仅大大扩大了动态范围,提高了运算精度,还大大节省了运算时间和存储空间,因为大大减少了定标,移位和溢出检查。

由于浮点DSP的浮点运算用硬件来实现,可以在单周期内完成,因而其处理速度大大高于定点DSP。

这一优点在实现高精度复杂算法时尤为突出,为复杂算法的实时处理提供了保证。

32bit浮点DSP的总线宽度较定点DSP宽得多,因而寻址空间也要大得多。

这一方面为大型复杂算法提供了可能、因为省的DSP目标子程序已使用到几十MB存储器或更多;另一方面也为高级语言编译器、DSP操作系统等高级工具软件的应用提供了条件。

DSP的进一步发展,必然是多处理器的应用。

新型的浮点DSP已开始在通信口的设置和强化、资源共享等方面有所响应。

DSP学习进阶学习TI的各种DSP,本着循序渐进的原则,可以分为多个层次。

根据我多年开发DSP的经验,在这里总结一下各个层次的进阶:1、DSP2000(除了2812):进阶:标准C -> C和汇编混合编程说明:把DSP2000当作单片机来玩就可以了,非常简单。

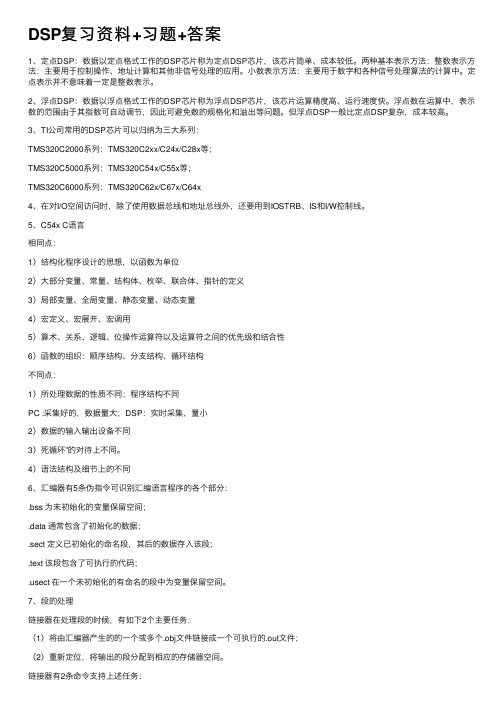

DSP复习资料+习题+答案

DSP复习资料+习题+答案1、定点DSP:数据以定点格式⼯作的DSP芯⽚称为定点DSP芯⽚,该芯⽚简单、成本较低。

两种基本表⽰⽅法:整数表⽰⽅法:主要⽤于控制操作、地址计算和其他⾮信号处理的应⽤。

⼩数表⽰⽅法:主要⽤于数字和各种信号处理算法的计算中。

定点表⽰并不意味着⼀定是整数表⽰。

2、浮点DSP:数据以浮点格式⼯作的DSP芯⽚称为浮点DSP芯⽚,该芯⽚运算精度⾼、运⾏速度快。

浮点数在运算中,表⽰数的范围由于其指数可⾃动调节,因此可避免数的规格化和溢出等问题。

但浮点DSP⼀般⽐定点DSP复杂,成本较⾼。

3、TI公司常⽤的DSP芯⽚可以归纳为三⼤系列:TMS320C2000系列:TMS320C2xx/C24x/C28x等;TMS320C5000系列:TMS320C54x/C55x等;TMS320C6000系列:TMS320C62x/C67x/C64x4、在对I/O空间访问时,除了使⽤数据总线和地址总线外,还要⽤到IOSTRB、IS和I/W控制线。

5、C54x C语⾔相同点:1)结构化程序设计的思想,以函数为单位2)⼤部分变量、常量、结构体、枚举、联合体、指针的定义3)局部变量、全局变量、静态变量、动态变量4)宏定义、宏展开、宏调⽤5)算术、关系、逻辑、位操作运算符以及运算符之间的优先级和结合性6)函数的组织:顺序结构、分⽀结构、循环结构不同点:1)所处理数据的性质不同;程序结构不同PC :采集好的,数据量⼤;DSP:实时采集,量⼩2)数据的输⼊输出设备不同3)死循环”的对待上不同。

4)语法结构及细节上的不同6、汇编器有5条伪指令可识别汇编语⾔程序的各个部分:.bss 为未初始化的变量保留空间;.data 通常包含了初始化的数据;.sect 定义已初始化的命名段,其后的数据存⼊该段;.text 该段包含了可执⾏的代码;.usect 在⼀个未初始化的有命名的段中为变量保留空间。

7、段的处理链接器在处理段的时候,有如下2个主要任务:(1)将由汇编器产⽣的的⼀个或多个.obj⽂件链接成⼀个可执⾏的.out⽂件;(2)重新定位,将输出的段分配到相应的存储器空间。

DSP终极总结

DSP终极总结1.什么是定点DSP芯⽚和浮点DSP芯⽚?各有什么优缺点?解:按数据的定点格式⼯作的DSP芯⽚称为定点DSP;按数据的浮点格式⼯作的DSP芯⽚称为浮点DSP;定点DSP的价格便宜,功耗低,但运算精度低;浮点DSP的价格较⾼,C语⾔编程调试⽅便,运算精度⾼。

2. 简述流⽔线操作的基本原理。

解:流⽔线操作是各指令以机器周期为单位相差⼀个时钟周期,连续并⾏⼯作的情况。

其本质是DSP多条总线彼此独⽴地同时⼯作,使得同⼀条指令在不同机器周期内占⽤不同总线资源。

同时,不同指令在同⼀机器周期内占⽤不同总线资源。

3. ’C54x DSP有哪些重复操作?各有什么优点?解:有单条指令重复执⾏和程序块重复执⾏两种重复操作。

单条指令重复操作功能,可以使乘法/累加和数据块传送那样的多周期指令在执⾏⼀次之后变成单周期指令,⼤⼤提⾼了这些指令的执⾏速度。

利⽤块重复操作进⾏循环,是⼀种零开销循环。

4. 软件可编程等待状态发⽣器的功能是什么?解:软件可编程等待状态产⽣器可以将外部总线周期扩展到7个机器周期(C549、C5402、C5410和C5420为14个机器周期),这样’C54x DSP可以⽅便地与慢速的⽚内存储器和I/O器件接⼝。

三、问答题(10分)1. ’C54x DSP的串⾏⼝有哪些类型?各有什么特点?解:有标准同步串⼝SP、缓冲同步串⼝BSP、多路缓冲串⼝McBSP、时分多路同步串⼝TMD 四种。

缓冲串⼝(BSP)是⼀个增强型的标准串⼝,它由⼀个全双⼯双缓冲串⼝和⼀个⾃动缓冲单元(ABU)组成。

由于其中的串⾏⼝与标准串⼝的功能相同,因此在标准模式下,缓冲串⼝的操作与标准串⼝的⼯作⽅式是⼀样的。

不过⽆论是标准模式还是⾃动缓冲模式,BSP 都提供了⼀些增强功能。

主要包括了可编程控制的串⼝时钟、可选择时钟和帧同步信号的正负极性,能够以每帧8位、10位、12位和16位传输数据。

通过配置BSP的控制寄存器,BSP还能实现忽略帧同步信号的数据传输。

献给初学者-DSP入门教程helloDSP论坛

献给初学者-DSP入门教程helloDSP论坛献给初学者-DSP入门教程helloDSP论坛前言:此资料也是来源于网络,并不是我们原创,但是希望这些资料能够给初学DSP的朋友们一点帮助,也希望你们能够把这里当成是你们学习DSP技术的一个家园,让我们携手共建,为更多的朋友创造学习的条件~1、TI DSP的选型主要考虑处理速度、功耗、程序存储器和数据存储器的容量、片内的资源,如定时器的数量、I/O口数量、中断数量、DMA通道数等。

DSP的主要供应商有TI,ADI,Motorola,Lucent和Zilog等,其中TI占有最大的市场份额。

TI公司现在主推四大系列DSP1)C5000系列(定点、低功耗):C54X,C54XX,C55X 相比其它系列的主要特点是低功耗,所以最适合个人与便携式上网以及无线通信应用,如手机、PDA、GPS等应用。

处理速度在80MIPS-- 400MIPS之间。

C54XX和C55XX 一般只具有McBSP同步串口、HPI 并行接口、定时器、DMA等外设。

值得注意的是C55XX提供了EMIF 外部存储器扩展接口,可以直接使用 SDRAM,而C54XX则不能直接使用。

两个系列的数字IO都只有两条。

2)C2000系列(定点、控制器):C20X,F20X,F24X,F24XX ,C28x该系芯片具有大量外设资源,如:A/D、定时器、各种串口(同步和异步),WATCHDOG、CAN总线/PWM发生器、数字IO脚等。

是针对控制应用最佳化的DSP,在TI所有的DSP中,只有C2000有FLASH,也只有该系列有异步串口可以和PC的UART相连。

3)C6000系列:C62XX,C67XX,C64X 该系列以高性能著称,最适合宽带网络和数字影像应用。

32bit,其中:C62XX和C64X是定点系列,C67XX 是浮点系列。

该系列提供EMIF扩展存储器接口。

该系列只提供BGA封装,只能制作多层PCB。

定点DSP与浮点DSP的比较

声明:本文章系转载并稍加整理标注,可能对于入门级的dsp开发者有所帮助。

本文关注定点dsp与浮点dsp的对比,感谢我所引用的资料的作者。

定点dsp与浮点dsp的比较(1)DSP数字信号处理器是一种特别适合于进行数字信号处理的微处理器,主要用于实时快速地实现各种数字信号处理算法定点运算DSP数字信号处理器在应用中已取得了极大的成功,而且仍然是DSP应用的主体。

然而,随着对DSP处理速度与精度、存储器容量、编程的灵活性和方便性要求的不断提高、自80年代中后期以来,各DSP生产厂家陆续推出了各自的32bit浮点运算DSP。

定点DSP指令集定点DSP指令集是按两个目标来设计的:·使处理器能够在每个指令周期内完成多个操作,从而提高每个指令周期的计算效率。

·将存贮DSP程序的存储器空间减到最小(由于存储器对整个系统的成本影响甚大,该问题在对成本敏感的DSP应用中尤为重要)。

和定点运算DSP相比,浮点运算DSP具有许多优越性:浮点运算DSP比定点运算DSP的动态范围要大很多。

定点DSP的字长每增加1bit,动态范围扩大6dB。

16bit字长的动态范围为96dB。

程序员必须时刻关注溢出的发生。

例如,在作图像处理时,图像作旋转、移动等,就很容易产生溢出。

这时,要么不断地移位定标,要么作截尾。

前者要耗费大量的程序空间和执行时间,后者则很快带来图像质量的劣化。

总之,是使整个系统的性能下降。

在处理低信噪比信号的场合,例如进行语音识别、雷达和声纳信号处理时,也会发生类似的问题。

而32bit浮点运算DSP的动态范围可以作到1536dB,这不仅大大扩大了动态范围,提高了运算精度,还大大节省了运算时间和存储空间,因为大大减少了定标,移位和溢出检查。

由于浮点DSP的浮点运算用硬件来实现,可以在单周期内完成,因而其处理速度大大高于定点DSP。

这一优点在实现高精度复杂算法时尤为突出,为复杂算法的实时处理提供了保证。

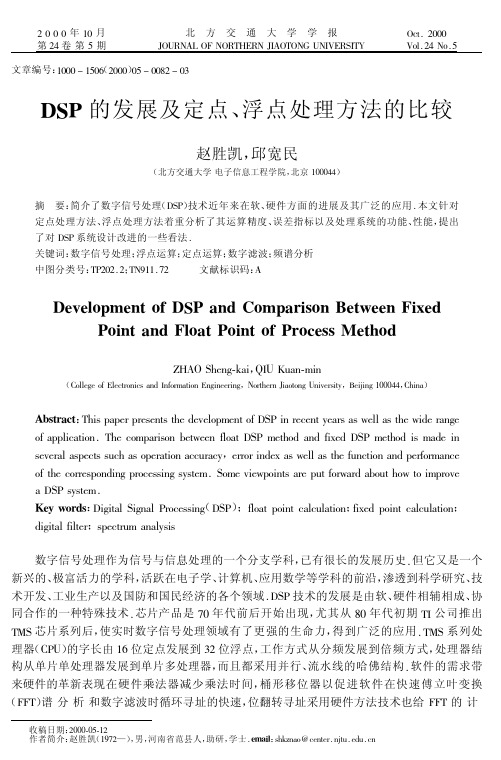

DSP的发展及定点、浮点处理方法的比较

在数字信号处理中经常会遇到 ! $"%" & ’"(" 这样的式子, 当 ! 较大时会有溢出可能, 程

"#)

运算误差在定点舍入系统 序员必须时刻关注溢出的发生、 预防与处理 ! 在处理的数据较多时, 中影响很大 ! 在定点运算中克服字长的影响可采用双字存储方法, 也可采用定标或块浮点法等 多种方法, 但都必须以牺牲存储器、 浪费 ’$( 执行时间、 增加软件设计难度等为代价 ! 浮点 它只有不可避免的 * + " 量化误差较明显, 在运算处理过程中的字长 ’$( 的处理则简单得多,

:;2+0-7+: .6=L S<S7K SK7L78JL J67 M7O7FESC78J EG *+, =8 K7I78J P7<KL <L T7FF <L J67 T=M7 K<897 EG <SSF=I<J=E8 - .67 IECS<K=LE8 U7JT778 GFE<J *+, C7J6EM <8M G=V7M *+, C7J6EM =L C<M7 =8 L7O7K<F <LS7IJL LBI6 <L ES7K<J=E8 <IIBK<IP,7KKEK =8M7V <L T7FF <L J67 GB8IJ=E8 <8M S7KGEKC<8I7 EG J67 IEKK7LSE8M=89 SKEI7LL=89 LPLJ7C- +EC7 O=7TSE=8JL <K7 SBJ GEKT<KM <UEBJ 6ET JE =CSKEO7 < *+, LPLJ7C( *+,) ;GFE<J SE=8J I<FIBF<J=E8; <$= 4’0.2: *=9=J<F +=98<F ,KEI7LL=89 G=V7M SE=8J I<FIBF<J=E8; M=9=J<F G=FJ7K;LS7IJKBC <8<FPL=L 数字信号处理作为信号与信息处理的一个分支学科, 已有很长的发展历史 - 但它又是一个 新兴的、 极富活力的学科, 活跃在电子学、 计算机、 应用数学等学科的前沿, 渗透到科学研究、 技 术开发、 工业生产以及国防和国民经济的各个领域 - *+, 技术的发展是由软、 硬件相辅相成、 协 同合作的一种特殊技术 - 芯片产品是 1" 年代前后开始出现, 尤其从 ’" 年代初期 .? 公司推出 使实时数字信号处理领域有了更强的生命力, 得到广泛的应用 - .W+ 系列处 .W+ 芯片系列后, 理器 ( D,@) 的字长由 !% 位定点发展到 (& 位浮点, 工作方式从分频发展到倍频方式, 处理器结 构从单片单处理器发展到单片多处理器, 而且都采用并行、 流水线的哈佛结构 - 软件的需求带 来硬件的革新表现在硬件乘法器减少乘法时间, 桶形移位器以促进软件在快速傅立叶变换 谱 分 析 和数字滤波时循环寻址的快速, 位翻转寻址采用硬件方法技术也给 XX. 的 计 ( XX.)

DSP中的浮点与定点比较

Q8

S7.8

-128 ≤ X ≤ 127.996 093 8

Abstract:This paper introduces the fixed-point data format and floating-point data format commonly used in DSP, compares the advantages and disadvantages of the two data formats,and puts forward some suggestions on the applicable scenarios and format selection.

1 浮点数据格式与定点数据格式

1.1 浮点数据格式

在计算机系统的发展过程中提出过多种方法表

示实数,但是目前为止使用最广泛的是浮点表示法。

IEEE(Institute of Electrical and Electronics Engineers, 电子电气工程师协会)在 I985 年制定的 IEEE 754(IEEE Standard for Binary Floating-Point Arithmetic,ANSI/IEEE Std 754-1985)二进制浮点运算规范,是浮点运算部件 的工业标准 [1]。

采用以下浮点表示格式表示 16 位浮点数,该格式

为 IEEE 745 标准的子集,除了能够完成要求的实数表 示外,处理上也更为简洁。总位宽 m=16 bit,格式如图 1 所示,用一个三元组 {S,E,M} 来表示一个数 N。

15 14

10 9

0

S

E

M

1 bit

n bit

(m-n-1) bit

图 1 三元组表示法举例

DSP简介

DSP(digital singnal processor)是一种独特的微处理器,是以数字信号来处理大量信息的器件。

其工作原理是接收模拟信号,转换为0或1的数字信号,再对数字信号进行修改、删除、强化,并在其他系统芯片中把数字数据解译回模拟数据或实际环境格式。

它不仅具有可编程性,而且其实时运行速度可达每秒数以千万条复杂指令程序,源源超过通用微处理器,是数字化电子世界中日益重要的电脑芯片。

它的强大数据处理能力和高运行速度,是最值得称道的两大特色DSP既是Digital Signal Processing的缩写(数字信号处理的理论和方法)或者是Digital Signal Processor(用于数字信号处理的可编程微处理器)的缩写。

我们所说的DSP技术,则一般指将通用的或专用的DSP处理器用于完成数字信号处理的方法和技术。

1. DSP的特点(1)在一个指令周期内可完成一次乘法和一次加法。

(2)程序和数据空间分开,可以同时访问指令和数据。

(3)片内具有快速RAM,通常可通过独立的数据总线在两块中同时访问。

(4)具有低开销或无开销循环及跳转的硬件支持。

(5)快速的中断处理和硬件I/O支持。

(6)具有在单周期内操作的多个硬件地址产生器。

(7)可以并行执行多个操作。

(8)支持流水线操作,使取指、译码和执行等操作可以重叠执行。

与通用微处理器相比,DSP芯片的其他通用功能相对较弱些。

1)哈佛结构和改进的哈佛结构。

哈佛结构就是将程序代码和数据的存储空间分开,各有自己的地址和数据总线。

之所以采用哈佛结构,是为了并行进行指令和数据处理,从而可以大大地提高运算的速度。

为了进一步提高信号处理的效率,在哈佛结构的基础上,又加以改善。

使得程序代码和数据存储空间之间可以进行数据的传输,称为改善的哈佛结构。

2)采用流水技术。

流水技术是将各指令的各个步骤重叠起来执行。

DSP处理器所采用的将程序存储空和数据存储空间的地址与数据总线分开的哈佛结构,为采用流水技术提供了很大的方便。

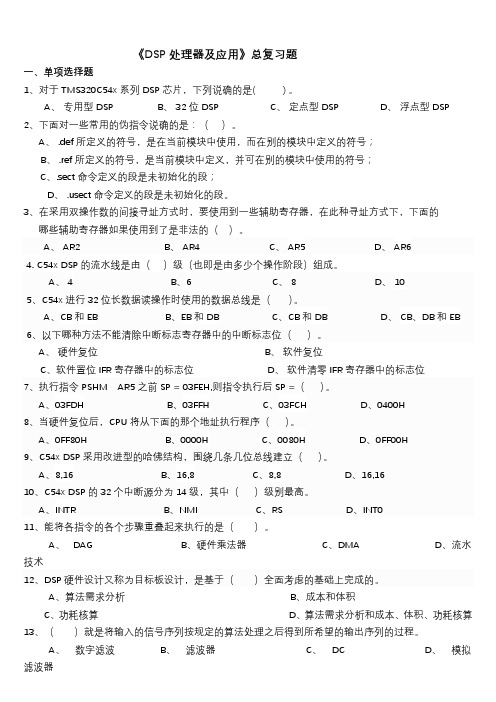

《DSP处理器及应用》复习题

《DSP处理器及应用》总复习题一、单项选择题1、对于TMS320C54x系列DSP芯片,下列说确的是()。

A、专用型DSPB、32位DSPC、定点型DSPD、浮点型DSP2、下面对一些常用的伪指令说确的是:()。

A、.def所定义的符号,是在当前模块中使用,而在别的模块中定义的符号;B、.ref所定义的符号,是当前模块中定义,并可在别的模块中使用的符号;C、.sect命令定义的段是未初始化的段;D、.usect命令定义的段是未初始化的段。

3、在采用双操作数的间接寻址方式时,要使用到一些辅助寄存器,在此种寻址方式下,下面的哪些辅助寄存器如果使用到了是非法的()。

A、AR2B、AR4C、AR5D、AR64.C54x DSP的流水线是由()级(也即是由多少个操作阶段)组成。

A、4B、6C、8D、105、C54x进行32位长数据读操作时使用的数据总线是()。

A、CB和EBB、EB和DBC、CB和DBD、CB、DB和EB6、以下哪种方法不能清除中断标志寄存器中的中断标志位()。

A、硬件复位B、软件复位C、软件置位IFR寄存器中的标志位D、软件清零IFR寄存器中的标志位7、执行指令PSHM AR5之前SP = 03FEH,则指令执行后SP =()。

A、03FDHB、03FFHC、03FCHD、0400H8、当硬件复位后,CPU将从下面的那个地址执行程序()。

A、0FF80HB、0000HC、0080HD、0FF00H9、C54x DSP采用改进型的哈佛结构,围绕几条几位总线建立()。

A、8,16B、16,8C、8,8D、16,1610、C54x DSP的32个中断源分为14级,其中()级别最高。

A、INTRB、NMIC、RSD、INT011、能将各指令的各个步骤重叠起来执行的是()。

A、DAGB、硬件乘法器C、DMAD、流水技术12、DSP硬件设计又称为目标板设计,是基于()全面考虑的基础上完成的。

A、算法需求分析B、成本和体积C、功耗核算D、算法需求分析和成本、体积、功耗核算13、()就是将输入的信号序列按规定的算法处理之后得到所希望的输出序列的过程。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

定点dsp与浮点dsp的比较DSP数字信号处理器是一种特别适合于进行数字信号处理的微处理器,主要用于实时快速地实现各种数字信号处理算法定点运算DSP数字信号处理器在应用中已取得了极大的成功,而且仍然是D SP应用的主体。

然而,随着对DSP处理速度与精度、存储器容量、编程的灵活性和方便性要求的不断提高、自80年代中后期以来,各DSP生产厂家陆续推出了各自的32bit浮点运算DSP。

定点DSP指令集定点DSP指令集是按两个目标来设计的:·使处理器能够在每个指令周期内完成多个操作,从而提高每个指令周期的计算效率。

·将存贮DSP程序的存储器空间减到最小(由于存储器对整个系统的成本影响甚大,该问题在对成本敏感的DSP应用中尤为重要)。

和定点运算DSP相比,浮点运算DSP具有许多优越性:浮点运算DSP比定点运算DSP的动态范围要大很多。

定点DSP的字长每增加1bit,动态范围扩大6dB。

16bit字长的动态范围为96dB。

程序员必须时刻关注溢出的发生。

例如,在作图像处理时,图像作旋转、移动等,就很容易产生溢出。

这时,要么不断地移位定标,要么作截尾。

前者要耗费大量的程序空间和执行时间,后者则很快带来图像质量的劣化。

总之,是使整个系统的性能下降。

在处理低信噪比信号的场合,例如进行语音识别、雷达和声纳信号处理时,也会发生类似的问题。

而32bit浮点运算DSP的动态范围可以作到1536dB,这不仅大大扩大了动态范围,提高了运算精度,还大大节省了运算时间和存储空间,因为大大减少了定标,移位和溢出检查。

由于浮点DSP的浮点运算用硬件来实现,可以在单周期内完成,因而其处理速度大大高于定点DSP。

这一优点在实现高精度复杂算法时尤为突出,为复杂算法的实时处理提供了保证。

32bit浮点DSP的总线宽度较定点DSP宽得多,因而寻址空间也要大得多。

这一方面为大型复杂算法提供了可能、因为省的DSP目标子程序已使用到几十MB存储器或更多;另一方面也为高级语言编译器、DSP操作系统等高级工具软件的应用提供了条件。

DSP的进一步发展,必然是多处理器的应用。

新型的浮点DSP已开始在通信口的设置和强化、资源共享等方面有所响应======================================================TI科学家谈浮点DSP未来发展自十多年前浮点数字信号处理器(DSP)诞生以来,便为实时信号处理提供了算术上更为先进的备选方案。

不过,定点器件至今仍是业界的主流--当然低成本是主要原因。

定点DSP每器件产品的价格很低,这对大规模大众市场应用而言是相当重要的优势。

相比较而言,浮点DSP能够实现更快速而简便的开发,因此对开发成本比单位制造成本重要的小规模应用而言,更是最佳的选择。

最近几年,高密度集成与支持改善使两种DSP在使用方便性与成本上都较为接近。

目前,器件类型的选择越来越取决于应用数据集是否要求浮点格式的更多计算功能。

因此,设计大规模量产信号处理应用的开发人员现在开始发现浮点格式更多的内在价值。

他们将视线投向传统定点DSP开发模式之外的领域,并探索浮点DSP 所带来的设计机遇。

不同的数字格式定点与浮点DSP的基本差异在于它们各自对数据的数字表示法不同。

定点硬件严格执行整数运算,而浮点DSP 既支持整数运算又支持实数运算,后者以科学计数法进行了标准化。

字长为16 位的定点DSP 实现(rovide) 64K 的精度,带符号整数值范围为-215 至215-1。

与此相对比,浮点DSP将数据路径分为两部分:一是可用作整数值或实数基数的尾数,二是指数。

在支持业界标准单一精确运算的32位浮点DSP中,尾数为24位,指数为8位。

由于其较长的字长与取幂范围,该器件支持16M 的精度范围,这样的动态范围大大高于定点格式可提供的精确度。

实施业界标准双精度(64 位,包括一个53 位的尾数与11 位的指数)的器件还可实现更高的精确度。

成本与方便易用性浮点DSP 提供的计算能力更高,这也是其区别于定点DSP 功能的最大差异所在。

但在浮点DSP 刚刚出现的20世纪90年代初期,其它因素往往掩盖了基本的数学计算问题。

浮点功能需要的内部电路多,而32位数据路径比当时可用的定点器件要宽一倍。

晶片面积越大,引脚数量就越多,封装也越大,这就大大提高了新款浮点器件的成本,因此数字化语音与电信集成卡(concentration c ard)等高产量应用仍更倾向于采用较低成本的定点器件。

当时,方便易用性抵消了成本问题带来的不利影响。

浮点器件是最早支持 C 语言的DSP 之一,而定点DSP则仍须在汇编代码级上进行编程。

此外,对浮点格式而言,实数运算可直接通过代码加入硬件运算中,而定点器件则必须通过软件才能间接执行实数运算,这就增加了算法指令并延长了开发时间。

由于浮点DSP 易于编程,因此其最初主要用于开发工作强度较大的情况,如研究、原型开发、影像识别、工作站的三维图像加速器以及雷达等军用系统。

逐渐趋同目前,早先的成本与易用性间的差异已经不那么明显了。

总体说来,定点DSP 仍然在成本上有优势,而浮点DSP 仍然在易用性上有优势,但差别已经缩小很多,因此上述因素已经不再起决定作用了。

成本日益成为片上系统(SoC)集成与产量的问题,而不是DSP内核本身大小的问题。

在十年前还只能放置单个晶体管的空间,目前可放置数十个晶体管。

目前,占据晶片面积最多的是存储器,而不是逻辑,而且许多基于DSP的产品都充分利用再扩展(rescaling)的优势,针对具体市场的需求集成了不只一个内核。

定点DSP的成本仍然较低,因为其针对大众市场应用的产量很高;但是,如果大规模量产的需求出现,那么浮点器件也将受益于规模效益带来的同样的成本降低。

早期在易用性方面的差异也已经减小。

高效的C编译程序与工具早已能支持定点DSP,为代码执行带来了可视性。

直接采用浮点硬件实施实数运算仍有优势;但目前先进的建模工具、完整的数学函数库以及现成的算法降低了为定点器件开发复杂应用的难度。

浮点的精确度目前,选用定点DSP还是浮点DSP归根结底在于应用数据集是否需要浮点算术功能。

总体说来,设计人员应解决两个问题:数据集要求多高的精确度?数据集的可预见度有多大?三个因素影响着浮点格式的内在高精度。

首先,浮点DSP的24位I/O字长在整数与实数值方面可实现比定点器件中常用的16 位字长更高的精确度。

第二,取幂大幅提高了应用可用的动态范围,较大的动态范围对处理极大数据集以及难以方便预计数据集范围的情况相当重要。

第三,浮点硬件内部的数据表示法比定点器件更为精确,这就保证了最终结果的精确度更高。

最后一点应稍做解释。

在DSP的内部架构中,三种数据字长相当重要,应当考虑。

第一是I/O信号字长,正如我们已经说过的那样,其就浮点而言为24位,就定点DSP而言通常为16位。

第二就是用于乘法的系数字长。

定点系数为16位,与信号数据相同;但浮点系数则可能为24位或53位,这取决于所用的是单宽度精度还是双宽度精度。

如果指数表示有意义的零,则精确度实际上会超过上述位数。

最后,就是保存乘加器(MAC)运算中间结果的字长,通常称作寄存器文件。

对单一16位乘以16位的乘法而言,将需要32位的乘积;而就单一24位乘以24位的尾数乘法而言,则需48位的乘积(指数有不同的数据路径)。

但是,MAC 需要额外的位用于溢出空间(overflow headroom)。

在16位定点器件中,溢出空间通常为8 位,这就使总的中间结果字长为40 位(16 个信号+16 个系数+ 8 个溢出)。

将相同大小的溢出空间集成到浮点DSP中将需要60个中间结果位(24个信号+24个系数+12个溢出),这将超过大多数应用对精度的要求。

但就取幂而言,我们将结果标准化,这样所有24位或53位都有效,溢出位就不必要了。

TI的TMS320C67x系列等浮点DSP允许开发人员在双精度内部运算与单精度I/O结合的模式下优化精确度与性能。

其结果是得到的精确度比定点或单精度浮点运算提供的精确度高得多,但又不会产生完全双精度I/O 带来的周期问题。

视频与音频数据集要求将视频与音频应用的数据集要求加以对比,就很容易看出使用浮点格式的优势。

视频的采样率很高,其像素数据采样率相当于每秒数十乃至数百个兆位(Mbp s),具体的值决于应用。

像素数据通常以8 至12 位的短字表示,每一位代表影像的红、绿、蓝(RGB)位面。

业界标准的MPEG视频压缩算法的关键数学运算包括离散余弦变换(DCT)与量化,且过滤有限。

DCT与量化采用整数运算就能有效处理,它与短数据字相结合使得视频成为定点DSP很自然的应用,特别对那些设计有大量并行数据路径与片上视频接口的情况更是如此。

另一方面,音频的数据流更为有限,对24 位采样且每秒48 千个采样(ksps) 的速度而言,约为1Mbps的速度。

新兴的采样率为192ksps,为该数据速率的四倍,但其数据流仍然大大低于视频流。

不过音频数据的处理必须比视频精确得多。

眼睛很容易就被欺骗,特别当影像运动时更是如此;但耳朵就很难欺骗了。

因此音频需要浮点硬件提供的更大的字长。

使用完全24位浮点I/O精度来进行声音采样,这就得到144dB的动态范围,大大超出了声音复制所需的全振幅范围。

此外,音频还要求宽系数与中间结果提供的精确度,其原因有二。

首先,音频应用通常使用串联无限脉冲响应滤波器(IIR)以实现最低时延与最高性能。

但串联过滤每一级都会传播上一级的错误。

信号与系数字长越长,精确度越高,上述传播错误的影响就越小。

第二,在接近于零时必须保持信号精确度,以避免人耳可以分辨的谐波失真。

浮点格式从本质上说与人耳的敏感度配合得很好,因为它在分数趋近于零时会变得更精确。

相反,定点系统在分数极小的情况下会取近似值等于零,这就降低了精确度。

所有上述浮点实数算法方面都对真实复制音频信号至关重要。

尽管过去常用定点器件实现高保真音频,但目前则转向采用精确度更高的浮点格式。

某些浮点DSP集成了多通道音频串行端口(McASP),从而简化了音频系统的设计,这就为上述发展趋势提供了支持。

随着最新型音频创新在消费类电子产品中的日益普及,对浮点DSP的需求也将上升,这也有助于让其成本更接近于定点DSP。

其他数据集其它类型应用的数据集也可受益于浮点的精确度。

在医疗影像识别中,更高的精确度能够支持许多层次的信号输入,包括光、X射线、超声波与其它来源的输入等,它们都必须进行定义与处理,以生成提供有用诊断信息的输出影像。

动态范围较大对雷达至关重要,这种情况下,系统应能够在从零到无穷大的范围内进行跟踪,而只用整个范围的一个较小的子集进行目标捕获与识别。

动态范围较大也有助于让机器人处理不可预见的情况,如在机器人正常有限的运动范围中遇到的障碍等。