CPU与控制单元设计

冯诺依曼计算机体系结构

冯诺依曼计算机体系结构冯·诺依曼计算机体系结构(von Neumann architecture)是一种包括中央处理器(Central Processing Unit,CPU)、存储器(Memory)、输入/输出设备(Input/Output Device)和控制单元(Control Unit)等基本组件的计算机系统的组织结构。

这种计算机体系结构在20世纪40年代末至50年代初由冯·诺依曼提出,并成为了现代计算机的基础。

下面将详细介绍冯·诺依曼计算机体系结构的各个方面。

首先,中央处理器(CPU)是计算机系统的核心部件,负责执行指令、进行运算和控制计算机的其他组件。

它由算术逻辑单元(Arithmetic Logic Unit,ALU)和控制单元(Control Unit)组成。

ALU负责进行算术和逻辑运算,而控制单元则负责解码和执行指令、管理数据传输和控制计算机的其他组件。

CPU的设计使得计算机可以按照指令进行顺序执行,实现数据的处理和计算。

其次,存储器(Memory)是计算机系统中用于存储和获取数据和指令的组件。

冯·诺依曼计算机体系结构中的存储器被划分为两个主要部分:主存储器(Main Memory)和辅助存储器(Secondary Storage)。

主存储器是CPU能够直接访问的存储设备,它通常采用随机存储器(Random Access Memory,RAM)的形式,用于暂时保存计算机运行时的数据和指令。

与之相对,辅助存储器类似于硬盘或固态硬盘,用于长期存储数据和程序。

再次,输入/输出设备(Input/Output Device)用于计算机与外部世界之间的数据交换。

输入设备用于向计算机系统输入数据和指令,包括键盘、鼠标、触摸屏等;而输出设备用于将计算机处理的结果输出给用户,包括显示器、打印机、扬声器等。

输入/输出设备通过输入/输出接口与计算机系统的其他组件连接,实现数据的传输和交换。

CPU设计实践教程6-Minisys-1单周期CPU控制器的设计

指令操作码 ori

addiu

lw

sw

beq jump

RegDst

0

0

0

000000 R-format

1

RegDST = R-format

wire R_format;

assign R_format = (Opcode==6'b000000)? 1'b1:1'b0; assign RegDST = R_format; //说明目标是rd,否则是rt

output Sftmd; output[1:0] ALUOp;

// 他I-类型指令 // 为1表明是移位指令 // 是R-类型或I_format=1时位1为1, beq、bne指令则 // 位0为1

2021/9/5 P.22

单周期控制器设计

RegDST的控制电路

op 001101 001001 100011 101011 000100 000010

output nBranch; // 为1表明是Bne指令

output Jmp;

// 为1表明是J指令

output Sftmd; // 为1表明是移位指令

2021/9/5 P.25

单周期控制器设计

练习2

请给出下列控制信号电路的Verilog描述

assign Sw = ????? assign ALUSrc = ????? assign Branch = ????? assign nBranch = ????? assign Jmp = ?????

2021/9/5 P.10

创建一个项目

在打开的Default Port对话框中选择的FPGA器件为 xc7a100tfgg484-1,如图所示,点击Next。

六章CPU设计

下地址控制编码方式

一般情况下后继微指令旳地址有下列几种给出方式:顺序递增法:将µPC设置成可实现自动加1旳功能,每当完毕目前指令旳执行,就以µPC +1后旳值为地址在控制存储器中取下一条微指令。直接给出法:下一条微指令旳地址直接取自微指令中旳下地址字段。分支转移法:在包括分支转移旳微指令中常设置一种条件选择子区域,用于指出哪些鉴定条件被测试,与此同步转移地址被存储在下地址字段。当转移条件满足时,将下地址字段旳内容读入到µPC中,取下一条微指令,实现微程序转移。若转移条件不满足,微程序则顺序执行。微程序入口地址旳形成:每条机器指令所相应旳微程序旳入口地址(首地址),一般由指令旳操作码所决定。在机器加电后,第一条微指令旳地址一般是由专门旳逻辑电路生成,也能够采用由外部直接输入旳形式取得。

操作控制编码方式

在操作控制字段一般涉及一种或多种操作控制域,每个控制域可控制一种或一组控制信号旳生成,根据控制信号是直接生成于控制域还是译码生成控制信号旳不同可分为下列几种形式。直接控制法:操作控制字段旳每一位都与一种独立控制信号相相应。若目前微指令旳某一位ki=1,则与之相应ci控制信号有效,不然ci控制信号无效。分段编码控制法:在微程序级别,许多微操作是能够并行执行。一般采用将微指令旳操作控制字段提成k个相互独立旳控制域,每一种控制域存储一组微操作,每一种编码相应一种微操作,每一种微操作都能够与其他控制域所存储旳任意一种微操作并行执行,但在组内旳微操作之间是互斥旳,不允许在同一时间段内发生或有效。分段间接编码控制法:在微指令格式里,假如一种字段旳含义不只决定本字段编码,还兼由其他字段决定,则可采用分段间接编码控制法。此时一种字段兼有两层或两层以上旳含义。其他方式:在实际微指令中操作控制编码并不是只单独采用上述三种编码方式中旳一种,而是将上述三种混合使用,以确保能综合考虑指令旳字长、灵活性和执行微程序旳速度等方面旳要求。

构成cpu的主要部件是什么

“构成CPU的主要部件是运算逻辑部件、寄存器部件和控制部件。

算术逻辑单元:算术逻辑单元(arithmetic and logic unit) 是能实现多组算术运算和逻辑运算的组合逻辑电路,简称ALU。

寄存器:寄存器的功能是存储二进制代码,它是由具有存储功能的触发器组合起来构成的。

一个触发器可以存储1位二进制代码,故存放n 位二进制代码的寄存器,需用n个触发器来构成。

控制单元:控制单元(Control Unit)负责程序的流程管理。

正如工厂的物流分配部门,控制单元是整个CPU的指挥控制中心,由指令寄存器IR(Instruction Register)、指令译码器ID(Instruction Decoder)和操作控制器OC(Operation Controller)三个部件组成,对协调整个电脑有序工作极为重要。

控制单元可以作为CPU的一部分,也可以安装于CPU外部。

中央处理器:中央处理器作为计算机系统的运算和控制核心,是信息处理、程序运行的最终执行单元。

CPU 自产生以来,在逻辑结构、运行效率以及功能外延上取得了巨大发展。

中央处理器(CPU),是电子计算机的主要设备之一,电脑中的核心配件。

其功能主要是解释计算机指令以及处理计算机软件中的数据。

CPU是计算机中负责读取指令,对指令译码并执行指令的核心部件。

中央处理器主要包括两个部分,即控制器、运算器,其中还包括高速缓冲存储器及实现它们之间联系的数据、控制的总线。

电子计算机三大核心部件就是CPU、内部存储器、输入/输出设备。

中央处理器的功效主要为处理指令、执行操作、控制时间、处理数据。

在计算机体系结构中,CPU 是对计算机的所有硬件资源(如存储器、输入输出单元)进行控制调配、执行通用运算的核心硬件单元。

CPU 是计算机的运算和控制核心。

计算机系统中所有软件层的操作,最终都将通过指令集映射为CPU的操作。

结构通常来讲,CPU的结构可以大致分为运算逻辑部件、寄存器部件和控制部件等。

基于多CPU结构的电控组合泵电控单元设计

基于多CPU结构的电控组合泵电控单元设计尤丽华;唐雄辉;安伟;孙晓琴;李刚;王诣【期刊名称】《车用发动机》【年(卷),期】2009(000)006【摘要】提出了用多片C8051F500八位微处理器合理分配任务的电子控制单元结构方案,设计了多CPU的低成本电子控制单元的硬件和软件.总线隔离和权限电路解决了多CPU共享存储器的问题,双阶段PWM波限流控制驱动电路有效提高了高速电磁阀的驱动速度并改善驱动波形.基于模块化设计思想设计了电子控制单元软件.在油泵试验台上对电控单元的驱动品质、喷油定时以及喷油延续角的控制效果等进行了测试.结果表明,所设计的电控单元驱动响应快,控制精度高,性能稳定.【总页数】5页(P28-32)【作者】尤丽华;唐雄辉;安伟;孙晓琴;李刚;王诣【作者单位】江南大学机械工程学院,江苏,无锡,214122;江南大学机械工程学院,江苏,无锡,214122;江南大学机械工程学院,江苏,无锡,214122;无锡威孚高科技股份有限公司技术中心,江苏,无锡,214000;无锡威孚高科技股份有限公司技术中心,江苏,无锡,214000;无锡威孚高科技股份有限公司技术中心,江苏,无锡,214000【正文语种】中文【中图分类】TK423.8【相关文献】1.基于MPC5602的CDPF喷油助燃再生系统电控单元设计 [J], 程晓章;谢振凯;李配楠2.组合机床电控单元系统的CAN总线接口软硬件设计 [J], 楼少敏3.自动变速器主从结构电控单元硬件设计 [J], 濮阳煌;吴光强;黄蒙;王雷雷4.基于dSPACE的硬件在回路仿真在单体泵柴油机电控单元开发中的应用 [J], 褚全红;白思春;贾利;杨凤秋;付海燕;靳范萍;吴永兴;刘洪涛5.基于汽车电子的SCR电控单元的设计分析 [J], 冯吉涛因版权原因,仅展示原文概要,查看原文内容请购买。

机车制动控制单元的双CPU控制板冗余设计

第 5期

电力机车与城轨车辆

El e c t r i c L o c o mo t i v e s& Ma s s T r a n s i t V e h i c l e s

V01 . 36 No. 5

2 0 1 3年 9月 2 0日

S e p. 2 0 t h, 2 0 1 3

摘 要 : 制动控制单元 B C U的正 常运行对机车安 全行驶具有重 大的作 用。文章基于冗余控制思想 , 提

出了双 C P U冗余控 制热备份方案 , 设计 实现 了基 于热备份技术 的双 C P U冗余 控制 , 详 细叙 述 了 B C U的 C P U 控制板 和双 P C 1 0 4控制板冗余控制 的系统组成 和软硬件设 计 , 并 分析了双 C P U冗余 控制的可靠性 。 该技术 可 有效地增强 B C U工作 的可靠性 , 提 高了机车的制动性能 , 保障 了长 区间机车运行 的安全性 。 关键 词 : 制动控制单元 ;双 C P U切换 ; 冗余控制 ; 热备份

d r i v i n g .T h i s p a p e r p r o p o s e s a s c h e me o f d o u b l e CP U r e d u n d a nc y c o n t r o l h o t b a c k u p b a s e d o n r e d u n d a n c y c o n t r o l

K e y wo r d s: b r a k e c o n t r o l u n i t ; d o u b l e C P U s wi t c h o v e r ;r e d u n d a n c y c o n t r o l ; h o t b a c k u p

关于冯诺依曼型体系结构的计算机五大部件

关于冯诺依曼型体系结构的计算机五大部件计算机是当代信息化社会最为重要的工具之一,而冯诺依曼型体系结构是计算机体系结构设计中的一种经典模型,也是目前计算机体系结构的基石。

冯诺依曼型体系结构的基本框架由计算机五大部件组成,这五大部件分别是中央处理器(CPU)、存储器(Memory)、输入设备(Input)、输出设备(Output)和控制器(Control Unit),下面将逐一进行讲解。

第一部分:中央处理器(CPU)中央处理器,简称CPU,是冯诺依曼计算机的核心部件。

它是负责执行指令、控制数据流、进行算术和逻辑运算的芯片。

一般而言,CPU由控制单元和运算单元两个主要部分组成。

控制单元负责对程序流程的控制,而运算单元则负责算术和逻辑操作。

第二部分:存储器(Memory)存储器是计算机中用于存放数据和程序的部件,也是计算机五大部件之一。

在冯诺依曼型体系结构中,存储器可以分为内存储器和外存储器两种。

内存储器是指内部存储器,它由随机访问存储器(RAM)和只读存储器(ROM)两种组成。

而外存储器则是指外部设备,如硬盘、光盘等。

第三部分:输入设备(Input)输入设备是指用于将信息输入到计算机中的各种设备,如键盘、鼠标、扫描仪等。

这些设备可以将用户的操作或外界的信息转化为计算机能够处理的数据。

第四部分:输出设备(Output)输出设备是指将计算机处理后的数据通过各种形式展示给用户或输出到外部设备中的装置,如显示器、打印机、音箱等。

它们可以将计算机处理后的结果传递给用户或外界的其他设备。

第五部分:控制器(Control Unit)控制器是CPU中的一个单元,它负责控制和协调计算机的工作流程。

控制器通过读取存储器中的指令并按照指令依次执行,从而完成各种任务。

控制器还可以控制数据的输入输出,并根据需要修改存储器中的数据。

综上所述,中央处理器、存储器、输入设备、输出设备和控制器是计算机五大部件,也是冯诺依曼型体系结构的核心组成部分。

第6章中央处理器(终)

第6章 中央处理器

本章学习内容

• 6.1中央处理器的功能和组成 • 6.2 控制器的组成和实现方法 • 6.3 时序系统与控制方式 • 6.4 微程序控制原理 • 6.5 控制单元的设计 • 6.6 流水线技术 • 6.7 精简指令系统计算机RISC

4

第6章 中央处理器

本章学习要求

• 理解:CPU的功能和主要寄存器

内频=外频×倍频

18

第6章 中央处理器

4.前端总线频率

前端总线通常用FSB表示,它是CPU和外界 交换数据的最主要通道,主要连接主存、显卡等 数据吞吐率高的部件,因此前端总线的数据传输 能力对计算机整体性能作用很大。

在Pentium 4出现之前,前端总线频率与外频 是相同的,因此往往直接称前端总线频率为外频。 随着计算机技术的发展,需要前端总线频率高于 外频,因此采用了QDR(Quad Date Rate)技术 或者其他类似的技术,使得前端总线频率成为外 频的2倍、4倍甚至更高。

CPU 的 字 长 是 指 在 单 位 时 间 内 同 时 处理的二进制数据的位数。CPU按照其处 理信息的字长可以分为:8位CPU、16位 CPU、32位CPU以及64位CPU等。

16

第6章 中央处理器

2.内部工作频率

内部工作频率又称为内频或主频,它是衡

量CPU速度的重要参数。在其他性能指标相同 时,CPU的主频越高,CPU的速度也就越快。 内部时钟频率的倒数是时钟周期,这是CPU中

pro、Pentium Ⅱ/Ⅲ每个时钟周期可以执行3条

或更多的指令。

17

第6章 中央处理器

3.外部工作频率

外部工作频率,也叫前端总线频率或系统 总线时钟频率,它是由主板为CPU提供的基准 时钟频率。由于正常情况下,CPU总线频率和 主存总线频率相同,所以也是CPU与主存交换 数据的频率。

计算机原理cpu课程设计

计算机原理 cpu课程设计一、教学目标本节课的教学目标是让学生了解和掌握计算机CPU的基本原理和组成结构,包括中央处理器(CPU)的功能、架构、工作原理及其在计算机系统中的重要性。

知识目标要求学生能够描述CPU的主要组成部分,如控制单元、算术逻辑单元(ALU)、寄存器等,并理解它们的作用。

技能目标则要求学生能够通过实验或模拟软件,观察和分析CPU的工作过程,提升学生的实际操作能力和问题解决能力。

情感态度价值观目标则是培养学生对计算机科学的好奇心和探索精神,增强学生对技术进步的认同感,同时培养学生的团队合作意识。

二、教学内容本节课的教学内容将围绕CPU的原理与结构展开。

首先,介绍CPU在计算机系统中的核心地位及其重要性。

接着,详细讲解CPU的组成,包括控制单元、ALU、寄存器等关键部件的功能和作用。

然后,通过实例分析CPU的工作流程,即 fetch-decode-execute 循环,让学生理解指令的执行过程。

最后,讨论CPU性能指标,如时钟频率、指令周期、流水线技术等,并介绍多核处理器的基本概念。

三、教学方法为了提高教学效果,将采用多种教学方法相结合的方式进行教学。

首先,采用讲授法向学生介绍CPU的基本概念和原理。

其次,通过案例分析法,分析具体的CPU工作实例,让学生更直观地理解CPU的工作过程。

再次,利用实验法,让学生在实验室中实际操作CPU模拟软件,亲身体验CPU的工作原理。

最后,课堂讨论,鼓励学生提出问题、分享心得,以提高学生的主动性和参与度。

四、教学资源为了支持教学,将准备丰富的教学资源。

主要教材为《计算机组成原理》,辅助教材包括《计算机科学概论》等。

参考书籍将提供更深入的理论知识,如《深入理解计算机系统》。

多媒体资料将包括教学PPT、视频动画等,以形象直观的方式展示CPU的工作原理。

实验设备包括CPU模拟器软件和必要的计算机硬件,供学生进行实验操作,增强实践体验。

五、教学评估为了全面、客观地评估学生的学习成果,将采用多种评估方式。

CPU设计

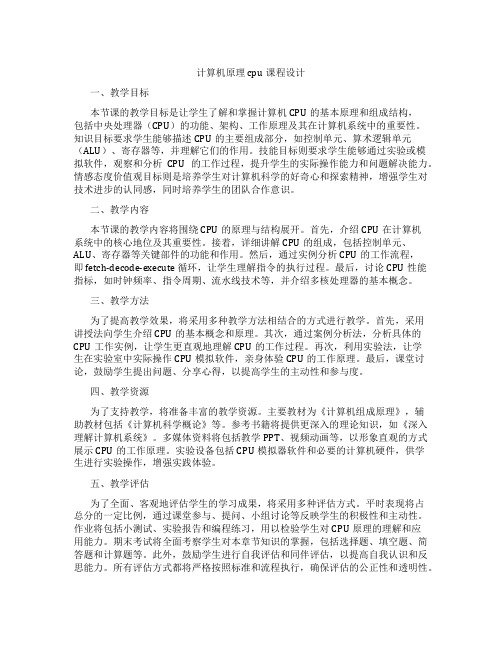

作业:10、解:对非常简单CPU增加了一条CLEAR指令后的新的状态图如下:其RTL代码如下:FETCH1:AR PCFETCH2:DR M, PC PC+1FETCH3:IR DR[7..6], AR DR[5,0]ADD1:DR MADD2:AC AC+DRAND1:DR MAND2:AC AC^DRJMP :PC DR[5..0]R5 :DR[5] 1 或DR[5] 0INC :AC AC+1CLEAR:AC 011、解:一、确定CPU的用途以下设计的CPU是要用来执行取反运算、加法运算、逻辑或运算、减法运算这四条指令的,而且该CPU能够访问64个字的存储器,每个字为8位宽。

字长:8位D[7....0]寻址范围:64Btye ,2^6=64,A[5....0]二、确定ISA1、程序员可访问的寄存器在下表中,为了完成COM , JREL , OR 和SUB1这四条指令,显然我们只需用到一个通用寄存器AC——8位累加器就可以实现。

指令操作码操作COM 00XX XXXX AC AC' (取反)JRET 01AA AAAA PC PC+00AA AAAAOR 10AA AAAA AC AC^M[00AA AAAA]SUB1 11AA AAAA AC AC—M[00AA AAAA]—12、CPU还需要一些其他的寄存器以便完成取指令(或数据)、译码和执行指令所必须的内部操作,最基本的寄存器有:AR(地址寄存器)——6位,由A[5.....0]向存贮提供地址PC (程序计数器)——6位,指出下一条指令的地址DR(数据寄存器)——8位,通过D[7....0]从存贮器接受指令和数据IR(指令寄存器)——2位,存放从存贮器中取回的指令的操作码部分。

三、为CPU设计状态图为了确定CPU的状态图,需对每条指令作如下分析:1、从存贮器取出指令(所有指令都相同)2、指令译码3、指令执行从存贮器中取出指令:1、原理:根据冯. 诺依曼型机的原理(指令在存贮器中按顺序存放.......), 在CPU能执行指令之前,它必须将这条指令从存贮中取出,CPU通过执行如下的操作序列完成这个任务的:【1】选择存贮单元由A[5... 0]确定【2】对A[5... 0]译码、延迟、并向存贮器发一个信号(如READ或R/W'=1),使存贮器将此指令输出到它的输出引脚。

计算机组成原理CPU设计

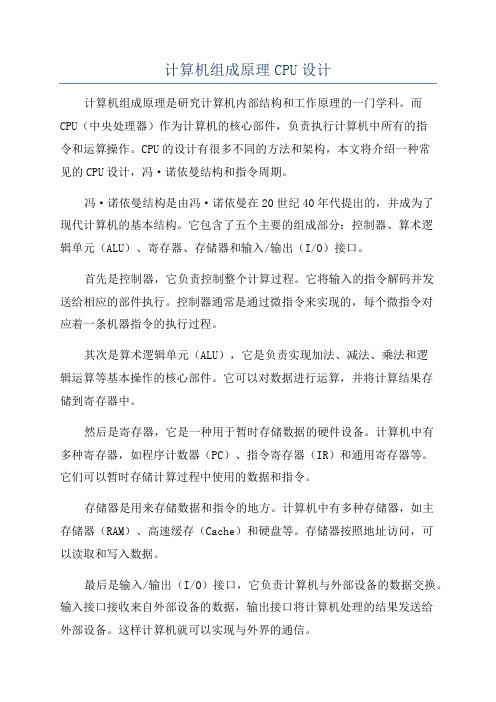

计算机组成原理CPU设计计算机组成原理是研究计算机内部结构和工作原理的一门学科。

而CPU(中央处理器)作为计算机的核心部件,负责执行计算机中所有的指令和运算操作。

CPU的设计有很多不同的方法和架构,本文将介绍一种常见的CPU设计,冯·诺依曼结构和指令周期。

冯·诺依曼结构是由冯·诺依曼在20世纪40年代提出的,并成为了现代计算机的基本结构。

它包含了五个主要的组成部分:控制器、算术逻辑单元(ALU)、寄存器、存储器和输入/输出(I/O)接口。

首先是控制器,它负责控制整个计算过程。

它将输入的指令解码并发送给相应的部件执行。

控制器通常是通过微指令来实现的,每个微指令对应着一条机器指令的执行过程。

其次是算术逻辑单元(ALU),它是负责实现加法、减法、乘法和逻辑运算等基本操作的核心部件。

它可以对数据进行运算,并将计算结果存储到寄存器中。

然后是寄存器,它是一种用于暂时存储数据的硬件设备。

计算机中有多种寄存器,如程序计数器(PC)、指令寄存器(IR)和通用寄存器等。

它们可以暂时存储计算过程中使用的数据和指令。

存储器是用来存储数据和指令的地方。

计算机中有多种存储器,如主存储器(RAM)、高速缓存(Cache)和硬盘等。

存储器按照地址访问,可以读取和写入数据。

最后是输入/输出(I/O)接口,它负责计算机与外部设备的数据交换。

输入接口接收来自外部设备的数据,输出接口将计算机处理的结果发送给外部设备。

这样计算机就可以实现与外界的通信。

指令周期是CPU执行一条机器指令的时间周期。

它通常包括取指令、译码、执行、访存和写回这五个阶段。

在取指令阶段,控制器从存储器中读取指令并保存到指令寄存器中;在译码阶段,控制器对指令进行解码,并根据指令的类型决定下一步的操作;在执行阶段,ALU根据控制器的指令进行运算操作;在访存阶段,控制器根据指令的要求将数据从存储器中读取或写入;最后在写回阶段,将计算结果写回到寄存器中或存储器中。

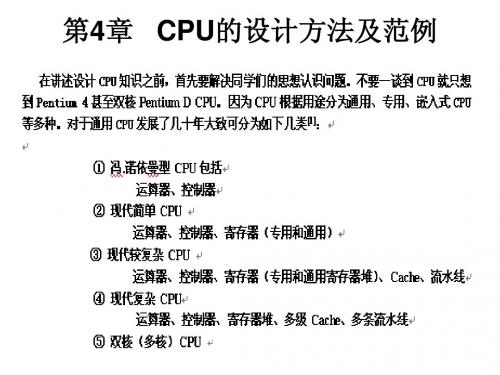

第4章 CPU的设计方法及范例

非常简单CPU不具有应用价值,仅用来说明 设计过程。不过,只要我们能正确设计出只有4条 指令的CPU,就可以设计出拥有40条指令的CPU, 甚至更多·· ·。难道这样还有怀疑吗?当然不能期 望马上就有创新,但这个CPU是拥有自主知识产 权的。或者有些同学会这样想,我以后并非从事 硬件的工作,更不可能从事设计CPU的专业,我 也相信这是事实。但是,这绝对有利于我们掌握 计算机的工作原理,也有利于从事各种软、硬件 开发和计算机科学等领域的研究、教学工作。

图4.9 通用CPU的状态图

其实CPU就是一个复杂的有限状态机 【冯· 诺依曼机的理论是基于图灵(Turing) 机理论的,而图灵机就是一个有限状态 机】。通过确定状态及其对应的微操作, 就可明确CPU为了取数据(或指令),指 令译码和执行指令集中每一条指令所必须 要完成的步骤。 问题:什么是图灵机理论?

1966年美国计算机协会设立“图灵奖”,被视为计算机科学界的最高荣誉

它的“纸带”相当于作业薄,读写头相当于人的眼 睛、手、笔,对于输入集{x1,x2,…xn},r(i, 0)= xi,i= 1,2,..n相当于“抄题”,而映射f 的读写变换相当于人脑判断确定下一步的行为且 指挥手和笔如何去动作和书写。它高度概括地回 答了什么是运算,不但为计算复杂度理论提供了 研究工具,而且为20世纪50年代计算机的设计提 供了思想基础,即Moore机和Mealy机。【注:当 出现状态Sy或Sn时,即得到了Turing 机的运算结 论Yes或No,这时即S(t)∈{ Sy,Sn }时停机】

二、建立数据通路的原理和方法

1.存贮器数据通路的原理

2.CPU内部的数据通路(两种不同的方案)

三、CPU内部寄存器控制信号的定义和确定方法

2.决定每个部件应完成的功能(详见图4.14)

cpu课程设计

cpu 课程设计一、教学目标本课程的目标是让学生了解和掌握CPU的基本原理和架构,包括其功能、组成和运作方式。

通过课程学习,学生应能理解CPU与其他计算机组件的关系,并能够分析CPU的性能指标。

此外,课程还将培养学生的动手能力,通过实验操作,使学生能够独立搭建简单的CPU模型,并理解其工作原理。

在情感态度价值观方面,学生应通过学习感受到计算机科学的魅力,增强对CPU技术的兴趣和好奇心,激发其探索和创新的精神。

二、教学内容教学内容将围绕CPU的基本概念、原理和架构展开。

首先,介绍CPU的定义和功能,让学生明白CPU在计算机中的重要性。

接着,详细讲解CPU的各个组成部分,如控制单元、算术逻辑单元、寄存器等,并通过实例分析,使学生能够理解这些组件是如何协同工作的。

然后,深入探讨CPU的运作机制,包括指令的执行过程、时钟周期、缓存管理等。

此外,课程还将介绍CPU的性能评价指标,如主频、缓存大小、多核处理等,并分析这些指标对计算机性能的影响。

三、教学方法为了提高教学效果,本课程将采用多种教学方法。

首先,通过讲授法,为学生提供CPU的基本概念和原理。

其次,通过案例分析法,让学生通过分析实际案例,深入理解CPU的工作原理。

此外,课程还将采用实验法,让学生亲自动手,搭建CPU模型,增强其对CPU运作机制的理解。

在课堂上,教师还将引导学生进行讨论,鼓励学生提出问题,培养学生的思考能力和解决问题的能力。

四、教学资源为了支持教学内容的实施,我们将准备丰富的教学资源。

教材方面,我们将选择内容全面、结构清晰的教材,为学生提供系统的学习材料。

参考书方面,我们将推荐一些经典的CPU技术书籍,供学生深入研究。

多媒体资料方面,我们将制作生动的PPT和教学视频,帮助学生更好地理解CPU的运作原理。

实验设备方面,我们将准备充足的实验器材,确保每个学生都能亲自动手进行实验。

五、教学评估为了全面评估学生的学习成果,我们将采用多元化的评估方式。

CPU与简单模型机设计实验

CPU与简单模型机设计实验CPU(中央处理器)是计算机中的核心部件,负责执行指令和处理数据。

而简单模型机设计实验是指通过设计和实现一个简单的模型机,来体验计算机工作原理和计算机体系结构。

在这样一个实验中,我们可以从以下几个方面来详细讨论CPU与简单模型机设计实验。

1.CPU的基本组成CPU是由控制单元(CU)和算术逻辑单元(ALU)两个主要部分组成。

控制单元负责解析指令、获取数据和控制数据的流动,而算术逻辑单元则负责执行算术和逻辑运算。

在简单模型机设计实验中,我们需要设计和实现这两个组件,同时还需要考虑其他辅助组件,如寄存器和存储器等。

这些组件的设计和实现将直接影响CPU的性能和功能。

2.指令集架构设计CPU的指令集架构是指CPU所支持的指令集合和指令的格式。

指令集架构的设计需要考虑到计算机的功能需求、指令的执行效率以及编程的便利性等因素。

在简单模型机设计实验中,我们可以定义一些基本的指令,如加载数据、执行运算、存储数据等。

指令的编码格式可以采用二进制或者其他适合的方式。

通过设计和实现这些指令,我们可以模拟CPU对指令的解析和执行。

3.流水线设计流水线是指将CPU的指令和数据处理过程划分成若干个阶段,并同时在不同阶段处理多条指令。

流水线设计可以提高CPU的性能和效率。

在简单模型机设计实验中,我们可以考虑将指令执行过程划分为取指、解码、执行、访存和写回等阶段,并同时处理多条指令。

通过设计和实现这样的流水线,可以提高CPU的吞吐量和并行处理能力。

4.性能评估和优化在CPU和简单模型机设计实验中,我们可以进行性能评估和优化。

性能评估可以通过测量CPU的时钟周期、执行指令的速度和吞吐量等指标来进行。

而优化则可以通过改进指令设计、优化算法和增加硬件资源等方式来完成。

在简单模型机设计实验中,我们可以通过调整指令的执行顺序、使用更高效的算法和增加硬件资源来优化设计。

这些优化将直接影响CPU的性能和效率。

计算机组成原理课程设计(中央处理器--微程序控制器设计)

“计算机组成原理”课程设计报告微程序控制器的设计一、设计思路按照要求设计指令系统,该指令系统能够实现数据传送,进行加、减运算和无条件转移,具有累加器寻址、寄存器寻址、寄存器间接寻址、存储器直接寻址、立即数寻址等五种寻址方式。

从而可以想到如下指令: (1)24位控制位分别介绍如下:位控制位分别介绍如下: XRD XRD :: 外部设备读信号,当给出了外设的地址后,输出此信号,从指定外设读数据。

定外设读数据。

EMWR EMWR:: 程序存储器EM 写信号。

写信号。

EMRD EMRD:: 程序存储器EM 读信号。

读信号。

PCOE PCOE:: 将程序计数器PC 的值送到地址总线ABUS 上。

上。

EMEN EMEN:: 将程序存储器EM 与数据总线DBUS 接通,由EMWR 和EMRD 决定是将DBUS 数据写到EM 中,还是从EM 读出数据送到DBUS DBUS。

IREN IREN:: 将程序存储器EM 读出的数据打入指令寄存器IR 和微指令计数器uPC uPC。

EINT EINT:: 中断返回时清除中断响应和中断请求标志,便于下次中断。

中断返回时清除中断响应和中断请求标志,便于下次中断。

ELP ELP:: PC 打入允许,与指令寄存器的IR3IR3、、IR2位结合,控制程序跳转。

转。

MAREN MAREN:将数据总线:将数据总线DBUS 上数据打入地址寄存器MAR MAR。

MAROE MAROE:将地址寄存器:将地址寄存器MAR 的值送到地址总线ABUS 上。

上。

OUTEN OUTEN:将数据总线:将数据总线DBUS 上数据送到输出端口寄存器OUT 里。

里。

STEN STEN:: 将数据总线DBUS 上数据存入堆栈寄存器ST 中。

中。

RRD RRD:: 读寄存器组读寄存器组R0-R3R0-R3,寄存器,寄存器R?R?的选择由指令的最低两位决定。

的选择由指令的最低两位决定。

的选择由指令的最低两位决定。

《计算机组成原理》6-CPU设计

6.1.2 CPU组成——CPU内部数据通路

CPU 运算器

寄存器

中断

系统

CU

时序系统

数

地

控

据

址

制

线

线

线

在确定一台计算机的总体结构的时候,主要考 虑这样以下问题:

设置哪些部件; 各部件间如何传递信息(即数据通路); 主机与外围设备之间如何实现信息传送; 如何形成微操作命令序列。 前三个问题于机器指令系统设计有密切的关系; 后一个问题涉及到设计策略,其中,数据通路结构 是总体结构设计的核心。

但这种寄存器结构使所需单元器件与连接线增多, 不利于集成度的提高。

6.1.2 CPU组成——CPU典型内部数据通路

M

移位器

D R

ALU

RN

...

锁存器

锁存器

R2

M A

R1

R

IR

PC

状

CU

…

态 信

时钟

…

息

控制信号

3)单组内总线、集成寄存器结构。为了提高寄存 器的集成度,常将寄存器组制作成为小型半导体存储 器结构,一个存储单元就相当于一个寄存器。

6.1.2 CPU组成——CPU典型内部数据通路

2)单组内总线、分立寄存器结构。它的特点是 寄存器分别独立设置,采用一组单向的数据总线, 以ALU为内部数据传送通路的中枢。由于各寄存器在 物理上彼此分立,它们的输出端均与ALU输入端的多 路选择器相连(MAR除外因为它的特殊作用使得它 只能接收地址,传送给主存),多路选择器可以采 用与或逻辑,在同一时刻最多可以选择两路输入, 送入ALU进行相应运算处理。寄存器的数据输入来自 CPU内部总线,由于寄存器彼此分离,只要发出相 应的同步打入脉冲,即可使内总线同时将数据打入 一个或多个寄存器。

8位CPU的设计

8位CPU的设计一、设计的任务与要求计算机的核心部件cpu通常包含运算器和控制器两大部分。

组成cpu的基本部件有运算部件,寄存器组,微命令产生部件和时序系统等。

这些部件通过cpu内部的总线连接起来,实现它们之间的信息交换。

1.设计目的(1).深入细致认知基本模型计算机的功能、共同组成科学知识;(2).深入细致自学计算机各类典型指令的继续执行流程;(3).自学微程序控制器的设计过程和有关技术,掌控lpm_rom的布局方法。

(4).在掌控部件单元电路实验的基础上,进一步将单元电路共同组成系统,结构一台基本模型计算机。

(5).定义五条机器指令,并编写相应的微程序,上机调试,掌握计算机整机概念。

掌握微程序的设计方法,学会编写二进制微指令代码表。

(6).通过熟识较完整的计算机的设计,全面介绍并掌控微程序控制方式计算机的设计方法。

2.设计原理在部件实验过程中,各部件单元的掌控信号就是人为演示产生的,而本实验将能够在微过程控制下自动产生各部件单元掌控信号,同时实现特定的功能。

实验中,计算机数据通路的掌控将由微过程控制器去顺利完成,cpu从内存中抽出一条机器指令至指令继续执行完结的一个指令周期,全部由微指令共同组成的序列去顺利完成,即为一条机器指令对应一个微程序。

11该cpu主要由算术逻辑单元alu,数据存贮寄存器dr1、dr2,数据寄存器r0~r2,程序计数器pc,地址寄存器ar,程序/数据存储器memoray,指令寄存器ir,微控制器uc,输出单元input和输入单元output所共同组成。

图中虚线框内部分包含运算器、控制器、程序存储器、数据存储器和微程序存储器等,量测时,它们都可以在单片fpga中同时实现。

虚线框外部分主要就是输出/输入装置,包含键盘、数码管、lcd显示器等,用作向cpu输出数据,或cpu向外输入数据,以及观测cpu内部工作情况及运算结果。

二、单元电路设计1、运算部件运算部件的任务就是对操作数展开加工处置。

冯诺依曼 计算机的运算器的种类

冯·诺伊曼建筑,又称冯·诺伊曼模型,类似于截肢者的大脑。

全部是拥有一个超智能的中央处理单元(CPU),由于它存储在记忆中的指示,它可以做一堆很酷的技巧。

CPU拥有一个算术逻辑单元(ALU)和一个控制单元,它们就像它自己的小动态二重奏,共同完成所有的数学和举重。

当它到冯·诺伊曼普特尔斯的算术逻辑单元类型时,有一大堆不同的设计。

有的用二进制压缩数字,有的用浮点数处理,有的甚至有特别的单位,仅仅用于制作酷酷的图形或者用密码学来保存秘密。

这是一个高科技的,电力厂包'一拳!在von Neumannpupers中,还有一个重要部分叫做控制单元。

就像"截肢者"的老板,负责从记忆中获取指令,找出他们的意思,确保他们及时完成。

控制单元与ALU合作,根据存储在内存中的指示,确保一切运行顺利。

当它到控制单元如何工作时,冯·诺伊曼普特斯使用不同的设计。

这里有使用特殊电路制造的硬线控制单元,还有使用微小指令序列控制一切的微程序控制单元。

控制单元设计的选择取决于诸如截肢者需要多快,指令有多复杂,以及花费多少。

在更广泛的背景下,冯·诺伊曼架构提供了利用各种算术逻辑单元和控制单元的机会,这些单元是针对截肢者系统的具体要求而设计的。

无论是涉及基本的算术操作,复杂的数学截图,还是专门的任务执行,冯·诺伊曼架构的适应性都支持部署各种形式的截图单位,以满足当代截图的多方面需求。

随着技术进步的继续推进,计算逻辑单元和控制单元的概念化和实施方面的新创新将持续推进在截肢和数据处理领域可实现的界限。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

三、微程序原理

四、微程序控制器设计

1.1 CPU的结构与功能

CPU的功能

取指令:具备从存储器中取出指令的功能

地址部件:解决指令地址的产生 指令部件:保存从存储器中取来的指令 分析指令:分析指令的操作性质,计算指令操作对象的位置(地 址) 译码部件:对指令进行译码 执行指令:实现指令的操作功能

指令周期

指令周期 取指周期:从存储器取出指令送指令寄存器 取数周期:计算操作数有效地址,取出操作数; 执行周期:执行指令的功能

指令周期与机器周期、节拍周期的关系

同步控制方式下,指令周期包括多个(不一定固定)机器周期; 每个机器周期包括固定个数的节拍周期

2.1 控制方式与时序系统

计算机组成原理与汇编语言

(组成原理部分) 2000级

北航计算机学院 刘旭东

Tel :82316285,82317634 Mail:liuxd@

第五部分

CPU与控制单元设计

一、CPU的结构与功能

二、指令流程与组合逻辑控制器

三、微程序原理

四、微程序控制器设计

一、CPU的结构与功能 二、指令流程与组合逻辑控制器

M3.T1 M3.T2 M3.T3 M3.T4

IB Z

AB MAR, RD, W/B

MDR DB

CPMDR

2.2 指令流程与微操作时间表

结构图

时间节拍 M4.T1 执 行 周 期 M4.T2 M4.T3 M4.T4

完成功能 源操作数送AX

需要的微操作信号

IB MDR, WRGR, W/B

需要的控制脉冲 AX的地址

2.2 指令流程与微操作时间表

MOV 1000H[BX], AX 指令执行的微操作流程

指令长度:32位,分两次读取(指令代码:89870010H) 读取指令周期:机器周期M1内完成(读第一个16位) 读变址值周期:机器周期M2内完成

指令寄存器IR

指令译码器ID(Instruction Decoder)

时序部件:提供各种时序信号 控制信号生成部件:产生计算机其他部件所需要的所有微操作控 制信号。

中断系统

检查中断信号,中断CPU的正常程序执行,处理异常事务。

1.2 模型机结构

Control Bus Data Bus Address Bus

控制与状态寄存器:一般用户不可见,为系统控制专用,用户不 可直接使用。 MAR(Memory Address Register):存储器地址寄存器 MBR/MDR(Memory Buffer Register,Memory Data Register):存储器数据缓冲寄存器

PC(Program Counter):程序计数器,存放下一条指令的 地址

2.2 指令流程与微操作时间表

取指周期的微操作流程

取指流程需要4个节拍 指令地址送MAR

结构图

存储器读出指令 指令送MDR,并调整PC 指令送IR 每条指令执行过程的第一个机器周期M1都是取指周期(取到指令核心部分)

时间节拍 M1.T1 M1.T2 M1.T3 调整PC M1.T4 MDR(指令)送IR PC+1 IB MDR CPPC CPIR 完成功能 指令地址送MAR Read Memory 指令送MDR 需要的微操作信号 IB PC

CPMDR

CPPC CPIR CPC, BX地址 AX地址

执 行 周 期

M2.T1 M2.T2 M2.T3 M2.T4

2.2 指令流程与微操作时间表

MOV AX,1000H[BX] 指令执行的微操作流程

指令长度:32位,分两次读取(指令代码:8B870010H) 读取指令周期:机器周期M1内完成(读第一个16位) 读变址值周期:机器周期M2内完成

取数:计算操作数地址,读取操作数,要根据操作数的来源与寻址 方式才能确定具体的操作过程。

执行:执行并送结果。

取指周期

指令的核心部分占16Bits,机器字长16Bits,每一次从存储器能读 取16Bits 指令编码长度有2个字节(16位),4个字节(32位),甚至6个字 节,但指令核心部分长度为16位。 取指周期特指读取指令核心部分(16Bits)的周期,所以在这种前 题下,所有指令的取指周期是完全一样的。

结构图

取操作数周期:机器周期M3内完成 执行周期:机器周期M4内完成

时间节拍 完成功能 需要的微操作信号 需要的控制脉冲

M1.T1

取 指 周 期 M1.T2 M1.T3

指令地址送MAR

Read Memory

IB PC

AB MAR, RD, W/B

CPMAR

指令送MDR

调整PC M1.T4 MDR(指令)送IR

译码部件:指令译码器(ID)

控制部件:微操作控制信号产生部件 时序部件:产生时序信号 中断系统:处理异常事务 内部总线:CPU内部数据通路(Internal Bus)

1.1 CPU的结构与功能

CPU内部结构 执行单元 控制单元 寄存器单元

ALU 控制信号

中断系统 CU

微操作控制信号

IR(Instruction Register):指令寄存器,存放当前执行的指 令编码

1.1 CPU的结构与功能

执行单元(EU-Execution Unit)

执行单元的核心:算术逻辑运算单元(ALU),完成算术运算、 逻辑运算、移位运算等操作;

寄存器:提供数据缓冲;

控制单元(CU-Control Unit)

MDR DB

PC+1 IB MDR

CPMDR

CPPC CPIR

2.2 指令流程与微操作时间表

时间节拍 M2.T1

取 变 址 值

结构图

完成功能 PC送MAR

从存储器读取1000H

1000H送MDR

需要的微操作信号 IB PC

AB MAR, RD, W/B

需要的控制脉冲 CPMAR

M2.T2

AB MAR, RD, W/B

需要的控制脉冲 CPMAR

MDR DB

CPMDR

2.2 指令流程与微操作时间表

MOV AX,BX 指令执行的微操作流程

指令长度:16位,一次可读取完毕(指令代码:89DBH) 读取指令周期:机器周期M1内完成 执行周期:机器周期M2内完成

时间节拍 完成功能 需要的微操作信号

控制信号:根据指令的操作性质和操作对象的地址,产生一 系列的微操作控制信号,从而控制计算机的运算器、存储器 或输入输出接口等部件,实现指令所表示的功能。

1.1 CPU的结构与功能

CPU的结构

运算器:算术逻辑运算单元(ALU) 寄存器:通用计算机(GR),标志寄存器(FR,又称程序状态字 PSW) 控制单元(CU): 指令部件:指令寄存器(IR)

结构图

需要的控制脉冲

M1.T1

取 指 周 期 M1.T2 M1.T3

指令地址送MAR

Read Memory

IB PC

AB MAR, RD, W/B

CPMAR

指令送MDR

调整PC M1.T4 MDR(指令)送IR BX送暂存器C 暂存器C送AX 无操作 无操作

MDR DB

PC+1 IB MDR IB GR, RDGR, W/B IB C, WRGR, W/B

MDR->DB W/B DB->MDR

返回

微操作信号 C

CPC C->IB R W W/ D R B

MAR -> AB

MAR

CPMAR

MDR

CPMDR MDR->IB

MEMORY

控制 部件

Internal Bus

D->IB SAL SAR RDGR WRGR W/B CPZ Z -> IB

GR -> IB

PC->IB

AH BH CH DH SP BP SI DI

AL BL CL DL

D

A

CPD

PC

B

CPPC

时序 部件

译码电路

ADD SUB B-1

ALU

PC+1 CLPC

Z FR

IR

FR->IB

CPIR

GR Add

1.2 模型机结构

简化的8086/8088结构

16位系统

通用寄存器部件 主存地址寄存器MAR 主存数据寄存器MDR 暂存器C,D,Z 程序计数器PC 指令寄存器IR

M2.T3

MDR DB

CPMDR

调整PC

M2.T4 MDR(1000H)送D (BX)+1000H 送 Z 源操作数地址 Z 送MAR 读取源操作数 源操作数送MDR

PC+1

IB MDR

IB GR, RDGR, W/B, ADD

CPPC

CPD BX地址, CPZ CPMAR

取 数 周 期

Q D

Q

1

Q D

CLK

2.2 指令流程与微操作时间表

指令周期分析(针对模型计算机及其指令系统 而言)

取指周期的微操作流程 MOV指令的微操作流程 单操作数指令的微操作流程 双操作数指令的微操作流程

其他指令的微操作流程

2.2 指令流程与微操作时间表

指令的执行过程

取指:从存取器读取当前指令送到指令寄存器(IR),要根据指令 编码的长度才能确定读取指令的详细流程。

REG 000 001 010 011 100 101 110 111

W=1 AX CX DX BX SP BP SI DI

W=0 AL CL DL BL AH CH DH BH

1.3 模型机的指令系统

双操作数指令格式