微机组成原理2

微机原理第二章习题答案

2.11

• 一本以ASCII码编码的300页的小说,按 57.6 Kbps的速率需要传输多长时间?

– T=8bit/字符*3500字符/页*300页/57.6 Kbps≈146秒

2.12

• 一个存储器的容量为4 MB,每个单元可以 存放一个字节,那么其最大地址的十六进 制表示是什么?

– 因为4MB=222,所以若存储单元从00000H开始 编址,则其最大地址为3FFFFFH。

2.20

• 某系统总线的一个存取周期最快为3个总线 时钟周期,在一个总线周期中可以存取32 位数据。若总线的时钟频率为8.33 MHz, 则总线的带宽为多少MBps?

– 总线带宽= 32bit × 8.33MHz × 1 ÷ 8bit / Byte = 11.11MBps

3

13

总线带宽

总线带宽(bus band width) 表示单位时间内总线能 传送的最大数据(bit)量,因此可以用

– 优点:全互锁方式可靠性高,适应性强,传输 距离长。

– 缺点:比同步效率低,握手控制电路复杂,交 互的网络过程会影响系统工作速度,且速度难 以提高。

2.18

• 半同步总线怎样实现总线

联络?什么是零等待?

– 采用CLK和WAIT两个控制 信号;

– 系统在收发双方速度基本匹 配的情况下由CLK信号进行 同步;

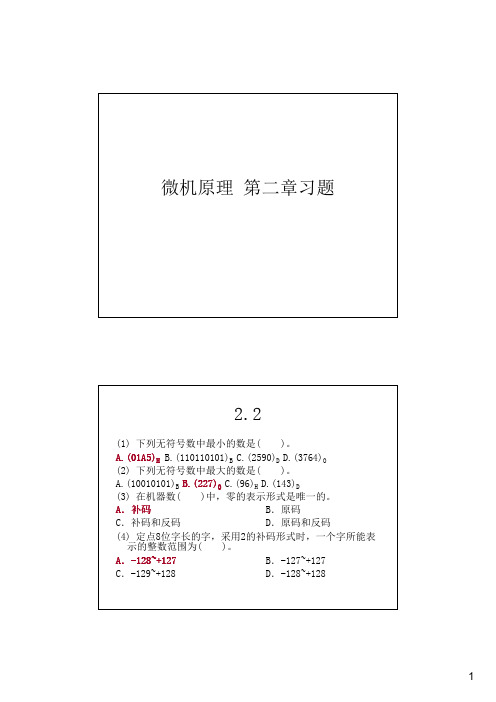

A.11001011

B.11010110

C.11000001

D.11001001

(6) 单纯从理论出发,计算机的所有功能都可以交给硬件实 现。而事实上,硬件只实现比较简单的功能,复杂的功能 则交给软件完成。这样做的理由是( BCD )。

A.提高解题速度

B.降低成本

C.增强计算机的适应性,扩大应用面

微机原理(杭州电子科技大学【4】8086系统结构[2-3]

![微机原理(杭州电子科技大学【4】8086系统结构[2-3]](https://img.taocdn.com/s3/m/3b8cd1f4f90f76c661371a65.png)

15:28

22

二、系统的复位与启动

【8086CPU时序】

① 复位信号:通过RESET引脚上的触发信号来引起8086系统复位和启

动,RESET至少维持4个时钟周期的高电平。

② 复位操作:当RESET信号变成高电平时,8086/8088CPU结束现行

操作,各个内部寄存器复位成初值。

标志寄存器

清零

指令寄存器 CS寄存器 DS寄存器 SS寄存器 ES寄存器

的比例倍频后得到CPU的主频,即: CPU主频 = 外频 × 倍频系数

⑥ PC机各子系统时钟(存储系统,显示系统,总线等)是由系统频率按 照一定的比例分频得到。

15:28

5

内频 550MHz Pentium III

倍频系数5.5

L1 Cache

L2 550MHz Cache

处理机总线 100MHz

微机原理与接口技术

第四讲

15:28

第二章 8086系统结构

内容提要

z微型计算机的发展概况 z8086CPU内部结构 z8086CPU引脚及功能 z8086CPU存储器组织 z8086CPU系统配置 z8086CPU时序

15:28

2

※有关概念介绍

z 主频,外频,倍频系数 z T状态 z 总线周期 z 指令周期 z 时序 z 时序图

总线操作

读存储器操作 (取操作数)

写存储器操作 (将结果存放到内存)

读 I/O 端口操作 (取 I/O 端口中的数)

写 I/O 端口操作 (往 I/O 端口写数)

中断响应操作

总线周期

存储器读周期 存储器写周期 I/O 端口读周期 I/O 端口写周期 中断响应周期

15:28

微机原理-第6章(2)

四.扩展存储器设计

Note:8086 CPU同8088 CPU一样,也有20条地址总线,其寻 8086 CPU同 CPU一样 也有20条地址总线, 一样, 20条地址总线 址能力达1MB。不同之处是8086 数据总线是16位的, 16位的 址能力达1MB。不同之处是8086 CPU 数据总线是16位的, 与8086 CPU对应的1MB存储空间可分为两个512kB(524 288 CPU对应的1MB存储空间可分为两个512kB(524 对应的 存储空间可分为两个512 B)的存储体。其中一个存储体由奇地址的存储单元(高字节) B)的存储体。其中一个存储体由奇地址的存储单元(高字节) 的存储体 奇地址的存储单元 组成,另一个存储体由偶地址的存储单元(低字节)组成。 组成,另一个存储体由偶地址的存储单元(低字节)组成。 偶地址的存储单元 前者称为奇地址的存储体,后者称为偶地址的存储体。 前者称为奇地址的存储体,后者称为偶地址的存储体。

≈

0

≈ ≈

0 0

0

0

0

0

0

0

0 1…1

作片外寻址的高位不变地址线全部 参加了译码,这种译码方法称为全 参加了译码,这种译码方法称为全 地址译码方法 方法。 地址译码方法。

片外寻址

四.扩展存储器设计

A19 A18 A17 A16 A15 A14 A13 A12 A11 A10 A9~A0 X 0 0 0 0 0 0 0 0 0 0…0

4KB 00000H 00FFFH

≈

●

模块1 模块

微机原理第2章课后答案

第2章8086微处理器及其系统教材习题解答1. 8086 CPU 由哪两部分构成,它们的主要功能是什么?在执行指令期间,EU 能直接访问存储器吗,为什么?【解】8086CPU由执行部件(EU)和总线接口部件(BIU)两部分组成。

执行部件由内部寄存器组、算术逻辑运算单元(ALU)与标志寄存器(FR)及内部控制逻辑等三部分组成。

寄存器用于存储操作数和中间结果;算术逻辑单元完成16位或8位算术逻辑运算,运算结果送上ALU内部数据总线,同时在标志寄存器中建立相应的标志;内部控制逻辑电路的主要功能是从指令队列缓冲器中取出指令,对指令进行译码,并产生各种控制信号,控制各部件的协同工作以完成指令的执行过程。

总线接口部件(BIU)负责CPU与存储器、I/O设备之间传送数据、地址、状态及控制信息。

每当EU部件要执行一条指令时,它就从指令队列头部取出指令,后续指令自动向前推进。

EU要花几个时钟周期执行指令,指令执行中若需要访问内存或I/O设备,EU就向BIU 申请总线周期,若BIU总线空闲,则立即响应,若BIU正在取一条指令,则待取指令操作完成后再响应EU的总线请求。

2. 8086CPU与传统的计算机相比在执行指令方面有什么不同?这样的设计思想有什么优点?【解】8086 CPU与传统的计算机相比增加了指令队列缓冲器,从而实现了执行部件(EU)与总线接口(BIU)部件的并行工作,因而提高了8086系统的效率。

3. 8086 CPU 中有哪些寄存器,各有什么用途?【解】8086共有8个16位的内部寄存器,分为两组:①通用数据寄存器。

四个通用数据寄存器AX、BX、CX、DX均可用作16位寄存器也可用作8位寄存器。

用作8位寄存器时分别记为AH、AL、BH、BL、CH、CL、DH、DL。

AX(AH、AL)累加器。

有些指令约定以AX(或AL)为源或目的寄存器。

实际上大多数情况下,8086的所有通用寄存器均可充当累加器。

BX(BH、BL)基址寄存器。

微机原理 第四章2

静态RAM的结构组成原理图 静态RAM的结构组成原理图 RAM 举例:其存储体为64*64=4096个 举例:其存储体为64*64=4096个6管静态存储电路组成 64*64=4096

静态RAM 静态RAM

常用的SRAM芯片有2114、2142( 常用的SRAM芯片有 SRAM芯片有2114 )、6116(2K× 6116 6264(8K× )、62128 16K× )、62256 32K× 62128( 62256( 6264(8K×8)、62128(16K×8)、62256(32K×8)等。 SRAM芯片 芯片2114 1、SRAM芯片2114 2114芯片容量为 芯片容量为1 18引脚DIP封装 引脚DIP封装。 Intel 2114芯片容量为1K×4位,为18引脚DIP封装。该芯片 共有10根地址线A 10根地址线 根数据线I/O 共有10根地址线A9~A0和4根数据线I/O4~I/O1。该芯片的读 写控制:无效时,数据线呈高阻;有效时选中芯片, 写控制:无效时,数据线呈高阻;有效时选中芯片,允许读 写操作,此时,若有效则进行写操作,无效时进行读操作。 写操作,此时,若有效则进行写操作,无效时进行读操作。

随机存取存储器(RAM) 随机存取存储器(RAM)

行线X 行线 +5V

6管静态RAM存储电路 管静态RAM存储电路 RAM (MOS) )

T3 T5 A

T4 B T6

T1

T2

T7 1 写控制 数据线 读控制 3 2

T8 列线Y 列线

读出信息: 非破坏性读出” 读出信息:“非破坏性读出” Out

NDRO—Non Destructive Read

3管动态基本存储电路

1、DRAM芯片2116 DRAM芯片2116 芯片 2116为单管动态RAM芯片。其存储容量为16 RAM芯片 16K Intel 2116为单管动态RAM芯片。其存储容量为16K×l位, 需用14条地址输入线,但2116只有16条引脚。由于受封装引 需用14条地址输入线, 2116只有16条引脚。 14条地址输入线 只有16条引脚 线的限制,只用了A 条地址输入线,数据线只有1 线的限制,只用了A6~A0 7条地址输入线,数据线只有1条 (1位 而且数据输入( 和输出( 端是分开的, (1位),而且数据输入(DIN)和输出(DOUT)端是分开的,它们有 各自的锁存器。数据输入( 和输出( 各自的锁存器。数据输入(DIN)和输出(DOUT)线可通过外部电 路形成一个双向数据线。 路形成一个双向数据线。写允许信号为低电平时表示允许写 入,为高电平时可以读出,它需要3种电源。 为高电平时可以读出,它需要3种电源。

微机原理课件第二章 8086系统结构

但指令周期不一定都大于总线周期,如MOV AX,BX

操作都在CPU内部的寄存器,只要内部总线即可完成,不 需要通过系统总线访问存储器和I/O接口。

2021/8/17

17

• 8086CPU的典型总线时序,充分体现了总 线是严格地按分时复用的原则进行工作的。 即:在一个总线周期内,首先利用总线传 送地址信息,然后再利用同一总线传送数 据信息。这样减少了CPU芯片的引脚和外 部总线的数目。

• 执行部件(EU)

• 功能:负责译码和执行指令。

2021/8/17

5

• 联系BIU和EU的纽带为流水指令队列

• 队列是一种数据结构,工作方式为先进先出。写入的指令 只能存放在队列尾,读出的指令是队列头存放的指令。

2021/8/17

6

•BIU和EU的动作协调原则 BIU和EU按以下流水线技术原则协调工作,共同完成所 要求的任务: ①每当8086的指令队列中有空字节,BIU就会自动把下 一条指令取到指令队列中。 ②每当EU准备执行一条指令时,它会从BIU部件的指令 队列前部取出指令的代码,然后译码、执行指令。在执 行指令的过程中,如果必须访问存储器或者I/O端口, 那么EU就会请求BIU,完成访问内存或者I/O端口的操 作; ③当指令队列已满,且EU又没有总线访问请求时,BIU 便进入空闲状态。(BIU等待,总线空操作) ④开机或重启时,指令队列被清空;或在执行转移指令、 调用指令和返回指令时,由于待执行指令的顺序发生了 变化,则指令队列中已经装入的字节被自动消除,BIU会 接着往指令队列装入转向的另一程序段中的指令代码。 (EU等待)

•CF(Carry Flag)—进位标志位,做加法时最高位出现进位或 做减法时最高位出现借位,该位置1,反之为0。

微机原理第2章答案

第2章习题参考解答1.8086处理器内部一般包括哪些主要部分?8086处理器与其他处理器一样,其内部有算术逻辑部件、控制与定时部件、总线与总线接口部件、寄存器阵列等。

按功能结构可分为两部分,即总线接口单元(BIU)与执行单元(EU)。

BIU主要包括段寄存器、内部通信寄存器、指令指针、6字节指令队列、20位地址加法器和总线控制逻辑电路。

EU主要包括通用寄存器阵列、算术逻辑单元、控制与定时部件等。

2.什么是总线? —般微机中有哪些总线?所谓总线是指电脑中传送信息的一组通信导线,它将各个部件连接成—个整体。

在微处理器内部各单元之间传送信息的总线称为片内总线;在微处理器多个外部部件之间传送信息的总线称为片外总线或外部总线。

外部总线又分为地址总线、数据总线和控制总线。

随着电脑技术的发展,总线的概念越来越重要。

微机中常用的系统总线有PC总线、ISA总线、PCI总线等。

3.什么是堆栈?它有什么用途?堆栈指针的作用是什么?堆栈是一个按照后进先出的原则存取数据的部件,它是由栈区和栈指针组成的。

堆栈的作用是:当主程序调用子程序、子程序调用子程序或中断时转入中断服务程序时,能把断点地址及有关的寄存器、标志位及时正确地保存下来,并能保证逐次正确地返回。

堆栈除了有保存数据的栈区外,还有一个堆栈指针SP,它用来指示栈顶的位置。

假设是“向下生成”的堆栈,随着压入堆栈数据的增加,栈指针SP的值减少。

但SP始终指向栈顶。

4.在8086 CPU中,FR寄存器有哪些标志位?分别说明各位的功能。

8086 CPU中设置了一个16位的标志寄存器FR,其中用了9位,还有7位保留。

9位中有3位作为控制标志,6位作为状态标志。

IF:中断控制标志。

当IF=1时,允许可屏蔽中断请求;当IF=0时,禁止可屏蔽中断请求。

TF:单步运行标志。

当TF=1,单步运行;TF=0,连续运行程序。

DF:方向标志。

当DF=0,串操作时地址按增量修改;DF=1,地址按减量修改。

第2章微型计算机系统的组成及工作原理

2.5.6 ISA总线的定义与应用

2. ISA总线的信号线定义 ——98芯插槽,包括地址线、数据线、控制线、时钟和电源线 (1)地址线:SA019和LA1723 (2)数据线:SD015 (3)控制线:AEN、BALE、 IOR 和 IOW、 SMEMR和 SMEMW

MEMR 和 MEMW、 MEM CS16 和 I/O CS16 、SBHE

2.1.2 微机系统的软件配置

系统软件、工具软件、应用软件、用户应用程序

.3 微机系统中的信息流与信息链

1. 微机系统中信息流与信息链的构成 信息流:存储器中的数据、程序代码;接口寄存器中的I/O数据、 状态、I/O命令 信息链:信息流在系统中流动的路径; 包括物理(硬件)环节和逻辑(软件)环节 2. 微机系统中信息流与信息链 ——早期微机系统/现代微机系统中的信息链 3. 研究信息流与信息链的意义 ——通过信息流从整体上认识微机体系结构和组成微机系统的各 部件之间的关系

2.5.7 现代微机总线技术的新特点

3. 总线桥 (1) 总线桥 ——总线转换器和控制器,是两种不同总线间的总线接口 内部包含兼容协议及总线信号和数据缓冲电路;把一条总线映 射到另一条总线上 北桥:连接CPU总线和PCI总线的桥 南桥:连接PCI总线和本地总线(如ISA)的桥 (2) PCI总线芯片组 ——实现总线桥功能的一组大规模集成专用电路 保持主板结构不变前提下,改变这些芯片组的设计,即可适应 不同微处理器的要求 4. 多级总线结构中接口与总线的连接

2.4 I/O设备与I/O设备接口

2.4.1 I/O设备及其接口的作用

1. I/O设备的作用 2. I/O设备接口的作用——连接与转换

2.4.2 I/O设备的类型及设备的逻辑概念

微机原理第二版+田辉+课后答案

微机原理第⼆版+⽥辉+课后答案答:2 =1048576=1MB 习题1-1.微型计算机包括哪⼏个主要组成部分,各部分的基本功能是什么?答:微型计算机由CPU、存储器、输⼊/输出接⼝及系统总线组成。

CPU是微型计算机的核⼼部件,⼀般具有下列功能:进⾏算术和逻辑运算。

暂存少量数据。

对指令译码并执⾏指令所规定的操作。

与存储器和外设进⾏数据交换的能⼒。

提供整个系统所需要的定时和控制信号。

响应其他部件发出的中断请求;总线是计算机系统各功能模块间传递信息的公共通道,⼀般由总线控制器、总线发送器、总线接收器以及⼀组导线组成;存储器是⽤来存储数据、程序的部件;I/O接⼝是微型计算机的重要组成部件,在CPU 和外设之间起适配作⽤。

1-2.CPU 执⾏指令的⼯作过程。

答:取指令、执⾏指令。

指令执⾏的基本过程:(1)开始执⾏程序时,程序计数器中保存第⼀条指令的地址,指明当前将要执⾏的指令存放在存储器的哪个单元。

(2)控制器:将程序计数器中的地址送⾄地址寄存器MAR,并发出读命令。

存储器根据此地址取出⼀条指令,经过数据总线进⼊指令寄存器IR。

(3)指令译码器译码,控制逻辑阵列发操作命令,执⾏指令操作码规定的操作。

(4)修改程序计数器的内容。

1-3.果微处理器的地址总线为20 位,它的最⼤寻址空间为多少?201-4.处理器、微型计算机和微型计算机系统之间有什么关系?答:微处理器是微型计算机的核⼼部件。

微处理器配上存储器、输⼊/输出接⼝及相应的外设构成完整的微型计算机。

以微型计算机为主体,配上系统软件和外部设备以后,就构成了完整的微型计算机系统。

1-5.下⾯⼗进制数分别转换为⼆进制、⼋进制和⼗六进制数:128,65535,1024答:128,⼆进制:10000000B,⼋进制:200O,⼗六进制:80H65535,⼆进制:1111111111111111B,⼋进制:177777O,⼗六进制:FFFFH1024,⼆进制:10000000000B,⼋进制:2000O,⼗六进制:400H1-6.下⾯⼆进制数分别转换为⼗进制及⼗六进制数:1011.1010B,1111101.11 B答:1011.1010B,⼗进制:11.625,⼗六进制:B.AH1111101.11B,⼗进制:125.75,⼗六进制:7D.CH1-7.(5487)10=(0101010010000111)BCD=1010101101111 B若 CPU 的主时钟频率为 10MHz ,则⼀个时钟周期为10 s ,⼀个基本总线周期为 4× 1-8.设字长为 8 位,请写出下列数的原码、反码、补码和移码:15,-20,-27/32 答:[+15]原 =00001111, [+15]反 =00001111, [+15]补 =00001111, [+15]移 =10001111[-20]原 =10010100, [-20]反 =11101011, [-20]补 =11101100, [-20]移 =01101100[-27/32]原 =1.1101100, [-27/32]反 =1.0010011, [-27/32]补 =1.0010100,第 2 章微型计算机系统的微处理器习题2-1.086/8088 CPU 的功能结构由哪两部分组成?它们的主要功能是什么?答:8086/8088 CPU 的功能结构由以下两部分组成:总线接⼝单元BIU (Bus Interface Unit ),执⾏部件EU (Execution Unit )。

微机原理第2章习题与答案

习题一、选择题1.8086/8088CPU内部有一个始终指示下条指令偏移地址的部件是_______。

A. SPB.CSC.IPD.BP答案:C2. 指令队列的作用是_________。

A.暂存操作数地址B.暂存操作数C.暂存指令地址D.暂存预取指令答案:D3. 8086/8088下列部件中与地址形成无关的是______。

A. ALUB. 通用寄存器C. 指针寄存器D. 段寄存器答案:A4.对于8086,下列说法错误的是_______。

A.段寄存器位于BIU中B.20位的物理地址是在EU部件中形成的C.复位后CS的初值为FFFFHD.指令队列的长度为6个字节答案:B5.8086/8088中ES、DI分别属于_______。

A. EU、BIUB. EU、EUC. BIU、BIUD. BIU、EU答案:D6.BIU与EU工作方式的正确说法是_______。

A. 并行但不同步工作B.同步工作C. 各自独立工作D. 指令队列满时异步工作,空时同步工作答案:A7.在执行转移、调用和返回指令时,指令队列中原有的内容_______。

A.自动清除B.用软件清除C.不改变D.自动清除或用软件清除答案:A8.下列说法中,正确的一条是______A. 8086/8088标志寄存器共有16位,每一位都有含义。

B. 8088/8086的数据总线都是16位。

C. 8086/8088的逻辑段不允许段的重叠和交叉D. 8086/8088的逻辑段空间最大为64KB,实际应用中可能小于64KB。

答案:D9.8086/8088工作于最大模式,是因为_____。

A.可以扩展存储容量B.可以扩大I/O空间C.可以构成多处理器系统D.可以提高CPU主频答案:C10.8088/8086最大模式比最小模式在结构上至少应增加_____。

A.中断优先级控制器B.总线控制器C.数据驱动器D.地址锁存器答案:B11.组成最大模式下的最小系统,除CPU、时钟电路,ROM,RAM及I/O接口外,至少需增加的芯片类型为______。

微机原理第二章习题答案

1. 8086CPU内部由哪两部分组成?它们的主要功能?8086CPU由指令执行部件EU和总线接口部件BIU两部分组成。

EU完成指令译码和指令执行的工作,BIU是CPU与外部(存储器和I/O口)的接口,它提供了16位双向数据总线和20位地址总线,完成所有的外部总线操作。

具有地址形成、取指令、指令排队、读/写操作数、总线控制等功能。

2.8080CPU中有哪些寄存器?各有什么用途?答:8086CPU的寄存器有通用寄存器组、指针和变址寄存器、段寄存器、指令指针寄存器及标志位寄存器PSW。

4个16位通用寄存器,它们分别是AX,BX,CX,DX,用以存放16位数据或地址。

也可分为8个8位寄存器来使用,低8位是AL、BL、CL、DL,高8位是AH、BH、CH、DH,只能存放8位数据,不能存放地址。

指针和变址寄存器存放的内容是某一段内地址偏移量,用来形成操作数地址,主要在堆栈操作和变址运算中使用。

段寄存器给出相应逻辑段的首地址,称为“段基址”。

段基址与段内偏移地址结合形成20位物理地址。

指令指针寄存器用来存放将要执行的下一条指令在现行代码中的偏移地址。

16位标志寄存器PSW用来存放运算结果的特征,常用作后续条件转移指令的转移控制条件。

3.8086CPU与8088CPU的主要区别是什么?答:(1)8086的指令队列是6字节,8088是4字节;(2)8088与外部交换数据的总线宽度是8位,所以,对16位数的存储器读/写需要2个总线周期,8086是16位;AD~(3)8088外部数据总线只有8条,所以分时复用的地址/数据总线为7AD;(4)8088中,用IO/M信号代替M/IO;(5)8088中,不需要BHE信号。

4. 简要解释下列名词的意义。

CPU:中央处理单元CPU (Control Processing Unit)也称微处理器,是微型计算机的核心部件,由运算器ALU、控制器、寄存器组以及总线接口等部件组成。

主要完成各种运算,负责对整机的控制。

计算机组成原理和微机原理

计算机组成原理和微机原理计算机组成原理和微机原理是计算机科学与技术领域中非常重要的两门课程,它们涉及到计算机的硬件和软件方面的知识。

本文将详细介绍计算机组成原理和微机原理的概念、内容和重要性。

一、计算机组成原理的概念和内容计算机组成原理是计算机科学与技术领域中的基础课程之一,它主要研究计算机的硬件结构和工作原理。

计算机组成原理涉及到的内容很广泛,主要包括计算机的基本组成、计算机的运行过程、计算机的存储结构、计算机的输入输出系统等方面。

1.计算机的基本组成计算机的基本组成包括中央处理器(CPU)、存储器(memory)和输入输出设备(I/O devices)。

中央处理器是计算机的核心部件,负责执行计算机的指令和处理数据。

存储器用于存放程序和数据,可以分为主存储器(RAM)和辅助存储器(硬盘、光盘等)。

输入输出设备用于与计算机进行交互,如键盘、鼠标、显示器等。

2.计算机的运行过程计算机的运行过程包括指令的周期性执行和数据的处理。

在计算机中,每个指令都是由一系列的操作码(Opcode)和操作数(Operand)组成,其中操作码表示操作的类型,操作数表示操作的具体内容。

指令的周期性执行是通过时钟信号来实现的,时钟信号可以控制计算机的时序和同步。

3.计算机的存储结构计算机的存储结构主要包括主存储器和辅助存储器。

主存储器用于存放正在执行的程序和数据,是计算机运行的关键部件。

主存储器可以按照访问方式分为随机存取存储器(RAM)和只读存储器(ROM)等。

辅助存储器用于存放大量的程序和数据,可以分为硬盘、光盘、磁带等。

4.计算机的输入输出系统计算机的输入输出系统是计算机与外部世界进行交互的重要组成部分。

输入设备用于将外部的信息传递给计算机,如键盘、鼠标等;输出设备用于将计算机的结果显示给用户,如显示器、打印机等。

输入输出设备和计算机之间有一个接口(interface),可以通过接口进行数据的传输和控制。

二、微机原理的概念和内容微机原理是计算机科学与技术领域中的重要课程,它主要研究微型计算机的组成和工作原理。

微型计算机原理范文

微型计算机原理范文一、硬件原理1.数据传输:微型计算机通过数据总线、地址总线和控制总线来实现数据的传输。

数据总线用于传输数据信息,地址总线用于传输存储器或外设的地址,控制总线用于传输控制信号。

2.运算:中央处理器是微型计算机的核心组件,主要负责数据的处理和运算。

它由算术逻辑单元(ALU)和控制单元组成。

ALU用于进行算术和逻辑运算,控制单元用于控制指令的执行顺序。

3.存储:主存储器用于存储数据和程序。

它的存取速度较快,但容量较小。

微型计算机还可以连接辅助存储器,如硬盘、光盘和闪存,用于存储大量的数据和程序。

4.控制:微型计算机通过控制单元来控制指令的执行。

控制单元根据指令寄存器中的指令来产生相应的控制信号,实现指令的取指、译码、执行和访存等过程。

5.外围设备:微型计算机可以连接各种外围设备,如显示器、打印机、键盘、鼠标、扫描仪等。

它们通过输入输出端口与计算机系统进行通信。

二、软件原理1.系统软件:系统软件包括操作系统和语言处理程序等。

操作系统是微型计算机的核心软件,负责管理计算机的硬件资源和提供给应用软件的环境。

语言处理程序用于将高级语言转换为计算机可以执行的机器语言。

2.应用软件:应用软件包括各种办公软件、设计软件、娱乐软件等。

它们是根据用户需求来开发的,用于解决特定的实际问题。

三、微型计算机的工作原理1.初始化:当微型计算机通电时,控制单元首先从BIOS(基本输入输出系统)中读取并执行一段特定的程序,进行系统的初始化。

2.取指:控制单元从主存储器中按照程序计数器指定的地址读取指令,存放在指令寄存器中。

3.译码:控制单元对指令进行译码,确定指令的执行类型和操作对象。

4.执行:根据指令的类型和操作对象,控制单元产生相应的控制信号,使算术逻辑单元和主存储器执行相应的操作。

5.存取数据:微型计算机通过数据总线和地址总线将数据和地址传输到相应的部件,实现对数据的存取。

6.结果输出:微型计算机将运算结果通过数据总线和输出接口传输到相应的外围设备,如显示器或打印机。

微机原理 第2章_8086系统结构

8086 CPU的引脚及其功能

8086 CPU的两种工作模式

最小模式:用于单机系统,系统所需要的控 制信号由8086直接提供,MN/MX=1,CPU 工作于最小模式 最大模式:用于多处理机系统,系统所需的 控制信号由总线控制器8288提供, MN/MX=0,CPU工作于最大模式

8086 CPU在最小模式下的引脚定义 8088与8086的区别

通 用 寄 存 器

AX BX CX DX SP BP SI DI

8086 CPU结构框图

20位地址总线

Σ

数据 总线 16位

ALU数据总线 (16位) 暂存器

队列 总线 (8位)

CS DS SS ES IP 内部寄存器 指令队列

总线 控制 电路 8086 总线

ALU

标志寄存器

EU 控制器

1 3 4 5 6

PSW

存放状态标志、控制标志和系统标 志

PSW格式:

15 11 10

OF DF

9 IF

8

7

6

4 AF

2 PF

0 CF

TF SF ZF

状态标志

状态标志用来记录程序中运行结果的状态信息,它们根据有关指 令的运行结果由CPU自动设置,这些状态信息往往作为后续条件 转移指令的转移控制条件,包括6位: OF:溢出标志,在运算过程中,如操作数超出了机器数的表示范 围,称为溢出,OF=1,否则OF=0 SF:符号标志,记录结果的符号,结果为负SF=1,否则SF=0 ZF:零标志,运算结果为0,ZF=1,否则ZF=0 CF:进位标志,进行加法运算时从最高位产生进位,或减法运算 从最高位产生借位CF=1,否则CF=0 AF:辅助进位标志:本次运算结果,低4位向高4位产生进位或借 位,AF=1,否则AF=0 PF:奇偶标志,用来为机器中传送信息时可能产生的代码出错情 况提供检验条件,当结果操作数中低8位中1的个数为偶数时PF=1, 否则PF=0

微机组成原理

微机组成原理

微机组成原理是指微机中各个部件的相互关系和工作原理。

微机由中央处理器(CPU)、主存储器(RAM)、输入输出设

备(I/O)、系统总线等组件组成。

中央处理器是微机的核心部件,负责执行各种运算和控制指令。

它由运算器、控制器和寄存器组成。

运算器负责执行算术和逻辑运算,控制器负责解码指令并控制微机的操作步骤,寄存器则用于暂存指令和数据。

主存储器是用来存储微机运行时所需要的指令和数据的地方。

它主要有随机存取存储器(RAM)和只读存储器(ROM)两

种类型。

RAM可以读写,但是断电后数据会消失;ROM一般用来存储程序、固件等,不会因为断电而丢失。

输入输出设备负责实现微机与外部环境的信息交互。

常见的输入设备有键盘、鼠标、扫描仪等,输出设备有显示器、打印机等。

输入输出设备通过适配器或接口连接到系统总线上,实现与中央处理器之间的数据传输。

系统总线是微机各个部件之间进行数据传输的通道。

它分为地址总线、数据总线和控制总线三个部分。

地址总线用于传输指令和数据的地址信息,数据总线用于传输指令和数据,控制总线用于传输各种控制信号。

微机组成原理的核心思想是通过中央处理器对指令和数据的处理,实现计算、控制和存储等功能。

不同的部件通过系统总线

相互连接,共同完成微机的工作任务。

这种组成原理在现代计算机中得到广泛应用,使得微机可以实现各种复杂的任务和功能。

微机原理及应用课件第2章

四、内部寄存器

内部寄存器的类型

含14个16位寄存器,按功能可分为三类

8个通用寄存器 4个段寄存器 2个控制寄存器

深入理解:每个寄存器中数据的含义

28

1. 通用寄存器

数据寄存器(AX,BX,CX,DX) 地址指针寄存器(SP,BP) 变址寄存器(SI,DI)

29

数据寄存器

8088/8086含4个16位数据寄存器,它们又可分为8个 8位寄存器,即:

DX:

数据寄存器。在间接寻址的I/O指令中存放I/O端口地址;在 32位乘除法运算时,存放高16位数。

地址指针寄存器

SP:堆栈指针寄存器,其内容为栈顶的偏移地址; BP:基址指针寄存器,常用于在访问内存时存放内存单

元的偏移地址。

BP与BX的区别:

作为通用寄存器,二者均可用于存放数据; 作为基址寄存器,用BX表示所寻找的数据在数据段;用

┇

操作数

35

状态标志位(1)

CF(Carry Flag)

进位标志位。加(减)法运算时,若最高位有进(借)位则CF=1

OF(Overflow Flag)

溢出标志位。当算术运算的结果超出了有符号数的可表达范 围时,OF=l

ZF(Zero Flag)

零标志位。当运算结果为零时ZF=1

SF(Sign Flag)

欲实现对1MB内存空间的正确访问,每个内

存单元在整个内存空间中必须具备20位字长

的惟一地址

物理地址

XXXXXH

12H

00H

内存地址变换:

…

如何将直接产生的16位编码变换

…

为20位物理地址?

┇

内存单元的编址(1)

内存每个单元的地址在逻辑上都由两部分组成:

微机原理第2章 习题答案

第2章习题参考答案18086CPU由哪两部分构成它们的主要功能是什么?答:8086CPU由两部分组成:指令执行部件(EU,Execution Unit)和总线接口部件(BIU,Bus Interface Unit)。

指令执行部件(EU)主要由算术逻辑运算单元(ALU)、标志寄存器FR、通用寄存器组和EU控制器等4个部件组成。

其主要功能是执行指令。

总线接口部件(BIU)主要由地址加法器、专用寄存器组、指令队列和总线控制电路等4个部件组成。

其主要功能是形成访问存储器的物理地址、访问存储器并取指令暂存到指令队列中等待执行,访问存储器或I/O端口读取操作数参加EU运算或存放运算结果等。

2.8086CPU预取指令队列有什么好处?8086CPU内部的并行操作体现在哪里?答:8086CPU的预取指令队列由6个字节组成。

按照8086CPU的设计要求,指令执行部件(EU)在执行指令时,不是直接通过访问存储器取指令,而是从指令队列中取得指令代码,并分析执行它。

从速度上看,该指令队列是在CPU内部,EU从指令队列中获得指令的速度会远远超过直接从内存中读取指令。

8086CPU内部的并行操作体现在指令执行的同时,待执行的指令也同时从内存中读取并送到指令队列。

3. 8086CPU中有哪些寄存器?各有什么用途?答:CPU有14个内部寄存器,可分为3大类:通用寄存器、控制寄存器和段寄存器。

通用寄存器是一种面向寄存器的体系结构,操作数可以直接存放在这些寄存器中,既可减少访问存储器的次数,又可缩短程序的长度,提高了数据处理速度,占用内存空间少。

指令执行部件(EU)设有8个通用寄存器:AX:累加器,一般用来存放参加运算的数据和结果,在乘、除法运算、I/O操作、BCD数运算中有不可替代的作用BX:基址寄存器,除可作数据寄存器外,还可放内存的逻辑偏移地址CX:计数寄存器,既可作数据寄存器,又可在串指令和移位指令中作计数用DX:DX除可作通用数据寄存器外,还在乘、除法运算、带符号数的扩展指令中有特殊用途源变址寄存器SI:多用于存放内存的逻辑偏移地址,隐含的逻辑段地址在DS寄存器中,也可放数据目标变址寄存器DI:多用于存放内存的逻辑偏移地址,隐含的逻辑段地址在DS寄存器中,也可放数据基址指针BP:用于存放内存的逻辑偏移地址,隐含的逻辑段地址在SS寄存器中堆栈指针SP:用于存放栈顶的逻辑偏移地址,隐含的逻辑段地址在SS寄存器中控制寄存器包括指令指针寄存器IP和标志寄存器FLAG:IP用来指示当前指令在代码段的偏移位置。

32位微机原理

32位微机原理一、引言32位微机是一种计算机架构,它具有32位数据总线和32位地址总线。

本文将介绍32位微机的基本原理和工作方式。

二、32位微机的组成部分1. 中央处理器(CPU):32位微机的CPU是其核心部件,负责执行指令和控制计算机的运行。

它包括运算器、控制器和寄存器等组件。

2. 存储器:32位微机的存储器主要包括随机存取存储器(RAM)和只读存储器(ROM)。

RAM用于临时存储数据和程序,而ROM用于存储固化的程序和数据。

3. 输入输出设备:32位微机通过输入输出设备与外部环境进行交互。

常见的输入设备包括键盘、鼠标和触摸屏,而输出设备包括显示器、打印机和扬声器等。

4. 总线系统:32位微机的各个组件通过总线进行数据和控制信号的传输。

总线系统包括数据总线、地址总线和控制总线。

三、32位微机的工作原理1. 指令执行过程:32位微机的CPU按照指令的顺序逐条执行。

它从存储器中读取指令,并根据指令的操作码和操作数执行相应的操作。

2. 数据传输过程:32位微机的数据传输可以分为内部数据传输和外部数据传输。

内部数据传输是指CPU内部寄存器之间的数据传输,而外部数据传输是指CPU与外部设备之间的数据交换。

3. 中断处理过程:32位微机可以响应外部设备的中断请求。

当外部设备发生中断时,CPU会立即暂停当前任务,保存现场并执行中断服务程序,然后返回到原来的任务继续执行。

四、32位微机的特点和优势1. 大内存寻址能力:32位微机的32位地址总线可以寻址的内存空间达到4GB,远远超过16位微机的64KB寻址能力,可以处理更大规模的程序和数据。

2. 高精度运算能力:32位微机的32位数据总线可以进行高精度的运算,提供更准确的计算结果。

3. 并行处理能力:32位微机的指令集架构支持并行处理,可以同时执行多条指令,提高计算机的运行效率。

4. 多任务处理能力:32位微机的操作系统支持多任务处理,可以同时执行多个任务,提高计算机的利用率。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

One for DMA controller to request clearance from CPU One used by CPU to acknowledge that DMA controller is free to send data over data lines without interference from CPU

How BIOS Finds/Loads the OS

Involves initially turning on power with on/off switch More stressful than soft boot because of initial power surge through equipment Uses OS to reboot Faster than hard boot

Assignments for I/O Addresses DMA Channels

• • •

Provide shortcuts for a device to send data directly to memory; bypasses CPU A chip on the motherboard contains DMA logic and manages the process Each channel requires two lines to manage it

How Memory Addresses Are Assigned

•

Shadowing ROM

Process of copying programs from ROM to RAM for execution

I/O Addresses

• •

Numbers the CPU can use to access hardware devices, in same way it uses memory addresses to access physical memory Also called port addresses or ports

BIOS and Device Drivers

•

Categories of BIOS (firmware) programs

System BIOS Startup BIOS CMOS setup Small programs stored on hard drive that tell computer how to communicate with an input/output device Necessary for communication between OS and more complex devices

Startup BIOS Controls the Beginning of the Boot

•

Startup BOS is in control for first three steps and beginning of the fourth, where control is turned over to the OS

IRQs

Memory Addresses

•

Hexadecimal numbers, often written in segment/offset form, assigned to RAM and ROM so that the CPU can access both

How Memory Addresses Are Assigned

•

Soft boot (warm boot)

Plug and Play (PnP) Standard

• •

Makes installing hardware devices less complicated Rather than having to reset DIP switches and jumpers, OS and/or startup BIOS automatically configures hardware devices to reduce or eliminate conflicting requests for system resources Applies to OS, BIOS on the motherboard, and BIOS on devices

• • •

CPU has fixed number of memory addresses, determined by CPU and bus it is using They can be assigned to any type of physical memory in the system that needs to be addressed by the CPU Once addresses have been assigned (usually during boot process), CPU sees physical memory as a single list that can be accessed using memory addresses

Polling is an alternative to an interrupt

IRQs

•

Preconfigured assignments make it easier to configure devices and avoid conflicts with other devices

COM1 and COM2 (for serial devices such as modems) LPT1 and LPT2 (for parallel devices such as printers)

Consists of programs that instruct computers to perform specific tasks

Operating System (OS)

•

Software that controls a computer

Manages hardware Runs applications Provides user interface Stores, retrieves, and manipulates files

•

Tools used by hardware or software to communicate with the other:

Memory addresses I/O addresses Interrupt request numbers (IRQs) Direct memory access (DMA) channels

•

continued…

Functions Performed During the Boot

4. Startup BIOS finds the OS, which is loaded, configured, matched up with the BIOS and device drivers that control them 6. Some application software may be loaded and executed

Boot Step 1 Parts of the Boot Process

• • • •

Step 1: POST Step 2: ROM BIOS startup program searches for and loads an OS Step 3: OS configures the system and completes its own loading Step 4: User executes application software

Learn … You Will Learn… Chapter 2

How Hardware and Software Work Together

• • • •

How hardware and software interact How BIOS and device drivers are used to send instructions to hardware How different operating systems work The steps involved in booting your computer

Hardware and Software Interaction: An Overview

•

Software

Intelligence of the computer

• • •

Determines what hardware is present Decides how hardware is configured and used Uses hardware to perform tasks

Interrupt Request Number (IRQ)

• •

Line on a bus that a device uses to alert the CPU that it needs servicing

Common Uses for Some IRQs

Interruptions to CPU are called hardware interrupts

Functions Performed During the Boot

1. Startup BIOS tests essential hardware components (power-on self test or POST) 2. Setup information is used to configure both hardware and software 3. Hardware components are assigned system resources they will later use for communication