X86,MIPS,ARM CPU体系结构特点

ARM、 MIPS 、X86三大芯片架构对比

慢。

Second的相关语),是一种采取精简指令集(RISC)的处理器架构,1981年

出现,由MIPS科技公司开发并授权,广泛被使用在许多电子产品、网络设

备、个人娱乐装置与商业装置上。最早的MIPS架构是32位,最新的版本已

经变成64位。

MIPS的基本特点是:

(1)包含大量的寄存器、指令数和字符。

(2)可视的管道延时时隙。

这些特性使MIPS架构能够提供最高的每平方毫米性能和当今SoC设计

中最低的能耗。

3. X86

X86架构是芯片巨头Intel设计制造的一种微处理器体系结构的统称。如

果这样说你不理解,那幺当我说出8086,80286等这样的词汇时,相信你肯

定马上就理解了,正是基于此,X86架构这个名称被广为人知。如今,我们

所用的PC绝大部分都是X86架构。可见X86架构普及程度,这也和Intel的

霸主地位密切相关。x86采用CISC(ComplexInstrucTIonSetComputer,复

杂指令集计算机)架构。与采用RISC不同的是,在CISC处理器中,程序的

各条指令是按顺序串行执行的,每条指令中的各个操作也是按顺序串行执行

ARM、MIPS、X86三大芯片架构对比

1. ARM

ARM是高级精简指令集的简称(AdvancedRISCMachine),它是一个32

位的精简指令集架构,但也配备16位指令集,一般来讲比等价32位代码节

省达35%,却能保留32位系统的所有优势。

ARM处理器的主要特点是:

(1)体积小、低功耗、低成本、高性能ARM被广泛应用mb(16位)/ARM(32位)双指令集,能很好

cpu架构简析

CPU架构解析报告报告人:夏栩四川农业大学信息工程学院本报告旨在从x86、MIPS、ARM等不同,简单分析说明各种架构之间关系、以及各自特点。

首先明确体系架构和体系结构的定义,然后分别论述x86、ARM、MIPS架构的特点,然后是简单介绍ARM与MIPS对比,ARM与X86对比,最后是谈一下对ARM处理器的前景观望。

首先,体系架构的定义:CPU架构是CPU厂商给属于同一系列的CPU产品定的一个规范,主要目的是为了区分不同类型CPU的重要标示。

目前市面上的CPU主要分有两大阵营,一个是intel系列CPU,另一个是AMD系列CPU。

图表1第一块支持X86指令集的Intel i8086处理器图表 2 AMD系列CPU体系结构的定义:在计算世界中, "体系结构"一词被用来描述一个抽象的机器,而不是一个具体的机器实现。

一般而言,一个CPU的体系结构有一个指令集加上一些寄存器而组成。

“指令集”与“体系结构”这两个术语是同义词。

一、x86、ARM、MIPS架构x86、ARM、MIPS算是是目前最常见也相对最知名的处理器架构了。

1、x86架构图表 3 X86架构处理器示意图x86或80x86是英特尔首先开发制造的一种微处理器体系结构的泛称。

该系列较早期的处理器名称是以数字来表示,并以“86”作为结尾,包括Intel 8086、80186、80286、80386以及80486,因此其架构被称为“x86”。

x86架构于1978年推出的Intel 8086中央处理器中首度出现,它是从Intel 8008处理器中发展而来的,而8008则是发展自Intel 4004的。

8086在三年后为IBM PC 所选用,之后x86便成为了个人电脑的标准平台,成为了历来最成功的CPU架构。

8086是16位元处理器;直到1985年32位元的80386的开发,这个架构都维持是16位元。

接着一系列的处理器表示了32位元架构的细微改进,推出了数种的扩充,直到2003年AMD对于这个架构发展了64位元的扩充,并命名为AMD64。

MIS,RMCPU体系结构特点

MIS,RMCPU体系结构特点在回答以下问题之前我们有必要说明一下什么是处理器体系结构和体系架构。

体系架构:CPU架构是CPU厂商给属于同一系列的CPU产品定的一个规范,主要目的是为了区分不同类型CPU的重要标示。

目前市面上的CPU主要分有两大阵营,一个是intel系列CPU,另一个是AMD系列CPU。

体系结构:在计算世界中, "体系结构"一词被用来描述一个抽象的机器,而不是一个具体的机器实现。

一般而言,一个CPU的体系结构有一个指令集加上一些寄存器而组成。

“指令集”与“体系结构”这两个术语是同义词。

问题一:X86,MIPS,ARM三块cpu的体系结构和特点X86:X86采用了CISC指令集。

在CISC指令集的各种指令中,大约有20%的指令会被反复使用,占整个程序代码的80%。

而余下的80%的指令却不经常使用,在程序设计中只占20%。

总线接口部件BIU总线接口部件由4个16位段寄存器(DS,ES,SS,CS)、一个16位指令指针寄存器(IP)、20位物理地址加法器、6字节指令队列(8088为4字节)及总线控制电路组成,负责与存储器及I/O端口的数据传送。

执行部件EU执行部件由ALU、寄存器阵列(AX,BX,CX,DX,SI,DI,BP,SP)、标志寄存器(PSW)等几个部分组成,其任务就是从指令队列流中取出指令,然后分析和执行指令,还负责计算操作数的16位偏移地址。

寄存器的结构1)数据寄存器AX、BX、CX、DX均为16位的寄存器,它们中的每一个又可分为高字节H和低字节L。

即AH、BH、CH、DH及AL、BL、CL、DL可作为单独的8位寄存器使用。

不论16位寄存器还是8位寄存器,它们均可寄存操作数及运算的中间结果。

有少数指令指定某个寄存器专用,例如,串操作指令指定CX专门用作记录串中元素个数的计数器。

2)段寄存器组:CS、DS、SS、ES。

8086/8088的20位物理地址在CPU内部要由两部分相加形成的。

ARM与Mips架构对比

MIPS起始地址是0xbfc00000,会有4Mbyte的大小限制,但一般MIPS芯片都会采 取一些方法解决这个问题。

ARM没有这种问题。

MIPS24K起始地址改到了0xbf000000,现在有16Mbyte的空间了。6.性能 具体性能比较,因为差异性太大,所以很难分出谁好谁坏。从个人经验来讲MIPS4k和ARM9基本上是同一个级别的,但ARM9性能似乎要比MIPS4K好。

CPU架构对比(MIPS和ARM)一、概述:

RISC(精简指令集处理器)家族的两大佼佼者MIPS和ARM,相对应的是CISC(复 杂指令集处理器),典型的是X86家族的系列

二、应用领域:

1.在1GHz以上的应用,ARM架构的产品相比之下不还不是很这恰恰是ARM的 主攻市场。

1.流水线结构

MIPS是最简单的体系结构之一,所以使大学喜欢选择MIPS体系结构来介绍计 算体系结构课程。

MIPS最初的设计思想就是使用简单的RISC硬体

2.指令结构instruction

MIPS是开放式的架构,用户可以在开发的内核中加入自己的指令,

3.寄存器register

MIPS内核中有32个寄存器(Register),而ARM只有16个,这种结构设计上 的先天优势,决定了在同等性能表现下,MIPS的芯片面积和功耗会更小。ARM有一组特殊用途寄存器cp0-cp15,可以使用MCR,MRC等指令控制;相对应 的,MIPS也有cp00-30,使用mfc0,mtc0指令控制。

8.未来发展

ARM的下一代走向多内核结构,而MIPS公司的下一代核心则转向硬件多线程功能(multithreading)

MIPS的multithreading很类似Intel的HyperThreading技术。从现在的发展来看, 多内核占上风。

X86、ARM、MIPS微处理器架构浅析

X86、ARM、MIPS微处理器架构浅析作者:刘帅来源:《智富时代》2015年第12期【摘要】上世纪80~90年代PC的快速发展促进了微处理器的快速发展,其中最为成功的是X86架构微处理器。

而21世纪是移动终端爆发发展的时代,现今最为流行的是智能终端(智能手机、平版电脑),这些都使得ARM架构微处理器发展的如日中天,本文对这些微处理器架构的特点作了简要的分析。

【关键词】X86;ARM;MIPS;RISC;CISC一、微处理器架构发展简述从处理器指令集来划分微处理器主要分为两个体系: RISC(Reduced Instruction Set Computer,精简指令集计算机)与CISC(Complex Instruction Set Computer,复杂指令集计算机)。

RISC主旨是简化指令系统,优化处理器设计,从而它有以下特点:指令编码、长度统一,可快速解析;缓存通用化,所有缓存可用于所有内容,简化了编译器的设计;指令寻址模式简单,复杂寻址模式以计算指令序列实现;硬件支持数据类型少。

CISC拥有庞大的指令系统,其指令功能复杂,寻址方式多,指令都可以直接访问存储器;绝大多数指令需多个机器周期完成;内部采用微程序控制;有少量专用寄存器。

在CISC 指令集的各种指令中,大约有20%的指令会被反复使用,占整个程序代码的80%。

而余下的80%的指令却不经常使用。

但实际中RISC和CISC发展到现在也不断的相互学习,现在的RISC指令集也达到数百条,运行周期也不是完全固定。

但RISC设计的根本原则还是针对流水线化的处理器优化。

目前MIPS、ARM和X86架构是世界三大主流处理器架构。

(一)X86架构Intel在1978年推出8086中央处理器,这是X86架构首度出现,三年后8086被IBM PC 选用,之后x86架构便成为了个人电脑的标准平台,成为了历来最成功的CPU架构。

8086是16位处理器,1985年随着80386的发布,32位处理器才在PC中广泛推广,2003年AMD在X86的架构上进行了64位扩充,并命名为AMD64。

X86架构与ARM架构区别

X86架构与ARM架构区别1.设计理念:-X86架构是传统的复杂指令集计算机(CISC)架构,它的设计目标是提供功能丰富和灵活的指令集,以支持多样化的计算任务。

-ARM架构则是精简指令集计算机(RISC)架构,它更注重的是简化指令集,提高整体效率和节省功耗。

2.指令集:-X86架构有一套复杂的指令集,包含大量的指令,可完成复杂的任务,支持多种操作模式和寻址模式。

这使得X86架构的处理器在处理大型软件和运算密集型任务时表现出色。

-ARM架构的指令集相对精简,仅有32位或64位的固定长度指令。

虽然指令集较少,但非常高效,适用于移动设备和嵌入式系统,可以提供较低的功耗和较高的性能。

3.功耗和性能:-X86架构的处理器通常具有较高的功耗,适用于高性能计算领域,如桌面电脑、工作站和服务器。

它们通常拥有更高的主频和更多的核心,能够处理更大的数据集和更多的并行任务。

-ARM架构的处理器功耗较低,适合用在移动设备和嵌入式系统中。

虽然单个处理核心的性能可能不如X86处理器高,但ARM架构的优势在于可以通过多核心并行处理来提高整体性能。

4.软件兼容性:- X86架构是PC领域的标准架构,几乎所有的桌面软件和操作系统都能够运行在基于X86架构的处理器上,例如Windows、MacOS和Linux。

这使得X86架构成为主流的计算平台。

-ARM架构则是移动设备领域的主流架构,大部分移动设备和嵌入式系统都采用ARM架构。

但是,由于指令集和结构的不同,ARM架构与X86架构不兼容,因此软件和操作系统需要适配才能在ARM处理器上运行。

5.生态系统:-X86架构具有非常庞大的生态系统,有大量的硬件设备和软件开发者支持,同时拥有成熟的工具链和开发环境,使得开发者能够更轻松地开发和优化软件。

-ARM架构经过近年来的迅速发展,也建立了庞大的生态系统,并且已经在移动设备和物联网领域得到了广泛应用。

随着ARM服务器和高性能计算的兴起,ARM架构的生态系统也在不断扩大。

4大主流CPU处理器技术架构分析

4大主流CPU处理器技术架构分析1.x86架构:x86架构是由英特尔和AMD共同推出的一种处理器架构。

它是32位和64位处理器的主流架构,广泛用于个人电脑和服务器。

x86架构采用复杂指令集计算机(CISC)的设计思想,通过提供大量的指令集,能够直接执行复杂的操作,从而提高性能。

不过,由于复杂的指令集和多级流水线设计,x86架构的处理器功耗较高,且难以优化。

2.ARM架构:ARM架构是一种低功耗架构,广泛用于移动设备和嵌入式系统。

它采用精简指令集计算机(RISC)的设计思想,通过简化指令集和流水线设计,减少了功耗和芯片面积。

ARM架构具有高效能和低功耗的优势,在移动设备上取得了巨大成功。

它还采用了模块化的设计,可以根据需求选择不同的组件来构建处理器。

3. Power架构:Power架构由IBM开发,广泛应用于大型服务器和超级计算机。

Power架构采用RISC设计思想,通过减少指令数量和复杂度,提高了性能和效率。

Power架构也支持多线程和多处理器技术,可以实现高度的并行计算。

Power架构的处理器主要被用于高性能计算场景,如大数据分析、科学计算等。

4.RISC-V架构:RISC-V架构是一个开源的指令集架构,于2024年由加州大学伯克利分校开发。

RISC-V架构采用RISC设计思想,通过精简指令集和模块化设计,提供了灵活性和可扩展性。

RISC-V架构的指令集规范是公开的,可以任意修改和扩展,使得硬件开发者可以根据需求进行定制。

RISC-V架构对于嵌入式系统和物联网设备具有较大的潜力,也得到了学术界和开源社区的广泛支持。

这四种主流的CPU处理器技术架构各有优势和应用场景,选择合适的架构需要根据具体需求和应用来决定。

无论是个人电脑、服务器还是移动设备,处理器架构的选择都直接影响着性能、功耗和功能扩展性。

随着技术的不断发展,未来的处理器架构可能会进行更多的创新和突破,满足日益增长的计算需求。

电脑中央处理器的架构与性能比较

电脑中央处理器的架构与性能比较随着计算机技术的飞速发展,电脑中央处理器(CPU)作为计算机的核心组件之一,扮演着重要的角色。

不同架构的CPU具有不同的性能优势和特点。

本文将探讨几种常见的CPU架构,并对它们的性能进行比较。

一、x86架构x86架构是当前主流桌面和笔记本电脑CPU的主要架构之一。

这种架构由英特尔和AMD等公司研发,被广泛应用于个人电脑的处理器上。

x86架构的CPU采用复杂指令集(CISC)设计,可以执行复杂而功能强大的指令。

这种设计特点使得x86架构的CPU在应对复杂计算和多任务处理时表现出色。

同时,由于x86架构的广泛应用,针对这种架构开发的软件和应用生态系统也非常丰富,使得x86架构的CPU在应用兼容性和软件支持方面具有明显的优势。

然而,由于x86架构历史悠久,设计上存在一些问题,比如指令冗余和复杂性,导致功耗和性能方面的一些限制。

此外,x86架构在移动设备和嵌入式系统等领域的应用相对较少,主要集中在个人电脑领域。

二、ARM架构ARM架构是一种精简指令集(RISC)架构,最初是为移动设备和嵌入式系统设计的。

如今,ARM架构的CPU在智能手机、平板电脑、物联网设备等领域得到广泛应用。

ARM架构的CPU采用精简指令集设计,指令集较为简单,执行效率高,功耗低。

这使得ARM架构的CPU在移动设备上具有出色的性能和电池续航能力。

同时,由于ARM架构设计上的优势,ARM芯片在单核和多核处理器的设计上也更具灵活性。

然而,由于ARM架构的历史相对较短,软件生态系统相对不够成熟。

尽管ARM架构的CPU在处理器核心数量上具有一定的优势,但在单核性能上可能不及x86架构的CPU。

此外,由于ARM架构的广泛应用领域,对特定应用的优化程度可能不同,也导致了某些特定领域的性能不足。

三、RISC-V架构RISC-V架构是一种开放指令集(RISC)架构,近年来逐渐崭露头角。

由于其开放性和免费许可证,RISC-V架构的CPU正在吸引越来越多的关注和应用。

解读x86、ARM和MIPS三种主流芯片架构

解读x86、ARM和MIPS三种主流芯片架构派进展风格导致其商业进程远远滞后于ARM,当ARM与高通、苹果、NVIDIA等芯片设计公司合作大举进攻移动终端的时候,MIPS还停歇在高清盒子、打印机等小众市场产品中;五是MIPS自身系统的软件平台也较为落后,应用软件与ARM体系相比要少无数。

x86 CISC是一种为了便于编程和提高记忆体拜访效率的芯片设计体系,包括两大主要特点:一是用法微代码,命令集可以挺直在微代码记忆体里执行,新设计的处理器,只需增强较少的电晶体就可以执行同样的命令集,也可以很快地编写新的命令集程式;二是拥有浩大的命令集,x86拥有包括双运算元格式、寄存器到寄存器、寄存器到记忆体以及记忆体到寄存器的多种命令类型,为实现复杂操作,微处理器除向程序员提供类似各种寄存器和机器命令功能外,还通过存于只读存储器(ROM)中的微程序来实现极强的功能,微处理器在分析完每一条命令之后执行一系列初级命令运算来完成所需的功能。

x86命令体系的优势体现在能够有效缩短新命令的微代码设计时光,允许实现CISC体系机器的向上兼容,新的系统可以用法一个包含早期系统的命令集合。

另外微程式命令的格式与高阶语言相匹配,因而编译器并不一定要重新编写。

相较ARM RISC命令体系,其缺点主要包括四个方面。

第一,通用寄存器规模小,x86命令集惟独8个通用寄存器,CPU大多数时光是在拜访存储器中的数据,影响囫囵系统的执行速度。

而RISC 系统往往具有十分多的通用寄存器,并采纳了重叠寄存器窗口和寄存器堆等技术,使寄存器资源得到充分的利用。

其次,影响性能表现,解码器的作用是把长度不定的x86命令转换为长度固定的类似于RISC的命令,并交给RISC内核。

解码分为硬件解码和微解码,对于容易的x86命令只要硬件解码即可,速度较快,而碰到复杂的x86命令则需要举行微解码,并把它分成若干条容易命令,速度较慢且很复杂。

第三,x86命令集寻址范围小,约束用户需要。

ARM处理器与X86处理器的区别

ARM处理器与X86处理器的区别CPU的指令集从主流的体系结构上分为精简指令集(RISC)和复杂指令集(CISC)。

嵌入式系统中的主流处理器——ARM处理器,所使用的就是精简指令集。

而桌面领域的处理器大部分使用的是复杂指令集,比如Intel的X86系列处理器。

我们把ARM处理器所使用的指令集称为ARM指令集,把X86处理器所使用的指令集称为X86指令集,ARM 处理器与X86处理器采用不同类型的指令集,造成了处理器在性能、成本、功耗等方面的诸多差异。

ARM指令集和X86指令集的比较:(1) 功耗:这是ARM主板最大的优点之一,一般的VIA的X86主板,功耗都在40W左右或者以上,而ARM主板的功耗极低,EICB系列主板功耗整体也只有1W左右。

(2) 发热:ARM主板不会发热,主板温度一般是常温,因此可以一直常年累月开机在线工作,不会出现任何问题。

而X86主板CPU必须配风扇而且不能长期工作,否则主板产生的温度会让主板整体性能寿命降低。

风扇的工作寿命也会影响主板的寿命。

(3) 开机时间:ARM主板的开机速度非常快,一般只有几秒就可以了,而X86需要开机一段时间,Windows系统才会起来。

(4) 性能:目前来看,ARM主板的性能已经越来越接近X86主板,甚至在某些方面超过了它。

从视频多媒体、数据通信等几个方面,基本和X86类似。

(5) 工作时间和环境:ARM主板不受时间限制,可以一直开机工作,无须人员去维护,而且在调电情况下,只要来电,那么就会自动启动,无须人员去开机或者关机,而X86主板却要人员维护,而且不能长期工作,否则会让主板寿命大大降低。

环境:ARM主板一般都是工业极,不受环境影响,最低温度可以在-20摄氏度左右,最高温度可以在70摄氏度左右,而X86一般都不行。

(6) 数据安全性:ARM主板都采用高度集成方式,数据一般都放在Flash内部,都是二进制格式,外部无法直接拷贝内部数据。

而且最大的优点是:目前ARM主板的系统都是WinCE系统或者Linux系统,不会受病毒感染,客户无须担心病毒感染而导致数据泄漏,尤其是一些对于数据安全性要求很高的场所。

CPU架构讲解X86、ARM、RISC、MIPS

CPU架构讲解X86、ARM、RISC、MIPS一、当前CPU的主流架构:1.X86架构采用CISC指令集(复杂指令集计算机),程序的各条指令是按顺序串行执行的,每条指令中的各个操作也是按顺序串行执行的。

2.ARM架构是一个32位的精简指令集(RISC)架构。

3.RISC-V架构是基于精简指令集计算(RISC)原理建立的开放指令集架构。

4.MIPS架构是一种采取精简指令集(RISC)的处理器架构,可支持高级语言的优化执行。

CPU架构是CPU厂商给属于同一系列的CPU产品定的一个规范,是区分不同类型CPU的重要标示。

二、目前市面上的CPU分类主要分有两大阵营:1.intel、AMD为首的复杂指令集CPU;2.IBM、ARM为首的精简指令集CPU。

两个不同品牌的CPU,其产品的架构也不相同,例如,Intel、AMD的CPU是X86架构的,而IBM的CPU是PowerPC架构,ARM是ARM架构。

三、四大主流CPU架构详解(X86、ARM、RISC、MIPS)1.X86架构X86是微处理器执行的计算机语言指令集,指一个Intel通用计算机系列的标准编号缩写,也标识一套通用的计算机指令集合。

1978年6月8日,Intel 发布了新款16位微处理器8086,也同时开创了一个新时代:X86架构诞生了。

X86指令集是Intel为其第一块16位CPU(i8086)专门开发的,IBM 1981年推出的世界第一台PC机中的CPU–i8088(i8086简化版)使用的也是X86指令。

采用CISC(Complex Instruction Set Computer,复杂指令集计算机)架构。

与采用RISC不同的是,在CISC处理器中,程序的各条指令是按顺序串行执行的,每条指令中的各个操作也是按顺序串行执行的。

顺序执行的优点是控制简单,但计算机各部分的利用率不高,执行速度慢。

随着CPU技术的不断发展,Intel陆续研制出更新型的i80386、i80486直到今天的Pentium 4系列,但为了保证电脑能继续运行以往开发的各类应用程序以保护和继承丰富的软件资源,所以Intel所生产的所有CPU仍然继续使用X86指令集。

汇编语言种类

汇编语言种类汇编语言是一种低级编程语言,用于编写计算机程序。

它是计算机硬件能够理解和执行的指令集的一种表达方式。

在不同的计算机体系结构中,存在着多种汇编语言种类。

本文将介绍一些常见的汇编语言种类及其特点。

1. x86汇编语言x86汇编语言是应用最广泛的汇编语言之一,被用于大多数个人计算机上的x86架构。

x86汇编语言的语法相对复杂,但功能强大。

它是许多操作系统和应用程序的底层代码的基础。

2. ARM汇编语言ARM汇编语言是用于ARM架构的低级编程语言。

ARM架构主要用于移动设备和嵌入式系统中,如智能手机、平板电脑和物联网设备。

ARM汇编语言相对于x86汇编语言来说更简洁,但仍然非常强大。

3. MIPS汇编语言MIPS汇编语言是用于MIPS芯片架构的一种汇编语言。

MIPS架构广泛应用于路由器、控制器和嵌入式系统等领域。

MIPS汇编语言相对于其他汇编语言来说,指令集较为简单,易于学习和理解。

4. PowerPC汇编语言PowerPC汇编语言是用于PowerPC架构的汇编语言。

PowerPC架构曾被应用在苹果电脑和IBM的一些服务器中。

PowerPC汇编语言是一种非常强大的汇编语言,拥有丰富的指令集和功能。

5. SPARC汇编语言SPARC汇编语言是用于SPARC芯片架构的一种汇编语言。

SPARC 芯片广泛被应用于服务器和超级计算机等高性能计算领域。

SPARC汇编语言具有丰富的指令集和强大的计算能力。

6. 68k汇编语言68k汇编语言是用于Motorola 68000系列芯片的汇编语言。

这种汇编语言在上世纪80年代和90年代非常流行,在早期的个人电脑和游戏机中被广泛使用。

虽然现在已经不再流行,但在某些老旧系统中仍然可以见到。

总结:汇编语言种类繁多,不同的计算机体系结构使用不同的汇编语言。

本文介绍了一些常见的汇编语言种类,包括x86汇编语言、ARM汇编语言、MIPS汇编语言、PowerPC汇编语言、SPARC汇编语言和68k汇编语言。

浅谈几种常见的嵌入式处理器比较分析修订稿

浅谈几种常见的嵌入式处理器比较分析修订稿嵌入式处理器作为一种特殊类型的处理器,其设计目标是为了满足嵌入式系统对低功耗、小尺寸、高性能和实时性的要求。

在市场上常见的嵌入式处理器有ARM、MIPS和X86等,下面将对这几种处理器进行比较分析。

首先,ARM处理器是当前市场上最常见的一种嵌入式处理器。

ARM处理器以其低功耗、高集成度、高性能和广泛应用的特点受到了广大嵌入式系统开发者的青睐。

ARM处理器有多个系列,其中Cortex-M系列是针对低功耗的微控制器市场,Cortex-R系列是针对实时性要求较高的嵌入式应用市场,而Cortex-A系列则是面向高性能计算和移动设备市场。

其次,MIPS处理器是另一种常见的嵌入式处理器。

MIPS处理器以其简洁的指令集架构和高性能而被广泛应用于各种嵌入式系统中。

MIPS处理器在计算密集型应用和实时性要求较高的应用中表现出色,但相对于ARM处理器,MIPS处理器的应用范围较窄。

最后,X86处理器是一种广泛应用于个人计算机和服务器领域的处理器架构,但它也可以用于一些嵌入式应用。

X86处理器以其强大的性能和低成本而受到许多嵌入式系统开发者的关注。

然而,X86处理器的主要问题是功耗较高和体积较大,这在一些对功耗和尺寸有严格要求的嵌入式系统中可能不够适用。

综上所述,ARM处理器是目前市场上最常见的嵌入式处理器,并且在低功耗、高性能和广泛应用等方面具有较大优势。

MIPS处理器在一些特定的应用场景中具有一定优势,但应用范围相对较窄。

X86处理器在性能和低成本方面有优势,但在功耗和尺寸等方面存在一些局限性。

在选择嵌入式处理器时,需要根据具体应用需求和系统要求来进行比较分析,选择最适合的处理器。

arm体系结构特点

arm体系结构特点

ARM 体系结构是一种广泛使用的 32 位微处理器体系结构,具有以下特点:

1. 简单的指令集:ARM 指令集是一种 RISC(精简指令集计算机)指令集,它具有固定长度的指令和简单的指令格式。

这种简单的指令集可以提高指令的执行速度和效率,同时也可以减少指令的解码时间。

2. 高效的流水线:ARM 体系结构采用了高效的流水线技术,可以在一个时钟周期内执行多条指令。

这种流水线技术可以提高指令的执行速度和效率,从而提高处理器的性能。

3. 低功耗设计:ARM 体系结构采用了低功耗设计,可以在不影响性能的情况下降低处理器的功耗。

这种低功耗设计对于移动设备和嵌入式系统非常重要,可以延长设备的电池寿命。

4. 可扩展性:ARM 体系结构具有很好的可扩展性,可以通过增加更多的寄存器和指令来扩展处理器的功能。

这种可扩展性可以满足不同应用的需求,例如多媒体处理、网络通信等。

5. 支持Thumb 指令集:ARM 体系结构还支持 Thumb 指令集,这是一种 16 位的指令集。

Thumb 指令集可以在不损失性能的情况下减少代码的大小,从而节省存储空间。

6. 强大的异常处理机制:ARM 体系结构具有强大的异常处理机制,可以处理各种硬件和软件异常。

这种异常处理机制可以提高系统的可靠性和稳定性。

总之,ARM 体系结构具有简单的指令集、高效的流水线、低功耗设计、可扩展性、支持Thumb 指令集和强大的异常处理机制等特点,这些特点使得 ARM 体系结构成为了移动设备和嵌入式系统领域的主流处理器体系结构。

ARM,MIPS,X86三种典型指令集的简介及其特点

ARM,MIPS,X86三种典型指令集的简介及其特点ARM、MIPS、X86三种典型指令集的特点20122261 梅亮亮1.ARM指令集1.1 ARM指令集的特点:●体积小,低功耗,低成本,高性能;●支持 Thumb ( 16 位) /ARM ( 32 位)双指令集,能很好的兼容 8 位 /16 位器件;●大量使用寄存器,指令执行速度更快;●大多数数据操作都在寄存器中完成;●寻址方式灵活简单,执行效率高;●指令长度固定;●流水线处理方式●Load_store结构:在RISC中,所有的计算都要求在寄存器中完成。

而寄存器和内存的通信则由单独的指令来完成。

而在CSIC中,CPU是可以直接对内存进行操作的。

1.2 Thumb指令及应用Thumb指令集是ARM指令集的一个子集,所有的Thumb指令都有对应的ARM指令。

它舍弃了ARM指令集的一些特性如大多数的Thumb指令是无条件执行的,而几乎所有的ARM指令都是有条件执行的;大多数的Thumb数据处理指令的目的寄存器与其中一个源寄存器相同。

Thumb指令集在保留32代码优势的同时,大大的节省了系统的存储空间。

Thumb指令集中操作数仍然是32位,指令地址也为32位,指令编码16位。

由于Thumb指令的长度为16位,即只用ARM指令一半的位数来实现同样的功能,所以,要实现特定的程序功能,所需的Thumb指令的条数较ARM指令多。

1.2.1 Thumb指令优势与局限性优势:– Thumb代码所需的存储空间约为ARM代码的60%~70%;– Thumb代码使用的指令数比ARM代码多约30%~40%;–若使用32位的存储器,ARM代码比Thumb代码快约40%;–若使用16位的存储器,Thumb代码比ARM代码快约40%~50%;–与ARM代码相比较,使用Thumb代码,存储器的功耗会降低约30%。

局限性:条件跳转限制在256byte 偏移范围内,无条件跳转限制为4K偏移范围内,而ARM为32 Mbytes偏移。

体系结构 RISC, CISC, x86, ARM, MIPS

体系结构: RISC, CISC, x86, ARM, MIPS硬件体系结构(Architecture)软件操作系统(Operating System)一、RISC与CISC1.CISC(Complex Instruction SetComputer,复杂指令集计算机)复杂指令集(CISC,Complex Instruction Set Computer)是一种微处理器指令集架构(ISA),每个指令可执行若干低阶操作,诸如从内存读取、储存、和计算操作,全部集于单一指令之中。

CISC特点:1.指令系统庞大,指令功能复杂,指令格式、寻址方式多;2.绝大多数指令需多个机器周期完成;3.各种指令都可访问存储器;4.采用微程序控制;5.有专用寄存器,少量;6.难以用优化编译技术生成高效的目标代码程序;在CISC指令集的各种指令中,大约有20%的指令会被反复使用,占整个程序代码的80%。

而余下的80%的指令却不经常使用,在程序设计中只占20%。

2.RISC(reduced instruction setcomputer,精简指令集计算机)精简指令集这种设计思路对指令数目和寻址方式都做了精简,使其实现更容易,指令并行执行程度更好,编译器的效率更高。

它能够以更快的速度执行操作。

这种设计思路最早的产生缘自于有人发现,尽管传统处理器设计了许多特性让代码编写更加便捷,但这些复杂特性需要几个指令周期才能实现,并且常常不被运行程序所采用。

此外,处理器和主内存之间运行速度的差别也变得越来越大。

在这些因素促使下,出现了一系列新技术,使处理器的指令得以流水执行,同时降低处理器访问内存的次数。

实际上在后来的发展中,RISC与CISC在竞争的过程中相互学习,现在的RISC指令集也达到数百条,运行周期也不再固定。

虽然如此,RISC设计的根本原则——针对流水线化的处理器优化—0—没有改变,而且还在遵循这种原则的基础上发展出RISC的一个并行化变种VLIW(包括Intel EPIC),就是将简短而长度统一的精简指令组合出超长指令,每次执行一条超长指令,等于并行执行多条短指令。

X86架构与ARM架构区别

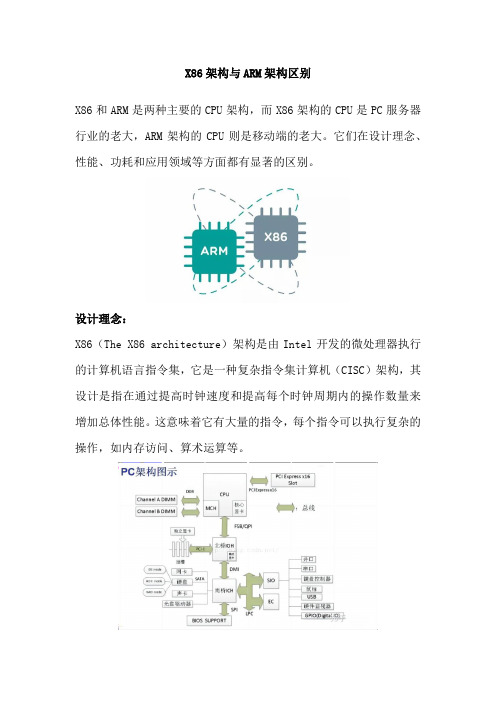

X86架构与ARM架构区别X86和ARM是两种主要的CPU架构,而X86架构的CPU是PC服务器行业的老大,ARM架构的CPU则是移动端的老大。

它们在设计理念、性能、功耗和应用领域等方面都有显著的区别。

设计理念:X86(The X86 architecture)架构是由Intel开发的微处理器执行的计算机语言指令集,它是一种复杂指令集计算机(CISC)架构,其设计是指在通过提高时钟速度和提高每个时钟周期内的操作数量来增加总体性能。

这意味着它有大量的指令,每个指令可以执行复杂的操作,如内存访问、算术运算等。

ARM架构是由ARM公司开发的32位精简指令集,这是一种精简指令集计算机(RISC)架构,它的设计重点是在限制的功率和热环境下,优化每瓦特的性能。

因此,它的指令集相对较小,每个指令执行的操作相对简单,但是可以通过组合多个指令来完成复杂的操作。

性能和功耗:●X86架构的处理器通常具有较高的时钟频率和更强的计算能力,因此它的功耗也是常年居高不下的。

一般来说,X86架构的处理器,尤其是用于桌面和服务器的处理器,其功耗相对较高,即使是用于笔记本电脑的Intel Core系列处理器,其功耗通常在15W 到45W之间。

●ARM架构的处理器设计更注重能效,即在单位能耗下完成的计算量。

因此,ARM处理器通常在功耗敏感的应用中更受欢迎,如移动设备(手机、平板电脑)、嵌入式系统等。

应用领域:●X86架构由于其强大的计算能力,主要应用在个人电脑、工作站和服务器等领域。

●ARM架构由于其低功耗的特性,主要应用在嵌入式系统设计,低耗电节能,非常适用移动通讯领域。

消费性电子产品,例如可携式装置(PDA、移动电话、多媒体播放器、掌上型电子游戏,和计算机),电脑外设(硬盘、桌上型路由器),甚至导弹的弹载计算机等军用设施。

软件兼容性:●X86架构有着丰富的软件生态,尤其是在桌面操作系统(如Windows、Linux、macOS等)和各类应用软件上,这使得X86成为许多不同应用场景的理想选择。

了解一下不同CPU架构的特点

了解一下不同CPU架构的特点在计算机领域中,CPU(中央处理器)是一种重要的硬件组件,它负责执行计算机的指令并控制各个硬件部件的工作。

不同的CPU架构具有各自独特的特点和优势。

本文将介绍几种常见的CPU架构,并分析它们的特点。

一、x86架构x86架构是目前个人计算机使用最广泛的CPU架构。

它最早由英特尔(Intel)推出,并被AMD等公司所采用。

x86架构的特点主要集中在以下几个方面:1. 平台广泛:由于x86架构的流行,大量的软件和应用程序都是基于x86架构开发的,这使得x86架构成为了许多厂商和用户的首选。

2. 性能优越:随着技术的不断发展,x86架构在性能上已经达到了非常高的水平。

高频率、多核心和大缓存的设计使得x86架构的处理器能够处理复杂的计算任务。

3. 兼容性强:x86架构具有很强的向下兼容性,旧版的x86架构的软件和应用程序可以在新的x86处理器上运行,这为用户的升级提供了便利。

二、ARM架构ARM架构是一种低功耗、高性能的CPU架构,广泛应用于移动设备和嵌入式系统。

以下是ARM架构的特点:1. 低功耗:ARM架构的设计注重功耗的优化,因此在相同功耗下,ARM处理器可以提供更好的性能。

这使得ARM架构成为了移动设备的首选。

2. 高度集成:ARM架构的处理器通常集成了多个功能模块,如图形处理器(GPU)、视频编解码器等,这种高度集成的设计可以提供更好的性能和功耗比。

3. 架构灵活:ARM架构支持多种变体和扩展,可以根据不同的应用需求进行定制设计。

这使得ARM架构在各种嵌入式设备中都有广泛的应用。

三、Power架构Power架构是由IBM开发的一种RISC(精简指令集计算机)架构。

它具有以下特点:1. 高性能:Power架构的处理器在科学计算和企业级应用等领域中拥有卓越的性能。

其强大的浮点计算能力和高度优化的指令集为高性能计算提供了支持。

2. 可扩展性:Power架构具有良好的可伸缩性,可以应对不同规模和复杂度的系统需求。

ARM的架构相较于x86有哪些特点

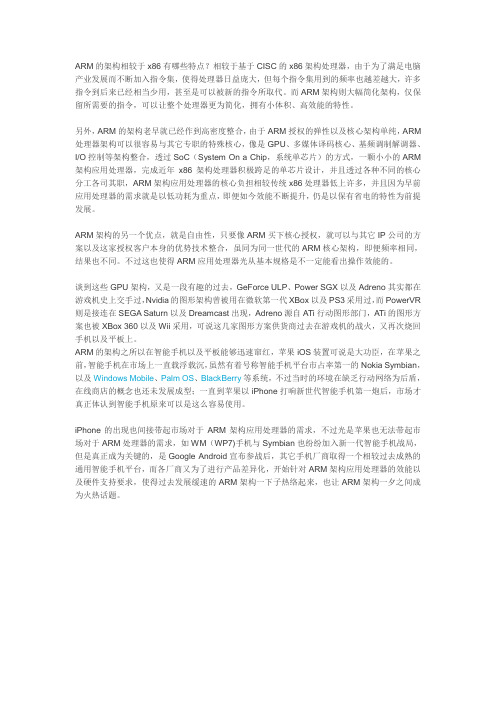

ARM的架构相较于x86有哪些特点?相较于基于CISC的x86架构处理器,由于为了满足电脑产业发展而不断加入指令集,使得处理器日益庞大,但每个指令集用到的频率也越差越大,许多指令到后来已经相当少用,甚至是可以被新的指令所取代。

而ARM架构则大幅简化架构,仅保留所需要的指令,可以让整个处理器更为简化,拥有小体积、高效能的特性。

另外,ARM的架构老早就已经作到高密度整合,由于ARM授权的弹性以及核心架构单纯,ARM 处理器架构可以很容易与其它专职的特殊核心,像是GPU、多媒体译码核心、基频调制解调器、I/O控制等架构整合,透过SoC(System On a Chip,系统单芯片)的方式,一颗小小的ARM 架构应用处理器,完成近年x86架构处理器积极跨足的单芯片设计,并且透过各种不同的核心分工各司其职,ARM架构应用处理器的核心负担相较传统x86处理器低上许多,并且因为早前应用处理器的需求就是以低功耗为重点,即便如今效能不断提升,仍是以保有省电的特性为前提发展。

ARM架构的另一个优点,就是自由性,只要像ARM买下核心授权,就可以与其它IP公司的方案以及这家授权客户本身的优势技术整合,虽同为同一世代的ARM核心架构,即便频率相同,结果也不同。

不过这也使得ARM应用处理器光从基本规格是不一定能看出操作效能的。

谈到这些GPU架构,又是一段有趣的过去,GeForce ULP、Power SGX以及Adreno其实都在游戏机史上交手过,Nvidia的图形架构曾被用在微软第一代XBox以及PS3采用过,而PowerVR 则是接连在SEGA Saturn以及Dreamcast出现,Adreno源自ATi行动图形部门,ATi的图形方案也被XBox 360以及Wii采用,可说这几家图形方案供货商过去在游戏机的战火,又再次烧回手机以及平板上。

ARM的架构之所以在智能手机以及平板能够迅速窜红,苹果iOS装置可说是大功臣,在苹果之前,智能手机在市场上一直载浮载沉,虽然有着号称智能手机平台市占率第一的Nokia Symbian,以及Windows Mobile、Palm OS、BlackBerry等系统,不过当时的环境在缺乏行动网络为后盾,在线商店的概念也还未发展成型;一直到苹果以iPhone打响新世代智能手机第一炮后,市场才真正体认到智能手机原来可以是这么容易使用。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

在回答以下问题之前我们有必要说明一下什么是处理器体系结构和体系架构。

体系架构:●CPU架构是CPU厂商给属于同一系列的CPU产品定的一个规范,主要目的是为了区分不同类型CPU的重要标示。

●目前市面上的CPU主要分有两大阵营,一个是intel系列CPU,另一个是AMD系列CPU。

体系结构:●在计算世界中, "体系结构"一词被用来描述一个抽象的机器,而不是一个具体的机器实现。

一般而言,一个CPU的体系结构有一个指令集加上一些寄存器而组成。

“指令集”与“体系结构”这两个术语是同义词。

问题一:X86,MIPS,ARM三块cpu的体系结构和特点X86:X86采用了CISC指令集。

在CISC指令集的各种指令中,大约有20%的指令会被反复使用,占整个程序代码的80%。

而余下的80%的指令却不经常使用,在程序设计中只占20%。

●总线接口部件BIU总线接口部件由4个16位段寄存器(DS,ES,SS,CS)、一个16位指令指针寄存器(IP)、20位物理地址加法器、6字节指令队列(8088为4字节)及总线控制电路组成,负责与存储器及I/O 端口的数据传送。

●执行部件EU执行部件由ALU、寄存器阵列(AX,BX,CX,DX,SI,DI,BP,SP)、标志寄存器(PSW)等几个部分组成,其任务就是从指令队列流中取出指令,然后分析和执行指令,还负责计算操作数的16位偏移地址。

●寄存器的结构1)数据寄存器AX、BX、CX、DX均为16位的寄存器,它们中的每一个又可分为高字节H和低字节L。

即AH、BH、CH、DH及AL、BL、CL、DL可作为单独的8位寄存器使用。

不论16位寄存器还是8位寄存器,它们均可寄存操作数及运算的中间结果。

有少数指令指定某个寄存器专用,例如,串操作指令指定CX专门用作记录串中元素个数的计数器。

2)段寄存器组:CS、DS、SS、ES。

8086/8088的20位物理地址在CPU内部要由两部分相加形成的。

SP、BP、SI、DI是用以指明其偏移地址,即20位物理地址的低16位;而CS、DS、SS、ES是用以指明20位物理地址的高16位的,故称作段寄存器。

4个存储器使用专一,不能互换,CS识别当前代码段,DS识别当前数据段,SS识别当前堆栈段;ES识别当前附加段。

一般情况下,DS和ES都须用户在程序中设置初值。

3)控制寄存器组:IP和FLAG。

指令指针IP用以指明当前要执行指令的偏移地址(段地址由CS提供)。

标志寄存器FLAG有16位,用了其中的九位,分两组:状态标志和控制标志。

前者用以记录状态信息,由6位组成,后者用以记录控制信息由3位组成。

6位状态标志,包括CF、AF、OF、SF、PF和ZF,它反映前一次涉及ALU操作的结果,对用户它“只读不写”。

控制标志包括方向标志DF,中断允许标志IF及陷阱标志TF,中断允许标志IF及陷阱标志TF,可通过指令设置。

MIPS:●所有指令都是32位编码;●有些指令有26位供目标地址编码;有些则只有16位。

因此要想加载任何一个32位值,就得用两个加载指令。

16位的目标地址意味着,指令的跳转或子函数的位置必须在64K 以内(上下32K);●所有的动作原理上要求必须在1个时钟周期内完成,一个动作一个阶段;●有32个通用寄存器,每个寄存器32位(对32位机)或64位(对64位机);●本身没有任何帮助运算判断的标志寄存器,要实现相应的功能时,是通过测试两个寄存器是否相等来完成的;●所有的运算都是基于32位的,没有对字节和对半字的运算(MIPS里,字定义为32位,半字定义为16位);●没有单独的栈指令,所有对栈的操作都是统一的内存访问方式。

因为push和pop指令实际上是一个复合操作,包含对内存的写入和对栈指针的移动;●由于MIPS固定指令长度,所以造成其编译后的二进制文件和内存占用空间比x86的要大,(x86平均指令长度只有3个字节多一点,而MIPS是4个字节);●寻址方式:只有一种内存寻址方式。

就是基地址加一个16位的地址偏移;●内存中的数据访问必须严格对齐(至少4字节对齐);●跳转指令只有26位目标地址,再加上2位的对齐位,可寻址28位的空间,即256M;●条件分支指令只有16位跳转地址,加上2位的对齐位,共18位寻址空间,即256K;●MIPS默认不把子函数的返回地址(就是调用函数的受害指令地址)存放到栈中,而是存放到$31寄存器中;这对那些叶子函数有利。

如果遇到嵌套的函数的话,有另外的机制处理;●高度的流水线:*MIPS指令的五级流水线:(每条指令都包含五个执行阶段)第一阶段:从指令缓冲区中取指令。

占一个时钟周期;第二阶段:从指令中的源寄存器域(可能有两个)的值(为一个数字,指定$0~$31中的某一个)所代表的寄存器中读出数据。

占半个时钟周期;第三阶段:在一个时钟周期内做一次算术或逻辑运算。

占一个时钟周期;第四阶段:指令从数据缓冲中读取内存变量的阶段。

从平均来讲,大约有3/4的指令在这个阶段没做什么事情,但它是指令有序性的保证。

占一个时钟周期;第五阶段:存储计算结果到缓冲或内存的阶段。

占半个时钟周期;所以一条指令要占用四个时钟周期;ARM:ARM处理器是一个32位元精简指令集(RISC)处理器架构,其广泛地使用在许多嵌入式系统设计。

●RISC(Reduced Instruction Set Computer,精简指令集计算机)RISC体系结构应具有如下特点:1)采用固定长度的指令格式,指令归整、简单、基本寻址方式有2~3种。

2)使用单周期指令,便于流水线操作执行。

3)大量使用寄存器,数据处理指令只对寄存器进行操作,只有加载/存储指令可以访问存储器,以提高指令的执行效率。

●ARM体系结构还采用了一些特别的技术,在保证高性能的前提下尽量缩小芯片的面积,并降低功耗:1)所有的指令都可根据前面的执行结果决定是否被执行,从而提高指令的执行效率。

2)可用加载/存储指令批量传输数据,以提高数据的传输效率。

●寄存器结构ARM处理器共有37个寄存器,被分为若干个组(BANK),这些寄存器包括:1)31个通用寄存器,包括程序计数器(PC指针),均为32位的寄存器。

2)6个状态寄存器,用以标识CPU的工作状态及程序的运行状态,均为32位,目前只使用了其中的一部分。

●指令结构ARM微处理器的在较新的体系结构中支持两种指令集:ARM指令集和Thumb指令集。

其中,ARM指令为32位的长度,Thumb指令为16位长度。

Thumb指令集为ARM指令集的功能子集,但与等价的ARM代码相比较,可节省30%~40%以上的存储空间,同时具备32位代码的所有优点。

问题二:arm 和x86在体系架构上的区别和各自的优点Arm 使用RISC 结构。

X86使用CISC 结构。

所以要说明两者的区别需要从RISC , CISC 的结构特点来入手:●CISC和RISC的比较CISC:CISC体系的指令特征使用微代码。

指令集可以直接在微代码记忆体(比主体的速度快很多)里执行,新设计的处理器,只需增加较少的电晶体就可以执行同样的指令集,也可以很快地编写新的指令集程式。

有庞大的指令集。

CISC体系的优缺点优点:能够有效缩短新指令的微代码设计时间,允许设计师实现CISC体系机器的向上相容。

新的系统可以使用一个包含早期系统的指令超集合,也就可以使用较早电脑上使用的相同软体。

另外微程式指令的格式与高阶语言相匹配,因而编译器并不一定要重新编写。

缺点:指令集以及晶片的设计比上一代产品更复杂,不同的指令,需要不同的时钟周期来完成,执行较慢的指令,将影响整台机器的执行效率。

RISC:1)精简指令集包含了简单、基本的指令,透过这些简单、基本的指令,就可以组合成复杂指令。

2)每条指令的长度都是相同的,可以在一个单独操作里完成。

3)大多数的指令都可以在一个机器周期里完成,并且允许处理器在同一时间内执行一系列的指令。

RISC体系的优缺点:优点:在使用相同的晶片技术和相同运行时钟下,RISC系统的运行速度将是CISC的2~4倍。

由于RISC处理器的指令集是精简的,它的记忆体管理单元、浮点单元等都能设计在同一块晶片上。

RISC处理器比相对应的CISC处理器设计更简单,所需要的时间将变得更短,并可以比CISC 处理器应用更多先进的技术,开发更快的下一代处理器。

缺点:多指令的操作使得程式开发者必须小心地选用合适的编译器,而且编写的代码量会变得非常大。

另外就是RISC体系的处理器需要更快记忆体,这通常都集成于处理器内部,就是L1 Cache (一级缓存)。

综合上面所述,若要再进一步比较CISC与RISC之差异,可以由以下几点来进行分析:1、指令的形成CISC因指令复杂,故采用微指令码控制单元的设计,而RISC的指令90%是由硬体直接完成,只有10%的指令是由软体以组合的方式完成,因此指令执行时间上RISC较短,但RISC所须ROM空间相对的比较大,至于RAM使用大小应该与程序的应用比较有关系。

2、定址模式CISC需要较多的定址模式,而RISC只有少数的定址模式,因此CPU在计算记忆体有效位址时,CISC占用的汇流排周期较多(是什么?)。

3、指令的执行CISC指令的格式长短不一,执行时的周期次数也不统一,而RISC结构刚好相反,故适合采用管线处理架构的设计,进而可以达到平均一周期完成一指令的方向努力。

因此,在设计上RISC较CISC简单,同时因为CISC的执行步骤过多,闲置的单元电路等待时间增长,不利于平行处理的设计,所以就效能而言RISC较CISC还是站了上风,但RISC因指令精简化后造成应用程式码变大,需要较大的程式记忆体空间,且存在指令种类较多等等的缺点。

综上来分析X86和ARM的区别:X86指令集有以下几个突出的缺点:通用寄存器组——对CPU内核结构的影响X86指令集只有8个通用寄存器。

所以,CISC的CPU执行是大多数时间是在访问存储器中的数据,而不是寄存器中的。

这就拖慢了整个系统的速度。

RISC系统往往具有非常多的通用寄存器,并采用了重叠寄存器窗口和寄存器堆等技术使寄存器资源得到充分的利用。

●解码——对CPU的外核的影响解码器,这是x86CPU才有的东西。

其作用是把长度不定的x86指令转换为长度固定的类似于RISC的指令,并交给RISC内核。

解码分为硬件解码和微解码,对于简单的x86指令只要硬件解码即可,速度较快,而遇到复杂的x86指令则需要进行微解码,并把它分成若干条简单指令,速度较慢且很复杂。

●寻址范围小——约束了用户需要(优点见CISC优点)ARM指令集的特点:●体积小,低功耗,低成本,高性能;●支持Thumb (16 位)/ARM (32 位)双指令集,能很好的兼容8 位/16 位器件;●大量使用寄存器,指令执行速度更快;●大多数数据操作都在寄存器中完成;●寻址方式灵活简单,执行效率高;●指令长度固定;●流水线处理方式●Load_store结构:在RISC中,所有的计算都要求在寄存器中完成。