华师网络学院作业答案 数字电路分析题

华师网络教育_本科_数字电路与逻辑设计_在线练习(整理)解读

目录26 = 64,28 = 256,29 = 512,210 = 1024,220 = 1024K = 1M 选择题TTLTTL电路如图所示, TTL电路实现逻辑功能Y=()。

答案:ATTL电路如图所示,其输出的逻辑函数Y=()。

P22 P77 或非门(电阻相当于输入高电平1)答案:ATTL电路如图所示,其逻辑函数Y=()。

P24 P77 异或门答案:BTTL电路如图所示,其逻辑函数Y=()。

P22 P77 与非门答案:A如图所示TTL电路实现的逻辑关系是()答案:D可以用作模拟开关,被称为双向开关的器件是()A.TTL三态门B.TTL与非门C.CMOS异或门D.CMOS传输门答案:D选择题真值表逻辑功能若采用正逻辑,如下真值表所表示的逻辑功能是()答案:D若采用正逻辑,如下真值表所表示的逻辑功能是()。

答案:A若采用正逻辑,如下真值表所表示的逻辑功能是()答案:C答案:B答案:B选择题存储器触发器只读存储器ROM的存储矩阵是()。

A.与阵列B.或阵列C.三态控制端D.与非阵列答案:B2048×8位的RAM有()位地址线。

2048 = 211A.8B.10C.11D.12答案:C1024×4位的RAM有()位数据线。

A.2B.4C.8D.16答案:B以下器件中具有脉冲鉴幅功能的器件是()。

A.反相器B.译码器C.施密特触发器D.单稳态触发器答案:Cn位寄存器由()个触发器构成。

A.2B.nC.2nD. 2 n答案:B将T触发器接成如图所示电路,其特性方程Q n+1 =()答案:D将JK触发器接成图中所示电路,其次态逻辑表达式:Q n+1=( )答案:B将D 触发器接成如图所示电路,其特性方程Qn+1=( )答案:D同步时钟RS 触发器与边沿RS 触发器具有( )。

A.相同的逻辑功能 B.相同的电路结构 C.相同的触发脉冲 D.相同的输出波形 答案:A选择题某二位时序电路的状态转换图如下所示,可以判断该时序电路是( )A.二进制加法计数器B.二进制减法计数器C.二位环型计数器D.三进制计数器 答案:A三位二进制计数器的有效状态数为( ) A.2 B.3 C.6 D.8 答案:DDAC实现的功能是( )A.反相输出B.数模转换C.模数转换D.输出缓冲答案:B以下所列器件中,能实现模数转换的是()A.双积分型ADCB.集成DACC.权电阻DACD.PROM答案:A如图所示电路,该电路为()A.二极管与门B.二极管或门C.MOS管反相器D.CMOS与非门答案:A组合逻辑电路中的竞争冒险现象是由于 ( )所引起的。

数字电路习题及答案

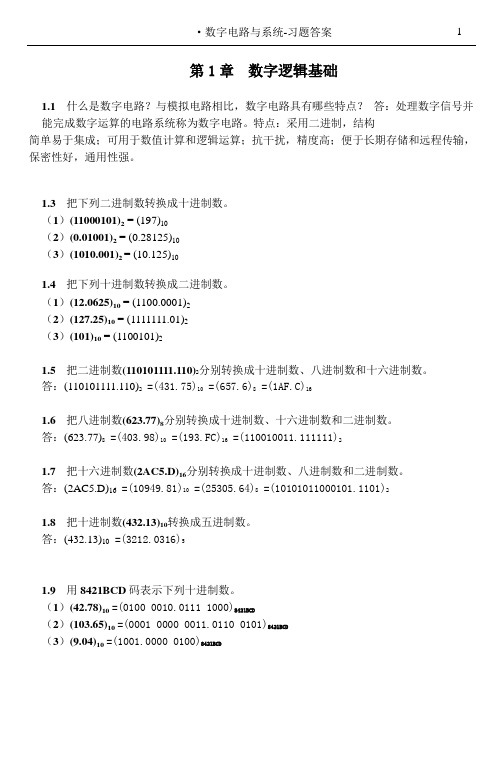

·数字电路与系统-习题答案1第1 章数字逻辑基础1.1 什么是数字电路?与模拟电路相比,数字电路具有哪些特点?答:处理数字信号并能完成数字运算的电路系统称为数字电路。

特点:采用二进制,结构简单易于集成;可用于数值计算和逻辑运算;抗干扰,精度高;便于长期存储和远程传输,保密性好,通用性强。

1.3 把下列二进制数转换成十进制数。

(1)(11000101)2 = (197)10(2)(0.01001)2 = (0.28125)10(3)(1010.001)2 = (10.125)101.4 把下列十进制数转换成二进制数。

(1)(12.0625)10 = (1100.0001)2(2)(127.25)10 = (1111111.01)2(3)(101)10 = (1100101)21.5 把二进制数(110101111.110)2分别转换成十进制数、八进制数和十六进制数。

答:(110101111.110)2 =(431.75)10 =(657.6)8 =(1AF.C)161.6 把八进制数(623.77)8分别转换成十进制数、十六进制数和二进制数。

答:(623.77)8 =(403.98)10 =(193.FC)16 =(110010011.111111)21.7 把十六进制数(2AC5.D)16分别转换成十进制数、八进制数和二进制数。

答:(2AC5.D)16 =(10949.81)10 =(25305.64)8 =(10101011000101.1101)21.8 把十进制数(432.13)10转换成五进制数。

答:(432.13)10 =(3212.0316)51.9 用8421BCD 码表示下列十进制数。

(1)(42.78)10 =(0100 0010.0111 1000)8421BCD(2)(103.65)10 =(0001 0000 0011.0110 0101)8421BCD(3)(9.04)10 =(1001.0000 0100)8421BCD数字电路与系统-习题答案21.10 把下列8421BCD 码表示成十进制数。

数字电路习题答案详解

受5号译码器输出控制。(1)当 CD=00时, 只1号译码器译码,其他译码器不译码。

当 CD=01时, 只2号译码器译码。(3)当 CD=10时, 只3号译码器译码。当 CD=11

时, 只4号译码器译码F1。0、F20、F30、F40

的逻辑函数表达式为:

第11页,共50页。

3-7 图示电路每一方框均为2线一4线译码器组成。其输出低电平有效。要求:

3-11

G AB

Y A BC

RC

G AB AB Y A BC ABC RC

需用七个与非门。而圈0则:

G A B AB

Y AB C ABC

R C

G AB

Y ABC RC

第25页,共50页。

3-11

试用六个与非门设计一个水箱控制电路。图为水箱示意图。A、B、C是三个电极。 当电极被水浸没时, 会有信号输出。水面在A,B间为正常状态,点亮绿灯G;水面在B、C间或在A以上为异常状态,点亮黄灯Y;水 面在C以下为危险状态.点亮红灯R。

其他电路:

第16页,共50页。

第17页,共50页。

第18页,共50页。

第19页,共50页。

3-10 试用与非门设计一个逻辑选择电路。S1、S0为

选择端,A、B为数据输入端。选择电路的 功能见下表。选择电路可以有反变量输入。

第20页,共50页。

3-10 F S1 AB S0 AB S0 A B S0 AB S1S0 A B F F S1 AB S0 AB S0 A B S0 AB S1S0 A B F S1S0 AB S1S0 ( A B) S1S0 ( A B AB) S1S0 ( A B AB )

择信号;比较结果F从74151 Y 反相输出端得到。

华中师范大学大一计算机专业数字电子技术试卷及答案

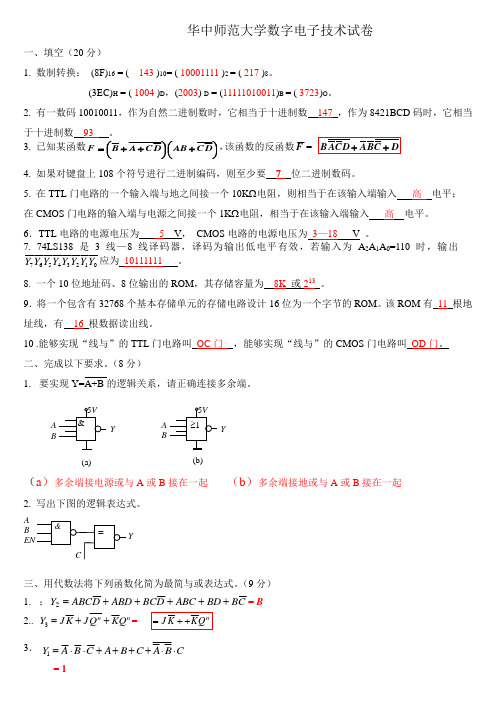

D C B A D C A B ++C B A C B A C B A Y ⋅⋅++++⋅⋅=1华中师范大学数字电子技术试卷一、填空(20分)1. 数制转换: (8F)16 = ( 143 )10= ( 10001111 )2 = ( 217 )8。

(3EC)H = ( 1004 )D ,(2003) D = (11111010011)B = ( 3723)O 。

2. 有一数码10010011,作为自然二进制数时,它相当于十进制数 147 ,作为8421BCD 码时,它相当于十进制数 93 。

3. 已知某函数⎪⎭⎫ ⎝⎛+⎪⎭⎫ ⎝⎛++=D C AB D C A B F ,该函数的反函数F = 4. 如果对键盘上108个符号进行二进制编码,则至少要 7 位二进制数码。

5. 在TTL 门电路的一个输入端与地之间接一个10K Ω电阻,则相当于在该输入端输入 高 电平; 在CMOS 门电路的输入端与电源之间接一个1K Ω电阻,相当于在该输入端输入 高 电平。

6.TTL 电路的电源电压为 5 V , CMOS 电路的电源电压为 3—18 V 。

7. 74LS138是3线—8线译码器,译码为输出低电平有效,若输入为A 2A 1A 0=110时,输出 01234567Y Y Y Y Y Y Y Y 应为 10111111 。

8. 一个10位地址码、8位输出的ROM ,其存储容量为 8K 或213 。

9.将一个包含有32768个基本存储单元的存储电路设计16位为一个字节的ROM 。

该ROM 有 11 根地址线,有 16 根数据读出线。

10 .能够实现“线与”的TTL 门电路叫 OC 门 ,能够实现“线与”的CMOS 门电路叫 OD 门。

二、完成以下要求。

(8分)1. 要实现Y=A+B 的逻辑关系,请正确连接多余端。

(a )多余端接电源或与A 或B 接在一起 (b )多余端接地或与A 或B 接在一起2. 写出下图的逻辑表达式。

华师网络学院作业答案-软件工程题目.

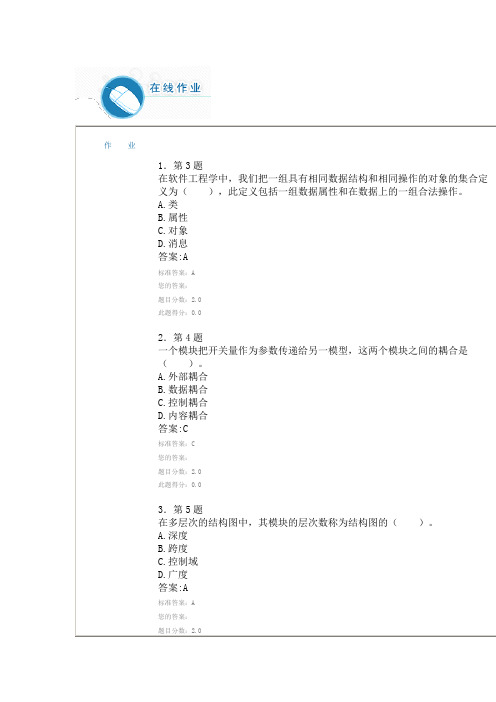

作业1.第3题在软件工程学中,我们把一组具有相同数据结构和相同操作的对象的集合定义为(),此定义包括一组数据属性和在数据上的一组合法操作。

A.类B.属性C.对象D.消息答案:A标准答案:A您的答案:题目分数:2.0此题得分:0.02.第4题一个模块把开关量作为参数传递给另一模型,这两个模块之间的耦合是()。

A.外部耦合B.数据耦合C.控制耦合D.内容耦合答案:C标准答案:C您的答案:题目分数:2.0此题得分:0.03.第5题在多层次的结构图中,其模块的层次数称为结构图的()。

A.深度B.跨度C.控制域D.广度答案:A标准答案:A您的答案:题目分数:2.0此题得分:0.04.第6题下列方式中,不是由数据元素组成数据方式的是()。

A.顺序B.层次C.选择D.重复答案:B标准答案:B您的答案:题目分数:2.0此题得分:0.05.第7题在对数据流的分析中,主要是找到中心变换,这是从()导出结构图的关键。

A.数据结构B.实体关系C.数据流图D.E-R图答案:C标准答案:C您的答案:题目分数:1.0此题得分:0.06.第8题数据流图是用于表示软件模型的一种图示方法,在下列可采用的绘图方法中,()是常采用的。

①自顶向下②自底向上③分层绘制④逐步求精A.全是B.①③④C.①③D.①②答案:B标准答案:B您的答案:题目分数:1.0此题得分:0.07.第11题结构化分析方法使用的描述工具()定义了数据流图中每一个图形元素。

A.数据流图B.数据字典C.判定表D.判定树答案:B标准答案:B您的答案:题目分数:1.0此题得分:0.08.第12题程序的三种基本控制结构是()。

A.过程、子程序和分程序B.顺序、选择和重复C.递归、堆栈和队列D.调用、返回和转移答案:B标准答案:B您的答案:题目分数:1.0此题得分:0.09.第13题Alpha测试是()。

A.由用户在开发者的场所进行B.由软件的最终用户在开发者的一个或多个客户场所进行C.是在不受开发者控制的环境中进行的D.是软件在开发者不能控制的环境中的“真实应用答案:A标准答案:A您的答案:题目分数:1.0此题得分:0.010.第14题模块内的某成分的输出是另一成分的输入,该模块的内聚度是()的。

华中师大《数字电路》练习测试题库及答案

华中师范大学网络教育学院《数字电路》练习测试题库及答案一、单项选择题。

1、在下列逻辑电路中,不是组合逻辑电路的是------ 。

A. 译码器B. 编码器C. 全加器D. 寄存器2、时序电路可以由____________组成。

A.门电路B. 触发器或门电路C. 触发器或触发器和门电路的组合3、时序电路输出状态的改变____________。

A. 仅与该时刻输入信号的状态有关B. 仅与时序电路的原状态有关C. 与以上两者皆有关4、组合电路的竞争和险象是指___________。

A. 输入信号有干扰时,在输出端产生了干扰脉冲B. 输入信号改变状态时,输出端可能出现的虚假信号C. 输入信号不变时,输出端可能出现的虚假信号5、仅具有“置0” “置1”功能的触发器叫___________。

A. JK触发器B. RS触发器C. D触发器6、译码电路的输入量是____________。

A. 二进制B. 十进制C. 某个特定的输入信号7、由n个JK触发器构成的扭环形计数器,其有效计数状态共有___________个A.n;B.2的n次方;C.2n8、编码电路和译码电路中,____________电路的输出是二进制代码。

A. 编码B. 译码C. 编码和译码9、ROM是指_____________。

A. 随机读写存储器B. 只读存储器C. 不可擦除式只读存储器D. 可擦可编程只读存储器10、寄存器在电路组成上的特点是____________。

A. 有CP输入端,无数据输入端B. 有CP输入端和数据输入端C. 无CP输入端,有数据输入端11、组合电路的竞争和险象是指___________。

A. 输入信号有干扰时,在输出端产生了干扰脉冲B. 输入信号改变状态时,输出端可能出现的虚假信号C. 输入信号不变时,输出端可能出现的虚假信号12、若使JK 触发器仅有翻转功能,控制端J 、K 正确接法是___________。

A .J= K= Q nB .J=K=1C .J=K=013、逻辑函数中的最小项_______________。

【奥鹏】19春华师《数字电路》在线作业[第三套]答案

![【奥鹏】19春华师《数字电路》在线作业[第三套]答案](https://img.taocdn.com/s3/m/40a7ae41a2161479171128e9.png)

【奥鹏】19春华师《数字电路》在线作业

试卷满分:100 试卷得分:100

一、单选题(共30题,60分)

1、常用的BCD码有().

A奇偶校验码

B格雷码

C8421码

D汉明码

[仔细阅读以上试题,并作出选择]

正确选择:C

2、在下列逻辑电路中,不是组合逻辑电路的有()A译码器

B编码器

C全加器

D寄存器

[仔细阅读以上试题,并作出选择]

正确选择:D

3、一位十六进制数可以用()位二进制数来表示

A1

B2

C4

D16

[仔细阅读以上试题,并作出选择]

正确选择:C

4、下列逻辑电路中为时序逻辑电路的是()

A变量译码器

B加法器

C数码寄存器

D数据选择器

[仔细阅读以上试题,并作出选择]

正确选择:C

5、与十进制数(53.5)10等值的数或代码为(). A(01010011.0101)8421BCD

B(36.8)16

C(100101.1)2

D(65.7)8

[仔细阅读以上试题,并作出选择]

正确选择:A。

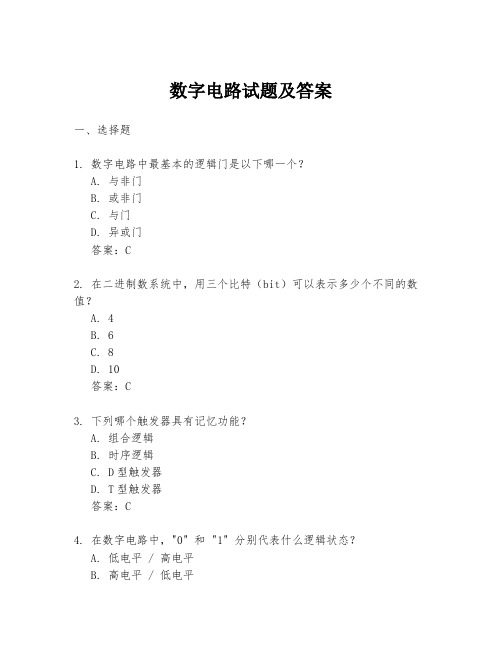

数字电路试题及答案

数字电路试题及答案一、选择题1. 数字电路中最基本的逻辑门是以下哪一个?A. 与非门B. 或非门C. 与门D. 异或门答案:C2. 在二进制数系统中,用三个比特(bit)可以表示多少个不同的数值?A. 4B. 6C. 8D. 10答案:C3. 下列哪个触发器具有记忆功能?A. 组合逻辑B. 时序逻辑C. D型触发器D. T型触发器答案:C4. 在数字电路中,"0" 和 "1" 分别代表什么逻辑状态?A. 低电平 / 高电平B. 高电平 / 低电平C. 接地 / 供电D. 禁用 / 启用答案:A5. 以下哪种类型的逻辑门是使用晶体管实现开关功能的?A. 模拟门B. 数字门C. 模拟数字门D. 晶体管逻辑门答案:D二、填空题1. 在数字电路中,一个______门输出的高电平可以驱动多个输入端,而不会改变输出电平。

答案:或门2. _______是数字电路设计中的一种基本方法,它将复杂的电路分解为更简单的子电路。

答案:模块化设计3. 在数字电路中,一个______触发器在时钟信号的上升沿改变状态,而______触发器在下降沿改变状态。

答案:D型;JK型4. 一个4位二进制计数器的最大输出值是______。

答案:155. 在数字电路中,______是一种用于存储数据的电路,它可以在没有时钟信号的情况下保持信息。

答案:触发器三、简答题1. 请简述数字电路与模拟电路的主要区别。

答:数字电路处理的是离散的信号,通常只有两种状态(如高电平代表“1”,低电平代表“0”),而模拟电路处理的是连续变化的信号。

数字电路的主要优点是抗干扰能力强,易于实现逻辑运算和存储功能,而模拟电路则更擅长处理连续变化的信号,如音频和视频信号。

2. 什么是组合逻辑和时序逻辑?答:组合逻辑是指其输出仅依赖于当前输入信号的逻辑电路,不包含存储元件,如与门、或门和非门等。

时序逻辑则包含存储元件(如触发器),其输出不仅依赖于当前的输入信号,还依赖于历史状态,因此具有记忆功能。

数字电路习题及答案

数字电路习题及答案项目一一.填空题1.电子电路中的信号可分为两类。

一类是时间的连续信号,称为__________,另一类是时间和幅度都是离散的(即不连续的信号),称为__________。

(模拟信号、数字信号)2.所谓数字信号,是指可以用两种逻辑电平__________和__________来描述的信号。

(0、1)3.在数字电路中,应用最为广泛的是__________集成门电路和__________集成门电路。

(TTL、CMOS)4.基本的逻辑关系有三种:__________、__________、__________。

(逻辑与、逻辑或、逻辑非)5.任何逻辑函数都可以用__________、__________、__________和__________四种形式来表示。

(逻辑表达式、逻辑图、真值表、卡诺图)6.常用的数制有__________、__________、__________和__________等。

(十进制、二进制、八进制、十六进制)7.BCD码有很多种形式,常用的有__________、__________、__________、__________、__________等。

(8421码、余3码、格雷码、2421码、5421码)8.在实践中最常用的逻辑函数的化简方法是__________法,它比较适用于__________变量以内的逻辑函数的化简。

(卡诺图化简、四)9.数字电路按逻辑功能和电路结构的不同特点可划分为两大类,一类称为__________,另一类称为__________。

(组合逻辑电路、时序逻辑电路)10.能实现基本和常用逻辑运算的电子电路称为__________。

(门电路)11.仿真软件__________是学习数字电路有效的辅助工具,它可以在计算机上完成电路的连接及测试,大大提高数字电路学习的效率。

(Multisim 10)二.简答题1.与模拟电路相比,数字电路具有哪些优点?答:与模拟电路相比,数字电路具有以下显著的优点:(1)结构简单,便于集成化、系列化生产,成本低廉,使用方便。

数字电路试题及答案

数字电路试题及答案一、选择题(每题2分,共20分)1. 数字电路中最基本的逻辑关系是:A. 与逻辑B. 或逻辑C. 非逻辑D. 异或逻辑2. 以下哪个不是数字电路的优点?A. 高速度B. 低功耗C. 可编程性D. 易于制造3. 一个3输入的与门,当所有输入都为1时,输出为:A. 0B. 1C. 2D. 34. 触发器的主要用途是:A. 存储一位二进制信息B. 进行算术运算C. 执行逻辑判断D. 放大信号5. 下列哪个不是组合逻辑电路的特点?A. 输出只依赖于当前的输入B. 输出可以延迟输入C. 没有记忆功能D. 可以进行复杂的逻辑运算二、填空题(每空2分,共20分)6. 一个典型的数字电路由________、________和输出三部分组成。

7. 一个4位二进制计数器可以计数的最大数值是________。

8. 一个D触发器的两个主要输入端是________和________。

9. 在数字电路中,________是一种常用的同步信号,用于协调电路的时序。

10. 一个3-8译码器可以将3位二进制信号转换为________种可能的输出状态。

三、简答题(每题15分,共30分)11. 简述数字电路与模拟电路的主要区别。

12. 解释什么是时钟信号,并说明它在数字电路中的作用。

四、计算题(每题15分,共30分)13. 给定一个逻辑表达式 Y = A'B + AB',使用卡诺图化简该表达式,并画出相应的逻辑电路图。

14. 设计一个2位二进制计数器,使用D触发器实现,并说明其工作原理。

答案一、选择题1. 答案:A(与逻辑)2. 答案:D(易于制造)3. 答案:B(1)4. 答案:A(存储一位二进制信息)5. 答案:B(输出可以延迟输入)二、填空题6. 答案:输入、处理7. 答案:15(2^4 - 1)8. 答案:数据输入(D)、时钟输入(CLK)9. 答案:时钟信号(Clock Signal)10. 答案:8三、简答题11. 数字电路与模拟电路的主要区别在于:数字电路处理的是离散的数字信号,而模拟电路处理的是连续的模拟信号。

华师网络学院作业答案-数字电路分析题

华师网络学院作业答案-数字电路分析题-标准化文件发布号:(9456-EUATWK-MWUB-WUNN-INNUL-DDQTY-KIITTL电路及输入A、B、C波形如图所示,写出其输出逻辑表达式,并画输出Y的波形图。

TTL电路及输入A、B、C波形如图所示,写出输出逻辑表达式,并画出输出Y的波形图。

答案:TTL电路及输入A、B波形如图所示,写出其输出逻辑表达式,并画输出Y的波形图。

答案:如图所示电路是边沿D触发器,要求:(1)写出触发器的次态逻辑表达式;(2)给出CP和A的波形如下,画出触发器的状态波形。

设触发器初始状态为0。

答案:译码器74LS138和与非门构成的逻辑电路如图所示。

请写出最简的输出逻辑表达式。

答案:同步十六进制计数器74LS161构成电路如下图所示。

要求:画出电路的状态转换图,说明该电路的逻辑功能。

答案:分析如图所示电路,要求:(1)写出输出Y的逻辑表达式;(2)由逻辑表达式列写真值表;(3)说明电路功能。

答案:图为用译码器74LS138和与非门构成的逻辑电路。

请写出其逻辑表达式,并将其化简为最简的与或式。

答案:二个JK触发器构成的时序电路如下图所示。

要求:(1).写出时钟方程和状态方程;(2).画对应的波形图;(3)说明电路功能。

设触发器初始状态均为0。

答案:根据如图所示ROM,写出Y1、Y2的逻辑表达式,并将Y1、Y2化简为最简式。

答案:根据如图所示ROM,(1)ROM的存储容量是:;(2)写出Y1、Y2的逻辑表达式,并将Y1、Y2化简为最简逻辑表达式。

答案:解:(1)ROM的存储容量是: 4×2 ;(2)写输出逻辑表达式并化简函数:三个D触发器构成时序电路如下图所示。

要求:写出状态方程,状态转换图,说明该时序电路的逻辑功能。

设触发器初始状态Q1 Q2 Q3 =110答案:如图所示电路是边沿T触发器,要求:(1)写出触发器的次态逻辑表达式;(2)给出CP的波形如下,画出触发器的状态波形。

华中师范大学网络学院《数字逻辑》试题库及答案

华中师范大学网络学院《数字逻辑》试题库及答案一、选择题1. 和二进制数(1100110111.001)等值的十六进制数学是( )。

A.337.2B.637.2C.1467.1D.c37.42. 是8421BCD 码的是( )A.1010B.0101C.1100D.11113. 和二进制码1100对应的格雷码是( )A.0011B.1100C.1010D.01014. 如下图,电路实现的逻辑功能F=( )A.ABB.0C.A+BD.15. TTL 电路中,高电平V H 的标称值是( )A.0.3VB.2.4VC.3.6VD.5V 6. 和逻辑式ABC A +__相等的式子是( ) A.ABC B.1+BC C.A D.BC A +___7. 若干个具有三态输出的电路输出端接到一点工作时,必须保证( )A.任何时候最多只能有一个电路处于三态,其余应处于工作态。

B.任何时候最多只能有一个电路处于工作态,其余应处于三态。

C.任何时候至少要有两个或三个以上电路处于工作态。

D.以上说法都不正确。

8. A+B+C+__A +A __B =( )A.AB.__AC.1D.A+B+C9. 下列等式不成立的是( )A.B A B A A +=+__B.(A+B)(A+C)=A+BCC.AB+AC+BC=AB+BCD.1________=+++B A AB B A B A10. ) (F ,)6,5,4,3,2,1,0(C)B,,F(A ==∑则m A.ABC B.A+B+C C.______C B A ++ D. ______C B A11. 欲对全班53个同学以二进制代码编码表示,最少需要二进制的位数是( )A.5B.6C.10D.5312. 一块数据选择器有三个地址输入端,则它的数据输入端应有( )。

A.3B.6C.8D.113. 或非门构成的基本RS 触发器,输入端SR 的约束条件是( ) A.SR=0 B.SR=1 C.1____=+R S D.0____=+R S14. 在同步方式下,JK 触发器的现态Q n = 0,要使Q n+1 = 1,则应使( )。

数字电路考试题目及答案

数字电路考试题目及答案一、选择题(每题2分,共20分)1. 以下哪个选项是数字电路中的基本逻辑门?A. 与门B. 或门C. 非门D. 所有以上选项答案:D2. 在数字电路中,一个输入为0,另一个输入为1时,或门的输出是什么?A. 0B. 1C. 不确定D. 无输出答案:B3. 一个触发器的初始状态是0,当触发器的时钟信号上升沿到来时,触发器的状态会如何变化?A. 保持不变B. 变为1C. 变为0D. 随机变化答案:B4. 下列哪个不是数字电路中的计数器类型?A. 二进制计数器B. 十进制计数器C. 十六进制计数器D. 模拟计数器答案:D5. 在数字电路中,一个D触发器的Q输出和Q'输出之间的关系是什么?A. 相同B. 相反C. 无关系D. 有时相同有时相反答案:B6. 一个4位二进制计数器能表示的最大数值是多少?A. 15B. 16C. 255D. 256答案:B7. 以下哪个不是数字电路中的编码方式?A. 二进制编码B. 格雷码编码C. 十进制编码D. 模拟编码答案:D8. 在数字电路中,一个异或门的输出为1的条件是什么?A. 输入相同B. 输入不同C. 至少一个输入为0D. 至少一个输入为1答案:B9. 一个3线到8线解码器有多少个输入线?A. 3B. 4C. 5D. 8答案:A10. 在数字电路中,一个锁存器和触发器的主要区别是什么?A. 锁存器可以保持一个稳定的状态,而触发器不能B. 触发器可以保持一个稳定的状态,而锁存器不能C. 两者没有区别D. 两者都是存储设备答案:B二、填空题(每题2分,共20分)1. 在数字电路中,一个3位二进制计数器可以表示的最大数值是__7__。

2. 如果一个触发器的J和K输入都是1,则触发器的状态将会__翻转__。

3. 在数字电路中,一个4位二进制计数器有__16__个不同的状态。

4. 一个D触发器的输出Q在时钟信号的__上升沿__时更新。

5. 一个3线到8线解码器可以产生__8__个输出。

数字电路试题及答案

数字电路试题及答案一、选择题(每题2分,共20分)1. 在数字电路中,最基本的逻辑关系是:A. 与逻辑B. 或逻辑C. 非逻辑D. 异或逻辑答案:A2. 一个3输入的与门,当所有输入都为高电平时,输出为:A. 低电平B. 高电平C. 浮空D. 不确定答案:B3. 触发器的两个稳定状态是:A. 0和1B. 正和负C. 高和低D. 真和假答案:A4. 下列哪个不是数字电路的优点?A. 高速度B. 高稳定性C. 低功耗D. 易于集成答案:C5. 以下哪个是组合逻辑电路的特点?A. 输出状态只与当前输入有关B. 具有记忆功能C. 输出状态与过去输入有关D. 以上都不是答案:A6. 一个D触发器的Q端在时钟信号上升沿触发时,其输出将:A. 保持不变B. 变为0C. 变为1D. 翻转答案:D7. 以下哪个逻辑门不是基本逻辑门?A. 与门B. 或门C. 非门D. 异或门答案:D8. 以下哪个是数字电路设计中的同步设计?A. 所有信号在同一个时钟信号下操作B. 信号在不同的时钟信号下操作C. 信号没有时钟信号D. 以上都不是答案:A9. 一个4位二进制计数器,其计数范围是:A. 0到3B. 0到7C. 0到15D. 1到4答案:C10. 在数字电路中,布尔代数的基本原理不包括:A. 幂等律B. 互补律C. 反演律D. 欧拉定律答案:D二、简答题(每题10分,共30分)1. 简述数字电路与模拟电路的主要区别。

答:数字电路主要处理离散的数字信号,使用二进制数字表示信息,具有较高的抗干扰能力,易于实现大规模集成。

而模拟电路处理连续变化的模拟信号,使用电压或电流的连续变化来表示信息,通常需要较高的精度和稳定性。

2. 解释什么是时序逻辑电路,并给出一个例子。

答:时序逻辑电路是一种数字电路,其输出不仅依赖于当前的输入,还依赖于电路的历史状态。

这种电路通常包含存储元件,如触发器或寄存器。

一个常见的例子是计数器,它可以按照时钟信号的上升或下降沿进行计数。

《数字电路》网上作业题及答案

[9006]《数字电路》第一次作业[填空题]叫数制。

参考答案:把多位数码中每一位的构成方法以及从低位到高位的进位规则[论述题]1、将下列二进制数转换为等值的八进制数和十六进制数。

(1)(1110.0111)2 ;(2)(1001.1101)2参考答案:(1)(16.34)8 和(E.7)16(2)(11.64)8 和(9.D)16[填空题]叫二进制算术运算。

参考答案:当两个二进制数码表示两个数量大小时,它们之间可以进行数值运算第二次作业[论述题]2、逻辑函数的公式化简法的概念及其常用方法。

参考答案:1、最小项有下列性质:(1)每一个最小项都有一组也只有一组使其值为1的对应变量取值;(2)任意两个不同的最小项之积,值恒为0;(3)变量全部最小项之和,值恒为1。

2、公式化简法,就是在与或表达式的基础上,利用公式和定理,消去表达式中多余的乘积项和每个乘积项中多余的因子,求出函数的最简与或式。

常用方法有并项法、吸收法、消去法、配项消项法[判断题]物理量的变化在时间上或在数值上是间断的,我们把这一类物理量称为模拟量。

参考答案:错误[判断题]在用数码表示不同的事物时,这些数码己没有数量大小的含义,所以将它们称为代码。

参考答案:正确[判断题]二进制数的符号在数字电路中的表示方法有原码、反码和补码。

参考答案:正确[判断题]ASCII码己经由国际标准化组织(ISO)认定为国际通用的标准代码。

参考答案:正确[判断题]卡诺图的主要缺点是随着变量个数的增加,图形也更简单。

参考答案:错误[判断题]在八进制数中,每一位用1-8八个数码表示。

参考答案:错误[判断题]基本的逻辑运算只有与、或、非三种。

参考答案:正确[判断题]逻辑变量的取值可以是0,1,2。

参考答案:错误第三次作业[论述题]1、什么是组合电路?2、组合电路的基本分析方法和设计方法是什么?参考答案:1、任何时刻电路的稳定输出,仅仅只决定于该时刻各个输入变量的取值,这样的逻辑电路叫做组合电路。

数字电路习题参考答案详解

第27页,共29页。

4.24 判断用下列函数构成的电路是否存在冒险?冒险的类型?

(1)F=AB+ABC

AC

F

00

0

01

0

10

B

1 1 B+B

0型冒险

(4)F=AB+AB

11 0 0 1 1

10 1 0 0 1

D1 D3 D7 D5

10

D

第25页,共29页。

(3)三变量多数表决电路。

AB

D0 D2 D6 D4

C 00 01 11

0 100 0 1 0

1 0 1 01 1

D1 D3 D7 D5

10

第26页,共29页。

4.23 用数据选择器组成的电路如图所示,求输出Y 的表达式。

又Si m1 m2 m4 m7 Ai BiCi1 Ai BiCi1 Ai BiCi1 Ai BiCi1

比较得: D0=D3= Ci-1 D1=D2= Ci-1

且 Ci m3 m5 Ai Bi Ai BiCi1 Ai BiCi1 Ai Bi

Y m0 D0 m1D1 m2 D2 m3D3

D0 B 0 0 1 1 0 1 1111

D1 1

D2 B D3 1

A C

B1

第22页,共29页。

(4)二变量异或表达式。

A

B

0

00

1 AB

1

11 0

D0=0

AB

D3=0

《数字电路》作业参考答案

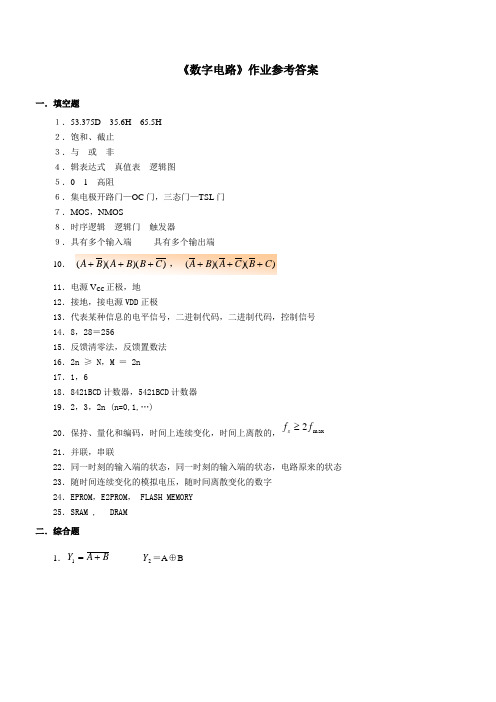

《数字电路》作业参考答案一.填空题1.53.375D 35.6H 65.5H 2.饱和、截止 3.与 或 非4.辑表达式 真值表 逻辑图 5.0 1 高阻6.集电极开路门—OC 门,三态门—TSL 门 7.MOS ,NMOS10.1112.接地,接电源VDD 正极13.代表某种信息的电平信号,二进制代码,二进制代码,控制信号 14.8,28=25615.反馈清零法,反馈置数法 16.2n ≥ N ,M = 2n 17.1,618.8421BCD 计数器,5421BCD 计数器 19.2,3,2n (n=0,1,…)20.保持、量化和编码,时间上连续变化,时间上离散的,max 2f f s ≥21.并联,串联22.同一时刻的输入端的状态,同一时刻的输入端的状态,电路原来的状态 23.随时间连续变化的模拟电压,随时间离散变化的数字 24.EPROM ,E2PROM , FLASH MEMORY 25.SRAM , DRAM 二.综合题1.B A Y +=1 2Y =A ⊕B2.将L1的接地输入端设为+Vcc,将Y2的+Vcc改为接地3.J n +K Q n得4. 由Q n+1=D 和Q n+1=QnJ n +K QD=Q2数字电路第 3 页 共 10 页5.6.7.1F A B =+, 2F AB =8.1111n n n Q S RQ A BQ +=+=+, 22222n n n n nQ JQ KQ AQ BQ =+=+9.对D 触发器有 1n QD +=,对RS 触发器有 111n n Q S RQ +=+令 n D S RQ =+,化为与非表达式 nD S RQ =,由表达式得D 触发器到RS 触发器得转换电路,如下图所示。

410.11.L AB BC D E AB BC D E ==+++12.解:对于TTL 门来说,高电平的标准电压值为:VOH=2.4V ,VIH=2V 。

题中(2)、(3),由于输入电压分别为2V 和3.6V ,属高电平,故为逻辑1。

数字电路试题及答案

数字电路试题及答案一、单项选择题(每题2分,共10分)1. 在数字电路中,最基本的逻辑门是:A. 与门B. 或门C. 非门D. 异或门答案:C2. 以下哪个不是数字电路的特点?A. 离散性B. 线性C. 确定性D. 可预测性答案:B3. 一个D触发器的输入端是:A. SB. RC. DD. Q答案:C4. 在TTL逻辑门中,高电平的最小值是:A. 0.8VB. 2.0VC. 3.5VD. 5.0V答案:A5. 以下哪个是组合逻辑电路?A. 计数器B. 寄存器C. 译码器D. 触发器答案:C二、填空题(每题2分,共10分)1. 一个标准的二进制数由______和______组成。

答案:0,12. 一个完整的触发器可以存储______位二进制信息。

答案:13. 一个4位二进制计数器可以计数到______。

答案:154. 一个8x3的译码器可以产生______个输出。

答案:85. 在数字电路中,______是最小的可识别信号单位。

答案:位三、简答题(每题5分,共20分)1. 简述数字电路与模拟电路的主要区别。

答案:数字电路处理的是离散信号,具有确定性,而模拟电路处理的是连续信号,具有不确定性。

2. 解释什么是上升沿触发。

答案:上升沿触发是指在时钟信号的上升沿(从低电平变为高电平)时,触发器会根据输入信号更新其状态。

3. 什么是同步电路和异步电路?答案:同步电路是指电路中的各个部分都由同一个时钟信号控制,而异步电路则没有统一的时钟信号,各个部分可以独立工作。

4. 描述一个典型的数字电路设计流程。

答案:数字电路设计流程通常包括需求分析、逻辑设计、电路设计、仿真测试、PCB布局布线、调试和验证。

四、计算题(每题10分,共20分)1. 给定一个逻辑表达式:Y = AB + A'C,请计算当A=0, B=1, C=0时,Y的值。

答案:Y = 0*1 + 0'*0 = 0 + 1 = 12. 一个4位二进制计数器,初始状态为0000,每次计数加1,求经过5次计数后的状态。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

TTL电路及输入A、B、C波形如图所示,写出其输出逻辑表达式,并画输出Y 的波形图。

TTLABCY的波形图。

、、电路及输入波形如图所示,写出输出逻辑表达式,并画出输出

答案:

TTLABY的波形图。

波形如图所示,写出其输出逻辑表达式,并画输出电路及输入、

: 答

案.

D12CPA的波形如下,画出触发(和)给出如图所示电路是边沿触发器,要求:()写出触发器的次态逻辑表达式;0。

器的状态波形。

设触发器初始状态为

答案:

74LS138和与非门构成的逻辑电路如图所示。

请写出最简的输出逻辑表达式。

译码器

: 答

案.

74LS161构成电路如下图所示。

要求:画出电路的状态转换图,说明该电路的逻辑功能。

同步十六进制计数器

答案:

1Y23)说明电路功能。

)由逻辑表达式列写真值表;((分析如图所示电路,要求:)写出输出的逻辑表达式;

(

: 答

案.

和与非门构成的逻辑电路。

请写出其逻辑表达式,并将其化简为最简的与或式。

图为用译码器74LS138

答案:

二个JK触发器构成的时序电路如下图所示。

要求:(1).写出时钟方程和状态方程;(2).画对应的波形图;(3)说明电路。

0功能。

设触发器初始状态均为

: 答案

Y化简为最简式。

Y的逻辑表达式,并将Y、ROM根据如图所示,写出Y、2211

: 答案

,根据如图所示ROM;ROM1()的存储容量是:(2)写出Y、Y的逻辑表达式,并将Y、Y化简为最简逻辑表达式。

2121.

: 答案解:的存储容量是:4×2 ROM(1);

(2)写输出逻辑表达式并化简函数:

三个D触发器构成时序电路如下图所示。

要求:写出状态方程,状态转换图,说明该时序电路的逻辑功能。

设触发器=110 QQ Q初始状态321

答案:

如图所示电路是边沿T触发器,要求:(1)写出触发器的次态逻辑表达式;(2)给出CP的波形如下,画出触发器的状。

态波形。

设触发器初始状态为0

: 答

案.

如图所示RAM,1()RAM 的存储容量是:

(2)RAM的地址线为:位;位线为:位

答案:

解:

(1)RAM的存储容量是:2048×2

(2)RAM的地址线为:11 位;位线为: 2 位

(3)

波形如下,画输出波形。

、CBA分析如下图所示电路,写出其输出的逻辑表达式。

给出输入、

: 答

案.

81数据选择器功能表和电路连接图如图所示。

请写出输出逻辑表达式并化简为最简与或表达式。

某选

答案:

分析如图所示ROM,写出输出Y的逻辑表达式,并将Y化简为最简与或式。

: 答

案.

的波形。

电路的输出逻辑表达式,并根据输入信号的波形,画输出YTTL写出如图

答案:

如图所示电路是边沿D触发器,要求:(1)写出触发器的次态逻辑表达式;(2)给出CP的波形如下,画出触发器的状。

态波形。

设触发器初始状态为0

: 答

案.

ROM,如图所示(1)ROM 的存储容量是:

(2)ROM的地址线为:位;位线为:位

(3)分析如图逻辑电路,写出其逻辑表达式Y,并将其化简为最简与或式。

答案:

41数据选择器功能表及电路连接图如下所示,写输出逻辑表达式并化简。

选某

答案:

四选一数据选择器功能表及电路连接图如下所示,写输出逻辑表达式,并化简。

答案:

TTLABCY的波形图。

、电路及输入波形如图所示,写出输出逻辑表达式,并画输出、

答案:

的波形A和)写出触发器的次态逻辑表达式;(1CP)给出2触发器,要求:(如图所示电路是边沿T如下,画出触发器的状态波形。

设触发器初始状态为0。

: 答

案.。