DSP寄存器

DSP课件NO34寄存器

通用寄存器

用于存储临时数据,可用于算术运算、逻辑操 作和数据传输。

特殊寄存器

具有特定的功能和用途,例如程序计数器、指 令寄存器和堆栈指针。

控制器寄存器

用于控制DSP的特定功能,例如定时器、中断控

状态寄存器

记录DSP的状态信息,例如中断状态、运行模式

寄存器的分类和特点

寄存器可以根据其功能和特点进行分类,例如通用寄存器和特殊寄存器之间的区别,以及控制器寄存器 和状态寄存器的独特特点。

输。

令的跳转和访存操作。地址存器提供

了程序计数器、堆栈指针等特殊寄存

器。

寄存器的读写操作

寄存器支持数据的输入和输出操作,包括数据的写入和读出,以及控制信号的设置和查询。

1 数据输入输出

通过写入和读出操作,实现数据的输入和输出。数据可以用于运算、传输和存储。

2 寄存器Байду номын сангаас入和读出

通过设置和查询指定的控制信号,实现寄存器的写入和读出。控制信号包括使能信号、 写使能和读使能。

直接编址

使用寄存器的地址直接访问和操作数据,适合简单的数据处理。

间接编址

使用寄存器中保存的地址作为数据的地址,允许动态计算和变换地址,适合复杂的数据结构 和算法。

控制器寄存器和状态寄存器的使用

控制器寄存器和状态寄存器在DSP中起到关键作用,用于控制DSP的行为和监测DSP的状态。

控制器寄存器

用于设置DSP的工作模式、功能和参数,例如启 动、停止、时钟选择和定时器设置。

状态寄存器

记录DSP的状态信息,例如中断状态、错误标志 和运行模式。

数据寄存器和地址存器的作用分析

数据寄存器和地址寄存器是DSP中重要的组成部分,用于存储和操作数据和地址。

TI DSP位域寄存器文件(Bit Field and Register-File Structure)结构

DSP28335 GPIO模块的各寄存器详解

DSP28335 GPIO模块DSP28335 GPIO模块分为三类IO口:PORTA(0-31),PORTB(32-63),PORTC(64-87)对GPIO模块的设置主要通过三类寄存器来完成,分别是:控制寄存器、数据寄存器、中断寄存器。

1、控制寄存器GPxCTRL; // GPIO x Control Register (GPIO0 to 31)//设置采样窗周期T=2*GPXCTRL*Tsysclk;GPxQSEL1; // GPIO x Qualifier Select 1 Register (GPIO0 to 15)(32-47)GPxQSEL2; // GPIO x Qualifier Select 2 Register (GPIO16 to 31)(48-63) //每两位控制一个引脚,确定是3周期采样还是6周期采样或者不用采样GPxMUX1; // GPIO x Mux 1 Register (GPIO0 to 15)(32-47)(64-79)GPxMUX2; // GPIO x Mux 2 Register (GPIO16 to 31)(48-63)(80-95)//配置各个引脚的功能,0:I/O功能,1:外设功能。

GPxDIR; // GPIO x Direction Register (GPIO0 to 31)(32-63)(64-95)//配置每个引脚是输入还是输出,0:数字量输入;1:数字量输出。

GPxPUD; // GPIO x Pull Up Disable Register (GPIO0 to 31)(32-63)(64-95) //使能或禁止jie口的内部上拉2、数据寄存器GPxDAT; // GPIO Data Register (GPIO0 to 31)(32-63)(64-95)GPxSET; // GPIO Data Set Register (GPIO0 to 31)(32-63)(64-95)GPxCLEAR; // GPIO Data Clear Register (GPIO0 to 31)(32-63)(64-95)GPxTOGGLE; // GPIO Data Toggle Register (GPIO0 to 31)(32-63)(64-95)3、中断寄存器GPIOXINT1SEL; // XINT1 GPIO Input SelectionGPIOXINT2SEL; // XINT2 GPIO Input SelectionGPIOXNMISEL; // XNMI_Xint13 GPIO Input SelectionGPIOXINT3SEL; // XINT3 GPIO Input SelectionGPIOXINT4SEL; // XINT4 GPIO Input SelectionGPIOXINT5SEL; // XINT5 GPIO Input SelectionGPIOXINT6SEL; // XINT6 GPIO Input SelectionGPIOXINT7SEL; // XINT7 GPIO Input SelectionGPIOLPMSEL; // Low power modes GP I/O input select 可以对GPIO0-63进行外部中断设置。

DSP存储空间的配置

DSP存储空间的配置在DSP的开发过程中,开发者难免会遇到DSP芯片内部存储器和片外扩展存储器的配置等问题。

本文以TMS320C54x系列DSP为例,讨论DSP存储空间的分配问题。

存储器空间'C54x系列DSP存储器分为三个独立选择的空间—程序、数据和I/O,其中程序存储器存放待执行的指令和执行中所用的系数(常数),可使用片内或片外的RAM、ROM或EPROM等来构成;数据存储器存放指令执行中产生的数据,可使用片内或片外的RAM和ROM来构成。

I/O存储器存放与映象外围接口相关的数据,也可以作为附加的数据存储空间使用。

这三个空间的寻址范围取决于DSP芯片地址线数目。

例如,'C54x系列DSP 从'C548开始,芯片有23根地址线,具有8M字节存储空间寻址能力。

'C54x通过包含在处理器工作方式的状态寄存器(PMST)中的3个状态位,选择片内存储器作为程序空间或数据空间。

这3个状态位是:1.MP/MC位。

MP/MC=0,则片内ROM安排到程序空间;MP/MC=1,则片内ROM不安排到程序空间。

2.OVLY位。

OVLY=1,则片内RAM安排到程序和数据空间;OVLY=0,则片内RAM只安排到数据存储空间。

3.DROM位。

当DROM=1,则部分片内ROM安排到数据空间;DROM=0,则片内ROM不安排到数据空间。

程序设计者可根据不同的需求,相应的配置这3个位,使系统的存储空间满足应用要求。

同时,为了扩展'C54x系列DSP的寻址空间,还增加了一个额外的存储器映像寄存器—程序计数器扩展寄存器XPC,以及6条寻址扩展程序空间的指令。

以TMS320C5410为例,它的程序空间分成128页面,每页64K字。

该64K字程序空间分为两部分:一部分是公共的32K 字,另一部分是各自独立的32K字。

公共存储器为所有页面共享,每个页面独立的32K字存储器只能按指定的页面号寻址,这个页面号由XPC寄存器设定。

TMS320C2000系列DSP寄存器及初始化(精)

TMS320C2000系列DSP寄存器及初始化 TMS320LF240X系列DSP使用时,在掌握了其工作原理和过程之后,就要熟练使用DSP自带的一些资源如:IO口、DSRM、SRAM、EVA、,EVB、SCI、SPI、ADC和WD等等;对这些资源的使用很重要的一点就是对其合理配置和初始化,初始化的关键就是对其相关寄存器的设置,设置寄存器必须了解各位的含义,记住每位的含义是不大现实的;为此,我们专门设计了DSP初始化子程序,注明每个模块所用到的寄存器以及每位的含义,以方便设计。

;Init_DSP.asm .text ;---------------------------------------------------------- ; function: Init DSP DSP初始化子程序 ; input: ------ ; output: ------ ; usege:aCC ;========================================================== DSP_Init: ;======================================================= === ; DSP系统初始化 ;---------------------------------------------------------- ;ST0------ ;15~~13 12 11 10 9 8~~0 ;ST0 ARP OV OVM 1 INTM DP ; 15~13 12 11 10 9 8~5 4 3~2 1~0 ;ST1 ARB CNF TC SXM C 1 XF 1 PM ; ARB---辅助寄存器指针缓冲器:当ARP 被加载到ST0,除了使用LST指令外,原有的 ; ARP值被复制到ARB中;当通过LST#1指令加载ARB时,也把相同的ARB ; 值复制到ARP ; ; ARP----辅助寄存器指针:ARP选择间接寻址时当前的辅助寄存器AR;当ARP被加载 ; 时,原有的ARP值被复制到ARB寄存器中;在间接寻址时,ARP可由存储器 ; 相关指令改变,也可由LARP,MAR,和LST指令改变;当执行LST#1指令 ; 时,ARP也可加载每ARB相同的值 ; C---- 进位位:此位在加法结果产生进位时被置为1,或在减法结果产生借位时被清0 ; 否则,除了执行带有16 位移位的ADD或SUB指令外,C 在加法后被清除或在减 ; 法后被设置;在ADD或USB指令时,ADD仅可对进位位进行置位而SUB仅可 ; 对进位位进行清除,而不会对进位位产生其他影响;移1位和循环指令也可影响 ; 进位位C,以及SETC、CLRC和LST指令也可影响C;条件转移、调用和返回 ; 指令可以根据C的状态进行执行;复位时C被置1 ; CNF----片内DARAM配置位:若CNF=0,可配置的双口RAM区被映射到数据存储空 ; 间;若CNF=I,可配置的双口RAM区被映射到程序存储空间;CNF位可通过 ; SETC CNF,CLRC CNF和LST指令修改;R/S/复位时CNF置为0 ; DP---- 数据存储器页指针:9位的DP寄存器与一个指令字的低七位一起形成一个16 ; 位的直接寻址地址 ; INTM---中断模式位:当INTM被置为0时,所有的未屏蔽中断使能;当它被置1, ; 所有可屏蔽中断禁止; ; OV---- 溢出标志位:该位保存一个被锁存的值,用以指示CALU中是否有溢出发生; ; 一旦发生溢出,OV位保持为1直到下列条件中的一个发生时才能被清除 ; OVM----溢出方式位:当OVM=0时,累加器中结果正常溢出;当OVM=1时,根据 ; 遇到溢出的情况,累加器被设置为它的最大正值或负值;SETC指令和 ; CLRC指令分别对该位进行置位和复位; ; PM----乘积移位方式: ; 若PM=00,乘法器的32位乘积结果不移位直接装入CALU; ; 若PM=01,PREG输出左移1位后装入CALU,最低位LSB以0填充; ; 若PM=10,PREG输出左移4位后装入CALU,最低位LSB以0填充; ; 若PM=11,时PREG输出进行符号扩展右移六位 ; SXM----符号扩展方式位:当SXM一1时,数据通过定标移位器传送到累加器时将产 ; 生符号扩展;SXM=0将抑制符号扩展;SXM位对某些指令没有影响; ; TC---- 测试/控制标志位:在下述情况之一,TC位被置1:由BIT或BITT指令测 ; 试的位为1;当利用NORM指令测试时,累加器的两个最高有效位"异或" ; 功能为真;条件转移、调用和返回指令可根据TC位的条件来执行; ; BIT、BITT、CMPR、LST和NORM指令影响TC位 ; XF---- XF引脚状态位:该位决定XF引脚的状态;SETCXF指令可对位XF进行置位, ; 而CLRCXF指令可对其进行清0;复位时XF置1 ;SCSR1------系统控制和状态寄存器1---地址7018H ; D15---保留位 ; D14---CLKSRC。

DSP概述及存储器

60% Core Performance Boost Vs C’5409

High Performance

JTAG Test/ JTAG Test/ Emulation Emulation Control Control Muxed GP I/O Muxed GP I/O

Program/Data SRAM Program/Data SRAM 128K Words 128K Words

Copyright © 2003 Texas Instruments. All rights reserved.

TMS320C54x系列DSP TMS320C54x系列DSP

TMS320C54x系列DSP概述

C54x DSP具有很高操作灵活性和速度。它具有先进的修 正哈佛结构(一条程序总线、三条数据总线和四条地址总线)、 专门硬件逻辑的CPU、片内存储器、片内外设和专用的指令集、 将C54x DSP的CPU和片内存储器与外设配置组合在一起的螺 旋结构,使得它可以满足电子市场众多领域的应用要求: C54x DSP具有以下优点:

DSP的应用

DSP已经在信号处理、通信、雷达等领域得到广泛的应 用。目前,DSP的价格越来越低,性能价格比日益提高,具 有巨大的应用潜力。DSP的应用主要有: ☆ 用数字信号处理,如数字滤波、自适应滤波、相关 算、快速傅立叶变换等; ☆ 通信领域,如数据加密、数据压缩、传真、移动电 网络通信等; ☆ 语音处理,如语音编码、语音合成、语音识别、语 增强、语音存储等; ☆ 图形/图像,二维或三维图形处理、图像压缩与传输、 指纹识别、图像识别等;

DSP主要特点

根据数字信号处理的要求,DSP一般具有如下的主要特点: ☆ 在一个指令周期内,可完成一次乘法和一次加法; ☆ 程序和数据空间分开,可以同时访问指令和数据; ☆ 片内具有快速RAM,通常可通过独立的数据总线, 在两块芯片中同时访问; ☆ 具有低开销或无开销循环及跳转的硬件支持; ☆ 快速的中断处理和硬件I/O接口支持; ☆ 具有在单周期内操作的多个硬件地址产生器; ☆ 可以并行执行多个操作; ☆ 支持流水线操作,使取指、译码、取操作数和执行等 操作可以重叠执行。

dsp复习重点电信

第二章1、DSP芯片内有3个CPU状态控制寄存器,用于表示工作状态和控制之用,分别说明是哪3个寄存器,并指出其中的状态位或者控制位。

ARP,DP,XF,INTM,IPTR,MP/MC,OVLY,DROM的作用。

’C54x提供三个16位寄存器来作为CPU状态和控制寄存器,它们分别为:状态寄存器0(ST0)状态寄存器1(ST1)工作方式状态寄存器(PMST) ST0和ST1主要包含各种工作条件和工作方式的状态;PMST包含存储器的设置状态和其他控制信息。

1.状态寄存器0(ST0)表示寻址方式和运行状态。

DP:数据存储器页指针。

用来与指令中提供的7位地址结合形成1个16位数据存储器的地址。

OVA/B:累加器A/B的溢出标志。

用来反映A/B是否产生溢出。

C:进位标志位。

用来保存ALU加减运算时所产生的进/借位。

TC:测试/控制标志。

用来保存ALU测试操作的结果。

ARP:辅助寄存器指针。

用来选择使用单操作数间接寻址时的辅助寄存器AR0~AR7。

2.状态寄存器1 (ST1)表示寻址要求、初始状态的设置、I/O及中断的控制等。

BRAF:块重复操作标志位。

用来指示当前是否在执行块重复操作。

BRAF=0 表示当前不进行重复块操作;BRAF=1 表示当前正在进行块重复操作。

CPL:直接寻址编辑方式标志位;用来指示直接寻址选用何种指针。

CPL=0 选用数据页指针DP的直接寻址;CPL=1 选用堆栈指针SP的直接寻址。

XF:外部XF引脚状态控制位。

用来控制XF通用外部输出引脚的状态。

执行SSBX XF=1 XF通用输出引脚为1;执行RSBX XF=0 XF通用输出引脚为0。

HM:保持方式位;响应HOLD信号时,指示CPU是否继续执行内部操作。

HM=0 CPU从内部程序存储器取指,继续执行内部操作。

HM=1 CPU停止内部操作。

INTM:中断总开关INTM=0 开放全部可屏蔽中断;INTM=1 禁止所有可屏蔽中断。

0:保留位,未被使用,总是读为0。

DSP28335的EPWM寄存器详解

7-0

Reserved

AQCTLA功能定义

寄存器位 15-12

名称 Reserved

11-10

CBD

9-8

CBU

7-6

CAD

5-4

CAU

3-2

PRD

1-0

ZRO

AQCTLB功能定义

寄存器位 15-12 11-10

名称 Reserved CBD

9-8

CBU

复位值 00 0

000

001 0 00 0 0 00

描述 保留位 AQCSFRC寄存器重载条件位。00:TBCTR=0;01:TBCTR=TBPRD;10:TBCTR=0或 输出B的一次软件强迫事件初始化。0:写入0没有效果;1:初始化一个s/w信号强迫事件。 当触发了一次软件强迫事件时的动作。00:禁止动作;01:清零,使得EPWMxB输出为低电 输出A的一次软件强迫事件初始化。0:写入0没有效果;1:初始化一个信号软件强迫事件。 当触发了一次软件强迫事件时的动作。00:禁止动作;01:清零,使得EPWMxA输出为低电

读写模式 R R/W R/W R/W R/W R/W R/W

复位值 0 00 00

读写模式 R R/W R/W

7-6

CAD

5-4

CAU

3-2

PRD

1-0

ZRO

AQSFRC功能定义

寄存器位 名称

15-8

Reserved

7-6

RLDCSF

5

OTSFB

4-3

ACTSFB

2

OTSFA

1-0

ACTSFA

AQCSFRC功能定义

9-0

DEL

00

R/W

DSP28335 I2C寄存器中文资料及例程

1I2C寄存器1.1.1I2C模式寄存器——I2CMDR16位寄存器,包含了I2C模块的控制部分I2C作为主机时,RM、STT、STP位于总线发送/接收数据格式和总线状态关系表1.1.2I2C中断使能寄存器——I2CIER包括I2C中断的使能与屏蔽位;1.1.3I2C状态寄存器——I2CSTR包括中断标志状态和读状态信息;1.1.4I2C中断源寄存器——I2CSRC该寄存器主要表明是哪个中断源触发了I2C中断;1.1.5I2C时钟分频寄存器——I2CPSC用于设置I2C输入时钟的分频系数,I2C模块复位时必须初始化I2CPSC;1.1.6I2C时钟宽度寄存器——I2CCLKL、I2CCLKH该寄存器决定I2C时钟的高低电平持续时间I2CCLKL 中的ICCL。

ICCL 决定了时钟信号的低电平时间。

I2CCLKH 中的ICCH。

ICCH 决定了时钟信号的高电平时间。

主机时钟宽度计算公式:T mst=T mod∗((ICCL+d)+(ICCH+d))T mst=(IPSC+1)∗((ICCL+d)+(ICCH+d))I2C输入时钟频率其中T mod为I2C模块的时钟电平宽度,及时钟周期,d的值由IPSC决定。

1.1.7I2C从机地址寄存器——I2CSARI2C模块从机地址寄存器,当I2C模块作为主机时,该寄存器用来存储下一次要发送的从机地址。

它包含了一个7位或者10位从机地址空间,当I2C工作在非全数据模式时(I2CMDR.FDF=0),寄存器中的地址是传输的首帧数据。

如果寄存器中地址值非全零,那该地址对应一个指定的从机;如果寄存器中的地址为全零,地址就为广播地址,呼叫所有挂在总线上的从机。

如果选择7位地址模式(I2CMDR.XA=0),只有位6到位0是可用的,位9到位7写0。

1.1.8I2C模块自身地址寄存器——I2COARI2C模块使用该寄存器从所有挂在总线上的从机中找出属于自己的从机。

如果选择7位地址模式(I2CMDR.XA=0),只有位6到位0是可用的,位9到位7写0。

什么是DSP__DSP 处理器与通用处理器的比较

什么是DSP (2009-03-05 19:22:36)转载▼标签:it 分类:基础学堂DSP(digital singnal processor)是一种独特的微处理器,是以数字信号来处理大量信息的器件。

其工作原理是接收模拟信号,转换为0或1的数字信号,再对数字信号进行修改、删除、强化,并在其他系统芯片中把数字数据解译回模拟数据或实际环境格式。

它不仅具有可编程性,而且其实时运行速度可达每秒数以千万条复杂指令程序,源源超过通用微处理器,是数字化电子世界中日益重要的电脑芯片。

它的强大数据处理能力和高运行速度,是最值得称道的两大特色。

DSP芯片,也称数字信号处理器,是一种特别适合于进行数字信号处理运算的微处理器,其主机应用是实时快速地实现各种数字信号处理算法。

根据数字信号处理的要求,DSP芯片一般具有如下主要特点:(1)在一个指令周期内可完成一次乘法和一次加法;(2)程序和数据空间分开,可以同时访问指令和数据;(3)片内具有快速RAM,通常可通过独立的数据总线在两块中同时访问;(4)具有低开销或无开销循环及跳转的硬件支持;(5)快速的中断处理和硬件I/O支持;(6)具有在单周期内操作的多个硬件地址产生器;(7)可以并行执行多个操作;(8)支持流水线操作,使取指、译码和执行等操作可以重叠执行。

当然,与通用微处理器相比,DSP芯片的其他通用功能相对较弱些DSP 处理器与通用处理器的比较(2009-03-05 19:24:35)转载▼分类:基础学堂标签:it考虑一个数字信号处理的实例,比如有限冲击响应滤波器(FIR)。

用数学语言来说,FIR 滤波器是做一系列的点积。

取一个输入量和一个序数向量,在系数和输入样本的滑动窗口间作乘法,然后将所有的乘积加起来,形成一个输出样本。

类似的运算在数字信号处理过程中大量地重复发生,使得为此设计的器件必须提供专门的支持,促成了了DSP器件与通用处理器(GPP)的分流:1 对密集的乘法运算的支持GPP不是设计来做密集乘法任务的,即使是一些现代的GPP,也要求多个指令周期来做一次乘法。

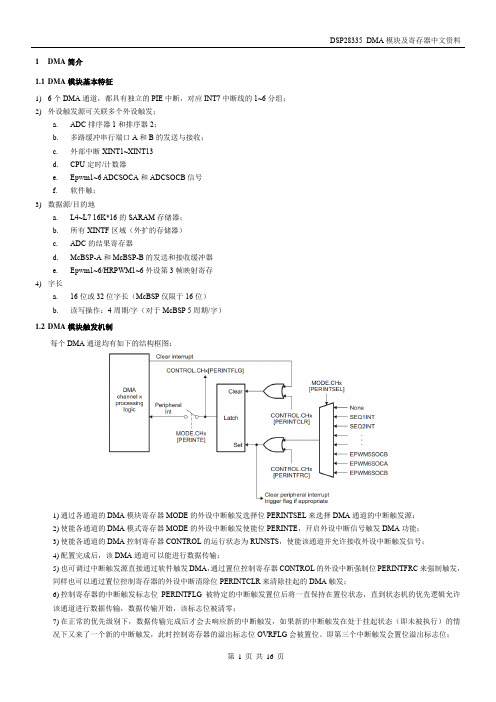

DSP28335 DMA模块及寄存器中文资料

1DMA简介1.1DMA模块基本特征1)6个DMA通道,都具有独立的PIE中断,对应INT7中断线的1~6分组;2)外设触发源可关联多个外设触发;a.ADC排序器1和排序器2;b.多路缓冲串行端口A和B的发送与接收;c.外部中断XINT1~XINT13d.CPU定时/计数器e.Epwm1~6 ADCSOCA和ADCSOCB信号f.软件触;3)数据源/目的地a.L4~L7 16K*16的SARAM存储器;b.所有XINTF区域(外扩的存储器)c.ADC的结果寄存器d.McBSP-A和McBSP-B的发送和接收缓冲器e.Epwm1~6/HRPWM1~6外设第3帧映射寄存4)字长a.16位或32位字长(McBSP仅限于16位)b.读写操作:4周期/字(对于McBSP 5周期/字)1.2DMA模块触发机制每个DMA通道均有如下的结构框图:1)通过各通道的DMA模块寄存器MODE的外设中断触发选择位PERINTSEL来选择DMA通道的中断触发源;2)使能各通道的DMA模式寄存器MODE的外设中断触发使能位PERINTE,开启外设中断信号触发DMA功能;3)使能各通道的DMA控制寄存器CONTROL的运行状态为RUNSTS,使能该通道并允许接收外设中断触发信号;4)配置完成后,该DMA通道可以能进行数据传输;5)也可调过中断触发源直接通过软件触发DMA,通过置位控制寄存器CONTROL的外设中断强制位PERINTFRC来强制触发,同样也可以通过置位控制寄存器的外设中断清除位PERINTCLR来清除挂起的DMA触发;6)控制寄存器的中断触发标志位PERINTFLG被特定的中断触发置位后将一直保持在置位状态,直到状态机的优先逻辑允许该通道进行数据传输,数据传输开始,该标志位被清零;7)在正常的优先级别下,数据传输完成后才会去响应新的中断触发,如果新的中断触发在处于挂起状态(即未被执行)的情况下又来了一个新的中断触发,此时控制寄存器的溢出标志位OVRFLG会被置位。

(完整版)DSP GPIO相关寄存器的设置最详细的一份资料了

每个通用I/O 端口都受多路复用(MUX),方向(DIR),数据(DAT),置位(SET),清除(CLEAR),以及切换(TOGGLE)寄存器的控制。

下面介绍这些寄存器的功能。

GPxMUX 寄存器(x=A,B,D,E,F,G)每个I/O 端口都有一个MUX(多路复用)寄存器。

这个寄存器用来在每个引脚(PIN)的外设操作及I/O 操作之间进行选择。

复位时所有通用I/O 引脚都配置成数字I/O 功能。

任何一个引脚都可通过16 位的多路复用寄存器 GPxMUX 进行外设或GPIO 功能的设置:当GPxMUX.bit = 0,相应的一个引脚配置成I/O 功能;当GPxMUX.bit = 1,相应的一个引脚配置成外设功能。

GPxDIR 寄存器(x=A,B,D,E,F,G)每个I/O 端口都有一个方向控制寄存器。

不论是将相应的I/O 引脚配置成输入还是输出,都由方向寄存器控制。

复位时,所有通用I/O 引脚均配置成输入。

当GPxDIR.bit = 0,引脚配置成输入;当GPxDIR.bit = 1,引脚配置成输出。

在采用GPxDIR 寄存器位将输入端口改变成输出端口之前,引脚的当前电平反映到GPxDAT 寄存器中。

当端口的方向从输入改变成输出时,GPxDAT 寄存器的值用来确定引脚的电平。

例如,如果引脚已经从内部上拉,则复位后上拉将致使GPxDAT 寄存器对应位为1用于反映引脚的当前高电平。

当端口的方向从输入改变成输出时,GPxDAT 寄存器已经为1 的位强迫该引脚为同一高电平。

这样,在电平不变的情况下,引脚能够从输入转换为输出。

GPxDAT 寄存器(x=A,B,D,E,F,G)。

DSP课件第2章硬件结构

5、电源

采用高性能静态CMOS技术,供电电压为3.3V。 可用IDLE指令进入低功耗模式。

6、在片仿真接口

具有符合IEEEll49.1标准的在片仿真接口(JTAG)。

7、速度

单周期定点指令的执行时间为50ns、35ns或25ns(20MIPS,28.5MIPS, 或40MIPS)。

2.2 TMS320LF240x的总线结构

INTM:中断模式位

用来允许(INTM=0)或禁止(INTM=1)所有的可屏蔽中断。用 SETC OVM或CLRC OVM可将该位置1或清0。LST指令不影响OVM位。

DP:数据页面指针

当使用直接寻址方式时,DP存放存储器的数据页,DP与指令代 码的最低7位构成16位存储器地址。

数据存储器地址

SARAM的地址可以用于数据存储器和程序存储器。可通过软件配置 为外部存储器或内部SARAM。

SARAM在一个机器周期内只能访问一次。当CPU要求多次访问时, SARAM会向CPU提供一个未准备好的信号,然后在每个周期内执行一次 访问。

闪速存储器(Flash) 是电可擦除的、可编程的、可长期保存数据的存储器。

CPU的基本组成包括: 32位中央算术逻辑运算单元(CALU); 32位累加器(ACC);输入与输出数据比例移位器; 16位×16位的乘 法器(MUL)以及乘积比例移位器。

CPU功能结构图

2、输入比例部分

功能:将来自存储器的16位数据左移0~16位送往中央算术逻辑单元 (CALU)。

移位方法:左移后有使用的低位LSB填0,高位MSB填0或用符号 扩展,取决于状态寄存器ST1的符号扩展模式位SXM(D10)。 SXM=0 填0 SXM=1 符号扩展

中央算术逻辑单元

(整理)DSP存储空间的分配问题.

在DSP的开发过程中,开发者难免会遇到DSP芯片内部存储器和片外扩展存储器的配置等问题。

本文以TMS320C54x系列DSP为例,讨论DSP存储空间的分配问题。

存储器空间'C54x系列DSP存储器分为三个独立选择的空间—程序、数据和I/O,其中程序存储器存放待执行的指令和执行中所用的系数(常数),可使用片内或片外的RAM、ROM或EPROM等来构成;数据存储器存放指令执行中产生的数据,可使用片内或片外的RAM和ROM来构成。

I/O存储器存放与映象外围接口相关的数据,也可以作为附加的数据存储空间使用。

这三个空间的寻址范围取决于DSP芯片地址线数目。

例如,'C54x系列 DSP 从'C548开始,芯片有23根地址线,具有8M字节存储空间寻址能力。

'C54x通过包含在处理器工作方式的状态寄存器(PMST)中的3个状态位,选择片内存储器作为程序空间或数据空间。

这3个状态位是:(1)MP/MC位。

MP/MC=0,则片内ROM安排到程序空间;MP/MC=1,则片内ROM不安排到程序空间。

(2)OVLY位。

OVLY=1,则片内RAM安排到程序和数据空间;OVLY=0,则片内RAM只安排到数据存储空间。

(3)DROM位。

当DROM=1,则部分片内ROM安排到数据空间;DROM=0,则片内ROM不安排到数据空间。

程序设计者可根据不同的需求,相应的配置这3个位,使系统的存储空间满足应用要求。

同时,为了扩展'C54x系列DSP的寻址空间,还增加了一个额外的存储器映像寄存器—程序计数器扩展寄存器XPC,以及6条寻址扩展程序空间的指令。

以TMS320C5410为例,它的程序空间分成128页面,每页64K字。

该64K字程序空间分为两部分:一部分是公共的32K字,另一部分是各自独立的32K字。

公共存储器为所有页面共享,每个页面独立的32K字存储器只能按指定的页面号寻址,这个页面号由XPC寄存器设定。

DSP术语

分配:链接器计算输出段的最终存储器地址的过程。 分配节点:将节间消息分配至的处理器节点。 ALU:请参见算术逻辑单元。 ALU 函数:对于并行处理器,是指对到算术逻辑单元 (ALU) 的输入进行的操作, 其中包括三个输入的任何算术或 Boolean 组合,以及混合算术和 Boolean 函 数。(TMS320C8x)

汇编器:从包含汇编语言说明和指令的源文件创建机器语言程序的软件程序。汇 编器将绝对操作代码替换为符号 操作代码,并将绝对或浮动地址替换为符号地 址。

汇编语言:低级的符号编程语言,类似于机器代码语言并由字母组组成 — 每个 字母组代表一个指令;使计算机用 户可以使用助记符(而不是数字指令)来编 写程序。

汇编语言指令:使用计算机操作来表示助记符的语言。

汇编模式:无论当前运行哪种类型的代码,在 DISASSEMBLY 窗口中显示汇编语 言代码但不会显示 FILE 窗口 的调试模式。

汇编程序优化器:可优化线性汇编代码(尚未分配寄存器或预定的汇编代码)的 软件程序。当其中一个输入文件具 有 .sa 扩展名时,汇编程序优化器将会通过 shell 程序 cl6x 自动调用该文件。(TMS320C6x)

异步发送 (TX) 引脚:在该引脚上,来自异步串行端口的数据串行传输;从异步 串行端口移位寄存器 (AXSR) 按一 次一位的速度接收字符。(TMS320C2xx)

属性:指定适用于后续图形信息的部分特性或特点的参数。

音频输出电缆:将软件开发板 (SDB) 连接到音频输入和输出外设的电缆。包含 立体声线路输出、线路输入和辅助 输入的标准 RCA 插孔。(TMS320C8x)

DSP28335 McBSP模块及寄存器中文资料

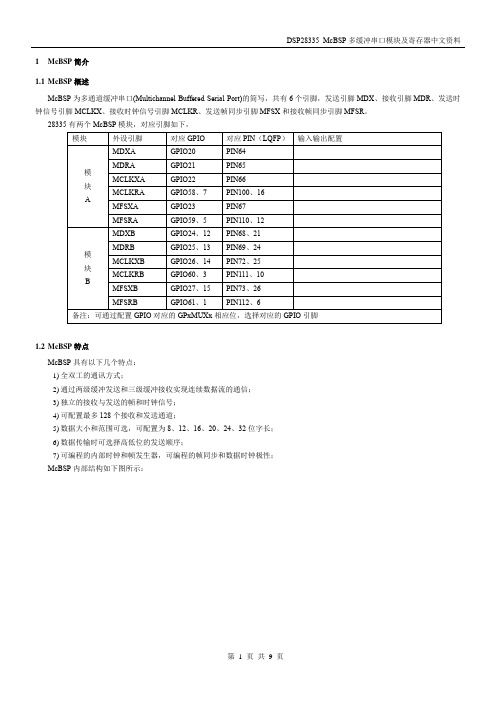

1McBSP简介1.1McBSP概述McBSP为多通道缓冲串口(Multichannel Buffered Serial Port)的简写,共有6个引脚,发送引脚MDX、接收引脚MDR、发送时钟信号引脚MCLKX、接收时钟信号引脚MCLKR、发送帧同步引脚MFSX和接收帧同步引脚MFSR。

28335有两个McBSP模块,对应引脚如下,1.2McBSP特点McBSP具有以下几个特点:1)全双工的通讯方式;2)通过两级缓冲发送和三级缓冲接收实现连续数据流的通信;3)独立的接收与发送的帧和时钟信号;4)可配置最多128个接收和发送通道;5)数据大小和范围可选,可配置为8、12、16、20、24、32位字长;6)数据传输时可选择高低位的发送顺序;7)可编程的内部时钟和帧发生器,可编程的帧同步和数据时钟极性;McBSP内部结构如下图所示:McBSP结构图1.3McBSP中断描述1.3.1接收中断1.3.2发送中断2DMA模块寄存器2.1.1控制寄存器1——SPCR1该寄存器设置McBSP串口的数字回环模式、接收字符拓展和校验模式、ClockStop模式、DX是否允许、A-bis模式、接收中断模式等,并给很粗接受同步错误、接收移位寄存器空、接收就绪等状态位,此外该可以接收复位。

2.1.2控制寄存器2——SPCR2SPCR2设置了McBSP自由运行模式、SOFT模式、发送中断模式,并给出发送同步错误、发送移位寄存器空、发送准备好等状态位,此外还可进行发送复位、采样率发生器复位、帧同步发生电路复位。

表FREE、SOFT设置2.1.3引脚控制寄存器PCRPCR设置McBSP传输帧同步模式、接收帧同步模式、发送时钟模式、接收时钟模式、发送帧同步信号的极性、接收帧同步信号的极性、发送时钟极性、接收时钟极性,并给出CLKS、DX、DR引脚的状态。

此外PCR还定义发送和接收部分在复位时相应引脚引脚是否配置为通用I/O;2.1.4接收控制寄存器RCR1RCR1设置McBSP接收时第一相的接收帧长度(从1个字到128个字、接收字长度(8、12、16、20、24、32bits)。

用C语言对DSP的寄存器进行操作?

用C语言对DSP的寄存器进行操作?在嵌入式软件的开发过程中,我们常用的语言主要是:汇编语言和C语言。

相比较于汇编语言,C语言对我们来说,更贴近我们的一些语言习惯。

在DSP的开发过程中,我们主要还是用C语言,其中最最常用的操作就是对于DSP各个寄存器的控制了。

那么如何用C语言对DSP的寄存器进行操作呢?我们先来说书单片机里面是如何操作的:一般寄存器在单片机头文件中的宏定义都有如下的形式:#define TIFR *((volatile unsignedchar *)0x58) /*ATmega16的TIFR寄存器*/在ATmega16中TIFR寄存器的地址是0x0058,我们要实现:TIFR = 0x01这条,就是要把0x58这个地址的内容修改成0x01。

而在C语言中,指针就是地址。

现在要告诉编译器0x58是地址,就要把0x58强制转换成指针(unsigned char *)0x58。

这样(unsigned char *)0x58就表示TIFR在ATmega16 中的地址了,而*((unsigned char*)0x58)表示这个地址的内容。

然后如果想对寄存器TIFR单个的位进行下面的操作,(1)将寄存器TIFR的第1位置“1”TIFR |= (1 <>(2)将寄存器REG的第3位清零TIFR &= ~(1 <>(3)将寄存器REG的第3、5位置“1”TIFR |= (1 < 5)="" |="" (1=""><>(4)将寄存器REG的第3、5位清零TIFR &= ~( (1 < 5)="" |="" (1="">< 3)="">在单片机里面是使用宏定义的方式来对寄存器进行操作。

DSP程序中寄存器如何分配地址

DSP程序中寄存器如何分配地址DSP中某个寄存器怎么分配地址?在数据⼿册中,我们常常看到说某个寄存器地址是多少,以TMS320F28335的时钟系统寄存器为例,在ti公司给出的⼿册我们看到如下信息我们看到HISPCP中的地址为0x701A;翻看ti公司给的⼀系列库我们发现其寄存器定义在结构体SYS_CTRL_REGS中,经过⼀系列查找,我们发现SYS_CTRL_REGS映射的是 DSP281x_Headers_nonBIOS.cmd⽂件中,其对应的地址映射是System:0我们发现其⾸地址是0x7010;⽽resvd1不代表任何含义,仅仅⽅便位置偏移设数,⽽结构体中HISPCP前⾯有10个16进制变量,HISPCP是第11个,在C语⾔中,下标是从0开始,所有HISPCP是第10个,也就是A,那么HISPCP地址是0x701A,查看芯⽚数据发现吻合,相关内容,可参考下⾯⼀⽚博客⽤过F2812的朋友⼀定会对cmd⽂件很熟悉,因为这个⽂件中为每个程序和数据分配了相应的地址。

我们常⽤的cmd⽂件包括连个:(1) DSP281x_Headers_nonBIOS.cmd(2) F2812_EzDSP_RAM_lnk.cmdDSP281x_Headers_nonBIOS.cmd上⾯第⼀个⽂件⽤于对DSP外设分配地址,⽽第⼆个⽂件是为系统的程序和数据分配地址。

当然,如果DSP的外设地址我们⽤C 语⾔已经⾃⼰定义,那第⼀个⽂件我们就可以不⽤了,笔者就是⾃⼰定义的,所以没有⽤到第⼀个⽂件。

对于为什么要⾃⼰定义外设寄存器以及中断地址,有这⼏个原因:(1) ⾃⼰定义外设寄存器地址可以很清楚的了解DSP的⼯作原理,虽然这样很耗费时间,但是会了解到DSP的中断等等是怎么⼯作的。

(2) 因为DSP外设寄存器地址的分配时采⽤寄存器形式分配到的。

举个例⼦,以sci串⼝通信为例,其他的外设以及中断都⼀样。

⽐如我们设置波特率,肯定是设置某个寄存器的相应位来实现。

DSP28335SCI 总结

2.1 SCI模块寄存器概述表2SCI-A寄存器名称地址占用空间功能描述SCICCR 0x0000 7050 1 SCI-A 通信控制寄存器SCICTL1 0x0000 7051 1 SCI-A 控制寄存器1SCIHBAUD 0x0000 7052 1 SCI-A 波特率设置寄存器高字节SCILBAUD 0x0000 7053 1 SCI-A 波特率设置寄存器低字节SCICTL2 0x0000 7054 1 SCI-A 控制寄存器2SCIRXST 0x0000 7055 1 SCI-A 接收状态寄存器SCIRXEMU 0x0000 7056 1 SCI-A 接收仿真数据缓冲寄存器SCIRXBUF 0x0000 7057 1 SCI-A 接收数据缓冲寄存器SCITXBUF 0x0000 7059 1 SCI-A 发送数据缓冲寄存器SCIFFTX 0x0000 705A 1 SCI-A FIFO发送寄存器SCIFFRX 0x0000 705B 1 SCI-A FIFO接收寄存器SCIFFCT 0x0000 705C 1 SCI-A FIFO控制寄存器SCIPRI 0x0000 705F 1 SCI-A 极性控制寄存器注意:SCIFFRX、SCIFFTX是FIFO的功能,现在还知道怎么使用。

参考例子使只使能其中的复位、清标志位就行。

最后写复位使能。

第四位:一定设置为0。

不知道有什么作用。

表3 SCI通信控制寄存器(SCICCR)功能描述位名称功能描述7 STOP BITS SCI停止位的个数该位决定了发送的停止位的个数。

接收器仅对一个停止位检查。

0 一个停止位;1 两个停止位;6 PARITY 奇偶校验选择位如果PARITY ENABLE位(SCICCR, 位5)被置位,则PARITY (位6)确定采用奇校验还是偶校验(在发送和接收的字符中奇偶校验位的位数都是1位)。

0 奇校验;1 偶校验;5 PARITY SCI奇偶校验使能位ENABLE 该位使能或禁止奇偶校验功能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

DSP寄存器设置

2010-07-02 14:47

一个ePWM module包括Time-base (TB) module,Counter-compare (CC) module,Action-qualifier (AQ) module,Dead-band (DB) module,PWM-chopper (PC) module,Event-trigger (ET) module,Trip-zone (TZ) module等七个模块。

正常的发出PWM波要配置TB、CC、AQ、DB、ET等五个模块。

Time-base (TB) module为定时器模块,有

TBCTL(控制寄存器)配置定时器的时钟、计数模式、同步模式

TBSTS(状态寄存器)

TBPHSHR(高速PWM用)

TBPHS(相位寄存器)计数器的起始计数位置,例如寄存器为0x0100则计数器从0x0100开始计数

TBCTR(计数器)

TBPRD(周期寄存器)设置计数器的计数周期。

只有TBPRD(周期寄存器)有影子寄存器。

本程序的设置为count-up-and-down mode计数模式,相位为零,ePWM2 、ePWM3、ePWM4、 ePWM5、 ePWM6通过ePWM1的计数器到零时进行同步,计数周期为0.5ms。

Counter-compare (CC) module为比较器模块有

CMPCTL (比较控制寄存器)设置CMPA、CMPB的重载模式

CMPAHR(高速PWM用),

CMPA(比较值寄存器A)设置EPWMxA的比较值,有影子寄存器。

CMPB(比较值寄存器B)设置EPWMxB的比较值,有影子寄存器。

本程序只应用了CMPA,设置计数器到零时重载CMPA。

Action-qualifier (AQ) module比较方式预设模块

AQCTLA (输出A比较方式控制寄存器)设置EPWMA的比较方式有CBD、CBU、CAD、CAU、PRD、ZRO,无影子寄存器,立即装载

AQCTLB (输出B比较方式控制寄存器)设置EPWMB的比较方式有CBD、CBU、CAD、CAU、PRD、ZRO,无影子寄存器,立即装载

AQSFRC (软件强制控制寄存器)设置AQCSFRC重载方式(RLDCSF),通过(OTSFB、ACTSFB)设置EPWMB、(OTSFA、ACTSFA)设置EPWMA启动一次强制置位无效、置零、置高、反向,当OTSFB、OTSFA被写1时,动作一次,写0无效,无影子寄存器

AQCSFRC (软件连续强制控制寄存器)可以强制EPWMA、EPWMB的输出为low或high或AQCSFRC不起作用,有影子寄存器,当寄存期被加载后的第二个时钟开始作用,如TBCLK=0时加载,TBCLK=1时开始起作用

说明:

CBD为TBCTR(计数器)与CMPB在down计数时相等使输出为low或high或反向或不动作

CBU为TBCTR(计数器)与CMPB在up计数时相等使输出为low或high或反向或不动作

CAD为TBCTR(计数器)与CMPA在down计数时相等使输出为low或high或反向或不动作

CAU为TBCTR(计数器)与CMPA在up计数时相等使输出为low或high或反向或不动作

PRD为TBCTR(计数器)与TBPRD(周期寄存器)相等时使输出为low或high或反向或不动作

ZRO为TBCTR(计数器)计到零时使输出为low或high或反向或不动作

注意:以上均是相等时起作用,其它时间不管,只有AQCSFRC(软件连续强制控制寄存器)持续起作用

如同时出现比较则优先级如图

例:CMPA=100,CMPB=100,up计数,EPWMA初始为低,CAU设置高,CBU设置低,当TBCTR计到100时,CAU、CBU同时作用,根据优先级,EPWMA输出低。

当CMPA=100,CMPB=110,其它不变,当TBCTR计到100时,EPWMA输出高,计到110时EPWMA输出低。

本程序只应用了EPWMA输出通过Dead-band (DB) module产生互补的PWM波形。

Action-qualifier (AQ) module比较方式预设模块配置如下:AQCTLA (输出A 比较方式控制寄存器)的CAU置高,CAD置低,其它无效。

在初始化中配置。

AQCSFRC (软件连续强制控制寄存器)通过AQSFRC(软件强制控制寄存器)的RLDCSF配置为TBCTR(计数器)计到零时装载,根据需要每次中断配置CSFA置

高、置低或软件连续强制无效。

其优先级最高,强制时CAU置高,CAD置低不起作用,无效时CAU置高,CAD置低起作用。

AQSFRC(软件强制控制寄存器)的ACTSFA配置为置低,当本周期软件连续强制无效时,向OTSFA写1,保证有效高周期的起始是低状态,防止上一周期结束时为高。

Dead-band (DB) module死区模块

DBCTL(死区控制寄存器)设置S5,S4,S3,S2,S1,S0开关选择的

DBRED(死区上升沿延时)上升沿延时时间

DBFED(死区下降沿延时)下降沿延时时间

本程序的设置为S5=0,S4=0,S3=1,S2=0,S1=1,S0=1;延时时间为5us。

EPWMxA= EPWMxA in,EPWMxB为EPWMxA in的反向。

Event-trigger (ET) module中断事件模块

ETSEL(中断选择寄存器)使能及事件源选择(SOCA触发ADC转换,SOCB触发ADC转换,中断)

ETPS(中断预设寄存器)xxxCNT记录时间发生次数,当与xxxPRD相等时,发出中断信号,xxxCNT停止计数,当标志为清除时xxxCNT置零重新计数

ETFLG(中断标志寄存器)状态标志位,中断时为1

ETCLR(中断标志清除寄存器)写1清除相应标志位

ETFRC(强制中断寄存器)写1强制相应中断发生

本程序选择SOCA触发ADC转换,TBCTR=0位中断事件源,xxxPRD为1。