时钟信号RC阻抗匹配

阻抗匹配的原理及应用

阻抗匹配的原理及应用1. 阻抗匹配的定义在电子电路设计中,阻抗匹配是指将输入和输出电路的阻抗调整为互相匹配的过程。

阻抗匹配可以使信号在电路之间传输时最大限度地传递能量,减少能量反射和损耗。

通过阻抗匹配,可以提高电路的性能和信号传输质量。

2. 阻抗匹配的原理阻抗匹配的原理是基于两个基本的电路理论:傅里叶变换和最大功率传输定理。

2.1 傅里叶变换傅里叶变换是将一个时域信号分解成不同频率的正弦和余弦分量的数学技术。

在阻抗匹配中,傅里叶变换用于将时域信号转换为频域信号,从而分析信号的频谱特性。

2.2 最大功率传输定理最大功率传输定理是指当负载电阻与源电阻相等时,电路能够以最大功率传输能量。

阻抗匹配通过调整电路的阻抗使其与源电阻或负载电阻相等,从而实现最大功率传输。

3. 阻抗匹配的应用阻抗匹配在电子电路设计和通信系统中有广泛的应用。

3.1 无线通信系统在无线通信系统中,阻抗匹配用于将天线阻抗与无线发射机或接收机的阻抗匹配。

这可以提高无线信号的传输效率,减少信号损失和反射。

3.2 放大器设计在放大器设计中,阻抗匹配被广泛应用于放大器的输入和输出端口。

阻抗匹配可以使信号在放大器中传输时最大限度地传递能量,提高放大器的增益和线性度。

3.3 系统集成在系统集成中,阻抗匹配用于连接不同的电路模块。

通过阻抗匹配,可以使各个模块之间的阻抗匹配,确保信号的正确传输和系统的正常运行。

4. 阻抗匹配的方法在实际应用中,有多种方法可用于实现阻抗匹配。

以下是几种常见的方法:•使用阻抗变换器:阻抗变换器可以将一个阻抗转换为另一个阻抗,以实现阻抗匹配。

常见的阻抗变换器有电感、电容、变压器等。

•使用匹配网络:匹配网络是由电感、电容和电阻等元件构成的网络,用于调整输入和输出电路的阻抗以实现匹配。

•使用负馈:负馈可以将一个电路的输出信号反馈到输入端,以调整输入电路的阻抗与负载电路的阻抗匹配。

负馈可以通过放大器或运算放大器来实现。

•使用传输线:传输线可以通过调整传输线的长度或特性阻抗来实现阻抗匹配。

高速时钟信号的匹配电路设计与分析

高速时钟信号的匹配电路设计与分析摘要:时钟信号是数字电路能够正常工作的基础,决定着数据能否正常判决。

但是随着集成电路工艺的发展,时钟信号的边沿变化速率都变得非常快,快速的边沿速率会导致严重的信号完整性和电磁兼容性问题,为了确保时钟信号的完整性,时钟信号需要进行匹配设计。

信号完整性分析中常用的几种匹配方法是否都适合于时钟信号,各种匹配方法的取值如何确定就成为了设计难点。

为了能够获取高质量的时钟信号,文章结合仿真分析的方法,设计出典型时钟电路RC匹配电路,指导实际应用。

关键词:时钟信号;匹配电路;信号完整性0前言当今电子技术不断地发展,高密、高速、高可靠性已经成为电子产品所面临的难题之一。

集成电路也随着这一发展不断地改进工艺以应对信号的快速翻转,14纳米技术已经在商用产品中通用。

信号快速的翻转给我们提供更高速率的可能性的同时也引入了新的问题,信号的边沿速率也变得非常快。

特别是时钟等边沿敏感信号,快速的边沿速率会导致严重的信号完整性和电磁兼容性问题。

为了在设计阶段就能提前解决这一系列的问题,提高产品的设计效率,就需要深入探讨时钟的原理设计、PCB设计。

本文将结合仿真分析的方法,详细介绍时钟设计。

1基本概念高速电路设计是当今的一个热门的话题,但是高速电路的定义却不是那么的清晰明确,现在比较通用的定义为信号的上升时间小于6倍的信号传输时延时,就认为此信号为高速信号。

当信号频率较高(高于30MHz)时,信号的边沿速率一定比较快,此时可以认为是高速信号,当信号速率不高(低于30MHz)时,但是由于工艺问题信号速率较快,此时也可以认为是高速信号。

2时钟线设计时钟信号是电路设计中的时序基准,是决定其他电路信号是否能够被正常运转的基础,因此时钟信号自身的电路设计及信号质量非常关键,本节将详细阐述时钟信号的电气要求、设计方法以及仿真分析。

2、1时钟信号的电气要求时钟信号一般为LVCOMS、LVTTL等类型的电平信号,其电气特性要求与LVCOMS、LVTTL等信号类似,一般包括高电平判决门限、低电平判决门限、周期、上升、下降时间以及占空比等。

rc滤波电路阻抗匹配

rc滤波电路阻抗匹配English Answer:Introduction to Impedance Matching in RC Filter Circuits.Impedance matching in RC filter circuits is a fundamental concept in analog electronics. It involves adjusting the input and output impedances to optimize signal transmission and minimize reflections. In this article, we will explore the theory and applications of impedance matching in RC filter circuits.Theory of Impedance Matching.In an RC filter circuit, the input and output impedances must be matched to prevent signal reflections and ensure maximum power transfer. Mismatched impedances cause energy losses, signal distortion, and reduced efficiency.The condition for impedance matching is:Zin = Zout.where:Zin is the input impedance.Zout is the output impedance.Types of Impedance Matching.There are two main types of impedance matching:1. Series Impedance Matching: A resistor is added in series with the input or output of the filter to match the impedances.2. Parallel Impedance Matching: A capacitor or inductor is added in parallel with the input or output of the filter to match the impedances.Applications of Impedance Matching in RC Filter Circuits.Impedance matching is essential in various applications, including:Audio Amplifiers: Matching the input impedance of the amplifier to the output impedance of the source ensures efficient signal transfer and prevents distortion.Signal Conditioning: Impedance matching is used to optimize signal levels and minimize noise in dataacquisition systems.Filter Design: By matching the input and output impedances, filters can be cascaded without signal loss or distortion.Power Conversion: Impedance matching is crucial in power supplies and converters to achieve maximum power transfer and minimize energy losses.Advantages and Disadvantages of Impedance Matching. Advantages:Increased signal power transmission.Reduced signal distortion.Improved efficiency.Simplified circuit design.Disadvantages:Additional components may be required.Can increase circuit complexity.Not always easy to achieve perfect matching.Conclusion.Impedance matching in RC filter circuits is essentialfor optimizing signal transmission, minimizing signal distortion, and improving circuit efficiency. By understanding the theory and techniques of impedance matching, engineers can design high-performance analog circuits for various applications.Chinese Answer:RC滤波电路中的阻抗匹配。

高速时钟信号的RC匹配电路设计与分析

2018年第2期信息通信2018(总第182 期)INFORMATION & COMMUNICATIONS (Sum. N o 182)高速时钟信号的RC匹配电路设计与分析韩熳莉,刘婷婷(中国航空工业西安航空计算技术研究所,陕西西安710065)摘要:时钟信号是数字电路能够正常工作的基础,决定着数据能否正常判决。

但是随着集成电路工艺的发展,时钟信号的边沿 变化速率都变得非常快,快速的边沿速率会导致严重的信号完整1■生和电磁兼容性问题,为了确保时钟信号的完整I■生,时钟信号 需要进行匹配设计。

信号完整I•生分析中常用的几种匹配方法是否都适合于时钟信号,各种匹配方法的取值如何确定就成为了 设计难点。

为了能够获取高质量的时钟信号,文章结合仿真分析的方法,设计出典型时钟电路R C匹配电路,指导实际应用。

关键词:时钟信号;匹配电路;信号完整性中图分类号:TN79 文献标识码:A文章编号:1673-1131(2018)02-0045-03〇前言当今电子技术不断地发展,高密、高速、高可靠性已经成为电子产品所面临的难题之一。

集成电路也随着这一发展不断地改进工艺以应对信号的快速翻转,14纳米技术已经在商用产品中通用。

信号快速的翻转给我们提供更高速率的可能性的同时也弓丨入了新的问题,信号的边沿速率也变得非常快。

特别是时钟等边沿敏感信号,快速的边沿速率会导致严重的信号完整性和电磁兼容性问题。

为了在设计阶段就能提前解决这一系列的问题,提髙产品的设计效率,就需要深入探讨时钟的原理设计、PCB设计。

本文将结合仿真分析的方法,详细介绍时钟设计。

1基本概念高速电路设计是当今的一个热门的话题,但是高速电路的定义却不是那么的清晰明确,现在比较通用的定义为信号的上升时间小于6倍的信号传输时延时,就认为此信号为高速信号。

当信号频率较高(高于30MHz)时,信号的边沿速率一定比较快,此时可以认为是高速信号,当信号速率不高(低于30MHz)时,但是由于工艺问题信号速率较快,此时也可以认为是高速信号。

时钟信号产生与分配电路的设计与实现

时钟信号产生与分配电路的设计与实现时钟信号是数字电路中必不可少的元件,它用于同步各个部件的运行时间。

在现代技术中,时钟信号产生与分配电路的设计与实现是一个关键的挑战。

本文将就这一话题展开讨论,旨在探索时钟信号的原理、设计以及实现过程。

一、时钟信号的基本原理1.1 时钟信号的定义时钟信号是一种周期性的电子信号,用于同步数字电路中各个部件的操作时间。

它是一种频率稳定且精确的信号,用于控制计算机、通信系统和其他数字电路中的数据传输和处理过程。

1.2 时钟信号的产生方式时钟信号可以通过多种方式产生,最常见的方式是使用石英晶体振荡器。

石英晶体振荡器基于晶体的振荡特性,能够产生高稳定性和精确频率的时钟信号。

此外,还可以使用LC谐振电路、RC振荡电路以及数字锁相环等方法来生成时钟信号。

1.3 时钟信号的特点时钟信号具有以下几个主要特点:(1)频率稳定:时钟信号的频率应具有高度稳定性,以确保各个部件的同步操作。

(2)精确性:时钟信号应具备较高的精确性,能够达到要求的时钟精度。

(3)均匀性:时钟信号应保持均匀的时间分布,以确保各个部件执行任务的一致性。

二、时钟信号产生电路的设计2.1 振荡电路的设计振荡电路是产生时钟信号的核心组成部分,其设计应考虑以下因素:(1)选择合适的振荡器类型:根据实际需求选择石英晶体振荡器、LC谐振电路或RC振荡电路等振荡器类型。

(2)稳定性与精确度的要求:根据应用场景确定时钟信号的稳定性和精确度要求,选择合适的电路参数和元器件。

(3)噪声抑制:设计时应考虑噪声抑制技术,以降低振荡电路对时钟信号稳定性的影响。

2.2 时钟信号输出电路的设计时钟信号输出电路的设计应满足以下要求:(1)输出阻抗匹配:时钟信号输出电路应与接收电路的输入阻抗匹配,以避免信号传输过程中的反射和干扰。

(2)噪声和毛刺抑制:通过合适的滤波电路和抗干扰设计,降低时钟信号输出电路的噪声和毛刺水平。

(3)电平转换:根据不同部件的电平要求,设计适当的电平转换电路,以确保时钟信号的正常传输和接收。

信号阻抗匹配

2、高速电子设计的板级信号完整性处理高速数字系统的振铃和串扰问题一直是一个令人头疼的问题,特别是在今天,越来越多的VLSI芯片工作在100MHz的频率以上,450MHz的CPU也将广泛应用,信号的边沿越来越陡(已达到ps级),这些高速器件性能的增加也给高速系统设计带来了困难。

同时,高速系统的体积不断减小使得印制板的密度迅速提高。

比较现在新的PC主板与几年前的主板,可以看到新的主板上加入了许多端接。

信号完整性问题已经成为新一代高速产品设计中越来越值得注意的问题,这已是毋庸置疑的了。

信号完整性(Signal Integrity,简称SI)是指在信号线上的信号质量。

差的信号完整性不是由某一单一因素导致的,而是板级设计中多种因素共同引起的。

主要的信号完整性问题包括反射、振铃、地弹、串扰等。

源端与负载端阻抗不匹配会引起线上反射,负载将一部分电压反射回源端。

如果负载阻抗小于源阻抗,反射电压为负,反之,如果负载阻抗大于源阻抗,反射电压为正。

布线的几何形状、不正确的线端接、经过连接器的传输及电源平面的不连续等因素的变化均会导致此类反射。

信号的振铃(ringing)和环绕振荡(rounding)由线上过度的电感和电容引起,振铃属于欠阻尼状态而环绕振荡属于过阻尼状态。

信号完整性问题通常发生在周期信号中,如时钟等,振铃和环绕振荡同反射一样也是由多种因素引起的,振铃可以通过适当的端接予以减小,但是不可能完全消除。

新一代的EDA信号完整性工具主要包括布线前 /布线后SI分析工具和系统级SI工具等。

使用布线前SI分析工具可以根据设计对信号完整性与时序的要求在布线前帮助设计者选择元器件、调整元器件布局、规划系统时钟网络和确定关键线网的端接策略。

SI分析与仿真工具不仅可以对一块PCB板的信号流进行分析,而且可以对同一系统内其它组成部分如背板、连接器、电缆及其接口进行分析,这就是系统级的SI分析工具。

针对系统级评价的SI分析工具可以对多板、连接器、电缆等系统组成元件进行分析,并可通过设计建议来帮助设计者消除潜在的SI问题,它们一般都包括IBIS模型接口、2维传输线与串扰仿真、电路仿真、SI分析结果的图形显示等功能。

rc 尖峰脉冲吸收电路

rc 尖峰脉冲吸收电路全文共四篇示例,供读者参考第一篇示例:RC尖峰脉冲吸收电路是一种常见的电路设计,用于处理脉冲信号中的干扰和噪声。

这种电路结合了电容和电阻的作用,能够快速吸收和平滑处理输入信号,使得输出信号更加稳定可靠。

在各种电子设备和系统中广泛应用,发挥着重要的作用。

RC尖峰脉冲吸收电路的基本原理是利用电容和电阻的特性来对输入信号进行滤波和吸收。

在电路中,电容起到存储电荷和对变化电压的响应作用,而电阻则通过电流的阻碍作用对信号进行控制。

当输入脉冲信号进入电路时,电容会迅速充电或放电,从而吸收脉冲中的能量;电阻会限制电流的流动,使得输出信号变得平稳和连续。

具体来说,RC尖峰脉冲吸收电路可以分为两种类型:一种是高通滤波器,另一种是低通滤波器。

高通滤波器主要用于滤除低频干扰,保留高频信号;低通滤波器则用于滤除高频噪声,保留低频信号。

通过合理设计电容和电阻的数值,可以根据需要选择合适的滤波器类型,实现对不同频率信号的处理。

在实际应用中,RC尖峰脉冲吸收电路可以用于多种场景,例如通信系统、传感器接口、电源管理等领域。

在通信系统中,脉冲信号常常受到频率干扰和噪声影响,需要通过RC尖峰脉冲吸收电路进行滤波处理,以确保信号质量和稳定性。

在传感器接口中,输入信号可能受到环境干扰和电磁干扰影响,需要通过RC尖峰脉冲吸收电路进行滤波和抑制,以提高传感器的精度和可靠性。

在电源管理中,脉冲信号的变化会引起电压波动和波形失真,需要通过RC尖峰脉冲吸收电路进行调节和平滑,以保护设备和延长使用寿命。

第二篇示例:RC尖峰脉冲吸收电路是一种常见的电路设计,在电子技术领域应用广泛。

它可以有效地吸收脉冲信号中的高频噪声,保护后续电路不受干扰。

本文将详细介绍RC尖峰脉冲吸收电路的原理、设计方法以及应用。

一、原理RC尖峰脉冲吸收电路主要由一个电阻(R)和一个电容(C)构成。

当输入端接收到高频脉冲信号时,电容会迅速充电或放电,形成一个尖峰波形。

常见的阻抗匹配方式

常见的阻抗匹配方式1、源端串联匹配在信号源阻抗低于传输线特征阻抗的条件下,在信号的源端和传输线之间接一个电阻R,使源端的输出阻抗与传输线的特征阻抗相匹配,抑制从负载端反射回来的信号发生再次反射。

匹配电阻选择原则,匹配电阻值与驱动器的输出阻抗之和等于传输线的特征阻抗,常见的COMS和TTL驱动器,其输出阻抗会随信号的电平大小变化而变化。

因此,对TTL或CMOS电路来说,不可能有十分正确的匹配电阻,只能这种考虑。

链状拓扑结构的信号王不适合使用串联终端匹配,所有负责必须接到传输线的末端。

串联匹配是最常用的终端匹配方法。

它的优点是功耗小,不会给驱动器带来额外的直流负载,也不会在信号和地之间引入额外的阻抗,而且只需要一个电阻元件。

常见应用:一般的CMOS、TTL电路的阻抗匹配。

USB信号也采样这种方法做阻抗匹配。

2、并联终端匹配在信号源端阻抗很小的情况下,通过增加并联电阻使负载端输入阻抗与传输线的特征阻抗相匹配,达到消除负载端反射的目的。

实现形式分为单电阻和双电阻两种形式。

匹配电阻选择原则:在芯片的输入阻抗很高的情况下,对单电阻形式来说,负载端的并联电阻值必须与传输线的特征阻抗相近或相等;对双电阻形式来说,每个并联电阻值为传输线特征阻抗的两倍。

并联终端匹配优点是简单易行,而易见的缺点是会带来直流损耗:单电阻方式的直流功耗与信号的占空比紧密相关;双电阻方式则无论信号是高电平还是低电平都有直流功耗,但电流比单电阻方式少一半。

常见应用:以高速信号应用较多(1)DDR、DDR2等SSTL驱动器。

采用单电阻形式,并联到VTT(一般为IOVDD的一半)。

其中DDR2数据信号的并联匹配电阻使内置在芯片中的。

(2)TMDS等高速串行数据接口。

采用单电阻形式,在接受设备端并联到IOVDD,单端阻抗为50欧姆(差分对间为100欧姆)。

3.RC匹配4.二极管匹配。

阻抗匹配原理

阻抗匹配原理

阻抗匹配原理是指在电路设计或信号传输中,为了最大程度地传输信号能量,需要将信源的内阻与负载的外阻匹配,以达到阻抗最大化的目标。

阻抗匹配的基本原理是利用电阻、电容、电感等元件的特性来调整电路的阻抗大小。

在电路中,如果信源的内阻与负载的外阻不匹配,会导致能量的反射和损耗,使得信号传输效果下降。

为了解决这一问题,可以通过在信源和负载之间添加阻抗转换电路来实现匹配,使得信号完全传输到负载,最大程度地减小能量的损耗。

阻抗匹配的原理可以通过两种方法来实现。

一种是通过变换电路中的元件参数来达到匹配的目的,如改变电阻、电容、电感等的数值;另一种是通过变换电路的拓扑结构来实现匹配,如串联、并联、变压器等。

在阻抗匹配过程中,如果信源的内阻大于负载的外阻,可以通过串联电阻或并联电容的方式来降低信源的总阻抗,以实现匹配;如果信源的内阻小于负载的外阻,可以通过串联电感或并联电阻的方式来提高信源的总阻抗,以实现匹配。

总之,阻抗匹配原理是为了充分利用信号能量,提高信号传输效果而采取的一种调整电路阻抗的方法。

通过合理选择元件参数和拓扑结构,可以实现信源和负载之间阻抗的匹配,最大程度地减小信号的反射和损耗,提高信号传输的质量。

什么是阻抗匹配-阻抗匹配是什么意思-阻抗匹配原理

什么是阻抗匹配?阻抗匹配是什么意思?阻抗匹配原理阻抗匹配是微波电子学里的一部分,主要用于传输线上,来达至全部高频的微波信号皆能传至负载点的目的,不会有信号反射回来源点,从而提升能源效益。

大体上,阻抗匹配有两种,一种是透过转变阻抗力,另一种则是调整传输线的波长。

转变阻抗力:把电容或电感与负载串联起来,即可增加或削减负载的阻抗值,在图表上的点会沿著代表实数电阻的圆圈走动。

假如把电容或电感接地,首先图表上的点会以图中心旋转180度,然后才沿电阻圈走动,再沿中心旋转180度。

重覆以上方法直至电阻值变成1,即可直接把阻抗力变为零完成匹配。

阻抗匹配是指负载阻抗与激励源内部阻抗相互适配,得到最大功率输出的一种工作状态。

对于不同特性的电路,匹配条件是不一样的。

串联终端匹配:串联终端匹配的理论动身点是在信号源端阻抗低于传输线特征阻抗的条件下,在信号的源端和传输线之间串接一个电阻R,使源端的输出阻抗与传输线的特征阻抗相匹配,抑制从负载端反射回来的信号发生再次反射.串联终端匹配后的信号传输具有以下特点:A 由于串联匹配电阻的作用,驱动信号传播时以其幅度的50%向负载端传播;B 信号在负载端的反射系数接近+1,因此反射信号的幅度接近原始信号幅度的50%;C 反射信号与源端传播的信号叠加,使负载端接受到的信号与原始信号的幅度近似相同;D 负载端反射信号向源端传播,到达源端后被匹配电阻汲取;E 反射信号到达源端后,源端驱动电流降为0,直到下一次信号传输。

相对并联匹配来说,串联匹配不要求信号驱动器具有很大的电流驱动力量。

选择串联终端匹配电阻值的原则很简洁,就是要求匹配电阻值与驱动器的输出阻抗之和与传输线的特征阻抗相等。

抱负的信号驱动器的输出阻抗为零,实际的驱动器总是有比较小的输出阻抗,而且在信号的电平发生变化时,输出阻抗可能不同。

比如电源电压为+4.5V的CMOS驱动器,在低电平常典型的输出阻抗为37Ω,在高电平常典型的输出阻抗为45Ω[4];TTL驱动器和CMOS驱动一样,其输出阻抗会随信号的电平大小变化而变化。

阻抗匹配原理

阻抗匹配原理阻抗匹配是电子电路中的重要概念,它能够有效地提高信号传输的效率,降低信号反射和损耗。

在实际电路设计中,阻抗匹配原理被广泛应用于各种通信系统、射频电路和微波电路中。

本文将介绍阻抗匹配的基本原理、常见的匹配网络以及在电路设计中的应用。

阻抗匹配的基本原理是为了使信号源和负载之间的阻抗相互匹配,从而最大限度地传输能量,减小信号反射。

在电路中,如果信号源的输出阻抗与负载的输入阻抗不匹配,就会导致信号反射和能量损耗。

因此,为了最大限度地传输信号能量,需要采取一定的方法来匹配信号源和负载之间的阻抗。

常见的阻抗匹配网络包括L型匹配网络、π型匹配网络、串联匹配网络和并联匹配网络。

这些匹配网络可以通过合适的阻抗变换元件,如电感、电容和阻性元件,来实现阻抗的匹配。

在实际电路设计中,设计工程师需要根据具体的应用场景和要求,选择合适的匹配网络来实现阻抗匹配。

阻抗匹配在电路设计中起着至关重要的作用。

在射频和微波电路中,阻抗匹配可以有效地提高信号传输的效率,降低信号反射和损耗,从而提高整个系统的性能。

在通信系统中,阻抗匹配可以保证信号的稳定传输,提高通信质量。

因此,设计工程师需要深入理解阻抗匹配原理,并灵活运用在实际的电路设计中。

总之,阻抗匹配原理是电子电路设计中不可或缺的重要概念。

通过合理的阻抗匹配,可以提高信号传输效率,降低信号反射和损耗,从而提高整个系统的性能。

在实际的电路设计中,设计工程师需要根据具体的应用场景和要求,选择合适的匹配网络来实现阻抗匹配,从而达到最佳的设计效果。

希望本文能够帮助读者更好地理解阻抗匹配原理,并在实际的电路设计中加以运用。

阻抗匹配的原理与应用 (2)

阻抗匹配的原理与应用1. 什么是阻抗匹配?阻抗匹配是指在电路或信号传输中,通过调整电阻、电感或电容等元件的数值,使输入端和输出端的阻抗相匹配的一种技术手段。

阻抗匹配可以最大限度地提高信号的传输效率,减小信号的反射和损耗。

2. 阻抗匹配的原理阻抗匹配的原理基于最大功率传输定理。

在电路中,当信号源和负载的阻抗不匹配时,会发生信号的反射,导致部分信号被反射回去,无法有效地传输到负载端。

阻抗匹配的目的就是使信号的阻抗在传输线上保持一致,最大限度地减小信号的反射。

具体来说,阻抗匹配可以通过以下几种方式来实现:•串联阻抗匹配:通过串联一个适当的阻抗元件,将输入端的阻抗与输出端的阻抗匹配。

这种方法常用于信号源的输出阻抗与负载的输入阻抗不匹配的情况。

•并联阻抗匹配:通过并联一个适当的阻抗元件,将输出端的阻抗与输入端的阻抗匹配。

这种方法常用于负载的输出阻抗与输入端的阻抗不匹配的情况。

•变压器阻抗匹配:通过变压器的变压比调整输入端和输出端的阻抗,从而实现阻抗的匹配。

这种方法常用于交流电路中。

3. 阻抗匹配的应用阻抗匹配在电子电路设计和信号传输中都有广泛的应用。

下面列举了一些常见的应用场景:3.1. 无线通信系统在无线通信系统中,为了提高信号传输的效果,常常需要进行阻抗匹配。

例如,将发射机的输出阻抗与天线的输入阻抗匹配,可以提高信号的传输距离和质量。

3.2. 音频放大器设计在音频放大器设计中,为了最大限度地提高功率传输效率,需要进行输入端和输出端的阻抗匹配。

这样可以减小信号的失真和损耗,提高音频信号的质量。

3.3. 射频电路设计在射频电路设计中,阻抗匹配是非常重要的一步。

射频信号的频率特性对阻抗匹配的要求比较高,需要通过精确的电路设计和调整来实现良好的阻抗匹配。

3.4. 混频器设计在混频器设计中,为了提高混频器的性能,通常需要进行阻抗匹配。

阻抗匹配能够减小信号的泊松噪声、杂散响应和失真,提高混频器的输入阻抗和输出阻抗。

高速数字电路设计中的时钟信号分析

高速数字电路设计中的时钟信号分析在高速数字电路设计中,时钟信号分析是一个至关重要的环节。

时钟信号在数字电路中扮演着同步和调控的角色,确保各个部件能够按照预定的节奏工作,保证整个系统的稳定性和可靠性。

因此,正确地分析和设计时钟信号是设计数字电路的重要一环。

首先,时钟信号的频率是时钟设计中的一个关键参数。

时钟信号的频率决定了系统的工作速度和性能。

在设计时钟信号时,需要考虑系统的整体需求和性能要求,选择合适的时钟频率。

通常情况下,时钟频率越高,系统性能越好,但也会增加功耗和设计复杂度。

因此,在选择时钟频率时需综合考虑系统的实际需求和性能指标。

其次,时钟信号的相位和延迟也是时钟设计中需要关注的重要参数。

时钟信号的相位关系着各个部件的协同工作和数据的传输速度。

合理设计时钟信号的相位可以有效地减少系统中的时序问题和数据传输错误。

而时钟信号的延迟则影响着系统的响应速度和数据传输效率。

因此,在设计时钟信号时,需要严格控制时钟信号的相位和延迟,确保系统的稳定性和性能。

另外,时钟信号的波形和质量也是时钟设计中需要考虑的重要因素。

时钟信号的波形应当稳定、清晰,确保各个部件能够准确地识别和响应时钟信号。

而时钟信号的质量则包括时钟信号的峰值、占空比、上升时间和下降时间等参数,质量好的时钟信号可以降低系统中的时序问题和数据传输错误。

因此,在设计时钟信号时,需要选择合适的时钟源和时钟分配策略,确保时钟信号的波形和质量达到要求。

最后,在高速数字电路设计中,时钟信号的布线和阻抗匹配也是一个重要的考量因素。

时钟信号的布线设计直接影响着时钟信号的传输速度和稳定性,合理设计时钟信号的布线可以有效地减少信号串扰和传输延迟。

而时钟信号的阻抗匹配则关系着信号的功耗和抗干扰能力,正确匹配时钟信号的阻抗可以提高系统的稳定性和可靠性。

因此,在设计时钟信号时,需要合理设计时钟信号的布线和确保时钟信号的阻抗匹配,以提高系统的性能和可靠性。

综上所述,时钟信号在高速数字电路设计中扮演着至关重要的角色,设计好时钟信号是确保系统性能和可靠性的关键一环。

阻抗匹配原理

阻抗匹配原理阻抗匹配原理是一种用于改善信号传输中信号完整性和电源效率的概念。

它可以改善从接收器到放大器(以及放大器到设备)中信号完整性和电源效率。

阻抗匹配是一种设计有效的信号传输系统的重要技术。

它使用一种反馈技术,以确保信号有效地从发送端到接收端的传输。

阻抗匹配的重要性在于,它将源端和接收端的阻抗(以及电源)调整到一个互动的值,这样可以有效地传输最大能量。

例如,假设源端有50Ω阻抗,而接收端有80Ω阻抗,那么两端的阻抗就不匹配,因此传输的最大能量也就大大降低了。

使用阻抗匹配原理,可以将源端的电阻调整为与接收端的电阻相匹配,以获得最佳的信号传输能力。

阻抗匹配是一种电气系统的设计原理,用来确保最佳的能量传输效率。

它采用一种名为“反馈”的方法,来确保信号从发送端有效传输到接收端。

反馈原理让源端和接收端的阻抗(及电源)同时调整到一个和谐的值,这样就可以有效地传输最大能量。

另外,阻抗匹配采用原理还可以用来改善发射机,接收器和无线电设备之间的信号传输,这样可以提高电源效率和信号完整性。

例如,当两个元件之间的阻抗不一致时,作为发射机的电路中的能量被浪费,这也将影响信号的传输效率和信号完整性。

但是,如果采用阻抗匹配技术,可以提供更好的传输效率和信号完整性。

通过阻抗匹配的作用,可以确保最佳的能量传输效率。

这样做不仅可以提高效率,还可以降低系统的工作噪声,同时减少电源损耗。

总之,使用阻抗匹配原理是确保最佳电源效率和信号完整性的有效工具。

阻抗匹配技术的应用可以追溯到古人,电路的阻抗匹配也是一种古老的技术,可以实现有效的信号传输。

随着技术的发展,阻抗匹配技术被应用于更多的领域,如:无线传输、光纤通信和电缆通信等等。

如今,阻抗匹配在电子行业被广泛地应用,扮演着重要的角色。

总之,阻抗匹配原理是一种关于改善信号传输中信号完整性和电源效率的概念。

它可以有效地调整源端和接收端的阻抗,以达到最佳的信号传输效率和信号完整性。

它的重要性不言而喻,因此,阻抗匹配原理是现在电子技术的重要组成部分。

时序问题 阻抗不匹配的原因

时序问题阻抗不匹配的原因

阻抗不匹配的原因有多种,主要包括:

1. 驱动源、传输线和负载的阻抗不同。

这是最主要的阻抗不匹配的原因。

2. 传输线的不连续,例如导通孔、短截线。

3. 返回路径上局部电感、电容的变化或返回路径不连续。

4. 传输线材料、连接器以及外部设备造成的阻抗不匹配。

5. 信号发生器或传感器内部电路中阻抗不匹配。

阻抗不匹配会导致信号的反射和衰减,具体表现为信号的反向传输、信号衰减以及信号失真等。

在实际应用中,为了避免阻抗不匹配对信号的影响,可以采取的措施包括使用匹配阻抗的元件(如变压器)、调整传输线的长度、设置阻抗转换器等等。

芯片级原子钟射频模块阻抗匹配设计

芯片级原子钟射频模块阻抗匹配设计

芯片级原子钟射频模块的阻抗匹配设计至关重要,它可以确保电路的

最佳性能和稳定性。

以下是一些实用的阻抗匹配设计步骤:

1.首先,确定射频模块中的关键部件,例如晶体管、传输线、电感器等。

这些元件的阻抗应该匹配,以确保信号传输流畅。

2.接下来,进行模块的阻抗分析。

使用模拟器或软件模型来分析电路

的阻抗,然后识别任何不匹配的地方。

3.根据分析结果,采取合适的措施进行匹配。

可以使用传输线、变压器、网络分析仪等工具来匹配阻抗。

4.优化设计。

进行进一步的模拟和测试,以确保模块阻抗的最优匹配。

需要注意的是,芯片级射频模块的设计需要对电路和材料的性能有深

入的了解和技能。

在设计和制造过程中需要遵循严格的规范和标准,以确

保最终产品的质量和稳定性。

时钟信号RC阻抗匹配

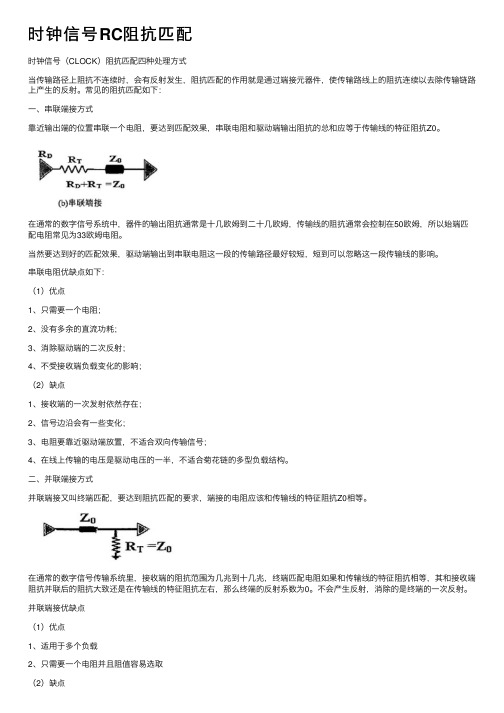

时钟信号RC阻抗匹配时钟信号(CLOCK)阻抗匹配四种处理⽅式当传输路径上阻抗不连续时,会有反射发⽣,阻抗匹配的作⽤就是通过端接元器件,使传输路线上的阻抗连续以去除传输链路上产⽣的反射。

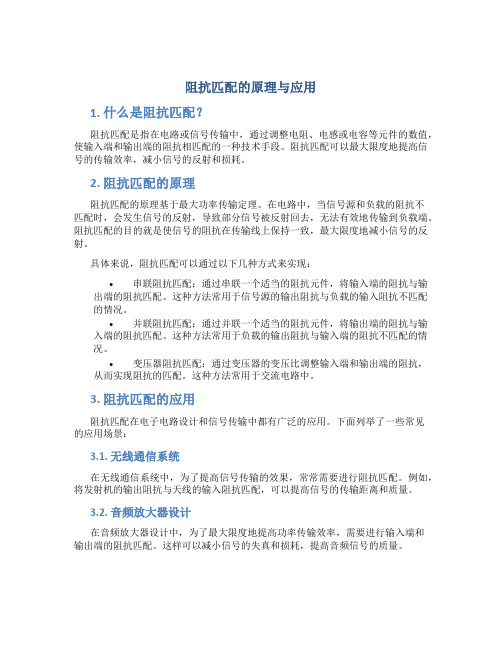

常见的阻抗匹配如下:⼀、串联端接⽅式靠近输出端的位置串联⼀个电阻,要达到匹配效果,串联电阻和驱动端输出阻抗的总和应等于传输线的特征阻抗Z0。

在通常的数字信号系统中,器件的输出阻抗通常是⼗⼏欧姆到⼆⼗⼏欧姆,传输线的阻抗通常会控制在50欧姆,所以始端匹配电阻常见为33欧姆电阻。

当然要达到好的匹配效果,驱动端输出到串联电阻这⼀段的传输路径最好较短,短到可以忽略这⼀段传输线的影响。

串联电阻优缺点如下:(1)优点1、只需要⼀个电阻;2、没有多余的直流功耗;3、消除驱动端的⼆次反射;4、不受接收端负载变化的影响;(2)缺点1、接收端的⼀次发射依然存在;2、信号边沿会有⼀些变化;3、电阻要靠近驱动端放置,不适合双向传输信号;4、在线上传输的电压是驱动电压的⼀半,不适合菊花链的多型负载结构。

⼆、并联端接⽅式并联端接⼜叫终端匹配,要达到阻抗匹配的要求,端接的电阻应该和传输线的特征阻抗Z0相等。

在通常的数字信号传输系统⾥,接收端的阻抗范围为⼏兆到⼗⼏兆,终端匹配电阻如果和传输线的特征阻抗相等,其和接收端阻抗并联后的阻抗⼤致还是在传输线的特征阻抗左右,那么终端的反射系数为0。

不会产⽣反射,消除的是终端的⼀次反射。

并联端接优缺点(1)优点1、适⽤于多个负载2、只需要⼀个电阻并且阻值容易选取(2)缺点1、增加了直流功耗2、并联端接可以上拉到电源或者下拉到地,是的低电平升⾼或者⾼电平降低,减⼩噪声容限。

三、AC并联端接并联端接为消除直流功耗,可以采⽤如下所⽰的AC并联端接(AC终端匹配)。

要达到匹配要求,端接的电阻应该和传输线的特征阻抗Z0相等。

优缺点描述如下:(1)优点1、适⽤于多个负载2、⽆直流功耗增加(2)缺点1、需要两个器件2、增加了终端的容性负载,增加了RC电路造成的延时3、对周期性的信号有效(如时钟),不适合于⾮周期信号(如数据)四、戴维南端接戴维南端接同终端匹配,如下图,要达到匹配要求,终端的电阻并联值要和传输线的特征阻抗Z0相等。

时钟线、数据线、地址线上串联小电阻作用分析与阻抗匹配

经常看到时钟线/数据线/地址线上串联一个小电阻有什么作用?2008-09-05 14:19这个电阻有两个作用,第一是阻抗匹配。

因为信号源的阻抗很低,跟信号线之间阻抗不匹配,串上一个电阻后,可改善匹配情况,以减少反射,避免振荡等。

第二是可以减少信号边沿的陡峭程度,从而减少高频噪声以及过冲等。

因为串联的电阻,跟信号线的分布电容以及负载的输入电容等形成一个RC电路,这样就会降低信号边沿的陡峭程度。

大家知道,如果一个信号的边沿非常陡峭,含有大量的高频成分,将会辐射干扰,另外,也容易产生过冲。

通常,在高速信号线中才考虑使用这样的电阻。

在低频情况下,一般是直接连接。

怎样理解阻抗匹配?2008-09-05 14:19阻抗匹配是指信号源或者传输线跟负载之间的一种合适的搭配方式。

阻抗匹配分为低频和高频两种情况讨论。

我们先从直流电压源驱动一个负载入手。

由于实际的电压源,总是有内阻的(请参看输出阻抗一问),我们可以把一个实际电压源,等效成一个理想的电压源跟一个电阻r串联的模型。

假设负载电阻为R,电源电动势为U,内阻为r,那么我们可以计算出流过电阻R的电流为:I=U/(R+r),可以看出,负载电阻R越小,则输出电流越大。

负载R上的电压为:Uo=IR=U/[1+(r/R)],可以看出,负载电阻R越大,则输出电压Uo越高。

再来计算一下电阻R消耗的功率为:P=I2×R=[U/(R+r)]2×R=U2×R/(R2+2×R×r+r2) =U2×R/[(R-r)2+4×R×r] =U2/{[(R-r)2/R]+4×r}对于一个给定的信号源,其内阻r是固定的,而负载电阻R则是由我们来选择的。

注意式中[(R-r)2/R],当R=r时,[(R-r)2/R]可取得最小值0,这时负载电阻R上可获得最大输出功率Pmax=U2/(4×r)。

即,当负载电阻跟信号源内阻相等时,负载可获得最大输出功率,这就是我们常说的阻抗匹配之一。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

时钟信号(CLOCK)阻抗匹配四种处理方式

当传输路径上阻抗不连续时,会有反射发生,阻抗匹配的作用就是通过端接元器件,使传输路线上的阻抗连续以去除传输链路上产生的反射。

常见的阻抗匹配如下:

一、串联端接方式

靠近输出端的位置串联一个电阻,要达到匹配效果,串联电阻和驱动端输出阻抗的总和应等于传输线的特征阻抗Z0。

在通常的数字信号系统中,器件的输出阻抗通常是十几欧姆到二十几欧姆,传输线的阻抗通常会控制在50欧姆,所以始端匹配电阻常见为33欧姆电阻。

当然要达到好的匹配效果,驱动端输出到串联电阻这一段的传输路径最好较短,短到可以忽略这一段传输线的影响。

串联电阻优缺点如下:

(1)优点

1、只需要一个电阻;

2、没有多余的直流功耗;

3、消除驱动端的二次反射;

4、不受接收端负载变化的影响;

(2)缺点

1、接收端的一次发射依然存在;

2、信号边沿会有一些变化;

3、电阻要靠近驱动端放置,不适合双向传输信号;

4、在线上传输的电压是驱动电压的一半,不适合菊花链的多型负载结构。

二、并联端接方式

并联端接又叫终端匹配,要达到阻抗匹配的要求,端接的电阻应该和传输线的特征阻抗Z0相等。

在通常的数字信号传输系统里,接收端的阻抗范围为几兆到十几兆,终端匹配电阻如果和传输线的特征阻抗相等,其和接收端阻抗并联后的阻抗大致还是在传输线的特征阻抗左右,那么终端的反射系数为0。

不会产生反射,消除的是终端的一次反射。

并联端接优缺点

(1)优点

1、适用于多个负载

2、只需要一个电阻并且阻值容易选取

(2)缺点

1、增加了直流功耗

2、并联端接可以上拉到电源或者下拉到地,是的低电平升高或者高电平降低,减小噪声容限。

三、AC并联端接

并联端接为消除直流功耗,可以采用如下所示的AC并联端接(AC终端匹配)。

要达到匹配要求,端接的电阻应该和传输线的特征阻抗Z0相等。

优缺点描述如下:

(1)优点

1、适用于多个负载

2、无直流功耗增加

(2)缺点

1、需要两个器件

2、增加了终端的容性负载,增加了RC电路造成的延时

3、对周期性的信号有效(如时钟),不适合于非周期信号(如数据)

四、戴维南端接

戴维南端接同终端匹配,如下图,要达到匹配要求,终端的电阻并联值要和传输

线的特征阻抗Z0相等。

优缺点描述:

(1)优点

1、适用于多个负载

2、很适用于SSTL/HSTL电平上拉或下拉输出阻抗很好平衡的情况。

(2)缺点

1、直流功耗增加

2、需要两个器件

3、端接电阻上拉到电源或下拉到地,会使得低电平升高或高电平降低

4、电阻值较难选择,电阻值取值小会使低电平升高,高电平降低更加恶劣;电阻值取大有可能造成不能完全匹配,使反射增大,可以通过仿真来确定。