数字电子技术第四章习题答案

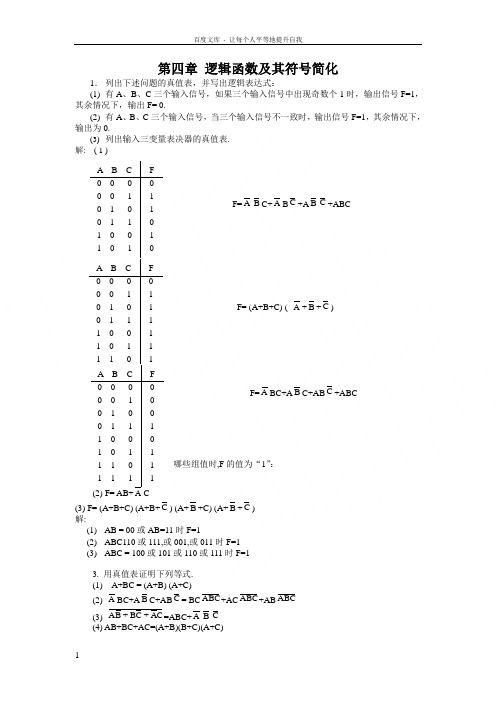

《数字电子技术基础》第四章习题答案

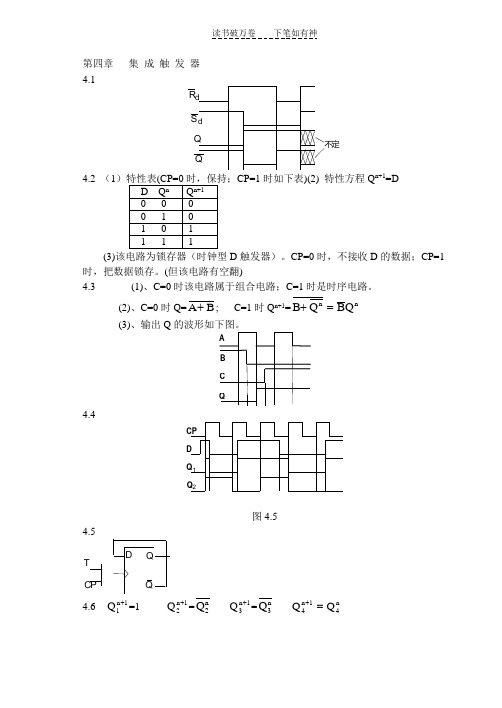

第四章 集 成 触 发 器 4.1R d S d Q Q不定4.2 (1CP=1时如下表)(2) 特性方程Q n+1=D(3)该电路为锁存器(时钟型D 触发器)。

CP=0时,不接收D 的数据;CP=1时,把数据锁存。

(但该电路有空翻)4.3 (1)、C=0时该电路属于组合电路;C=1时是时序电路。

(2)、C=0时Q=A B +; C=1时Q n+1=B Q BQ nn+= (3)、输出Q 的波形如下图。

A B C Q4.4CP D Q 1Q 2图4.54.5 DQ QCPT4.6 Q 1n 1+=1 Q 2n 1+=Q 2n Q n 13+=Q n 3 Q Q 4n 14n+=Q1CP Q2Q3Q44.7 1、CP 作用下的输出Q 1 Q 2和Z 的波形如下图; 2、Z 对CP 三分频。

DQ QCPQ1DQ QQ2ZRd CP Q1Q2Z14.8由Q D J Q KQ J Q KQ n 1n n n n +==+=⋅得D 触发器转换为J-K 触发器的逻辑图如下面的左图;而将J-K 触发器转换为D 触发器的逻辑图如下面的右图CPD Q QJKQ QDQ QJ KCP4.9CP B CA4.10CP X Q1Q2Z4.11 1、555定时器构成多谐振荡器 2、u c, u o 1, u o 2的波形u c u o 1u o 2t t t 1.67V3.33V3、u o 1的频率f 1=1074501316..H z ⨯⨯≈ u o 2的频率f 2=158H z4、如果在555定时器的第5脚接入4V 的电压源,则u o 1的频率变为1113001071501232....H z ⨯⨯+⨯⨯≈4.12 图(a)是由555定时器构成的单稳态触发电路。

1、工作原理(略);2、暂稳态维持时间t w =1.1RC=10ms(C 改为1μF);3、u c 和u o 的波形如下图:u ou ct t tu i (ms)(ms)(ms)5 10 25 30 45 503.33V4、若u i 的低电平维持时间为15m s ,要求暂稳态维持时间t w 不变,可加入微分电路4.13由555定时器构成的施密特触发器如图(a)所示 1、电路的电压传输特性曲线如左下图; 2、u o 的波形如右下图;3、为使电路能识别出u i 中的第二个尖峰,应降低555定时器5脚的电压至3V 左右。

数字电子技术第4章组合逻辑电路习题解答

习题4.1写出图所示电路的逻辑表达式,并说明电路实现哪种逻辑门的功能。

习题4.1图解:B A B A B A B A B A F ⊕=+=+= 该电路实现异或门的功能4.2分析图所示电路,写出输出函数F 。

习题4.2图解:[]B A B BB A F ⊕=⊕⊕⊕=)(4.3已知图示电路及输入A 、B 的波形,试画出相应的输出波形F ,不计门的延迟.图解:B A B A B A AB B AB A AB B AB A F ⊕=•=•••=•••=4.4由与非门构成的某表决电路如图所示。

其中A 、B 、C 、D 表示4个人,L=1时表示决议通过。

(1) 试分析电路,说明决议通过的情况有几种。

(2) 分析A 、B 、C 、D 四个人中,谁的权利最大。

习题4.4图解:(1)ABD BC CD ABD BC CD L ++=••=B AC & && & D L B A =1 =1=1FF A B & &&& & F B A(3)4.5分析图所示逻辑电路,已知S 1﹑S 0为功能控制输入,A ﹑B 为输入信号,L 为输出,求电路所具有的功能。

习题4.5图解:(1)011011)(S S B S A S S B S A L ⊕⊕+⊕=⊕⊕•⊕= (2)4.6试分析图所示电路的逻辑功能。

习题4.6图解:(1)ABC C B A F )(++=10电路逻辑功能为:“判输入ABC 是否相同”电路。

4.7已知某组合电路的输入A 、B 、C 和输出F 的波形如下图所示,试写出F 的最简与或表达式。

习题4.7图解:(1)根据波形图得到真值表:C AB BC A C B A F ++=4.8、设∑=)14,12,10,9,8,4,2(),,,(m D C B A F ,要求用最简单的方法,实现的电路最简单。

1)用与非门实现。

2)用或非门实现。

3) 用与或非门实现。

数字电子技术基础教材第四章答案

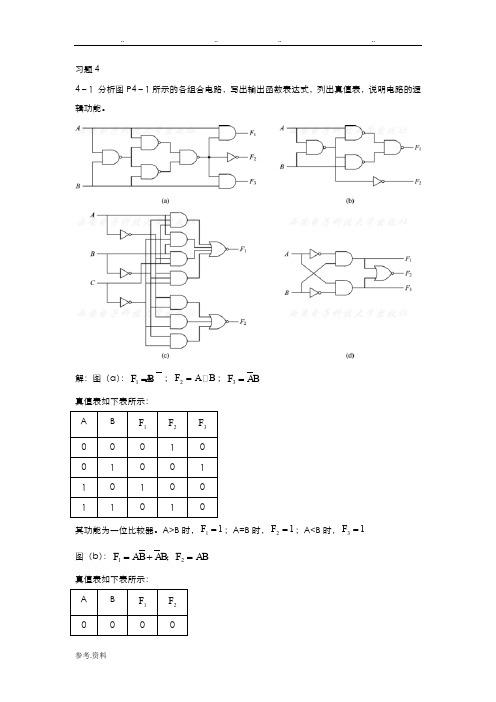

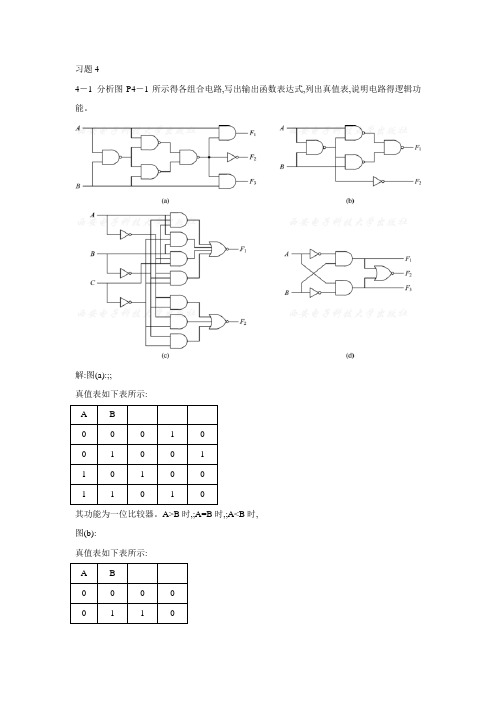

习题44-1 分析图P4-1所示的各组合电路,写出输出函数表达式,列出真值表,说明电路的逻辑功能。

解:图(a ):1F A B =;2F A B =;3F AB =真值表如下表所示:其功能为一位比较器。

A>B 时,11F =;A=B 时,21F =;A<B 时,31F = 图(b ):12F AB AB F AB =+=; 真值表如下表所示:功能:一位半加器,1F 为本位和,2F 为进位。

图(c ):1(0,35,6)(124,7)F M m==∑∏2(0,1,2,4)(3,5,6,7)F M m ==∑∏真值表如下表所示:功能:一位全加器,1F 为本位和,2F 为本位向高位的进位。

图(d ):1F A B =;2F A B =;3F AB =功能:为一位比较器,A<B 时,1F =1;A=B 时,2F =1;A>B 时,3F =14-2 分析图P4-2所示的组合电路,写出输出函数表达式,列出真值表,指出该电路完成的逻辑功能。

解:该电路的输出逻辑函数表达式为:100101102103F A A x A A x A A x A A x =+++因此该电路是一个四选一数据选择器,其真值表如下表所示:4-3 图P4-3是一个受M 控制的代码转换电路,当M =1时,完成4为二进制码至格雷码的转换;当M =0时,完成4为格雷码至二进制的转换。

试分别写出0Y ,1Y ,2Y ,3Y 的逻辑函数的表达式,并列出真值表,说明该电路的工作原理。

解:该电路的输入为3x 2x 1x 0x ,输出为3Y 2Y 1Y 0Y 。

真值表如下:由此可得:1M =当时,33232121010Yx Y x x Y x x Y x x =⎧⎪=⊕⎪⎨=⊕⎪⎪=⊕⎩ 完成二进制至格雷码的转换。

0M =当时,332321321210321010Y x Y x x Y x x x Y x Y x x x x Y x =⎧⎪=⊕⎪⎨=⊕⊕=⊕⎪⎪=⊕⊕⊕=⊕⎩ 完成格雷码至二进制的转换。

数字电子技术第四章课后习题答案(江晓安等编)

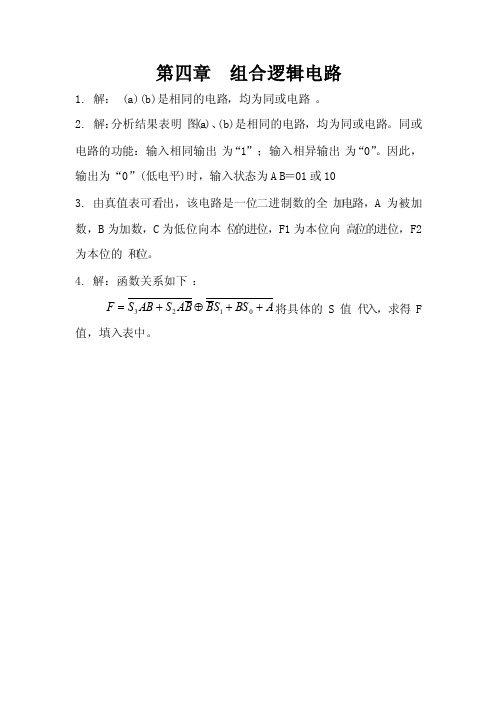

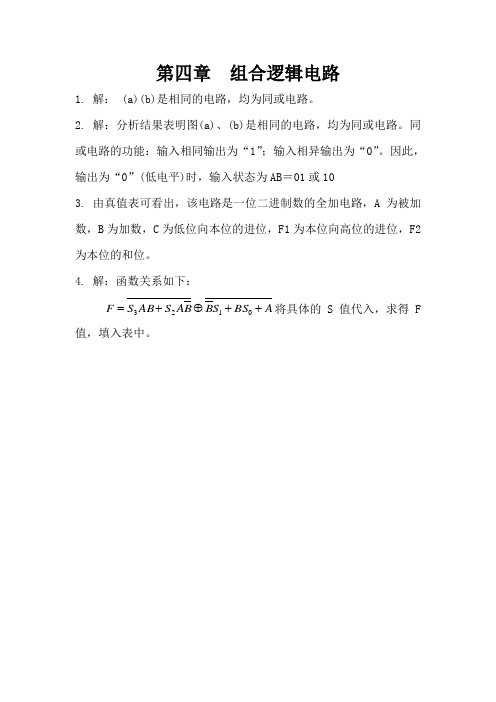

第四章组合逻辑电路1. 解: (a)(b)是相同的电路,均为同或电路。

2. 解:分析结果表明图(a)、(b)是相同的电路,均为同或电路。

同或电路的功能:输入相同输出为“1”;输入相异输出为“0”。

因此,输出为“0”(低电平)时,输入状态为AB=01或103. 由真值表可看出,该电路是一位二进制数的全加电路,A为被加数,B为加数,C为低位向本位的进位,F1为本位向高位的进位,F2为本位的和位。

4. 解:函数关系如下:SF++⊕=+ABSABS BABS将具体的S值代入,求得F 312值,填入表中。

A A FB A B A B A A F B A B A A F A A F AB AB F B B A AB F AB B A B A B A AB F B A A AB F B A B A B A F B A AB AB B A B A F B B A B A B A B A B A B A F AB BA A A B A A B A F F B A B A F B A B A F A A F S S S S =⊕==+==+⊕===+⊕===⊕===⊕===+⊕===+=+⊕===⊕==+==⊕==Θ=+=+⊕===+++=+⊕===+=⊕===⊕==+=+⊕==+=+⊕===⊕==01111111011010110001011101010011000001110110)(01010100101001110010100011000001235. (1)用异或门实现,电路图如图(a)所示。

(2) 用与或门实现,电路图如图(b)所示。

6. 解因为一天24小时,所以需要5个变量。

P变量表示上午或下午,P=0为上午,P=1为下午;ABCD表示时间数值。

真值表如表所示。

利用卡诺图化简如图(a)所示。

化简后的函数表达式为D C A P D B A P C B A P A P DC A PD B A P C B A P A P F =+++=用与非门实现的逻辑图如图(b )所示。

数字电子技术_第四章课后习题答案_(江晓安等编)

第四章组合逻辑电路1. 解: (a)(b)是相同的电路,均为同或电路。

2. 解:分析结果表明图(a)、(b)是相同的电路,均为同或电路。

同或电路的功能:输入相同输出为“1”;输入相异输出为“0”。

因此,输出为“0”(低电平)时,输入状态为AB=01或103. 由真值表可看出,该电路是一位二进制数的全加电路,A为被加数,B为加数,C为低位向本位的进位,F1为本位向高位的进位,F2为本位的和位。

4. 解:函数关系如下:ABSF+⊕=++ABSSSABB将具体的S值代入,求得F 312值,填入表中。

A A FB A B A B A A F B A B A A F A A F AB AB F B B A AB F AB B A B A B A AB F B A A AB F B A B A B A F B A AB AB B A B A F B B A B A B A B A B A B A F AB BA A A B A A B A F F B A B A F B A B A F A A F S S S S =⊕==+==+⊕===+⊕===⊕===⊕===+⊕===+=+⊕===⊕==+==⊕==Θ=+=+⊕===+++=+⊕===+=⊕===⊕==+=+⊕==+=+⊕===⊕==01111111011010110001011101010011000001110110)(01010100101001110010100011000001235. (1)用异或门实现,电路图如图(a)所示。

(2) 用与或门实现,电路图如图(b)所示。

6. 解因为一天24小时,所以需要5个变量。

P变量表示上午或下午,P=0为上午,P=1为下午;ABCD表示时间数值。

真值表如表所示。

利用卡诺图化简如图(a)所示。

化简后的函数表达式为D C A P D B A P C B A P A P DC A PD B A P C B A P A P F =+++=用与非门实现的逻辑图如图(b)所示。

数字电子技术基础(第四版)课后习题答案_第四章

第4章触发器[题4.1]画出图P4.1所示由与非门组成的根本RS触发器输出端Q、Q的电压波形,输入端S、R的电压波形如图中所示。

图P4.1[解]见图A4.1图A4.1[题4.2]画出图P4.2由或非门组成的根本R-S触发器输出端Q、Q的电压波形,输出入端S D,R D的电压波形如图中所示。

图P4.2[解]见图A4.2[题4.3]试分析图P4.3所示电路的逻辑功能,列出真值表写出逻辑函数式。

图P4.3 [解]:图P4.3所示电路的真值表S R Q n Q n+1 0 0 0 0 0 0 1 1 0 1 0 0 0 1 1 0 1 0 0 1 1 0 1 1 1 1 0 0* 1 110*由真值表得逻辑函数式 01=+=+SR Q R S Q nn[题4.4] 图P4.4所示为一个防抖动输出的开关电路。

当拨动开关S 时,由于开关触点接触瞬间发生振颤,D S 和D R 的电压波形如图中所示,试画出Q 、Q 端对应的电压波形。

图P4.4[解] 见图A4.4图A4.4[题4.5] 在图P4.5电路中,假设CP 、S 、R 的电压波形如图中所示,试画出Q 和Q 端与之对应的电压波形。

假定触发器的初始状态为Q =0。

图P4.5[解]见图A4.5图A4.5[题4.6]假设将同步RS触发器的Q与R、Q与S相连如图P4.6所示,试画出在CP 信号作用下Q和Q端的电压波形。

己知CP信号的宽度t w = 4 t Pd 。

t Pd为门电路的平均传输延迟时间,假定t Pd≈t PHL≈t PLH,设触发器的初始状态为Q=0。

图P4.6图A4.6[解]见图A4.6[题4.7]假设主从结构RS触发器各输入端的电压波形如图P4.7中所给出,试画Q、Q端对应的电压波形。

设触发器的初始状态为Q=0。

图P4.7[解] 见图A4.7图A4.7[题4.8]假设主从结构RS触发器的CP、S、R、DR各输入端的电压波形如图P4.8所示,1DS。

数电第四章习题答案

4.11图P4.11(a)所示各电路中,FF1~FF2均为边沿触发器:

1)写出各个触发器次态输出的函数表达式;

图P4.2

解答:见图A4.2

图A4.2

4.3一种特殊的RS触发器如图P4.3所示。

1)试列出状态转换真值表;

2)写出次态方程;

3)R与S是否需要约束条件?

图P4.3

解答:1)

①CP=0时,SS=1,RR=1,期间 ,状态保持。

2CP=1时,

即在CP=1的情况下:若R=0,S=0。则RR=1,SS=1,有 ,状态保持。

图P4.13

解答:根据电路图可知 ,而该电路中的触发器是CP上升沿触发的D触发器,其新态方程为: 。据已知的CP信号波形,可以画出A、B端的输出波形如图A4.13所示。

图A4.13

4.14什么是触发器的空翻现象?造成空翻的原因是什么?

解答:所谓触发器的“空翻”是指在同一个时钟脉冲作用期间触发器状态发生两次或两次以

图A4.17

4.18图P4.18一个扭环计数器,如果电路的初始状态为 ,试画出在一系列CP作用下的 、 、 、 波形(CP数目多于8)。

图P4.18

解答:从电路图可知, (CP上升沿时成立)

如果电路的初始状态为 ,可以画出在一系列CP作用下 、 、 、 的波形如图A4.18所示。

图A4.18

4.19据如图P4.19示的电路,试画出在8个CP作用下 、 、 的波形,假设电路的初始状态为 。

为使主从JK触发器按其特性表正常工作,在CP = 1期间,必须使JK端的状态保持

数字电路与数字电子技术课后答案第四章

数字电路与数字电子技术-课后答案第四章第四章逻辑函数及其符号简化1.列出下述问题的真值表,并写出逻辑表达式:(1)有A、B、C三个输入信号,如果三个输入信号中出现奇数个1时,输出信号F=1,其余情况下,输出F= 0.(2)有A、B、C三个输入信号,当三个输入信号不一致时,输出信号F=1,其余情况下,输出为0.(3)列出输入三变量表决器的真值表.解: ( 1 )F=A B C+A B C+A B C+ABC ( 2 )F= (A+B+C) ( A+B+C)A BC F0 00 00 0A BC F0 00 00 0F=A BC+A B C+AB C+ABC2. 对下列函数指出变量取哪些组值时,F的值为“1”:(1) F= AB+A B(2) F= AB+A C(3) F= (A+B+C) (A+B+C) (A+B+C) (A+B+C) 解:(1)AB = 00或AB=11时F=1(2)ABC110或111,或001,或011时F=1(3)ABC = 100或101或110或111时F=1 3. 用真值表证明下列等式.(1) A+BC = (A+B) (A+C)(2) A BC+A B C+AB C= BC ABC+AC ABC+AB ABC(3) C A+C B+B A=ABC+A B C(4) AB+BC+AC=(A+B)(B+C)(A+C)(5) ABC+A+B+C=1证:( 1 )A B CA+BC(A+B)(A+C)0 0 00 0( 2 )A B C ABC + ABC + ABCBCABC + ACA B C + ABABC0 0 0 00 0 1 0( 3 )A B C AB +BC + AC ABC + A B C0 0 01 10 0 1( 4 )( 5 )4. 直接写出下列函数的对偶式F ′及反演式F 的函数表达式. A B C AB+BC+AC (A+B)(B+C)(A+C) 0 0 0 0 0 0 0 1 0 A B C ABC + A + B + C 0 0 0 1 0 0 1(1) F= [A B (C+D)][B C D+B (C+D)](2) F= A BC+ (A+B C) (A+C)(3) F= AB+CD+E+D+E C+D+BC(4) F=D+B A•B A+C解:(1)F`= [A+B+CD]+[(B+C+D)(•B+C D]]F= [A+B+C D]+[(B+C+D)(•B+C D]](2)F`= (A+C+B)]AC)C+B(•A[•F= (A+C+B)]C A+)C+B(•A[•(3)F`=)B+A(•C+D•)B+A(F=)B+A(•C+D•)B+A(5. 若已知x+y = x+z,问y = z吗?为什么? 解:y不一定等于z,因为若x=1时,若y=0,z=1,或y=1,z=0,则x+y = x+z = 1,逻辑或的特点,有一个为1则为1。

数字电子技术基础教材第四章答案

习题44-1 分析图P4-1所示得各组合电路,写出输出函数表达式,列出真值表,说明电路得逻辑功能。

解:图(a):;;真值表如下表所示:A B0 0 0 1 00 1 0 0 11 0 1 0 01 1 0 1 0其功能为一位比较器。

A>B时,;A=B时,;A<B时,图(b):真值表如下表所示:A B0 0 0 00 1 1 0功能:一位半加器,为本位与,为进位。

图(c):真值表如下表所示:功能:一位全加器,为本位与,为本位向高位得进位。

图(d):;;功能:为一位比较器,A<B时,=1;A=B时,=1;A>B时,=14-2 分析图P4-2所示得组合电路,写出输出函数表达式,列出真值表,指出该电路完成得逻辑功能。

解:该电路得输出逻辑函数表达式为:因此该电路就是一个四选一数据选择器,其真值表如下表所示:0 00 11 01 14-3 图P4-3就是一个受M控制得代码转换电路,当M=1时,完成4为二进制码至格雷码得转换;当M=0时,完成4为格雷码至二进制得转换。

试分别写出,,,得逻辑函数得表达式,并列出真值表,说明该电路得工作原理。

解:该电路得输入为,输出为。

真值表如下:M=1 0 0 0 0 0 0 0 00 0 0 1 0 0 0 10 0 1 0 0 0 1 10 0 1 1 0 0 1 00 1 0 0 0 1 1 00 1 0 1 0 1 1 10 1 1 0 0 1 0 10 1 1 0 0 1 0 0 M=0 1 0 0 0 1 1 1 11 0 0 1 1 1 1 01 0 1 0 1 1 0 01 0 1 1 1 1 0 11 1 0 0 1 0 0 01 1 0 1 1 0 0 11 1 1 0 1 0 1 11 1 1 1 1 0 1 0由此可得:完成二进制至格雷码得转换。

完成格雷码至二进制得转换。

4-4 图P4-4就是一个多功能逻辑运算电路,图中,,,为控制输入端。

数字电路与数字电子技术课后答案第四章(供参考)

(4) F=ΠM(5,7,13,15)

= BD

F= +

(5) F=ΠM(1,3,9,10,11,14,15)

= AC+ D

F = ( + )(B+ )

(6) F=∑m (0,2,4,9,11,14,15, 16,17,19,23,25,29,31)

F= + + BCD+ B E+AB E+ACDE+A +A E

= A⊙B⊙C

(6) = ⊙ ⊙

证:

左=

= [(A⊕B)+ ] (A⊙B)+C]

= (A⊙B) +[(A⊕B)C]

= +AB + BC+A C

右= ( ⊙ )⊙

= [( ⊙ ) + ]

= [( +AB) + ]

= +AB +

= +AB +(A⊕B)C

= +AB + BC+A C

9.证明

(1)如果a + b = c,则a + c = b,反之亦成立

(2)F在输入组合为1,3,5,7时使F=1

15.变化如下函数成另一种标准形式

(1) F=∑m (1,3,7)

(2) F=∑m (0,2,6,11,13,14)

(3) F=ΠM(0,3,6,7)

(4) F=ΠM(0,1,2,3,4,6,12)

解:

(1)F=ΠM(0,2,4,5,6)

(2)F=ΠM(1,3,4,5,7,8,9,10,12,15)

(3)F=∑m (1,2,4,5)

数字电子技术基础-课后习题答案第4章组合逻辑电路

第四章习题答案4-1(a)100A A F ⊕=,211A A F ⊕=,322A A F ⊕=,33A F =(b) 000B A C =,011111)()(C B A B A C ⊕+=,000B A S ⊕=,0111)(C B A S ⊕⊕= (c) B A AB F +=(同或)(d) B A AC F +=1,B A BC F +=2,C A BC F+=3, 4-2,F ,F ,F∑=)9,8,7,6,5(3m F ,∑=)9,4(2m F ,∑=)8,7,3,2(1m F ,∑=)8,6,3,1(0m F卡诺图化简D F =3,AD D C B F +=2,D A C B CD F ++=1,D B A D A F +=0,F ,F ,F∑=)9,8,7,6,5(3m Y ,∑=)9,4,3,2,1(2m Y , ∑=)8,7,4,3,0(1m Y ,∑=)8,6,4,2,0(0m Y用4-16线译码器实现987653F F F F F Y =,943212F F F F F Y =,874301F F F F F Y =,864200F F F F F Y =4-3将四片138译码器级联,ST 接高电平,ST 接低电平,ST 由译码控制3442A A ST =,3432A A ST =,3432A A ST =,3432A A ST =4-4113471347(1,3,4,7)F m m m m m F F F F ===∑ 2046046(0,4,6)F m m m m F F F ===∑4-51)一片8选1,输入A 、B 、C 分别接8选1的地址A 2,A 1,A 00,,1,17563420========D D D D D D D D D D2)两片8选1,输入A 、B 、C ,D 分别接4选1的地址012,,,A A A E1,01413121197651151084320================D D D D D D D D D D D D D D D D4-6A S SB A S S B A S S AB S S F 01010101)()(+⊕+++= A S S B A S S B A S S B S S A S S AB S S F 010*********+++++=将A S S ,,01分别接8选1的地址012,,A A A ,则输入端分别是0,1,,70635421========D D D D B D B D D D4-71) 输入A,B,C,D 分别接加法器的A 3,A 2,A 1,A 0, 加法器的B 3B 2B 1B 0=0011,CI=0 2) 输入A,B,C,D 分别接加法器的A 3,A 2,A 1,A 0, 加法器的B 3B 2B 1B 0=1101,CI=04-8假设四位被加数为ABCD ,加数为EFGH 输入A,B,C,D 分别接加法器的A 3,A 2,A 1,A 0, 加法器的B 3,B 2,B 1,B 0如下:M CI M H B M G B M F B M E B =⊕=⊕=⊕=⊕=,,,,01234-9真值表∑=)15,14,13,11,7(m F1)8选1数据选择器,将B A M ,,分别接8选1的地址012,,A A A ,则输入端分别是0,1,42107653========D D D D D C D D D2)用3-8译码器151413117151413117F F F F F m m m m m F ==4-10设三个开关分别为A,B,C ,开关的关闭为1,打开为0;灯的输出为F ,灯的亮为1,灭为0真值表C B A F =输入ABCD 分别接4-16译码器的地址段A 3,A 2,A 1,A 0 1) a 端:0158421=====D D D D D , 其余数据端接1 2) b 端:所有数据端均接1,1150=D D3) c 端:012109653======D D D D D D ,其余数据端接1 4) d 端:0158421=====D D D D D ,其余数据端接15) e 端:01514131187421=========D D D D D D D D D ,其余数据端接1 6) f 端:1150==D D ,其余数据端接07) g 端:08421====D D D D ,其余数据端接1设输出灯亮为1,灭为0真值表如下:1)4-16输入ABCD 分别接4-16译码器的地址段A 3,A 2,A 1,A 0(1) F 1端:143210=====D D D D D , 其余数据端接0 (2) F 2端:198765=====D D D D D , 其余数据端接0 (3) F3端:1151413121110======D D D D D D , 其余数据端接0 2)4位数据比较器实现用两片数据选择器,输入端ABCD 分别接两个比较器的A 3A 2A 1A 0,第一片比较器的B 3B 2B 1B 0=0101,第二片的B 3B 2B 1B 0=1001,两片的级联端0,1===<>=B A B A B A I I I ,则:B A I F <=11,B A I F >=23,212F F F =用4-16输入A 1A 0B 1B 0分别接4-16译码器的地址段A 3,A 2,A 1,A 0 (1) F 0端:1151375====D D D D , 其余数据端接0(2) F 1端:1141311976======D D D D D D , 其余数据端接0 (3) F 2端:1141110===D D D , 其余数据端接0 (4) F 3端:115=D , 其余数据端接04-141)只要把两片的B A I =直接相连就可以判断三个输入数据是否相等,假定输入为ABCD 四门课程,及格为1,不及格为0;输出F 为能否毕业,能够毕业为1,不能毕业为0。

数字电子技术基础第四章习题及参考答案

数字电子技术基础第四章习题及参考答案第四章习题1.分析图4-1中所示的同步时序逻辑电路,要求:(1)写出驱动方程、输出方程、状态方程;(2)画出状态转换图,并说出电路功能。

CPY图4-12.由D触发器组成的时序逻辑电路如图4-2所示,在图中所示的CP脉冲及D作用下,画出Q0、Q1的波形。

设触发器的初始状态为Q0=0,Q1=0。

D图4-23.试分析图4-3所示同步时序逻辑电路,要求:写出驱动方程、状态方程,列出状态真值表,画出状态图。

CP图4-34.一同步时序逻辑电路如图4-4所示,设各触发器的起始状态均为0态。

(1)作出电路的状态转换表;(2)画出电路的状态图;(3)画出CP作用下Q0、Q1、Q2的波形图;(4)说明电路的逻辑功能。

图4-45.试画出如图4-5所示电路在CP波形作用下的输出波形Q1及Q0,并说明它的功能(假设初态Q0Q1=00)。

CPQ1Q0CP图4-56.分析如图4-6所示同步时序逻辑电路的功能,写出分析过程。

Y图4-67.分析图4-7所示电路的逻辑功能。

(1)写出驱动方程、状态方程;(2)作出状态转移表、状态转移图;(3)指出电路的逻辑功能,并说明能否自启动;(4)画出在时钟作用下的各触发器输出波形。

CP图4-78.时序逻辑电路分析。

电路如图4-8所示:(1)列出方程式、状态表;(2)画出状态图、时序图。

并说明电路的功能。

1C图4-89.试分析图4-9下面时序逻辑电路:(1)写出该电路的驱动方程,状态方程和输出方程;(2)画出Q1Q0的状态转换图;(3)根据状态图分析其功能;1B图4-910.分析如图4-10所示同步时序逻辑电路,具体要求:写出它的激励方程组、状态方程组和输出方程,画出状态图并描述功能。

1Z图4-1011.已知某同步时序逻辑电路如图4-11所示,试:(1)分析电路的状态转移图,并要求给出详细分析过程。

(2)电路逻辑功能是什么,能否自启动?(3)若计数脉冲f CP频率等于700Hz,从Q2端输出时的脉冲频率是多少?CP图4-1112.分析图4-12所示同步时序逻辑电路,写出它的激励方程组、状态方程组,并画出状态转换图。

数字电路与数字电子技术 课后答案第四章

第四章逻辑函数及其符号简化1.列出下述问题的真值表,并写出逻辑表达式:(1)有A、B、C三个输入信号,如果三个输入信号中出现奇数个1时,输出信号F=1,其余情况下,输出F= 0.(2)有A、B、C三个输入信号,当三个输入信号不一致时,输出信号F=1,其余情况下,输出为0.(3)列出输入三变量表决器的真值表.解: ( 1 )F=A B C+A B C+A B C+ABC( 2 )F= (A+B+C) ( A+B+C)( 3 )F=A BC+A B C+AB C+ABC2. 对下列函数指出变量取哪些组值时,F的值为“1”:(1) F= AB+A B (2) F= AB+A C(3) F= (A+B+C) (A+B+C ) (A+B +C) (A+B +C ) 解:(1) AB = 00或AB=11时F=1(2) ABC110或111,或001,或011时F=1 (3) ABC = 100或101或110或111时F=13. 用真值表证明下列等式. (1) A+BC = (A+B) (A+C)(2) A BC+A B C+AB C = BC ABC +AC ABC +AB ABC (3) C A +C B +B A =ABC+A B C (4) AB+BC+AC=(A+B)(B+C)(A+C) (5) ABC+A +B +C =1 证: ( 1 ) ( 2 )( 3 )( 4 ) ( 5 )4. 直接写出下列函数的对偶式F ′及反演式F 的函数表达式. (1) F= [A B (C+D)][B C D +B (C +D)] (2) F= A BC + (A +B C ) (A+C) (3) F= AB+CD +E +D +E C +D +BC (4) F=D +B A •B A +C 解:(1) F`= [A +B+CD]+[(B+C +D )(•B+C D]]F = [A+B +C D ]+[(B +C+D)(•B +C D ]](2) F`= (A+C +B )]AC )C +B (•A [•F = (A +C +B )]C A +)C +B (•A [•(3) F`=)B +A (•C +D •)B +A (F =)B +A (•C +D •)B +A (5. 若已知x+y = x+z ,问y = z 吗?为什么? 解:y 不一定等于z,因为若x=1时,若y=0,z=1,或y=1,z=0,则x+y = x+z = 1,逻辑或的特点,有一个为1则为1。

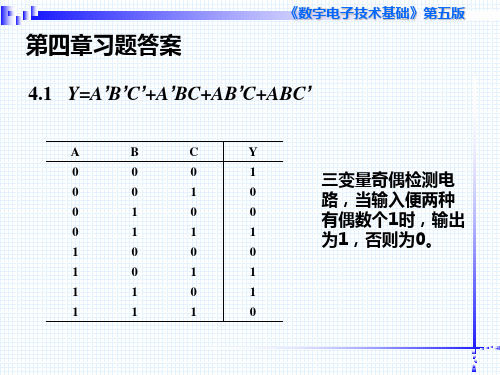

数字电子技术第四章习题答案

第四章习题答案

4.1 Y=A’B’C’+A’BC+AB’C+ABC’

A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 Y 1 0 0 1 0 1 1 0

三变量奇偶检测电 路,当输入便两种 有偶数个1 有偶数个1时,输出 否则为0 为1,否则为0。

《数字电子技术基础》第五版 数字电子技术基础》

4.12 用3线-8线译码器实现多输出逻辑函数。 线译码器实现多输出逻辑函数。 线 线译码器实现多输出逻辑函数

' ' Y1 = AC = AB ' C + ABC = m5 + m7 = ( m5 m7 )' = (Y5'Y7' )' ' ' ' ' Y2 = A ' B ' C + AB ' C '+ BC = ( m1m3 m4 m7 )' = (Y1'Y3'Y4'Y7' )' ' ' ' Y3 = B ' C '+ ABC ' = ( m0 m4 m6 )' = (Y0'Y4'Y6' )'

Y’2(2) 1 1 0 1 1

Y’2(1) 1 1 1 0 1

D2 1 1 1 1 0

设片1优先级别 设片 优先级别 最低, 优先 最低,片4优先 级别最高。 级别最高。 输出5位数为原 输出 位数为原 码D4D3D2D1D0

《数字电子技术基础》第五版 数字电子技术基础》

数字电子技术第4章组合逻辑电路习题解答

001

0 10

0 11

1 0 0

1 0 1

1 1 0

1 1 1

0

1

1

0

1

0

0

1

(2)由真值表得到逻辑函数表达式为:

(3)画出逻辑电路图

4.10、试设计一个8421BCD码的检码电路。要求当输入量DCBA≤4,或≥8时,电路输出L为高电平,否则为低电平。用与非门设计该电路。

解:(1)根据题意列出真值表为:

100

101

110

111

0

1

1

1

1

1

1

0

(2)

电路逻辑功能为:“判输入ABC是否相同”电路。

4.7已知某组合电路的输入A、B、C和输出F的波形如下图所示,试写出F的最简与或表达式。

习题4.7图

解:(1)根据波形图得到真值表:

ABC

F

000

001

010

011

100

101

110

111

1

0

0

1

0

0

1

0

(2)由真值表得到逻辑表达式为

(1)试分析电路,说明决议通过的情况有几种。

(2)分析A、B、C、D四个人中,谁的权利最大。

习题4.4图

解:(1)

(2)

ABCD

L

ABCD

L

0000

0001

0010

0011

0100

0101

0110

0111

0

0

0

1

0

0

1

1

1000

1001

1010

1011

数电第四章练习册答案

数电第四章练习册答案问题1:解释什么是逻辑门,并给出常见的逻辑门类型。

答案:逻辑门是数字电路中的基本组件,用于实现基本的逻辑运算,如与(AND)、或(OR)、非(NOT)、异或(XOR)等。

常见的逻辑门类型包括:与门(AND)、或门(OR)、非门(NOT)、异或门(XOR)、与非门(NAND)、或非门(NOR)、同或门(XNOR)等。

问题2:描述二进制数和十进制数之间的转换方法。

答案:二进制数转换为十进制数的方法是将每个二进制位的值乘以其权重(2的幂),然后将结果相加。

十进制数转换为二进制数的方法是将十进制数除以2,取余数,然后继续除以2,直到结果为0。

问题3:什么是布尔代数?答案:布尔代数是一种数学系统,用于描述和操作逻辑运算。

它是数字电路设计中的基础,由布尔代数的基本原理和规则组成,如布尔代数的五个基本规则:交换律、结合律、分配律、德摩根定律和幂等律。

问题4:解释什么是组合逻辑电路,并给出一个例子。

答案:组合逻辑电路是一种数字电路,其输出仅依赖于当前的输入值,不包含存储元件。

一个常见的组合逻辑电路例子是加法器,它接受两个二进制数作为输入,并产生它们的和以及进位。

问题5:什么是时序逻辑电路?答案:时序逻辑电路是一种包含存储元件(如触发器)的数字电路,其输出不仅依赖于当前的输入值,还依赖于电路的历史状态。

一个常见的时序逻辑电路例子是寄存器,它可以存储一定数量的位,并在时钟信号的控制下更新其内容。

问题6:解释什么是触发器,并说明其功能。

答案:触发器是一种具有两个稳定状态的存储元件,它可以存储一位二进制信息。

触发器的功能是存储和转换信息,它们是构成更复杂时序逻辑电路的基本组件。

结束语:通过本章的练习,希望同学们能够加深对数字电子技术的理解,掌握逻辑门、二进制与十进制转换、布尔代数、组合逻辑电路和时序逻辑电路等基本概念和原理。

这些知识是数字电子技术领域的基石,对于未来深入学习和应用数字电路至关重要。

希望同学们能够不断练习,提高自己的理解和应用能力。

数字电子技术第4章习题解答

第4章习题解答4-1 写出图T4-1电路的输出函数式,证明a 、b 有相同的逻辑功能。

B(a)A(b)BA 图T4-1 习题4-1的图解4-1 Y 1= A B ' +A ' B ' ; Y 2=( A+B)(A ' +B ' )= AB ' +A ' B ' =Y 14-2 试写出图T4-2所示逻辑电路的输出函数式并化简,指出电路的逻辑功能。

A BMBA图T4-2习题4-2的图图T4-3习题4-3的图解4-2 由图T4-2写电路的输出函数式并化简得AB B A B A AB Y +''='''''=))()(( (JT4-2)由JT4-2式可知,电路实现的是二变量同或功能。

4-3 图T4-3是一个选通电路。

M 为控制信号,通过M 电平的高低来选择让A 还是让B 从输出端送出。

试写逻辑电路的输出函数式并化简,分析电路能否实现上述要求。

解4-3 由图T4-3写电路的输出函数式并化简得M B AM M B M A Y '+='''=)((( (JT4-3)由JT4-3式可知,电路能够实现选通要求,当M=1时,Y=A ;当M=0时,Y=B 。

4-4.用与非门设计一个四人表决逻辑电路,结果按“少数服从多数”的原则决定。

解4-4(1)列真值表设四个人的意见为变量A 、B 、C 、D ,表决结果为函数Y 。

按正逻辑给变量赋值:同意为“1”,不同意为“0”;提案通过为“1”,没通过为“0”,所列真值表如表JT4-4所示。

表JT4-4输 入输 出A B C D 0 0 0 0 0 00 0 0 1 0 1 0 1 0 10 0 0 1 1 0 1 1 0 0 0 1 1 01 1 Y000000001 0 1 0 1 0 1 01 1 1 1 1 11 1 0 0 0 1 1 0 1 1 0 00 1 1 0 1 100000000输 入输 出A B C D Y(2)写输出逻辑函数式由表JT4-4可写输出逻辑函数式ABCD D ABC D C AB CD B A BCD A Y +'+'+'+'= (JT4-4a)(3)化简填卡诺图,如图JT 4-4(a)所示合并最小项,得最简与—或式BCD ACD ABD ABC Y +++= (JT4-4b)(4)画逻辑电路图将式JT4-4(b)转换成与非—与非式)()()()(('''''=D BC ACD ABD ABC Y (JT4-4c)按式JT4-4(c)用与非门画逻辑电路图,如图JT4-4(b)所示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第四章 集 成 触 发 器 4.1

R d S d Q Q

4.2 (1

CP=1时如下表)(2) 特性方程Q n+1=D

(3)该电路为锁存器(时钟型D 触发器)。

CP=0时,不接收D 的数据;CP=1时,把数据锁存。

(但该电路有空翻)

4.3 (1)、C=0时该电路属于组合电路;C=1时是时序电路。

(2)、C=0时Q=A B +; C=1时Q n+1=B Q BQ n n += (3)、输出Q 的波形如下图。

A B C Q

4.4

CP D Q 1Q 2

图4.5

4.5

D

Q Q

CP

T

4.6 Q 1n 1+=1 Q 2n 1+=Q 2n Q n 13+=Q n

3 Q Q 4n 14n +=

Q1CP Q2Q3

Q4

4.7 1、CP 作用下的输出Q 1 Q 2和Z 的波形如下图; 2、Z 对CP 三分频。

D

Q Q

CP

Q1

D

Q Q

Q2

Z

Rd CP Q1Q2

Z

1

4.8由Q

D J Q KQ J Q KQ n 1

n n n n +==+=⋅得D 触发器转换为J-K 触发器的逻

辑图如下面的左图;而将J-K 触发器转换为D 触发器的逻辑图如下面的右图

CP

D Q Q

J

K

Q Q

D

Q Q

J K

CP

4.9

CP B C

A

4.10

CP X Q1Q2Z

4.11 1、555定时器构成多谐振荡器

2、

u c, u o 1, u o 2的波形

u c u o 1u o 2

t t t 1.67V

3.33V

3、u o 1的频率f 1=

1

074501316..

H z ⨯⨯≈ u o 2的频率f 2=158H z

4、如果在555定时器的第5脚接入4V 的电压源,则u o 1的频率变为

1

113001071501232....

H z ⨯⨯+⨯⨯≈

4.12 图(a)是由555定时器构成的单稳态触发电路。

1、工作原理(略);

2、暂稳态维持时间t w =1.1RC=10ms(C 改为1μF);

3、u c 和u o 的波形如下图:

u o

u c

t t t

u i (ms)

(ms)(ms)5 10 25 30 45 50

3.33V

4、若u i 的低电平维持时间为15m s ,要求暂稳态维持时间t w 不变,可加入微分电路

4.13由555定时器构成的施密特触发器如图(a)所示

1、电路的电压传输特性曲线如左下图;

2、u o的波形如右下图;

3、为使电路能识别出u i中的第二个尖峰,应降低555定时器5脚的电压至3V左右。

4、在555定时器的7脚能得到与3脚一样的信号,只需在7脚与电源之间接一电阻。

4.14延迟时间t d=1.1×1×10=11s

扬声器发出声音的频率f=

1

0715001

10 ..

kH

z ⨯⨯

≈。