试卷答案3

心血管内科学考试试卷及答案3

一、病例分析(1小题,共15.0分)(15分)[1]男性患者,67岁。

反复活动后胸痛5年,再发并加重4小时。

既往高血压病史10年,最高血压185/105mmHg。

PE:BP 145/85mmHg,心界正常,S减弱,心电图如图所示。

请问:(1)最可能的诊断是什么?(2)为明确诊断需进一步做哪些检查?(3)治疗措施有哪些?二、单选题(62小题,共62.0分)(1分)[1]女,21岁,突然发作持续性心悸1小时,既往有支气管哮喘史。

心电图:心率180次/分,节律规则,QRS波群<0.11秒,未见明确P波。

经采用刺激迷走神经方法无效。

目前应首先选用哪种方法治疗 ( )A、静脉注射维拉帕米B、静脉注射奎尼丁C、肌内注射新斯的明D、静脉注射西地兰E、同步直流电复律(1分)[2]心房扑动时,心电图上锯齿样扑动波的频率为( )A、75~150次/分B、150~200次/分C、250~350次/分D、200~250次/分E、350~600次/分(1分)[3]治疗成人室性心律失常时,利多卡因静滴的速度为( )A、1~4mg/minB、0.1~0.4mg/(kg.min)C、0.1~0.4mg/minD、1~4mg/(kg.min)E、10~40mg/min(1分)[4]下列哪种心律失常容易发生阿斯发作( )A、窦性心动过缓B、窦房传导阻滞C、窦性停搏D、右束支传导阻滞E、左束支传导阻滞(1分)[5]一患者因大量呕吐、腹泻突然晕厥、抽搐、颈动脉搏动消失。

抢救首选方法为( )A、静脉注射肾上腺素B、静脉注射利多卡因C、急速叩击心脏D、胸外心脏按压E、人工呼吸(1分)[6]关于房性早搏的心电图特点,下列哪项不正确( )A、有提早出现的P’波B、P-R间期≥0.12秒C、P’波与窦性P波形态常不同D、代偿间歇不完全E、多数P’波后的QRS波群宽大畸形(1分)[7]男,65岁,诊断为扩张型心肌病,住院期间,患者突然出现意识丧失,四肢抽搐,急描记心电图,如图所示,从图中可以看出,患者发作( )A、室性心动过速B、室性纤颤C、室性扑动D、尖端扭转型室性心动过速E、以上均不正确(1分)[8]男,67岁,突起持续性胸骨后痛6小时,含服硝酸甘油无效。

2023年单招考试英语试卷及答案 (3)

2023年单独招生统一考试英语试卷(满分120分,考试时间90分钟)一、选择题:(本题共20小题,每小题3分,共60分)1.Troubled by a terrible headache,Catherine wondered how she could __________herself of the bad situation.A.throwB.ridC.moveD.remove2.more and more forests destroyed,many animals are facing the danger of dying out.()A.BecauseB.AsC.WithD.Since3.---What a nice jacket!It looks good on me!---Don’t you think it is too tight___the shoulders?A.beyondB.betweenC.fromD.across4.The more words you are familiar with,the less you are aware of readingwords and_______you are aware of content and meaning.A.moreB.lessC.The moreD.the less5.Even in winter days,Jane likes to have the window()A、to openB、opening isC、opensD、open6.—There are so many grammar difficulties in this book,aren’t there?—Yes._________what the book is talking about,you’d better refer to English teachers.A.KnownB.KnowingC.To knowD.Know7.—It's a long time________we last met at the airport.—Yes,and it will be another week________we can meet again.A、before;sinceB.when;beforeC.since,whenD.since;before8.You'd better.__the word in a dictionary.A、look upB、look forC、look afterD、look out9..Anna eats at home every day.She.__goes to a restaurant.A、seldomB、probablyC、usuallyD、already10.l was flowing into the river when a pipeline__A、damagedB、burstC、disturbedD、met11.-Excuse me,I am looking for a copy machine.()Go upstairs and it's in the room______your left.A、at isB、fromC、in andD、on12.I told Mary that you'd be late_____she wouldn't start worrying.()A、so thatB、becauseC、even ifD、unless13.We thought there must be something_________because we hadn't heard from you for quite a long time.()A、rightB、wrongC、good isD、bad14.She'd lived in London and Manchester,but she liked______and moved to Cambridge.A.bothB.neitherC.noneD.either15.Grandma pointed to the hospital and said,"That's______I was born."A.whenB.howC.whyD.where16.Would you please tell me the price of___handbag you are carrying?If it’s reasonable,I plan to buy______,too.()A、/,itB、the,oneC、a,itD、/,one17.---1am going to take you to Shanghai Disneyland this summer holiday, Bob.()---Is it a____?Don’t disappoint me,I hope.A、requestB、solutionC、replyD、Promise18.___.the course she preferred a bit hard for her,she decided to move to()a lower level.A、FindingB、FoundC、To findD、Find is19.Before you select a book,you'd better the first few pages to() know whether it is it too easy or too difficult for you.A、look outB、look upC、look forD、look through20、______makes Mr.Mark ley anxious is.fewer and fewer customers step into his store.And shopping online is getting increasingly popular in recent years.()A、What,whyB、What,thatC、That,thatD、It,what二、填空题:(共30分)There was once a lonely girl who wanted love very much.One day__1____she was walking in the forests,she found two__2____birds.She took them ___3___and put them in a small cage.She was___4___to have two friends. She looked after them with love and the birds grew___5____.One day the girl___6__to leave the door of the cage open.The larger and stronger of the__7___flew out of the cage.The girl was___8___that it would fly away.She__9___it quickly.She felt glad that she caught the bird before it could__10___away.Suddenly she couldn’t hear a__11____ from the bird When she opened her hand,the bird was___12____dear Her love killed the bird!Then she noticed the other bird jumping up and down__13____the cage.She could feel its great need for___14_____.It wanted to fly into the clear,blue sky.So she lifted it from the cage and let it fly away____15____.The bird circled once,twice and three times.The girl___16__as the bird flew.She didn’t care about___17___the bird any more.She wanted it to be happy.Suddenly the bird flew___18____and landed softly on her shoulder.It sang the sweetest song she had ever ___19___.The fastest way to lose love is to hold on it too hard and the best way to keep love is to give it___20____.()1.A、while B、during C、before D、after()2.A、dead B、dying C、living D、alive()3.A、on B、out C、up D、home()4.A、worried B、quick C、happy D、sad()5.A、heavier B、strong C、bigger D、weak()6.A、happened B、started C、stopped D、wanted()7.A、two B、three C、four D、five()8.A、surprised B、shocked C、afraid D、wondering ()9.A、held B、caught C、put D、killed()10.A、walk B、jump C、run D、fly()11.A、sound B、voice C、word D、cry()12.A、still B、already C、yet D、just ()13.A、outside B、inside C、against D、across()14.A、freedom B、water C、food D、air()15.A、sad B、happy C、sadly D、happily()16.A、cried B、watched C、ran D、walked()17.A、losing B、catching C、keeping D、feeding ()18.A、farther B、closer C、slower D、quicker ()19.A、sung B、written C、heard D、learned ()20.A、care B、cage C、wings D、help三、阅读理解:(共20分)Baths and bothing have long been considered of medical importance to man. In Greece there are the ruins(废墟)of a water system(系统)for baths built over3,000years ago.The Romans had warm public baths.In some baths, as many3,000persons could bathe at the same time.Treating disease by taking bathing has been popular for centuries. Modern medical bathing first became popular in Europe and by the late1700’s has also become popular in the United States.For many years frequent(经常的)bathing was believed to be bad for one’s health.Ordinary bathing just to keep clean was avoided(避免),and perfume was often used to cover up body smells!By the1700’s doctors began to say that soap and water were good for health.They believed that it was good for people to be clean.Slowly, people began to bathe more frequently.During the Victorian Age of the late19th century,taking a bath on Saturday night became common.In the United States ordinary bathing was slow to become popular. During the18th and early19th centuries,many Americans were know as“The Great Unwashed!”In one American city,for example,a person was only allowed to take a bathe every thirty days!That was a law!Frequency of bathing today is partly a matter of habit.People know that bathing for cleanliness is important to health,Doctors know that dirty bodies increase the chance of diseases.As a result,in the United States,people generally bathe often.Some people bath once a day at least. They consider a daily bath essential(=necessary)to good health.1.A water system for baths was built by_____over3,000years ago.A.the RomansB.the GreeksC.the AmericansD.the Europeans2.Dirty bodies can_____.A.ruin one’s businessB.cause diseaseC.drive customers awayD.cause good health3.In the18th century doctors believed that being cleanwas_____.A.unimportantB.good for healthC.harmful D.important4.The underlined word perfume probably means______.A.a sweet smelling substanceB.good healthC.a strange smelling substancerge wealth5.Which_____of the following gives the main idea of the passage?A.Everybody in America takes a daily bath.B.A bath a day keeps the doctor away.C.Taking baths has become popular in the world.D.Bathing has become easier and cheaper.四、书面表达:(满分10分)请以"绝不放弃"为话题,写一篇不少于50词的文章,立意自定,文体自选,标题自拟,所写内容必须在话题范围之内.要求选好角度,确定立意,明确文体,自拟标题;不要套作,不得抄袭.参考答案:一、选择题:1-5:BCDCD6-10:CDAAB11-15:DABBD16-20:BDADB部分选择题答案解析:8、答案:A解析:考查动词短语辨析。

计划生育练习试卷3(题后含答案及解析)

计划生育练习试卷3(题后含答案及解析) 题型有:1. X型题 2. A1型题1.输卵管结扎术的适应症有A.已婚育龄期妇女,自愿接受且无禁忌B.要求避孕者C.有严重的心脏病不宜生育者D.哺乳期妊娠者E.第2次剖宫产术后正确答案:A,C 涉及知识点:计划生育2.取出皮下埋植剂的指征为A.阴道点滴出血B.雌激素禁忌者C.反复发作异常剧烈头痛D.急性视觉失调E.长期卧床者正确答案:C,D,E 涉及知识点:计划生育3.输卵管绝育的并发症有A.感染B.出血、血肿C.脏器损伤D.内分泌紊乱E.再孕正确答案:A,B,C,E 涉及知识点:计划生育4.复方短效口服避孕药的禁忌症为A.慢性肝炎B.脑血栓患者C.I型糖尿病D.38岁女性有15年吸烟史E.剖宫产术后1年正确答案:A,B,C,D 涉及知识点:计划生育5.放置宫内节育器常见的不良反应为A.月经血量增多B.腰酸下坠C.白带增多D.功能失调性子宫出血E.闭经正确答案:A,B,C 涉及知识点:计划生育6.放置宫内节育器的禁忌症有A.生殖器官炎症B.生殖器官肿瘤C.子宫畸形D.宫颈重度裂伤E.慢性肝炎正确答案:A,B,C,D 涉及知识点:计划生育7.节育的方法有A.宫内节育器B.药物避孕C.避孕套D.人工流产E.药物流产正确答案:A,B,C 涉及知识点:计划生育8.口服避孕药不仅起避孕作用,还有其他益处A.预防血栓形成B.不影响内分泌改变C.降低子宫内膜癌的发生危险D.缓解经前期紧张综合征E.减少贫血、缓解痛经正确答案:C,D,E 涉及知识点:计划生育9.宫内节育器放置的时间可选择在A.月经干净3~7天B.剖宫产后半年C.正常产后3个月以上D.药物流产不全清宫术后立即放置E.剖宫产术中正确答案:A,B,C 涉及知识点:计划生育10.安全套除避孕外,其他的益处有A.降低PID的发生和预防SDT传播B.降低CIN及宫颈癌的发生C.治疗早泄D.改变阴道内酸碱度E.对配偶精液过敏者有保护作用正确答案:A,B,E 涉及知识点:计划生育11.输卵管结扎术的并发症有A.出血B.感染C.肠管损伤D.子宫穿孔E.再通正确答案:A,B,C,E 涉及知识点:计划生育12.手术流产的并发症有A.子宫穿孔B.吸宫不全C.色素沉着D.人流综合征E.体重增加正确答案:A,B,D 涉及知识点:计划生育13.输卵管结扎术最适宜的时间为A.月经干净后14天内B.正常产后56天C.难产后72天D.人工流产后35天E.月经干净后3~7天正确答案:E 涉及知识点:计划生育14.下列哪种情况可考虑放置含孕激素的宫内节育器A.月经量偏少B.生殖道有急、慢性炎症C.有全身性疾病者D.月经量偏多,伴有痛经者E.宫颈内口松弛者正确答案:D 涉及知识点:计划生育15.下列哪种情况宜选用宫内节育器避孕A.子宫脱垂B.月经频发血量多C.宫颈重度裂伤,宫口松D.慢性肝炎E.黏膜下子宫肌瘤正确答案:D 涉及知识点:计划生育16.丈夫突然由外地回家探亲,妻子应使用哪种避孕药:A.探亲避孕药B.短效口服避孕药C.长效避孕药D.长效针E.含孕激素的阴道环正确答案:A 涉及知识点:计划生育17.最适于进行输卵管结扎术的时间:A.正常月经干净后15天B.正常产后10天C.难产后72天D.人流后35天E.月经后3~7天正确答案:E 涉及知识点:计划生育18.放置节育器术后注意事项哪项不妥:A.术后休息B.术后2周禁止性交及盆浴C.术后经期或排便时注意有无节育器脱落D.金属节育器可放置3~5年,塑料节育器可放置1年E.未见尾丝可摄片或B超检查正确答案:D 涉及知识点:计划生育19.女,26岁,孕1产1。

操作系统试卷3及答案

操作系统试卷3及答案一、单项选择题(本大题共15小题,每小题1分,共15分)在每小题列出的四个选项中只有一个选项是符合题目要求的,请将正确选项前的字母填在题中的括号内。

1通道又被称为I/O处理器,它用于实现()之间的信息传输。

A、主存与外设B、CPU与外设C、外设与外设D、CPU与辅存2、磁盘是可共享的设备,每一时刻( )进程与它交换信息。

A、允许有两个B、可以有任意多个C、最多有1个D、至少有1个3、在存储管理的各方案中,可扩充主存容量的方案是( )存储管理。

A、固定分区B、可变分区C、连续D、页式虚拟4、分时系统中进程调度算法通常采用( )。

A、响应比高者优先B、时间片轮转法C、先来先服务D、短作业优先5、设有三个进程共享一个资源,如果每次只允许一个进程使用该资源,则用PV操作管理时信号量S的可能取值是( )。

A、1,0,-1,-2B、2,0,-1,-2C、1,0,-1D、3,2,1,06、设有三个作业J1,J2,J3,它们的到达时间和执行时间如下表:作业名到达时间执行时间J1 8:00 2小时J2 8:45 1小时J3 9:30 0.25小时它们在一台处理器上按单道运行,若采用短作业优先调度算法,则此三作业的执行次序是( )A、J3,J2,J1B、J1,J2,J3C、J1,J3,J2D、J3,J1,J27、计算机系统中设置的访管指令,( )执行。

A、只能在目态B、只能在管态C、既可在目态又可在管态D、在目态和管态下都不能8、一个多道批处理系统,提高了计算机系统的资源利用率,同时( )。

A、减少各个作业的执行时间B、增加了单位时间内作业的吞吐量C、减少单位时间内作业的吞吐量D、减少了部份作业的执行时间9、操作系统实现文件管理后,允许用户对记录式文件进行存取的最小单位是( )。

A、文件B、记录C、数据项D、字符串10、文件系统采用多级目录结构可以( )。

A、节省存储空间B、解决命名冲突C、缩短文件传送时间D、减少系统开销11、在页式虚拟存储管理中,为实现地址变换,应建立()。

c语言试卷和答案3

程序2 2, 4, 6, 8, 10

(5) 08是正确的整型常量。

(6) 设变量定义为 char s[ ]= “hello”则数组s中有6个元素。

(7) 若x是单精度实型变量,表达式(x=10/4)的值是2.5。

(8) 若变量已正确定义,表达式x=y=1符合C语言语法。

#include <stdio.h>

void sort( (26) )

{ int i, k, m, t;

for(i=0; i<n-1; i++) {

k=i;

for (m=i+1; m<n; m++)

if ( (27) ) k=m;

#define M(x,y) x/y

printf( “%d”, M(10,2+3));

A)2 B)2.0 C)5 D)8

(15)已知字符’c’的ASCII码为99,语句printf(“%d,%c”, ‘c’, ‘c’+1);的输出为 。

int f (int n)

{ static int k, s;

n- -;

for(k=n; k>0; k- -)

s+=k;

return s;

}

void main()

{ int k;

struct line

{ int num;

struct line *next;

};

void main()

{ int k;

struct line *p, *head;

head=NULL;

for(k=10; k>0; k--) {

婚姻家庭继承法试卷3及答案

婚姻家庭继承法试卷3考试时间为120分钟一、单项选择题(每题1分,共10分)【在下列备选答案中,选出1个正确答案】1.小张和其父母收养的养妹从小一起长大,产生了爱慕之情,他们()。

A.可以结婚 B.如不是三代以内的旁系血亲,可以结婚C.不能结婚 D.征得其父母同意后方可结婚2.甲(男,22周岁)为达到与乙(女,19周岁)结婚的目的,故意隐瞒乙的真实年龄办理了结婚登记。

两年后,因双方经常吵架,乙以办理结婚登记时未达到法定婚龄为由向法院起诉,请求宣告婚姻无效。

法院应如何处理?()A.以办理结婚登记时未达到法定婚龄为由宣告婚姻无效B.对乙的请求不予支持C.宣告婚姻无效,确认为非法同居关系,并予以解除D.认定为可撤销婚姻,乙可行使撤销权3.甲男与乙女通过网聊恋爱,后乙提出分手遭甲威胁,乙无奈遂与甲办理了结婚登记。

婚后乙得知,甲与己有三代以内旁系血亲关系,因甲被送养而不知。

乙向法院起诉离婚。

下列哪一说法是正确的?()A.法院应判决撤销该婚姻B.法院应判决宣告该婚姻无效C.对该案的审理应当进行调解4.下列财产中,属于夫妻共同财产的是()。

A.夫妻一方的生活用品 B.经过若干年以后的夫妻一方婚前财产C.夫妻一方的婚前财产 D.夫妻关系存续期间的知识产权收益5.甲乙是夫妻,甲在婚前发表小说《昨天》,婚后获得稿费。

乙在婚姻存续期间发表了小说《今天》,离婚后获得稿费。

甲在婚姻关系存续期间创作小说《明天》,离婚后发表并获得稿费。

下列哪一选项是正确的?()A.《昨天》的稿费属于甲婚前个人财产B.《今天》的稿费属于夫妻共同财产C.《明天》的稿费属于夫妻共同财产D.《昨天》、《今天》和《明天》的稿费都属于夫妻共同财产6.未形成抚养关系的继父母与继子女之间属于()。

A.自然直系血亲关系 B.拟制直系血亲关系C.直系姻亲关系 D.拟制旁系血亲关系7.47周岁的甲在妻子逝世后与年方5周岁的儿子相依为命,甲想收养一个女儿。

下列何人可被其依法收养?()A.福利院抚养的10周岁残疾女童B.福利院抚养的10周岁的孤女C.福利院抚养的查找不到父母的6周岁女童D.生父母有特殊困难无力抚养子女的6周岁女童8.甲乙夫妻双方协议离婚,乙委托丙去婚姻登记管理机关代理办理离婚登记手续。

质量改进常用的七种工具练习试卷3(题后含答案及解析)

质量改进常用的七种工具练习试卷3(题后含答案及解析)题型有:1. 单项选择题 2. 多项选择题 3. 综合分析题单项选择题每题1分。

每题的备选项中,只有1个符合题意。

1.数据的平均值与最大值和最小值的中间值相同或接近,平均值附近的数据的频数最多,频数在中间值向两边缓慢下降,以平均值左右对称,这是()。

A.普通型直方图B.标准型直方图C.平顶型直方图D.锯齿型直方图正确答案:B 涉及知识点:质量改进常用的七种工具2.平均值远左离(右离)直方图的中间值,频数自左至右减少(增加),直方图不对称。

这种直方图是()直方图。

A.偏峰型B.陡壁型C.双峰型D.孤岛型正确答案:B解析:偏峰型直方图的特点是:数据的平均值位于中间值的左侧(或右侧),从左至右(或从右至左),数据分布的频数增加后突然减少,形状不对称;双峰型直方图的特点是:靠近直方图中间值的频数较少,两侧各有一个“峰”;孤岛型直方图的特点是:在标准型的直方图的一侧有一个“小岛”。

知识模块:质量改进常用的七种工具3.收集数据时,方法要简单,数据处理要方便。

通常,可用()来实现这一目的。

A.控制图B.散布图C.直方图D.调查表正确答案:D解析:质量管理要用数据说话,因此需要收集数据。

收集数据的根本点是数据要清楚地反映现状。

实际收集数据时,方法要简单,数据处理要方便。

通常,可用调查表来实现这一目的。

知识模块:质量改进常用的七种工具4.工序分布调查是在()的同时进行数据处理。

A.分析数据B.收集数据C.测量数据D.运用数据正确答案:B解析:在工序分布调查表上用检查标记或简单的符号记录数据,在收集数据的同时进行数据处理。

知识模块:质量改进常用的七种工具5.工序分布调查表相当于简化了的()。

A.控制图B.因果图C.直方图D.排列图正确答案:C解析:工序分布调查表相当于简化了的直方图,它能在收集数据的同时进行数据处理。

知识模块:质量改进常用的七种工具6.某厂对其产品检验中所出现的缺陷按不合格分类进行统计,进而清楚地表明了哪种不合格经常发生,这里该厂采用的调查表方式是()。

2022年9月华医考试卷和答案(3)

2022年9月华医考试卷和答案(3)共2种题型,共170题一、多选题(共100题)1.体动脉压持续升高可能由下列哪些因素引起()()A:心钠素分泌过多B:醛固酮分泌过多C:肾素分泌过多D:左心室肥大E:慢性呼吸衰竭引起的低氧【答案】:BC2.恶性肿瘤康复治疗的主要目的是()A:增进食欲B:延长存活时间C:消除心理障碍D:改善功能E:提高生活质量【答案】:BCDE3.慢性肾炎患者的饮食应为()A:高蛋白饮食B:低蛋白饮食C:高磷饮食D:低磷饮食E:优质蛋白饮食【答案】:BDE4.非语言沟通的形式包括()A:体语B:触摸C:空间效应D:类语言E:物理和环境因素【答案】:ABCDE5.特殊治疗膳食包括()A:糖尿病膳食B:低脂肪膳食C:溃疡病膳食D:血液病膳食E:高血压膳食【答案】:ACD6.流行病学研究的基本含义包括()A:从群体的角度研究该病和健康状况B:研究各种疾病,不限于传染病C:主要研究临床个体的诊断和治疗D:从频率和分布出发研究疾病E:研究预防和控制疾病的对策与策略【答案】:ABDE7.下述有关膳食营养的叙述,哪些是正确的()A:膳食中钙的最好来源是奶类B:维生素A的良好食物来源是动物肝脏C:膳食中维生素B1的主要来源是粮谷类D:膳食中维生素C的主要来源是蔬菜、水果E:膳食中蛋白质含量最高的食物是豆类【答案】:ABCDE8.介水传染病有以下哪些流行特点()A:有机物污染B:短期内出现暴发流行C:饮用同一水源D:表现的症状各有所异E:控制污染源,疾病流行即得到控制【答案】:ABCE9.病人因咳嗽无力而造成排痰不畅,易导致()A:心力衰竭B:肺水肿C:肺不张D:呼吸困难E:窒息【答案】:CDE10.以下哪些项目是循证医学的应用范围()()A:医疗管理B:制定卫生政策C:卫生技术评价D:指导临床实践E:药物研究与应用【答案】:ABCDE11.肾脏的主要功能有()A:排泄体内的代谢废物B:调节酸碱平衡C:调节机体内的水和渗透压D:调节电解质浓度E:调节血糖【答案】:ABC12.核医学显像诊断的特点是()()A:放射性核素显像诊断是一种功能性显像,对某些疾病可早期发现B:核素显像是较好的特异性显像C:能进行连续动态和静态显像诊断D:安全、简便、非创伤性的诊断方法E:显像图像比X-CT更清晰【答案】:ABCD13.高压氧对循环系统的影响包括()A:心排血量减少B:心率减慢C:血流减慢D:心脏负荷加重E:血循环时间缩短【答案】:ABC14.自然疫源性疾病的特点有()()A:自然界长期有病原体存在B:节肢动物为传播媒介C:发病有地方性D:发病有季节性E:局部地区突发烈性传染病【答案】:ABCD15.属于神经毒类毒蛇的是()A:竹叶青蛇B:银环蛇C:眼镜蛇D:五步蛇E:金环蛇【答案】:BE16.院前急救原则包括()A:先复苏后固定B:先止血后包扎C:先救治后运送D:先重伤后轻伤E:搬运与医护的一致性【答案】:ABCDE17.属于高度危险物品的有()A:手术器械B:心导管C:听诊器D:体温表E:压舌板【答案】:AB18.医务人员洗手的指征包括()A:接触病人前后B:进行无菌技术操作前后C:带口罩和穿、脱隔离衣前后D:接触血液、体液和被污染的物品前后E:脱手套后【答案】:ABCDE19.病人角色模式的主要类型有()A:病人角色忽略B:病人角色牵强C:病人角色强化D:病人角色淡化E:病人角色隐瞒【答案】:BCDE20.获得性免疫缺陷综合征艾滋病传播的途径包括()A:血液传播B:消化道传播C:性接触传播D:体液传播E:母婴传播【答案】:ACDE21.病毒灭活的概念是()()A:失去感染性B:保留抗原性C:保留血凝特性D:保留细胞融合特性E:保留遗传特性【答案】:ABC22.护理的任务是()A:减轻痛苦B:治疗疾病C:恢复健康D:促进健康E:维持健康【答案】:ACDE23.弛张热常见于下列哪些病人()A:伤寒B:败血症C:疟疾D:化脓性疾病E:风湿热【答案】:BDE24.用已知A型血与待测者血做交叉配血,若主反应凝聚,次反应不凝聚,待测者血型可能为()()A:AB型B:O型C:A1型D:B型E:A2型【答案】:BE25.躯干骨包括()()A:髋骨B:锁骨C:肋骨D:胸骨E:椎骨【答案】:CDE26.大咯血窒息抢救措施应包括()A:仰卧头低脚高位B:清除口腔血凝块和血液C:防止舌后坠D:低浓度持续给氧E:适当用呼吸中枢兴奋剂【答案】:BCE27.注射前需检查有无回血的操作是()A:皮内注射B:皮下注射C:肌内注射D:静脉注射E:动脉穿刺【答案】:BCDE28.常见的误诊、漏诊的原因包括下面哪几种()()A:病史资料不完整、不确切B:观察不细致或检验结果误差C:先入为主、主观臆断D:医学知识不足、缺乏临床经验E:疾病的临床表现不同【答案】:ABCD29.高压氧治疗气性坏疽的作用是()A:抑制梭状芽孢杆菌的生长B:抑制α-外毒素的产生C:阻止组织坏死,促进伤口愈合D:增强抗毒血清的作用E:增强抗生素的效力【答案】:ABC30.肺癌的主要转移途径不包括()A:直接扩散B:淋巴转移C:血行转移D:种植转移E:局部浸润【答案】:DE31.下述腺体中,哪些是消化腺()()A:腮腺B:甲状腺C:前列腺D:下颌下腺E:胸腺【答案】:AD32.高钾血症可见于()A:急性肾衰竭B:慢性肾衰竭C:Addison病D:糖尿病E:经胃肠摄钾过多【答案】:ABCD33.病人,女,34岁,风湿性心脏病史16年,因感冒、发热住院。

江西公务员考试行测类比推理专项强化真题试卷3(题后含答案及解析)

江西公务员考试行测类比推理专项强化真题试卷3(题后含答案及解析)题型有:1.1.水:湖泊A.富裕:休闲B.山:水C.营养:健康D.蓝图:海洋正确答案:C解析:湖泊里必然有水,健康必然包括营养。

2.屏幕:彩屏A.时间:纳米B.何首乌:中药材C.酷暑:空洞D.青年:愤青正确答案:D解析:彩屏是屏幕的一种,愤青是青年中的一类人。

3.历史:明智A.新闻:广播B.法律:约束C.制度:学问D.政策;援藏正确答案:B解析:历史使人明智,法律使人的行为受约束。

故选B。

4.摩擦:生热A.冬天:寒流B.海啸:灾难C.高薪:养廉D.位高:权重正确答案:B解析:摩擦是生热的原因,海啸是灾难的原因。

5.英国:伦敦A.美国:加州B.中国:北京C.东京:日本D.葡萄牙:西班牙正确答案:B解析:题干中英国的首都是伦敦。

A项美国的首都是华盛顿;B项中国的首都是北京;C项顺序颠倒;D项葡萄牙和西班牙是两个国家。

所以选B。

6.义务警员:警察A.小偷:模范B.狮子:小羊C.肖像:装饰D.死刑:刑罚正确答案:D解析:义务警员是警察的一种;死刑是刑罚的一种。

所以选D。

7.()对于鸵鸟相当于梵蒂冈对于()A.蜂鸟俄罗斯B.麻雀加拿大C.燕子美国D.喜鹊中国正确答案:A解析:蜂鸟是最小的鸟类,鸵鸟是最大的鸟类;梵蒂冈是面积最小的国家,俄罗斯是面积最大的国家。

所以选A。

8.奋斗:成功A.大雪:封山B.学习:理解C.财富:贫困D.考试:成绩正确答案:B解析:奋斗才能成功,但不一定会成功;学习才能理解,但不一定会理解。

9.石油:汽油A.铁矿石:钢铁B.木材:家具C.水泥:房屋D.玻璃:窗户正确答案:A解析:石油中能提炼出汽油,铁矿石中能提炼出钢铁。

10.糖对于( )相当于汞对于( )A.苦毒B.核糖非金属C.咖啡温度计D.碳水化合物水银正确答案:D解析:糖一般指碳水化合物,汞就是水银。

糖可以加到咖啡里,但并不是制作咖啡的原材料,而汞是制作温度计的一种原材料,C项错误。

西安电子科技大学线性代数试卷及参考答案3

α1 = (1,1, 0 ) ,

T

α 2 = ( 0, 0,1)

T

同理,当 λ2 = 0 时,得线性无关的特征向量为 α 3 = ( −1,1, 0 ) .

T

将 α1 , α 2 , α 3 单位化得

η1 =

1 1 T T T (1,1, 0 ) ,η2 = ( 0, 0,1) ,η3 = ( −1,1, 0 ) 2 2

n

0 0

L

0 0

L L

n −1 1− n

L

三、 (12 分)问 a, b 为何值时,线性方程组

⎧ x1 + x2 + 2 x3 + 3 x4 = 1; ⎪ x + 3 x + 6 x + x = 3; ⎪ 1 2 3 4 ⎨ ⎪3 x1 − x2 − ax3 + 15 x4 = 3; ⎪ ⎩ x1 − 5 x2 − 10 x3 + 12 x4 = b.

故 λ1 = −1 为 A 的三重特征值.

⎛ −3 1 −2 ⎞ ⎛ 1 0 1 ⎞ ⎜ ⎟ ⎜ ⎟ 解 (λ1 E − A) X = 0 .因 − E − A = −5 2 −3 → 0 1 1 ⎜ ⎟ ⎜ ⎟ ⎜ 1 0 1 ⎟ ⎜ 0 0 0⎟ ⎝ ⎠ ⎝ ⎠

得其基础解系中只含一个解向量 α = (−1, −1,1) ,从而属于 λ1 = −1 的线性无关的特征向

⎛1 ⎜ 0 初等行 三 解: A ⎯⎯⎯ →⎜ ⎜0 ⎜ ⎜0 ⎝

( −1) 或

2

n −1

( n + 1)! )

1 2 3 −1 1 2 0 2−a 2 0 0 3

1 ⎞ ⎟ 1 ⎟ = A1 4 ⎟ ⎟ b+5 ⎟ ⎠

全国自考(现代汉语)模拟试卷3(题后含答案及解析)

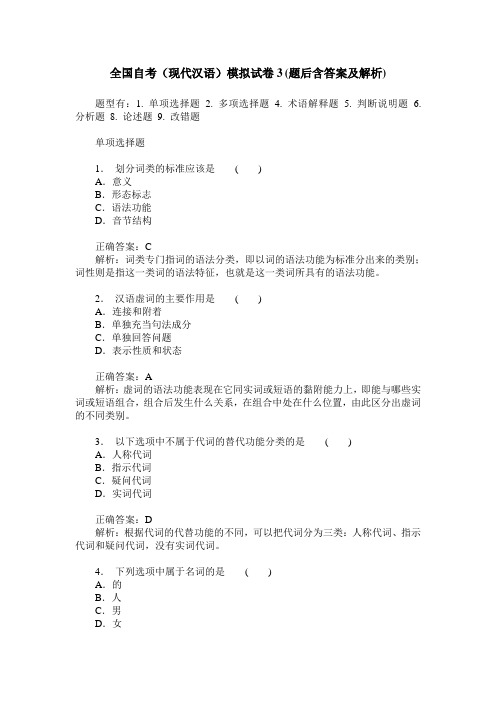

全国自考(现代汉语)模拟试卷3(题后含答案及解析)题型有:1. 单项选择题 2. 多项选择题 4. 术语解释题 5. 判断说明题 6. 分析题8. 论述题9. 改错题单项选择题1.划分词类的标准应该是( )A.意义B.形态标志C.语法功能D.音节结构正确答案:C解析:词类专门指词的语法分类,即以词的语法功能为标准分出来的类别;词性则是指这一类词的语法特征,也就是这一类词所具有的语法功能。

2.汉语虚词的主要作用是( )A.连接和附着B.单独充当句法成分C.单独回答问题D.表示性质和状态正确答案:A解析:虚词的语法功能表现在它同实词或短语的黏附能力上,即能与哪些实词或短语组合,组合后发生什么关系,在组合中处在什么位置,由此区分出虚词的不同类别。

3.以下选项中不属于代词的替代功能分类的是( )A.人称代词B.指示代词C.疑问代词D.实词代词正确答案:D解析:根据代词的代替功能的不同,可以把代词分为三类:人称代词、指示代词和疑问代词,没有实词代词。

4.下列选项中属于名词的是( )A.的B.人C.男D.女正确答案:B解析:名词主要指称人和事物,也可以表示一些抽象的概念、性质、关系等。

其中A项是助词,C、D项是区别词。

5.以下选项中,不属于语气词的是( )A.的B.吗C.啊D.第正确答案:D解析:语气词:常用附着在句末表示某种语气,依据所表语气的不同,可以分为四种:(1)表示陈述语气:的、了、呢、罢了、啊;(2)表示疑问语气:吗、呢、啊;(3)表示祈使语气:吧、了、啊;(4)表示感叹语气:啊。

6.把短语分成名词性短语、动词性短语、形容词性短语等,是根据( )A.短语内部不同的语法层次B.短语内部成分组合时的紧密程度C.短语的语法功能D.短语内部成分的组合方式正确答案:C解析:短语是词和词按照一定方式组合起来的语言单位。

从短语的内部结构关系分析,汉语的基本结构类型有主谓、述宾、述补、偏正和联合五种。

7.“豆腐一碗’和“一碗豆腐”分别是( )A.主谓短语、偏正短语B.偏正短语、偏正短语C.述补短语、偏正短语D.偏正短语、述补短语正确答案:A解析:主谓短语:由主语和谓语两个成分组成。

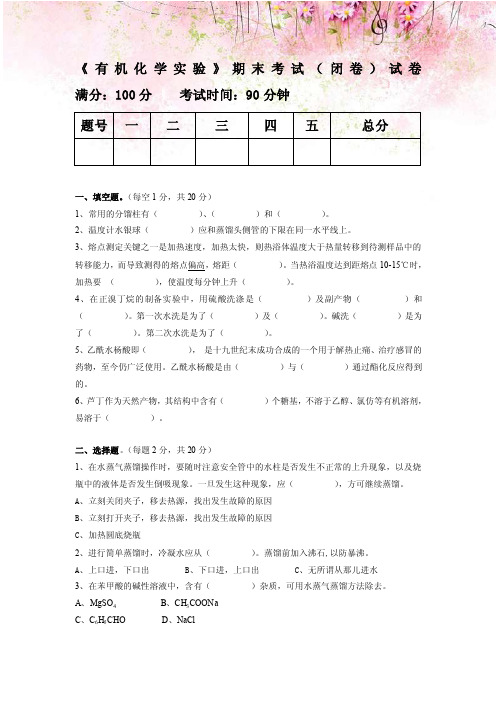

《有机化学实验》期末考试(闭卷)试卷及答案3

《有机化学实验》期末考试(闭卷)试卷满分:100分考试时间:90分钟题号一二三四五总分一、填空题。

(每空1分,共20分)1、常用的分馏柱有()、()和()。

2、温度计水银球()应和蒸馏头侧管的下限在同一水平线上。

3、熔点测定关键之一是加热速度,加热太快,则热浴体温度大于热量转移到待测样品中的转移能力,而导致测得的熔点偏高,熔距()。

当热浴温度达到距熔点10-15℃时,加热要(),使温度每分钟上升()。

4、在正溴丁烷的制备实验中,用硫酸洗涤是()及副产物()和()。

第一次水洗是为了()及()。

碱洗()是为了()。

第二次水洗是为了()。

5、乙酰水杨酸即(),是十九世纪末成功合成的一个用于解热止痛、治疗感冒的药物,至今仍广泛使用。

乙酰水杨酸是由()与()通过酯化反应得到的。

6、芦丁作为天然产物,其结构中含有()个糖基,不溶于乙醇、氯仿等有机溶剂,易溶于()。

二、选择题。

(每题2分,共20分)1、在水蒸气蒸馏操作时,要随时注意安全管中的水柱是否发生不正常的上升现象,以及烧瓶中的液体是否发生倒吸现象。

一旦发生这种现象,应(),方可继续蒸馏。

A、立刻关闭夹子,移去热源,找出发生故障的原因B、立刻打开夹子,移去热源,找出发生故障的原因C、加热圆底烧瓶2、进行简单蒸馏时,冷凝水应从()。

蒸馏前加入沸石,以防暴沸。

A、上口进,下口出B、下口进,上口出C、无所谓从那儿进水3、在苯甲酸的碱性溶液中,含有()杂质,可用水蒸气蒸馏方法除去。

A、MgSO4B、CH3COONaC、C6H5CHOD、NaCl4、在色谱中,吸附剂对样品的吸附能力与()有关。

A、吸附剂的含水量B、吸附剂的粒度C、洗脱溶剂的极性D、洗脱溶剂的流速5、在用吸附柱色谱分离化合物时,洗脱溶剂的极性越大,洗脱速度越()。

A、快B、慢C、不变D、不可预测6、在对氨基苯磺酸的制备过程中,可用()来检查反应是否完全。

A、10%氢氧化钠溶液B、10%醋酸C、10%碳酸钠溶液7、在进行脱色操作时,活性炭的用量一般为()。

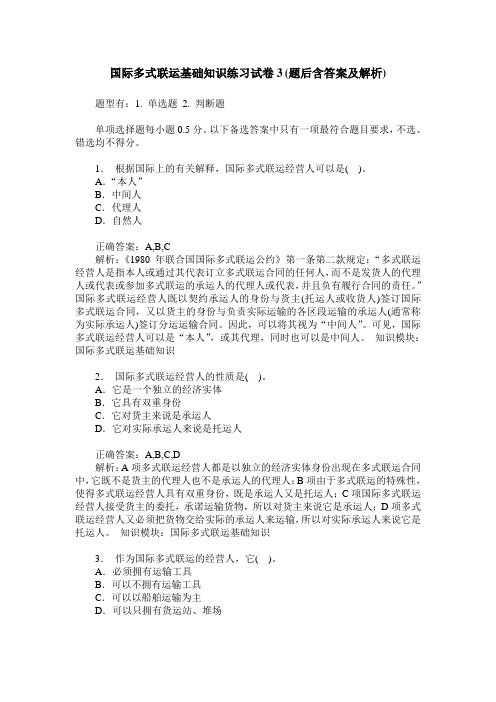

国际多式联运基础知识练习试卷3(题后含答案及解析)

国际多式联运基础知识练习试卷3(题后含答案及解析) 题型有:1. 单选题 2. 判断题单项选择题每小题0.5分。

以下备选答案中只有一项最符合题目要求,不选、错选均不得分。

1.根据国际上的有关解释,国际多式联运经营人可以是( )。

A.“本人”B.中间人C.代理人D.自然人正确答案:A,B,C解析:《1980年联合国国际多式联运公约》第一条第二款规定:“多式联运经营人是指本人或通过其代表订立多式联运合同的任何人,而不是发货人的代理人或代表或参加多式联运的承运人的代理人或代表,并且负有履行合同的责任。

”国际多式联运经营人既以契约承运人的身份与货主(托运人或收货人)签订国际多式联运合同,又以货主的身份与负责实际运输的各区段运输的承运人(通常称为实际承运人)签订分运运输合同。

因此,可以将其视为“中间人”。

可见,国际多式联运经营人可以是“本人”,或其代理,同时也可以是中间人。

知识模块:国际多式联运基础知识2.国际多式联运经营人的性质是( )。

A.它是一个独立的经济实体B.它具有双重身份C.它对货主来说是承运人D.它对实际承运人来说是托运人正确答案:A,B,C,D解析:A项多式联运经营人都是以独立的经济实体身份出现在多式联运合同中,它既不是货主的代理人也不是承运人的代理人;B项由于多式联运的特殊性,使得多式联运经营人具有双重身份,既是承运人又是托运人;C项国际多式联运经营人接受货主的委托,承诺运输货物,所以对货主来说它是承运人;D项多式联运经营人又必须把货物交给实际的承运人来运输,所以对实际承运人来说它是托运人。

知识模块:国际多式联运基础知识3.作为国际多式联运的经营人,它( )。

A.必须拥有运输工具B.可以不拥有运输工具C.可以以船舶运输为主D.可以只拥有货运站、堆场正确答案:B,C,D解析:国际多式联运经营人的职能在于负责完成多式运输合同或组织完成多式运输合同。

国际多式联运经营人既可以拥有运输工具从事一个或几个区段的实际运输,也可以不拥有任何运输工具,仅负责全程运输组织工作。

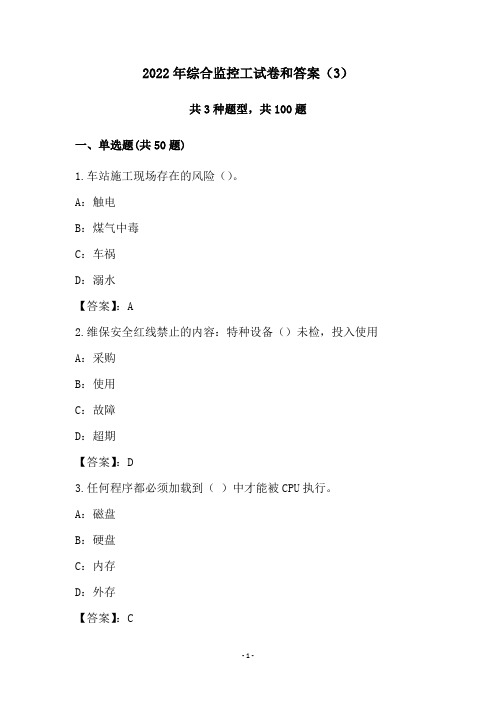

2022年综合监控工试卷和答案(3)

2022年综合监控工试卷和答案(3)共3种题型,共100题一、单选题(共50题)1.车站施工现场存在的风险()。

A:触电B:煤气中毒C:车祸D:溺水【答案】:A2.维保安全红线禁止的内容:特种设备()未检,投入使用A:采购B:使用C:故障D:超期【答案】:D3.任何程序都必须加载到()中才能被CPU执行。

A:磁盘B:硬盘C:内存D:外存【答案】:C4.经核实为与公司相关的外部信息,第一时间报()。

A:所属OCC及分公司生产调度B:所属OCCC:信息调度D:以上均对【答案】:A5.OSPF协议使用的算法是()。

A:最短路径优先算法B:最小生成树算法C:路径向量算法D:BF算法【答案】:A6.A、B、C类生产信息报送要求车间、站区负责人()分钟内报归口管理分部。

A:7B:8C:9D:10【答案】:D7.计算机最核心的部件是()。

A:主板B:CPUD:内存【答案】:B8.TCP协议通过()来区分不同的连接。

A:IP地址+端口号B:mac地址C:交换机地址D:服务器地址【答案】:A9.使用路由器对局域网进行分段的好处是()。

A:广播帧不会通过路由进行转发B:通过路由器转发减少了通信延迟C:路由器的价格便宜,比使用交换机更经济D:可以开发新的应用【答案】:A10.网络MAC地址一般由()位组成。

A:12B:24C:48D:96【答案】:C11.在网络中,为防止黑客攻击服务器所采取的关键技术是()。

B:加密C:备份D:身份识别【答案】:A12.当服务器硬盘出现黄灯提示预警时,可能是()部件故障。

A:硬盘B:内存条C:主板D:风扇【答案】:A13.IBP盘消火栓泵、喷淋泵的启泵按钮是()色。

A:绿B:红C:橙D:黄【答案】:B14.电气设备着火,首先必须采取的措施是()。

A:疏散B:拨打119C:停电D:灭火【答案】:C15.当车站站间或站内光纤出现断点或光纤损耗时,需要用()工具进行检测查找。

A:VWASB:modscan32C:tftpd32D:OTDR测试仪【答案】:D16.防火墙对数据包进行状态检测过滤时,不可以进行检测过滤的是()。

《工程热力学》参考试题与答案-试卷3

《工程热力学》参考试题及答案 3一.选择题(10 分)1. dq=dh-vdp 适用于系统,过程,工质。

[C] A.任意,任意,任意 B. 闭口,任意,理想气体C. 开口,可逆,任意D. 闭口,可逆,任意2. 理想气体经绝热节流后,温度。

[D]A.可能升高也可能降低 B. 升高C.降低 D. 不变3. 如图所示,以铜棒为系统进行分析:铜棒处于状态。

[B]A.平衡 B. 稳定但不平衡C.不稳定 D. 平衡且稳定4. 范德瓦尔状态方程a(P )(V m b) RT2Vm中,a 表示修正系数。

[B]A.气体分子体积修正系数 B. 内压力修正系数C.分子之间作用力修正系数D.分子之间斥力修正系数5. 压力为p 时,饱和水的熵为' s ;干饱和蒸汽的熵为'' s 。

当湿蒸汽的干度0<x<1 时,其熵为s,则。

[A]A.'' 's s s B.'' ' s s sC.' ''s s s D.' '' s s s二.判断题(10 分)1. 机械能可完全转化为热能,而热能却不能完全转化为机械能。

(×)2. 系统经历不可逆过程后,熵一定增大。

(×)3. 热机的热效率一定小于1。

(√)4. 水在湿蒸汽区发生定压吸热过程,温度升高。

(×)5. 若工质从同一初态,分别经可逆和不可逆过程,到达同一终态且两过程热源相同,那么传热量也相同。

(×)三.简答或画图分析题(30 分)6. (7 分)一闭口系统经历了一不可逆过程,已知终态熵小于初态熵,试分析此过程中热量的变化。

解:①闭口系统无质量交换;②不可逆过程:S g 0 ;③S S g S f 0 ;所以S f 0,即,此过程为一放热过程。

7. (8 分)在T-s 图上定性标出n=1.2 理想气体的压缩过程,并在图上用面积表示W 和W t 。

软膏剂、眼膏剂和凝胶剂练习试卷3(题后含答案及解析)

软膏剂、眼膏剂和凝胶剂练习试卷3(题后含答案及解析) 题型有:1. A1型题1.对凡士林基质说法错误的是A.凡士林是常用的油脂性基质B.凡士林是由多种分子量的烃类组成的半固体状混合物C.凡士林性质稳定无刺激性D.凡士林吸水性很强E.常温下每100g基质吸收水的克数即为水值正确答案:D 涉及知识点:软膏剂、眼膏剂和凝胶剂2.以下哪项检查最能反映栓剂的生物利用度A.体外溶出实验B.融变时限C.重量差异D.体内吸收实验E.硬度测定正确答案:D 涉及知识点:软膏剂、眼膏剂和凝胶剂3.下列哪种基质不属于凝胶基质A.明胶B.MCC.卡波普D.十六醇E.CMC-Na正确答案:D 涉及知识点:软膏剂、眼膏剂和凝胶剂4.软膏剂质量要求说法错误的是A.均匀、细腻并具有适当粘稠度B.软膏剂中药物应充分溶于基质中C.应无刺激性、过敏性与其他不良反应D.易涂布于皮肤或粘膜上E.眼用软膏剂应在无菌条件下进行制备正确答案:B 涉及知识点:软膏剂、眼膏剂和凝胶剂5.下列属于类脂基质的物质是A.聚乙二醇B.甘油C.羊毛脂D.硬脂酸脂肪酸酯E.十六醇正确答案:C 涉及知识点:软膏剂、眼膏剂和凝胶剂6.下列不是软膏剂质量检查项目的是A.酸碱度、熔点、物理外观B.刺激性、稳定性C.粒度、装量、灭菌D.融变时限E.稠度与粘度正确答案:D 涉及知识点:软膏剂、眼膏剂和凝胶剂7.下列不属于油脂性基质的是A.聚乙二醇B.凡士林C.石蜡D.二甲基硅油E.羊毛脂正确答案:A 涉及知识点:软膏剂、眼膏剂和凝胶剂8.下列不属于烃类基质的是A.凡士林B.硅酮C.蜂蜡D.液状石蜡E.固体石蜡正确答案:C 涉及知识点:软膏剂、眼膏剂和凝胶剂9.软膏剂的概念是A.软膏剂系指药物与适宜基质混合制成的半固体制剂B.软膏剂系指药物与适宜基质均匀混合制成的半固体制剂C.软膏剂系指药物与适宜基质混合制成的具有一定稠度的半固体制剂D.软膏剂就是油质性均匀细腻的外用制剂E.软膏剂系指药物与适宜基质均匀混合制成的具有一定稠度的半固体外用制剂正确答案:E 涉及知识点:软膏剂、眼膏剂和凝胶剂10.关于凡士林基质的错误表述为A.凡士林是由多种分子量的烃类组成的半固体状混合物B.凡士林是常用的油脂性基质C.凡士林吸水性很强D.常温下每100g基质吸收水的克数即为水值E.凡士林性质稳定,无刺激性正确答案:C 涉及知识点:软膏剂、眼膏剂和凝胶剂11.用来增加油性基质吸水性的物质是A.凡士林B.石蜡C.二甲基硅油D.羊毛脂E.十八醇正确答案:D 涉及知识点:软膏剂、眼膏剂和凝胶剂12.常用来调节基质稠度的物质是A.蜂蜡B.液状石蜡C.羊毛脂D.鲸蜡E.肥皂正确答案:B 涉及知识点:软膏剂、眼膏剂和凝胶剂13.药物透皮吸收的错误表述为A.角质层是药物吸收的主要屏障B.药物透皮吸收过程为药物穿透皮肤与吸收两个过程C.穿透指药物进入皮肤内对局部起作用D.穿透进入表皮层中的药物不会产生吸收作用E.药物进入真皮及皮下组织易为血管及淋巴管吸收正确答案:B 涉及知识点:软膏剂、眼膏剂和凝胶剂14.软膏剂的贮存应A.一般在常温下避光贮存B.一般在常温下避光、密闭条件下贮存,温度不宜过高或过低C.密闭条件下贮存D.温度不宜过高过低的条件下保存E.在常温下保存正确答案:B 涉及知识点:软膏剂、眼膏剂和凝胶剂15.下列关于乳化剂的错误表述为A.一价皂的乳化能力随脂肪酸碳原子数(在12~18范围内)增加而增强B.一价皂的HLB为10~15时,降低水相表面张力能力强C.十二烷基硫酸钠乳化作用最适pH为6~7D.多价皂HLB值小于6时形成W/O型基质E.制备乳剂型基质时,乳化剂常混合使用以调节适宜的HLB值正确答案:B 涉及知识点:软膏剂、眼膏剂和凝胶剂16.关于油脂性基质的正确表述为A.油脂性基质是指烃类物质B.凡士林基质常用于制备乳膏剂C.凡士林经漂白后可用于眼膏剂基质D.液状石蜡具有表面活性及一定的吸水性能E.羊毛脂的主要成分是胆固醇的棕榈酸酯及游离的胆固醇类正确答案:E 涉及知识点:软膏剂、眼膏剂和凝胶剂17.指出哪项不是一般眼膏剂的质量检查项目A.装量B.无菌C.色泽D.金属性异物E.微生物限度正确答案:C 涉及知识点:软膏剂、眼膏剂和凝胶剂18.常用的软膏剂基质分为A.油质性基质和水溶性基质B.油质性基质、水溶性基质和乳剂型基质C.油质性基质和乳剂型基质D.水溶性基质和乳剂型基质E.凝胶性基质和乳剂型基质正确答案:B 涉及知识点:软膏剂、眼膏剂和凝胶剂19.对乳剂型基质说法正确的是A.O/W型乳剂基质可选用高分子溶液作乳化剂B.HLB为7~9的表面活性剂易形成O/W型基质C.W/O乳剂基质“有反向吸收”现象D.O/W乳剂基质可使用于分泌物较多的病灶E.O/W型乳剂基质因外相水易蒸发变硬,故需加入保湿剂正确答案:E 涉及知识点:软膏剂、眼膏剂和凝胶剂20.以下为非离子型表面活性剂并可作乳化剂基质的是A.凡士林B.液体石蜡C.油脂类D.硅酮E.司盘吐温类正确答案:E 涉及知识点:软膏剂、眼膏剂和凝胶剂21.关于乳剂基质的错误表述为A.乳剂基质的油相多为固相B.乳剂型基质有水包油(O/W)型和油包水(W/O)型两种C.O/W型乳剂型软膏剂也称为“冷霜”D.O/W型基质软膏中的药物释放与透皮吸收较快E.肥皂类为O/W型乳剂基质的乳化剂正确答案:C 涉及知识点:软膏剂、眼膏剂和凝胶剂22.关于软膏剂的错误表述是A.软膏剂主要起保护、润滑和局部治疗作用B.有些药物要透入表皮才能发挥疗效C.软膏剂是由药物加入适宜基质制成的一种固体制剂D.软膏剂应均匀、细腻,涂于皮肤上无粗糙感E.用于创面的软膏剂应无菌正确答案:C 涉及知识点:软膏剂、眼膏剂和凝胶剂23.不作为栓剂质量检查的项目是A.溶点范围测定B.溶变时限测定C.重量差异测定D.稠度检查E.药物溶出速度正确答案:D 涉及知识点:软膏剂、眼膏剂和凝胶剂24.用来增加油性基质吸水性的物质是A.石蜡B.二甲基硅油C.十八醇D.凡士林E.羊毛脂正确答案:E 涉及知识点:软膏剂、眼膏剂和凝胶剂25.眼膏剂是指A.药物与基质混合制成的软膏剂B.药物混合均匀制成的软膏剂C.药物与基质制成的供眼用的软膏剂D.药物与基质制成的供眼用的灭菌软膏剂E.药物与适宜基质制成的专供眼用的灭菌软膏剂正确答案:E 涉及知识点:软膏剂、眼膏剂和凝胶剂26.对乳剂基质说法错误的是A.O/W型基质软膏中的药物释放与透皮吸收较快B.O/W型乳剂型软膏剂也称为“冷霜”C.乳剂型基质有水包油(O/W)型和油包水(W/O)型两种D.肥皂类为O/W型乳剂基质的乳化剂E.乳剂基质的油相多为固相正确答案:B 涉及知识点:软膏剂、眼膏剂和凝胶剂27.关于软膏剂基质的错误表述为A.基质不仅是软膏的赋形剂,也是药物的载体B.性质稳定,与主药不发生配伍禁忌C.稠度适宜,易于涂布D.易于清洗,不污染衣物E.对软膏剂的质量、药物释放、吸收无影响正确答案:E 涉及知识点:软膏剂、眼膏剂和凝胶剂28.下列关于油脂性基质的正确表述为A.硅酮即为二甲基硅油B.石蜡与液状石蜡为天然油脂性化合物C.羊毛脂可吸收2倍量的水而形成O/W型乳剂基质D.蜂蜡在W/O型基质中起稳定作用E.硅酮是一类具有表面活性剂的物质正确答案:A 涉及知识点:软膏剂、眼膏剂和凝胶剂29.下列不能用于制备眼膏剂的基质为A.黄凡士林B.液状石蜡C.固体石蜡D.硅酮E.羊毛脂正确答案:D 涉及知识点:软膏剂、眼膏剂和凝胶剂30.关于软膏剂的正确表述是A.二甲基硅油性能优良、无刺激性,可用作眼膏基质B.软膏剂应有良好的药物吸收能力C.软膏剂中药物的释放、吸收与基质性质无关D.某些软膏剂中药物透皮吸收后产生全身治疗作用E.凡士林经漂白后宜作为眼膏基质正确答案:D 涉及知识点:软膏剂、眼膏剂和凝胶剂31.以下为常用的眼膏剂的基质是A.黄凡士林和液体石蜡混合物B.黄凡士林和羊毛脂的混合物C.黄凡士林、液体石蜡和羊毛脂的8:1:1的混合物D.羊毛脂和液体石蜡的混合物E.羊毛脂正确答案:C 涉及知识点:软膏剂、眼膏剂和凝胶剂32.对乳化剂说法错误的是A.十二烷基硫酸钠乳化作用最适pH为6~7B.一价皂的乳化能力随脂肪酸碳数(由12~18)增加,而增强C.多价皂HLB值小于6时形成W/O型基质D.制备乳剂型基质乳化剂常混合使用以调节适宜的HLB值E.一价皂的HLB为10~15时,降低水相表面张力能力强正确答案:E 涉及知识点:软膏剂、眼膏剂和凝胶剂33.下属哪一种基质不是水溶性软膏基质A.聚乙二醇B.甘油明胶C.羊毛脂D.纤维素衍生物E.卡波普正确答案:C 涉及知识点:软膏剂、眼膏剂和凝胶剂34.软膏剂的类型按分散系统分为A.溶液型、乳剂型B.混悬型、乳剂型C.溶液型、混悬型D.溶液型、混悬型、乳剂型E.凝胶型、混悬型正确答案:D 涉及知识点:软膏剂、眼膏剂和凝胶剂35.下列关于油脂性基质的正确说法是A.石蜡与液体石蜡为天然油脂性化合物B.硅酮即为二甲基硅油C.羊毛脂可吸收2倍量的水而形成O/W型乳剂基质D.硅酮是一类具有表面活性剂的物质E.蜂蜡在W/O型基质中起稳定作用正确答案:B 涉及知识点:软膏剂、眼膏剂和凝胶剂36.关于油脂性基质的错误表述为A.此类基质涂于皮肤能形成封闭性油膜,促进皮肤水合B.油脂性基质中以类脂基质为常用C.类脂中以羊毛脂与蜂蜡应用较多D.固体石蜡与液状石蜡用以调节稠度E.羊毛脂可以增加基质吸水性及稳定性正确答案:B 涉及知识点:软膏剂、眼膏剂和凝胶剂37.油脂性基质的水值是A.100g基质所吸收水的克数B.一定量的基质所吸收水的克数C.常温下100g基质所吸收水的克数D.1g基质所吸收水的克数E.常温下1g基质所吸收水的克数正确答案:C 涉及知识点:软膏剂、眼膏剂和凝胶剂38.以下不属于凝胶基质的是A.十六醇B.CMC-NaC.明胶D.卡波姆E.MC正确答案:A 涉及知识点:软膏剂、眼膏剂和凝胶剂39.油脂性基质的水值是指A.常温下100g基质所吸收水的克数B.100g基质所吸收水的克数C.常温下1g基质所吸收水的克数D.1g基质所吸收水的克数E.一定量的基质所吸收水的克数正确答案:A 涉及知识点:软膏剂、眼膏剂和凝胶剂40.关于油脂性基质的错误表述为A.油脂性基质包括烃类、类脂类、油脂类三类B.凡士林基质适用于有大量渗出物的患处C.凡士林基质不适用于有大量渗出物的患处D.液状石蜡最适合用于调节凡士林基质的稠度E.凡士林中加入适量羊毛脂可提高其吸水性能正确答案:B 涉及知识点:软膏剂、眼膏剂和凝胶剂41.以下常用来调节油性基质稠度的物质是A.羊毛脂B.鲸蜡C.液体石蜡D.肥皂E.蜂蜡正确答案:C 涉及知识点:软膏剂、眼膏剂和凝胶剂42.哪种物质不宜作为眼膏基质成分A.液体石蜡B.羊毛脂C.白凡士林D.甘油E.卡波普正确答案:C 涉及知识点:软膏剂、眼膏剂和凝胶剂。

2022年财富考试试卷和答案(3)

2022年财富考试试卷和答案(3)共3种题型,共105题一、单选题(共35题)1.若国家GDP陷入负增长意味着()A:经济过热、黄金下跌B:经济过热、黄金上涨C:经济衰退、黄金下跌D:经济衰退、黄金上涨【答案】:D2.下列表述中错误的是()。

A:理财产品是金融机构发行的,根据合同约定将募集的资金投资于金融机构或非金融机构B:理财产品的发行方获得投资收益后,应根据合同约定将收益进行分配C:投资者购买理财产品属于间接投资行为,由金融机构代理理财D:银行理财产品一般期限较短,因此不存在流动性风险【答案】:D3.证券投资基金市场营销不同于有形产品营销,应根据投资者的风险承受能力销售不同风险等级的产品,这主要体现了证券投资基金销售具有()A:一次性B:效益性C:适用性D:灵活性【答案】:C4.下列对影响白银价格的因素描述错误的是()。

A:供求关系是影响白银价格的根本因素B:白银是重要的工业原材料,又可作为避险资产,其需求量与经济形势、政治局势密切相关C:根据经验,美元对主要货币汇率的变化将改变白银市场的大趋势D:随着基金参与商品期货交易程度的大幅提高,基金在白银价格波动中起到了推波助澜的作用【答案】:C5.可以体现基金盈利能力和分红能力的指标为()。

A:期末基金资产B:期末基金份额净值C:期初基金资产D:期末基金份额【答案】:B6.理财业务中违反法律、法规应承担的法律责任不包括()。

A:道义责任B:刑事责任C:民事责任D:行政责任【答案】:A7.基金财产投资的相关税收,由()承担,扣缴义务人按照国家有关税收征收的规定代扣代缴。

A:基金份额持有人B:基金财产本身C:基金管理人D:基金托管人【答案】:A8.在所有的财富管理工具中,()的防御性最强,是资产安全规划的主要工具之一。

A:股票B:保险C:固定收益债券D:个人信托【答案】:B9.银行对超过()岁(含)的客户进行风险承受能力评估时,应当充分考虑客户年龄、相关投资经验等因素。

基础心理学练习试卷3(题后含答案及解析)

基础心理学练习试卷3(题后含答案及解析) 题型有:1. 职业道德基础理论与知识部分 2.职业道德职业道德基础理论与知识部分单项选择题1.巴甫洛夫认为神经活动的基本过程是()。

A.兴奋B.抑制C.兴奋与抑制D.反射正确答案:C 涉及知识点:基础心理学2.“谈虎色变”是一种条件反射的表现,它属于()。

A.第一信号系统的活动B.第二信号系统的活动C.两种信号系统相结合D.以上答案都不对正确答案:B 涉及知识点:基础心理学3.感受性是()。

A.能引起感觉的最小刺激量B.感觉器官对适宜刺激的感觉能力C.感觉阈限的大小D.最小可觉差的大小正确答案:B 涉及知识点:基础心理学4.听觉的适宜刺激是()。

A.空气振动B.物体振动C.空气D.声源正确答案:A 涉及知识点:基础心理学5.下列关于听觉特性的描述不正确的是()。

A.声音有音调、响度和音色三种性质B.声波的频率越低,音调就越高C.声波的振幅越大,声音就越响D.日常生活的声音大多是声波混合的结果正确答案:B 涉及知识点:基础心理学6.下列关于平衡觉的说法不正确的是()。

A.平衡觉也叫做静觉B.平衡觉的感受器是前庭器官C.人平躺的时候,平衡觉较弱D.平衡觉是人对自己身体位置与地心引力关系的反映正确答案:C 涉及知识点:基础心理学7.两可图形反映出人对事物知觉的()。

A.整体性B.选择性C.恒常性D.理解性正确答案:B 涉及知识点:基础心理学8.()概念不是由巴甫洛夫提出的。

A.操作性条件反射B.反射、反射弧和反馈C.第一信号系统和第二信号系统D.动力定型正确答案:A 涉及知识点:基础心理学9.彼此接近的物体比相隔较远的物体更容易产生()的倾向。

A.知觉选择性B.知觉整体性C.知觉理解性D.知觉恒常性正确答案:B 涉及知识点:基础心理学10.知觉条件在—定范围内发生变化,知觉映象保持相对不变的特性被称为()。

A.知觉的整体性B.知觉的理解性C.知觉的选择性D.知觉的恒常性正确答案:D 涉及知识点:基础心理学11.一支白粉笔,无论把它置于明亮处还是黑暗处,人们都会把它知觉为白粉笔,这种知觉特性被称为()。

液压传动技术试卷3(含答案)

重庆科技学院液压传动技术试卷3一、填空题:(本题共11小题,20空,每空1分,共20分)1、液压传动系统的压力主要取决于,执行元件的速度取决于进入它的液体的。

2、液压马达是把_______________能转变为_______________能的转换装置。

3、液压泵的效率主要包括效率和机械效率,前者反映了泄漏的大小,影响实际流量,后者反映了机械摩擦损失,影响驱动泵所需的转速。

4、对于三位四通换向阀,当中位机能为型时活塞浮动,液压泵卸荷。

为_______型时可组成差动连接。

5、在液压系统中,产生气蚀现象的根本原因是。

6、压力继电器是将信号转换为信号的一种转换元件。

7、已知单活塞杠液压缸的活塞直径D为活塞杆直径d的两倍,则差动连接的快进速度等于非差动连接前进速度的倍。

8、液压泵能正常工作的必备条件是①②③。

9、溢流阀常用在定量泵节流调速液压系统中作定压阀使用,此时,溢流阀的阀口是常(开/闭)。

10、液压传动的调速回路有、和三种。

11、液压泵的实际流量比理论流量;而液压马达实际流量比理论流量。

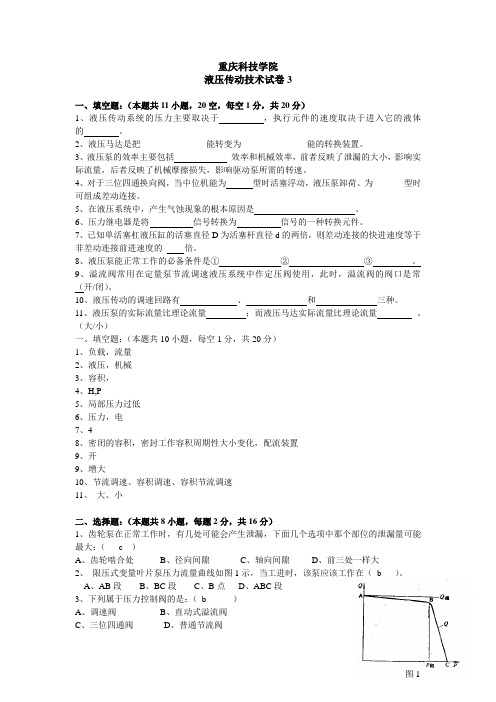

(大/小)一、填空题:(本题共10小题,每空1分,共20分)1、负载,流量2、液压,机械3、容积,4、H,P5、局部压力过低6、压力,电7、48、密闭的容积,密封工作容积周期性大小变化,配流装置9、开9、增大10、节流调速、容积调速、容积节流调速11、大、小二、选择题:(本题共8小题,每题2分,共16分)1、齿轮泵在正常工作时,有几处可能会产生泄漏,下面几个选项中那个部位的泄漏量可能最大:( c )A、齿轮啮合处B、径向间隙C、轴向间隙D、前三处一样大2、限压式变量叶片泵压力流量曲线如图1示,当工进时,该泵应该工作在(b )。

A、AB段B、BC段C、B点D、ABC段3、下列属于压力控制阀的是:(b )A、调速阀B、直动式溢流阀C、三位四通阀D、普通节流阀图14、在定量泵-变量马达的容积调速回路中,如果液压马达所驱动的负载转矩变小,若不考虑泄漏的影响,试判断马达转速:( c )A 、增大B 、减小C 、基本不变D 、无法判断 5、调速阀是 而成的。

C语言期末考试试卷及答案3

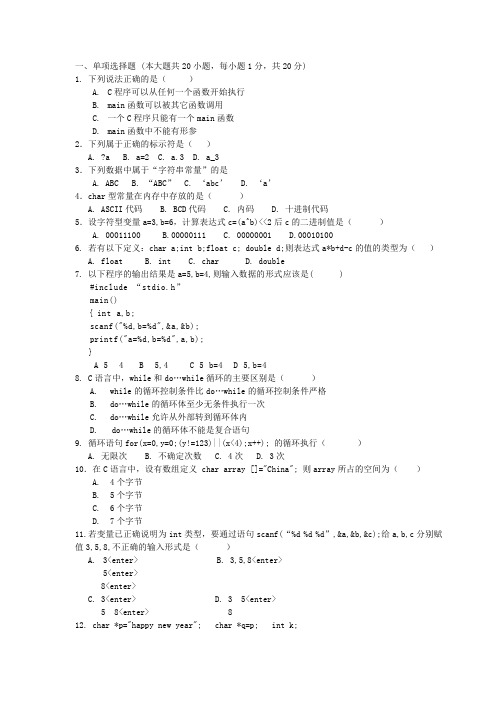

一、单项选择题(本大题共20小题,每小题1分,共20分)1.下列说法正确的是()A.C程序可以从任何一个函数开始执行B.main函数可以被其它函数调用C.一个C程序只能有一个main函数D.main函数中不能有形参2.下列属于正确的标示符是()A.?aB.a=2C.a.3D.a_33.下列数据中属于“字符串常量”的是A.ABCB.“ABC”C.‘abc’D.‘a’4.char型常量在内存中存放的是()A.ASCII代码B.BCD代码C.内码D.十进制代码5.设字符型变量a=3,b=6,计算表达式c=(a^b)<<2后c的二进制值是()A.00011100B.00000111C.00000001D.000101006.若有以下定义:char a;int b;float c;double d;则表达式a*b+d-c的值的类型为()A.floatB.intC.charD.double7.以下程序的输出结果是a=5,b=4,则输入数据的形式应该是()#include“stdio.h”main(){int a,b;scanf("%d,b=%d",&a,&b);printf("a=%d,b=%d",a,b);}A54B5,4C5b=4D5,b=48.C语言中,while和do…while循环的主要区别是()A.while的循环控制条件比do…while的循环控制条件严格B.do…while的循环体至少无条件执行一次C.do…while允许从外部转到循环体内D.do…while的循环体不能是复合语句9.循环语句for(x=0,y=0;(y!=123)||(x<4);x++);的循环执行()A.无限次B.不确定次数C.4次D.3次10.在C语言中,设有数组定义char array[]="China";则array所占的空间为()A.4个字节B.5个字节C.6个字节D.7个字节11.若变量已正确说明为int类型,要通过语句scanf(“%d%d%d”,&a,&b,&c);给a,b,c分别赋值3,5,8,不正确的输入形式是()A.3<enter>B.3,5,8<enter>5<enter>8<enter>C.3<enter>D.35<enter>58<enter>812.char*p="happy new year";char*q=p;int k;for(k=1;k<8;k++){putchar(*q);q++;}上面C程序段的输出结果是()A.happy new yearB.happy newC.happy nD.happyE.appy n13.设double*p[5];则A.p是指向double型变量的指针B.p是double型数组C.p是指针数组,其元素是指向double型变量的指针D.p是数组指针,指向double型数组14.两个指针变量不可以()A.相加B比较C相减D指向同一地址15.对C语言函数描述正确的是A.在C语言中调用函数时,只能把实参的值传给形参,形参的值不能传回给实参B.C函数既可以嵌套定义又可以递归调用C.函数必须有返回值,否则不能使用函数D.函数必须有返回值,返回值类型不定16.设有如下定义,则对data中的a成员的正确引用是()struct test{int a;float b;}data,*p=&data;A.(*p).data.aB.(*p).aC.p->data.aD.p.data.a17.有如下程序(提示:注意宏替换的规则)#define N2#define M N+1#define NUM2*M+1#main(){int i;for(i=1;i<=NUM;i++)printf(“%d\n”,i);}该程序中的for循环执行的次数是()A.5B.6C.7D.818.若有以下定义,则printf(“%d\n”,sizeof(them));的输出是()typedef union{long x[2];int y[4];char z[8];}MYTYPE;MYTYPE them;A.32B.16C.8D.2419.下列语句中,将c定义为文件型指针的是()A.FILE c;B.FILE*c;C.file c;D.file*c;20.下列关于C语言数据文件的叙述中正确的是A.文件由ASCII码字符序列组成,C语言只能读写文本文件B.文件由二进制数据序列组成,C语言只能读写二进制文件C.文件由记录序列组成,可按数据存放形式分为二进制文件和文本文件D.文件由数据流形式组成,可按数据的存放形式分为二进制文件和文本文件二、填空题(本大题共10小题,每小题2分,共20分)1.在定义变量的同时给变量赋予初值就称为___________________________________ 2.下面程序段的输出结果是___________________________________________ int a=28;a=a&21;printf(“%d%o\n”,a,a);3.能正确表示0≤a≤10的逻辑表达式是_________________________________4.若有定义int a[3],*p;则使p指向数组a的赋值语句是_______________________ 5.strcmp函数的功能是________________________________________6.写出数学式a acbbx24 2-+-=的C语言表达式________________________________ 7.将以下程序写成三目运算符的表达式是____________________________________if(a>b)max=a;else max=b8.设有定义如下:#define F(N)2*N,则表达式F(2+3)的值是_____________________. 9.在C语言中,指针运算符为___________________,取地址运算符________________。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

华北航天工业学院试题

课程名称:可编程器件EDA技术与实践

试卷种类:期末考试(A)卷,共5页

班级:姓名:学号:成绩:

———————————————————————————————

1.基于可编程器件EDA技术主要包括四大要素,分别为大规模可编程器件、硬件描述语言、软件开发系统、实验开发系统。

2.可编程器件分为PLD和PAC。

3.CPLD的基本结构看成由可编程逻辑宏单元、可编程I/O控制模块和可编程内部连线等三部分组成。

4.FPGA由可编程逻辑块(CLB)、可编程互连单元(I/O)和可编程互连三种可编程电路和一个SRAM结构的配置存储单元组成。

5.CPLD中的逻辑单元是大单元,适合逻辑型系统系统;FPGA的逻辑单元是小单元,

适合数据型系统系统。

6.根据数字系统的功能定义,可将整个系统划分为两个子系统:数据处理子系统和控制子系统。

7.MAX+PLUSII支持的设计输入方法有图形输入,波形输入,文本输入。

8.图形文件的扩展名是GDF ,仿真通道文件的扩展名是SCF,波形文件的扩展名是WDF,使用VHDL语言,文本设计文件的扩展名是.VHD 。

三、简答题20分(每题5分)

1.设计时怎样选择CPLD和FPGA芯片?

从以下几个方面进行选择:

1.逻辑单元

CPLD中的逻辑单元是大单元,通常其变量数约20~28个。

FPGA逻辑单元是小单元,其输入变量数通常只有几个,

2.内部互连资源与连线结构

FPGA单元小、互连关系复杂,所以使用的互连方式较多。

CPLD不采用分段互连方式,它使用的是集总总线。

3.编程工艺

CPLD属于只读(ROM)型编程,可以反复编程,但它们一经编程,片内逻辑就被固定,如果数据改变就要进行重新擦写。

FPGA芯片采用RAM型编程,功耗低,但掉电后信息不能保存,必须与存储器联用。

每次上电时须先对芯片配置,然后方可使用。

4.规模

逻辑电路在中小规模范围内,选用CPLD价格较便宜,能直接用于系统。

对于大规模的逻辑

设计,则多采用FPGA.

5.FPGA和CPLD封装形式的选择

FPGA和CPLD器件的封装形式很多。

同一型号的器件可以多种不同的封装。

2.说明用原理图输入方法设计电路的详细流程。

答:MAX+PLUSⅡ的设计过程包括设计项目的建立与设计的输入、设计编译、设计校验(仿真和定时分析)、器件编程四个步骤。

设计输入:可以采用原理图输入、HDL语言描述、及波形输入等几种方式。

设计编译:先根据设计要求设定编译参数和编译策略,如器件的选择、逻辑综合方式的选择等。

然后根据设定的参数和策略对设计项目进行网表提取、逻辑综合和器件适配,并产生报告文件、延时信息文件及编程文件,供分析仿真和编程使用。

设计校验(项目仿真):包括功能仿真、时序仿真和定时分析,可以利用软件的仿真功能来验证设计项目的逻辑功能是否正确。

器件编程与验证:用经过仿真确认后的编程文件通过编程器(Programmer)将设计下载到实际芯片中,最后测试芯片在系统中的实际运行性能。

在设计过程中,如果出现错误,则需重新回到设计输入阶段,改正错误或调整电路后重复上述过程。

3.说明端口模式INOUT和BUFFER有何异同点。

答:INOUT:双向端口;BUFFER:输出并向内部反馈。

4.简述元件例化语句的作用,组成及格式。

答:把已经设计好的设计实体称为一个元件或一个模块,它可以被高层次的设计引用。

引用时就会用到元件声明和元件例化语句。

二者缺一不可。

1)元件声明

COMPONENT 元件实体名

PORT (元件端口信息);

END COMPONENT;

2)元件例化

例化名:元件名PORT MAP (端口列表)

三、判断下列程序是否有错误,如有则指出错误所在,并给出完整程序。

(10分)

(10分)

程序1:

library ieee;

use ieee.std_logic_1164.all;

ENTITY mux21 is

port(a,b,sel:in std_logic;

y:out std_logic;);

end mux21;

architecture one of mux21 is

BEGIN

PROCESS(SEL,a,b)

IF sel=’0’ THEN y<=a;

ELSE y<=b;

End if;

End process;

End ONE;

程序2:

signal A,EN: std_logic;

process(A,EN)

variable B: std_logic;

begin

if EN=1 then B:=A;

end if;

end process;

四、解释程序(30分)

要求:

1.解释带有下划线的语句。

2.画出该程序的原理图符号。

3.说明该程序逻辑功能。

Library ieee; 定义元件库

Use ieee.std_logic_1164.all;

Use ieee.std_logic_unsigned.all;

Entity up_down is 实体说明

Port(clk,rst,en,up: in std_logic;

Sum: out std_logic_vector(2 downto 0);

Cout: out std_logic);

End up_down;

Architecture a of up_down is 结构体说明

Signal count: std_logic_vector(2 downto 0);

Begin

Process(clk,rst) 进程,敏感信号为clk rst

Begin

If rst=’0’ then

Count<=(others=>’0’);异步清零

Elsif rising_edge(clk) then 上升沿

If en=’1’ then计数控制端EN=1

Case up is

When ‘1’ => coun t<=count+1; UP=1加法计数

When others =>count<=count-1; UP=0减法计数

End case;

End if;

End if;

End process;

Sum<=count;

Cout <=’1’ when en=’1’ and ((up=’1’ and count=7) or (up=’0’ and count=0)) else ‘0’;进位信号

End a;

异步清零,同步计数的三位二进制可逆计数器

五、编程序(20分)

1.已知电路原理图如下,请用VHDL语言编写其程序

library ieee;

use ieee.std_logic_1164.all;

ENTITY mux21 is

port(a,b,s:in bit;

y:out bit);

end mux21;

architecture one of mux21 is

single d,e:bit;

begin

d<=a and (not)s;

e<=b and s;

y<=d or e;

end one;

2.用元件例化语句设计如图所示电路。

元件为2输入与非门。

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY yf4 IS

PORT( A,B,C,D: IN std_logic;

Z: OUT std_logic);

END yf4;

ARCHITECTURE a OF yf4 IS

COMPONENT yf2

PORT (A1,B1: IN std_logic;

C1: O UT std_logic);

END COMPONENT;

SIGNAL X,Y: std_logic ;

BEGIN

U1:yf2 PORT MAP (A,B,X);

U2:yf2 PORT MAP (C,D,Y);

U3:yf2 PORT MAP (A1 => X, C1=>Z, B1 => Y);

END a;。