数电第五版阎石课后习题及答案

阎石《数字电子技术基础》(第5版)(课后习题 数制和码制)【圣才出品】

1.3 将下列二进制小数转换为等值的十进制数。

(1)(0.1001)2

;(2)(0.0111)2

;(3)(0.101101)2

(0.001111)2 。

解:(1) (0.1001)2 1 21 0 22 0 23 1 24 0.5625 (2) (0.0111)2 0 21 1 22 1 23 1 24 0.4375

3/8

圣才电子书

十万种考研考证电子书、题库视频学习平

台

1.9 将下列十进制数转换为等值的二进制数和十六进制数。要求二进制数保留小数点

以后 4 位有效数字。

Байду номын сангаас

(1)(25.7)10 ; (2)(188.875)10 ; (3)(107.39)10 ; (4)

(174.06)10 。

2/8

圣才电子书

十万种考研考证电子书、题库视频学习平

台

。

解:(1)

8C 16

1000

1100 2

(2) 3D.

BE 16

0011 1101.1011 1110 2

(3)

8F

.FF

16

1000

1111. 1111

1111 2

(4) 10.

00 16

0001

0000.0000

(4) (255)10 (11111111)2 (FF )16

1.8 将下列十进制数转换为等值的二进制数和十六进制数。要求二进制数保留小数点 以后 8 位有效数字。

(1)(0.519)10 ; (2)(0.251)10 ; (3)(0.0376)10 ; (4) (0.5128)10 。

解:(1) (0.519)10 (0.10000100)2 (0.84)16 (2) (0.251)10 (0.01000000)2 (0.40)16 (3) (0.0376)10 (0.00001001)2 (0.09)16 (4) (0.5128)10 (0.10000011)2 (0.83)16

阎石《数字电子技术基础》(第5版)(课后习题 可编程逻辑器件)【圣才出品】

第8章 可编程逻辑器件8.1试分析图8-1的与-或逻辑阵列,写出Y 1、Y 2、Y 3与A 、B 、C 、D 之间的逻辑函数式。

图8-1解:Y 1、Y 2、Y 3与A 、B 、C 、D 之间的逻辑函数式分别为:Y 1=A'+B +C +D'Y 2=AB +A'B'+CD'+C'DY 3=ABCD +A'B'C'D'8.2试分析图8-2的与-或逻辑阵列,写出Y 1、Y 2与A 、B 、C 、D 之间的逻辑关系式。

图8-2解:Y1、Y2与A、B、C、D之间的逻辑关系式分别为:Y1=(AB'+A'B+CD)'当AB=1时,Y2=(CD'+C'D)',否则Y2呈现高阻态。

8.3 试分析图8-3中由PAL16L8构成的逻辑电路,写出Y1、Y2、Y3与A、B、C、D、E之间的逻辑关系式。

图8-3解:Y1、Y2、Y3与A、B、C、D、E之间的逻辑关系式分别为:Y1=(A'B'+A'C'+A'D'+A'E'+B'C'+B'D'+B'E'+C'D'+C'E'+D'E')'Y2=ABCD+ACDE+ABCE+ABDE+BCDEY 3=ABCDE8.4 用PAL16L8产生如下一组组合逻辑函数。

画出与-或逻辑阵列编程后的电路图。

PAL16L8的电路图见图8-3。

解:先将组合逻辑函数化为与-或-非形式。

得到用PAL16L8的实现如图8-4所示。

图8-48.5 试分析图8-5给出的用PAL16R4构成的时序逻辑电路,写出电路的驱动方程、状态方程、输出方程,画出电路的状态转换图。

工作时,11脚接低电平。

图8-5解:若11脚接低电平,电路正常工作。

数字电子技术第五版阎石 第五版第6章的 习题答案

第六章习题课后一、选择题1.PROM和PAL的结构是。

A.PROM的与阵列固定,不可编程B. PROM与阵列、或阵列均不可编程C.PAL与阵列、或阵列均可编程D. PAL的与阵列可编程2.PAL是指。

A.可编程逻辑阵列B.可编程阵列逻辑C.通用阵列逻辑D.只读存储器3.当用异步I/O输出结构的PAL设计逻辑电路时,它们相当于。

A.组合逻辑电路B.时序逻辑电路C.存储器D.数模转换器4.PLD器件的基本结构组成有。

A.输出电路B.或阵列C. 与阵列D. 输入缓冲电路5.PLD器件的主要优点有。

A.集成密度高B. 可改写C.可硬件加密D. 便于仿真测试6.GAL的输出电路是。

A.OLMCB.固定的C.只可一次编程D.可重复编程7.PLD开发系统需要有。

A.计算机B. 操作系统C. 编程器D. 开发软件8.只可进行一次编程的可编程器件有。

A.PALB.GALC.PROMD.PLD9.可重复进行编程的可编程器件有。

A.PALB.GALC.PROMD.ISP-PLD10.ISP-PLD器件开发系统的组成有。

A.计算机B.编程器C.开发软件D.编程电缆11.全场可编程(与、或阵列皆可编程)的可编程逻辑器件有。

A.PALB.GALC.PROMD.PLA12.GAL16V8的最多输入输出端个数为。

A.8输入8输出B.10输入10输出C.16输入8输出D.16输入1输出13一个容量为1K×8的存储器有个存储单元。

A.8B. 8192C.8000D. 8K14.要构成容量为4K×8的RAM,需要片容量为256×4的RAM。

A. 8B.4C. 2D.3215.寻址容量为16K×8的RAM需要根地址线。

A. 8B. 4C.14D.16KE. 1616.RAM的地址码有8位,行、列地址译码器输入端都为4个,则它们的字线加位线共有条。

A.8B.16C.32D.25617.某存储器具有8根地址线和8根双向数据线,则该存储器的容量为。

阎石《数字电子技术基础》(第5版)(课后习题 数-模和模-数转换)【圣才出品】

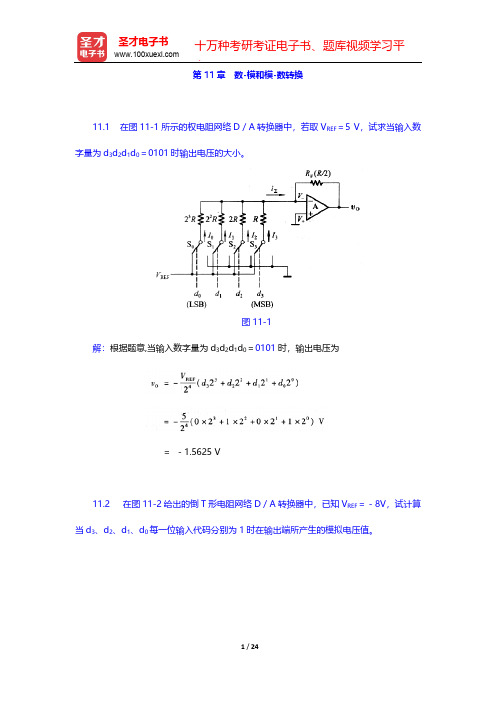

第11章 数-模和模-数转换11.1 在图11-1所示的权电阻网络D/A转换器中,若取V REF=5 V,试求当输入数字量为d3d2d1d0=0101时输出电压的大小。

图11-1解:根据题意,当输入数字量为d3d2d1d0=0101时,输出电压为=-1.5625 V11.2 在图11-2给出的倒T形电阻网络D/A转换器中,已知V REF=-8V,试计算当d3、d2、d1、d0每一位输入代码分别为1时在输出端所产生的模拟电压值。

图11-2解:由题意可得因此,当31d =时,O 4v V =;当21d =时,O v 2V =;当11d =时,O 1v V =;当01d =时,O 05v .V =。

11.3 在图11-3所示的D /A 转换电路中,给定V REF =5V ,试计算(1)输入数字量的d 9~d 0每一位为1时在输出端产生的电压值。

(2)输入为全1、全0和1000000000时对应的输出电压值。

图11-3解:由题意可得因此,题(1)、(2)的结果如表11-1所示。

表11-111.4 在图11-3由CB7520所组成的D /A 转换器中,已知V REF =-10V ,试计算当输入数字量从全0变到全1时输出电压的变化范围。

如果想把输出电压的变化范围缩小一半,可以采取哪些方法?解:由题意可得当输入全为0时,有0O min v V =;当输入全为1时,有()1010219992REF O max V v .V =--=。

因此,电压变化范围为0~9.99 V 。

如果想把输出电压的变化范围缩小一半,可以采取以下方法:①令参考电压REF V 的绝对值减半;②令求和放大器的放大倍数减少一半。

即在out I 与放大器输出端O v 之间外接一个大小等于2R 的反馈电阻。

11.5 图11-4所示电路是用CB7520和同步十六进制计数器74LS161组成的波形发生器电路。

已知CB7520的V REF =-10V ,试画出输出电压O v的波形,并标出波形图上各点电压的幅度。

数电第五版答案阎石第一三章(完整资料).doc

【最新整理,下载后即可编辑】第一章1.1 二进制到十六进制、十进制(1)(10010111)2=(97)16=(151)10 (2)(1101101)2=(6D)16=(109)10(3)(0.01011111)2=(0.5F)16=(0.37109375)10 (4)(11.001)2=(3.2)16=(3.125)10 1.2 十进制到二进制、十六进制(1)(17)10=(10001)2=(11)16(2)(127)10=(1111111)2=(7F)16(3) (0.39) 10 (0.0110 0011 1101 0111 0000 101 0)2 (0.63 D70 A )161.8 用公式化简逻辑函数(1)Y=A+B(2)Y ABC A B C 解:Y BC A B C C A B C (1 A+A=1)(4)Y ABCD ABD ACD 解:Y AD(BC B C ) AD(B C C) AD(5)Y=0(4) (25.7) 10 (11001.101 1 0011)2 (19.B3)16(3)Y=1(7)Y=A+CD(6)Y AC(CD AB) BC(B AD CE) 解:Y BC(B AD CE) BC(B AD) CE ABCD(C E ) ABCDE(8)Y A (B C)(A B C)(A B C) 解:Y A (B C)(A B C)(A B C) A (ABC BC)(A B C) A BC( A B C) A ABC BC A BC(9)Y BC AD AD(10)Y AC AD AEF BDE BDE1.9 (a) Y ABC BC(b)(c) Y1 AB AC D,Y2 AB AC D ACD ACD (d) Y1 AB AC BC,Y2 ABC ABC ABC ABC 1.10 求下列函数的反函数并化简为最简与或式Y ABC ABC(1) (2)Y A C DY AC BC(3)Y (A B)(A C)AC BC 解:Y ( A B)(A C)AC BC [(A B)(A C) AC] BC(4)Y A B C ( AB AC BC AC)(B C) B C【最新整理,下载后即可编辑】(5)Y AD AC BCD C 解:Y (A D)(A C)(B C D)C AC(A D)(B C D) ACD(B C D) ABCD1.11 将函数化简为最小项之和的形式(6)Y 0(1)Y ABC AC BC 解:Y ABC AC BC ABC A(B B )C ( A A)BC ABC ABC ABC ABC ABC ABC ABC ABC ABC(2)Y ABCD ABCD ABCD ABCD ABCD ABCD (3)Y A B CD解:Y A(BC D BCD BCD BCD BC D BCD BCD BCD) B( ACD ACD ACD ACD AC D ACD ACD ACD) (AB AB AB AB)CD ABC D ABCD ABCD ABCD ABC D ABCD ABCD ABCD ABC D ABCD ABCD ABCD ABCD (13)(4)Y ABCD ABCD ABCD ABC D ABCD ABCD ABCD ABCD (5)Y LM N LMN LMN LMN L M N LMN1.12 将下列各函数式化为最大项之积的形式(1)Y (A B C )( A B C)( A B C )(2)Y (A B C)( A B C)( A B C)(3)Y M 0 M 3 M 4 M 6 M 7(4) Y M 0 M 4 M 6 M 9 M12 M13(5)Y M 0 M 3 M 51.13 用卡诺图化简法将下列函数化为最简与或形式:(1)Y A D(3)Y 1(2)Y AB AC BC CD(4)Y AB AC BC(5)Y B C DY C D AB(7)(9)Y B D AD BC ACD (8)Y ( A, B, C, D) m (0,1,2,3,4,6,8,9,10,11,14)Y AB AC(6)Y AB AC BCY C(10)Y ( A, B, C) (m1,m4 , m7 )Y B CD AD 【最新整理,下载后即可编辑】Y ABC ABC ABC1.14 化简下列逻辑函数 (1)Y A B C D (3)Y AB D AC (5)Y AB DE CE BDE AD ACDE1.20 将下列函数化为最简与或式 (1)Y ACD BCD AD (3)Y A B C (5)Y 1 第三章3.1 解:由图可写出 Y1、Y2 的逻辑表达式:Y1 ABC ( A B C) AB AC BC ABC ABC ABC ABCY2 AB AC BC真值表:(2)Y CD ACD (4)Y BC BD(2)Y B AD AC (4)Y A B D (6)Y CD B D AC3.2 解: , comp 1、Z 0 时,Y1 A,Y2 A2,Y3 A2 A3 A2 A3,Y4 A2 A3 A4comp 0、Z 0 时,Y1 A1,Y2 A2,Y3 A3,Y4 A真值表:3.3 解:【最新整理,下载后即可编辑】3.4 解:采用正逻辑,低电平=0,高电平=1。

数电第五版答案阎石第一三章

数电第五版答案阎⽯第⼀三章1.1⼆进制到⼗六进制、⼗进制(4)(11.001)2=(3.2) 16=(3.125) 10(3) Y (A B)(A C)AC BC第⼀章(1)Y=A+B(3)Y=1(2)Y ABC A BC(4)Y ABCD ABD ACD解:Y BC AB CC A B C 1(A + A =1)解:Y AD(BC B C) AD(B C C) AD(5)Y=0(7)Y=A+CD(6)Y AC (CD :AB) BC(BAD CE)解:Y BC(B AD CE) BC(B AD) CE ABCD(CE) ABCDE(0.63D70A )16(2)(127) 10=(1111111) 2=(7F) 16(4) (25.7)10(11001.101 1 0011)2(19.B3)16⑻丫解:A Y A (B C)(A B C)(A B A (B C)(A B C)(AC A A (ABC \ BCBC)(A B C)BC(A B C) AABC (9)Y BCA D AD(10)Y AC AD AEF BDE BDE1.9 (a)Y ABC BC(b)Y ABC ABC(c) Y 1AB ACD,Y 2AB ACDACD , ACD(d) 丫 1 AB AC BC,Y 2ABC ABCABC ABC1.10 求下列函数的反函数并化简为最简与或式 Y A C D (1)Y ABC ACBC解: Y ABCAC Be A BC A (B B)C (AA)BCA BC ABC ABC ABC ABC A B CABC ABC⑵YABCD ABCD ABCD ABCD ABCDA BCDACD(B C D) ABCD将函数化简为最⼩项之和的形式ABC(3)(0.01011111) 2=(0.5F) 16=(0.37109375) 10 1.2⼗进制到⼆进制、⼗六进制(1)(17) 10=(10001) 2=(11) 16 (3) (0.39)10 (0.0110 0011 1101 0111 0000 1010) 2 1.8⽤公式化简逻辑函数 (1) Y AC BC 解:丫 (A B)(A C)AC BC[(AB)(A C) AC] BC(5)Y(AB AC BCAD AC BCD C 解:丫 (A D)( A C)(BAC)(BC)C D)C AC(A D)(B D)1.11(3) Y A B CD解:Y A(BCDBCD BCD BCD BCD BCD BCD BCD)B(ACDACDA CD A CD ACD ACD ACDACD) (AB AB AB AB)CDABCD ABCDABCD ABCD ABCDABCD ABCD ABCDA B CD A B C D A BCD A BCDABCD (13)⑷ Y ABCD ABCD ABCD ABCD ABCD ABCD ABCD ABCD(5) Y LMN LMN LMN LMN LMN LMN 1.12 将下列各函数式化为最⼤项之积的形式(1) Y (A B C)(A B C)(A B C) (2)(5) Y M o M 3 M 5 1.13⽤卡诺图化简法将下列函数化为最简与或形式:1.20将下列函数化为最简与或式(1) Y ACD BCD AD (2) Y B AD AC(3) Y A BCA BD(5) Y 1(6)YCDBD ACY (A B C)(A B C)(A B C)(3) Y M o M 3 M 4 M 6 M 7Y M 0 M 4 M 6 M 9 M 12 M 13(1) Y A D (2) Y AB AC BCCD AB AC BC0 i r:0 J 1i1 1[1JLi)D AB(6)(9)E p0 011〕 0ABACY AB AC BC Y BD AD BCA CD(8) Y(A,B,C,D) m (0,1,2,3,4,6,8,9,10,11,14) (10) Y (A ,B ,C)10 0 J 0 0 D 1j i11B CD AD1 0 0 11Y ABC ABC ABC(1) YABCD (2) ⑶ YAB D AC(4)⑸ Y A B D E CEBDE AD A C DEY CD ACD YBC BD00 01 II 10,1 JIt LCM 01.11 1001 11 101.14化简下列逻辑函数3.1解:由图可写出 Y i 、Y 2的逻辑表达式:Y 1 ABC (A B C) ―AC ―BCABC ABC ABC ABC Y 2 AB AC BC真值表:ABC Yi Yi0 0 0 0 Q0 & 1 0 1 0 ;J 曲真值表知,电路是⼀亍⼀位全加器。

数字电子技术基础阎石第五版课后答案

数字电子技术基础阎石第五版课后答案第一章:引言1.数字电子技术是现代电子技术的基础,它是将模拟电子技术应用到数字系统中的学科。

数字电子技术的发展对计算机技术、通信技术等领域起到了重要的推动作用。

2.数字电子技术的基本概念包括数字信号、模拟信号、信号采样、量化、编码等。

3.数字电子技术的应用广泛,涵盖数字计算机、数字通信、数字音频、数字视频等多个领域。

第二章:数字逻辑基础1.逻辑代数是数字电子技术的基础,它包括逻辑运算、逻辑表达式、逻辑函数等概念。

2.逻辑代数的基本运算包括与运算、或运算、非运算等。

3.逻辑函数可以用真值表、卡诺图等形式表示。

4.数字逻辑电路是由逻辑门组成的,常见的逻辑门有与门、或门、非门等。

5.在数字逻辑电路中,还有多种逻辑门的组合形式,如与或非门、与非门等。

第三章:组合逻辑电路1.组合逻辑电路是由多个逻辑门组成的电路,逻辑门的输入和输出之间没有时钟信号的约束。

2.组合逻辑电路的设计过程包括确定所需逻辑关系、选择合适的逻辑门、进行逻辑门的连线等。

3.组合逻辑电路常见的应用有加法器、减法器、译码器、多路选择器等。

4.确定组合逻辑电路的最小项和最大项是一种常用的设计方法。

5.组合逻辑电路可以用Karnaugh图来进行化简和优化。

第四章:时序逻辑电路1.时序逻辑电路是由组合逻辑电路和触发器组成的电路,触发器引入了时钟信号来控制电路的状态。

2.触发器的种类有RS触发器、D触发器、JK触发器等。

3.时序逻辑电路中常见的电路有时钟发生器、计数器、寄存器等。

4.时序逻辑电路在数字系统中起到了重要的作用,可以实现状态的存储和传输。

5.时序逻辑电路的设计需要考虑时序条件、逻辑功能、触发器的选择等因素。

第五章:数字系统的设计1.数字系统的设计包括功能设计和硬件设计两个方面。

2.功能设计是根据系统的需求,确定系统所完成的功能和算法。

3.硬件设计是根据功能设计,选择合适的逻辑门、触发器等器件,进行电路图的设计。

数字电子技术基础第五版(阎石)第1章绪论习题答案

5.C 6.B 7. D

补充习题:

8.设n>=10,下面程序段的时间复杂度是( for(i=10; i<n; i++) )。

{

j=k=0; while(j+k<=i) if (j>k) k++; else j++;

B)O(n) C)O(nlog2n) D)O(n2)

} A)O(log2n)

9.计算机算法是指( )。 A)计算方法 B)排序方法 C)调度方法 D)解决问题的有限运算序列 8.D 9.D

补充习题:语句频度与时间复杂度

5. 在下面的程序段中,对x的赋值语句的频度为: n(n+1)(n+2)/6 O(n3) for(i= 1;i<=n; i++) for(j=1;j<=i;j++) n n for (k=1;k<=j; k++) 1 1 x=x+1; i1 j i 6. 已知如下程序段,则各语句的频度为: n n n for(i= n;i>=1; i- -) //语句1 n+1 1 1 { x=x+1; //语句2 n i1 j i i1 for(j= n;j>=i;j--) //语句3 n(n+3)/2 n (n i 1) n y=y+1; //语句4 n(n+1)/2 i1 }

习题1.2:

r1={(p1,p2),(p3,p4),(p5,p6),(p7,p8)} r2={(p1,p2),(p1,p3),(p1,p4),(p2,p3), (p2,p4),(p3,p4),(p5,p6),(p5,p7), (p5,p8),(p6,p7),(p6,p8),(p7,p8)}

数电第五版(阎石)第五章课后习题与答案

【题5.9】 若主从结构SR触发器的CLK,S,R, 各输入端电压波 形如图P5.9所示, =1,试画出Q,Q’ 端对应的电压波形。

解:根据SR触发器逻辑功能的定义及脉冲触发方式的动作特 点,即可画出Q,Q’的电压波形,如图A5.9所示。

【题5.11】已知脉冲触发JK触发器输入端J,K和CLK的电压波 形如图P5.11所示,试画出Q,Q’端对应的电压波形。设触发器 的初始状态为Q=0.

解:根据SR触发器逻辑功能的定义和脉冲触发方式的动作特 点(主从结构触发器属于脉冲触发方式),即可画出如图 A5.7所示的输出电压波形图。

【题5.8】 在脉冲触发SR触发器电路中,若S,R,CLK 端的电压 波形如图P5.8所示,试画出Q,Q’端对应的电压波形。假定触 发器的初始状态为Q=0.

解:根据SR触发器逻辑功能的定义及脉冲触发方式的动作特 点,即可画出图A5.8中Q和Q’的电压波形。

【题5.14】已知维持阻塞结构D触发器各输入端的电 压波形如图P5.14所示,试画出Q,Q’端对应的电压波形。

解:根据D触发器逻辑功能的定义及维持阻塞结构所具有的 边沿触发方式,即可画出Q和Q’的电压波形如图A5.14。

【题5.15】已知CMOS边沿触发方式JK触发器各输入端 的电压波形如图P5.15所示,试画出Q,Q式的动作特 点,画出的Q,Q’ 端电压波形如图A5.15。

【题5.18】设图P5.18中各触发器的初始状态皆为Q=0,试画 出在CLK信号连续作用下各触发器输出端的电压波形

解:根据每个触发器的逻辑功能和触发方式,画出输出端Q 的电压波形,如图A5.18。

解:见图A5.4.

【题5.5】 在图P5.5电路中,若CLK,S,R的电压波形如图中所 示,试画出Q和Q’端与之对应的电压波形。假定触发器的初 始状态为Q=0.

数电第五版(阎石)第三章课后习题及答案

习题三答案-计算题

1

计算题1答案:Y=AB'C+A'BC'+AB'C'+ABC

逻辑函数的化简

2

3

通过利用逻辑代数的基本定律,将给定的逻辑函 数进行化简,得到Y=AB'C+A'BC'+AB'C'+ABC。

04

习题四答案

习题四答案-选择题

选择题1答案:B 选择题3答案:A

选择题2答案:D 选择题4答案:C

习题一答案-计算题

计算题1答案:8。

计算题3答案:101000。

计算题2答案:1010。

02

习题二答案

习题二答案-选择题

01

选择题1答案:CD

02

选择题2答案:ABD

03

选择题3答案:ABC

04

选择题4答案:AB

习题二答案-填空题

01

02

03

04

填空题1答案:正逻辑; 负逻辑

填空题2答案:正逻辑; 负逻辑

03

习题三答案

习题三答案-选择题

在此添加您的文本17字

选择题1答案:C

在此添加您的文本16字

逻辑代数的基本运算规则

在此添加您的文本16字

选项C是逻辑代数的基本运算规则之一,即A+B=B+A,表 示逻辑加法满足交换律。

在此添加您的文本16字

选择题2答案:B

在此添加您的文本16字

逻辑代数的吸收律

在此添加您的文本16字

感谢您的观看

THANKS

计算题3答案

计算题4答案

Y=(A'B+AB')'+BC'=A'B'+AB'+B'C'+A'C'= Y1; Y2=(A+B)(A'+B')+(B+C)(B'+C')=AA'+AB' +BA'+BB'+BC'+CC'=Y3

数电第五版阎石课后习题及答案

学习要点: 1、不同电路结构触发器的动作 特点; 2、不同逻辑功能触发器的特性;

1

【题5.1】 画出图P5.1由与 的电压波形如图中所示。 解:见图A5.1.

2020/2/11

2

2020/2/11

3

【题5.4】图P5.4所示为一个防抖动输出的开关电路。当拨动 开关S时,由于开关触点接通瞬间发生振颤 , 和 的电压波 形如图中所示,试画出Q,Q'端对应的电压波形。

从高电平跳变成低电平以后电路的工作过程与上述过 程类似。这样就得到了图A5.20的 电压波形。

2020/2/11

25

【题5.21】 在图P5.21所示的主从JK触发器电路中,CLK 和 A 的电压波形如图中所示,试画出 Q 端对应的电压波形。设触 发器的初始状态为 Q = 0.

2020/2/11

26

利用这个电路可以监视在CLK=1期间A端是否有高电平信号 输入。如果A端有高电平输入信号,则Q端给出一个正脉冲; 如果A端没有输入信号,则Q端始终为0.

2020/2/11

27

2020/2/11

4

解:见图A5.4.

2020/2/11

5

【题5.5】 在图P5.5电路中,若CLK,S,R的电压波形如图中所 示,试画出Q和Q'端与之对应的电压波形。假定触发器的初 始状态为Q=0.

2020/2/11

6

解:见图A5.5.

2020/2/11

7

【题5.7】若主从结构SR触发器各输入端的电压波形如图P5.7 中所给出,试画出Q,Q'端对应的电压波形。设触发器的初始 状态为Q=0.

【题5.15】已知CMOS边沿触发方式 JK触发器各输入端 的电压波形如图 P5.15所示,试画出Q,Q'端对应的电压 波形。

精选数电第五版阎石课后习题及答案

? 0.68k?

故????的取值范围应为:

R 0.68k? ? L ? 4.29k?

2020/2/8

30

【题3.29】试说明下列各种门电路哪些可以将输出端并联使 用(输入端的状态不一定相同): (1)具有推拉式输出级的TTL电路; (2)TTL电路的OC门; (3)TTL电路的三态输出门; (4)互补输出结构的CMOS门; (5)CMOS电路的OD门; (6) CMOS电路三态输出门。 解:(1)、(4)不可; (2)、(3)、(5)、(6)可以

用电表使用5V量程,内阻为20KΩ/V。

解:这时相当于??12 端经过一个100KΩ的电阻接地。假定与非 门输入端多发射极三极管每个发射结的导通压降为0.7V,则有

(1)??12 ≈ 1.4V (3)??12 ≈ 1.4V

(2) ??12 ≈ 0.2V (4) ??12 ≈ 0V

(5) ??12 ≈ 1.4V

解:在满足V OL ? 0.4V 的条件下,求得

可驱动的负载门数目为:

NL

?

IOL (max) I IL

?

16 1.6

? 10

在满足V OH ? 3.2V 的条件下,求得可

驱动的负载门数目为:

NH

?

1 IOH (max) 2 IIH

?

1 0.4 ? 103 ? 5 2 40

故最多驱动5个与非门

2020/2/8

电平满足V OH

?

V 3.2V , OL

?

0.4V

。与非门的输入电流为?????≤?

I V I -1.6mA, IH

?

40? A。 OL

?

0.4V

时输出电流最大值为

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2020/2/11

24

解:当 =0 ,Q=0时,异或门的输出 等于0. 变为高电平以 后, 也变成高电平。因为 也是触发器的时钟输入端,所以 经过触发器的延迟时间后,Q端被置为1状态;再经过异或门 的传输延迟时间, 回到低电平。因此, 高电平持续时间等 于触发器的传输延迟时间与异或门的传输延迟时间之和。

2020/2/11

10

解:根据SR触发器逻辑功能的定义及脉冲触发方式的动作特 点,即可画出图A5.8中Q和Q'的电压波形。

2020/2/11

ห้องสมุดไป่ตู้

11

【题5.9】 若主从结构SR触发器的CLK,S,R, 各输入端电压波 形如图P5.9所示, =1,试画出Q,Q' 端对应的电压波形。

2020/2/11

12

利用这个电路可以监视在CLK=1期间A端是否有高电平信号 输入。如果A端有高电平输入信号,则Q端给出一个正脉冲; 如果A端没有输入信号,则Q端始终为0.

2020/2/11

27

解:在CLK =1期间主从JK触发器的主触发器接收输入信号。 若此期间出现 A = 1 的信号,则主从触发器被置1,在CLK变 为低电平后,从触发器随之被置1,使输出为Q=1.而当CLK回

到高电平以后与非门的输出变为低电平,于是又通过异步置 0 端R将触发器置0.这样我们就得到了图A5.21的波形图。

14

解:根据JK触发器逻辑功能的定义及脉冲触发的动作特点, 画出的Q,Q'端电压波形如图A5.11。

2020/2/11

15

[题5.12] 若主从结构JK触发器CLK, , ,J,K端的电压波形如图 P5.12所示,试画出Q,Q'端对应的电压波形。

2020/2/11

16

解:根据JK触发器逻辑功能的定义及脉冲触发方式的动作特 点,画出的Q,Q' 端电压波形如图A5.12。

从高电平跳变成低电平以后电路的工作过程与上述过 程类似。这样就得到了图A5.20的 电压波形。

2020/2/11

25

【题5.21】 在图P5.21所示的主从JK触发器电路中,CLK 和 A 的电压波形如图中所示,试画出 Q 端对应的电压波形。设触 发器的初始状态为 Q = 0.

2020/2/11

26

2020/2/11

8

解:根据SR触发器逻辑功能的定义和脉冲触发方式的动作特 点(主从结构触发器属于脉冲触发方式),即可画出如图 A5.7所示的输出电压波形图。

2020/2/11

9

【题5.8】 在脉冲触发SR触发器电路中,若S,R,CLK 端的电压 波形如图P5.8所示,试画出Q,Q'端对应的电压波形。假定触 发器的初始状态为Q=0.

【题5.15】已知CMOS边沿触发方式 JK触发器各输入端 的电压波形如图 P5.15所示,试画出Q,Q'端对应的电压 波形。

2020/2/11

20

解:根据JK触发器逻辑功能的定义和边沿触发方式的动作特 点,画出的Q,Q' 端电压波形如图A5.15。

2020/2/11

21

【题5.18】设图P5.18中各触发器的初始状态皆为Q=0,试画 出在CLK信号连续作用下各触发器输出端的电压波形

2020/2/11

22

解:根据每个触发器的逻辑功能和触发方式,画出输出端Q 的电压波形,如图A5.18。

2020/2/11

23

[题5.20] 在图P5.20电路中已知输入信号 的电压波形如图所 示,试画出与之对应的输出电压 的波形。触发器为维持 阻塞结构,初始状态为Q=0 。(提示:应考虑触发器和异或 门的传输延迟时间。)

2020/2/11

17

【题5.14】已知维持阻塞结构 D触发器各输入端的电 压波形如图 P5.14 所示,试画出 Q ,Q '端对应的电压波形。

2020/2/11

18

解:根据D触发器逻辑功能的定义及维持阻塞结构所具有的 边沿触发方式,即可画出Q和Q'的电压波形如图A5.14。

2020/2/11

19

2020/2/11

4

解:见图A5.4.

2020/2/11

5

【题5.5】 在图P5.5电路中,若CLK,S,R的电压波形如图中所 示,试画出Q和Q'端与之对应的电压波形。假定触发器的初 始状态为Q=0.

2020/2/11

6

解:见图A5.5.

2020/2/11

7

【题5.7】若主从结构SR触发器各输入端的电压波形如图P5.7 中所给出,试画出Q,Q'端对应的电压波形。设触发器的初始 状态为Q=0.

解:根据SR触发器逻辑功能的定义及脉冲触发方式的动作特 点,即可画出Q,Q'的电压波形,如图A5.9所示。

2020/2/11

13

【题5.11】已知脉冲触发JK触发器输入端J,K和CLK的电压波 形如图P5.11所示,试画出Q,Q'端对应的电压波形。设触发器 的初始状态为Q=0.

2020/2/11

第五章

学习要点: 1、不同电路结构触发器的动作 特点; 2、不同逻辑功能触发器的特性;

1

【题5.1】 画出图P5.1由与非门组成的SR锁存器输出端Q,Q'的 电压波形,输入端 , 的电压波形如图中所示。 解:见图A5.1.

2020/2/11

2

2020/2/11

3

【题5.4】图P5.4所示为一个防抖动输出的开关电路。当拨动 开关S时,由于开关触点接通瞬间发生振颤 , 和 的电压波 形如图中所示,试画出Q,Q'端对应的电压波形。