DC基本流程教程

DC综合教程

DC操作流程

1.在虚拟机中 打开终端

DC操作流程 2. 创建综合 环境 在终端输入: new_dc xxx

xxx为你想要创 建的文件夹的名 字

DC操作流程

3. 修改环境(参考Readme

文件)

a.修改filelist.tcl 添加通过验证的源代 码

DC操作流程

b.修改synopsys.sdc 添加综合约束

DC 工具简要入门

2012年秋

内容

• 1. 逻辑综合以及综合工具

Design Compile • 2.DC操作流程

• 3.现场演示

逻辑综合

• 将RTL代码转换为门级网表 的过程

逻辑综合

DC工具

• Design Compile是常用的综合 工具,在DC中,共有8中设计 实体 • 1、设计(Design):一种能 完成一定逻辑功能的电路。设 计中可以包含子设计

• 对于DC而言,通常要指定下面4种库 • 1、Target library 工艺库,由代工厂提供的和具体工艺 相关的工艺库 • 2、Link library 指定DC查找时所指定的目标,通常 也就是Target library

DC工具--指定参考库

• Synthetic library DC综合时将转化HDL代码为相应元 件时所参考的IP库。比如符号“+”, 通过IP库查找生成某类加法器。默认 使用自带的加法库。 • Symbol library 使用图形界面时,在原理图上绘制 与非门等标准单元的符号库

DC工具

• 2、单元(Cell):子设计的实例 • 3、参考(Reference):单元的参考对 象,即单元是参考的实例 • 4、端口(Port) • 5、管脚(Pin) • 6、线网(Net) • 7、时钟(Clock) • 8、库(Library):综合时用到的一组基 本单元的集合

DC入门实例详细教程

DC入门实例详细教程

1、课程介绍

编程入门使用DC,也称为“DC编程入门”,是一个全面的、实用的

和容易上手的入门课程,旨在帮助初学者快速学习DC和实际编程。

该课

程包括以下内容:基础知识介绍,DC软件开发环境介绍,DC编程语言介绍,DC编程实战,DC程序调试,DC应用开发,深入学习等。

2、编程入门DC基础知识介绍

DC基础知识介绍是了解DC编程的必要基础。

本章将介绍DC的基本

概念、编程环境,并在此基础上,介绍了DC编程的基本技术和工具,包括:编程语言介绍(C、C++、JavaScript、VBScript等)、编程环境设置、编程工具的选择等内容。

3、DC软件开发环境介绍

DC软件开发环境介绍指的是详细介绍DC的硬件和软件环境,这里主

要介绍了DC的系统软件安装、环境配置、编程环境设置、调试工具安装

和使用等内容。

4、DC编程语言介绍

DC编程语言介绍是指详细介绍了DC编程语言C++、JavaScript、VBScript等的基本知识,包括变量、数据类型、控制语句、循环语句、

函数等内容,同时还介绍了开发工具的使用,以及常见的错误分析等内容。

5、DC编程实战

DC编程实战是指在上述基础知识的基础上,对DC各种功能和功能配

置的具体应用。

Acrobat Pro DC基础知识教程

Acrobat Pro DC基础知识教程Adobe Acrobat Pro DC是一款功能强大的PDF编辑和管理工具。

本教程将为您提供关于Acrobat Pro DC的基础知识和使用技巧。

安装和启动安装完成后,您可以在计算机桌面上找到Acrobat Pro DC的快捷方式。

双击快捷方式,即可启动该软件。

基本界面Acrobat Pro DC的界面分为几个主要部分:1. 菜单栏:包含各种功能和操作选项。

2. 工具栏:快速访问常用工具和功能。

3. 侧边栏:提供更多选项和设置,如浏览器视图、缩略图、导航窗格等。

4. 文档窗口:显示当前打开的PDF文档。

打开和编辑文档要打开一个PDF文档,您可以使用菜单栏的“文件”选项,然后选择“打开”。

您还可以直接拖放PDF文件到Acrobat Pro DC中。

一旦打开了文档,您可以进行各种编辑操作,例如:- 添加文本:使用“添加文本”工具,单击文档中的位置,并开始键入。

- 插入图片:选择“插入”选项,然后选择要插入的图片文件。

- 修改文本格式:使用“文字属性”工具,选择文本并更改字体、大小、颜色等属性。

导出和共享文档Acrobat Pro DC还提供了几种导出和共享文档的选项:- 导出为PDF:选择“文件”->“另存为”,选择PDF格式,并指定保存路径。

- 导出为其他格式:选择“文件”->“另存为其他格式”,选择所需的格式,并进行相应设置。

高级功能除了基本编辑功能外,Acrobat Pro DC还具有许多高级功能,例如:- 添加电子签名:选择“工具”->“电子签名”,然后按照提示添加和验证签名。

- 创建表单:使用“表单”工具,将文档中的文本字段转换为可填写表单。

- OCR识别:选择“工具”->“文本识别”,然后选择识别语言并开始识别文本。

总结本教程提供了关于Acrobat Pro DC的基础知识和使用技巧,涵盖了安装和启动、界面介绍、文档打开和编辑、导出和共享文档以及高级功能等方面的内容。

dc使用教程

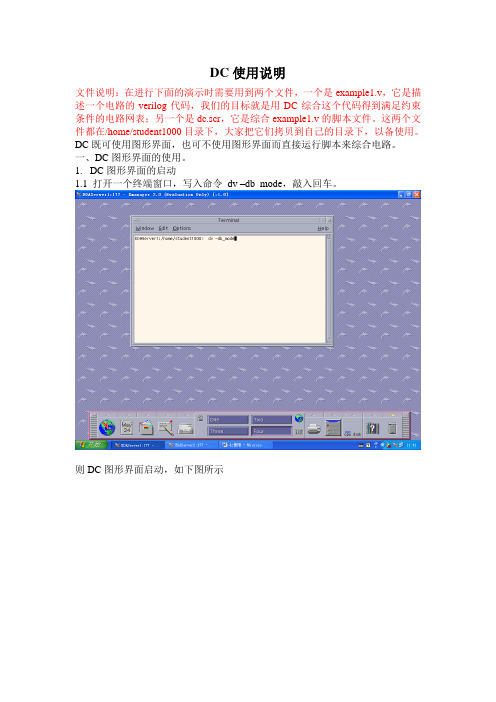

d c使用教程-CAL-FENGHAI.-(YICAI)-Company One1DC使用说明文件说明:在进行下面的演示时需要用到两个文件,一个是,它是描述一个电路的verilog代码,我们的目标就是用DC综合这个代码得到满足约束条件的电路网表;另一个是,它是综合的脚本文件。

这两个文件都在/home/student1000目录下,大家把它们拷贝到自己的目录下,以备使用。

DC既可使用图形界面,也可不使用图形界面而直接运行脚本来综合电路。

一、DC图形界面的使用。

1.DC图形界面的启动打开一个终端窗口,写入命令 dv –db_mode,敲入回车。

则DC图形界面启动,如下图所示红框处是DC的命令输入框,以下在图形界面上的操作都可以在命令输入框中输入相应的命令来完成。

选择Help-----Man Pages可以查看DC的联机帮助。

相应指令:man。

例:man man表示查看man命令的帮助。

man create_clock表示查看creat_clock命令的帮助。

2.设置库文件选择File----Setup需要设置以下库文件,如下图。

相应指令:set search_path [list /tools/lib/smic25/feview_s/version1/STD/Synopsys \ /tools/lib/smic25/feview_s/version1/STD/Symbol/synopsys]set target_library { }set link_library { }set symbol_library { }点OK,设置完成。

3.读入verilog文件选择File---Read在打开文件对话框中选中要打开的文件,在这里我们选中文件。

在Log框中出现successfully字样表明读入文件成功。

相应命令:read_file点击红色箭头所指的按钮可以查看该电路的symbol图。

4.设置约束条件4.1设置时钟约束在symbol图上选中clk端口选择Attributes-----Specify Clock出来设置时钟约束的对话框,按下图设置,给时钟取名为clock,周期20ns,上升沿0ns,下降沿10ns。

ubuntu中DC安装详细教程

说明:本教程在ubuntu10.04之后,一直到ubuntu11.10上验证成功,在之前的版本应该也以。

首先表示歉意。

由于之前发的那个教程在破解的地方少截了一张图,部分人无法找到文件,造成无法破解,对那些已经下载了的朋友造成误导,表示歉意。

为了能使更多的人正确破解并应用这个强大的软件,所以在此重新安装一次,并编写教程,顺便改正上次其他的几个小错误。

1、准备安装文件(setup文件夹),内容如下图:2、在主目录下建立soft文件夹,并在soft文件夹下建立dc2012,在dc2012下新建dc、scl 文件夹,同时把setup文件夹也拷贝到soft文件夹下(本教程中,主目录为lbq文件夹,在上步骤中,已经把setup文件夹拷贝到soft文件夹下了)。

3、由于早期的ubuntu默认没有安装csh,需要先打开终端,运行sudo apt-get install csh,11.04版之后的好像都默认安装了。

然后在ubuntu软件中心中搜索wine,并安装成功(在后面的破解中需要用到wine)。

4、开始安装。

如下图,按照图中所示路径,进入到该文件夹中,右键单击setup.sh,点击“属性”,打开“权限”标签,选中“允许以程序执行文件(E)”。

5、右键单击setup.sh,点击“打开”,如下图6、点击“运行”,如下图:7、点击“Start”,如下图:8、选择所要安装软件dc的原程序路径。

点击“Browse...”,选择路径如下图所示:9、点击“Done”,如下图所示:10、一路“Next”,遇到的几处选择如下几幅图所示,紫色表示选择。

11、直到出现选择所要安装软件dc的保存路径时,选择安装在dc2012下的“dc”文件夹中,如下图:12、点击“Next”,如下图,单击“Install”开始安装。

13、dc安装结束后,不要退出。

出现下图所示内容14、点击“Install Another Product”。

如下图,15、然后一路“Back”,直到出现下图为止。

黑骑士电动车dc安装教程

黑骑士电动车dc安装教程黑骑士电动车DC安装教程一、前言随着环保意识的提高和交通方式的多元化,电动车作为一种环保、经济、便捷的交通工具受到了越来越多人的喜爱。

而黑骑士电动车DC则是市场上一款备受欢迎的电动车品牌。

本文将为大家介绍如何正确安装黑骑士电动车DC,帮助大家更好地使用这款电动车。

二、安装前准备在开始安装之前,我们需要准备一些工具和材料,确保安装顺利进行。

以下是所需准备的工具和材料:1. 扳手和扭力扳手:用于拆卸和安装螺丝。

2. 电池:黑骑士电动车DC的电池,确保电量充足。

3. 充电器:用于给电池充电。

4. 电动车安装配件包:包括电动车车架、车轮、车把等配件。

三、安装步骤1. 拆卸原有车架:使用扳手和扭力扳手将原有车架上的螺丝拆卸下来。

注意保持好原有的螺丝,以备后续安装使用。

2. 安装新车架:将黑骑士电动车DC配件包中的车架取出,根据说明书上的示意图,将车架安装到原有车架的位置上。

使用扭力扳手逐个拧紧螺丝,确保车架稳固。

3. 安装车轮:根据配件包中的车轮安装说明,将车轮安装到车架上。

使用扭力扳手逐个拧紧螺丝,确保车轮安装牢固。

4. 安装车把:根据配件包中的车把安装说明,将车把安装到车架上。

使用扭力扳手逐个拧紧螺丝,确保车把安装稳固。

5. 连接电池和电动车:根据黑骑士电动车DC的说明书,将电池正确连接到电动车上。

确保连接牢固,电池能够正常供电。

6. 充电:将充电器插入电动车上的充电插口,将充电器连接到电源上进行充电。

根据电动车说明书上的充电时间,充电完毕后拔掉充电器。

7. 安全检查:安装完成后,要进行一次安全检查,确保所有零部件都安装牢固,并且电动车能够正常启动和行驶。

四、安全注意事项1. 在安装过程中,务必确保电动车处于停止状态,并且拔掉电池的连接线,以免发生意外。

2. 在拆卸和安装螺丝时,要使用合适的扳手和扭力扳手,以免损坏螺丝和零部件。

3. 在安装过程中,如果遇到不清楚的地方,可以查阅黑骑士电动车DC的说明书,或者咨询专业人士的帮助。

ubuntu中DC安装详细教程(修改版)

说明:本教程在ubuntu10.04 之后,一直到ubuntu11.10 上验证成功,在之前的版本应该也以。

首先表示歉意。

由于之前发的那个教程在破解的地方少截了一张图,部分人无法找到文件,造成无法破解,对那些已经下载了的朋友造成误导,表示歉意。

为了能使更多的人正确破解并应用这个强大的软件,所以在此重新安装一次,并编写教程,顺便改正上次其他的几个小错误。

1、准备安装文件(setup 文件夹),内容如下图:2、在主目录下建立soft 文件夹,并在soft 文件夹下建立dc2012,在dc2012 下新建dc、scl 文件夹,同时把setup 文件夹也拷贝到soft 文件夹下(本教程中,主目录为lbq 文件夹,在上步骤中,已经把setup 文件夹拷贝到soft 文件夹下了)。

3、由于早期的ubuntu 默认没有安装csh,需要先打开终端,运行sudo apt-get installcsh,11.04版之后的好像都默认安装了。

然后在ubuntu 软件中心中搜索wine,并安装成功(在后面的破解中需要用到wine)。

4、开始安装。

如下图,按照图中所示路径,进入到该文件夹中,右键单击setup.sh,“”点击属性,打开选中允许以程序执行文件(E)”。

权限标签, ““”5、右键单击setup.sh,“”点击打开,如下图6“”、点击运行,如下图:7“、点击Start”,如下图:8、选择所要安装软件dc “的原程序路径。

点击Browse...”,选择路径如下图所示:9“、点击Done”,如下图所示:10“、一路Next”,遇到的几处选择如下几幅图所示,紫色表示选择。

11、直到出现选择所要安装软件dc 的保存路径时,选择安装在dc2012“下的dc”文件夹中,如下图:12“如下图,单击Install ”开始安装。

、点击Next”,“13、dc 安装结束后,不要退出。

出现下图所示内容14“、点击Install Another Product”。

综合工具-DesignCompiler学习教程

综合⼯具-DesignCompiler学习教程Design Compiler 13讲中的部分内容:1、逻辑综合的概述DC⼯作流程分为三步2、DC的三种启动⽅式GUIdc_shellBatch mode3、DC-Tcl语⾔的基本结构1、⾼层次设计的流程图2、DC在设计流程中的位置3、使⽤DC进⾏基本的逻辑综合的流程图与相应的命令①准备设计⽂件②指定库⽂件③读⼊设计④定义设计环境⑤设置设计约束⑥选择编译策略⑦编译⑧分析及解决设计中存在的问题⑨存储设计数据(1)启动环境配置简述(2).synopsys_dc.setup配置⽂件的书写(3).synopsys_dc.setup的讲解(1)标准单元库①概述⼀个ASIC综合库包括如下信息:·⼀系列单元(包括单元的引脚)。

·每个单元的⾯积(在深亚微⽶中,⼀般⽤平⽅微⽶表⽰,在亚微⽶⼯艺下,⼀般⽤门来称呼,⾄于具体的单位,可以咨询半导体制造商)。

·每个输出引脚的逻辑功能。

·每个输⼊到输出的传递延时,输出到输出的传递延时;inout到输出的传递延时。

②内容与结构Synopsys的⼯艺库是⼀个.lib⽂件,经过LC编译后,产⽣.db⽂件。

⼯艺库⽂件主要包括如下信息:·单元(cell)(的信息):(主要有)功能、时间(包括时序器件的约束,如建⽴和保持)、⾯积(⾯积的单位不在⾥⾯定义,可按照规律理解,⼀般询问半导体⼚商)、功耗、测试等。

·连线负载模型(wire load models):电阻、电容、⾯积。

·⼯作环境/条件(Operating conditions):制程(process)(电压和温度的⽐例因数k,表⽰不同的环境之间,各参数缩放的⽐例)·设计规则约束(Design ):最⼤最⼩电容、最⼤最⼩转换时间、最⼤最⼩扇出。

⼯艺库的结构如下所⽰:(2)DC的设计对象在了解了综合库之后,下⾯介绍⼀下DC的设计对象,虽然这个设计对象相对于综合库没有那么重要,但是还是要了解⼀下的。

(2024年)CADWorx培训教程

CADWorx培训教程•CADWorx 软件概述•CADWorx 基本操作与界面介绍•绘图工具与编辑技巧•三维建模与渲染技术•管道设计模块详解•设备布置与钢结构设计•电气仪表自动化集成应用目录01 CADWorx软件概述软件背景及发展历程初始阶段CADWorx起源于20世纪90年代,最初是一个为工程设计领域提供2D绘图功能的软件。

发展阶段随着技术的进步和用户需求的变化,CADWorx逐渐增加了3D建模、管道设计、设备布置等高级功能,成为一款综合性的工程设计软件。

成熟阶段近年来,CADWorx不断完善自身功能,同时积极与其他工程设计软件进行集成,提高了工作效率和设计质量。

CADWorx 具备强大的3D 建模能力,可以快速创建复杂的工程模型,提高设计效率。

强大的3D 建模功能CADWorx 提供全面的管道设计工具,支持各种类型的管道、阀门、法兰等元件的建模和编辑,满足管道设计的多样化需求。

丰富的管道设计工具CADWorx 可以自动进行设备布置和优化,减少人工干预,提高设计准确性和效率。

智能化的设备布置CADWorx 支持多种文件格式和数据交换标准,可以与其他工程设计软件进行无缝集成,实现数据共享和协同工作。

良好的兼容性CADWorx 软件特点与优势CADWorx 在石油天然气行业得到广泛应用,用于管道设计、设备布置、工艺流程模拟等方面。

石油天然气行业除了上述行业外,CADWorx 还可以应用于水处理、制药、造纸等多个领域,为工程设计提供全面的解决方案。

其他行业可以提供全面的设计CADWorx 可以提高应用领域与行业现状02 CADWorx基本操作与界面介绍启动与退出CADWorx启动CADWorx通过开始菜单或桌面快捷方式启动CADWorx软件。

退出CADWorx在软件界面中选择“文件”菜单下的“退出”选项,或者使用快捷键Alt+F4退出程序。

界面组成及功能区域划分标题栏显示当前文档的名称和CADWorx软件的版本信息。

synopsys dc中文教程(比较详细)

ASIC design flow

Initial Setup :建立设计环境,技术库文件及其它设计环境设置。 DC .synopsys_dc.setup 文件 company =―zte corporation‖; designer =―name‖; technology=―0.25 micron‖ search_path=search_path+{―.‖ ―/usr/golden/library/std_cells‖\ ―/usr/golden /library/pads‖} target_library ={std_cells_lib.db} link_library ={―*‖,std_cells_lib.db,pad_lib.db} symbol_library ={std_cells.sdb,pad_lib.sdb}

ASIC design flow

SDF generation,pre_layout的SDF文件,用于pre_layout timing仿真,同时还需 提供时序约束文件(SDF格式)给layout tool做布局布线。script文件如下:

active_design=tap_controller read active_design current_design active_design link Create_clock –period 33 –waveform {0 16.5} tck Set_dont_touch_network {tck trst} set_clock_skew –delay 2.0 –minus_uncertainty 3.0 tck set_driving_cell –cell BUFF1X –pin Z all_inputs() set_drive 0 {tck trst} set_input_delay 20.0 –clock tck –max all_inputs() set_output_delay 10.0 –clock tck –max all_outputs() write_timing –format sdf-v2.1 \ -output active_design+‖.sdf‖ write_constraints –format sdf –cover_design\ -output constraints.sdf

DC基本流程教程

DC基本流程教程直流(DC)是电流方向始终不变的电流。

与交流(AC)不同,直流流向电流始终是单向的。

直流电源是电子设备中常见的一种电源,因此了解直流基本流程对于电子工程师和电子爱好者来说是非常重要的。

下面将介绍直流基本流程的教程,以帮助初学者快速了解和掌握。

第一步:了解电源在接触直流之前,首先需要了解电源的工作原理。

直流电源一般由电池或者直流电源适配器提供。

电池可以提供相对较低的电压,适配器则可以提供更高的电压和电流。

根据实际需求,选择适合的电源。

第二步:了解电路了解电路是理解直流基本流程的关键。

电路由电源、负载和导线组成。

电源提供电流,负载消耗电流,导线将电流传输到负载。

第三步:连接电路将电源、负载和导线连接在一起。

使用插头和插座连接电源和负载,使用导线将两者连接起来。

确保连接牢固和安全,避免电路短路或者导线断裂。

第四步:检查电路在通电之前,要确保电路连接正确无误。

检查插头和插座的连接是否紧固,导线是否有损伤,负载是否正确连接等。

这样可以避免因电路问题造成的意外损坏或者电击等情况。

第五步:通电将电源插入插座,开启电源。

在此之前,确保电源开关在关闭状态下。

通电后,电源开始提供电流,通过导线到达负载。

第六步:负载工作当电流到达负载时,负载开始工作。

负载可以是任何需要电流供应的设备,如灯泡、电动机等。

负载根据电流的大小和电源电压的确定性来工作。

第七步:监测电流在开启电源时,可以通过电流表或者多用途测试仪来监测电流的大小。

这有助于了解电流是否在设备的额定范围内,以及是否存在异常情况。

第八步:关闭电源当不再需要直流电流时,应该关闭电源。

首先将负载断开,然后关闭电源开关,最后拔掉电源插头。

这样可以避免未使用设备浪费电能或者发生电源故障的风险。

总结以上就是直流基本流程的教程。

通过了解电源、电路连接、负载工作和电流监测等步骤,可以帮助初学者理解和掌握直流流程的基本知识。

在实际应用中,可以根据具体需求来调整和优化电源和电路,以获得更好的性能和效果。

浙大中控DCS基础版教程(2024)

I/O模块类型及作用

2024/1/29

模拟量输入模块

将现场模拟量信号转换为数字信号,供控 制器处理。

模拟量输出模块

将控制器输出的数字信号转换为模拟量信 号,驱动现场执行机构。

开关量输入模块

接收现场开关量信号,将信号状态传输给 控制器。

开关量输出模块

根据控制器指令,输出开关量信号控制现 场设备。

9

控制器区

显示与控制器相关的信息和操作,如控制器状态、变量监控等。

2024/1/29

19

主界面布局及功能区域划分

2024/1/29

图形组态区

用于创建和编辑DCS系统的图形界面 ,包括流程图、趋势图、报警窗口等 。

脚本编程区

提供脚本编程环境,支持用户编写自 定义脚本实现复杂控制逻辑。

20

常用操作命令和快捷键使用

工具栏

位于菜单栏下方,提供常用操作 命令的快捷按钮。

17

主界面布局及功能区域划分

工作区

占据界面中心区域,用于显示和编辑DCS系统的各种元素。

状态栏

位于界面底部,显示当前登录用户、系统时间、版本号等信息。

2024/1/29

18

主界面布局及功能区域划分

工程管理区

用于管理DCS工程文件,包括新建、打开、保存、另存为等操作。

组态软件使用

熟悉浙大中控DCS组态软件的操作界面和基本功能,掌握 建立工程、绘制流程图、配置IO点、编写控制逻辑等步骤 。

控制策略组态

在组态软件中,根据控制策略的要求,配置相应的控制模 块、设定参数、连接信号等,完成控制策略的组态。

36

回路调试技巧和经验分享

调试前准备

检查硬件连接、确认IO点配置正确、 确保控制策略组态无误。

【最新推荐】Acrobat DC Pro 下载和序列号及安装激活图文教程-范文模板 (4页)

本文部分内容来自网络整理,本司不为其真实性负责,如有异议或侵权请及时联系,本司将立即删除!== 本文为word格式,下载后可方便编辑和修改! ==Acrobat DC Pro 下载和序列号及安装激活图文教程Acrobat DC Pro 下载和序列号及安装激活图文教程Acrobat DC Pro 下载和序列号及安装激活图文教程Acrobat DC 官方版 + 便携版 + 注册机及产品介绍一、安装包下载Adobe Acrobat DC Pro (Perpetual) –永久版本/AdobeProducts/APRO/Solstice_Acrobat201X/win32/Acrobat_201X_Web_WWMUI .exeAdobe Acrobat DC Pro (Subscription) –连续版本/AdobeProducts/APRO/15/win32/Acrobat_DC_Web_WWMUI.exe永久版本,只能获得补丁,不能获取功能更新。

(以下安装以“永久版本”为例,本人亲测可以脱机激活)连续版本,也就是订阅版,可以获得功能更新。

(“连续版本”能否脱机激活,没有测试,请诸位自测。

)二、断网安装1、注意整个安装和激活的过程中一定要断网,禁用网卡或拔掉网线。

2、由于目前还没有发布针对Adobe Acrobat DC的专用注册机,所以仍用适用Acrobat XI的Adobe Acrobat XI的专用注册机(xf-aarpxi.exe)算安装序列号。

(不建议用Adobe破解补丁!)以下为通用序列号:1118-1583-7979-9484-4887-4319,输入的序列号要记住,因为后面脱机激活还要用到。

3、如果需要,可以选择“自定义”安装,“自定义安装”时组件和安装路径都可以更改。

注意安装过程中不要运行Office程序。

三、脱机激活1、安装完毕首次运行软件,提醒你需要使用Adobe ID登录才能激活本软件。

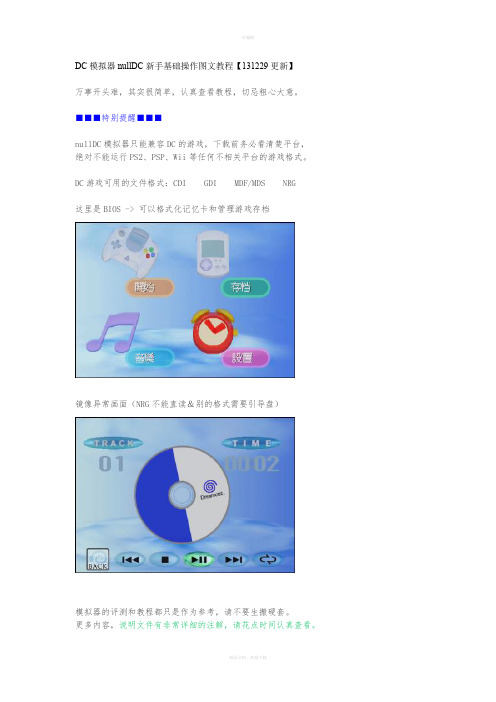

DC模拟器nullDC新手基础操作图文教程

DC模拟器nullDC新手基础操作图文教程【131229更新】万事开头难,其实很简单,认真查看教程,切忌粗心大意。

■■■特别提醒■■■nullDC模拟器只能兼容DC的游戏,下载前务必看清楚平台,绝对不能运行PS2、PSP、Wii等任何不相关平台的游戏格式。

DC游戏可用的文件格式:CDI GDI MDF/MDS NRG这里是BIOS -> 可以格式化记忆卡和管理游戏存档镜像异常画面(NRG不能直读&别的格式需要引导盘)模拟器的评测和教程都只是作为参考,请不要生搬硬套。

更多内容,说明文件有非常详细的注解,请花点时间认真查看。

■■■战前准备■■■①游戏镜像格式转换工具UltraISO下载:bbs。

/viewthread。

php?tid=91761②推荐使用的虚拟光驱Alcohol 52%下载:trial。

alcohol-soft。

com③还原NRG为DC模拟器通用直读的CDI格式:yncxr,如果您要查看本帖隐藏内容请回复■■■使用说明■■■根据实际情况选择和使用插件图像选项的设定要灵活调节用虚拟光驱直接双击对应盘符然后通过Go菜单引导游戏即可可以直接在虚拟光驱右键加载镜像在UltraISO工具菜单转换镜像格式■■■直读说明■■■NRG格式是全球独家研制的优化镜像,体积超小,原版封装。

完美兼容模拟器和游戏机(刻录运行),实现免引导盘启动。

NRG优化镜像不能直读运行,建议先用UltraISO转换为Alcohol格式(MDF/MDS)即可;Alcohol格式会添加20MB~100MB左右的缓冲数据实现直读。

虚拟光驱建议使用 Alcohol 52% (Alcohol 120% 是收费版);使用虚拟光驱的时候,通过Tools菜单~光驱,双击载入了游戏镜像的盘符,然后正常引导游戏。

■■■疑难解答■■■Q:某些游戏中无法正常控制??A:部分游戏(如:罗德岛战记)需要用到类比或者数码的方向键来控制人物的移动、菜单选择等操作,均可在控制插件中设置;Q:提示引导信息缺失或不完整??A:可以尝试更换显示类型(VGA或TV)后再继续操作;Q:如何转换NRG格式为直读镜像??A:运行UltraISO软件,在工具菜单找到格式转换功能,输出格式选择Alcohol即可;Q:????A:……………….。

MAGMASOFT V4-HPDC教程第三章

734313578目录:3.1 网格概述3.2 均衡网格3.3 非均衡网格3.4 测试网格3.5生成网格3.6检查网格质量3.1 网格概述MAGMASOFT ®网格生成的结果都存储在二进制文件‘<projectname>.grd ’,‘<projectname>.bnd’和‘<projectname>.melem ’;如果您生成网格求解5 ,附加档案‘<projectname>.ngrd’将写入。

你的任务是设置参数,以确定质量的网格。

当您启动网格生成的几何数据文件中的‘<projectname>.geo’,这是一个先决条件,在网格生成前用预处理sheets储存的功能‘SAVE ALL AS 1’。

网格的注意方面¾在每个方向的坐标系中每个几何薄壁领域里至少应有三个单元。

如果没有三个单元,熔体流动不能正常模拟,可用后处理‘Mesh_Quality ’结果的帮助下显示面积薄壁单元(‘Thin walls’) 的质量(查看网格质量)。

内浇口(材料组20, ‘INGATE’)是特别重要的,该算法用于检测截面,当计算量内浇口长度时至少有三个单元。

¾在网格划分时,冲头沿长度最少有2层单元网格,而料饼沿长度最少有3层单元网格,这才能确保充型模拟是正确进行。

3.2 均衡网格输入网格的大约总数按回车确定,输入数值越大网格分得越细,模拟计算时间越长。

自动生成网格是把所有材料组平均分配网格。

计算网格是测试网格生成的数量退出生成网格自动生成网格是最常用的,也是最简单的。

标准网格这些参数可调整,以这些参数向同一个坐标轴均匀划分网格单元。

3.3非均衡网格z非均匀网格参数z优化网格为特定材料组z优化网格非均匀网格参数选择其中一个按钮更改网格参数,才可优化网格优化网格壁厚(wall thickness)¾此参数控制转换几何数据到网格生成。

2024版CADWORX入门级教程

•CADWORX软件概述•CADWORX基本操作与界面介绍•绘图基础命令与技巧•三维建模方法与实例分析•设备库管理与使用技巧•管线设计与布局优化策略•报表生成与输出功能介绍CADWORX软件概述CADWORX 起源与初期发展介绍CADWORX 软件的诞生背景,以及其在工程设计领域初期的发展情况。

技术革新与版本迭代阐述CADWORX 在技术创新、功能增强以及版本升级方面的主要历程。

行业认可与市场地位概述CADWORX 在工程设计行业中的认可度、市场占有率以及行业影响力。

软件背景及发展历程030201CADWORX软件特点与优势强大的三维建模能力提供丰富的三维建模工具,支持快速、准确地创建各种设备和管道模型。

ABDC石油化工行业应用介绍CADWORX 在石油化工行业中的广泛应用,包括炼油、化工、天然气等领域。

电力行业应用阐述CADWORX 在电力行业中的应用情况,包括火力发电、核电、风电等领域。

制药行业应用概述CADWORX 在制药行业中的应用,包括原料药生产、制剂生产等领域。

其他行业应用及发展趋势介绍CADWORX 在其他行业中的应用情况以及未来发展趋势。

应用领域与行业现状CADWORX基本操作与界面介绍启动与退出CADWORX启动CADWORX双击桌面上的CADWORX图标,或者在开始菜单中找到CADWORX程序并单击启动。

退出CADWORX在CADWORX界面中选择“文件”菜单,然后单击“退出”选项,或者使用快捷键“Alt+F4”退出程序。

界面布局及功能区域划分标题栏显示当前打开的文档名称和CADWORX程序图标。

菜单栏包含文件、编辑、视图、插入、格式、工具、窗口和帮助等菜单项,用于执行各种命令和操作。

工具栏提供常用命令的快捷方式,如保存、撤销、重做、选择、缩放等。

绘图区域用于显示和编辑CAD图形的区域,可以进行缩放、平移、旋转等操作。

命令行窗口显示当前执行的命令和提示信息,可以输入命令并执行。

DC基本流程教程

4

Invoke Design Vision

source synthesis.csh mkdir xxxx cd xxxx

複製 “.synopsys_dc.setup” 到你目前的目錄xxxx

5

Invoke Design Vision (.cont)

design_vision& (or dv & )

Error (只要有任何的Error,合成即會失敗) Warning (部分Warning可忽略,但Multiple Design Instance不可忽略)

module REG4 (q,qn,data,clk,clrn); output [3:0] q, qn; input [3:0] data; input clk, clrn; DFF d0 (q[0],qn[0],data[0],clk,clrn); DFF d1 (q[1],qn[1],data[1],clk,clrn); DFF d2 (q[2],qn[2],data[2],clk,clrn); DFF d3 (q[3],qn[3],data[3],clk,clrn); endmodule

27

Change Naming Rule

在top_setup.dc中加入以下描述

set bus_inference_style {%s[%d]} set bus_naming_style {%s[%d]} set hdlout_internal_busses true change_name -hierarchy -rules verilog define_name_rules name_rule -allowed "a-z A-Z 0-9 _" -max_length 255 -type cell define_name_rules name_rule -allowed "a-z A-Z 0-9 _[]" -max_length 255 -type net define_name_rules name_rule -map {{"\*cell\*" "cell"}} define_name_rules name_rule -case_insensitive change_names -hierarchy -rules name_rule

dc使用教程

DC使用说明文件说明:在进行下面的演示时需要用到两个文件,一个是example1.v,它是描述一个电路的verilog代码,我们的目标就是用DC综合这个代码得到满足约束条件的电路网表;另一个是dc.scr,它是综合example1.v的脚本文件。

这两个文件都在/home/student1000目录下,大家把它们拷贝到自己的目录下,以备使用。

DC既可使用图形界面,也可不使用图形界面而直接运行脚本来综合电路。

一、DC图形界面的使用。

1.DC图形界面的启动1.1 打开一个终端窗口,写入命令dv –db_mode,敲入回车。

则DC图形界面启动,如下图所示红框处是DC的命令输入框,以下在图形界面上的操作都可以在命令输入框中输入相应的命令来完成。

选择Help----- Man Pages可以查看DC的联机帮助。

相应指令:man。

例:man man表示查看man命令的帮助。

man create_clock表示查看creat_clock命令的帮助。

2.设置库文件选择File---- Setup需要设置以下库文件,如下图。

相应指令:set search_path [list /tools/lib/smic25/feview_s/version1/STD/Synopsys \/tools/lib/smic25/feview_s/version1/STD/Symbol/synopsys] set target_library { smic25_ff.db }set link_library { smic25_ff.db smic25_ss.db }set symbol_library { smic25.sdb }点OK,设置完成。

3.读入verilog文件选择File--- Read在打开文件对话框中选中要打开的文件,在这里我们选中example1.v文件。

在Log框中出现successfully字样表明读入文件成功。

DC综合教程

启动dc的三种方法:DCSH:dc_shellTCL:dc_shell-t //注意:-t前没有空格图形化界面:design_visiontip1. 综合主要包括三个阶段:转换(translation)、优化(optimization)与映射(mapping)。

1. 转换阶段:综合工具将高层语言描述的电路用门级的逻辑来实现,对于Synopsys 的综合工具DC 来说,就是使用gtech.db库中的门级单元来组成HDL 语言描述的电路,从而构成初始的未优化的电路。

2. 优化与映射:是综合工具对已有的初始电路进行分析,去掉电路中的冗余单元,并对不满足限制条件的路径进行优化,然后将优化之后的电路映射到由制造商提供的工艺库上。

tip2DesignWare 是集成在DC综合环境中的可重用电路的集合DesignWare 分为DesignWare Basic 与DesignWare Foundation,DesignWare Basic 提供基本的电路,DesignWare Foundation提供性能较高的电路结构。

如果需要Foundation的DesignWare,需要在综合的时候设置synthetic_library3。

tip3 日志文件Design Analyzer 在启动时自动在启动目录下面创建两个日志文件:command.log 和view_command.log,用于记录用户在使用Design Compiler 时所执行的命令以及设置的参数,在运行过程中同时还产生filenames.log的文件,用于记录design compiler访问过的目录,包括库、源文件等,filenames.log文件在退出design compiler 时会被自动删除。

启动dc_shell时则只产生command.log 的日志文件。

tip4Propagation Delay传播延时Transition Time转变延时Setup Time建立时间The setup time for a sequential cell is theminimumlength of time the data-inputsignal must remain stable before the active edge of the clockHold Time保持时间The hold time for a sequential cell is the minimum length of time the data-inputsignal must remain stable after the active edge of the clock脚本:################################# Read design file #//read –format verilog[db、vhdl] file //dcsh的工作模式read_db file.db //TCL工作模式读取DB格式read_verilog file.v //TCL工作模式读取verilog格式read_vhdl file.vhd //TCL工作模式读取VHDL格式//设定时钟create_clock -name "clock" -period 20 -waveform { 0.000 10.000 } { clk }//输出文件write -f verilog -out output/count.v //输出网表write -f ddc -out output/count.ddc//综合数据文件write_sdf mapped/count.sdf //标准延时文件//综合compile -map_effort medium -incremental_mappingtip6设置设计环境Define the Design Environment1. Defining the Operating Conditions设置操作环境查看有哪些操作环境dc_shell> read_file my_lib.dbdc_shell> report_lib my_lib指定操作环境dc_shell> set_operating_conditions WCCOM -lib my_lib2.设置线负载模型set_wire_load_mode Top/Enclosed/Segmentedset_wire_load_model "10x10"3. Modeling the System Interface设置系统接口The set_drive and set_input_transition Commands:dc_shell> current_design top_level_designdc_shell> set_drive 1.5 {I1 I2}dc_shell> current_design sub_design2dc_shell> set_driving_cell -lib_cell IV {I3}dc_shell> set_driving_cell -lib_cell AN2 -pin Z -from_pin B {I4} Defining Loads on Input and Output PortsDefining Fanout Loads on Output Ports4. Setting Logic Constraints on Portsset_equal port1 port2set_oppositeset_logic_dcset_logic_oneset_logic_zeroset_unconnectedtip7设定设计约束When Design Compiler optimizes your design, it uses two types of constraints:Design rule constraintsOptimization constraints用于组成逻辑1. Maximum Transition Timedc_shell> set_max_transition 5 [current design]2. Maximum FanoutYou can set a maximum fanout constraint on every driving pin and input port as follows:dc_shell> set_max_fanout 8 [get_designs ADDER]计算Fanout值:Maximum Fanout>=Total Fanout Load注意:取出某些约束用:dc_shell> remove_attribute [get_designs adder] max_transitiondc_shell> remove_attribute [get_ports port_name] max_fanoutdc_shell> remove_attribute [get_designs design_name]max_fanoutdc_shell> remove_attribute port_name fanout_load3. The set_fanout_load command sets the expected fanout load value for listed output ports.To find the fanout load on the input pin of library cell AND2 in library libA, enterdc_shell> get_attribute "libA/AND2/i" fanout_loadTo find the default fanout load set on technology library libA, enterdc_shell> get_attribute libA default_fanout_load用于综合出可以驱动的最大扇出的引脚4. Maximum CapacitanceMaximum capacitance is a design rule constraint. It is set as a pin-level attribute that definesthe maximum total capacitive load that an output pin can drive. That is, the pin cannot connect to a net that has a total capacitance greater than or equal to the maximum capacitance defined at the pin.dc_shell> set_max_capacitance 3 [get_designs adder]5. Minimum CapacitanceThe min_capacitance design rule specifies the minimum load a cell can drive.设计规则的优先权1. Minimum capacitance2. Maximum transition3. Maximum fanout4. Maximum capacitance5. Cell degradationtip8设定优化约束Optimization ConstraintsTiming Constraints对于同步pashscreate_clockset_input_delayset_output_delay对于异步pashsset_max_delayset_min_delayMaximum Areadc_shell> set_max_area 0.0dc_shell> set_max_area 14.0Managing Constraint Prioritiesset_cost_priority [-default] [-delay] cost_listReporting Constraints:dc_shell >report_constraint写脚本tip9:在终端中启动DC用脚本综合dc_shell-t -f ./scripts/seg_drive.tcl > 1将报告写入1文件tip10:设计中有多个模块时,如果用top_down策略,则在脚本中得把所有的模块读入:set active_design seg_drive //注意:相等于一个宏定义,用active_design代替seg_drive read_verilog {encode_seg.v number_mod.v scan.v seg_drive.v} //read_file也可以,它可以读多种格式文件,包括.db#analyze -format verilog {encode_seg.v number_mod.v scan.v seg_drive.v}#elaborate $active_design //注意这里是$active_designcurrent_design $active_design //将顶层设置成当前设计link//read_verilog命令与后面的analyze、elaborate功能相同,可以选择其中一个;参看《ASIC综合与DC使用》:set_svf ./mapped/svf/$active_design.svf //没查###############################################1# Define the Design Environment#1###############################################113Modeling the SystemInterface设置系统接口21)set_operating_conditions slow //设定一个库的环境,库内包含使用温度、电压、电路特征线宽等2)set_wire_load_model –name model_name –lib_name library –max –min//设定线负载模型set_wire_load_model -name tsmc090_wl40 -library slow //表示使用库slow里的tsmc090_wl40线模型如果没有 wire_load_model,可以将 auto_wire_load_selection 参数设置为 true,则 DC自动根据综合之后的面积来选择一个统计的线负载模型用于估计连线延迟。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

0.7 FF clk 0.5 FF 0.65 FF

uncertainty = 0.7 - 0.5 = 0.2ns

20

Specify Latency

set_clock_latency -source 3 [get_clocks A ] set_clock_latency 1 [get_clocks A ]

24

Setting Area Constraint

Attributes > Optimization Constraints > Design Constraints

Unit:um x um

設為“0” Tool會自動合 出最小的面積

25

Save Constraints & Attributes

0.2 ns

22

Setting Input & Output Delay

In Symbol View select all input ports

Attributes > Operating Environment > Input Delay

0.381012 0.133056

0.600213 0.209607

Logic Synthesis with Design Vision

授課教師:洪進華老師 jhhong@.tw 實習助教:陳龍風 lfchen@.tw

1

What is synthesis

Synthesis = translation + optimazation +mapping

Error (只要有任何的Error,合成即會失敗) Warning (部分Warning可忽略,但Multiple Design Instance不可忽略)

module REG4 (q,qn,data,clk,clrn); output [3:0] q, qn; input [3:0] data; input clk, clrn; DFF d0 (q[0],qn[0],data[0],clk,clrn); DFF d1 (q[1],qn[1],data[1],clk,clrn); DFF d2 (q[2],qn[2],data[2],clk,clrn); DFF d3 (q[3],qn[3],data[3],clk,clrn); endmodule

set_dont_touch_network [ find clock A ]

Don’t add any buffer in clock network

set_fix_hold [ find clock A ]

19

Clock Skew

set_clock_uncertainty -setup 0.1 [get_clocks A ]

clk clock source latency network latency

FF

21

Specify Transition Time

set_input_transition -max 0.2 [get_ports E ]

0.2 ns

set_clock_transition -max 0.2 A

14

Setting Input Drive Impedance

set_drive [drive_of "tpz973pnwc/PDIZ/C"] [all_inputs]

PDIZ : I/O PAD Name C : Pin Name 可化簡成 = > set_drive 1 [all_inputs]

15

Setting Output Loading

set_load [load_of "tpz773pnwc/PDT02TZ/I"] [all_outputs]

PDT02TZ : I/O PAD Name I : Pin Name 可化簡成 = > set_load 1 [all_outputs]

18

Specify Clock

create_clock -name "A" -period B -waveform {C D} {E}

A Æ clock name. B Æ工作時脈,ex. 10 (ns) C Æ rising edge ex. 0 D Æ failling edge,ex.工作時脈/2 = 5 (ns) E Æ your module clock pin name.

切換到Design view, 並選擇multiple design instance

不建議使用

31

Method 1: dont_touch (.cont)

Attributes > Optimization Directives > Design

不建議使用

32

Method 2: ungroup

4

Invoke Design Vision

source synthesis.csh mkdir xxxx cd xxxx

複製 “.synopsys_dc.setup” 到你目前的目錄xxxx

5

Invoke Design Vision (.cont)

design_vision& (or dv & )

top (worst case) ,enclosed (middle) ,segmented (optimistic)

17

Setting Design Constraint

Define clock specification

1. 2. 3. 4. 5. 6. 7.

Period Waveform Uncertainty Æ skew Source latency Network latency Input tarnsition Clock transition

File > Save Info > Design Setup

將之前下的所有命令存檔 => top_setup.dc

26

Assign Problem

在top_setup.dc中加入以下描述,以消除gate level netlist 中的assign

set verilogout_no_tri true foreach_in_collection design [ get_designs "*"] { current_design $design set_fix_multiple_port_nets -all -buffer_constants } set_fix_multiple_port_nets -all -buffer_constants

2

1

12

Setting Design Environment

13

Setting Operating Condition

Attributes>Operating Environment>Operating Conditions

Worst

Best

set_operating_conditions -min_library fast -min fast -max_library slow -max slow 0.18可直接在Command Mode輸入

28

Execute Script File

File > Execute Script

執行你的top_setup.dc

29

Check Design

Execute check_design before you compile the design

Design > Check Design

30

Method 1: dont_touch

1. 2. 3. 4.

Select the multiple design instances block Compile the block(否則做完don’t_touch會不能compile) Attributes > Optimization Directives > Design Compile the whole design

27

Change Naming Rule

在top_setup.dc中加入以下描述

set bus_inference_style {%s[%d]} set bus_naming_style {%s[%d]} set hdlout_internal_busses true change_name -hierarchy -rules verilog define_name_rules name_rule -allowed "a-z A-Z 0-9 _" -max_length 255 -type cell define_name_rules name_rule -allowed "a-z A-Z 0-9 _[]" -max_length 255 -type net define_name_rules name_rule -map {{"\*cell\*" "cell"}} define_name_rules name_rule -case_insensitive change_names -hierarchy -rules name_rule