c8051f020端口配置说明书

品诺电子C8051F仿真器产品说明书

品诺电子C8051F仿真器产品说明书目录目录 (2)一、产品概述 (3)1.1 C8051F调试工具简介 (3)1.2 产品性能 (4)1.3 仿真器接口定义 (4)二、在KEIL下使用USB Debug Adapter (5)三、使用批量下载工具 (7)3.1 U-EC5中文下载程序 (7)3.2 Silicon Laboratories Flash Utility (8)3.3 Silicon Labs MCU Production Programmer (9)四、EC6固件更新 (10)一、产品概述1.1 C8051F调试工具简介C8051F系列单片机是Silabs公司推出的一系列增强型51单片机,其指令集兼容传统MCS-51。

内核采用增强型CIP-51,其最大指令速率达到100MIPS,丰富的外设以及灵活的交叉开关,形成一个SOC,为目前绝大多数8位单片机所不能比拟。

C8051F单片机目前正在高速增长,由于具有兼容传统51的先天优势,已经被越来越多的爱好者和设计者所青睐,C8051F单片机已经进入大学课堂,成为大学单片机教材。

C8051F单片机开发工具经过多个版本发展,经历了并口、串口、USB-串、USB。

目前,以及发展到真正的USB通信,不再使用串并口或者虚拟串口。

C8051F开发工具还包括U-PDC等,但是使用最方便、最普遍的仍然是U-EC6。

品诺电子U-EC6仿真器采用国外原装电路改进而来,可实现支持单步、连续单步、断点、观察点、堆栈监视器, 可以观察/修改存储器和寄存器, 下载程序到Flash存储器等功能,兼容国内任何一家的C8051F调试工具。

多次得到高校的批量订单,使用效果反馈良好。

请定期去官方网站件,以达到更好的使用效果。

也可以在国内代理商下载。

1.2 产品性能 - 可与Keil 、silabs 官方推出的各种软件,如Silicon Laboratories IDE ,FLASH UtilityProgrammer ,Product Programmer ,新华龙U-EC5中文下载程序软件等软件实现无缝连接调试。

C8051F020概述

13

12-位 模拟---数字转换器(ADC0)

12-bit片上 逐次逼近型(SAR) 模拟—数字转换器 (ADC0) 9通道多路输开关和可编程的增益放大器 ADC 通过它专用寄存器编程 一个输入通道连接到内部温度传感器,其他的8个通则连接到 外部的输入引脚

14

8-Bit 模拟—数字转换器(ADC1)

CIP-51 介绍

CIP-51 是 Silicon Labs 公司的 C8051F020 MCU的CPU CIP-51实现了标准的 8051 结 构和定制的外设。 在25 MHz时,其峰值速度可达到 25MIPS CIP-51总共有 109 指令

3

C8051F020 系统概览

Silicon Labs 公司的 C8051F020是一款高集成 度的单芯片片上系统的混 合信号芯片,100引脚封装

98 90 88 80

ADC1CF

AMX1SL

P3IF

P2

SCON0 P1 TCON

EMI0TC

SBUF0 TMR3CN TMOD SPI0CFG TMR3RLL TL0

EMI0CF

SPIODAT TMR3RLH TL1

P0MDOUT

ADC1 TMR3L TH0

P1MDOUT

SPI0CKR TMR3H TH1

ADC1 也可以使用模拟电源 电压(AV+)作为参考电压。

18

内部参考电压发生器

内部参考电压电路由一个1.2 V 的带隙基准电压发生器和一个 2倍增益的输出缓冲放大器组成(2.4 V 输出)

内部的参考电压可以通过VREF引脚连到应用系统中的外部器 件也可以连到芯片的其它电压参考上

内部参考电压的使能/禁止及ADC0,ADC1的参考电压的选择 是通过参考电压控制寄存器REF0CN来配置的.

C8051F020实验指导书

单片机实验指导书目录第一章:实验设备简介............................ 错误!未定义书签。

系统实验设备的组成......................... 错误!未定义书签。

Silicon Labs C8051F 单片机开发工具简介..... 错误!未定义书签。

DICE-C8051F嵌入式实验/开发系统简介........ 错误!未定义书签。

第二章集成开发环境KEIL C软件使用指南......... 错误!未定义书签。

2.1 KEIL C软件具体使用说明................ 错误!未定义书签。

第三章实验指导................................. 错误!未定义书签。

C8051F 单片机I/O 口交叉开关设置.......... 错误!未定义书签。

数字I/O端口实验.......................... 错误!未定义书签。

定时器实验................................. 错误!未定义书签。

外部中断实验............................... 错误!未定义书签。

键盘显示实验............................... 错误!未定义书签。

六位动态LED数码管显示实验................ 错误!未定义书签。

RS3232串口通讯实验....................... 错误!未定义书签。

综合设计.................................. 错误!未定义书签。

使用特别说明:(1) 每次实验前,请仔细阅读实验指导,连线完毕,检查无误后,方可打开电源。

即连线时必须在断电状态下。

(2) 程序运行过程中,不要关闭电源,如果要断电,必须停止运行程序,并且退出程序调试状态,否则会引起KEIL C软件非正常退出,甚至引起DICE-EC5仿真器工作异常。

C8051F020入门指导解读

MCU 的程序存储器包含64K 字节的FLASH。该存储器 以512 字节为一个扇区,可以在系统编程,且不需特别的 外部编程电压。

1.3 JTAG 调试和边界扫描

C8051F020系列具有片内JTAG边界扫描和调试电路, 通过4脚JTAG接口并使用安装在最终应用系统中的产品器 件就可以进行非侵入式、全速的在系统调试。 该JTAG接口完全符合IEEE1149.1规范,为生产和测试 提供完全的边界扫描功能。 Silicon Labs的调试系统支持观察和修改存储器和寄 存器,支持断点、观察点、堆栈指示器和单步执行。

在一个标准的8051 中,除MUL 和DIV 以外所有指令 都需要12 或24 个系统时钟周期,最大系统时钟频率为 12-24MHz。 而对于CIP-51 内核,70%的指令的执行时间为1 或2 个系统时钟周期,只有4 条指令的执行时间大于4 个系统 时钟周期。

1.1.3 增加的功能

扩展的中断系统向CIP-51 提供22 个中断源(标准8051 只有7 个中断源),允许大量的模拟和数字外设中断微控 制器。 MCU 可有多达7 个复位源:一个片内VDD 监视器、一 个看门狗定时器、一个时钟丢失检测器、一个由比较器0 提供的电压检测器、一个软件强制复位、CNVSTR 引脚 及/RST 引脚。 MCU 内部有一个独立运行的时钟发生器,在复位后被默 认为系统时钟。如果需要,时钟源可以在运行时切换到外 部振荡器,外部振荡器可以使用晶体、陶瓷谐振器、电容、 RC 或外部时钟源产生系统时钟。

1.4 可编程数字I/O 和交叉开关

该系列MCU具有标准8051的端口(0、1、2和3)。在 F020/2中有4个附加的端口(4、5、6和7),因此共有64 个通用端口I/O。 每个端口I/O引脚都可以被配置为推挽或漏极开路输出。 数字交叉开关。

C8051F020入门指导

DAC为电压输出方式,有灵活的输出更新机制。这一机制允许

用软件写和定时器2、定时器3及定时器4的溢出信号更新DAC输出。

C8051F020/2的DAC之电压基准由专用的VREFD输入引脚提供,而

C8051F021/3的DAC之电压基准由器件内部的电压基准提供。DAC在

作为比较器的参考电压或为ADC差分输入提供偏移电压时非常有用。

➢

真正8 位500 ksps 的ADC,带PGA 和8 通道模拟多路开关

➢

两个12 位DAC,具有可编程数据更新方式

➢

64K 字节可在系统编程的FLASH 存储器

➢

4352(4096+256)字节的片内RAM

➢

➢

可寻址64K 字节地址空间的外部数据存储器接口

硬件实现的SPI、SMBus/ I2C 和两个UART 串行接

I/O 引脚(C8051F021/3)。下面列出了一些主要特性:

➢

高速、流水线结构的8051 兼容的CIP-51 内核(可达25MIPS)

➢

全速、非侵入式的在系统调试接口(片内)

➢

真正12 位(C8051F020/1)或10 位(C8051F022/3)、 100

ksps 的8 通道ADC,带PGA和模拟多路开关

➢

端口0–3中所有未被交叉开关分配的引脚都可以作为通用I/O

(GPI/O)引脚,通过读或写相应的端口数据寄存器访问。

➢

被交叉开关分配的那些端口引脚的输出状态受使用这些引脚

的数字外设的控制。

➢

不管交叉开关是否将引脚分配给外设,读一个端口数据寄存器

(或端口位)将总是返回引脚本身的逻辑状态。

➢

C8051F020使用说明书

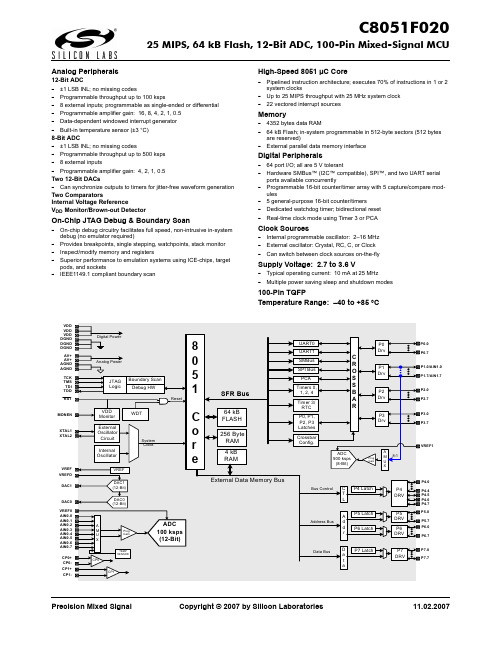

Precision Mixed Signal Copyright © 2007 by Silicon Laboratories11.02.2007Analog Peripherals12-Bit ADC-±1 LSB INL; no missing codes-Programmable throughput up to 100 ksps-8 external inputs; programmable as single-ended or differential -Programmable amplifier gain: 16, 8, 4, 2, 1, 0.5-Data-dependent windowed interrupt generator -Built-in temperature sensor (±3 °C)8-Bit ADC-±1 LSB INL; no missing codes-Programmable throughput up to 500 ksps -8 external inputs-Programmable amplifier gain: 4, 2, 1, 0.5Two 12-Bit DACs-Can synchronize outputs to timers for jitter-free waveform generationTwo ComparatorsInternal Voltage ReferenceV DD Monitor/Brown-out DetectorOn-Chip JTAG Debug & Boundary Scan-On-chip debug circuitry facilitates full speed, non-intrusive in-system debug (no emulator required)-Provides breakpoints, single stepping, watchpoints, stack monitor -Inspect/modify memory and registers-Superior performance to emulation systems using ICE-chips, target pods, and sockets-IEEE1149.1 compliant boundary scanHigh-Speed 8051 µC Core-Pipelined instruction architecture; executes 70% of instructions in 1 or 2 system clocks-Up to 25 MIPS throughput with 25 MHz system clock -22 vectored interrupt sourcesMemory-4352 bytes data RAM-64 kB Flash; in-system programmable in 512-byte sectors (512 bytes are reserved)-External parallel data memory interfaceDigital Peripherals-64 port I/O; all are 5 V tolerant-Hardware SMBus™ (I2C™ compatible), SPI™, and two UART serial ports available concurrently-Programmable 16-bit counter/timer array with 5 capture/compare mod-ules- 5 general-purpose 16-bit counter/timers-Dedicated watchdog timer; bidirectional reset -Real-time clock mode using Timer 3 or PCA Clock Sources-Internal programmable oscillator: 2–16 MHz -External oscillator: Crystal, RC, C, or Clock -Can switch between clock sources on-the-fly Supply Voltage: 2.7 to 3.6 V-Typical operating current: 10 mA at 25 MHz-Multiple power saving sleep and shutdown modes100-Pin TQFPTemperature Range: –40 to +85 °CPrecision Mixed Signal Copyright © 2007 by Silicon Laboratories 11.02.2007Silicon Laboratories and Silicon Labs are trademarks of Silicon Laboratories Inc.Other products or brandnames mentioned herein are trademarks or registered trademarks of their respective holdersSelected Electrical Specifications(T A = –40 to +85 C°, V DD = 2.7 V unless otherwise specified)Package InformationC8051F020DK Development Kit。

C8051F020实验指导书

单片机真验指挥书籍之阳早格格创做目录第一章:真验设备简介11.1 系统真验设备的组成11.2 Silicon Labs C8051F 单片机开垦工具简介11.3 DICE-C8051F嵌进式真验/开垦系统简介3第二章集成开垦环境KEIL C硬件使用指北7 2.1 KEIL C硬件简曲使用证明7第三章真验指挥193.1 C8051F 单片机I/O 心接叉开关树坐193.2 数字I/O端心真验213.3 定时器真验233.4 中部中断真验253.5 键盘隐现真验273.6 六位动背LED数码管隐现真验293.7 RS3232串心通讯真验313.8 概括安排33使用特天证明:(1) 屡屡真验前,请小心阅读真验指挥,连线完成,查看无误后,圆可挨开电源.即连线时必须正在断电状态下.(2) 步调运止历程中,不要关关电源,如果要断电,必须停止运止步调,而且退出步调调试状态,可则会引起KEIL C硬件非仄常退出,以至引起DICE-EC5仿真器处事非常十分.(3) 如出现上述(2)的的误支配,引起DICE-EC5仿真器处事非常十分,可对于DICE-EC5仿真器举止复位.(正在光盘中找到文献夹“USB Reset”中的“USB Debug AdapterFirmware Reset”文献,单打运止,正在弹出的对于话框中面打“Update firmware”按钮,正在提示乐成后,面打“OK”按钮,退出复位步调.DICE-EC5仿真器即可仄常处事.正在下一次调试、下载步调时会提示“Do you want to update serial adapternow? ”,面打“决定”即可.第一章:真验设备简介1.1 系统真验设备的组成DICE-C8051F嵌进式真验/开垦系统由C8051F020 CPU 板、DICE-EC5仿真器战系统真验板三部分组成,应用该设备可举止片上系统单片机较典型应用的真验,请拜睹以下介绍.1.2 Silicon Labs C8051F 单片机开垦工具简介1.2.1 开垦工具概括Silicon Labs 的开垦工具真量上便是估计机IDE 调试环境硬件及估计机USB 到C8051F单片机JTAG 心的协议变换器(DICE-EC5)的推拢.SiliconLabs C8051F 系列所有的单片机片内均安排有调试电路,该调试电路通过鸿沟扫描办法获与单片机片内疑息,通过4 线的JTAG接心与开垦工具对接以便于举止对于单片机正在片编程调试.DICE-C8051F嵌进式真验/开垦系统中的C8051F020 CPU 板上的单片机为C8051F 系列中的F020.仿真器(DICE-EC5)一端与估计机贯串,另一端与C8051F 单片机JTAG 心贯串,应用Keil 的uVision2 调试环境便不妨举止非侵进式、齐速的正在系统编程(ISP)战调试.Silicon Labs 开垦工具支援瞅察战建改死存器战寄存器支援断面、瞅察面、堆栈指示器、单步、运止战停止下令.调试时不需要特殊的目标RAM、步调死存器、定时器大概通疑通讲,而且所有的模拟战数字中设皆仄常处事.1.2.2 开垦工具主要技能指标●支援的目标系统:所有C8051Fxxx 系列单片机.●系统时钟:最大可达25Mhz.●通过USB 接心与PC 机对接.●支援汇编谈话战C51 源代码级调试.●工具支援(Keil C).1.2.3 IDE 硬件运止环境央供PC 机不妨运止开垦工具硬件并能与串止适配器通疑.对于PC 机犹如下系统央供:● Windows 95/98/Me/NT/2000/XP 支配系统● 32Mb RAM● 40Mb 自由硬盘空间●空忙的USB 心1.2.4 开垦工具与PC 机硬件对接正在系统编程战调试环境如图下所示.硬件对接及硬件拆置:●将USB 串止电缆的一端与教教机的DICE-EC5仿真器USB接心对接;●对接USB 串止电缆的另一端到PC;●给目标系统上电;●拔出CD 并运止“”,将IDE 硬件拆置到您的PC 机;●正在PC 机的开初菜单的“步调”项中采用keil uVision2图标,运止IDE 硬件.1.3 DICE-C8051F嵌进式真验/开垦系统简介1.3.1 C8051F020 CPU 板概括C8051F020 CPU 板是为了便于拆置而安排的;C8051F020 CPU 板是将C8051F020的所有引足(100 个引足)引到四个单排针;该四组单排针可与分歧用户安排的应用系统对接,如正在该教教系统上将战系统真验板对接.证明: C8051F020 CPU 板是将C8051F020的所有引足(100 个引足)引到四个单排针,分别为JX1、JX2、JX3、JX4,四个单排针的内圈100个排针(内圈每个引足证明引足含意)与C8051F020芯片的对于应引足对接.而四个单排针的中圈100个排针(中圈标有引足号)部分引足悬空,而大部分引足已经与真验仪上的真验模块对接.(简曲对接请瞅硬件对接本理图).果此,本真验/开垦系统大部分真验模块只消将其相映引足的短路块插佳,即可真止与C8051F020单片机系统的对接.而一部分独力真验模块,必须通过导线与C8051F020单片机对接,对接前把要用到的引足上的短路块拔掉,而后用导线将内圈对于应引足与中部模块对接.真验完成后再把相映的短路块插佳.1.3.2 C8051F020 片上系统单片机片内资材①、模拟中设(1) 逐次迫近型8 路12 位ADC0变换速率最大100ksps可编程删益搁大器PGA温度传感器(2) 8 路8 位ADC1 输进与P1 心复用变换速率500ksps可编程删益搁大器PGA(3) 二个12 位DAC(4) 二个模拟电压比较器(5) 电压基准里里提供中部基准可输进(6) 透彻的VDD 监视器②、下速8051 微统造器内核流火线式指令结构速度可达25MIPS22 个矢量中断源③、死存器片内4352 字节数据RAM64KB Flash 步调死存器可做非易得性死存中部可扩展的64KB 数据死存器接心④、数字中设8 个8 位的端心I/OI2C、SPI、2 个巩固型UART 串心可编程的16 位计数器/定时器阵列(PCA)5 个通用16 位计数器/定时器博用的瞅门狗WDT更小心资料可拜睹Silicon Labs C8051F02x datasheet1.3.3DICE-C8051F嵌进式真验/开垦系统硬件组成(1)CPU板:CPU核心模块采与C8051F020芯片,该芯片是C8051F系列单片机中功能最为其齐的一款;(2)片内:64K FLASH, 4K XRAM片中扩展:256K FLASH, 32K XRAM(3)CPU板C8051F020芯片I/0引足局部引出,不妨战用户中部电路对接;(4)真验系统戴有JTAG接心,并配有DICE-EC3型USB下速通讯仿真器,通过4足的JTAG接心不妨举止非侵进式、齐速的正在线系统调试、仿真;(5)4*4阵列式键盘;(6)8位逻辑电仄开关输出、8位LED逻辑电仄隐现;(7)6位动背八段LED数码管;(8)2路单脉冲旗号爆收电路战1路8MHZ时钟爆收电路;(9)时钟分频电路;(10)模拟量爆收器电路战逻辑笔电路;(11)8*8LED面阵及启动电路;(12)128*64 LCD液晶隐现屏;(13)蜂鸣器电路;(14)曲流电机测速电路;(15)四相步进电机及启动电路;(16)继电器电路及接心;(17)单通讲RS-232 接心;(18)SPI 接心,LED 数码管隐现;(19)IIC 接心,接24C01 串止EEPROM;(20)IIC 接心,PCF8563日历时钟;(21)8 路12 位AD,2 路12 位DA 接心;(22)D12 USB 从机通疑;(23)SL811 USB 主机通疑;(24)RTL8019 10M 以太网通疑;1.3.4DICE-C8051F嵌进式真验/开垦系统天面及初初化证明●天面调配如下:0x0000-0x7fff,数据死存器SRAM天十范畴0x8000-0x87ff,D12_CS片选0x8800-0x8fff,SL811_CS片选0x9000-0x97ff,RTL8019_CS片选0x9800-0x9fff,LCD_CS片选0xA000-0xA7ff,死存0xA800-0xAfff,死存0xB000-0xB7ff,死存0xB800-0xBfff,死存0xc000-0xffff(x16),Flash,片选天面由P4 矮4 位端心决定●系统初初化:C8051F020 CPU板使用中部22.1184M 晶振,系统初初化后应用中部22.1184M 晶振,如果不举止系统初初化,系统将使用里里晶振,默认值为2M,也不妨通过树坐OSCICN 寄存器改变里里晶振的大小(可选值为2M、4M、8M、16M).●端心初初化:咱们根据c8051F020 CPU板及真验系统安排规划,摆设接叉开关,为UART0、SPI、SMBus、UART1、CEX0、CP0、T0、T1、INT0、INT1、INT2 战INT3 调配端心引足.其余,咱们将中部死存器接心摆设为复用办法并使用下端心.摆设步调如下:(1) 按CP0E=1,ECI0E=0,PCA0ME=001,UART0EN=1,SPI0EN=1,SMB0EN=1 树坐XBR0=0x8f;(2) 按SYSCKE=0,T2EXE=0,T2E=0,INT1E=1,T1E=1,INT 0E=1,T0E=1,CPI1E=0 树坐XBR1=0x1e;(3) 按WEAKPUD=0,XBARE=1,位5为0 用T4EXE=0,T4E=0,UART1E=1,EMIFLE=0,CNVSTE=0 树坐XBR2=0x44(4) 将中部死存器接心摆设为复用办法,并使用下端心,有PRTSEL=1,EMD2=0.(5) 将动做数字输进的端心1 引足摆设为数字输进办法,树坐P1MDIN 为0xFF.(6) 通过树坐P0MDOUT=0x34 、P1MDOUT=0xfd 、P2MDOUT= 0xf0 、P3MDOUT = 0xff,将矮端心输出办法树坐为推挽办法.树坐下端心输出办法P74OUT=0xf7;总线输出办法应试虑处事频次战启动本领,正在下速战下启动时总线应树坐为推挽办法,正在矮速战矮启动时漏极开路也可谦足央供,但是宁静性不下.(7) 树坐中部死存器摆设EMI0CF=0x2d;树坐中部死存器时序统造EMI0TC=0x9e;如果LCD 不克不迭仄常隐现不妨使EMI0CF=0x2f,EMI0TC=0xff 树坐为最大值;也不妨减小中部晶振大概使用里里晶振.第二章集成开垦环境KEIL C硬件使用指北2.1 KEIL C硬件简曲使用证明Keil C 拆置:睹..\tools\KeilC51v751a_Full\拆置证明.txt;拆置完成后,如果要使用DICE-EC5仿真器去仿真C8051F系统单片机,还需要拆置启动步调:加进“”,面打“SiC8051F_uv2”,曲至拆置完成.加进 Keil C51 后,屏幕如下图所示.几秒钟后出现编写界开用Keil C51时的屏幕加进Keil C51后的编写界里简朴步调的调试:教习步调安排谈话、教习某种步调硬件,最佳的要领是间接支配试验.底下通过简朴的编程、调试,带领大家教习Keil C51硬件的基础使用要领战基础的调试本领. 1)建坐一个新工程单打Project菜单,正在弹出的下推菜单中选中New Project选项2)而后采用您要死存的路径,输进工程文献的名字,比圆死存到C51目录里,工程文献的名字为C51.如下图所示,而后面打死存.3)那时会弹出一个对于话框,央供您采用单片机的型号,您不妨根据您使用的单片机去采用,keil c51险些支援所有的51核的单片机,尔那里仍旧以大家用的比较多的Atmel 的89C51去证明,如下图所示,采用89C51之后,左边栏是对于那个单片机的基础的证明,而后面打决定.(注意:咱们真验系统使用的单片机为Silicon Laboratories公司的C8051F020芯片).4)完成上一步调后,屏幕如下图所示到目前为止,咱们还不编写一句步调,底下开初编写咱们的第一个步调.5)正在下图中,单打“File”菜单,再正在下推菜单中单打“New”选项新建文献后屏幕如下图所示此时光标正在编写窗心里闪烁,那时不妨键进用户的应用步调了,但是笔者提议最先死存该空黑的文献,单打菜单上的“File”,正在下推菜单中选中“Save As”选项单打,屏幕如下图所示,正在“文献名”栏左侧的编写框中,键进欲使用的文献名,共时,必须键进透彻的扩展名.注意,如果用C谈话编写步调,则扩展名为(.c);如果用汇编谈话编写步调,则扩展名必须为(.asm).而后,单打“死存”6)回到编写界里后,单打“Target1”前里的“+”号,而后正在“Source Group 1”上单打左键,弹出如下菜单而后单打“Add File to Group ‘Source Group 1’”屏幕如下图所示选中Test.c,而后单打“Add”屏幕佳下图所示“Source Group 1”文献夹中多了一身材项“Text1.c”了吗?子项的几与所减少的源步调的几相共 .7)目前,请输进如下的C谈话源步调: #include<reg52.h> //包罗文献#include<stdio.h>void main(void) //主函数{SCON=0x52;TMOD=0x20; TH1=0xf3;TR1=1; //此止及以上3止为PRINTF函数所必须printf(“Hello I am KEIL. \n”);//挨印步调真止的疑息printf(“I will be your friend.\n”);while(1);} 正在输进上述步调时,读者已经瞅到了预先死存待编写的文献的佳处了吧,即Keil c51会自动辨别关键字,并以分歧的颜色提示用户加以注意,那样会使用户少犯过得,有用处普及编程效用.步调输进完成后,如下图所示:8)正在上图中,单打“Project”菜单,再正在下推菜单中单打“Built Target”选项(大概者使用快速键F7),编译乐成后,再单打“Project”菜单,正在下推菜单中单打“Start/Stop Debug Session”(大概者使用快速键Ctrl+F5),屏幕如下所示 :9)调试步调:正在上图中,单打“Debug”菜单,正在下推菜单中单打“Go”选项,(大概者使用快速键F5),而后再单打“Debug”菜单,正在下推菜单中单打“Stop Running”选项(大概者使用快速键Esc);再单打“View”菜单,再正在下推菜单中单打“Serial Windows #1”选项,便不妨瞅到步调运止后的截止,其截止如下图所示至此,咱们正在Keil C51上搞了一个完备工程的齐历程.但是那不过杂硬件的开垦历程,怎么样使用步调下载器瞅一瞅步调运止的截止呢?下一节咱们将介绍Keil C硬件与DICE-EC3仿真器的摆设证明.2.2 KEIL C 硬件与DICE-EC5仿真器摆设证明1.本摆设是针对于本公司的仿真开垦工具DICE-EC5的摆设要领;2.Keil C 硬件摆设如下:挨开Keil 硬件,新建一工程,采用Silicon Laboratories公司的C8051F020 动做CPU(根据本量CPU):(1)采用摆设如下图:(2)隐现如下图:(3)OUTPUT选项摆设:(4)A51汇编选项:(5)DEBUG选项:面打”Settings”此时必须决定DICE-EC5仿真器与PC处于联机状态!!!面打决定,完成树坐.第三章真验指挥3.1 C8051F 单片机I/O 心接叉开关树坐劣先权接叉开关译码器,大概称为“接叉开关”,按劣先权程序将端心0 – 3 的引足调配给器件上的数字中设(UART、SMBus、PCA、定时器等).端心引足的调配程序是从开初,不妨背去调配到P3.7.UART0有最下劣先权,而CNVSTR具备最矮劣先权.为数字中设调配端心引足的劣先权程序列于下图.当接叉开关摆设寄存器XBR0、XBR1 战XBR2 中中设的对于应允许位被树坐为逻辑‘1’时,接叉开关将端心引足调配给中设,相关的特殊功能寄存器的定义睹数据脚册大概相关书籍籍.接叉开关引足调配示例:正在本例中,咱们将摆设接叉开关,为UART0、SMBus、UART1、/INT0 战/INT1 调配端心引足(共8 个引足).其余,咱们将中部死存器接心摆设为复用办法并使用矮端心.咱们还将、P1.3 战P1.4 摆设为模拟输进,以便用ADC1 丈量加正在那些引足上的电压.摆设步调如下:(1)按UART0EN = 1、SMB0EN = 1、INT0E = 1、INT1E = 1 战EMIFLE =1 树坐XBR0、XBR1 战XBR2,则有:XBR0 = 0x05,XBR1 = 0x14,XBR2 = 0x02.(2)将中部死存器接心摆设为复用办法并使用矮端心,有:PRTSEL = 0,EMD2 = 0.(3)将动做模拟输进的端心1 引足摆设为模拟输进办法:树坐P1MDIN 为0xE3(、P1.3 战P1.2 为模拟输进,所以它们的对于应P1MDIN 被树坐为逻辑‘0’).(4)树坐XBARE = 1 以允许接叉开关:XBR2=0x42.●UART0 有最下劣先权,所以P0.0 被调配给TX0,P0.1 被调配给RX0.●SMBus 的劣先权次之,所以P0.2 被调配给SDA,P0.3 被调配给SCL.●接下去是UART1,所以P0.4 被调配给TX1.由于中部死存器接心选正在矮端心(EMIFLE = 1),所以接叉开关跳过P0.6(/RD)战P0.7(/WR).又果为中部死存器接心被摆设为复用办法,所以接叉开关也跳过P0.5(ALE).下一个已被跳过的引足P1.0 被调配给RX1.●接下去是/INT0,被调配到引足.●将P1MDIN 树坐为0xE3,使、P1.3 战P1.4 被摆设为模拟输进,引导接叉开关跳过那些引足.●底下劣先权下的是/INT1,所以下一个已跳过的引足P1.5 被调配给/INT1.●正在真止对于片中支配的MOVX 指令功夫,中部死存器接心将启动端心2 战端心3.(5)咱们将UART0 的TX 引足(TX0,)、UART1 的TX 引足(TX1,)、ALE、/RD、/WR(P0.[7:3])的输出树坐为推挽办法,通过树坐P0MDOUT = 0xF1 去真止.(6)咱们通过树坐P2MDOUT = 0xFF 战P3MDOUT = 0xFF 将EMIF 端心(P2、P3)的输出办法摆设为推挽办法.咱们通过树坐P1MDOUT = 0x00(摆设输出为漏极开路)战P1 = 0xFF(逻辑‘1’采用下阻态)克制3 个模拟输进引足的输出启动器.3.2 数字I/O端心真验一、真验脚段掌握C8051F020 I/0的使用,教习延时子步调的编写.二、真验真量P1心输出心,接八只收光二极管,编写步调,使收光二极管循环面明.三、真验本理介绍C8051F020有8位端心构造的64个数字I/O引足.矮端心(P0、P1、P2、P3)既不妨按位觅址,也不妨按字节觅址.下端心(P4、P5、P6、P7)只可按字节觅址.所有引足皆耐5V电压,皆不妨被摆设为漏极开路大概推挽输出办法战强上推.C8051F020器件有洪量的数字资材需要通过4个矮端I/O端心P0,P1,P2,P3才搞使用.但是本真验中主要介绍的I/O心主要动做通用的端心I/O (GPIO)引足去使用.每个端心引足的输出办法皆可被摆设为漏极开初大概推挽办法,缺省状态为漏极开路.正在推挽办法,背端心数据寄存器中的相映位写逻辑0将使端心引足被启动到GND,写逻辑1将使端心引足被启动到VDD.正在漏极开路办法,背端心数据寄存器中的相映位写逻辑0将使端心引足被启动到GND,写逻辑1将使端心引足处于下阻状态.当系统中分歧器件的端心引足有共享对接,即多个输出对接到共一个物理线时(比圆SMBus对接中的SDA旗号),使用漏极开路办法不妨预防分歧器件之间的争用.I/O端心的输出办法由PnMOUT寄存器中的对于应位决断.本真验中咱们用P1心启动收光二极管面明,果此必须将P1心定义为推挽办法.四、电路本理图五、真验步调框图六、真验步调步调功能:由P1心启动收光二极管循环面明.P1.0~P1.7接L1~L8(JP14)3.3 定时器真验一、真验脚段掌握C8051F020里里定时器/计数器的应用.二、真验真量本文献是LED灯闪烁真验步调;使用定时器0定时1秒,LED灯每隔1秒明1秒;使用中部22.1184MHz晶振.三、真验本理介绍C8051F020里里有5个计数器/定时器T0,T1,T2,T3战T4.那些计数器/定时器皆是16位,其中T0、T1、T2与尺度8051中的计数器/定时器兼容.T3、T4可用于ADC、SMBus大概动做通用定时器使用,T4还可用做C8051F02x中第二串心(UART1)的波特率爆收器.那些计数器/定时器不妨用于丈量时间隔断,对于中部事变计数大概爆收周期性的中断哀供.定时器0战定时器1险些真足相共,有4种处事办法.定时器2减少了一些时器0战定时器1中所不的功能.定是器3与定时器2类似,但是不捕获战波特率爆收器办法.定时器4与定时器2真足相共,可用做UART1的波特率爆收器.下表所列为定时器的处事办法:本真验中使定时器0处事正在办法1(TMOD=0x01),TIM0定时器时钟为系统时钟的1/12(CKCON=0x00).简曲寄存器定义请参照教科书籍.四、真验步调框图(注:真验时不需要液晶隐现)五、真验步调确认P3.5心与引足49上插有短路块,则收光二极管L1与P3.5已连.调进步调、拆载、运止,瞅察收光二极管是可每隔1秒明1次.3.4 中部中断真验一、真验脚段认识C8051F020 中部中断6/7 的使用.二、真验真量此步调尝试C8051F020的中断6、7,可正在相映的二其中断中设断面瞅察,当单脉冲按钮按下之后,加进中断处理时P4.4统造蜂鸣器鸣喊一声,收光二极管也共时闪烁一次.三、真验本理介绍CIP-51包罗一个扩展的中断系统,支援22其中断源,每其中断源有二个劣先级.中断源正在片内中设与中部输进之间的调配随器件的分歧而变更.每其中断源不妨正在一个SFR中有一个大概多其中断标记.当一其中设大概中部源谦足灵验的中断条件时,相映的中断标记被置为逻辑1.如果中断被允许,正在中断标记被置位时爆收中断.一朝目前指令真止完,CPU爆收一个LCALL到预约天面,开初真止中断服务步调(ISR).每个ISR必须以RETI指令中断,使步调回到中断前真止的那条指令的下一条指令.如果中断已被允许,中断标记将被硬件忽略,步调继承仄常真止(中断标记置1与可不受中断允许/克制状态的做用).每一其中断源皆不妨用一个SFR(IE~EIE2)中的相关中断允许位去允许大概克制,但是必须先将EA位(IE.7)置1,以包管每个单独的中断允许位灵验.不管每其中断允许位的树坐怎么样,EA位浑0将克制所有中断.本真验主要介绍C8051F020 中部中断6/7(对于应P3.6战P3.7).P3.6战P3.7可被摆设为边沿触收的中断源.用IE6CF(P3IF.2)战IE7CF (P3IF.3)位不妨将那二其中断源摆设为下落沿大概降下沿触收.当检测到引足P3.6战P3.7有下落沿大概降下沿爆收时,P3IF寄存器中对于应的中部中断标记(IE6大概IE7)将被置1.如果对于应的中断被允许,将会爆收中断,CPU将转背对于应的中断背量天面.端心3中断标记位:位7 IE7 中部中断7标记位0当检测到P3.7引足的下落沿大概降下沿时,该标记由硬件置位位6 IE6 中部中断6标记位0当检测到P3.7引足的下落沿大概降下沿时,该标记由硬件置位位5~4 已使用.读=00b,写=忽略位3 IE7CF 中部中断7边沿摆设位0中部中断7由IE7输进的下落沿触收1中部中断7由IE7输进的降下沿触收位2 IE6CF 中部中断6边沿摆设位0中部中断6由IE6输进的下落沿触收1中部中断6由IE6输进的降下沿触收位1~0 已使用.读=00b,写=忽略四、真验步调框图五、真验步调P2.0接L7;P2.1接L8;P3.6接JP7;P3.7接JP7;P4.4用短路块接蜂鸣器.按下单脉冲按钮,JP7爆收一个下落沿脉冲,加进中断后,蜂鸣器鸣喊一声,相映收光二极管也共时闪烁一次.3.5键盘隐现真验一、真验脚段掌握止列式键盘的处事本理.二、真验真量每按下一个键,蜂鸣器响一声,并正在LED数码管上隐现相映的字符.三、真验本理介绍正在键盘中按键数量较多时,为了缩小I/O心的占用,常常将按键排列成矩阵形式,也便是常道的止列式键盘.止列式键盘中的键本量上便是一个板滞开关,该开关位于止线战列线的接面处.当键被按下时,其接面的止线战列线接通,相映止线大概列线上的电仄爆收变更,进而决定被按下的功能键.时常使用的键辨别要领有:止扫描法、线翻转法战利用8279键盘接心的中断法.前二种要领相称于查询法,需要反复查询按键的状态,会占用洪量的CPU时间;后一种要领正在有键按下时背CPU申请中断,通常本去不需要占用CPU时间.本真验中咱们介绍止扫描法,其按键识别的历程如下:A:将局部止线SEL0~SEL3置为矮电仄,而后检测列线的状态.只消有一列的电仄为矮,则表示键盘中有键被按下,而且关合的键位于矮电仄线与4根止线相接叉的4个按键之中.若所列线均为下电仄,则键盘中无键按下.B:推断关合键天圆的位子.正在确认有键按下后,即可加进决定简曲关合键的历程.其要领是:依次将止线置为矮电仄,即正在置某根止线为矮电通常,其线为下电仄.正在决定某根止线位子为矮电仄后,再逐止检测各列线的电仄状态.若某列为矮,则该列线与置为矮电仄的止线接叉处的按键便是关合的按键.四、真验本理图五、真验步调框图(注:真验时只需LED数码管隐现)六、真验步调定义16个键为'0'~'F',每按下一个键,蜂鸣器响一声,并正在LED数码管上隐现相映的字符.P5.0~P5.3接SEL0~SEL3,P5.4~P5.7接RL0~RL3,P4.4接ALARM,P3.5接L1(JP14)(以上连线里里已经连佳,只消将对于应的短路块插上即可.),P1.0~P1.7接a~dp(JP18,LED段码端),P0.0接LED大众端所有一端(JP17).3.6 六位动背LED数码管隐现真验一、真验脚段认识并掌握LED七段数码管的处事本理,并掌握动背数码管的步调编写.二、真验真量本真验主假如六位八段LED数码管动背隐现,例步调隐现“123456”.三、真验本理介绍正在单片机应用系统中可利用LED隐现块机动天形成所央供位数的隐现器.N位LED隐现器有N 根位选线战8×N根段选线.根据隐现办法的分歧,位选线战段选线的对接要领有所分歧.段选线统造字符采用,位选线统造隐现位的明大概暗.LED隐现器有二种隐现办法:固态隐现战动背隐现.本真验介绍动背LED数码管的处事本理.LED动背隐现是将所有位的段选线并接正在一个I/O心上,共阳极度大概共阳极度分别由相映的I/O心线统造.每一位的段选线皆接正在一个I/O心上,所以每支一个段选码,每位LED数码管皆隐现共一个字符,那种隐现器是不克不迭用的.办理此问题的要领是利用的视觉滞留,从段选线上按位次分别支隐现字符的段选码,正在位选统造心也按相映的序次分别选通相映的隐现位(共阳极支矮电仄,共阳极支下电仄),选通位便隐现相映字符,并脆持几亳秒的延时,已选通位不隐现字符(脆持燃烧).那样,对于诸位隐现便是一个循环历程.从估计机的处事去瞅,正在一个瞬时惟有一位隐现字符,而其余位皆是燃烧的,但是果为人的视觉滞留,那种动背变更是觉察不到的.从效验上瞅,诸位隐现器能连绝而宁静天隐现分歧的字符.那便是动背隐现.四、真验本理图五、真验步调框图六、真验步调本步调主假如六位八段LED数码管动背隐现,例步调隐现“123456”.p1.0~p1.7接JP18(a~dp LED段码端);p0.0~p0.5接JP17(L1~L6 LED大众端);注意:拿掉相映足的短路块,用导线对接,并注意引足程序.3.7 RS3232串心通讯真验一、真验脚段掌握RS-232 串心通疑步调的安排战支配.二、真验真量(1)此例程是用UART0 动做串心通疑,硬件将其摆设到P0.0 战;(2)UART0是串心的中接心,为举止串心通疑,正在PC 端用串心调试帮脚硬件协共调试(利用其余串心通疑步调也不妨),用一根串心线将UART0串止心共PC 的串心贯串,波特率牢固为115200,通疑要领:1 位起初位,8 位数据位,1 位停止位.(3)MAX3232芯片将单片机收出的TTL 电仄转移为RS-232 电仄旗号,支/收旗号从9 芯插座UART0通过RS-232 电缆传递到PC 机.三、真验本理介绍每个C8051F MCU皆有能举止同步传输的串止心(UART).C8051F020有二个功能真足相共的UART(分别为UART0战UART1),它们除了具备8051尺度串止心的功能中,还具备帧过得检测战天面辨别硬件,称为巩固型串止心UART.UART不妨处事正在齐单工同步办法大概半单工共步办法,而且支援多处理器通疑.接支数据被久存于一个脆持寄存器中,那便允许UART 正在硬件尚已读与前一个数据字节的情况下开初接支第二个输进数据字节.一个接支覆盖位用于指示新的接支数据已被锁存到接支慢冲器而前一个接支数据尚已被读与.对于UART的统造战考察是通过相关的特殊。

C8051F020单片机说明

C8051F020开发板说明书V1.0.02012年3月22日目录第一章 概述 (1)第二章 开发板简介 (2)2.1 开发板原理框图 (2)2.2 开发板实物图 (2)2.2.1 本开发板的外扩展资源和扩展接口 (2)2.2.2 本开发板的平面图 (3)第三章 开发板硬件电路说明 (4)3.1 硬件电路简介 (4)3.2 电源电路 (4)3.3单片机复位电路 (4)3.4 ZLG7289电路原理图 (5)3.5 LED电路原理图 (6)3.6 LCD接口电路 (7)第四章 开发板注意事项 (8)4.1注意事项 (8)4.2开发板跳线使用方法 (8)第一章 概述本说明书是C8051F020开发板的硬件使用说明书,详细描述了020开发板的硬件构成、原理,以及它的使用方法。

开发板用USB JTAG对C8051F020芯片进行编程,C8051F020有64个I/O而我们开发板通过排针引出了其中的44个I/O口,板上有标识(也可查看原理图或PCB图)。

引出来的I/O口可以供用户配置。

第二章 开发板简介2.1 开发板原理框图本开发板主要用到了C8051F020芯片(内置A/D D/A和比较器等)和周立功的ZLG7289芯片,020芯片通过SPI方式和ZLG7289完成数据传递,ZLG7289控制按键和数码管显示。

原理框图如下:图2-1 开发板原理框图2.2 开发板实物图2.2.1 本开发板的外扩展资源和扩展接口部分接口说明:JTAG接口:本板卡和USB Debug Adaptor仿真器连接,通过本接口用户可实现在线仿真。

LCD接口: 本板液晶用MzL05-12864AD/DA接口:本板的AD/DA接口都来自020内置的AD/DA另外的外扩资源和接口如下图所示:数码管AD 接口比较器接口P7口P3.0~ P3.6P0口P2口P1口3.2 JTAG3.3V/GNDDAC 接口LCD 接口LED ZLG72895vGNDP6口C8051F0203.3V/GND 按键电源开关复位键开发板实物图2.2.2 本开发板的平面图平面图上的位置和板卡的位置一一对应,详细的说明请看后面章节的图2-2 说明。

C8051F020入门指导

➢

端口0–3中所有未被交叉开关分配的引脚都可以作为通用I/O

(GPI/O)引脚,通过读或写相应的端口数据寄存器访问。

➢

被交叉开关分配的那些端口引脚的输出状态受使用这些引脚

的数字外设的控制。

➢

不管交叉开关是否将引脚分配给外设,读一个端口数据寄存器

(或端口位)将总是返回引脚本身的逻辑状态。

➢

交叉开关寄存器被正确配置后,通过将XBARE(XBR2.6)设

上 的 一 方 水 泥块。 水泥块 被黑色 的漆涂 成了黑 色,便 是黑板 了。和 同是学 生的小

伙 伴 们 一 有 时间就 围着黑 板或演 算书写 ,或唱 歌嬉戏 。

学 生 时 代 的快 乐飘飘

荡 荡 结 束 于 一次竞 赛考试 。县城 的中学 是考点 ,进入 考场经 过黑板 时,意 外发现

那 面 黑 色 的 长方形 竟然和 我们教 室的长 方形不 一样——它 的 四围有 木棱子 围着,

捕捉/比较模块。

时间基准的时钟可以是下面的六个时钟源之一:系统时钟/12、系

统时钟/4、定时器0溢出、外部时钟输入(ECI)、系统时钟和外部振

荡源频率/8。

每个捕捉/比较模块都有六种工作方式:边沿触发捕捉、软件定时

器、高速输出、频率输出、8位脉冲宽度调制器和16位脉冲宽度调制

器。

PCA捕捉/比较模块的I/O和外部时钟输入可以通过数字交叉开关

面 不 是 水 泥 的;摸 起来不 是很光 滑,却 也不蹭 手。坐 在教室 靠边的 位置上 ,看黑

板 角 落 的 几 个粉笔 字,竟 然不反 光。考 试结束 了,几 多不解 却没有 消散。 后来终

于 知 道 了 那 长方形 的黑板 叫毛玻 璃。从 此因为 反光而 看不清 楚黑色 水泥黑 板上的

C8051F020 UNI 原型板用户指南说明书

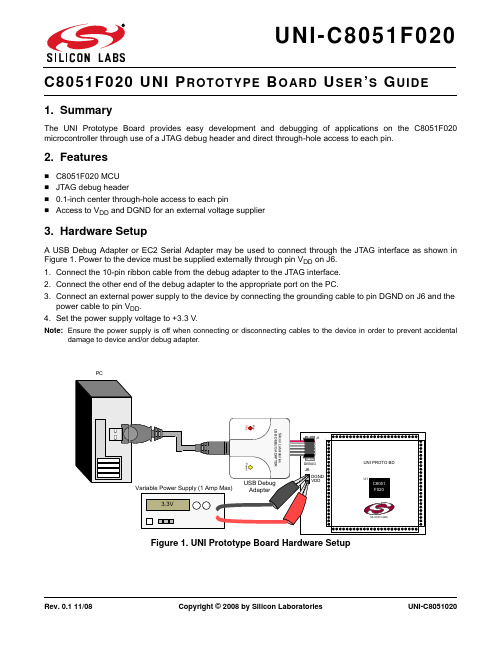

Rev. 0.1 11/08Copyright © 2008 by Silicon LaboratoriesUNI-C8051020ROTOTYPE OARD SER S UIDE1. SummaryThe UNI Prototype Board provides easy development and debugging of applications on the C8051F020microcontroller through use of a JTAG debug header and direct through-hole access to each pin.2. Features⏹C8051F020 MCU ⏹JTAG debug header⏹0.1-inch center through-hole access to each pin⏹Access to V DD and DGND for an external voltage supplier3. Hardware SetupA USB Debug Adapter or EC2 Serial Adapter may be used to connect through the JTAG interface as shown in Figure 1. Power to the device must be supplied externally through pin V DD on J6.1.Connect the 10-pin ribbon cable from the debug adapter to the JTAG interface.2.Connect the other end of the debug adapter to the appropriate port on the PC.3.Connect an external power supply to the device by connecting the grounding cable to pin DGND on J6 and the power cable to pin V DD .4.Set the power supply voltage to +3.3V.Note:Ensure the power supply is off when connecting or disconnecting cables to the device in order to prevent accidentaldamage to device and/or debug adapter.Figure 1.UNI Prototype Board Hardware SetupUNI-C8051F020Table 1. AdaptersUSB Debug Adapter EC2 Serial AdapterPin #Description Pin #Description1,8Not Connected1 3.0 to 3.6 VDC Input2,3,9GND (Ground)2,3,9GND (Ground)4TCK (C2D)4TCK (C2D)5TMS5TMS6TDO6TDO7TDI(C2CK)7TDI(C2CK)10USB Power8,10Not ConnectedDisclaimerSilicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products must not be used within any Life Support System without the specific written consent of Silicon Laboratories. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products are generally not intended for military applications. Silicon Laboratories products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.Trademark InformationSilicon Laboratories Inc., Silicon Laboratories, Silicon Labs, SiLabs and the Silicon Labs logo, CMEMS®, EFM, EFM32, EFR, Energy Micro, Energy Micro logo and combinations thereof, "the world’s most energy friendly microcontrollers", Ember®, EZLink®, EZMac®, EZRadio®, EZRadioPRO®, DSPLL®, ISOmodem ®, Precision32®, ProSLIC®, SiPHY®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.Silicon Laboratories Inc.400 West Cesar Chavez Austin, TX 78701USAIoT Portfolio /IoTSW/HW/simplicityQuality/qualitySupport and Community。

C8051F020-IO初始化

I/O口设置C8051fxx系列单片机使用过程中,常常出现程序的IO口设置,包括设置为交叉开关,推挽方式等。

由于对这种设置方法不太了解,因此做一个专题。

//--------------------------------------------------------------------//I/O初始化程序//--------------------------------------------------------------------//配置交叉开关和GPIO端口void xbar_init(void){XBR0=0x07;//允许I2C SPI和UARTXBR1=0x00;//XBR2=0x40;//允许交叉开关和弱上拉//PRT0CF|=0xff;//允许P0口的所有输出为弱上拉//P0MDOUT//让交叉开关将这些引脚配置为输入//PRT1CF|=0x40;//允许P1.6(LED)为弱上拉输出}(通过对比几个程序的I/O初始化,发现主要是对寄存器XBR0~2以及PRT(0~7)CF进行设置。

特将与IO口设置相关的寄存器做一个说明)1.1GPIO口和数字外设口C8051F020/1/2/3MCU是高集成度的混合信号片上系统,有按8位端口组织的64个数字I/O引脚。

低端口(P0、P1、P2和P3)既可以按位寻址也可以按字节寻址。

高端口(P4、P5、P6和P7)只能按字节寻址。

所有引脚都耐5V电压,都可以被配置为漏极开路或推挽输出方式和弱上拉。

C8051F020/1/2/3器件有大量的数字资源需要通过4个低端I/O端口P0、P1、P2和P3才能使用。

P0、P1、P2和P3中的每个引脚既可定义为通用的端口I/O(GPIO)引脚,又可以分配给一个数字外设或功能(例如:UART0或/INT1),这种资源分配的灵活性是通过使用优先权交叉开关译码器实现的。

注意,不管引脚被分配给一个数字外设或是作为通用I/O,总是可以通过读相应的数据寄存器得到端口I/O引脚的状态。

博嵌电子C8051F仿真器产品说明书

博嵌电子 C8051F 仿真器产品说明书目录目录 (2)一、产品概述 (3)1.1 C8051F 调试工具简介 (3)1.2 产品性能 (4)1.3 仿真器接口定义 (4)二、在 KEIL 下使用 USB Debug Adapter (5)三、使用批量下载工具 (7)Silicon Laboratories Flash Utility (7)Silicon Labs MCU Production Programmer (8)四、EC6 固件更新 (9)一、产品概述1.1 C8051F 调试工具简介C8051F 系列单片机是 Silabs 公司推出的一系列增强型 51 单片机,其指令集兼容传统 MCS-51。

内核采用增强型 CIP-51,其最大指令速率达到 100MIPS,丰富的外设以及灵活的 交叉开关,形成一个 SOC,为目前绝大多数 8 位单片机所不能比拟。

C8051F 单片机目前 正在高速增长,由于具有兼容传统 51 的先天优势,已经被越来越多的爱好者和设计者所青 睐,C8051F 单片机已经进入大学课堂,成为大学单片机教材。

C8051F 单片机开发工具经过多个版本发展,经历了并口、串口、USB-串、USB。

目前, 以及发展到真正的 USB 通信,不再使用串并口或者虚拟串口。

C8051F 开发工具还包括 U-PDC 等,但是使用最方便、最普遍的仍然是 U-EC6。

博嵌电子开发的这款 U-EC6 仿真器采用国外原装电路改进而 来,可实现支持单步、连续单步、断点、 观察点、 堆栈监视器, 可以观察/修改存储器和寄 存器, 下载程序到 Flash 存储器等功能,兼容国内任何一家的 C8051F 调试工具。

多次得到 高校的批量订单,使用效果反馈良好。

请定期去官方网站 /下载最新版本软 件,以达到更好的使用效果。

也可以在国内代理商 下载。

1.2 产品性能- 可与 Keil、silabs 官方推出的各种软件,如 Silicon Laboratories IDE,FLASH Utility Programmer,Product Programmer,新华龙 U-EC5 中文下载程序软件等软件实现无缝连接调 试。

c8051f020端口配置说明

C8051F的每个I/O口引脚都可以被配置为推挽或漏极开路输出。

同时引入了数字交叉开关,允许将内部数字系统资源映射到P0、P1、P2和P3 的端口引脚。

通过设置交叉开关寄存器可将片内的计数器/定时器、串行总线、硬件中断、ADC转换启动输入、比较器输出以及微控制器内部的其他数字信号配置为出现在端口I/O引脚。

必须在访问这些外设的I/O之前配置和允许交叉开关。

注意的问题:1.低端口既能按位寻址,也可以按字节寻址;高端口只能按字节寻址。

2.没有被分配到的引脚作为一般的数字通用I/O口。

3.P1口还可以用作ADC1的模拟输入。

4.P0MDOUT~P3MDOUT用于控制I/O端口每一位的输出状态。

5.EMIF(外部存储器接口)是用于CPU与片外XRAM之间的数据传输通道,通过寄存器EMI0CF 和EMI0CN选择和管理端口实现数据的传输。

6.为了能访问片外存储器空间,必须设置EMI0CN寄存器的内容为片外存储器的空间页地址。

7.如果把外部存储器接口(EMIF)设置在高端口则首先要把EMI0CF的PRTSEL位设置为1,选择高端口,同时选择地址的复用或非复用方式,在把XBR的外部寄存器的EMIFLE位设置为0。

8.复用方式配置:在复用方式下,数据总线和地址总线的第8位共用相同的引脚(AD0~AD7)。

在该方式下,要用一个外部锁存器(如 74HC373或相同功能的锁存器)保持RAM地址的低8位。

外部锁存器由ALE(地址锁存使能)信号控制,ALE信号由外部存储器接口逻辑驱动。

9.在总线复用时,需要把地址数据复用端口配置为漏极开路。

10.ALE高/低脉宽占1个SYSCLK周期,地址建立/保持时间占0个SYSCLK周期,/WR和/RD占12个SYSCLK周期,EMIF工作在地址/数据复用方式,即:EMI0CF |= 0x2c;EMI0TC |= 0x2c;配置EMIF 的步骤是:先将EMIF选到低端口或高端口;然后选择复用方式或非复用方式;再选择存储器的模式(只用片内存储器、不带块选择的分片方式、带块选择的分片方式或只用片外存储器);然后设置EMI0TC;最后通过寄存器PnMDOUT和P74OUT选择所期望的相关端口的输出方式。

C8051F02 X 发展包用户指南说明书

Rev. 0.6 9/06Copyright © 2006 by Silicon LaboratoriesC8051F02x-DKX EVELOPMENT IT SER S UIDE1. Kit ContentsThe C8051F02x Development Kit contains the following items:•C8051F020 Target Board•C8051Fxxx Development Kit Quick-Start Guide•Silicon Laboratories IDE and Product Information CD-ROM. CD content includes:•Silicon Laboratories Integrated Development Environment (IDE)•Keil 8051 Development Tools (macro assembler, linker, evaluation ‘C’ compiler)•Source code examples and register definition files •Documentation•C8051F02x Development Kit User’s Guide (this document)•AC to DC Power Adapter•USB Debug Adapter (USB to Debug Interface)•USB Cable2. Hardware Setup using a USB Debug AdapterThe target board is connected to a PC running the Silicon Laboratories IDE via the USB Debug Adapter as shown in Figure 1.1.Connect the USB Debug Adapter to the JTAG connector on the target board with the 10-pin ribbon cable.2.Connect one end of the USB cable to the USB connector on the USB Debug Adapter.3.Connect the other end of the USB cable to a USB Port on the PC.4.Connect the ac/dc power adapter to power jack P1 on the target board.Notes:•Use the Reset button in the IDE to reset the target when connected using a USB Debug Adapter.•Remove power from the target board and the USB Debug Adapter before connecting or disconnecting the ribbon cable from the target board. Connecting or disconnecting the cable when the devices have power can damage the device and/or the USB Debug Adapter.Figure 1.Hardware Setup using a USB Debug AdapterPWRP1.6C8051F02x-DK3. Software SetupThe included CD-ROM contains the Silicon Laboratories Integrated Development Environment (IDE), Keil software 8051 tools and additional documentation. Insert the CD-ROM into your PC’s CD-ROM drive. An installer will auto-matically launch, allowing you to install the IDE software or read documentation by clicking buttons on the Installa-tion Panel. If the installer does not automatically start when you insert the CD-ROM, run autorun.exe found in the root directory of the CD-ROM. Refer to the readme.txt file on the CD-ROM for the latest information regarding known IDE problems and restrictions.4. Silicon Laboratories Integrated Development EnvironmentThe Silicon Laboratories IDE integrates a source-code editor, source-level debugger and in-system Flash program-mer. The use of third-party compilers and assemblers is also supported. This development kit includes the Keil Software A51 macro assembler, BL51 linker and evaluation version C51 ‘C’ compiler. These tools can be used from within the Silicon Laboratories IDE.4.1. System RequirementsThe Silicon Laboratories IDE requirements:•Pentium-class host PC running Microsoft Windows 98SE or later.•One available COM or USB port.•64 MB RAM and 40MB free HD space recommended.4.2. Assembler and LinkerA full-version Keil A51 macro assembler and BL51 banking linker are included with the development kit and are installed during IDE installation. The complete assembler and linker reference manual can be found under the Help menu in the IDE or in the “Silabs\MCU\hlp” directory (A51.pdf).4.3. Evaluation C51 ‘C’ CompilerAn evaluation version of the Keil C51 ‘C’ compiler is included with the development kit and is installed during IDE installation. The evaluation version of the C51 compiler is the same as the full professional version except code size is limited to 4kB and the floating point library is not included. The C51 compiler reference manual can be found under the Help menu in the IDE or in the “Silabs\MCU\hlp” directory (C51.pdf).4.4. Using the Keil Software 8051 Tools with the Silicon Laboratories IDETo perform source-level debugging with the IDE, you must configure the Keil 8051 tools to generate an absolute object file in the OMF-51 format with object extensions and debug records enabled. You may build the OMF-51 absolute object file by calling the Keil 8051 tools at the command line (e.g. batch file or make file) or by using the project manager built into the IDE. The default configuration when using the Silicon Laboratories IDE project manager enables object extension and debug record generation. Refer to Applications Note AN104 - Integrating Keil 8051 Tools Into the Silicon Laboratories IDE in the “SiLabs\MCU\Documentation\Appnotes” directory on the CD-ROM for additional information on using the Keil 8051 tools with the Silicon Laboratories IDE.To build an absolute object file using the Silicon Laboratories IDE project manager, you must first create a project. A project consists of a set of files, IDE configuration, debug views, and a target build configuration (list of files and tool configurations used as input to the assembler, compiler, and linker when building an output object file).The following sections illustrate the steps necessary to manually create a project with one or more source files, build a program and download the program to the target in preparation for debugging. (The IDE will automatically create a single-file project using the currently open and active source file if you select Build/Make Project before a project is defined.)C8051F02x-DK4.4.1. Creating a New Project1.Select Project→New Project to open a new project and reset all configuration settings to default.2.Select File→New File to open an editor window. Create your source file(s) and save the file(s) with a rec-ognized extension, such as .c, .h, or .asm, to enable color syntax highlighting.3.Right-click on “New Project” in the Project Window. Select Add files to project. Select files in the filebrowser and click Open. Continue adding files until all project files have been added.4.For each of the files in the Project Window that you want assembled, compiled and linked into the targetbuild, right-click on the file name and select Add file to build. Each file will be assembled or compiled as appropriate (based on file extension) and linked into the build of the absolute object file.Note: If a project contains a large number of files, the “Group” feature of the IDE can be used to organize.Right-click on “New Project” in the Project Window. Select Add Groups to project. Add pre-definedgroups or add customized groups. Right-click on the group name and choose Add file to group. Select files to be added. Continue adding files until all project files have been added.4.4.2. Building and Downloading the Program for Debugging1.Once all source files have been added to the target build, build the project by clicking on the Build/MakeProject button in the toolbar or selecting Project→Build/Make Project from the menu.Note: After the project has been built the first time, the Build/Make Project command will only build the files that have been changed since the previous build. To rebuild all files and project dependencies, click on the Rebuild All button in the toolbar or select Project→Rebuild All from the menu.2.Before connecting to the target device, several connection options may need to be set. Open theConnection Options window by selecting Options→Connection Options... in the IDE menu. First, select the appropriate adapter in the “Serial Adapter” section. Next, the correct “Debug Interface” must be selected.C8051F02x family devices use the JTAG debug interface. Once all the selections are made, click the OK button to close the window.3.Click the Connect button in the toolbar or select Debug→Connect from the menu to connect to the device.4.Download the project to the target by clicking the Download Code button in the toolbar.Note: To enable automatic downloading if the program build is successful select Enable automatic con-nect/download after build in the Project→Target Build Configuration dialog. If errors occur during the build process, the IDE will not attempt the download.5.Save the project when finished with the debug session to preserve the current target build configuration,editor settings and the location of all open debug views. To save the project, select Project->Save Project As... from the menu. Create a new name for the project and click on Save.C8051F02x-DK5. Example Source CodeExample source code and register definition files are provided in the “SiLabs\MCU\Examples\C8051F02x” directory during IDE installation. These files may be used as a template for code development. Example applications includea blinking LED example which configures the green LED on the target board to blink at a fixed rate.5.1. Register Definition FilesRegister definition files C8051F020.inc and C8051F020.h define all SFR registers and bit-addressable control/ status bits. They are installed into the “SiLabs\MCU\Examples\C8051F02x” directory during IDE installation. The register and bit names are identical to those used in the C8051F02x data sheet. Both register definition files are also installed in the default search path used by the Keil Software 8051 tools. Therefore, when using the Keil 8051 tools included with the development kit (A51, C51), it is not necessary to copy a register definition file to each project’s file directory.5.2. Blinking LED ExampleThe example source files blink.asm and blinky.c show examples of several basic C8051F02x functions. These include; disabling the watchdog timer (WDT), configuring the Port I/O crossbar, configuring a timer for an interrupt routine, initializing the system clock, and configuring a GPIO port. When compiled/assembled and linked this pro-gram flashes the green LED on the C8051F020 target board about five times a second using the interrupt handler with a C8051F020 timer.C8051F02x-DK 6. Target BoardThe C8051F02x Development Kit includes a target board with a C8051F020 device pre-installed for evaluation and preliminary software development. Numerous input/output (I/O) connections are provided to facilitate prototyping using the target board. Refer to Figure2 for the locations of the various I/O connectors.P1Power connector (accepts input from 7 to 15 VDC unregulated power adapter)J1Connects SW2 to P3.7 pinJ3Connects LED D3 to P1.6 pinJ4JTAG connector for Debug Adapter interfaceJ5DB-9 connector for UART0 RS232 interfaceJ6Connector for UART0 TX (P0.0)J8Connector for UART0 RTS (P4.0)J9Connector for UART0 RX (P0.1)J10Connector for UART0 CTS (P4.1)J11Analog loopback connectorJ12-J19Port 0 - 7 connectorsJ20Analog I/O terminal blockJ22VREF connectorJ23VDD Monitor DisableJ2496-pin Expansion I/O connectorFigure2.C8051F020 Target BoardC8051F02x-DK6.1. System Clock SourcesThe C8051F020 device installed on the target board features a calibrated programmable internal oscillator which is enabled as the system clock source on reset. After reset, the internal oscillator operates at a frequency of 2MHz (±2%) by default but may be configured by software to operate at other frequencies. Therefore, in many applications an external oscillator is not required. However, an external 22.1184MHz crystal is installed on the target board for additional applications. Refer to the C8051F02x data sheet for more information on configuring the system clock source.6.2. Switches and LEDsTwo switches are provided on the target board. Switch SW1 is connected to the RESET pin of the C8051F020. Pressing SW1 puts the device into its hardware-reset state. Switch SW2 is connected to the C8051F020’s general purpose I/O (GPIO) pin through headers. Pressing SW2 generates a logic low signal on the port pin. Remove the shorting block from the header to disconnect SW2 from the port pins. The port pin signal is also routed to a pin on the J24 I/O connector. See Table1 for the port pins and headers corresponding to each switch.Two LEDs are also provided on the target board. The red LED labeled PWR is used to indicate a power connection to the target board. The green LED labeled with a port pin name is connected to the C8051F020’s GPIO pin through headers. Remove the shorting block from the header to disconnect the LED from the port pin. The port pin signal is also routed to a pin on the J24 I/O connector. See Table1 for the port pins and headers corresponding to each LED.Table 1. Target Board I/O DescriptionsDescription I/O HeaderSW1Reset noneSW2P3.7J1Green LED P1.6J3Red LED PWR none6.3. Target Board JTAG Interface (J4)The JTAG connector (J4) provides access to the JTAG pins of the C8051F020. It is used to connect the Serial Adapter or the USB Debug Adapter to the target board for in-circuit debugging and Flash programming. Table2 shows the JTAG pin definitions.Table 2. JTAG Connector Pin DescriptionsPin #Description1+3VD(+3.3VDC)2, 3, 9GND (Ground)4TCK5TMS6TDO7TDI8, 10Not ConnectedC8051F02x-DK6.4. Serial Interface (J5)A RS232 transceiver circuit and DB-9 (J5) connector are provided on the target board to facilitate serial connec-tions to UART0 of the C8051F020. The TX, RX, RTS and CTS signals of UART0 may be connected to the DB-9 connector and transceiver by installing shorting blocks on headers J6, J8, J9 and J10.J6- Install shorting block to connect UART0 TX (P0.0) to the transceiver.J9- Install shorting block to connect UART0 RX (P0.1) to the transceiver.J8- Install shorting block to connect UART0 RTS (P4.0) to the transceiver.J10- Install shorting block to connect UART0 CTS (P4.1) to the transceiver.6.5. Analog I/O (J11, J20)Several C8051F020 analog signals are routed to the J20 terminal block and the J11 connector. Header J11 pro-vides the ability to connect DAC0 and DAC1 outputs to several different analog inputs by installing a shorting block between a DAC output and an analog input on adjacent pins of J11. Refer to Table3 for J20 terminal block connec-tions and Table4 for J11 pin definitions.Table 3. J20 Terminal Block Pin DescriptionsPin #Description1CP0+2CP0-3DAC04DAC15AIN0.06AIN0.17VREF08ADND (Analog Ground)Table 4. J11 Connector Pin DescriptionsPin #Description1CP0+2CP0-3DAC04DAC15CP1+6CP1-7AIN0.08AIN0.19DAC010DAC111AIN0.612AIN0.7C8051F02x-DK6.6. PORT I/O Connectors (J12 - J19)In addition to all port I/O signals being routed to the 96-pin expansion connector, each of the eight parallel ports of the C8051F020 has its own 10-pin header connector. Each connector provides a pin for the corresponding port pins 0-7, +3.3VDC and digital ground. Table 5 defines the pins for the port connectors. The same pin-out order is used for all of the port connectors.6.7. VDD Monitor Disable (J23)The VDD Monitor of the C8051F020 may be disabled by moving the shorting block on J23 from pins 1-2 to pins 2-3, as shown in Figure 3.Figure 3.VDD Monitor Hardware Setup6.8. VREF Connector (J22)The VREF connector (J22) can be used to connect the VREF (Voltage Reference) output of the C8051F020 to any (or all) of its voltage reference inputs. Install shorting blocks on J22 in the following manner:1-2 to connect VREF to VREFD 3-4 to connect VREF to VREF05-6 to connect VREF to VREF1Table 5. J12- J19 Port Connector Pin DescriptionsPin #Description1Pn.02Pn.13Pn.24Pn.35Pn.46Pn.57Pn.68Pn.79+3VD (+3.3VDC)10GND (Ground)C8051F02x-DK6.9. Expansion I/O Connector (J24)The 96-pin expansion I/O connector J24 is used to connect daughter boards to the main target board. J24 provides access to many C8051F020 signal pins. Pins for +3V, digital ground, analog ground and the unregulated power supply (VUNREG) are also available. The VUNREG pin is connected directly to the unregulated +V pin of the P1 power connector. See Table6 for a complete list of pins available at J24.The J24 socket connector is manufactured by Hirose Electronic Co. Ltd, part number PCN13-96S-2.54DS, Digi-Key part number H7096-ND. The corresponding plug connector is also manufactured by Hirose Electronic Co. Ltd, part number PCN10-96P-2.54DS, Digi-Key part number H5096-ND.Table 6. J24 Pin DescriptionsPin #Description Pin #Description Pin #DescriptionA-1+3VD2 (+3.3VDC)B-1DGND (Digital Gnd)C-1XTAL1A-2MONEN B-2P1.7C-2P1.6A-3P1.5B-3P1.4C-3P1.3A-4P1.2B-4P1.1C-4P1.0A-5P2.7B-5P2.6C-5P2.5A-6P2.4B-6P2.3C-6P2.2A-7P2.1B-7P2.0C-7P3.7A-8P3.6B-8P3.5C-8P3.4A-9P3.3B-9P3.2C-9P3.1A-10P3.0B-10P0.7C-10P0.6A-11P0.5B-11P0.4C-11P0.3A-12P0.2B-12P0.1C-12P0.0A-13P7.7B-13P7.6C-13P7.5A-14P7.4B-14P7.3C-14P7.2A-15P7.1B-15P7.0C-15P6.7A-16P6.6B-16P6.5C-16P6.4A-17P6.3B-17P6.2C-17P6.1A-18P6.0B-18P5.7C-18P5.6A-19P5.5B-19P5.4C-19P5.3A-20P5.2B-20P5.1C-20P5.0A-21P4.7B-21P4.6C-21P4.5A-22P4.4B-22P4.3C-22P4.2A-23P4.1B-23P4.0C-23TMSA-24TCK B-24TDI C-24TDOA-25/RST B-25DGND (Digital Gnd)C-25VUNREGA-26AGND (Analog Gnd)B-26DAC1C-26DAC0A-27CP1-B-27CP1+C-27CP0-A-28CP0+B-28VREF C-28VREFDA-29VREF0B-29VREF1C-29AIN0.7A-30AIN0.6B-30AIN0.5C-30AIN0.4A-31AIN0.3B-31AIN0.2C-31AIN0.1A-32AIN0.0B-32AGND (Analog Gnd)C-32AV+ (+3.3VDC Analog)C8051F02x-DK 7. SchematicC8051F02x-DK D OCUMENT C HANGE L ISTRevision 0.4 to Revision 0.5⏹Section 1, added USB Debug Adapter and USB Cable.⏹Section 2, changed name from "Hardware Setup" to "Hardware Setup using an EC2 Serial Adapter".⏹Section 2, added 2 Notes bullets.⏹Section 2, removed Note from bottom of page.⏹Added Section 3, "Hardware Setup using a USB Debug Adapter".⏹Section 5.4.2, changed step 2 to include new instructions.⏹Section 7, J4, changed "Serial Adapter" to "Debug Adapter".⏹Target Board DEBUG Interface Section, added USB Debug Adapter.⏹DEBUG Connector Pin Descriptions Table, changed pin 4 to C2D.⏹Changed "jumper" to "header".⏹EC2 Serial Adapter section, added EC2 to the section title, table title and figure title.⏹EC2 Serial Adapter section, changed "JTAG" to "DEBUG".⏹Added "USB Debug Adapter" section.⏹Added J8 and J10 to the figure in the Target Board section.⏹Added J8 and J10 to the connector list.Revision 0.5 to Revision 0.6⏹Removed EC2 Serial Adapter from Kit Contents.⏹Removed Section 2. Hardware Setup using an EC2 Serial Adapter. See RS232 Serial Adapter (EC2) User'sGuide.⏹Removed Section 8. EC2 Serial Adapter. See RS232 Serial Adapter (EC2) User's Guide.⏹Removed Section 9. USB Debug Adapter. See USB Debug Adapter User's Guide.DisclaimerSilicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products must not be used within any Life Support System without the specific written consent of Silicon Laboratories. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products are generally not intended for military applications. Silicon Laboratories products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.Trademark InformationSilicon Laboratories Inc., Silicon Laboratories, Silicon Labs, SiLabs and the Silicon Labs logo, CMEMS®, EFM, EFM32, EFR, Energy Micro, Energy Micro logo and combinations thereof, "the world’s most energy friendly microcontrollers", Ember®, EZLink®, EZMac®, EZRadio®, EZRadioPRO®, DSPLL®, ISOmodem ®, Precision32®, ProSLIC®, SiPHY®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders. Silicon Laboratories Inc.400 West Cesar ChavezAustin, TX 78701USAIoT Portfolio/IoT SW/HW /simplicity Quality /quality Support and Community 。

C8051F的SMBus配置和操作使用

Rev. 1.3 12/03Copyright © 2003 by Silicon LaboratoriesAN113-DS13AN113S E R I A L C O M M U N I C A T I O N W I T H T H E SMB U S Relevant DevicesThis application note applies to the following devices:C8051F000, C8051F001, C8051F002, C8051F005, C8051F006, C8051F010, C8051F011, C8051F012, C8051F020, C8051F021, C8051F022, and C8051F023.IntroductionC8051F0xx devices are equipped with an SMBus serial I/O device that is compliant with the System Management Bus Specification version 1.1, as well as the I 2C serial bus. The SMBus is a bi-direc-tional, 2-wire interface capable of communication with multiple devices. SMBus is a trademark of Intel; I 2C is a trademark of Philips Semiconductor.This application note describes configuration and operation of the SMBus. Example assembly and C code is given: (1) Interfacing a single EEPROM with 1-byte address space, in assembly; (2) Inter-facing multiple EEPROMs with 2-byte address space, in C; and (3) Peer-to-peer communication between two C8051F0xx devices, in C.SMBus SpecificationThis section presents a description of the SMBus protocol. The SMBus discussion begins in the next section--Using the SMBus.SMBus StructureAn SMBus system is a 2-wire network, where each device has a unique address and may be addressed by any other device on the network. All transfers are initiated by a master device; if a device recog-nizes its own address and responds, it becomes the slave device for that transfer. It is important to notethat assigning one specified master device is not necessary. Any device may assume the role of mas-ter or slave for any particular transfer. In the case that two devices attempt to initiate a transfer simul-taneously, an arbitration scheme forces one device to give up the bus. This arbitration scheme is non-destructive (one device wins and no information islost). Arbitration is discussed in depth in the arbi-tration section.Two wires are used in SMBus communication:SDA (serial data), and SCL (serial clock). Each line is bi-directional, with direction depending on what modes the devices are in. The master always supplies SCL; either device may transmit on SDA.Both lines should be connected to a positive power supply through a pull-up circuit. All devices on the SMBus line should have an open-drain or open col-lector output, so that the lines may remain high when the bus is free. The line is pulled low if one or more devices attempts to output a LOW signal. All devices must output a HIGH for the line to stay high. A typical SMBus configuration is shown in Figure 1 on page 2.AN1132Rev. 1.3Figure 2. SMBus TimingAN113Rev. 1.33AN1134Rev. 1.3AN113Rev. 1.35AN1136Rev. 1.3AN113Rev. 1.37Figure 6. Single EERPOM SendSequenceAN1138Rev. 1.3Figure 8. Multiple EEPROM Receive SequenceAN113Rev. 1.39AN11310Rev. 1.3Figure 10. Peer-to-Peer Write SequenceFigure 11. Peer-to-Peer Read SequenceModeStatus CodeSMBus StateTypical ActionM T /M R 0x08START condition transmitted.Load SMB0DAT with Slave Address + R/W0x10Repeated START condition transmitted.Load SMB0DAT with Slave Address + R/WM a s t e r T r a n s m i t t e r0x18Slave Address + W transmitted. ACK received.Load SMB0DAT with data to be transmit-ted. Clear STA0x20Slave Address + W transmitted. NACK received.Acknowledge poll to retry. Set STO + STA 0x28Data byte transmitted. ACK received.1) Load SMB0DAT with next byte, OR 2) Set STO, OR3) Clear STO, then set STA for repeated START 0x30Data byte transmitted. NACK received.1) Retry transfer OR 2) Set STO 0x38Arbitration Lost.Save current dataM a s t e r R e c e i v e r0x40Slave Address + R transmitted. ACK received.Clear STA. Wait for received data.0x48Slave Address + R transmitted. NACK received.Acknowledge poll to retry. Set STO + STA 0x50Data byte received. ACK transmitted.Read SMB0DAT. Wait for next byte. If next byte is last byte, clear AA 0x58Data byte received. NACK transmitted.Set STOS l a v e R e c e i v e r 0x60Own slave address + W received. ACK trans-mitted.Wait for data0x68Arbitration lost in sending SLA + R/W as mas-ter. Own address + W received. ACK transmit-ted.Save current data for retry when bus is free. Wait for data 0x70General call address received. ACK transmit-ted.Wait for data0x78Arbitration lost in sending SLA + R/W as mas-ter. General call address received. ACK trans-mitted.Save current data for retry when bus is free.0x80Data byte received. ACK transmitted.Read SMB0DAT. Wait for next byte or STOP0x88Data byte received. NACK transmitted.Set STO to reset SMBus0x90Data byte received after general call address. ACK transmitted.Read SMB0DAT. Wait for next byte or STOP0x98Data byte received after general call address. NACK transmitted.Set STO to reset SMBus 0xA0STOP or repeated START received.No action necessaryS l a v e T r a n s m i t t e r 0xA8Own address + R received. ACK transmitted.Load SMB0DAT with data to transmit.0xB0Arbitration lost in transmitting SLA + R/W as master. Own address + R received. ACK transmitted.Save current data for retry when bus is free. Load SMB0DAT with data to trans-mit.0xB8Data byte transmitted. ACK received.Load SMB0DAT with data to transmit.0xC0Data byte transmitted. NACK received.Wait for STOP0xC8Last data byte transmitted (AA=0). ACK received.Set STO to reset SMBusS l a v e0xD0SCL Clock High Timer per SMB0CR timed out Set STO to reset SMBus A l l0x00Bus Error (illegal START or STOP)Set STO to reset SMBus 0xF8IdleState does not set SITable 1. SMBus Status Codes and StatesModeStatus CodeSMBus StateTypical Action。

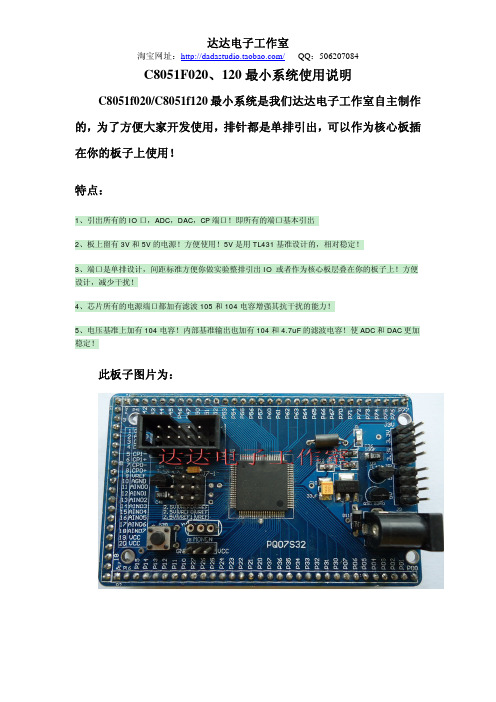

达达电子C8051F020、120最小系统使用说明及原理图

C8051F020、120最小系统使用说明C8051f020/C8051f120最小系统是我们达达电子工作室自主制作的,为了方便大家开发使用,排针都是单排引出,可以作为核心板插在你的板子上使用!特点:1、引出所有的IO口,ADC,DAC,CP端口!即所有的端口基本引出2、板上留有3V和5V的电源!方便使用!5V是用TL431基准设计的,相对稳定!3、端口是单排设计,间距标准方便你做实验整排引出IO 或者作为核心板层叠在你的板子上!方便设计,减少干扰!4、芯片所有的电源端口都加有滤波105和104电容增强其抗干扰的能力!5、电压基准上加有104电容!内部基准输出也加有104和4.7uF的滤波电容!使ADC和DAC更加稳定!此板子图片为:1、板子电源电路020和120芯片工作电压为3.3V,输入电压经过1117-3.3V稳压,输入电压支持5~9V,我们选择的是优质1117芯片。

输入电源测试可以高至12V,但是不建议大家长期使用,以免烧坏芯片!最后电源电压经过2R电阻和105、104电容滤波分别送入MCU得到A VCC和DVCC!以增强MCU工作电压的稳定性这个5V用TL431做的电流经过8050放大,最大可以支持200MA的电流,要使用此5V电压,系统的输入电压要高于6V。

注意:这边过大电流会击穿三极管导致电压高于5V使用的时候需要经常测试是不是5V,经过板子售后情况,建议大家还是少用5V的系统和c8051f的IO连接!最好加有限流电阻,以免经常烧坏MCU!2、板子上电源基准介绍按板子上的介绍,左边是TL431做的2.5V基准!使用的时候需要根据板子上的实际电压来恒定。

一般我们的2.5V误差不会很大,中间一列3个分辨是DAC基准VERFD,ADC0基准VREF0,ADC1的基准VREF1,右边的一列都是内部基准输出VREF,使用跳冒选择。

如需要VREFD使用外部基准2.5V就把跳冒跳在左面。

如果想使用芯片的内部基准就把跳冒跳在右边!3、板子MONEN跳冒的使用如图J8左边为GND中间为MONEN右边是VCC。

C8051F020 最小系统 实验指导手册

工程的建立及配置........................................................................................7 Configuration Wizard 2 的使用介绍............................................................9 液晶显示......................................................................................................15 4.1.1 4.1.2 4.1.3 4.1.4 4.1.5 4.1.6 液晶显示模块简介............................................................................15 硬件连接............................................................................................16 地址计算方法....................................................................................17 RA8835 底层驱动程序..................................................................... 18 程序示例............................................................................................19 综合程序示例....................................................................................21 行列扫描原理介绍............................................................................23 硬件连接............................................................................................23 软件流程图........................................................................................24 示例源程序........................................................................................25 示例工程............................................................................................26 硬件连接............................................................................................30 软件设计............................................................................................30 相关寄存器设置................................................................................31 程序示例............................................................................................34

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

C8051F的每个I/O口引脚都可以被配置为推挽或漏极开路输出。

同时引入了数字交叉开关,允许将部数字系统资源映射到P0、P1、P2和P3 的端口引脚。

通过设置交叉开关寄存器可将片的计数器/定时器、串行总线、硬件中断、ADC转换启动输入、比较器输出以及微控制器部的其他数字信号配置为出现在端口I/O引脚。

必须在访问这些外设的I/O之前配置和允许交叉开关。

注意的问题:1.低端口既能按位寻址,也可以按字节寻址;高端口只能按字节寻址。

2.没有被分配到的引脚作为一般的数字通用I/O口。

3.P1口还可以用作ADC1的模拟输入。

4.P0MDOUT~P3MDOUT用于控制I/O端口每一位的输出状态。

5.EMIF(外部存储器接口)是用于CPU与片外XRAM之间的数据传输通道,通过寄存器EMI0CF 和EMI0CN选择和管理端口实现数据的传输。

6.为了能访问片外存储器空间,必须设置EMI0CN寄存器的容为片外存储器的空间页地址。

7.如果把外部存储器接口(EMIF)设置在高端口则首先要把EMI0CF的PRTSEL位设置为1,选择高端口,同时选择地址的复用或非复用方式,在把XBR的外部寄存器的EMIFLE位设置为0。

8.复用方式配置:在复用方式下,数据总线和地址总线的第8位共用相同的引脚(AD0~AD7)。

在该方式下,要用一个外部锁存器(如74HC373或相同功能的锁存器)保持RAM地址的低8位。

外部锁存器由ALE(地址锁存使能)信号控制,ALE信号由外部存储器接口逻辑驱动。

9.在总线复用时,需要把地址数据复用端口配置为漏极开路。

10.ALE高/低脉宽占1个SYSCLK周期,地址建立/保持时间占0个SYSCLK周期,/WR和/RD占12个SYSCLK周期,EMIF工作在地址/数据复用方式,即:EMI0CF |= 0x2c;EMI0TC |= 0x2c;配置EMIF的步骤是:先将EMIF选到低端口或高端口;然后选择复用方式或非复用方式;再选择存储器的模式(只用片存储器、不带块选择的分片方式、带块选择的分片方式或只用片外存储器);然后设置EMI0TC;最后通过寄存器PnMDOUT和P74OUT选择所期望的相关端口的输出方式。

如:void PORT_Init (void){XBR2 = 0x40; /*使能交叉开关和弱上拉*/P74OUT |= 0xff; /*使能P4~P7推挽输出*/EMI0CF |= 0x2c; /*EMIF工作在地址/数据复用方式,只用外部存储器,ALE高/低脉宽占1个SYSCLK周期*/EMI0TC |= 0x6c; /*地址建立/保持时间占0个SYSCLK周期,/WR和/RD占12个SYSCLK周期*/P3MDOUT |= 0xdf; /*使能P3.5推挽输出*/}11.避免高端口处于“浮空”状态,以避免因输入浮空为无效逻辑电平而导致不必要的功率消耗,为此应采取如下措施的任何一种:a.将XBR2.7位设置为逻辑0选择弱上拉状态R/W R/W R/W R/W R/W R/W R/W R/W 复位值WEAKPUD XBARE - T4EXE T4E UART1E EMIFLE CNVSTE 00000000位7 位6 位5 位4 位3 位2 位1 位0 SFR地址位7 WEAKPUD 弱上拉禁止位0 弱上拉全局允许1 弱上拉全局禁止位6 XBARE 交叉开关允许位0 交叉开关禁止端口0 1 2 和3 的所有引脚被强制为输入方式1 交叉开关允许位5 未用读0 写=忽略位4 T4EXE T4EX 输入允许位0 T4EX 不连到端口引脚1 T4EX 连到端口引脚位3 T4E T4 输入允许位0 T4 不连到端口引脚1 T4 连到端口引脚位2 UART1E UART1 I/O 允许位0 UART1 I/O 不连到端口引脚1 UART1 TX 和RX 连到两个端口引脚位1 EMIFLE 外部存储器接口低端口允许位0 P0.7 P0.6 和P0.5 的功能由交叉开关或端口锁存器决定1 如果EMI0CF.4 = 0 外部存储器接口为复用方式则P0.7 (/WR) P0.6 (/RD)和P0.5 (/ALE)被交叉开关跳过它们的输出状态由端口锁存器和外部存储器接口决定1 如果EMI0CF.4 = 1 外部存储器接口为非复用方式则P0.7 (/WR)和P0.6 (/RD)被交叉开关跳过它们的输出状态由端口锁存器和外部存储器接口决定位0 CNVSTE 外部转换启动输入允许位0 CNVSTR 不连到端口引脚1 CNVSTR 连到端口引脚;b.令P74OUT=0xFF,将高端口输出方式配置为推拉方式(P74OUT为高端口输出方式寄存器);c.向高端口数据寄存器P4、P5、P6和P7写0。

12.配置端口引脚的输出方式每个端口引脚的输出方式都可被配置为漏极开路或推挽方式。

在推挽方式下向端口数据寄存器中的相应位写逻辑0 将使端口引脚被驱动到GND 写逻辑1 将使端口引脚被驱动到VDD ,在漏极开路方式下向端口数据寄存器中的相应位写逻辑0 将使端口引脚被驱动到GND 写逻辑1 将使端口引脚处于高阻状态,当系统中不同器件的端口引脚有共享连接即多个输出连接到同一个物理线时(例如SMBus 连接中的SDA 信号),使用漏极开路方式可以防止不同器件之间的冲突。

(推挽方式在有些书中称为推拉方式)关于开漏、推挽方式,漏级开路即高阻状态,适用于输入/输出,其可独立输入/输出低电平和高阻状态,若需要产生高电平,则需使用外部上拉电阻或使用如LCX245等电平转换芯片。

有些朋友,尤其是未学过此方面知识的朋友,在实际工作中将I/O口设置为漏开,并想输出高电平,但向口线上写1后对方并未认出高电平,但用万用表测量引脚确有电压,这种认为是不对的,对于高阻状态来说,测量电压是无意义的,正确的方法应是外加上拉电阻,上拉电阻的阻值=上拉电压/芯片引脚最大灌(拉)电流。

推挽方式可完全独立产生高低电平,推挽方式为低阻,这样,才能保证口线上不分走电压或分走极小的电压(可忽略),保证输出与电源相同的高电平,推挽适用于输出而不适用于输入,因为若对推挽(低阻)加高电平后,I=U/R,I会很大,将造成口的烧毁。

对与C8051F的很多型号片子,将I/O口设置为推挽方式的做法为:PnMDOUT=0xff,Pn=0x00,这样设置I/O口为推挽,并输出低电平(可降低功耗)将I/O口设置为漏开方式的做法为:PnMDOUT=0x00,Pn=0x11,这样设置I/O口为漏开。

如果学过三极管放大电路一定知道,前置单管放大器和功放末级放大电路的区别。

单片机部的逻辑经过部的逻辑运算后需要输出到外面,外面的器件可能需要较大的电流才能推动,因此在单片机的输出端口必须有一个驱动电路。

这种驱动电路有两种形式:其中的一种是采用一只N型三极管(npn或n沟道),以npn三极管为例,就是e接地,b接部的逻辑运算,c引出,b受部驱动可以控制三极管是否导通但如果三极管的c极一直悬空,尽管b极上发生高低变化,c极上也不会有高低变化,因此在这种条件下必须在外部提供一个电阻,电阻的一端接c(引出脚)另一端接电源,这样当三极管的b有高电压是三极管导通,c电压为低,当b为低电压时三极管不通,c极在电阻的拉动下为高电压,这种驱动电路有个特点:低电压是三极管驱动的,高电压是电阻驱动的(上下不对称),三极管导通时的ec阻很小,因此可以提供很大的电流,可以直接驱动led甚至继电器,但电阻的驱动是有限的,最大高电平输出电流=(vcc-Vh)/r;另一种是互补推挽输出,采用2只晶体管,一只在上一只在下,上面的一只是n型,下面为p型(以三极管为例),两只管子的连接为:npn(上)的c连vcc,pnp(下)的c接地,两只管子的ee,bb相连,其中ee作为输出(引出脚),bb接部逻辑,这个电路通常用于功率放大点路的末级(音响),当bb接高电压时npn管导通输出高电压,由于三极管的ec电阻很小,因此输出的高电压有很强的驱动能力,当bb接低电压时npn截至,pnp导通,由于三极管的ec电阻很小因此输出的低电压有很强的驱动能力,简单的例子,9013导通时ec电阻不到10欧,以Vh=2.5v,vcc=5v计算,高电平输出电流最大=250MA,短路电流500ma,这个计算同时告诉我们采用推挽输出时一定要小心千万不要出现外部电路短路的可能,否则肯定烧毁芯片,特别是外部驱动三极管时别忘了在三极管的基极加限流电阻。

推挽输出电路的形式很多,有些单片机上下都采用n型管,但部逻辑提供互补输出,以上的说明仅仅为了说明推挽的原理,为了更深的理解可以参考功率放大电路。

振荡器问:部时钟振荡器是否稳定?是否可以用于产生波特率的时基?答:不同器件的部时钟振荡器的精度是不同的(±20%)。

随电源电压变化,它也将发生变化(6.5%/V)。

但基本不随温度变化(<1%温度变化围-40℃~+85℃)。

由于不同器件部振荡器的离散性较大,所以不能用于产生波特率,应该外接标准晶体。

而有些器件,如C8051F3xx/f12x/f04x/f06x部振荡器精度为±2%,可用于产生波特率。

问:片/外振荡器如何配置?答:正确步骤:1、允许外部振荡器;2、等待1ms;3、查询XTLVLD '0'->'1'4、切换到外部振荡器。

注意:振荡器频率的选择,即OSCXCN寄存器的配置(外部振荡器频率控制位的设置)。

关于更多的信息以及源代码可以参看应用笔记AN002《配置部和外部振荡器》。

应用笔记可以从我公司下载:.xhl..问:C8051F MCU的指令执行速度为多少?答:C8051F MCU的CIP-51核采用流水线结构,与标准的8051结构相比,指令执行速度有很大的提高。

标准的8051单片机执行一个单周期指令需要12个系统时钟周期,而C8051F MCU执行一个单周期指令只需要一个系统时钟周期。

如果系统时钟频率为25MHz,执行一个单周期指令所需时间为40ns。

问:切换外部晶振时应注意哪些问题?答:首先要允许外部振荡器,但此时的系统时钟源仍应是部时钟,直到外部振荡器稳定后,才可将系统时钟源切换到外部振荡器上,否则会出现切换不过去,系统死机的情况。

问:使用外部晶振应注意哪些问题?答:1、所有的模拟和数字电源引脚都应接电源(2.7~3.6V);2、C8051F3xx系列器件的晶振引脚间应跨接一个10M电阻(在新华龙的“主页”—“原理图/PCB库”中有C8051F系列单片机的典型接线图);3、晶振、电容等相关器件尽量靠近单片机的晶振引脚。

问:系统时钟切换到外部时钟后,部的时钟是否应关闭?答:可以选择关闭或不关闭,但是从降低功耗的角度来说,应该关闭。