c8051f020端口配置说明

C8051F02X外部存储器接口和IO端口配置

C8051F02X外部存储器接口和IO端口配置C8051F02X外部存储器接口和I/O端口配置摘要:介绍美国Cygnal公司生产的C8051F02X系列单片机的外部存储器接口、I/O端口配置方法和有关注意的问题;在此基础上列举两个关于EMIF、I/O的配置应用。

关键词:C8051F02X EMIF I/O 交叉开关美国Cygnal公司C8051F02X系列单片机是集成在一起芯片上的混合信号系统级单片机。

该单片机具有32/64位数字I/O端口(引脚)、25MIPS高速流水线式8051微控制器内核、64KB在系统可编程Flash存储器、64KB地址的外部存储器接口、4352(4096+256)B片内RAM、各自独立的SPI、SMBUS/I2C和两个UART串行接口等特点。

其最突出的优点就是,通过设置交叉开关寄存器控制片内数字资源映射到外部I/O引脚,这就允许用户根据自己的特定应用,选择通用I/O端口和所需要数字资源。

当然,在设置数字交叉开关寄存器时,应该首先考虑EMIF的配置问题。

其配置不同,将导致单片机通过不同的端口(低或高)访问片外存储器和存储器映像的I/O部件,以及数字交叉开关是否分配外部设备给P0.7(WR)、P0.6(RD)、P0.5(ALE)引脚。

(如图EMIF设置为多路器模式。

)1 EMIF和I/O配置方法1.1 外部存储器接口(EMIF)配置C8051F02X系列MCU有4KB的RAM可以只映射在片内,也可以映射在64KB外部数据存储器地址空间,还可以同时映射到片内和片外(4KB地址以内在片内存储器空间访问,4KB以上经过EMIF访问)三种方式。

对于后两种存储器工作模式,需通过外部存储器接口使用MOVX和DPTR或MOVX和R0(R1)指令访问外部数据存储器和存储器映像的I/O设备。

但是对于高8位地址,必须由外部存储器接口寄存器(EMI0CN)提供;而EMIF可将外部数据存储器接口映射到低端口(P0~P3)(F020/2/3系列)或高端口(P4~P7)(F020/2系列),以及配置为复用模式或非复用模式等。

C8051F020学习笔记 串口通信

F020单片机的使用过程当中,有几个重点,一个是定时器和中断,一个是AD和DA,还有一个就是串口通信了。

由于当时设计的时候思想比较混乱,所以直接采用的MAX485作为通信芯片。

对于其具体的实现过程还不是十分的熟悉。

因此,做此专题专门针对与串口通信相关的寄存器做说明。

四,UART0UART0 是一个具有帧错误检测和地址识别硬件的增强型串行口。

UART0 可以工作在全双工异步方式或半双工同步方式,并且支持多处理器通信。

接收数据被暂存于一个保持寄存器中,这就允许UART0 在软件尚未读取前一个数据字节的情况下开始接收第二个输入数据字节。

一个接收覆盖位用于指示新的接收数据已被锁存到接收缓冲器而前一个接收数据尚未被读取。

对UART0 的控制和访问是通过相关的特殊功能寄存器即串行控制寄存器(SCON0)和串行数据缓冲器(SBUF0)来实现的。

一个SBUF0 地址可以访问发送寄存器和接收寄存器。

读操作将自动访问接收寄存器,而写操作自动访问发送寄存器。

UART0 可以工作在查询或中断方式。

UART0 有两个中断源:一个发送中断标志TI0(SCON0.1)(数据字节发送结束时置位)和一个接收中断标志RI0(SCON0.0)(接收完一个数据字节后置位)。

当CPU 转向中断服务程序时硬件不清除UART0 中断标志,中断标志必须用软件清除。

这就允许软件查询UART0 中断的原因(发送完成或接收完成)。

4.1UART0 工作方式UART0 提供四种工作方式(一种同步方式和三种异步方式),通过设置SCON0 寄存器中的配置位选择。

这四种方式提供不同的波特率和通信协议。

下面的表20.1 概述了这四种方式。

表20.1 UART0 工作方式方式同步性波特率时钟数据位起始/停止位0 同步SYSCLK/12 8 无1 异步定时器1 或定时器2 溢出8 一个起始位,一个停止位2 异步SYSCLK/32 或SYSCLK/64 9 一个起始位,一个停止位3 异步定时器1 或定时器2 溢出9 一个起始位,一个停止位方式0 的波特率是系统时钟频率/12。

C8051F020单片机完成16路信号源的输出

二、系统方案论证

本系统有 DA 输出部分、AD 反馈部分、串口输出部分组成,系统框图下:

URAT输 出

电脑上 位机

DA

单片机

AD

多路模 拟开关

跟随输 入

采样保 持部分

滤波电 路

放大部 分

16选1开 关

16路信 号输入

输出

1.单片机部分

图 1.系统流程图

单片机选用 C8051F020,是完全集成的混合信号系统级 MCU 芯片,具有 64

图 14.放大输出电路

图 15.仿真波形

5.串行通信方式的选择与上位机的选择

单片机通过 URAT 发送数据至上位机长采用以下 2 种方法即通过蓝牙或 TTL 转串口线将单片机数据发送到电脑上位机。其中由于蓝牙使用较为方便, 故采用集成蓝牙模块。上位机需要直观显示单片机发出数据,故采用 Serial_Digital_Scope V2。

系统集成与应用 实验报告

2013/2014 学年第 2 学期

学生姓名:

*杰

学 号:

*

学 院:

仪器与电子学院

专 业:

电子科学与技术

题 目 : 用 C8051F020 单片机完成 16 路信号源的输出

指导教师: 焦新泉 2014 年 5 月 15 日

一、 设计任务与要求

单片机C8051F020的初始化设置

单片机C8051F020的初始化设置在喧闹的世界中,能静下心来研究技术也是很有趣的事情。

好多年没作些具体的技术工作了,幸好领导给分配一个单片机任务。

现在把研究的技术写下来,与朋友们分享。

研究C8051F020编程不能离开初始化设置。

对于简单程序,读技术手册,将用到的I/O口,中断,串口,晶振等正确初试化后,已经成功一半了。

晶振需要初始化,C8051F020有内部晶振,精度不高,一般电路都使用外部晶振。

初始化晶振主要是OSCXCN和OSCICN两个寄存器的设置。

具体初始化代码可由Silicon的配置程序自动生成:void Oscillator_Init(){int i = 0;OSCXCN = 0x67;for (i = 0; i < 3000; i++);while ((OSCXCN & 0x80) == 0);OSCICN = 0x08;}上面程序包括了晶振初始化的全部过程:1、使能外部振荡器:OSCXCN = 0x67;2、等待至少1m钟,等待外部振荡器起稳:for (i = 0; i < 3000; i++);3、查询OSCXCN的第八位XTLVLD是否为1,1表明外部振荡器起稳:while ((OSCXCN & 0x80) == 0);4、关内部晶振,切换到外部晶振 OSCICN = 0x08;而同事们的设置是OSCICN= 0x88;应该是使用外部振荡器,但是内部振荡器也没关,这样MCU耗能高些。

串口0(UART0)也需要配置:void UART0_Init (void){SCON0 = 0x50; // SCON0: 模式1,可接收,8位串口TMOD = 0x20; // TMOD: 定时器1, 模式2, 8位自动重载TH1 = -(SYSCLK/BAUDRATE/16); // 设置定时器1TR1 =1; // 开始定时 CKCON |= 0x10; // 定时器用SYSCLK作基准时间PCON |= 0x80; // 禁止UART0波特率/2}SCON0是UART0控制寄存器,用来选择传输模式。

C8051F020概述

9

特殊功能寄存器

SFRs 提供了MCU 资源与外设的控制与数据交换

C8051F020的特殊功能寄存器比典型的8051多两倍左右

C8051F020 增加的SFRS提供了 访问配置并访问此MCU 的子系统的 功能.

这一特性容许它在增加新的功能后还保留了与MCS-51 指 令集兼容的特点。

以0X0或0X8结尾的特殊功能寄存器(例如: P0, TCON, P1, SCON, IE, 等.) 即可以按字节寻址也可以按位寻址

10

特殊功能寄存器

F8 F0 E8 E0

SPI0CN

B ADC0CN ACC

PCA0H

SCON1 PCA0L XBR0

PCA0CPH0

SBUF1 PCA0CPL0 XBR1

TL2 ADC0GTL ADC0CF

DAC1L

TH2 ADC0GTH P1MDIN P74OUT

DAC1H

DAC1CN

SMB0CR

SMB0ST A

SADEN0 OSCXCN SADDR0

ADC0LTL ADC0L FLSCL SADEN1

ADC0LTH ADC0H FLACL EMI0CN

B8

B0

A8 A0

8-bit SAR模拟—数字转换器 (ADC1) 端口1可以被配置为模拟输入 8通道输入多路复用器和可编程增益放大器 ADC 通过它的SFRS进行配置

15

数字—模拟转换器

2个 12-bit 数字—模拟 转换器:DAC0 和 DAC1

DAC通过 VREFD 输 入引脚提供参考电压 DACs 可以作为比较器 参考输入

同时端口1的引脚可以 用作ADC1的模拟输入

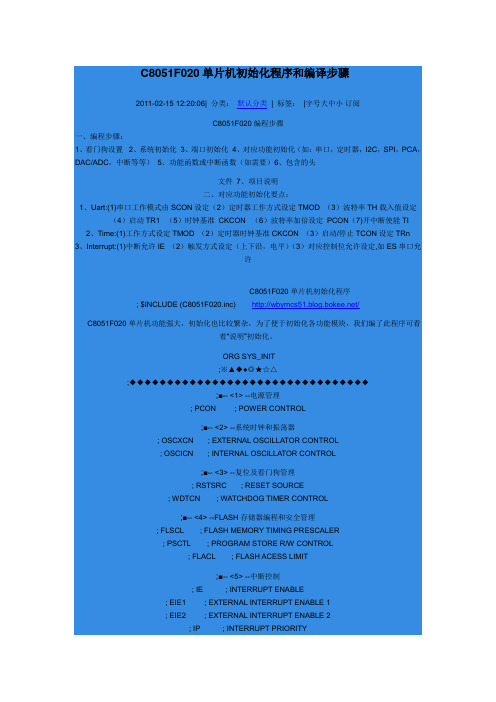

C8051F020单片机初始化

C8051F020单片机初始化程序和编译步骤2011-02-15 12:20:06| 分类:默认分类| 标签:|字号大中小订阅C8051F020编程步骤一、编程步骤:1、看门狗设置2、系统初始化3、端口初始化4、对应功能初始化(如:串口,定时器,I2C,SPI,PCA,DAC/ADC,中断等等)5、功能函数或中断函数(如需要)6、包含的头文件7、项目说明二、对应功能初始化要点:1、Uart:(1)串口工作模式由SCON设定(2)定时器工作方式设定TMOD (3)波特率TH载入值设定(4)启动TR1 (5)时钟基准CKCON (6)波特率加倍设定PCON(7)开中断使能TI2、Time:(1)工作方式设定TMOD (2)定时器时钟基准CKCON (3)启动/停止TCON设定TRn3、Interrupt:(1)中断允许IE (2)触发方式设定(上下沿,电平)(3)对应控制位允许设定,如ES串口允许C8051F020单片机初始化程序; $INCLUDE (C8051F020.inc) /C8051F020单片机功能强大,初始化也比较繁杂,为了便于初始化各功能模块,我们编了此程序可看着“说明”初始化。

ORG SYS_INIT;※▲◆●◎★☆△;◆◆◆◆◆◆◆◆◆◆◆◆◆◆◆◆◆◆◆◆◆◆◆◆◆◆◆◆◆◆◆◆;■-- <1> --电源管理; PCON ; POWER CONTROL;■-- <2> --系统时钟和振荡器; OSCXCN ; EXTERNAL OSCILLATOR CONTROL; OSCICN ; INTERNAL OSCILLA TOR CONTROL;■-- <3> --复位及看门狗管理; RSTSRC ; RESET SOURCE; WDTCN ; WA TCHDOG TIMER CONTROL;■-- <4> --FLASH存储器编程和安全管理; FLSCL ; FLASH MEMORY TIMING PRESCALER; PSCTL ; PROGRAM STORE R/W CONTROL; FLACL ; FLASH ACESS LIMIT;■-- <5> --中断控制; IE ; INTERRUPT ENABLE; EIE1 ; EXTERNAL INTERRUPT ENABLE 1; EIE2 ; EXTERNAL INTERRUPT ENABLE 2; IP ; INTERRUPT PRIORITY; EIP1 ; EXTERNAL INTERRUPT PRIORITY REGISTER 1; EIP2 ; EXTERNAL INTERRUPT PRIORITY REGISTER 2 ; P3IF ; PORT 3 EXTERNAL INTERRUPT FLAGS;■-- <6> --端口IO初始化及交叉开关设置; XBR0 ; DIGITAL CROSSBAR CONFIGURA TION REGISTER 0; XBR1 ; DIGITAL CROSSBAR CONFIGURA TION REGISTER 1; XBR2 ; DIGITAL CROSSBAR CONFIGURA TION REGISTER 2 ; P0MDOUT ; PORT 0 OUTPUT MODE CONFIGURATION; P1MDOUT ; PORT 1 OUTPUT MODE CONFIGURATION; P2MDOUT ; PORT 2 OUTPUT MODE CONFIGURATION; P3MDOUT ; PORT 3 OUTPUT MODE CONFIGURATION; P74OUT ; PORTS 4 - 7 OUTPUT MODE;■-- <7> --外部RAM和片内XRAM; EMI0CN ; EXTERNAL MEMORY INTERFACE CONTROL; EMI0CF ; EXTERNAL MEMORY INTERFACE (EMIF) CONFIGURA TION; EMI0TC ; EXTERNAL MEMORY;■-- <8> --定时器设置; TMOD ; TIMER MODE; TCON ; TIMER CONTROL; T2CON ; TIMER 2 CONTROL; T4CON ; TIMER 4 CONTROL; TMR3CN ; TIMER 3 CONTROL; TMR3RLL ; TIMER 3 RELOAD REGISTER - LOW BYTE; TMR3RLH ; TIMER 3 RELOAD REGISTER - HIGH BYTE; TMR3L ; TIMER 3 - LOW BYTE; TMR3H ; TIMER 3 - HIGH BYTE;■-- <9> --串行通讯; SCON0 ; SERIAL PORT 0 CONTROL; SCON1 ; SERIAL PORT 1 CONTROL; SBUF1 ; SERAIL PORT 1 DA TA; SADDR1 ; SERAIL PORT 1; PCON ; POWER CONTROL; RCAP2L ; TIMER 2 CAPTURE REGISTER - LOW BYTE; RCAP2H ; TIMER 2 CAPTURE REGISTER - HIGH BYTE; RCAP4L ; TIMER 4 CAPTURE REGISTER - LOW BYTE; RCAP4H ; TIMER 4 CAPTURE REGISTER - HIGH BYTE; SADDR0 ; SERIAL PORT 0 SLAVE ADDRESS;■-- <10> --可编程计数器阵列; PCA0CN ; PCA 0 COUNTER CONTROL; PCA0MD ; PCA 0 COUNTER MODE; PCA0CPM0 ; CONTROL REGISTER FOR PCA 0 MODULE 0; PCA0CPM1 ; CONTROL REGISTER FOR PCA 0 MODULE 1; PCA0CPM2 ; CONTROL REGISTER FOR PCA 0 MODULE 2; PCA0CPM3 ; CONTROL REGISTER FOR PCA 0 MODULE 3; PCA0CPM4 ; CONTROL REGISTER FOR PCA 0 MODULE 4;■-- <11> --SMBus通讯; SMB0CN ; SMBUS 0 CONTROL; SMB0CR ; SMBUS 0 CLOCK RA TE; SMB0STA; SMBUS 0 STA TUS; SMB0DA T ; SMBUS 0 DATA; SMB0ADR ; SMBUS 0 SLAVE ADDRESS;■-- <12> --SPI总线通讯; SPI0CKR ; SERIAL PERIPHERAL INTERFACE 0 CLOCK RA TE CONTROL ; SPI0DAT ; SERIAL PERIPHERAL INTERFACE 0 DA TA ; SPI0CFG ; SERIAL PERIPHERAL INTERFACE 0 CONFIGURATION ; SPI0CN ; SERIAL PERIPHERAL INTERFACE 0 CONTROL;-- <13> --ADC转换; AMX0CF ; ADC 0 MUX CONFIGURATION; AMX0SL ; ADC 0 MUX CHANNEL SELECTION; ADC0CF ; ADC 0 CONFIGURA TION; ADC0CN ; ADC 0 CONTROL; ADC0L ; ADC 0 DA TA - LOW BYTE; ADC0H ; ADC 0 DATA - HIGH BYTE; ADC1CF ; ADC 1 ANALOG MUX CONFIGURATION; AMX1SL ; ADC 1 ANALOG MUX CHANNEL SELECT; ADC1CN ; ADC 1 CONTROL; ADC0GTL ; ADC 0 GREA TER-THAN REGISTER - LOW BYTE; ADC0GTH ; ADC 0 GREA TER-THAN REGISTER - HIGH BYTE ; ADC0LTL ; ADC 0 LESS-THAN REGISTER - LOW BYTE; ADC0LTH ; ADC 0 LESS-THAN REGISTER - HIGH BYTE; REF0CN ; VOLTAGE REFERENCE 0 CONTROL; ADC1 ; ADC 1 DA TA;■-- <14> --DAC转换; PCA0L ; PCA 0 TIMER - LOW BYTE; PCA0H ; PCA 0 TIMER - HIGH BYTE; DAC0CN ; DAC 0 CONTROL; DAC1L ; DAC 1 REGISTER - LOW BYTE; DAC1H ; DAC 1 REGISTER - HIGH BYTE; DAC1CN ; DAC 1 CONTROL;■-- <15> --比较器设置; CPT0CN ; COMPARA TOR 0 CONTROL; CPT1CN ; COMPARA TOR 1 CONTROL; EMI0TC ; EMIF TIMING CONTROL;■-- <16> --时钟/电压基准设置; CKCON ; CLOCK CONTROL; SADEN1 ; SERIAL PORT 1 SLAVE ADDRESS MASK; SADEN0 ; SERIAL PORT 0 SLAVE ADDRESS MASK; P1MDIN ; PORT 1 INPUT MODE; PSW ; PROGRAM STATUS WORD; B ; B REGISTER; WDTCN ; WA TCHDOG TIMER CONTROL;◆◆◆◆◆◆◆◆◆◆◆◆◆◆◆◆◆◆◆◆◆◆◆◆◆◆◆◆◆◆◆◆;;==================================================================== ; function: Init_CTS 定时器/计数器,中断和串行通讯初始化子程序; input: -----------------; output: -----------------; usage: -----------------;====================================================================THS0 equ 0a8hTLS0 equ 09ah; THS1 equ 0fah;0feh;0fah;-4800;0f4h; TLS1 equ 0fah;0feh;0fah;-4800;0f4h;; THS2 equ 0ffh;0feh;0fah;-4800;0f4h; TLS2 equ 0b8h;0feh;0fah;-4800;0f4hInit_TCS: ;定时器/计数器,中断和串行通讯初始化子程序;〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓; ◆◆◆8051内部控制寄存器◆◆◆;************************************************************************************ ;|名称| 代号| 地址|位寻| B7 | B6 | B5 | B4 | B3 | B2 | B1 | B0 | ;|--------|------|------|----|-----|------|------|------|------|------|------|------| ;|电源控制| PCON | 87H | NO |SMOD | -- | -- | -- | GF1 | GF0 | PD | IDL | ;|--------|------|------|----|-----|------|------|------|------|------|------|------| ;|计时控制| TCON | 88H | YE |TF1 | TR1 | TF0 | TR0 | IE1 | IT1 | IE0 | IT0 | ;|--------|------|------|----|-----|------|------|------|------|------|------|------|;|计时模式| TMOD | 89H | NO |1GATE| 1C/T | 1M1 | 1M0 | 0GA TE| 0C/T | 0M1 | 0M0 | ;|--------|------|------|----|-----|------|------|------|------|------|------|------|;|串行控制| SCON | 98H | YE |SM0| SM1 | SM2 | REN | TB8 | RB8 | TI | RI | ;|--------|------|------|----|-----|------|------|------|------|------|------|------|;|中断允许| IE | A8H | YE |EA| -- | ET2 | ES | ET1 | EX1 | ET0 | EX0 | ;|--------|------|------|----|-----|------|------|------|------|------|------|------| ;|中断优先| IP | B8H | YE |-- | -- | PT2 | PS | PT1 | PX1 | PT0 | PX0 | ;************************************************************************************;时钟频率为:11.059200MHz;;机器周期为:12/fosc=1.085069μs;;CT0定时器设定延时为:2000μs;;CT0定时器工作于模式0;;CT0溢出处理采用中断方式;;CT0选择内部时钟;;CT0启动由TR0的0/1决定;;设定波特率为:4800bps;;串口0工作于方式1--T1定时器工作于方式2;;串口1工作于模式3--T2定时器用于波特率发生器4800bpsmov TH0, #THS0mov TL0, #TLS0; mov TH1, #THS1; mov TL1, #TLS1; mov TH2, #THS2; mov TL2, #TLS2;▲■-- <1> --电源管理;〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓;87H---PCON-------电源控制寄存器;复位值: 00000000;位7-2:保留。

C8051f020中文资料2

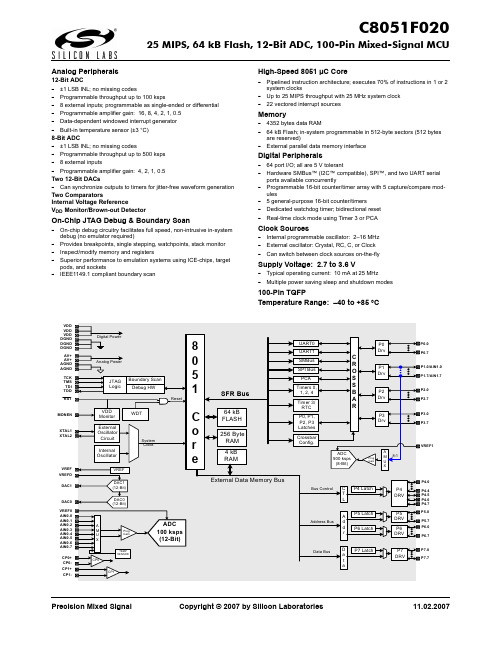

关于C8051F020系统概述C8051F020 器件是完全集成的混合信号系统级 MCU 芯片,具有 64 个数字I/O 引脚(C8051F020)。

下面列出了一些主要特性;有关某一产品的具体特性参见表 1.1;1. 高速、流水线结构的 8051 兼容的 CIP-51 内核(可达 25MIPS)2. 全速、非侵入式的在系统调试接口(片内)3. 真正 12 位(C8051F020)、 100 ksps 的8 通道 ADC,带 PGA和模拟多路开关4. 真正 8 位 500 ksps的 ADC,带 PGA和 8 通道模拟多路开关5. 两个 12 位 DAC,具有可编程数据更新方式6. 64K字节可在系统编程的 FLASH存储器7. 4352(4096+256)字节的片内 RAM8. 可寻址 64K字节地址空间的外部数据存储器接口9. 硬件实现的 SPI、SMBus/ I2C 和两个 UART 串行接口10. 5 个通用的 16 位定时器11. 具有 5 个捕捉/比较模块的可编程计数器/定时器阵列12. 片内看门狗定时器、VDD监视器和温度传感器具有片内 VDD 监视器、看门狗定时器和时钟振荡器的 C8051F020是真正能独立工作的片上系统。

所有模拟和数字外设均可由用户固件使能/禁止和配置。

FLASH 存储器还具有在系统重新编程能力,可用于非易失性数据存储,并允许现场更新 8051 固件。

片内 JTAG调试电路允许使用安装在最终应用系统上的产品 MCU进行非侵入式(不占用片内资源)、全速、在系统调试。

该调试系统支持观察和修改存储器和寄存器,支持断点、观察点、单步及运行和停机命令。

在使用 JTAG调试时,所有的模拟和数字外设都可全功能运行。

每个 MCU都可在工业温度范围(-45℃到+85℃)内用 2.7V-3.6V的电压工作。

端口 I/O、/RST 和 JTAG 引脚都容许 5V 的输入信号电压。

C8051F020 为100 脚 TQFP 封装见图 1.1)。

C8051F020使用说明书

Precision Mixed Signal Copyright © 2007 by Silicon Laboratories11.02.2007Analog Peripherals12-Bit ADC-±1 LSB INL; no missing codes-Programmable throughput up to 100 ksps-8 external inputs; programmable as single-ended or differential -Programmable amplifier gain: 16, 8, 4, 2, 1, 0.5-Data-dependent windowed interrupt generator -Built-in temperature sensor (±3 °C)8-Bit ADC-±1 LSB INL; no missing codes-Programmable throughput up to 500 ksps -8 external inputs-Programmable amplifier gain: 4, 2, 1, 0.5Two 12-Bit DACs-Can synchronize outputs to timers for jitter-free waveform generationTwo ComparatorsInternal Voltage ReferenceV DD Monitor/Brown-out DetectorOn-Chip JTAG Debug & Boundary Scan-On-chip debug circuitry facilitates full speed, non-intrusive in-system debug (no emulator required)-Provides breakpoints, single stepping, watchpoints, stack monitor -Inspect/modify memory and registers-Superior performance to emulation systems using ICE-chips, target pods, and sockets-IEEE1149.1 compliant boundary scanHigh-Speed 8051 µC Core-Pipelined instruction architecture; executes 70% of instructions in 1 or 2 system clocks-Up to 25 MIPS throughput with 25 MHz system clock -22 vectored interrupt sourcesMemory-4352 bytes data RAM-64 kB Flash; in-system programmable in 512-byte sectors (512 bytes are reserved)-External parallel data memory interfaceDigital Peripherals-64 port I/O; all are 5 V tolerant-Hardware SMBus™ (I2C™ compatible), SPI™, and two UART serial ports available concurrently-Programmable 16-bit counter/timer array with 5 capture/compare mod-ules- 5 general-purpose 16-bit counter/timers-Dedicated watchdog timer; bidirectional reset -Real-time clock mode using Timer 3 or PCA Clock Sources-Internal programmable oscillator: 2–16 MHz -External oscillator: Crystal, RC, C, or Clock -Can switch between clock sources on-the-fly Supply Voltage: 2.7 to 3.6 V-Typical operating current: 10 mA at 25 MHz-Multiple power saving sleep and shutdown modes100-Pin TQFPTemperature Range: –40 to +85 °CPrecision Mixed Signal Copyright © 2007 by Silicon Laboratories 11.02.2007Silicon Laboratories and Silicon Labs are trademarks of Silicon Laboratories Inc.Other products or brandnames mentioned herein are trademarks or registered trademarks of their respective holdersSelected Electrical Specifications(T A = –40 to +85 C°, V DD = 2.7 V unless otherwise specified)Package InformationC8051F020DK Development Kit。

EXP-C8051F021使用说明书

CE0

10

------

MSC

11

------

XF

12

------

/BHOLDA

13

------

IAQ

14

------

HOLD

15

------

NC

EXP-C8051F021 适配器板使用说明书

北京达盛科技有限公司

- 11 -

16

------

DGND

17

------

NC

18

55(J7 跳线)

SPICLK1

A14 +5V +5V

达 P2 接口管脚与 FPGA 管脚的对应关系:

P2 端口管脚号 1

C8051F021 管脚号 ------

功能定义 DGND

2

------

DGND

3

------

READY

4

------

PS

5

------

DS

6

------

IS

7

------

R/W

8

------

CE1

9

------

19

------

NC

20

52(J10 跳线)

SPISTE1

21

53(J5 跳线)

NC

22

53(J5 跳线)

SOMI1

23

------

NC

24

55(J7 跳线)

SPICLK1

25

------

NC

26

52(J10 跳线)

SPISTE1

27

------

NC

28

c8051f021需要定义的端口

1:CP0 连到端口引脚。

位6: ECI0E:PCA0 外部计数器输入使能位

0:PCA0 外部计数器输入不连到端口引脚。

1:PCA0 外部计数器输入连到端口引脚。

位5-3: PCA0ME:PCA0 模块I/O 使能位

000:所有的PCA0 I/O 都不连到端口引脚。

00000000

位7 位6 位5 位4 位3 位2 位1 位0 SFR地址:

0xA4

位7-0: P0MDOUT.[7:0]:端口0 输出方式位。

0:端口引脚的输出方式为漏极开路。

1:端口引脚的输出方式为推挽。

注:当SDA、SCL、RX0(当UART0 工作于方式0 时)和RX1(当UART1

位0: SMB0EN:SMBus 总线I/O 使能位

0:SMBus0 I/O 不连到端口引脚。

1:SMBus0 的SDA 和SCL 连到2 个端口引脚。

XBR2:端口I/O 交叉开关寄存器2

R/W R/W R/W R/W R/W R/W R/W R/W 复位值

WEAKPUD XBARE - T4EXE T4E UART1E EMIFLE CNVSTE 00000000

R/W R/W R/W R/W R/W R/W R/W R/W 复位值

11111111

位7 位6 位5 位4 位3 位2 位1 位0 SFR地址:

0xBD

位7-0: P1MDIN.[7:0]:端口1 输入方式位。

0:端口引脚被配置为模拟输入方式。数字输入通路被禁止(读端口位将总是

返回‘0’)。引脚的弱上拉被禁止。

P1MDOUT(图17.14)决定。有关ADC1 的更详细信息见“7. ADC1(8

C8051F020-IO初始化

I/O口设置C8051fxx系列单片机使用过程中,常常出现程序的IO口设置,包括设置为交叉开关,推挽方式等。

由于对这种设置方法不太了解,因此做一个专题。

//--------------------------------------------------------------------//I/O初始化程序//--------------------------------------------------------------------//配置交叉开关和GPIO端口void xbar_init(void){XBR0=0x07;//允许I2C SPI和UARTXBR1=0x00;//XBR2=0x40;//允许交叉开关和弱上拉//PRT0CF|=0xff;//允许P0口的所有输出为弱上拉//P0MDOUT//让交叉开关将这些引脚配置为输入//PRT1CF|=0x40;//允许P1.6(LED)为弱上拉输出}(通过对比几个程序的I/O初始化,发现主要是对寄存器XBR0~2以及PRT(0~7)CF进行设置。

特将与IO口设置相关的寄存器做一个说明)1.1GPIO口和数字外设口C8051F020/1/2/3MCU是高集成度的混合信号片上系统,有按8位端口组织的64个数字I/O引脚。

低端口(P0、P1、P2和P3)既可以按位寻址也可以按字节寻址。

高端口(P4、P5、P6和P7)只能按字节寻址。

所有引脚都耐5V电压,都可以被配置为漏极开路或推挽输出方式和弱上拉。

C8051F020/1/2/3器件有大量的数字资源需要通过4个低端I/O端口P0、P1、P2和P3才能使用。

P0、P1、P2和P3中的每个引脚既可定义为通用的端口I/O(GPIO)引脚,又可以分配给一个数字外设或功能(例如:UART0或/INT1),这种资源分配的灵活性是通过使用优先权交叉开关译码器实现的。

注意,不管引脚被分配给一个数字外设或是作为通用I/O,总是可以通过读相应的数据寄存器得到端口I/O引脚的状态。

c8051f020端口配置说明

C8051F的每个I/O口引脚都可以被配置为推挽或漏极开路输出。

同时引入了数字交叉开关,允许将内部数字系统资源映射到P0、P1、P2和P3 的端口引脚。

通过设置交叉开关寄存器可将片内的计数器/定时器、串行总线、硬件中断、ADC转换启动输入、比较器输出以及微控制器内部的其他数字信号配置为出现在端口I/O引脚。

必须在访问这些外设的I/O之前配置和允许交叉开关。

注意的问题:1.低端口既能按位寻址,也可以按字节寻址;高端口只能按字节寻址。

2.没有被分配到的引脚作为一般的数字通用I/O口。

口还可以用作ADC1的模拟输入。

~P3MDOUT用于控制I/O端口每一位的输出状态。

(外部存储器接口)是用于CPU与片外XRAM之间的数据传输通道,通过寄存器EMI0CF和EMI0CN选择和管理端口实现数据的传输。

6.为了能访问片外存储器空间,必须设置EMI0CN寄存器的内容为片外存储器的空间页地址。

7.如果把外部存储器接口(EMIF)设置在高端口则首先要把EMI0CF的PRTSEL位设置为1,选择高端口,同时选择地址的复用或非复用方式,在把XBR的外部寄存器的EMIFLE位设置为0。

8.复用方式配置:在复用方式下,数据总线和地址总线的第8位共用相同的引脚(AD0~AD7)。

在该方式下,要用一个外部锁存器(如 74HC373或相同功能的锁存器)保持RAM地址的低8位。

外部锁存器由ALE(地址锁存使能)信号控制,ALE信号由外部存储器接口逻辑驱动。

9.在总线复用时,需要把地址数据复用端口配置为漏极开路。

高/低脉宽占1个SYSCLK周期,地址建立/保持时间占0个SYSCLK周期,/WR和/RD占12个SYSCLK 周期,EMIF工作在地址/数据复用方式,即:EMI0CF |= 0x2c;EMI0TC |= 0x2c;配置EMIF的步骤是:先将EMIF选到低端口或高端口;然后选择复用方式或非复用方式;再选择存储器的模式(只用片内存储器、不带块选择的分片方式、带块选择的分片方式或只用片外存储器);然后设置EMI0TC;最后通过寄存器PnMDOUT和P74OUT选择所期望的相关端口的输出方式。

c8051f020端口配置说明

C8051F的每个I/O口引脚都可以被配置为推挽或漏极开路输出。

同时引入了数字交叉开关,允许将内部数字系统资源映射到P0、P1、P2和P3 的端口引脚。

通过设置交叉开关寄存器可将片内的计数器/定时器、串行总线、硬件中断、ADC转换启动输入、比较器输出以及微控制器内部的其他数字信号配置为出现在端口I/O引脚。

必须在访问这些外设的I/O之前配置和允许交叉开关。

注意的问题:1.低端口既能按位寻址,也可以按字节寻址;高端口只能按字节寻址。

2.没有被分配到的引脚作为一般的数字通用I/O口。

3.P1口还可以用作ADC1的模拟输入。

4.P0MDOUT~P3MDOUT用于控制I/O端口每一位的输出状态。

5.EMIF(外部存储器接口)是用于CPU与片外XRAM之间的数据传输通道,通过寄存器EMI0CF 和EMI0CN选择和管理端口实现数据的传输。

6.为了能访问片外存储器空间,必须设置EMI0CN寄存器的内容为片外存储器的空间页地址。

7.如果把外部存储器接口(EMIF)设置在高端口则首先要把EMI0CF的PRTSEL位设置为1,选择高端口,同时选择地址的复用或非复用方式,在把XBR的外部寄存器的EMIFLE位设置为0。

8.复用方式配置:在复用方式下,数据总线和地址总线的第8位共用相同的引脚(AD0~AD7)。

在该方式下,要用一个外部锁存器(如 74HC373或相同功能的锁存器)保持RAM地址的低8位。

外部锁存器由ALE(地址锁存使能)信号控制,ALE信号由外部存储器接口逻辑驱动。

9.在总线复用时,需要把地址数据复用端口配置为漏极开路。

10.ALE高/低脉宽占1个SYSCLK周期,地址建立/保持时间占0个SYSCLK周期,/WR和/RD占12个SYSCLK周期,EMIF工作在地址/数据复用方式,即:EMI0CF |= 0x2c;EMI0TC |= 0x2c;配置EMIF 的步骤是:先将EMIF选到低端口或高端口;然后选择复用方式或非复用方式;再选择存储器的模式(只用片内存储器、不带块选择的分片方式、带块选择的分片方式或只用片外存储器);然后设置EMI0TC;最后通过寄存器PnMDOUT和P74OUT选择所期望的相关端口的输出方式。

c8051F020寄存器

3位:AD1VRS-ADC1电压基准选择位,定义:0(取引脚电压)1(取AV+)

2位:TEMPE:温度传感器使能,定义,0(关闭),1(开启)

1位:BIASE-ADC/DAC偏压器发生使能,定义:0(关闭),1(开启)

0位:REFBE内部电压基准缓冲器使能,定义:0(关闭),1(开启)

CPT0CN(比较器0控制寄存器)0x9E

1位:PT0定时器0中断优先级控制,定义:0(低优先),1(高优先)

0位:PX0外部中断0优先级控制,定义:0(低优先),1(高优先)

EIE1(扩展中断允许1)0xE6

7

6

5

4

3

2

1

0

ECP1R ECP1F ECPDR ECP0F EPCA0 EWADC0 ESMB0 ESPI0

7位:ECP1R允许比较器1上升沿中断,定义:0(禁止),1(允许CPT1CN中断)

ADC0H(ADC数据字MSB寄存器)0xBF

7

6

5

4

3

2

1

0

7-0位:ADC0数据字高字节,当AD0LJST=0,7-4位为扩展,3-0是高4位。

当ADOLJST=1,7-0位为ADC0数据高8位

ADC0L(ADC数据字LSB寄存器)0xBE

7

6

5

4

3

2

1

0

7-0位:ADC0数据字高字节,当AD0LJST=0,7-0位为ADC0数据高8位

7

6

5

4

3

2

1

0

数据

DAC1L(DAC1低字节寄存器)0xD5

7

6

5

4

3

2

1

C8051F的SMBus配置和操作使用

Rev. 1.3 12/03Copyright © 2003 by Silicon LaboratoriesAN113-DS13AN113S E R I A L C O M M U N I C A T I O N W I T H T H E SMB U S Relevant DevicesThis application note applies to the following devices:C8051F000, C8051F001, C8051F002, C8051F005, C8051F006, C8051F010, C8051F011, C8051F012, C8051F020, C8051F021, C8051F022, and C8051F023.IntroductionC8051F0xx devices are equipped with an SMBus serial I/O device that is compliant with the System Management Bus Specification version 1.1, as well as the I 2C serial bus. The SMBus is a bi-direc-tional, 2-wire interface capable of communication with multiple devices. SMBus is a trademark of Intel; I 2C is a trademark of Philips Semiconductor.This application note describes configuration and operation of the SMBus. Example assembly and C code is given: (1) Interfacing a single EEPROM with 1-byte address space, in assembly; (2) Inter-facing multiple EEPROMs with 2-byte address space, in C; and (3) Peer-to-peer communication between two C8051F0xx devices, in C.SMBus SpecificationThis section presents a description of the SMBus protocol. The SMBus discussion begins in the next section--Using the SMBus.SMBus StructureAn SMBus system is a 2-wire network, where each device has a unique address and may be addressed by any other device on the network. All transfers are initiated by a master device; if a device recog-nizes its own address and responds, it becomes the slave device for that transfer. It is important to notethat assigning one specified master device is not necessary. Any device may assume the role of mas-ter or slave for any particular transfer. In the case that two devices attempt to initiate a transfer simul-taneously, an arbitration scheme forces one device to give up the bus. This arbitration scheme is non-destructive (one device wins and no information islost). Arbitration is discussed in depth in the arbi-tration section.Two wires are used in SMBus communication:SDA (serial data), and SCL (serial clock). Each line is bi-directional, with direction depending on what modes the devices are in. The master always supplies SCL; either device may transmit on SDA.Both lines should be connected to a positive power supply through a pull-up circuit. All devices on the SMBus line should have an open-drain or open col-lector output, so that the lines may remain high when the bus is free. The line is pulled low if one or more devices attempts to output a LOW signal. All devices must output a HIGH for the line to stay high. A typical SMBus configuration is shown in Figure 1 on page 2.AN1132Rev. 1.3Figure 2. SMBus TimingAN113Rev. 1.33AN1134Rev. 1.3AN113Rev. 1.35AN1136Rev. 1.3AN113Rev. 1.37Figure 6. Single EERPOM SendSequenceAN1138Rev. 1.3Figure 8. Multiple EEPROM Receive SequenceAN113Rev. 1.39AN11310Rev. 1.3Figure 10. Peer-to-Peer Write SequenceFigure 11. Peer-to-Peer Read SequenceModeStatus CodeSMBus StateTypical ActionM T /M R 0x08START condition transmitted.Load SMB0DAT with Slave Address + R/W0x10Repeated START condition transmitted.Load SMB0DAT with Slave Address + R/WM a s t e r T r a n s m i t t e r0x18Slave Address + W transmitted. ACK received.Load SMB0DAT with data to be transmit-ted. Clear STA0x20Slave Address + W transmitted. NACK received.Acknowledge poll to retry. Set STO + STA 0x28Data byte transmitted. ACK received.1) Load SMB0DAT with next byte, OR 2) Set STO, OR3) Clear STO, then set STA for repeated START 0x30Data byte transmitted. NACK received.1) Retry transfer OR 2) Set STO 0x38Arbitration Lost.Save current dataM a s t e r R e c e i v e r0x40Slave Address + R transmitted. ACK received.Clear STA. Wait for received data.0x48Slave Address + R transmitted. NACK received.Acknowledge poll to retry. Set STO + STA 0x50Data byte received. ACK transmitted.Read SMB0DAT. Wait for next byte. If next byte is last byte, clear AA 0x58Data byte received. NACK transmitted.Set STOS l a v e R e c e i v e r 0x60Own slave address + W received. ACK trans-mitted.Wait for data0x68Arbitration lost in sending SLA + R/W as mas-ter. Own address + W received. ACK transmit-ted.Save current data for retry when bus is free. Wait for data 0x70General call address received. ACK transmit-ted.Wait for data0x78Arbitration lost in sending SLA + R/W as mas-ter. General call address received. ACK trans-mitted.Save current data for retry when bus is free.0x80Data byte received. ACK transmitted.Read SMB0DAT. Wait for next byte or STOP0x88Data byte received. NACK transmitted.Set STO to reset SMBus0x90Data byte received after general call address. ACK transmitted.Read SMB0DAT. Wait for next byte or STOP0x98Data byte received after general call address. NACK transmitted.Set STO to reset SMBus 0xA0STOP or repeated START received.No action necessaryS l a v e T r a n s m i t t e r 0xA8Own address + R received. ACK transmitted.Load SMB0DAT with data to transmit.0xB0Arbitration lost in transmitting SLA + R/W as master. Own address + R received. ACK transmitted.Save current data for retry when bus is free. Load SMB0DAT with data to trans-mit.0xB8Data byte transmitted. ACK received.Load SMB0DAT with data to transmit.0xC0Data byte transmitted. NACK received.Wait for STOP0xC8Last data byte transmitted (AA=0). ACK received.Set STO to reset SMBusS l a v e0xD0SCL Clock High Timer per SMB0CR timed out Set STO to reset SMBus A l l0x00Bus Error (illegal START or STOP)Set STO to reset SMBus 0xF8IdleState does not set SITable 1. SMBus Status Codes and StatesModeStatus CodeSMBus StateTypical Action。

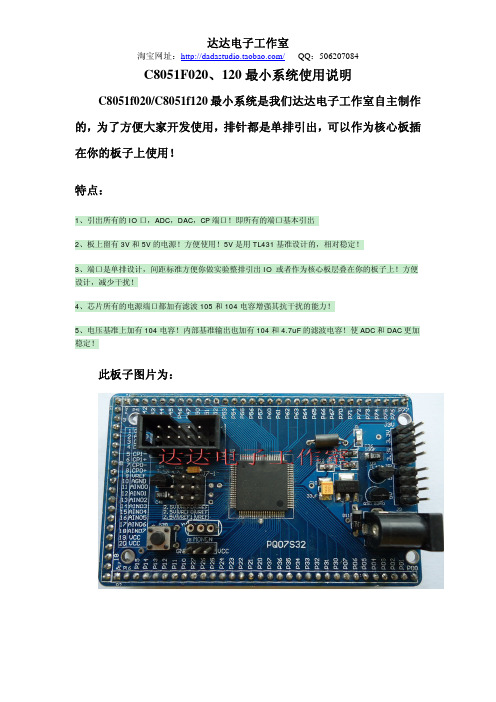

达达电子C8051F020、120最小系统使用说明及原理图

C8051F020、120最小系统使用说明C8051f020/C8051f120最小系统是我们达达电子工作室自主制作的,为了方便大家开发使用,排针都是单排引出,可以作为核心板插在你的板子上使用!特点:1、引出所有的IO口,ADC,DAC,CP端口!即所有的端口基本引出2、板上留有3V和5V的电源!方便使用!5V是用TL431基准设计的,相对稳定!3、端口是单排设计,间距标准方便你做实验整排引出IO 或者作为核心板层叠在你的板子上!方便设计,减少干扰!4、芯片所有的电源端口都加有滤波105和104电容增强其抗干扰的能力!5、电压基准上加有104电容!内部基准输出也加有104和4.7uF的滤波电容!使ADC和DAC更加稳定!此板子图片为:1、板子电源电路020和120芯片工作电压为3.3V,输入电压经过1117-3.3V稳压,输入电压支持5~9V,我们选择的是优质1117芯片。

输入电源测试可以高至12V,但是不建议大家长期使用,以免烧坏芯片!最后电源电压经过2R电阻和105、104电容滤波分别送入MCU得到A VCC和DVCC!以增强MCU工作电压的稳定性这个5V用TL431做的电流经过8050放大,最大可以支持200MA的电流,要使用此5V电压,系统的输入电压要高于6V。

注意:这边过大电流会击穿三极管导致电压高于5V使用的时候需要经常测试是不是5V,经过板子售后情况,建议大家还是少用5V的系统和c8051f的IO连接!最好加有限流电阻,以免经常烧坏MCU!2、板子上电源基准介绍按板子上的介绍,左边是TL431做的2.5V基准!使用的时候需要根据板子上的实际电压来恒定。

一般我们的2.5V误差不会很大,中间一列3个分辨是DAC基准VERFD,ADC0基准VREF0,ADC1的基准VREF1,右边的一列都是内部基准输出VREF,使用跳冒选择。

如需要VREFD使用外部基准2.5V就把跳冒跳在左面。

如果想使用芯片的内部基准就把跳冒跳在右边!3、板子MONEN跳冒的使用如图J8左边为GND中间为MONEN右边是VCC。

C8051F020 最小系统 实验指导手册

工程的建立及配置........................................................................................7 Configuration Wizard 2 的使用介绍............................................................9 液晶显示......................................................................................................15 4.1.1 4.1.2 4.1.3 4.1.4 4.1.5 4.1.6 液晶显示模块简介............................................................................15 硬件连接............................................................................................16 地址计算方法....................................................................................17 RA8835 底层驱动程序..................................................................... 18 程序示例............................................................................................19 综合程序示例....................................................................................21 行列扫描原理介绍............................................................................23 硬件连接............................................................................................23 软件流程图........................................................................................24 示例源程序........................................................................................25 示例工程............................................................................................26 硬件连接............................................................................................30 软件设计............................................................................................30 相关寄存器设置................................................................................31 程序示例............................................................................................34

C8051F020中的ADC应用要素

C8051F020中的ADC应用要素摘要:归纳SOC型芯片C8051F020中模数转换部分的应用要素,包括精度与通道、速率与启动、基准与增益、数据与控制,提出编程及相关SFR的操作顺序。

关键词:片上系统(SOC)A/D转换(ADC)特殊功能寄存器(SFR)C8051F020(简称F020)是美国德州Cygnal 公司推出的一种混合信号SO C型8位单片机。

它属于C8051F系列中的F02X子系列。

其性能价格比在目前应用领域极具竞争力。

F020具有8路12位A/D转换(简称ADC)接口和8路8位在线可编程(ISP)的ADC电路,片上的特殊功能寄存器(简称SFR)有15个与ADC的控制相关,它们是:AMUX0SL-AMUX0通道选择寄存器,复位值为00000000;AMX0CF-AMUX0配置寄存器,复位值为00000000;ADC0CF-ADC0配置寄存器,复位值为11111000;ADC0CN-ADC0控制寄存器,复位值为00000000;ADC0H-ADC0数据字MSB寄存器,复位值为00000000;ADC0L-ADC0数据字LSB寄存器,复位值为00000000;ADC0GTH-ADC0下限数据高字节寄存器,复位值为11111111;ADC0GTL-ADC0下限数据低字节寄存器,复位值为11111111;ADC0LTH-ADC0上限数据高字节寄存器,复位值为00000000;ADC0LTL-ADC0上限数据低字节寄存器,复位值为00000000;AMX1SL-AMUX1通道选择寄存器,复位值为00000000;ADC1CN-ADC1控制寄存器,复位值为00000000;ADC1CF-ADC1配置寄存器,复位值为11111000;ADC1-ADC1数据字寄存器,复位值为00000000;REF0CN-基准电压控制寄存器,复位值为00000000;ADC是混合信号控制器的重要功能,如欲在应用编程中得心应手,就必须对其相关的要素有较清晰的整体认识。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

C8051F的每个I/O口引脚都可以被配置为推挽或漏极开路输出。

同时引入了数字交叉开关,允许将内部数字系统资源映射到P0、P1、P2和P3 的端口引脚。

通过设置交叉开关寄存器可将片内的计数器/定时器、串行总线、硬件中断、ADC转换启动输入、比较器输出以及微控制器内部的其他数字信号配置为出现在端口I/O引脚。

必须在访问这些外设的I/O之前配置和允许交叉开关。

注意的问题:1.低端口既能按位寻址,也可以按字节寻址;高端口只能按字节寻址。

2.没有被分配到的引脚作为一般的数字通用I/O口。

3.P1口还可以用作ADC1的模拟输入。

4.P0MDOUT~P3MDOUT用于控制I/O端口每一位的输出状态。

5.EMIF(外部存储器接口)是用于CPU与片外XRAM之间的数据传输通道,通过寄存器EMI0CF 和EMI0CN选择和管理端口实现数据的传输。

6.为了能访问片外存储器空间,必须设置EMI0CN寄存器的内容为片外存储器的空间页地址。

7.如果把外部存储器接口(EMIF)设置在高端口则首先要把EMI0CF的PRTSEL位设置为1,选择高端口,同时选择地址的复用或非复用方式,在把XBR的外部寄存器的EMIFLE位设置为0。

8.复用方式配置:在复用方式下,数据总线和地址总线的第8位共用相同的引脚(AD0~AD7)。

在该方式下,要用一个外部锁存器(如74HC373或相同功能的锁存器)保持RAM地址的低8位。

外部锁存器由ALE(地址锁存使能)信号控制,ALE信号由外部存储器接口逻辑驱动。

9.在总线复用时,需要把地址数据复用端口配置为漏极开路。

10.ALE高/低脉宽占1个SYSCLK周期,地址建立/保持时间占0个SYSCLK周期,/WR和/RD占12个SYSCLK周期,EMIF工作在地址/数据复用方式,即:EMI0CF |= 0x2c;EMI0TC |= 0x2c;配置EMIF的步骤是:先将EMIF选到低端口或高端口;然后选择复用方式或非复用方式;再选择存储器的模式(只用片内存储器、不带块选择的分片方式、带块选择的分片方式或只用片外存储器);然后设置EMI0TC;最后通过寄存器PnMDOUT和P74OUT选择所期望的相关端口的输出方式。

如:void PORT_Init (void){XBR2 = 0x40; /*使能交叉开关和弱上拉*/P74OUT |= 0xff; /*使能P4~P7推挽输出*/EMI0CF |= 0x2c; /*EMIF工作在地址/数据复用方式,只用外部存储器,ALE高/低脉宽占1个SYSCLK周期*/EMI0TC |= 0x6c; /*地址建立/保持时间占0个SYSCLK周期,/WR和/RD占12个SYSCLK周期*/P3MDOUT |= 0xdf; /*使能P3.5推挽输出*/}11.避免高端口处于“浮空”状态,以避免因输入浮空为无效逻辑电平而导致不必要的功率消耗,为此应采取如下措施的任何一种:a.将XBR2.7位设置为逻辑0选择弱上拉状态R/W R/W R/W R/W R/W R/W R/W R/W 复位值WEAKPUD XBARE - T4EXE T4E UART1E EMIFLE CNVSTE 00000000位7 位6 位5 位4 位3 位2 位1 位0 SFR地址位7 WEAKPUD 弱上拉禁止位0 弱上拉全局允许1 弱上拉全局禁止位6 XBARE 交叉开关允许位0 交叉开关禁止端口0 1 2 和3 的所有引脚被强制为输入方式1 交叉开关允许位5 未用读0 写=忽略位4 T4EXE T4EX 输入允许位0 T4EX 不连到端口引脚1 T4EX 连到端口引脚位3 T4E T4 输入允许位0 T4 不连到端口引脚1 T4 连到端口引脚位2 UART1E UART1 I/O 允许位0 UART1 I/O 不连到端口引脚1 UART1 TX 和RX 连到两个端口引脚位1 EMIFLE 外部存储器接口低端口允许位0 P0.7 P0.6 和P0.5 的功能由交叉开关或端口锁存器决定1 如果EMI0CF.4 = 0 外部存储器接口为复用方式则P0.7 (/WR) P0.6 (/RD)和P0.5 (/ALE)被交叉开关跳过它们的输出状态由端口锁存器和外部存储器接口决定1 如果EMI0CF.4 = 1 外部存储器接口为非复用方式则P0.7 (/WR)和P0.6 (/RD)被交叉开关跳过它们的输出状态由端口锁存器和外部存储器接口决定位0 CNVSTE 外部转换启动输入允许位0 CNVSTR 不连到端口引脚1 CNVSTR 连到端口引脚;b.令P74OUT=0xFF,将高端口输出方式配置为推拉方式(P74OUT为高端口输出方式寄存器);c.向高端口数据寄存器P4、P5、P6和P7写0。

12.配置端口引脚的输出方式每个端口引脚的输出方式都可被配置为漏极开路或推挽方式。

在推挽方式下向端口数据寄存器中的相应位写逻辑0 将使端口引脚被驱动到GND 写逻辑1 将使端口引脚被驱动到VDD ,在漏极开路方式下向端口数据寄存器中的相应位写逻辑0 将使端口引脚被驱动到GND 写逻辑1 将使端口引脚处于高阻状态,当系统中不同器件的端口引脚有共享连接即多个输出连接到同一个物理线时(例如SMBus 连接中的SDA 信号),使用漏极开路方式可以防止不同器件之间的冲突。

(推挽方式在有些书中称为推拉方式)关于开漏、推挽方式,漏级开路即高阻状态,适用于输入/输出,其可独立输入/输出低电平和高阻状态,若需要产生高电平,则需使用外部上拉电阻或使用如LCX245等电平转换芯片。

有些朋友,尤其是未学过此方面知识的朋友,在实际工作中将I/O口设置为漏开,并想输出高电平,但向口线上写1后对方并未认出高电平,但用万用表测量引脚确有电压,这种认为是不对的,对于高阻状态来说,测量电压是无意义的,正确的方法应是外加上拉电阻,上拉电阻的阻值=上拉电压/芯片引脚最大灌(拉)电流。

推挽方式可完全独立产生高低电平,推挽方式为低阻,这样,才能保证口线上不分走电压或分走极小的电压(可忽略),保证输出与电源相同的高电平,推挽适用于输出而不适用于输入,因为若对推挽(低阻)加高电平后,I=U/R,I会很大,将造成口的烧毁。

对与C8051F的很多型号片子,将I/O口设置为推挽方式的做法为:PnMDOUT=0xff,Pn=0x00,这样设置I/O口为推挽,并输出低电平(可降低功耗)将I/O口设置为漏开方式的做法为:PnMDOUT=0x00,Pn=0x11,这样设置I/O口为漏开。

如果学过三极管放大电路一定知道,前置单管放大器和功放末级放大电路的区别。

单片机内部的逻辑经过内部的逻辑运算后需要输出到外面,外面的器件可能需要较大的电流才能推动,因此在单片机的输出端口必须有一个驱动电路。

这种驱动电路有两种形式:其中的一种是采用一只N型三极管(npn或n沟道),以npn三极管为例,就是e接地,b接内部的逻辑运算,c引出,b受内部驱动可以控制三极管是否导通但如果三极管的c极一直悬空,尽管b极上发生高低变化,c极上也不会有高低变化,因此在这种条件下必须在外部提供一个电阻,电阻的一端接c(引出脚)另一端接电源,这样当三极管的b有高电压是三极管导通,c电压为低,当b 为低电压时三极管不通,c极在电阻的拉动下为高电压,这种驱动电路有个特点:低电压是三极管驱动的,高电压是电阻驱动的(上下不对称),三极管导通时的ec内阻很小,因此可以提供很大的电流,可以直接驱动led甚至继电器,但电阻的驱动是有限的,最大高电平输出电流=(vcc-Vh)/r;另一种是互补推挽输出,采用2只晶体管,一只在上一只在下,上面的一只是n型,下面为p型(以三极管为例),两只管子的连接为:npn(上)的c连vcc,pnp(下)的c接地,两只管子的ee,bb相连,其中ee作为输出(引出脚),bb接内部逻辑,这个电路通常用于功率放大点路的末级(音响),当bb接高电压时npn管导通输出高电压,由于三极管的ec电阻很小,因此输出的高电压有很强的驱动能力,当bb接低电压时npn截至,pnp导通,由于三极管的ec电阻很小因此输出的低电压有很强的驱动能力,简单的例子,9013导通时ec电阻不到10欧,以Vh=2.5v,vcc=5v计算,高电平输出电流最大=250MA,短路电流500ma,这个计算同时告诉我们采用推挽输出时一定要小心千万不要出现外部电路短路的可能,否则肯定烧毁芯片,特别是外部驱动三极管时别忘了在三极管的基极加限流电阻。

推挽输出电路的形式很多,有些单片机上下都采用n型管,但内部逻辑提供互补输出,以上的说明仅仅为了说明推挽的原理,为了更深的理解可以参考功率放大电路。

振荡器问:内部时钟振荡器是否稳定?是否可以用于产生波特率的时基?答:不同器件的内部时钟振荡器的精度是不同的(±20%)。

随电源电压变化,它也将发生变化(6.5%/V)。

但基本不随温度变化(<1%温度变化范围-40℃~+85℃)。

由于不同器件内部振荡器的离散性较大,所以不能用于产生波特率,应该外接标准晶体。

而有些器件,如C8051F3xx/f12x/f04x/f06x内部振荡器精度为±2%,可用于产生波特率。

问:片内/外振荡器如何配置?答:正确步骤:1、允许外部振荡器;2、等待1ms;3、查询XTLVLD '0'->'1'4、切换到外部振荡器。

注意:振荡器频率的选择,即OSCXCN寄存器的配置(外部振荡器频率控制位的设置)。

关于更多的信息以及源代码可以参看应用笔记AN002《配置内部和外部振荡器》。

应用笔记可以从我公司网站下载:问:C8051F MCU的指令执行速度为多少?答:C8051F MCU的CIP-51内核采用流水线结构,与标准的8051结构相比,指令执行速度有很大的提高。

标准的8051单片机执行一个单周期指令需要12个系统时钟周期,而C8051F MCU执行一个单周期指令只需要一个系统时钟周期。

如果系统时钟频率为25MHz,执行一个单周期指令所需时间为40ns。

问:切换外部晶振时应注意哪些问题?答:首先要允许外部振荡器,但此时的系统时钟源仍应是内部时钟,直到外部振荡器稳定后,才可将系统时钟源切换到外部振荡器上,否则会出现切换不过去,系统死机的情况。

问:使用外部晶振应注意哪些问题?答:1、所有的模拟和数字电源引脚都应接电源(2.7~3.6V);2、C8051F3xx系列器件的晶振引脚间应跨接一个10M电阻(在新华龙网站的“主页”—“原理图/PCB 库”中有C8051F系列单片机的典型接线图);3、晶振、电容等相关器件尽量靠近单片机的晶振引脚。

问:系统时钟切换到外部时钟后,内部的时钟是否应关闭?答:可以选择关闭或不关闭,但是从降低功耗的角度来说,应该关闭。