基于FPGA的音乐播放器

基于FPGA的音乐播放控制电路设计

音乐播放器控制电路课程设计报告班级:学号:姓名:指导老师:一、设计目的将《断桥残雪》简谱按照要求进行编码并将其写入只读存储器ROM之中,然后通过设计的电路读出ROM的内容,进行解码后驱动蜂鸣器播放。

二、开发环境采用Altera Quartus II 9.0软件设计环境。

它提供了全面的逻辑设计能力,包括电路图、文本和波形的设计输入以及编译、逻辑综合、仿真和定时分析以及器件编程等诸多功能。

特别是在原理图输入等方面,Altera Quartus II 9.0被公认为是最易使用、人机界面最友好开发软件。

并采用FPGALP-2900开发装置硬件实现,给人们带来极大的方便。

三、设计过程概述1、数字简谱简介数字简谱用不同的点和线段配合8个阿拉伯数字0~7构成音符,记录表示千变万化的音乐曲子及其基本音乐元素。

乐音是由三个要素决定的:频率决定了乐音的音高,频谱决定过了乐音的音色,音形标志着演奏方式。

乐曲的基本元素是:音的高低(音高)、音的长短(时值)、音的力度和音质(音色)。

音的高低和长短不同决定了乐曲的不同,因此构成了音乐的最重要的基础元素。

音乐用1、2、3、4、5、6、7分别表示同一调式7个不同的音高:多、来、米、法、索、拉、西。

这七个数字上、下标注的点表示音调升高8度音程或降低8度音程。

数字0为休止符,表示停止发音。

数字下或数字上的线段表示因的持续时间的长短。

没有线段的数字为4分音符,器时值为音长的基本度量单元,成为一拍。

数字下面标注的线段表示时间减短,没增加一条线段,表示时值减少一半,音符相应的成为8分音、16分音……数字后面的线段称为延长线,表示前一个音符的市场的增加,每条延长线的时值增量为1拍。

音长是一个相对的时间概念,一拍的时间长度没有限制,可以是1s,也可以是2s或是0.5s,。

若将4分音符的时长定为1s,其他音符的时值长度以其为基本参照度量,半拍为0.5s,2拍为2s,以此类推。

2、音高与频率关系20Hz至20KHz的音频脉冲信号控制蜂鸣器,可以使其根据控制信号的频率发出不同的音调。

基于FPGA的音乐播放器

基于FPGA的音乐播放器尝试利用FPGA开发板板载资源以及外搭的功率放大电路制作一台音乐播放器,能够播放通过计算机拷贝在SD卡(或MMC卡、TF卡)的根目录中的某一个WAV文件。

一、基本要求:制作音乐播放器(50分)(1)除了外置的音频功率放大器之外,本系统的主体部分(单片机)应基于STI51开发板,音乐来源于SD卡(或MMC卡、TF卡)(10分)(2)制作一个音频功率放大器,能够实现音频信号的功率放大功能,并能成驱动普通扬声器或耳机。

(10分)(3)能够播放单声道、8位,采样率为1.5K(或更高)的WAV文件。

实际播放时,歌声、伴奏声能依稀可辨。

(30分)二、提高要求:提高音乐播放器的音质(50分)(1)能够播放单声道、8位,采样率为2.5K或更高的WAV文件。

实际播放时,歌声、伴奏声清晰可辨。

(20分)(2)音频功率放大器从FPGA开发板取电,使用USB即可完成系统所有器件的供电。

(10分)(3)改造一切可以改造的部分以提高播放器的音质。

(20分)(提示:可以利用Adobe Audition软件编辑WAV文件并改变音频位数与采样率;可以利用Ultraedit软件以二进制方式查看WAV文件;WAV文件数据区的每一个字节顺次送入D/A中即可实现WAV文件的播放。

)起草人:刘文浩2010-11-25,04:43若具备一定的基础,以下内容可以忽略。

下面的内容是利用单片机制作音乐播放器的步骤。

题目分析1 系统开发步骤本题目对于刚学习完单片机尚未上手的同学来说可能难度较大,刚开始就着手制作一个以SD卡(或MMC卡、TF卡)为存储介质的音乐播放器并且要想尽办法提高播放音乐的音质具有较大难度,且容易让制作者失去继续制作下去的信心。

建议在制作过程中循序渐进,一步一步逐步深入逐渐实现以下功能:第一步:能够播放存储在单片机程序(ROM)中的音乐。

(参考时间:4天)第二步:通过串口调试助手向单片机发送WAV文件,使单片机能够播放计算机发出的WAV文件数据流。

基于FPGA的MP3音乐播放器设计

现了 以下几个方面 的功能 : ① 循环播放系统 内预存 曲 目; ②播 放

列表 : 可 以建 立 自 己 的播 放 列 表 , 建 立 后 MP 3将 会 循 环 播 放 选 中 的 几 首 歌 曲 。如 只 选 择 一 首 歌 曲 ,则 可 以 实 现 重 复 播 放 的 功 能; ③播放模式选择 : 系统内贮存有“ 普通” 、 “ 流行” 、 “ 古典 ” 、 “ 摇 滚” 等模 式 可 供 选 择 , 以数字编号代 替 , 选 择 后 相 应 数 字 显 示 在

K e y wo r d s : F P GA, MP 3 , t h e c o n t r o l l e r , t o n e f r e q u e n c y

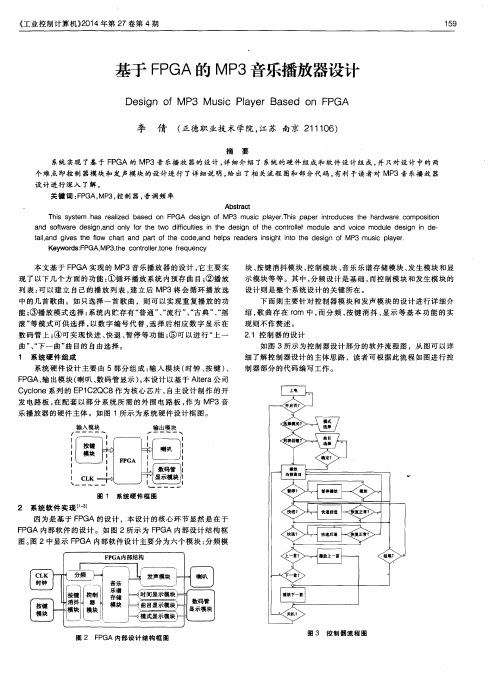

本文基于 F P G A 实 现 的 MP 3音 乐 播 放 器 的设 计 , 它 主 要 实

块、 按 键 消抖 模 块 、 控制模块 、 音乐乐谱存储模 块 、 发 生 模 块 和 显 示模块等等。其中 , 分频设计是基础 , 而 控 制 模 块 和 发 生 模 块 的

数码 管上 ; ④可 实现快进 、 快退 、 暂停等 功能 ; ⑤ 可 以进 行 “ 上一

曲” 、 “ 下一 曲” 曲 目的 自由 选 择 。

1 系统 硬 件 组成

系 统 硬 件 设 计 主 要 由 5部 分 组 成 : 输入模块 ( 时钟 、 按键 ) 、

F P G A、 输 出模 块 ( 喇叭 、 数码管显示 ) 。 本 设 计 以基 于 Al t e r a公 司 C y c l o n e系列 的 E P 1 C 2 QC 8作 为 核 心 芯 片 , 自主 设 计 制 作 的开 发 电路板 , 在 配 套 以 部 分 系 统 所 需 的外 围 电路 板 , 作 为 MP 3音 乐 播 放 器 的硬 件 主体 。 如 图 1所 示 为 系 统 硬 件 设 计 框 图 。

基于FPGA音乐播放器设计

参 考 文献 : 【 1 1 张庆 玲 , 杨 勇. F P G A 原 理 与 实践 [ M】 . 北京: 北 京航 空航 天 大 学 出版 社 . 2 0 0 6

[ 2 ] 刘睿 强. F P G A应 用技 术及 实践[ M ] . 北京: 北 京理 工大 学

出版 社 . 2 01 1

[ 3 】 袁 海林. 基于F P G A的具有存储功 能的 电子琴的设计 I J 1 .

中国科技信 g - 。 2 0 0 7 , ( 1 9 ) [ 4 ] 郑亚民. 可编程逻辑器件开发软件 Q u a a u s l I [ M] . 北京: 国

防 工 业 出版 社 . 2 0 0 6

机 械 与 自动 化

2 0 1 3 . N 0. 1 1 J o u r n a l o f He n a n S c i e n c e a n d ’ 。 。 。 。 。 T 。 。 。 e 。 ’ ’ c 。 。 。 h 。 。 。 。 ’ n ‘ 。 o 。 。 。 。 l 。 。 o 。 。 — g y —

计数 器是数字 系统 中应 用较 多的基本逻 辑器件 l 2 1 3 】 。 它的

综合分析 。其仿真结果如 图 2所示。

基本功能是实现计数操作 , 它也可用与分频 、 定 时、 产生节拍脉 冲和脉 冲序列等 。分频器是将不 同频段 的声音信号 区分开来 ,

分别给于放大 , 送到相应频段的扬声器 中再进行重放。

图 l 数控 果

作者简介 :

付莉 ( 1 9 8 5 年一 ) , 女, 汉族 , 毕业 于桂林 电子科技大学 , 助

教, 研究方向 : F P G A 及嵌 入 式 系统 设 计 。

基于-FPGA的音乐播放器的设计

摘要根据国家发改委与专业教学委员会对教育机构的要求,为培养适应我国21世纪国民经济发展的电子设计人才;同时基于国家教委面向21世纪电工电子课程体系改革和电工电子工科教学基地建设两项教学改革研究成果。

要求高等本科在校学生能够自己动手完成简单的数字器件设计。

本次设计在自己手动焊接简易的PFGA板子上实现,并且在QusrtusII 9.0上利用VHDL设计数控分频器电路,利用数控分频原理设计音乐硬件演奏电路,并制定LPM-ROM 存储音乐数据,以“梁祝”乐曲为例,将音乐数据存储到LPM-ROM,就达到了已纯硬件的手段来实现乐曲演奏的效果,只要修改LPM-ROM所存储的音乐数据,将其转换为其他的音乐数据,再重新制定LPM-ROM,在连接到程序中就可以实现其他与取得演奏。

本次设计采用的FPGA主芯片位ALTERA公司的FLEX系列的EPF10K10LC84-4。

由于板子是自己手动在万用板上焊接的所以只焊接了必要的外设如蜂鸣器和LED。

关键词FPGA;音乐播放器;QuartusII;VHDL;目录摘要 (I)第一章前言 (2)1.1关于EDA技术 (2)1.2 关于VHDL (2)1.3 关于EDA工具 (3)1.4 有关本次课程设计 (3)第二章设计实现 (4)2.1音乐演奏电路原理 (4)2.1.1音符频率的获得 (4)2.1.2乐曲节奏的控制 ............................................................... 错误!未定义书签。

2.1.3乐谱发生器 ....................................................................... 错误!未定义书签。

2.1.4乐曲演奏电路原理框图 ................................................... 错误!未定义书签。

基于FPGA的音乐播放器的设计-毕业设计论文

第三章

3.1

为了便于理解,首先介绍一下硬件电路的发声原理.我们知道,声音的频谱范围约在几十到几千赫兹,若能利用程序来控制 某个引脚输出一定频率的矩形波,接上扬声器就能发出相应频率的声音.而乐曲中的每一音符对应着一个确定的频率,因此,要想 发出不用音符的音调,实际上只要控制它输出相应音符的频率即可.乐曲都是由一连串的音符组成,因此按照乐曲的乐谱依次输出这些音符所对应的频率,就可以在扬声器上连续地发出各个音符的音调.而要准确地演奏出一首乐曲,仅仅让扬声器能够发声是不够的,还必须准确地控制乐曲的节奏,即每个音符的持续时间.由此可见,乐曲中每个音符的发音频率及其持续的时间是乐曲能够连续演奏的两个关键因素.

课程设计

课程名称:可编程数字片上系统实训

设计题目:基于FPGA的音乐播放器设计

院系:电气信息学院

指导教师:谷雷

专业:通信工程

学号:122700109

姓名:尚斌成

长春建筑学院

2015年12月31日

摘 要

在 开发环境下,采用 硬件描述语言设计了一个可以在 芯片上实现的音乐播放器.通过将音乐播放器电路设计进行模块化分解,层次化设计,分成几个单独的结构体,每个结构体实现部分功能,经顶层文件将各单独结构体进行综合,最后将设计代码结合 模块制作的 文件下载到 实验箱进行功能验证,实现乐曲播放.由于音乐播放器的通用性及 语言的可移植性, 因此本音乐播放器可直接应用于各种不同系列的 芯片的设计中.

而简易电子琴,工作原理与乐曲演奏一样,只是将固定预置乐曲变成了手动按键输入,节拍时间取决于按键的停留时间,如果合适,同样能播放出完整的歌曲来.

3.1.1

频率的高低决定了音调的高低.音乐的十二平均率规定:每两个八度音(如简谱中的中音1和高音1)之间的频率相差一倍.在两个八度音之间又分为十二个半音.另外,音名A(简谱中的低音6)的频率为440Hz,音名B到C之间、E到F之间为半音,其余为全音.由此可以计算出简谱中从低音1到高音1之间每个音名对应的频率,所有不同频率的信号都是从同一个基准频率分频得到的.由于音阶频率多为非整数,而分频系数又不能为小数,因此必须将计算得到的分频数四舍五入取整.若基准频率过低,则由于分频比太小,四舍五入取整后的误差较大,若基准频率过高,虽然误差较小,但分频数将变大.实际的设计应综合考虑这两方面的因素,在尽量减小频率误差的前提下取合适的基准频率.因此,要想 发出不同音符的音调,实际上只要控制它输出相应音符的频率即可.综合考虑各因素,本文中选取12MHZ作为CLK的分频计数器的输入分频信号.乐曲都是由一连串的音符组成,因此按照乐曲的乐谱依次输出这些音符所对应的频率,就可以在扬声器上连续地发出各个音符的音调.

基于FPGA的音乐播放器

基于FPGA的音乐播放器姓名:陆波学号:09090323指导老师:周爱军•音乐硬件演奏电路基本原理•硬件电路的发声原理,声音的频谱范围约在几十到几千赫兹,若能利用程序来控制FPGA芯片某个引脚输出一定频率的矩形波,接上扬声器就能发出相应频率的声音。

乐曲中的每一音符对应着一个确定的频率,要想FPGA发出不同音符的音调,实际上只要控制它输出相应音符的频率即可。

乐曲都是由一连串的音符组成,因此按照乐曲的乐谱依次输出这些音符所对应的频,就可以在扬声器上连续地发出各个音符的音调。

而要准确地演奏出一首乐曲,仅仅让扬声器能够发生是不够的,还必须准确地控制乐曲的节奏,即乐曲中每个音符的发生频率及其持续时间是乐曲能够连续演奏的两个关键因素。

•音调的控制:频率的高低决定了音调的高低。

通过查阅资料,得到下面的音符名与频率的关系表:音符名频率/hz音符名频率/hz音符名频率/hz 低音1262中音1523高音11046低音2294中音2587高音21175低音3330中音3659高音31318低音4349中音4698高音41397低音5392中音5784高音51568低音6440中音6880高音61760低音7494中音7988高音71976•分频比预置数的计算:•分频比就是从6Mhz基准频率通过二分频得到的3Mhz频率基础上计算得到的。

对于乐曲中的休止符,只需将其分频系数设为0,将分频预置数设为16383即可。

例如:低音3的频率为330hz,分频比为3M/330hz=3000000/330=9091,则其分频预置数为:16383-9091=7292。

其他的音符对应的分频比和分频比预置数均按此法计算可得到。

依次计算出低、中、高3X7=21个音的预置数。

•各音阶对应的预置数如右表:音符名预置数音符名预置数音符名预置数低音14933中音110647高音113515低音26179中音211272高音213830低音37292中音311831高音314107低音47787中音412085高音414236低音58730中音512556高音514470低音69565中音612974高音614678低音710310中音713347高音714858•音长的控制:•音符的持续时间必须根据乐曲的速度及每个音符的节拍数来确定。

基于FPGA的音乐播放器的设计

目录引言 (1)1 VHDL及QUARTUSII软件简介 (2)1.1EDA简介 (2)1.2硬件描述语言VHDL (2)1.3软件介绍 (3)2 简易音乐演奏器设计 (5)2.1硬件电路设计 (5)2.2软件代码设计 (6)2.2.1音符储存单元 (6)2.2.2选择播放模式及手动模块单元 (6)2.2.3分频模块单元 (8)2.2.4预置数模块单元 (9)2.2.5音频发声模块单元 (10)3引脚锁定及下载 (10)3.1引脚锁定 (10)3.2结果分析 (11)4设计总结 (11)参考文献 (116)附录 (16)引言VHDL语言是一种用于电路设计的高级语言。

它在80年代的后期出现。

最初是由美国国防部开发出来供美军用来提高设计的可靠性和缩减开发周期的一种使用范围较小的设计语言。

随着EDA技术的高速发展,电子系统的设计技术和工具发生了深刻的变化,大规模可编程逻辑器件CPLD/FPGA的出现,给设计人员带来了诸多方便。

利用它进行产品开发,不仅成本低、周期短、可靠性高,而且具有完全的知识产权。

突出了其作为硬件描述语言的良好的可读性、可移植性和易读性等优点。

本文基于FPGA开发系统,在QuartusII 7.2软件平台上,完成了简易乐曲演奏器设计和与仿真,并下载到试验箱进行硬件实现。

首先,本文介绍了QuartusII 7.2软件的基本使用方法和VHDL硬件描述语言的特点,采用VHDL 硬件描述语言描述简易信号发生器,完成对电路的功能仿真。

在设计过程中,重点探讨了简易乐曲演奏设计思路和功能模块划分。

然后,初步探讨了电路逻辑综合的原理,该软件对简易乐曲演奏器进行了逻辑综合。

最后,使用EDA实验开发系统进行电路的下载和验证。

验证结果表明设计的简易乐曲演奏器完成了预期的功能。

本设计是采用VHDL来实现的简易乐曲演奏器。

它能实现自动播放和手动播放。

1 VHDL及QuartusII软件简介1.1 EDA简介EDA是电子设计自动化(Electronic Design Automation)的缩写,在20世纪60年代中期从计算机辅助设计(CAD)、计算机辅助制造(CAM)、计算机辅助测试(CAT)和计算机辅助工程(CAE)的概念发展而来的。

基于FPGA的音乐播放控制电路设计

音乐播放器控制电路课程设计报告班级:学号:姓名:指导老师:一、设计目的将《断桥残雪》简谱按照要求进行编码并将其写入只读存储器ROM之中,然后通过设计的电路读出ROM的内容,进行解码后驱动蜂鸣器播放。

二、开发环境采用Altera Quartus II 9.0软件设计环境。

它提供了全面的逻辑设计能力,包括电路图、文本和波形的设计输入以及编译、逻辑综合、仿真和定时分析以及器件编程等诸多功能。

特别是在原理图输入等方面,Altera Quartus II 9.0被公认为是最易使用、人机界面最友好开发软件。

并采用FPGALP-2900开发装置硬件实现,给人们带来极大的方便。

三、设计过程概述1、数字简谱简介数字简谱用不同的点和线段配合8个阿拉伯数字0~7构成音符,记录表示千变万化的音乐曲子及其基本音乐元素。

乐音是由三个要素决定的:频率决定了乐音的音高,频谱决定过了乐音的音色,音形标志着演奏方式。

乐曲的基本元素是:音的高低(音高)、音的长短(时值)、音的力度和音质(音色)。

音的高低和长短不同决定了乐曲的不同,因此构成了音乐的最重要的基础元素。

音乐用1、2、3、4、5、6、7分别表示同一调式7个不同的音高:多、来、米、法、索、拉、西。

这七个数字上、下标注的点表示音调升高8度音程或降低8度音程。

数字0为休止符,表示停止发音。

数字下或数字上的线段表示因的持续时间的长短。

没有线段的数字为4分音符,器时值为音长的基本度量单元,成为一拍。

数字下面标注的线段表示时间减短,没增加一条线段,表示时值减少一半,音符相应的成为8分音、16分音……数字后面的线段称为延长线,表示前一个音符的市场的增加,每条延长线的时值增量为1拍。

音长是一个相对的时间概念,一拍的时间长度没有限制,可以是1s,也可以是2s或是0.5s,。

若将4分音符的时长定为1s,其他音符的时值长度以其为基本参照度量,半拍为0.5s,2拍为2s,以此类推。

2、音高与频率关系20Hz至20KHz的音频脉冲信号控制蜂鸣器,可以使其根据控制信号的频率发出不同的音调。

基于 FPGA 平台的乐曲播放技术

摘要一、设计的任务与要求 (2)1、任务与要求 (2)2、系统原理 (2)3、创新部分 (3)二、系统顶层原理图 (3)三、各功能模块叙述 (3)1、时钟生成模块 (3)2、时钟生成子模块 (4)3、时钟生成子模块各内部模块 (4)4、模式选择模块 (8)5、模式选择子模块 (9)6、模式选择子模块各内部模块 (9)7、显示模块 (15)8、显示子模块 (16)9、显示子模块各内部模块 (16)10、数据选择使能模块 (21)11、数据选择使能子模块 (22)12、数据选择使能子模块各内部模块 (22)13、数据选择模块 (26)14、音乐输出模块 (27)15、音乐输出子模块 (28)16、音乐输出模块子模块各内部模块 (28)四、硬件验证结果说明 (33)1、硬件资源使用情况 (33)2、引脚锁定 (33)3、基本功能验证 (34)五、心得体会 (36)六、参考文献 (36)摘要本文是以altera公司的FPGA芯片(EP2C5T144C8)为核心控制器,在QuartusII7.2软件平台上,完成了简易MP3的设计和与仿真,并下载到GW48-CK实验开发箱上进行了硬件验证。

通过定制LPM-ROM存储音乐数据,达到了以纯硬件的手段来实现乐曲的演奏效果。

只要修改LPM-ROM中所存储的音乐数据,就可以实现其它乐曲的演奏。

该音乐播放器设计具有电路简单、程序易改和调试方便等特点。

整个系统工作稳定,程序精简,界面友好。

关键词:altera、FPGA、EP2C5T144C8、音乐播放器一、设计的任务与要求:1、任务与要求:基于嵌入式技术利用VHDL硬件语言描述完成音乐播放器(1)基本要求:a、预存2首乐曲;b、用数码管显示当前播放乐曲的序列号;c、设置开始/暂停键,乐曲播放过程中按该键则暂停播放,再按则继续播放;(2)提高部分:a、播放模式选择(顺序播放和随机播放);b、用户可自行设置播放顺序;c、播放乐曲的时间显示;d、自拟其他功能。

基于FPGA的音乐播放器的设计

基于FPGA的音乐播放器的设计作者:陈嘉来源:《中国新通信》 2018年第19期【摘要】本文主要从FPGA 概述角度出发,阐述了基于FPGA 音乐播放器电路设计原理,论述了基于FPGA 音乐播放器算法模块设计,最后对音乐播放器系统实现进行叙述,并从不同角度进行详细分析,从而为基于FPGA 的音乐音乐播放器设计研究提供参考。

【关键词】电路原理电子产品系统设计引言随着科学技术不断创新与发展,电子产品生命周期逐渐被缩短,大部分电子产品在半年内便会被新产品所替代,因此要进一步对电子产品开发周期实施缩短,由此便应用到可编程逻辑器件,不仅能够有效缩短产品开发周期,同时随着集成电路制作技术水平不断提升,可编程逻辑器件整体设计技术水平得到有效提升,从而应用到各类电子产品开发当中。

一、FPGA 概述分析FPGA 主要指一种现场可编程门阵列,其主要以CPLD、GAL、PLA 等编程器为基础,通过不断发展和创新产生,属于半定制电路之一,属于专用集成电路领域中的一种,其优势在于填补定制电路存在的缺陷,并且可以解决可编程器件门电路数有限问题。

在实际应用过程中,其主要利用逻辑单元陈列,其中包括内部连线、输入输出模块以及可配置逻辑模块CLB,通过小型查找表来实施组合逻辑,每一个D 触发器输入端都连接着查找表,然后利用触发器来实现I/O 和逻辑电路驱动,同时利用向内部静态储存单元在实现编程数据加载,从而最终实现整个FPGA 功能。

二、基于FPGA 音乐播放器电路设计原理作为一种基本逻辑器件,计数器应用比较广泛,尤其是在数字系统当中应用比较频繁,其主要应用功能是通过计算操作来发挥自身效果,其在应用过程中可以和定时、分频产生脉冲序列和节拍脉冲,分频器能够将频段不同的声音信号进行划分,同时单独将不同声音信号方法,然后将其输送到一定频段扬声器当中,并通过重放方式来实现播放目的,由此可见,播放电路基本原理主要是将声音信号进行单独方法,并通过放大方式来达到一定播放效果。

基于FPGA的脉冲型音乐播放器的设计

基于FPGA/CPLD的脉冲信号型乐曲播放器的设计摘要用纯硬件来完成乐曲演奏电路的逻辑非常复杂,仅凭传统的数字逻辑技术,即使最简单的电路也难以实现。

但是借助于功能强大的EDA工具和硬件描述语言,就可以轻松的实现设计。

本设计利用可编程逻辑器件设计一个控制器让不同频率的脉冲信号有序的输出并驱动扬声器发声,最终完成一首乐曲的演奏。

设计以《世上只有妈妈好》为例,分析了硬件电路发声的基本原理,探讨了可以实现设计的方案,利用VHDL语言在QuartusⅡ上编程设计了节拍发生器、分频器、顺序控制、音高控制等模块的功能。

最后,运用原理图编辑器调出已经设计好的各个模块,根据设计的要求进行连线、加输入输出脚,得到了总体设计的仿真实体。

并对总体设计进行了功能仿真和下载。

本设计完成了乐曲《世上只有妈妈好》的32个音符64个节拍的播放,每个节拍0.5秒,整曲播放时长为32秒。

基于FPGA,利用Quartus Ⅱ和VHDL语言完成的脉冲型乐曲播放器,其特点是设计简单、灵活、设计周期短;缺陷是实现播放的乐曲种类单一,播放时间长度较短,若想要实现较长的乐曲播放,则需要很长的源程序。

关键词:FPGA,EDA,VHDL,QuartusⅡ,乐曲播放器The design of the pulse-type music player based on FPGA / CPLDAbstractIt is very complex to complete the music playing logic circuit using pure hardware. Only depend on the traditional digital logic technology, it is difficult to achieve even the simple circuit. However, it is very ease to achieve by using the EDA tools and hardware description language. The design finished a controller that output a series of orderly pulse signal with different frequencies and driven speaker with, by using the programmable logic device ,and finally complete the concert of a music.The music <shi shang zhi you ma ma hao> was used as an example. The basic principal of the hardware circuit sing was analyzed. How could achieve the player’s faction was also discussed. Following functional module was designed in Quartus II by using VHDL language: pulse generator, frequencies divider, sequence control, pitch control and so on. Finally, simulate entity was build in the Block Editor of the Quartus II , using all of the module which has been designed and according to the design’s requirements to connect, and plus input and output pin. Following these, the player’s entity was simulated and downloaded. The <shi shang zhi you ma ma hao>’s note 32 of the 64 players beat was completed in this design. One beat was sat as 0.5 seconds long, and the whole song was played within 32 seconds。

基于FPGA的音乐播放器设计报告

中国地质大学(武汉)基于FPGA的音乐播放器设计专业班级小组成员指导老师2015.06目录一、实现功能 (2)二、成员及任务分工 (2)三、详细设计及原理 (3)1.系统硬件结构设计 (3)2.程序流程 (4)四、具体实现 (5)1.SD卡文件系统的初始化 (5)2.按键选歌模式 (6)3.自动播放模式 (7)4.快进、快退、播放/暂停功能 (7)5.LCD显示歌曲名及歌词模块 (8)6.LED显示功能 (10)7.数码管显示当前曲目、总歌曲数和时间功能 (11)五、碰到的问题及解决过程 (12)1.问题一 (12)2.问题二 (12)3. 问题三 (13)4. 问题四 (13)六、运行效果 (13)七、设计小结 (19)一、实现功能1. 支持SD卡文件读取功能;2. 支持WAV格式音频功能;3. 支持歌词同步显示功能;3. 支持歌曲名称显示功能;4. 支持“播放/暂停”控制功能;5. 支持歌曲选择功能;6. 支持LED灯显示音量功能;7. 支持返回功能;8. 支持硬启动从ROM启动;9.支持数码管显示总歌曲数和第几首歌曲功能;10.支持数码管显示歌曲的播放进度功能;11. 支持LED灯指示拨码开关0~7状态功能;12. 支持前6首歌曲直接选择功能。

二、成员及任务分工三、详细设计及原理1.系统硬件结构设计本设计采用DE2 开发板,充分利用NiosII 软核的特性,结合自定义用户组件、自定义用户外设。

在FPGA 中使用软核处理器的优势在于灵活高效,硬核实现没有灵活性,通常无法使用最新的技术。

而应用Nios II 软核处理器,开发者能够完全定制CPU 和外设,获得恰好满足需求的处理器,充分利用了Nios II 处理器灵活和高效的特性。

通过DE2 开发板上的SD 卡插槽,读取SD 卡上的音频数据后,送到音频编/解码器,对音质进行相关处理后输出,进行音乐的播放. SD 卡音乐播放是由NiosII 处理器通过软件完成的。

基于FPGA的多媒体音乐播放器的设计

基于FPGA的多媒体音乐播放器的设计吴守霞【摘要】A multimedia music player was designed by using DE2 development board of Altera Corporation.The player took advantage of the rich resources of FPGA logic devices and the flexible design features of NiosII soft core's reconfigurability,combined with custom user commands,custom peripherals and software design architecture.SD card music playback function has been realized by using object-oriented software design and method.The system turns out to have high levels of integration and good stability.%设计了一款基于FPGA的多媒体音乐播放器.该播放器采用Altera公司的DE2开发板,充分利用FPGA丰富的逻辑器件资源和NiosⅡ软核灵活的可重构设计特性,结合自定义用户指令、自定义外设及软件设计架构,使用面向对象的设计思想和开发方法,实现了SD卡音乐播放功能,系统具有较高的集成度和良好的稳定性.【期刊名称】《兰州工业学院学报》【年(卷),期】2012(019)003【总页数】4页(P20-23)【关键词】多媒体音乐播放器;FPGA;NiosⅡ;SOPC;DE2【作者】吴守霞【作者单位】兰州工业高等专科学校电子信息工程系,甘肃兰州730050【正文语种】中文【中图分类】TN912.20 引言目前,电子产品的生命周期越来越短,许多消费类电子产品的生命周期只有一年左右,所以必须缩短产品的开发周期,而可编程逻辑器件与固定逻辑器件相比,可大大缩短开发周期.随着集成电路制造工艺的进步,可编程逻辑器件的设计水平不断提高,其成本已经降低到可以在消费类电子产品中大量使用的程度.从当前技术发展的趋势来看,可编程逻辑器件以其强大的优势将逐渐替代大部分的固定逻辑器件. 软核处理器的出现以及可编程逻辑器件片上存储容量的增大,使得可编程逻辑器件可以覆盖数字电子领域中的所有应用.Altera公司推出的片上可编程系统(System On a Programmable Chip,SOPC)以及Nois II软核处理器进一步证实了这一观点.目前Nios II处理器是使用最为广泛的软核处理器[1].DE2是Altera公司针对大学教学及研究机构推出的FPGA多媒体开发平台.DE2为用户提供了丰富的外设及多媒体特性,并具有灵活而可靠的外围接口设计,它能够帮助使用者迅速理解和掌握实时多媒体工业产品设计的技巧,并提供系统设计的验证,可靠性很高.消费电子是嵌入式系统重要的应用领域.随着电子信息技术的发展,人们生活质量不断提高,娱乐电子正逐渐走进百姓生活,电子娱乐产品的市场前景十分广阔.本设计就是基于SOPC技术设计的一款消费类电子产品——多媒体音乐播放器.整个系统采用FPGA可编程逻辑器件,利用先进的SOPC理念,在Altera公司提供的DE2开发板上实现了多媒体音乐播放器的功能.1 音乐播放器系统设计本设计采用DE2开发板,充分利用NiosII软核的特性,结合自定义用户组件、自定义用户外设.在FPGA中使用软核处理器的优势在于灵活高效,硬核实现没有灵活性,通常无法使用最新的技术.而应用Nios II软核处理器,开发者能够完全定制CPU和外设,获得恰好满足需求的处理器,充分利用了Nios II处理器灵活和高效的特性[2].设计充分利用了DE2开发板上的硬件资源,其中音频编/解码器(Audio CODEC)是系统的核心,它是由Wolfson公司的低功耗立体声24位音频编解码芯片WM8731来完成的[3]. WM8731包含了线路输入、麦克风输入及耳机(音响)输出.两路线路左、右声道能以1.5 dB的步距在+12~-34.5dB范围内进行对数音量调节,完成A/D转换后,还可以进行高通数字滤波,有效滤除输入信号中的直流成分.一路麦克风输入可以在-6~34 dB范围内进行音量调节.这三路输入都有单独的静音功能.D/A转换器输入、线路输入旁路及麦克风输入经过侧音电路后可相加作为输出以驱动耳机(RHPOUT和LHPOUT).DE2平台上的LINE OUT可以直接驱动耳机.LINE IN经过隔直电容输入,而MIC IN则直接输入.充分利用了24位立体声音频编/解码芯片WM8731高性能、低功耗的优点,可听到音质较好的音乐.利用这些硬件资源,设计实现了一个基于FPGA的多媒体音乐播放器.该音乐播放器主要分两种播放模式:一种是外接声源,如MP3等,通过音频输入(Line In)后,再经过音频编/解码器对音质进行相关处理后输出,进行音乐的播放.另一种是SD卡音乐播放器,即通过DE2开发板上的SD卡插槽,读取SD卡上的音频数据后,送到音频编/解码器,对音质进行相关处理后输出,进行音乐的播放.SD卡音乐播放是由NiosII处理器通过软件完成的.2 音乐播放器系统实现2.1 音乐播放器原理SD卡作为大容量的存储器,已经成为数码产品首选的存储设备,用于存储图像、音频等数据.本设计是将Wav格式的音乐保存在SD卡中,Nios II处理器从SD卡中读取音乐数据,并通过CD音质的音频编/解码器WM8731播放音乐[4].音频编/解码器被配置为从模式,需要外部电路为其提供A/D转换器(D/A转换器)串行时钟(BCK)及左/右通道时钟(LRCK),如图1所示.图中用一个音频DAC控制器产生时钟及数据控制信号,然后将该音频DAC控制器集成在Avalon总线上,Nois II处理器通过Avalon总线来控制音频DAC控制器[5].图1 SD卡音乐播放器原理框图2.2 系统硬件设计2.2.1 NIOS II处理器硬件框图根据多媒体音乐播放器系统对处理器、存储器和外设等的要求,构建的NiosII处理器结构框图如图2所示.在SOPC Builder工具中对NiosII软核进行的配置,配置的结果如图3所示.由于我们选择的FPGA是Cyclone II系列的EP2C35F672C6,所以在Target栏中的器件系列选择中选择Cyclone II[6].系统时钟选择外部的50 M晶振时钟.在NiosII 软核的选择时,由于考虑到FPGA丰富的逻辑资源,NiosII软核就选用了带有JTAG调试模块的NiosII/f(快速型),同其它两种核相比,快速型的性能最高,同时占用逻辑资源也是最多的[7].NiosII/f内核的主要特点有:指令和数据缓存分离、可访问高达2 GB的外部地址空间、可选的指令和数据紧耦合存储器、6级流水线操作、硬件乘除法和移位操作、256条定制指令等[8].其它配置的功能模块有LCD1602液晶控制器、2 K的片上ROM、512 K的外部SRAM控制器、EPCS控制器和一些输入输出通用PIO口.各模块配置完成后就可以对这些模块分配基地址和中断优先级.这些完成后,就可以生成配置好的NiosII系统(如图4所示).图2 NIOS II处理器的硬件框图图3 NiosII软核配置图2.2.2 音乐播放器软件设计总体软件设计即系统运行过程中的主逻辑,负责整个系统运行过程中各个状态之间的转换,程序流程图5所示,系统初始化完成以后,在音乐模式下,即可通过按键选择音乐目录中的音乐,解码WMA的音频文件,并播放.对SD卡的初始化后,才可以对SD卡进行读/写操作.在初始化完成后,通过设置数据长度,然后进行数据的读取,流程图如图6所示.3 结语本文给出了一种基于Nios II软核处理器的音乐播放系统.充分采用了软核处理器的开发思想以及Altera DE2开发平台,使系统具有开发周期短、易于维护、功能模块化等特点.本设计利用NiosII占用FPGA资源少和可裁剪性等特点,完全做到了系统体系的精简化和产品的低成本.使其在目前的多媒体娱乐市场上具有很高的竞争力,并且应用前景广泛.用基于FPGA的SOPC技术提高系统稳定性,使用NiosII提供的多种硬件加速方式,如自定义用户指令,自定义用户外设等大大提高运算速度,使算法和控制的实时性得到了有效的保证.图4 实现SD卡音乐播放的NiosII软核处理器参考文献:[1] 唐守龙,刘昊.浅谈Soc设计中的软硬件协同技术[J].电子器件,2002,25(2):5-6.[2] 赵川,徐涛,孙晓光.软硬件协同设计方法的研究[J].计算机工程与设计,2003,24(7):11-13.[3] 张志刚.FPGA与SOPC设计教程:DE2实践[M].西安:西安电子科技大学出版社,2007.[4] 吴喆庆.基于NiosⅡ系统的MP3播放器的设计[D].长春:吉林大学,2001.[5] 周立功.SOPC嵌入式系统基础课程[M].北京:北京航空航天大学出版社,2008:1-105.[6] FPGA/SOPC开发简明教程 V1.0[EB/OL].(2005-6-1)[2010-01-20]..[7] 陈麒.基于 NiosII处理器的SOPC设计[J].计算机与信息技术,2008,112(3):72-73.[8] 蔡伟纲.NIOS II软件架构解析[M].西安:西安电子科技大学出版社,2007.。

基于FPGA的音乐播放器课程设计

EDA是电子设计自动化(Electronic Design Automation)的缩写,在20世纪90年代初从计算机辅助设计(CAD)、计算机辅助制造(CAM)、计算机辅助测试(CAT)和计算机辅助工程(CAE)的概念发展而来。EDA技术是在电子CAD技术基础上发展起来的计算机软件系统,是指以计算机为工作平台,融合了应用电子技术、计算机技术、信息处理及智能化技术的最新成果,进行电子产品的自动设计。

(4)所有的制造厂商都提供了Verilog HDL的工艺库,用以支持仿真。

(5)Verilog HDL的程序语言接口拥有强大的功能,允许用户用C语言对内部

数据结构进行描述。

正是以上优点,使得Verilog HDL语言广泛流行。

下面是verilog的设计流程:

Verilog的设计流程图

2)了解怎样控制音调的高低变化和音长,从而完成乐曲的自动循环演奏。

3)培养自主学习、正确分析和解决问题的能力

1.2课程设计要求:

1)使用蜂鸣器播放音乐

2)三首音乐以上

3)数码管上显示当前播放的歌曲位置(第几首歌曲)

4)能够暂停和开始

5)能够选择上一首和下一首歌曲

2.应用工具介绍

作为当今最流行的计算机软件系统,EDA技术是以计算机为工作平台,融合了应用电子技术、计算机技术、信息处理及智能化技术的最新成果,进行电子产品的自动设计。EDA可提供文本输入以及图形编辑的方法将设计者的意图用程序或者图形方式表示出来,而我们经常见到的VHDL语言便是用于编写源程序所需的最常见的硬件描述语言(HDL)之一。

总成绩(100分)

提问

(答辩)

问题

情况

综

合

评

定

硬件课程设计-基于FPGA的MP3音乐播放器设计

基于FPGA的MP3音乐播放器设计——预置乐曲播放器设计摘要:本次课程设计的主题是‘基于FPGA的MP3播放器’,这是一个发展空间很大的课题,研究者可以根据自己的能力水平和兴趣爱好自由发展。

我们组实现的功能是‘预置乐曲的播放’。

本次设计是在BASYS2实验开发板上实现,使用xinlinx13.1软件,利用VHDL硬件描述言语设计数控分频器电路,利用数控分频原理设计音乐硬件播放数字电路,将音乐数据存放在程序中,利用时钟驱动音符输出,通过集成运放调节音量,达到了乐曲播放的效果。

程序中存放的音符数据易修改,只要修改程序中所放的的音符数据,将其转换为其他乐曲的音符数据,就可以实现不同乐曲的播放。

关键字:FPGA;xilinx;VHDL;预置音符;音乐播放目录摘要............................................................................................................................- 0 -一、绪论....................................................................................................................- 2 -1.1研究背景......................................................................................................- 2 -1.2基本技术简介..............................................................................................- 2 -1.2.1可编程逻辑器件FPGA .....................................................................- 2 -1.2.2硬件描述语言VHDL.........................................................................- 3 -1.2.3开发软件xilinx .................................................................................- 3 -二、需求分析和研究思路........................................................................................- 4 -2.1需求分析......................................................................................................- 4 -2.2研究思路......................................................................................................- 4 -三、系统设计............................................................................................................- 4 -3.1系统原理......................................................................................................- 4 -3.1.1音调控制...........................................................................................- 5 -3.1.2音长控制...........................................................................................- 6 -3.1.3乐谱发生器.....................................................................................- 6 -3.1.4音量控制...........................................................................................- 6 -3.2系统结构......................................................................................................- 7 -3.2.1各功能模块概述...............................................................................- 7 -3.2.2系统整体原理框图...........................................................................- 8 -四、详细的程序实现和仿真分析............................................................................- 8 -4.1时钟分频模块..............................................................................................- 8 -4.2乐谱码发生模块..........................................................................................- 9 -4.3乐谱码查表模块........................................................................................- 10 -4.4数控分频模块............................................................................................- 10 -4.5音量放大模块............................................................................................- 11 -4.6顶层模块....................................................................................................- 11 -五、结论..................................................................................................................- 11 -六、个人感想..........................................................................................................- 12 -一、绪论1.1研究背景在电子技术的飞速发展的今天,电子产品的种类越来越多,功能越来越强大,体积越来越小,功耗越来越低。

基于FPGA音乐播放器设计毕业设计

基于FPGA音乐播放器设计毕业设计简介本文档旨在介绍基于FPGA音乐播放器的毕业设计。

我们将使用FPGA技术设计一个音乐播放器,使其能够播放音乐文件,提供音频输出,并具备基本的控制功能。

设计目标1. 实现FPGA音乐播放器的硬件设计。

2. 支持音乐文件的播放和控制功能。

3. 实现音频输出功能。

4. 最大限度地减少功耗和硬件资源使用。

设计方案1. 硬件设计:使用FPGA芯片作为核心,构建音乐播放器的硬件电路。

考虑到资源使用的限制,采用简化的设计方案,保持硬件复杂度的最小化。

2. 控制功能:设计一个简单的用户界面,以便用户可以选择音乐文件并进行控制操作,如播放、暂停、停止等。

3. 音频输出:通过FPGA芯片的音频输出接口,将音乐信号转换为模拟音频信号,并通过扬声器或耳机进行播放。

4. 能耗优化:在设计中尽可能减少功耗,采用优化电路设计和功耗管理策略,以延长电池寿命或减少供电需求。

预期成果通过本毕业设计,预计可以实现一个基于FPGA的音乐播放器,具备基本的音乐播放和控制功能,并提供音频输出。

设计方案将遵循简化策略,以便在有限的资源和功耗约束下实现功能。

时间计划以下是预计的时间计划:- 第一周:调研相关的FPGA音乐播放器设计方案和技术。

- 第二周:设计FPGA音乐播放器的硬件电路。

- 第三周:实现音乐文件的播放和控制功能。

- 第四周:设计音频输出接口并测试音频输出功能。

- 第五周:优化设计,测试并调试整个系统。

- 第六周:完成毕业设计报告的撰写和总结。

参考文献1. 张三,李四。

FPGA音乐播放器设计方法。

《电子技术与软件应用》 2020年,第12期。

2. 王五,赵六。

FPGA音频输出接口设计技术研究。

《电子工程与设计》 2019年,第5期。

以上是基于FPGA音乐播放器设计的毕业设计文档。

请根据需要进行进一步的完善和修改。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于FPGA的音乐播放器

姓名:陆波

学号:09090323

指导老师:周爱军

•音乐硬件演奏电路基本原理

•硬件电路的发声原理,声音的频谱范围约在几十到几千赫兹,若能利用程序来控制FPGA芯片某个引脚输出一定频率的矩形波,接上扬声器就能发出相应频率的声音。

乐曲中的每一音符对应着一个确定的频率,要想FPGA发出不同音符的音调,实际上只要控制它输出相应音符的频率即可。

乐曲都是由一连串的音符组成,因此按照乐曲的乐谱依次输出这些音符所对应的频,就可以在扬声器上连续地发出各个音符的音调。

而要准确地演奏出一首乐曲,仅仅让扬声器能够发生是不够的,还必须准确地控制乐曲的节奏,即乐曲中每个音符的发生频率及其持续时间是乐曲能够连续演奏的两个关键因素。

•音调的控制:

频率的高低决定了音调的高低。

通过查阅资料,得到下面的音符名与频率的关系表:音符名频率

/hz

音符名频率

/hz

音符名频率

/hz 低音1262中音1523高音11046低音2294中音2587高音21175低音3330中音3659高音31318低音4349中音4698高音41397低音5392中音5784高音51568低音6440中音6880高音61760低音7494中音7988高音71976

•分频比预置数的计算:

•分频比就是从6Mhz基准频率通过二分频得到的3Mhz频率

基础上计算得到的。

对于乐曲

中的休止符,只需将其分频系

数设为0,将分频预置数设为

16383即可。

例如:低音3的频

率为330hz,分频比为

3M/330hz=3000000/330=9091,则其分频预置数为:16383-

9091=7292。

其他的音符对应

的分频比和分频比预置数均按

此法计算可得到。

依次计算出

低、中、高3X7=21个音的预置

数。

•各音阶对应的预置数如右表:音符名预置数音符名预置数音符名预置数低音14933中音110647高音113515低音26179中音211272高音213830低音37292中音311831高音314107低音47787中音412085高音414236低音58730中音512556高音514470低音69565中音612974高音614678低音710310中音713347高音714858

•音长的控制:

•音符的持续时间必须根据乐曲的速度及每个音符的节拍数来确定。

本

试验中,设定最短的音符为4分音符,若将全音符的持续时间设为1s的话,

则需要提供一个4Hz的时钟频率即可

产生4分音符的时间,每1/4个节拍的

时间为0.25s,一个完整的节拍为1s。

•右图即为音乐播放器的原理框图。

控制音调通过设置计数器的预置数来实

现,预置不同的数可以使计数器产生

不同频率的信号,从而产生不同的音

调。

控制音长则是通过控制计数器预

置数的停留时间来实现的,预置数停

留的时间越长,则该音符演奏的时间

越长。

每个音符的演奏时间都是0.25s 的整数倍,对于节拍较长的音符,例

如2分音符,占了2/4个节拍,在记谱

的时候将其连续记录2次即可。

•乐曲产生模块:

•核心模块就在这里,这里:(1)首先罗列了低、中、高21个音的分频比预置数(还有休止符的预置数16383),通过6Mhz的基准频率,在其上升沿的时候,计数器累加,当计满到16383之后就取反speaker(speaker<=~speaker非阻塞赋值),产生对应音符的频率,这里和单片机的定时计数器溢出中断差不多。

•产生了21个音调之后,我们要产生流畅的歌曲,还必须根据歌曲的谱子,调用相应音符并且根据节拍控制其持续的时间,例如:若一个音持续4个1/4节拍,则在clk_4hz的上升沿,连续调用4次它的音符就可以了。

用counter来计数,计满了(何时计满取决于歌曲长度)就将counter返回为0,这样就可以实现循环演奏了。

•分频产生4hz的节拍控制频率:

•module div_clk4hz(clk24m,clk4);

•input clk24m;

•output clk4;

•reg clk4;

•reg [21:0]cnt;

•always @(posedge clk24m)

•if(cnt<2999999)cnt=cnt+1;//(24m/4hz=60000 00,cnt<[6000000/2-1=2999999])

•else begin cnt=0;clk4=!clk4;end

•分频产生6Mz的基准频率:

•module div_clk6mhz(clk24m,clk6m);

•input clk24m;

•output clk6m;

•reg clk6m;

•reg cnt;

•always @(posedge clk24m)

•if(cnt<1)cnt=cnt+1; //(24m/6m=4分

频,cnt<[4/2-1=1]即可)•else begin cnt=0;clk6m=!clk6m;end •endmodule

•主程序大致:

•module song(clk_6mhz,clk_4hz,speaker);

•input clk_6mhz,clk_4hz;

•output speaker;

•reg [3:0]high,med,low;

•reg [13:0]divider,origin;

•reg [7:0]counter;

•reg speaker;

•wire carry;

•reg speaker;

•wire carry;

•assign carry=(divider==16383);

•always @(posedge clk_6mhz)

•begin if(carry)divider<=origin;

•else divider<=divider+1;

•end

•always @(posedge clk_4hz)

•begin

•if(counter==113)counter<=0;

•else counter=counter+1;

•case(counter)

•0: {high,med,low}<='b000000000101;•1: {high,med,low}<='b000000000101;//•2: {high,med,low}<='b000000000110;•3: {high,med,low}<='b000000000110;//•4: {high,med,low}<='b000000000101;•5: {high,med,low}<='b000000000101;//•6: {high,med,low}<='b000100000000;•7: {high,med,low}<='b000100000000;//•8: {high,med,low}<='b000001110000;

endcase

•三个模块都完成之后,生成相应的电路原理图,并连接起来,组成一个完整的音乐播放器电路,如下:

•完成以上步骤之后,分配引脚到试验箱上的芯片,连接好引脚到扬声器等,并且接好相应的短路帽。

然后烧写程序到芯片中去,测试音乐播放器是否可以产生预期已经谱好了曲子的歌曲。

经过硬件测试,能够产生《梁祝》,《两只老虎》,《生日歌》,《月亮之上》。

•实验总结;

•其实,音乐播放器用FPGA来实现是很简单的。

核心部分就是抓住了乐曲的两个要点:音调的控制和音长的控制。

因此,涉及到两个频率,一个用来控制产生相应的音调,一个是用来控制该音调持续的时间(即节拍)。

不过因为看不太懂乐谱,所以做得不是太好。

其实,可以做的完善和人性化一点,因为声音不只21个音,还有升半调#和降调b,可以加些按键控制,选中某一首歌曲播放。

或者还可以通过按键调整模式,可以有自己弹奏乐曲的模式,和音乐自动播放模式,两种模式进行切换。