数字时钟c语言代码

制作一个电子时钟C语言版

制作一个电子时钟C语言版平常我们常见的电子时钟,能够显示当下的时分秒信息,并且能够随时变化递增,记录着时间的流逝。

今天,我要用c语言来制作这样一款电子时钟,看时间这把杀猪刀如何“一刀一刀”溜掉。

我会一步一步引导大家了解制作过程。

首先,我们可以想到,需要获取系统的时间函数,并且显示在cmd控制台中。

time.h是c/c++日期和时间头文件,用于获取系统日期和时间等要求。

首先给出提取显示当前时间的1.0版本电子时钟。

#include<stdio.h>#include<time.h>#include<string.h>int main(){char str[50];//定义字符串用于存储时间time_t t;struct tm *nt;//tm是time.h中定义的一个结构体t=time(NULL);nt=localtime(&t);//获取当前时间strftime(str,50,"%Y-% m-%d %H:%M:%S ",nt);//strftime是根据当前计算机区域设置格式化本地时间日期printf("现在时刻:%s\n",str);//打印现在时刻getch();return 0;}运行的结果如下:可以看出,的确做到了显示当前时间,但是很明显这不是电子时钟,电子时钟要不断运行变换时间,而不是让时间凝滞。

那么,我们怎么实现真正的电子时钟呢?我们一起思考:如果要实现时间变化,需要不断重新获取当前时间,并且将之前的显示清除掉,然后再打印显示当前时间,这样循环往复。

所以,需要增加一个while(1)死循环,同时要增加一个清屏函数,清除原来的显示。

清屏函数常用的就是system("cls")。

下面是改进后的2.0版代码。

#include<stdio.h>#include<time.h>#include<string.h>int main(){char str[50];time_t t;struct tm *nt;while(1){system("cls");//清屏函数t=time(NULL);nt=localtime(&t);strftime(str,50,"%Y-%m-%d %H:%M:%S “,nt);printf("现在时刻:%s\n",str);}getch();return 0;}然后运行程序,就可以实现电子时钟了,时间不断刷新,秒数递增,时间随之递增。

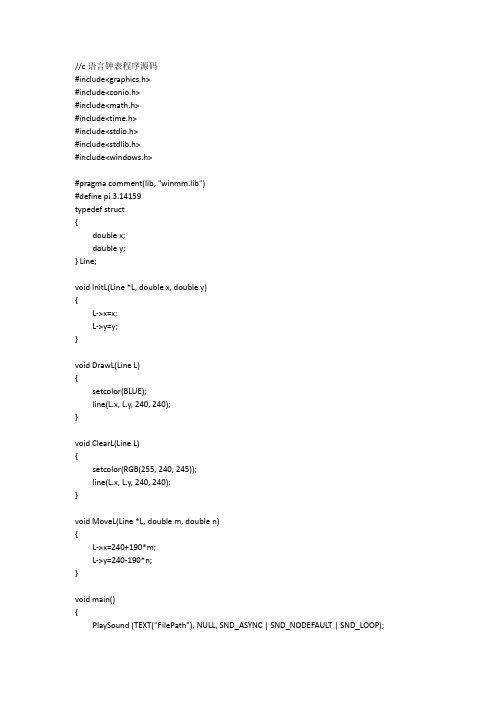

C语言钟表程序源码

//c语言钟表程序源码#include<graphics.h>#include<conio.h>#include<math.h>#include<time.h>#include<stdio.h>#include<stdlib.h>#include<windows.h>#pragma comment(lib, "winmm.lib")#define pi 3.14159typedef struct{double x;double y;} Line;void InitL(Line *L, double x, double y){L->x=x;L->y=y;}void DrawL(Line L){setcolor(BLUE);line(L.x, L.y, 240, 240);}void ClearL(Line L){setcolor(RGB(255, 240, 245));line(L.x, L.y, 240, 240);}void MoveL(Line *L, double m, double n){L->x=240+190*m;L->y=240-190*n;}void main(){PlaySound (TEXT("FilePath"), NULL, SND_ASYNC | SND_NODEFAULT | SND_LOOP);system("mode con cols=45 lines=15");system("color 79");initgraph(480, 480);loadimage(NULL, _T("IMAGE"), _T("BackGroud"));fillcircle(240,240,240);//画表盘setfillcolor(BLACK);fillrectangle(232, 35, 235, 84);fillrectangle(243, 35, 258, 38);fillrectangle(255, 39, 258, 57);fillrectangle(243, 58, 258, 61);fillrectangle(243, 62, 246, 80);fillrectangle(243, 81, 258, 84);//画12fillrectangle(40, 215, 60, 218);fillrectangle(40, 219, 43, 237);fillrectangle(57, 219, 60, 237);fillrectangle(40, 238, 60, 241);fillrectangle(57, 242, 60, 260);fillrectangle(40, 261, 60, 264);//画9fillrectangle(420, 215, 440, 218);fillrectangle(438, 219, 441, 237);fillrectangle(420, 238, 440, 241);fillrectangle(438, 242, 441, 260);fillrectangle(420, 261, 440, 264);//画3fillrectangle(230, 390, 250, 393);fillrectangle(230, 394, 233, 412);fillrectangle(230, 413, 250, 416);fillrectangle(230, 417, 233, 435);fillrectangle(247, 417, 250, 435);fillrectangle(230, 436, 250, 439);//画6int i;for(i=5; i<=60; i+=5){setcolor(RED);line(240+240*sin(pi/30*i), 240-240*cos(pi/30*i), 240+210*sin(pi/30*i),240-210*cos(pi/30*i));} //画出四个长的时刻针for(i=1; i<=60; i++){if(i%5==0) continue;setcolor(RED);line(240+240*sin(pi/30*i), 240-240*cos(pi/30*i), 240+225*sin(pi/30*i), 240-225*cos(pi/30*i));}Line L, M;time_t t=time(0);int h, m, s, a;char hour[3], min[3], sec[3];strftime( hour, sizeof(hour), "%I",localtime(&t));strftime( min, sizeof(min), "%M",localtime(&t));strftime( sec, sizeof(sec), "%S",localtime(&t));h=atoi(hour);m=atoi(min);s=atoi(sec);//画出其他时刻针InitL(&L, 240+190*sin(pi/30*(s+1)), 240-190*cos(pi/30*(s+1)));for(a=1; a; a++){DrawL(L);setcolor(GREEN);line(240, 240, 240+150*sin((pi/1800*(a+s))+(pi/30*m)), 240-150*cos(pi/1800*(a+s)+(pi/30*m)));setcolor(BLACK);line(240, 240, 240+130*sin(pi/108000*a+(pi/6*h)+(pi/360*m)), 240-130*cos(pi/108000*a+(pi/6*h)+(pi/360*m)));Sleep(1000);ClearL(L);MoveL(&L, sin(pi/30*a+(pi/30*s)), cos(pi/30*a+(pi/30*s))); //秒针的移动setcolor(RGB(255, 240, 245));line(240, 240, 240+150*sin(pi/1800*(a+s)+(pi/30*m)), 240-150*cos(pi/1800*(a+s)+(pi/30*m)));setcolor(RGB(255, 240, 245));line(240, 240, 240+130*sin(pi/108000*a+(pi/6*h)+(pi/360*m)), 240-130*cos(pi/108000*a+(pi/6*h)+(pi/360*m)));} //表针的移动getch();closegraph(); }。

数字时钟C语言源程序

#define uchar unsigned char

#define uint unsigned int //宏定义

uchar count;

uint hour,minute,second;

uint hour1=0,minute1=0;

sbit dula=P2^6;

{

count=0;

second++;

if(second==60)

{

second=0;

minute++;

}

if(minute==60)

{

minute=0;

hour++;

}

if(hour==24)

hour=0;

}

}

second=0;

while(!key5);

}

if(key2==0)

{

delay(10);

if(key2==0)

if(hour>0)

hour--;

else

hour=23;

while(!key2);

}

if(key4==0)

{

delay(10);

while(!key6);

}

if(key7==0)//复位功能

{

delay(10);

if(key7==0)

{

hour=0;

minute=0;

second=0;

}

while(!key7);

}

}

void zhengdianbaoshi()//整点报时(从50秒开始)

数字时钟_89C52_单片机C语言程序

uchar MON[]={0,31,28,31,30,31,30,31,31,30,31,30,31};

uchar A;

uchar BIN=0; /* 【BIN】作为倒计时开始的标志 */

TH0 = (65536 - 10000) / 256; /*给定计时器高位赋予 初值=15536/256*/

TL0 = (65536 - 10000) % 256; /*给定计时器低位赋予 初值=15536%256 */

ET0 = 1; /*打开定时器外部终断0允许 ET1是中断器1的开关*/

P2 = C[4];

Delay(1);

P0 = Code[Msec%10]; /*第五位的数字显示【分】的【个】位 */

P2 = C[5];

Delay(1);

Delay(1);

P0 = 0x40; /*第六位符号【-】的显示 */

P2 = C[6];

Delay(1);

P2 = C[2];

Delay(1);

if(x/50==0)

P0 = 0x40; /*第三位符号【-】的显示 */

else

P0 = 0x00;

P2 = C[3];

Delay(1);

P0 = Code[min/10]; /*第四位的数字的显示【分】的【十】位 */

uchar month=7;

uchar month2;

uchar day=19;

uchar set1 = 1; /* set1=1 是调节 时分秒 set1=2时时调节 年月日 set=3时事调节闹钟 */

AT8951单片机带闹钟数字时钟 C语言编程

{

delay(10);

//延时去抖

if(K2==0)

//加键按下

{

if(hour<23) hour++;

else hour=0;

}

while(!K2);

//等待按键释放

}

if(K3==0) {

delay(10); if(K3==0) {

if(hour> 0) hour--; else hour=23; } while(!K3); } } break;

}break; case 1:

{ if(S_flag==1) { a[0]=led[hour/10]; a[1]=led[hour%10]; } else {

a[0]=led[11]; a[1]=led[11]; } a[2]=led[10]; a[3]=led[minute/10]; a[4]=led[minute%10]; a[5]=led[10]; a[6]=led[second/10]; a[7]=led[second%10]; }break; case 2: { a[0]=led[hour/10]; a[1]=led[hour%10]; a[2]=led[10]; if(S_flag==1) { a[3]=led[minute/10]; a[4]=led[minute%10]; } else { a[3]=led[11]; a[4]=led[11]; } a[5]=led[10]; a[6]=led[second/10]; a[7]=led[second%10]; }break; case 3: { if(S_flag==1) { a[0]=led[hour1/10]; a[1]=led[hour1%10]; } else { a[0]=led[11]; a[1]=led[11]; } a[2]=led[10]; a[3]=led[minute1/10]; a[4]=led[minute1%10];

C语言课程设计 时钟代码

/*电子时钟源代码*/#include<graphics.h>#include<stdio.h>#include<math.h>#include<dos.h>#define PI 3.1415926 /*定义常量*/#define UP 0x4800 /*上移↑键:修改时间*/#define DOWN 0x5000 /*下移↓键:修改时间*/#define ESC 0x11b /*ESC键:退出系统*/#define TAB 0xf09 /*TAB键:移动光标*//*函数声明*/int keyhandle(int,int); /*键盘按键判断,并调用相关函数处理*/int timeupchange(int); /*处理上移按键*/int timedownchange(int); /*处理下移按键*/int digithour(double); /*将double型的小时数转换成int型*/int digitmin(double); /*将double型的分钟数转换成int型*/int digitsec(double); /*将double型的秒钟数转换成int型*/void digitclock(int,int,int ); /*在指定位置显示时钟或分钟或秒钟数*/void drawcursor(int); /*绘制一个光标*/ void clearcursor(int);/*消除前一个光标*/void clockhandle(); /*时钟处理*/ double h,m,s; /*全局变量:小时,分,秒*/double x,x1,x2,y,y1,y2; /*全局变量:坐标值*/struct time t[1];/*定义一个time结构类型的数组*/main(){int driver, mode=0,i,j;driver=DETECT; /*自动检测显示设备*/initgraph(&driver, &mode, "");/*初始化图形系统*/setlinestyle(0,0,3); /*设置当前画线宽度和类型:设置三点宽实线*/ setbkcolor(0);/*用调色板设置当前背景颜色*/setcolor(9); /*设置当前画线颜色*/ line(82,430,558,430);line(70,62,70,418);line(82,50,558,50);line(570,62,570,418);line(70,62,570,62);line(76,56,297,56);line(340,56,564,56); /*画主体框架的边直线*//*arc(int x, int y, int stangle, int endangle, int radius)*/arc(82,62,90,180,12);arc(558,62,0,90,12);setlinestyle(0,0,3);arc(82,418,180,279,12);setlinestyle(0,0,3);arc(558,418,270,360,12); /*画主体框架的边角弧线*/setcolor(15);outtextxy(300,53,"CLOCK"); /*显示标题*/setcolor(7);rectangle(342,72,560,360); /*画一个矩形,作为时钟的框架*/setwritemode(0); /*规定画线的方式。

C语言编写高精度 电子时钟

#include<reg51.h>#include "public.h"#define uchar unsigned char#define uint unsigned int#define write_addr 0xa0#define read_addr 0xa1extern number_list[10]={0xed,0x28,0xb5,0xb9,0x78,0xd9,0xdd,0xa8,0xfd,0xf9}; extern number_list1[10]={0xef,0x2A,0xb7,0xbB,0x7A,0xdB,0xdF,0xaA,0xfF,0xfB}; extern x_list[12]={0x10,0x11,0x12,0x13,0x14,0x15,0x16,0x17,0x18,0x19,0x1a,0x1b}; void int_clock(void);void delay(ms);void ds_time();void ds_day();void set_time();uchar Sec;uchar Min;uchar Hour;uchar Week;uchar day;uchar month;uchar year;uchar Sec_H;uchar Sec_L;uchar Min_H;uchar Min_L;uchar Hour_H;uchar Hour_L;uchar timer_count;uchar dsplay_count;uchar key_week;uchar key_h;uchar key_m;uchar key_s;uchar set_flag;uchar ds_flag;void main (){uchar i,day_sum;timer_count=0;dsplay_count=0xAA;key_h=0;key_m=0;key_s=0;key_week=0;set_flag=0;ds_flag=0xBB;LCD_EN=1;TMOD=0X01;TCON=0x10;TH0=0X63;TL0=0XC0;EA=1;ET0=1;int_clock();while(1){ WDT_RST=0xA1;//时钟计算、进位if((month==1)||(month==3)||(month==5)||(month==7)||(month==8)||(month==10)||(month==12)) {day_sum=31;}if(month==2) //暂不区分闰年{day_sum=28;}if((month==4)||(month==6)||(month==9)||(month==11)){day_sum=30;}if((timer_count==10)&&(set_flag==0)){timer_count=0;Sec++;if(Sec==60){Sec=0;Min++;if(Min==60){Min=0;Hour++;if(Hour==24){Hour=0;Week++;day++;if(Week==8){Week=1;}if(day==day_sum){day=1;month++;if(month==13){month=1;year++;}}}}}}if(ds_flag==0xbb){ds_time();}if(ds_flag==0xaa){ds_day();}if (ds_flag==0xcc){for(i=0;i<=12;i++){EXT_ADR=x_list[i];EXT_DAT=0x00;}}set_time();}}void ds_time(void){EXT_ADR=0x1b; // 显示时间EXT_DAT=0x10;//时钟显示Sec_H=Sec/10;Sec_L=Sec%10;EXT_ADR=0x17;EXT_DAT=number_list[Sec_H];EXT_ADR=0x18;if(Sec_L%2==0){EXT_DAT=number_list1[Sec_L];}else{EXT_DAT=number_list[Sec_L];}Min_H=Min/10;Min_L=Min%10;EXT_ADR=0x15;EXT_DAT=number_list[Min_H];EXT_ADR=0x16;EXT_DAT=number_list[Min_L];Hour_H=Hour/10;Hour_L=Hour%10;EXT_ADR=0x13;EXT_DAT=number_list1[Hour_H];EXT_ADR=0x14;EXT_DAT=number_list1[Hour_L];EXT_ADR=0x11;EXT_DAT=number_list[Week];}void ds_day (void){EXT_ADR=0x1b; // 显示日期EXT_DAT=0x40;// 日期显示EXT_ADR=0x17;EXT_DAT=number_list[day/10];EXT_ADR=0x18;EXT_DAT=number_list1[day%10];//monthEXT_ADR=0x15;EXT_DAT=number_list[month/10];EXT_ADR=0x16;EXT_DAT=number_list[month%10];//yearEXT_ADR=0x11;EXT_DAT=number_list[2];EXT_ADR=0x12;EXT_DAT=number_list[0];EXT_ADR=0x13;EXT_DAT=number_list1[1];EXT_ADR=0x14;EXT_DAT=number_list1[1];}void set_time(){//set_sif(key_s==1){if(set_s==0)key_s=0;}else{ if(set_s==1){delay(20000);if(set_s==1){set_flag=1;key_s=1;Sec++;if(Sec==60){Sec=0;}}}}set_flag=0;//set_hif(key_h==1){if(set_h==0)key_h=0;}else{ if(set_h==1){delay(20000);if(set_h==1){set_flag=1;key_h=1;Hour++;if(Hour==24){Hour=0;}}}}set_flag=0;//set_mif(key_m==1){if(set_m==0)key_m=0;}else{ if(set_m==1){delay(20000);if(set_m==1){set_flag=1;key_m=1;Min++;if(Min==60){Min=0;}}}}set_flag=0;//set_weekif(key_week==1){if(set_week==0)key_week=0;}else{if (set_week==1){delay(20000);if(set_week==1){key_week=1;Week++;if(Week==8){Week=1;}}}}}void timer0_int(void) interrupt 1 //定时100ms {TMOD=0X01;TCON=0x10;TH0=0X63;TL0=0XC0;WDT_RST=0xA1;timer_count++;dsplay_count++;if(dsplay_count<30){ds_flag=0xaa;}if(((dsplay_count)>30)&&((dsplay_count)<32)) {ds_flag=0xcc;}if(((dsplay_count)>32)&&((dsplay_count)<60)){ds_flag=0xbb;}if(dsplay_count>60){dsplay_count=0;}}/*void I2C_sart(){SDA=1;SCL=1;delay();//延时4毫秒SDA=0;SCL=0;}void I2C_stop(){SDA=0;SCL=1;delay();//延时4毫秒SDA=1;SCL=0;}*/void int_clock(void){uchar i;Sec=0;Min=41;Hour=7;Week=2;day=23;month=3;for(i=0;i<4;i++){EXT_ADR=x_list[i+5];EXT_DAT=number_list[0];}EXT_ADR=x_list[3];EXT_DAT=number_list[1];EXT_ADR=0X14;EXT_DAT=0Xb7;EXT_ADR=0X18;EXT_DAT=0XEF;}void delay (ms){uint i;for(i=0;i<ms;i++){;;;;;;}}。

数字时钟程序(完整版)

数字时钟程序/**************************************************程序名称:数字时钟程序全局变量:tt,shi,fen,miao等参数说明:无返回说明:无版本:1.0功能说明:通过数码实现时钟的显示,通过键盘实现时间的调整其中k1是开始调整,k2是增加,k3是减小,k5是实现定时屏幕的切换,k4是定时设置的开始。

带闹铃功能。

作者邮箱:****************(欢迎交流)**************************************************/#include<reg52.h>#define uint unsigned int#define uchar unsigned charsbit beep=P2^3;sbit dula=P2^6;sbit wela=P2^7;sbit k1=P3^0;sbit k2=P3^1;sbit k3=P3^2;sbit k4=P3^3;sbit k5=P3^4;sbit rd=P3^7;uchartt,shi_s,shi_g,shi1_s,shi1_g,fen1_s,fen1_g,miao1_s,miao1_g,fen_s,fen_g,miao_s,miao_g,k1num,k 4num,flag;char shi,fen,miao=20,shi1,fen1,miao1;/*********************************函数名称:延时程序设计全局变量:无参数说明:z传递给内部,是实现75*z条空指令延迟返回说明:无版本:1.0功能说明:约Z*75us延时程序设计作者邮箱:****************(欢迎交流)*********************************/void delay(uint z){uchar x;uint y;for(x=z;x>0;x--)for(y=75;y>0;y--);}/********八段数码管编码**********/uchar code table[]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,0x7f,0x6f,0x77,0x7c,0x39,0x5e,0x79,0x71};/*********************************函数名称:初始化函数全局变量:无参数说明:无返回说明:无版本:1.0功能说明:定时器装初值,开总中断,定时中断,并写定时中断函数作者邮箱:****************(欢迎交流)*********************************/void init(){TMOD=0x01;TH0=(65536-50000)/256;TL0=(65536-50000)%256;EA=1;ET0=1;TR0=1;}void timer0() interrupt 1{TH0=(65536-50000)/256;TL0=(65536-50000)%256;tt++;if(tt==20){tt=0;miao++;if(miao==60){miao=0;fen++;if(fen==60){fen=0;shi++;if(shi==24){shi=0;}}}}}/*********************************函数名称:6个数码管显示函数全局变量:shi fen miao 的个十位分离参数说明:将个十位的分离分别传递到各个数码管中并显示返回说明:无版本:1.0功能说明:实现时钟的数码管显示,动态扫描。

数字钟51单片机程序c语言

goto F0; //*按键未释放,在此等候*//

}

//*延时子函数*/

unsigned char i,j;

for(i=5;i>0;i--)

for(j=248;j>0;j--);

}

//*5mS定时中断服务 子函数*//

void zd(void) interrupt 1

{

TH0=-(4800//256);

TL0=-(4800%256);

deda++;

}

//*调整走时时间*//

{

t_dirve();

}

if(P3_7==0)

delay(1);

if(P3_7==0)

t_min++;

if(t_min==60)

{

if(deda<=100)

d_05s=0;

else d_05s=1;

if(deda>=200)

{sec++;deda=0;}

if(sec==60)

{min++;sec=0;}

if(min==60)

{hour++;min=0;}

if(hour==24)

{hour=0;}

p_out(); //*判别闹时到 子函数*// 否

}

//*定时器 T0 5mS初始化*//

void init_timer()

{

TMOD=0x01;

TH0=-(4800//256);

TL0=-(4800%256);

IE=0x82;

单片机数字钟万年历(c语言)

#include <REGX51.H>#include <ABSACC.h>#define Font_code XBYTE[0xefff] //字符码写地址#define reg_code XBYTE[0xdfff] //字位码写地址#define s_1_con_key P3_2#define m_1_con_key P3_3#define h_1_con_key P3_4#define w_1_con_key P3_5#define p1 P1sbit BELL=P1^0;//sbit p10=P1^0;//sbit p20=P1^1;//sbit p30=P1^2;//sbit p40=P1^3;//sbit p50=P1^4;//sbit p60=P1^5;//sbit p70=P1^6;//sbit p80=P1^7;//字型码const unsigned char seg_design[11]={0x3F,/*0*/0x06,/*1*/0x5B,/*2*/0x4F,/*3*/0x66,/*4*/0x6D,/*5*/0x7D,/*6*/0x07,/*7*/0x7F,/*8*/0x6F,/*9*/0x40,/*-*/};//字位码const unsigned char bit_design[8]={0x01,0x02,0x04,0x08,0x10,0x20,0x40,0x80};code unsigned char sszymmh[]={ 6,2,3, 5,2,1, 3,2,2, 5,2,2, 1,3,2, 6,2,1, 5,2,1,6,2,4, 3,2,2, 5,2,1, 6,2,1, 5,2,2, 3,2,2, 1,2,1,6,1,1, 5,2,1, 3,2,1, 2,2,4, 2,2,3, 3,2,1, 5,2,2,5,2,1, 6,2,1, 3,2,2, 2,2,2, 1,2,4, 5,2,3,3,2,1,2,2,1, 1,2,1, 6,1,1, 1,2,1, 5,1,6, 0,0,0} ;// 音阶频率表高八位code unsigned char FREQH[]={0xF2,0xF3,0xF5,0xF5,0xF6,0xF7,0xF8,0xF9,0xF9,0xFA,0xFA,0xFB,0xFB,0xFC,0xFC,//1,2,3,4,5,6,7,8,i0xFC,0xFD,0xFD,0xFD,0xFD,0xFE,0xFE,0xFE,0xFE,0xFE,0xFE,0xFE,0xFF,} ;// 音阶频率表低八位code unsigned char FREQL[]={0x42,0xC1,0x17,0xB6,0xD0,0xD1,0xB6,0x21,0xE1,0x8C,0xD8,0x68,0xE9,0x5B,0x8F,//1,2,3,4,5,6,7,8,i0xEE,0x44, 0x6B,0xB4,0xF4,0x2D,0x47,0x77,0xA2,0xB6,0xDA,0xFA,0x16,};unsigned char bit_con;unsigned int ms_1_con; //毫秒计数器unsigned char s_1_con; //秒计数器unsigned char m_1_con; //分计数器unsigned char h_1_con=12;//时计数器unsigned char w_1_con=6; //周计时器unsigned char d_1_con=1;unsigned char mon_1_con=1;unsigned int y_1_con=2011;unsigned char s1; //秒计数器unsigned char m1; //分计数器unsigned char h1; //时计数器unsigned char Display_Buffer[8]; //显示缓冲区unsigned int k1=0;unsigned int k2=0;unsigned char timer0h,timer0l,time,led=1,j=0;unsigned char flagd=0;void delay_nms(unsigned int n);void Calculation_display(void);void time_set(void);void time_set1(void);void time_set2(void);void InitTimer0(void){TMOD = 0x01; // 方式1,16位计数器方式TH0 = 0xFC; //定时初值=65536-n n=1000,定时周期是1ms TL0 = 0x18;EA = 1; //开总中断使能ET0 = 1; //允许定时器T0溢出中断TR0 = 1; //T0 运行}void delay(unsigned char t){unsigned char t1;unsigned long t2;for(t1=0;t1<t;t1++){for(t2=0;t2<4000;t2++){;}}TR0=0;}void song(){TH0=timer0h;TL0=timer0l;TR0=1;delay(time);}void sing(){unsigned char k,i=0;time=1;while(time){if(k1==0) break;InitTimer0();Calculation_display();if(k2==0)time_set();else if(k2==1)time_set1();elsetime_set2();p1=~seg_design[8];k=sszymmh[i]+7*sszymmh[i+1]-1;timer0h=FREQH[k];timer0l=FREQL[k];time=sszymmh[i+2];i=i+3;song();}}void main(void){InitTimer0();while(1){Calculation_display();delay_nms(100);if(k2==0)time_set();else if(k2==1)time_set1();elsetime_set2();sing();k1=0;InitTimer0();}}void Timer0Interrupt(void) interrupt 1 using 1 {TH0 = 0xFC;TL0 = 0x18;ms_1_con++;//采用定时扫描方式bit_con++;if(bit_con > 7) bit_con = 0;reg_code = 0x00; //先消隐显示Font_code = Display_Buffer[bit_con];reg_code = bit_design[bit_con];if(k1==1){TR0=0;BELL=!BELL;TH0=timer0h;TL0=timer0l;TR0=1;}}void delay_nms(unsigned int n) //延时N ms{unsigned char a,b;unsigned int c;for(c=n;c>0;c--)for(b=142;b>0;b--)for(a=2;a>0;a--);}void Calculation_display(void){unsigned char day;if(ms_1_con > 999) //1000ms定时到{ms_1_con = 0;s_1_con++;if(s_1_con > 59){s_1_con = 0;m_1_con++;if(m_1_con > 59){m_1_con = 0;h_1_con++;k1=1;if(h_1_con > 23){h_1_con = 0;w_1_con++;if(w_1_con>7)w_1_con=1;switch(mon_1_con){case 1:case 3:case 5:case 7:case 8:case 10:case 12:day=31;break;case 2:day=28;break;case 4:case 6:case 9:case 11:day=30;break;}d_1_con++;if(d_1_con>day){mon_1_con++;d_1_con=1;if(mon_1_con>12){y_1_con++;mon_1_con=1;}}}}}}p1=~seg_design[w_1_con];if(k2==0){if(ms_1_con<500){Display_Buffer[2] = seg_design[10];Display_Buffer[5] = seg_design[10];}else{Display_Buffer[2] = !seg_design[10];Display_Buffer[5] = !seg_design[10];}Display_Buffer[6] = seg_design[s_1_con/10];//秒十位Display_Buffer[7] = seg_design[s_1_con%10]; //秒个位Display_Buffer[3] = seg_design[m_1_con/10]; //分十位Display_Buffer[4] = seg_design[m_1_con%10]; //分个位Display_Buffer[0] = seg_design[h_1_con/10]; //时十位Display_Buffer[1] = seg_design[h_1_con%10]; //时个位}if(k2==1){Display_Buffer[3] = seg_design[y_1_con%10]; //年个位Display_Buffer[2] = seg_design[(y_1_con/10)%10]; //年十位Display_Buffer[1] = seg_design[((y_1_con/100)%10)]; //年百位Display_Buffer[0] = seg_design[y_1_con/1000]; //年千位Display_Buffer[6] = seg_design[d_1_con/10]; //日十位Display_Buffer[7] = seg_design[d_1_con%10]; //日个位Display_Buffer[4] = seg_design[mon_1_con/10]; //月十位Display_Buffer[5] = seg_design[mon_1_con%10]; //月个位}if(k2==2){Display_Buffer[2] = seg_design[10];Display_Buffer[5] = seg_design[10];Display_Buffer[6] = seg_design[s1/10]; //秒十位Display_Buffer[7] = seg_design[s1%10]; //秒个位Display_Buffer[3] = seg_design[m1/10]; //分十位Display_Buffer[4] = seg_design[m1%10]; //分个位Display_Buffer[0] = seg_design[h1/10]; //时十位Display_Buffer[1] = seg_design[h1%10]; //时个位}if(s1==s_1_con&&m1==m_1_con&&h1==h_1_con)k1=1;}void time_set(void){unsigned char day;if(!s_1_con_key){s_1_con++;if(s_1_con > 59){s_1_con = 0;m_1_con++;if(m_1_con > 59){m_1_con = 0;h_1_con++;if(h_1_con > 23){h_1_con = 0;w_1_con++;if(w_1_con>7)w_1_con=1;d_1_con++;switch(mon_1_con){case 1:case 3:case 5:case 7:case 8:case 10:case 12:day=31;break;case 2:day=28;break;case 4:case 6:case 9:case 11:day=30;break;}if(d_1_con>day){mon_1_con++;d_1_con=1;if(mon_1_con>12){y_1_con++;mon_1_con=1;}}}}}}if(!m_1_con_key){m_1_con++;if(m_1_con > 59){m_1_con = 0;h_1_con++;if(h_1_con > 23){h_1_con = 0;w_1_con++;if(w_1_con>7)w_1_con=1;d_1_con++;switch(mon_1_con){case 1:case 3:case 5:case 7:case 8:case 10:case 12:day=31;break;case 2:day=28;break;case 4:case 6:case 9:case 11:day=30;break;}if(d_1_con>day){mon_1_con++;d_1_con=1;if(mon_1_con>12){y_1_con++;mon_1_con=1;}}}}}if(!h_1_con_key){h_1_con++;if(h_1_con > 23){h_1_con = 0;w_1_con++;if(w_1_con>7)w_1_con=1;d_1_con++;switch(mon_1_con){case 1:case 3:case 5:case 7:case 8:case 10:case 12:day=31;break;case 2:day=28;break;case 4:case 6:case 9:case 11:day=30;break;}if(d_1_con>day){mon_1_con++;d_1_con=1;if(mon_1_con>12){y_1_con++;mon_1_con=1;}}}}if(!w_1_con_key){k2=1;}}void time_set1(void){unsigned char day;switch(mon_1_con){case 1:case 3:case 5:case 7:case 8:case 10:case 12:day=31;break;case 2:day=28;break;case 4:case 6:case 9:case 11:day=30;break;}if(!s_1_con_key){d_1_con++;w_1_con++;if(w_1_con>7)w_1_con=1;if(d_1_con>day){mon_1_con++;d_1_con=1;if(mon_1_con>12){y_1_con++;mon_1_con=1;}}}if(!m_1_con_key){mon_1_con++;w_1_con=(w_1_con+day%7)%7;if(mon_1_con>12){y_1_con++;mon_1_con=1;}}if(!h_1_con_key){y_1_con++;if(y_1_con>9999){w_1_con=(w_1_con+365%7)%7;y_1_con=0;}}if(!w_1_con_key){k2=2;}}void time_set2(void){if(!s_1_con_key){s1++;if(s1>59)s1=0;}if(!m_1_con_key){m1++;if(m1>59)m1=0;}if(!h_1_con_key){h1++;if(h1>23)h1=0;}if(!w_1_con_key){k2=0;}}。

数字时钟代码

#include<graphics.h> /* 引入graphic.h */#include<math.h> /* 引入math.h */#include<dos.h> /* 引入dos.h */#define pi 3.1415926 /*定义pi=3.14159*/#define X(a,b,c) x=a*cos(b*c*pi/180-pi/2)+300;#define Y(a,b,c) y=a*sin(b*c*pi/180-pi/2)+240;#define d(a,b,c) X(a,b,c);Y(a,b,c);line(300,240,x,y) /*定义……*/ void init() /*初始化程序*/{int i,l,x1,x2,y1,y2; /*定义……*/setbkcolor(1); /*设置颜色*/circle(300,240,200); /*作园*/circle(300,240,205);circle(300,240,5);for(i=0;i<60;i++) /*循环(算时间)*/{if(i%5==0) l=15;else l=5;x1=200*cos(i*6*pi/180)+300;y1=200*sin(i*6*pi/180)+240;x2=(200-l)*cos(i*6*pi/180)+300;y2=(200-l)*sin(i*6*pi/180)+240;line(x1,y1,x2,y2);}}main(){int x,y;int gd=VGA,gm=2;unsigned char h,m,s; /*定义*/struct time t[1];initgraph(&gd,&gm,"d:\\tc");init();setwritemode(1);gettime(t);h=t[0].ti_hour;m=t[0].ti_min;s=t[0].ti_sec; /*定义时分秒*/setcolor(7); /*设置颜色*/d(150,h,30);setcolor(14);d(170,m,6);setcolor(4);d(190,s,6);while(!kbhit()) /*获取键盘相应*/{while(t[0].ti_sec==s)gettime(t); /*C语言中得到时间的函数*/sound(400); /*计算时间……*/delay(70);sound(200);delay(30);nosound();setcolor(4);d(190,s,6);s=t[0].ti_sec;d(190,s,6);if (t[0].ti_min!=m){setcolor(14);d(170,m,6);m=t[0].ti_min;d(170,m,6);}if (t[0].ti_hour!=h){ setcolor(7);d(150,h,30);h=t[0].ti_hour;d(150,h,30);sound(1000);delay(240);nosound();delay(140);sound(2000);delay(240);nosound();}}getch(); /*设置空格后退出*/closegraph();}具体的。

c语言数字时钟设计实例

#include <reg51.h>#include <absacc.h>#define uchar unsigned char#define PA XBYTE[0x0fefc]#define PB XBYTE[0x0fefd]#define PC XBYTE[0x0fefe]#define CTL XBYTE[0x0feff]code unsigned char pan[]={0x0e7,10,0x0eb,3,0x0ed,2,0x0ee,1, //键盘0x0d7,11,0x0db,6,0x0dd,5,0x0de,4,0x0b7,12,0x0bb,9,0x0bd,8,0x0be,7,0x77,13,0x7b,14,0x7d,0,0x7e,15};unsigned char buf[]={0,0,0,0,0,0,0,0},now,old=0xff;code char led[]={0x0c0,0x0f9,0x0a4,0x0b0, 0x99,0x92,0x82,0x0f8,0x80,0x90,0x0bf, 0x40,0x79,0x24,0x30,0x19,0x12,0x02,0x078,0x00,0x10,0x88,0x0c8,0x8e};//字段码0~9,-,0.~9.,n,fchar time[8]={0,0,0,0,0,0,0,0}; //用于放时间char date[8]={0,0,0,0,0,0,0,0}; //用于放日期int show_state;code int MAX=150;//用于设置时,无键按下的最多时间unsigned char clock_hour=6,clock_minute=30;//设置闹钟的时间char ms50,mx50,hour=5,minute=59,second=55;int year=2008;unsigned char month=10,day=1;// XXXXXXXXXXXXXXXX延时1毫秒XXXXXXXXXXXXXXXX //void delay(void){uchar m;for(m=0;m<150;m++);}//XXXXXXXXXXXXXXXX LED显示子程序1 XXXXXXXXXXXXXXXXX // void scan1(){unsigned char m,tc=0x80;int j;for(m=0;m<8;m++){PA=0x00;PB=tc; tc>>=1;for(j=0;j<1000;j++) delay();PB=0x00;for(j=0;j<100;j++) delay();}}//XXXXXXXXXXX LED显示XXXXXXXXXXX//void scan2(unsigned char x[],char a) {unsigned char m,tb,tc=0x80; for(m=0;m<8;m++){tb=x[m];PA=led[tb];if(m==a){PB=0x00;//灭}else{PB=tc;}//亮tc>>=1;delay();}}void time1() //时间存放数组{time[7]=second%10;time[6]=second/10;time[5]=10;time[4]=minute%10;time[3]=minute/10;time[2]=10;time[1]=hour%10;time[0]=hour/10;}void date1() //日期存放数组{date[7]=day%10;date[6]=day/10;date[5]=month%10+11;date[4]=month/10;date[3]=year%10+11;date[2]=year%100/10;date[1]=year%1000/100;date[0]=year/1000;}//XXXXXXXXXXXX 判断闰年程序XXXXXXXXXXXXXXXXXXX//char runnian(){if((year%400==0)||(year%4==0&&year%100!=0)){return 1;}return 0;}void timechange(void) interrupt 1 using 2 //定时器0中断程序{ int m;unsigned char xday;TF0=0;TH0=0x4B;TL0=0x0ff; //0.05sTR0=1;ms50++;if(ms50>=20)//50毫秒中断20次为1秒{{ms50=0;second++;}if(second>=60){second=0;minute++;}if(minute>=60){minute=0;hour++;}if(hour>=24){hour=0;day++;}if(month==1,3,5,7,8,10,12){xday=31;}if(month==4,6,9,11){xday=30;}if(month==2){if(runnian()==1){xday=29;} else {xday=28;}}//判断闰年if(day>xday){month++;day=1;}if(month>12){year++;month=1;}}//XXXXXXXXXXXXXXXXXXX计算星期几XXXXXXXXXXXXXXXXXXX// char week(){ unsigned char y,w;y=month;if(y==1||y==2) y=y+12;w=(day+1+2*y+3*(y+1)/5+year+year/4-year/100+year/400)%7;//基姆拉尔森计算公式return w;}//XXXXXXXXXXXXXXXXXXX显示星期几XXXXXXXXXXXXXXXXXXX// void show_week(){char n,w,key;show_state=0;w=week();for(n=0;n<8;n++)time[n]=w;while(1){show_state++;if(show_state==MAX) break;key=jian(time);if(key==13)break;scan(time);}}//闹钟响if(hour==clock_hour&&minute==clock_minute){ P3=P3&0x0fb;for(m=0;m<5;m++) delay();P3=P3|0x04;}}//XXXXXXXXXXXXXXXX键盘子程序XXXXXXXXXXXXXXXXXX// unsigned char jianpan(){unsigned char m,row,line,k_value;PC=0xf0;if(PC&0xf0==0xf0) return 0x0ff; //无键按下line=0x0FE;for (m=0;m<4;m++){ PC= line; //输出扫描信号row=PC; //读键盘口if ((row & 0xf0) != 0xf0)break;line=(line<<1)+1;//下一行}if (m==4) return 0xff;k_value = (row & 0xf0) | (line & 0x0f);//给各键赋键值for(m=0;m<32;m=m+2){if(pan[m]==k_value)return pan[m+1];}return 0x0ff;}unsigned char jian(unsigned char a[]){//读键盘5次,每次间隔10ms,判断键值是否有变,起到消抖动作用unsigned char jj[5]={0,0,0,0,0};char n;for(n=0;n<5;n++){ h[n]=jianpan(); scan(a);}if((h[0]==h[1])&&(h[1]==h[2])&&(h[2]==h[3])&&(h[3]==h[4])){now=jj[0];if(now!=old)//键值前后不等{old=now;return now;}return 0xff;}elsereturn 0xff;}//XXXXXXXXXXXXXXXXXXX设置时间XXXXXXXXXXXXXXXXXXX//void set_time(){unsigned char m=0,key=0xff,team=0,j;show_state=0;time[6]=10;//--用于区别时间设置与时间显示time[7]=10;while(1){show_state++;if(show_state==MAX) {team=1;break;}//5s无按键自动退出for(j=0;j<12;j++)scan2(time,m);key=jian(time);//获取键值if(key!=0x0ff){ show_state=0;if(key==13&&(time[0]*10+time[1])<24&&(time[3]*10+time[4])<60)//确定,退出break;else if(key==15) {team=1;break;}//取消,退出else if(key<=9){if(m==0&&key<=2) //控制时、分钟的个位和及十位输入的有效的键值{ time[m]=key;m++; }else if(m==1&&time[0]<2&&key<=9){ time[m]=key;m++; }else if(m==1&&key<=3){ time[m]=key;m++; }else if(m==3&&key<=5){ time[m]=key;m++; }else if(m==4){ time[m]=key;m++; }m=m%5;}}else if(m==2)m++;}if(team==0){hour=time[0]*10+time[1];minute=time[3]*10+time[4];}}//XXXXXXXXXXXXXXXXXXX设置日期XXXXXXXXXXXXXXXXXXX// void set_date(){unsigned char m=0,key,j,team=0;int y=year;show_state=0;date1();date[6]=0;date[7]=1;while(1){show_state++;if(show_state==MAX) {team=1;break;}//5s无按键自动退出for(j=0;j<12;j++)scan2(date,m);key=jian(date);if(key!=0x0ff){ show_state=0;if(key==13&&(date[4]*10+date[5]-11)<13&&(date[4]*10+date[5]-11)>0) //确认退出{break;}else if(key==15) {team=1;break;}{if(m==3) {date[m]=key+11;m++;} //年份的最后一位else if(m==4&&key<=1) {date[m]=key;m++;} //月份的高位只能为0或1else if(m==5){if(date[4]==1&&key<=2) {date[m]=key+11;m++;}//如果月份高位大于0,那月份的低位只能小于3else{date[m]=key+11;m++;}}else if(m==6&&key<=2&&date[4]==0&&date[5]==13) {date[m]=key;m++;}//如果月份是2月,天数的高位要小于3else if(m==6&&key<=3&&date[4]!=0&&date[5]!=13) {date[m]=key;m++;}//不是2月,天数的高位可以为3elseif(m==7&&key<=9&&date[6]==2&&date[4]==0&&date[5]==13)//二月且天数高位为2{year=date[0]*1000+date[1]*100+date[2]*10+date[3]-11;if(runnian()!=1&&key<=8)//不是闰年,低位只能0-8{date[m]=key;m++;}else if(runnian()==1)//是闰年,低位0-9{date[m]=key;m++;}year=y;}else if(m==7&&key<=9&&date[6]==2){date[m]=key;m++;} //不是二月且天数的高位为2,天数的低位0-8else if(m==7&&key<=1&&date[6]==3) //天数的高位为3{y=date[4]*10+date[5]-11;if((y==2||y==4,y==6||y==9||y==11)&&key==0){date[m]=key;m++;} //是2,4,6,9,11月,天数的低位只能为0,否则为1else{date[m]=key;m++;}}else if((m==0||m==1||m==2)&&key<=9) {date[m]=key;m++;} m=m%8;}}}if(team==0){year=date[0]*1000+date[1]*100+date[2]*10+date[3]-11;month=date[4]*10+date[5]-11;day=date[6]*10+date[7];}}//XXXXXXXXXXXXXX开机自检子程序XXXXXXXXXXXXXXXX //void zijian(){int m,j;scan1();//检查数码管p_jiance();for(j=0;j<3;j++){P3=P3&0x0fb;for(m=0;m<1000;m++) delay();P3=P3|0x04;for(m=0;m<1000;m++)delay();}}//XXXXXXXXXXXX LED显示子程序2 XXXXXXXXXXXX //void scan(char buf[]){unsigned char m,tb,tc=0x80;for(m=0;m<8;m++){tb=buf[m];PA=led[tb];PB=tc;tc>>=1;//右移一位delay();}}//XXXXXXXXXXXXXXXXXXX指示灯检测XXXXXXXXXXXXXXXXXXX// void p_jiance(){unsigned char team,m;int j;team=0x80;for(m=0;m<8;m++){P1=~team;team>>=1;for(j=0;j<100;j++)scan(time);}P1=0xff;}//XXXXXXXXXXXXXXXXXXX主程序XXXXXXXXXXXXXXXXXXX // void main(){uchar j,key=0;for(j=0;j<255;j++)delay();CTL=0x88; //设置8255工作方式zijian(); //开机自检TMOD=0x01;TH0=0x4B;TL0=0x0ff; //0.05sTR0=1;IE=0x82;ms50=0;//这两个为50毫秒计数mx50=0;for(j=0;j<255;j++)scan(time);while(1){if(key==10)//时间、日期显示切换{if(mx50>=100)mx50=0;else mx50=101;}else if(key==11)set_time();//时间设置else if(key==12)set_date();//日期设置show_week();//显示星期if(mx50<100)//5秒时间显示{time1();key=jian(time);}else //5秒日期显示{date1();key=jian(date);if(mx50>=200)//重新计数mx50=0;}}}。

数字时钟

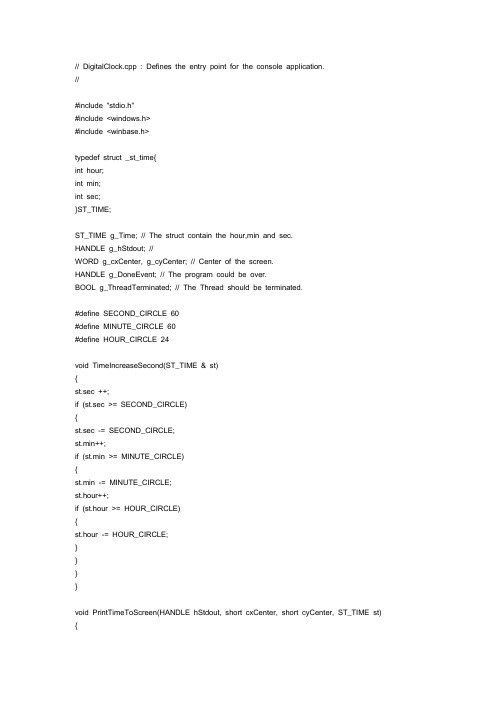

// DigitalClock.cpp : Defines the entry point for the console application.//#include "stdio.h"#include <windows.h>#include <winbase.h>typedef struct _st_time{int hour;int min;int sec;}ST_TIME;ST_TIME g_Time; // The struct contain the hour,min and sec.HANDLE g_hStdout; //WORD g_cxCenter, g_cyCenter; // Center of the screen.HANDLE g_DoneEvent; // The program could be over.BOOL g_ThreadTerminated; // The Thread should be terminated.#define SECOND_CIRCLE 60#define MINUTE_CIRCLE 60#define HOUR_CIRCLE 24void TimeIncreaseSecond(ST_TIME & st){st.sec ++;if (st.sec >= SECOND_CIRCLE){st.sec -= SECOND_CIRCLE;st.min++;if (st.min >= MINUTE_CIRCLE){st.min -= MINUTE_CIRCLE;st.hour++;if (st.hour >= HOUR_CIRCLE){st.hour -= HOUR_CIRCLE;}}}}void PrintTimeToScreen(HANDLE hStdout, short cxCenter, short cyCenter, ST_TIME st) {char buf[64] = {0};COORD crdPos;// make it format to output.sprintf (buf, "%02d:%02d:%02d", st.hour, st.min, st.sec);crdPos.X = cxCenter - 4;crdPos.Y = cyCenter;SetConsoleCursorPosition(hStdout, crdPos);printf(buf);}#ifdef USE_TIMERQUEUE// if we use the timer queue function.// Its procdure is in this.void CALLBACK TimerRoutine (LPVOID lpParam, BOOL TimerOrWaitFired) {if (lpParam == NULL){printf ("NULL parameters.\n");}else{ST_TIME *st = (ST_TIME *)lpParam;TimeIncreaseSecond(st);PrintTimeToScreen(g_hStdout, g_cxCenter, g_cyCenter, *st);}}#elseDWORD WINAPI TimerThreadProc(LPVOID lpParam){#define ID_TIMER_SECOND 1MSG msg;BOOL ret;ST_TIME *st = (ST_TIME *)lpParam;SetTimer(NULL, ID_TIMER_SECOND, 1000, NULL);PeekMessage(&msg, NULL, WM_USER, WM_USER, PM_NOREMOVE);while (!g_ThreadTerminated && (ret = GetMessage (&msg, NULL, 0, 0)) != 0) {if (ret == -1){//process fatal event.}else if (msg.message == WM_TIMER){TimeIncreaseSecond(*st);PrintTimeToScreen(g_hStdout, g_cxCenter, g_cyCenter, *st); }else{TranslateMessage (&msg);DispatchMessage (&msg);}}return 1;}#endif// If the ctrl+break combined key pressed. call this function. // It set the g_DoneEvent. this terminate the program. BOOL WINAPI CtrlHandler(DWORD fdwCtrlType){switch (fdwCtrlType){case CTRL_BREAK_EVENT:// Terminate the program.printf ("Terminate.\n");SetEvent(g_DoneEvent);return TRUE;default:return FALSE;}}BOOL InitApplication(){// Get the stdin and stdout handle.HANDLE hStdIn;hStdIn = GetStdHandle(STD_INPUT_HANDLE);if (hStdIn == INVALID_HANDLE_VALUE)return FALSE;g_hStdout = GetStdHandle(STD_OUTPUT_HANDLE);// Set the mode, make the input echo.DWORD fOldMode;GetConsoleMode(hStdIn, &fOldMode);fOldMode |= ENABLE_LINE_INPUT | ENABLE_ECHO_INPUT;SetConsoleMode(hStdIn, fOldMode);// Set the window buffer.// make a line 40 columns.CONSOLE_SCREEN_BUFFER_INFO csbiInfo;GetConsoleScreenBufferInfo(g_hStdout, &csbiInfo);csbiInfo.srWindow.Right = 40;// get the center point.g_cxCenter = csbiInfo.srWindow.Right / 2;g_cyCenter = csbiInfo.srWindow.Bottom / 2;// Set the window.SetConsoleWindowInfo(g_hStdout, TRUE, &csbiInfo.srWindow);return TRUE;}BOOL PrintTheInitalStateAndGetInput(HANDLE hStdout, WORD cxCenter, WORD cyCenter, ST_TI ME & time){#define GAPS_LEFT_COLON (-2)#define GAPS_RIGHT_COLON (1)#define GAPS_LEFT_UNDERLINE_START (-4)#define GAPS_MIDDLE_UNDERLINE_START (-1)#define GAPS_RIGHT_UNDERLINE_START (2)// __:__:__// So the left ":" center -2// so the right ":" center + 1// so the left "_" center - 4;// so the lfet "_" center - 1;// so the right "_" center + 2;COORD crdPos;crdPos.X = cxCenter + GAPS_LEFT_COLON;crdPos.Y = cyCenter;SetConsoleCursorPosition(hStdout, crdPos);printf (":");crdPos.X = cxCenter + GAPS_RIGHT_COLON;SetConsoleCursorPosition(hStdout, crdPos);printf (":");crdPos.X = cxCenter + GAPS_LEFT_UNDERLINE_START;SetConsoleCursorPosition(hStdout, crdPos);scanf ("%d", &time.hour);crdPos.X = cxCenter + GAPS_MIDDLE_UNDERLINE_START; SetConsoleCursorPosition(hStdout, crdPos);scanf ("%d", &time.min);crdPos.X = cxCenter + GAPS_RIGHT_UNDERLINE_START; SetConsoleCursorPosition(hStdout, crdPos);scanf ("%d", &time.sec);if (time.hour < 0 || time.hour > HOUR_CIRCLE ||time.min < 0 || time.min > MINUTE_CIRCLE ||time.sec < 0 || time.sec > SECOND_CIRCLE)return FALSE;return TRUE;}int main(int argc, char* argv[]){InitApplication();PrintTheInitalStateAndGetInput(g_hStdout, g_cxCenter, g_cyCenter, g_Time);// create a event to tell the program to terminate.g_DoneEvent = CreateEvent(NULL, TRUE, FALSE, NULL);#ifdef USE_TIMERQUEUEHANDLE hTimerQueue, hTimer;hTimerQueue = CreateTimerQueue();if (!CreateTimerQueueTimer(&hTimer,hTimerQueue, TimerRoutine, &g_Time, 1000, 0, 0)){printf("CreateTimerQueueTimer failed (%d)\\n", GetLastError());return 3;}#else// create the thread.HANDLE hThreadTimer;DWORD dwThreadId;g_ThreadTerminated = FALSE;hThreadTimer = CreateThread(NULL, 0,TimerThreadProc, &g_Time, 0, &dwThreadId);if (hThreadTimer == NULL){}#endifSetConsoleCtrlHandler(CtrlHandler, TRUE);if (WaitForSingleObject(g_DoneEvent, INFINITE) != WAIT_OBJECT_0)printf("WaitForSingleObject failed (%d)\\n", GetLastError());#ifdef USE_TIMERQUEUEif (!DeleteTimerQueue(hTimerQueue))printf("DeleteTimerQueue failed(%d) \\n", GetLastError());#elseg_ThreadTerminated = TRUE;if (WaitForSingleObject(hThreadTimer, INFINITE) != WAIT_OBJECT_0) printf("WaitForSingleObject failed (%d)\\n", GetLastError());#endifreturn 0;}。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY SECOND1 ISPORT(CLKS,CLR:IN STD_LOGIC;SECS,SESG:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);COUT1:OUT STD_LOGIC);END SECOND1;ARCHITECTURE S OF SECOND1 ISBEGINPROCESS(CLKS,CLR)V ARIABLE SS,SG:STD_LOGIC_VECTOR(3 DOWNTO 0);V ARIABLE CO:STD_LOGIC;BEGINIF CLR='1' THEN SS:="0000";SG:="0000";ELSIF CLKS'EVENT AND CLKS='1' THENIF (SS="0101") AND (SG="1001") THENSS:="0000";SG:="0000";CO:='1';ELSIF SG<"1001" THENSG:=SG+1;CO:='0';ELSIF SG="1001" THENSG:="0000";SS:=SS+1;CO:='0';END IF;END IF;COUT1<=CO;SECS<=SS;SESG<=SG;END PROCESS;END S;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY MIN1 ISPORT(CLKM,CLR:IN STD_LOGIC;MINS,MING:BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);ENMIN,ALARM:OUT STD_LOGIC);END MIN1;ARCHITECTURE M OF MIN1 ISBEGINPROCESS(CLKM,CLR)V ARIABLE MS,MG:STD_LOGIC_VECTOR(3 DOWNTO 0);V ARIABLE SO,ALM:STD_LOGIC;BEGINIF CLR='1' THEN MS:="0000";MG:="0000";ELSIF CLKM'EVENT AND CLKM='1' THENIF (MS="0101") AND (MG="1001") THENMS:="0000";MG:="0000";SO:='1';ALM:='1';ELSIF MG<"1001" THENMG:=MG+1;SO:='0';ALM:='0';ELSIF MG="1001" THENMG:="0000";MS:=MS+1;SO:='0';ALM:='0';END IF;END IF;ALARM<=ALM;ENMIN<=SO;MINS<=MS;MING<=MG;END PROCESS;END M;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY HOUR1 ISPORT(CLKH,CLR:IN STD_LOGIC;HOURS,HOURG:OUT STD_LOGIC_VECTOR(3 DOWNTO 0)); END HOUR1;ARCHITECTURE H OF HOUR1 ISBEGINPROCESS(CLKH,CLR)V ARIABLE HS,HG:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINIF CLR='1' THEN HS:="0000";HG:="0000";ELSIF CLKH'EVENT AND CLKH='1' THENIF (HS="0010") AND (HG="0011") THENHS:="0000";HG:="0000";ELSIF HG<"1001" THENHG:=HG+1;ELSIF HG="1001" THENHG:="0000";HS:=HS+1;END IF;END IF;HOURS<=HS;HOURG<=HG;END PROCESS;END H;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY JIAOFEN ISPORT(EN,CLK,SECIN,M1:IN STD_LOGIC;MINSET:OUT STD_LOGIC);END JIAOFEN;ARCHITECTURE F OF JIAOFEN ISBEGINPROCESS(EN,M1)BEGINIF EN='1' THENIF M1='1' THENMINSET<=CLK;ELSE MINSET<=SECIN;END IF;ELSE MINSET<=SECIN;END IF;END PROCESS;END F;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY JIAOSHI ISPORT(EN,CLK,MININ,H1:IN STD_LOGIC;HOURSET:OUT STD_LOGIC);END JIAOSHI;ARCHITECTURE J OF JIAOSHI ISBEGINPROCESS(EN,H1)BEGINIF EN='1' THENIF H1='1' THENHOURSET<=CLK;ELSE HOURSET<=MININ;END IF;HOURSET<=MININ;END IF;END PROCESS;END J;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY TOP ISPORT(CLKS,CLK,CLR,EN,M1,H1:IN STD_LOGIC;BAO,ALARM:OUT STD_LOGIC;SECS,SESG,MINS,MING,HOURS,HOURG:BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0));END TOP;ARCHITECTURE ONE OF TOP ISCOMPONENT SECOND1PORT(CLKS,CLR:IN STD_LOGIC;SECS,SESG:BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);COUT1:OUT STD_LOGIC );END COMPONENT;COMPONENT MIN1PORT(CLKM,CLR:IN STD_LOGIC;MINS,MING:BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);ENMIN,ALARM:OUT STD_LOGIC );END COMPONENT;COMPONENT HOUR1PORT(CLKH,CLR:IN STD_LOGIC;HOURS,HOURG:BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0) );END COMPONENT;COMPONENT JIAOFENPORT(EN,M1,CLK,SECIN:IN STD_LOGIC;MINSET:OUT STD_LOGIC );END COMPONENT;COMPONENT JIAOSHIPORT(EN,H1,CLK,MININ:IN STD_LOGIC;HOURSET:OUT STD_LOGIC );END COMPONENT;SIGNAL A,B,C,D:STD_LOGIC;BEGINU1:SECOND1 PORT MAP(CLR=>CLR,SECS=>SECS,SESG=>SESG,CLKS=>CLK,COUT1=>A);U2:MIN1 PORT MAP(CLR=>CLR,ALARM=>ALARM,MINS=>MINS,MING=>MING,CLKM=>B,ENMIN=>C );U3:HOUR1 PORT MAP(CLR=>CLR,HOURS=>HOURS,HOURG=>HOURG,CLKH=>D);U4:JIAOFEN PORT MAP(EN=>EN,M1=>M1,CLK=>CLK,SECIN=>A,MINSET=>B);U5:JIAOSHI PORT MAP(EN=>EN,H1=>H1,CLK=>CLK,MININ=>C,HOURSET=>d); PROCESS(CLKS,CLK)BEGINIF CLKS'EVENT AND CLKS='1' THENIF (SECS="0000")AND(SESG="0000")AND(MINS="0000")AND(MING="0000") THENBAO<=CLK ;ELSE BAO<='0';END IF;END IF;END PROCESS;end one;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY JIAOMIAO ISPORT(EN,CLK,O1:IN STD_LOGIC;MIAOSET:OUT STD_LOGIC);END JIAOMIAO;ARCHITECTURE O OF JIAOMIAO ISBEGINPROCESS(EN,O1)BEGINIF EN='1' THENIF O1='1' THENMIAOSET<=CLK;END IF;END IF;END PROCESS;END O;。