AWR射频微波电路设计与仿真教程实验报告

开题报告 AWR平台下的微波电路设计与仿真分析

开题报告 AWR平台下的微波电路设计与仿真分析————————————————————————————————作者:————————————————————————————————日期:2012 届本科毕业设计(论文)开题报告题目年级专业班级学号学院姓名指导教师职称毕业设计(论文)AWR平台下的微波电路设计与仿真分析题目一、课题来源、研究的目的和意义、国内外研究现状及分析微波理论和微波技术的技术是19世纪科学家和数学家奠定的。

1873年麦克斯韦总结了拉普拉斯、泊松、法拉第、高斯等人的研究,提出了电磁场的基本规律和电磁波传播的假说,并指出光也是电磁能量的一种形式。

有麦克斯韦等人建立和完善了麦克斯韦方程。

后由赫兹在1887—1891年做了一系列的实验,完善了麦克斯韦的电磁波理论。

20世纪初无线电技术的快速发展主要发生在高频到甚高频范围。

20世纪40年代第二次世界大战期间,雷达的出现和发展使微波理论和技术得到了人们的根本上的重视。

随后微波在通信领域得到迅速的发展.Microwave Office是AWR公司推出的微波EDA软件,为微波平面电路设计提供了最完整,最快捷和最精速的解答。

它是通过两个模拟器来对微波平面电路进行模拟和仿真的。

对于由集成元件构成的电路,用电炉的方法来处理较为简便;该软件设有“VoltaireXL”的模拟器来处理继承总原件构成的平面微波电路问题,而对于有具体的微带几何图形构成的微波平面电路,则采用场的方法较为有效,;该软件采用的是“EMsight”的模拟器来处理任何多层面结构的三维电磁场的问题。

“VoltaireXL”模拟器内设有一个元件库,在建立电路模型时,可以调出微波电路所用的原件,其中无源器件有电感,电阻、电容、谐振腔、微带线、带状线、同轴线等,非线性元件有双极晶体管、场效应晶体管、二极管等。

“EMsight”模拟器是一个三维电磁场模拟程序包,可用于平面高频电路和天线结构分析。

射频电路课程设计或者微波电路课程设计报告——波导微带转换电路设计报告

波导到微带转换电路一、技术指标要求:工作频率:26.5~40GHz输入/输出驻波比:<1.2插入损耗:<1.0dB二、理论分析:现在波导到微带的转换电路一般采用E面或H面插入探针的办法实现。

本设计做的是H面探针的模型仿真。

仿真模型如下图1所示:矩形波导的主模是TE模,电场在宽边的中心处达到最大值,所以将微带探针从10宽边中心插入波导,这样波导中的场将在探针上尽可能大的激励起电流。

探针附近被激励起的高次模存储无功功率的局部场,使接头具有电抗性质。

由于探针过渡具有容性电抗,一段具有感性电抗的高阻线被串联在探针过渡器后面,以消除容性电抗。

通过仿真发现对转换电路影响较大的参量有6个,分别是:探针长度L1,探针宽度W1,开口面大小(宽d,高h),高阻抗线长度L2,高阻抗线宽度W2,短路面离探针的距离D。

由于短路面为电壁,所以在短路面的四分之一波长处的电场有最大值,设计时将D取为四分之一波长。

三、设计过程:本设计中心频率取工作的两边界和的一半大约为33GHZ,工作频段为26.5GHz 到40GHz。

确定矩形波导尺寸、基板的材料和尺寸以及微带金属条带的初始尺寸并建立模型。

此处采用WR-28标准矩形波导,尺寸为7.112mm*3.556mm,基板材料选用Rogers5880型基片,厚度为0.254mm,相对介电常数为2.2,微带金属条带厚度为0.05mm,通过阻抗软件计算得出50欧姆微带线在33GHZ的宽度为0.75mm。

波导开口面的大小对电路的性能有一定的影响,为了抑制高次模又较好的实现匹配这里取开口面宽边d为1.8mm高h为1mm。

探针的尺寸先设置初始值在通过HFSS仿真优化得出长度L1=1.79mm,宽度W1=0.8mm,厚度取0.05mm。

高阻抗线长度L2=0.5mm,宽度W2=0.3mm,厚度取0.05mm。

短路面至探针的距离经计算得D=2.28mm。

整个波导的长度取为13.28mm。

四、设计结果及存在问题分析:从下图S21的曲线图可以看出在26.5GHZ-40GHZ频段S21的大小都小于0.065Db,信号能很好的传输满足插损要求。

awr 实验报告

awr 实验报告AWR实验报告引言:AWR(Advanced Wireless Research)是一种基于无线通信技术的研究方法,旨在提高无线网络的性能和效率。

本实验报告将介绍我们在AWR实验中的设计、实施和结果分析。

实验目的:我们的实验目的是通过使用AWR软件来设计和模拟无线通信系统。

具体而言,我们希望通过AWR来优化系统的传输速率、信号质量和能耗。

实验步骤:1. 系统设计:我们首先在AWR中设计了一个基于OFDM(正交频分复用)的无线通信系统。

我们选择OFDM是因为它在抗干扰和频谱利用率方面具有优势。

2. 参数设置:我们根据实验需求设置了系统的参数,包括载波频率、子载波数量、调制方式等。

3. 信道建模:我们模拟了不同的信道环境,包括理想信道、多径衰落信道等,以评估系统在不同信道条件下的性能表现。

4. 性能分析:我们通过AWR中的仿真工具,对系统的传输速率、误码率和能耗进行了分析。

同时,我们也对系统的功率谱密度和频谱利用率进行了评估。

5. 优化调整:根据分析结果,我们对系统进行了优化调整,包括调整调制方式、增加码率等,以提高系统性能。

实验结果:在AWR实验中,我们获得了一系列有关无线通信系统性能的数据。

通过分析这些数据,我们得出了以下结论:1. OFDM系统相对于其他调制方式,具有更好的抗干扰性能和频谱利用率。

2. 在多径衰落信道下,系统的传输速率和信号质量会受到一定影响,但通过优化调整可以改善系统性能。

3. 调制方式、码率和信道环境等参数的选择对系统性能有重要影响,需要根据实际情况进行优化调整。

讨论与展望:AWR实验为我们提供了一个全面的无线通信系统设计和优化的平台。

通过实验,我们深入了解了无线通信系统的原理和性能评估方法。

未来,我们可以进一步探索AWR在其他无线通信领域的应用,如5G通信、物联网等。

结论:通过AWR实验,我们成功设计和模拟了一个基于OFDM的无线通信系统,并通过优化调整提高了系统的性能。

射频微波电路综合课程设计带通滤波器实验报告(模板)

射频微波电路综合课程设计带通滤波器实验报告射频微波电路综合课程设计带通滤波器实验报告篇一:射频电路课程设计摘要滤波电路的综合设计是相当复杂的,需要好多理论知识和数学知识做铺垫,我们知道用于无线的模拟电路是在吉赫兹频段,高性能计算机、工作站,当然还有作为这方面例子的个人计算机,他们所使用电路的时钟频率不断的增加。

全球定位系统载波频率在122 7.60m hz~1575.42mh z范围,而此次课程设计主要向大家介绍最大平滑巴特沃兹微波电路和等波纹契比学夫微波电路设计方法。

当微波电路工作在射频的低端频段,可以使用集总参数的元件进行设计,利用集总参数的电感和电容,按照一定的设计规则选取合适的电路和元件的参数,就可以实现归一化低通滤波电路的设计。

然后通过利用频率变换就可以低通微波电路、高通微波电路、带通微波电路和带阻微波电路的设计。

关键字:滤波电路平滑巴特沃兹微波电路等波纹契比学夫微波电路一引言通过对射频设计电路的学习,我们知道无线通信的快速发展,更紧凑的滤波器和混频器电路正在被设计和使用。

通常这些电路的工作频率高于1Ghz。

毫无疑问这种趋势将会继续下去,因此不仅要有独特性能的技术装置,而且要学会对高频电路中遇到的问题进行分析,我们知道随着频率的升高以及其相应的电磁波的波长变得可与分立电路元件的尺寸相比拟时,电阻、电容和电感这些元件的电响应就开始偏离他们的理想频率特性,下面将简单的向大家介绍一下本次滤波电路的设计方法,以及如何对其进行归一化。

微波与射频电路仿真报告

微波射频仿真实验报告一、实验室名称:微波、毫米波实验室二、实验项目名称:微波与射频电路仿真与设计实验三、实验学时:32学时四、实验原理:应用微波电路仿真软件ADS(Advanced Design System),完成给定的微波电路设计任务。

五、实验目的:掌握微波电路CAD的基本概念;了解现代微波电路CAD的基本组成;掌握ADS软件并进行微波电路的建模,仿真,优化和调试等任务。

六、实验内容:微波电路的基本概念;微波网络基本理论;ADS软件的使用方法。

上机操作:1.完成给定的微波器件设计;2.完成实验报告。

七、实验器材(设备、元器件):台式计算机70台;ADS 2009仿真软件;U盘(学生自备)。

八、实验步骤:Wilkinson功分器的设计本实验是利用εr=4.3,厚度h=0.8mm的介质基板,设计公分比是1:1的Wilkinson功分器,在中心频率处实现功率分配功能。

电路模型和参数均参考冯新宇编写的《ADS2009射频电路与仿真》。

之后进对电路行了优化仿真,并生成版图。

虽然带宽不作要求,但是通过不断优化后设计出来的功分器,其分配损耗、隔离度和输入输出端驻波比在较宽的频带内均有较好的特性。

a.设计指标设计一功分器,在f0=3GHz处实现最佳工作,带宽不作要求,并作出版图仿真。

注:本实验设计的是Wilkinson功分器,指标若用设计出来后的指标既是:通带2.9~3.1 GHz,公分比1:1,带内各端口反射系数S11、S22、S33小于-20dB,两端口隔离度S23小于-25dB,传输损耗S21小于3.1dB。

b.功分器简介在射频/微波电路中,为了将功率按一定比例分成两路或多路,需要使用功率分配器(简称功分器),在近代射频/微波大功率固态发射源的功率放大器中广泛的使用功分器,而且通常功分器是成对使用的,现将功率分成若干份,然后在分别放大,再合成输出。

Wilkinson功分器的结构如图1所示,对于功率平分的情况,输入和输出口间的分支线特性阻抗=Z0,线长为四分之一线上波长,在分支线末端跨接一个电阻R,其值为2。

杭电电磁场与微波实验 AWR实验报告 功率放大器的设计仿真与分析

杭州电子科技大学实验报告课程名称:电磁场与微波实验实验名称:功率放大器的设计仿真与分析一实验目的学习功率放大器的设计仿真与分析二实验仪器设备或关键器材机房计算机和软件:三实验内容及步骤1.Choose File > New Project. (建工程) Choose File > Save Project As.2.Creating a Schematic (画电路图)3. Placing a Nonlinear Model from the Library找到器件4.Editing the IV Curve Meter Element (编辑IV曲线仪元素)5.Adding an IV Curve Measurement (添加一个IV曲线的测量)仿真图:6.Creating a Bias Circuit7)Adding Schematic Back Annotation(加入图解)8)Choose Simulate > Analyze.9)Adding a Harmonic Balance Port10)Specifying Nonlinear Simulation Frequencies(指定频率非线性仿真)11)Adding a Large Signal Reflection Coefficient Measurement12)Adding Subcircuits to a Schematic15)Creating a Pout vs. Frequency Measurement仿真图:16)Creating a Dynamic Load Line Measurement17)Copying a Schematic in the Project Browser18)Using Variable Sweeps to Measure IP3 vs Voltage最后的图像是:。

AWR微波实验报告(创建功放电路)

微波实验报告--------创建功放电路实验步骤:1.创建一个工程(project),命名,选择好保存的位置。

2.设置预设工程单位:将电感的单位设置为μH。

3.创建一个新的Schematic。

在Project下Add schematic下选择New schematic,创建一个新的Schematic,命名,保存。

4. 单击右侧窗口左下方的Elem 标签,出现一个工作窗口,用其中的BLT11_chip,IVCURVEI和地组建一个如下电路。

5.对IVCURVEI元件数值进行编辑。

编辑后如下表所示。

6.增加一个IVCURVEI元件的测量曲线。

右击Graphs,选择添加一个Graph,命名为“IV BJT”,图表类型为Rectangular。

7.右击IV BJT,选Add Measurement,在出现的弹出工作单元中,meas. 类型(Meas. Type)选非线性电流(Nonlinear Current),随后Measurement 选项选IV Curve 。

Data Source Name 选IV Curve。

8.点Analyze进行分析。

结果如下:9再创建一个新的Schematic。

在Project下Add schematic下选择New schematic,创建一个新的Schematic,命名,保存。

10. 单击右侧窗口左下方的Elem 标签,出现一个工作窗口,用其中的BLT11_chip,IVCURVEI,电感(IND),电阻(RES),电压源(DCVS),电流表(I_METER),电压表(V_METER)和地组建电路,并设置参数使之如下图所示:11.添加直流电压和电流的测量。

右击Graphs,选择添加一个Graph,命名为“DC Bias”,图表类型为Tabular。

12. .右击DC Bias,选Add Measurement,在出现的弹出单元中,meas. 类型(Meas. Type)选非线性电流,随后Measurement 选项选Icomp 。

AWR微波实验报告(集总参数元件滤波器)

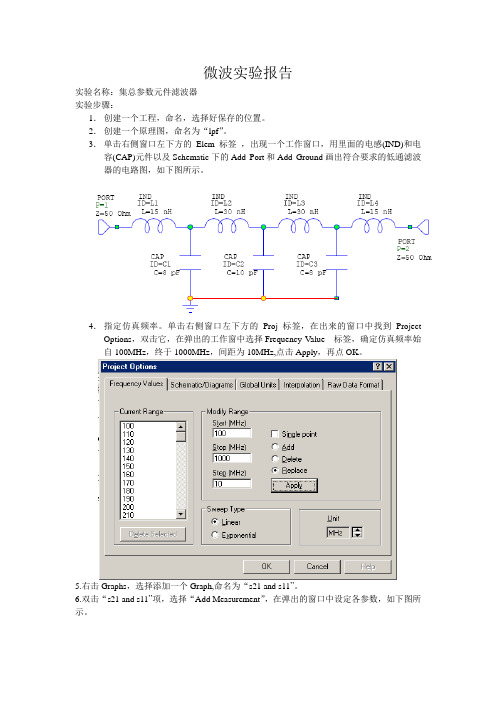

微波实验报告实验名称:集总参数元件滤波器实验步骤:1.创建一个工程,命名,选择好保存的位置。

2.创建一个原理图,命名为“lpf”。

3.单击右侧窗口左下方的Elem 标签,出现一个工作窗口,用里面的电感(IND)和电容(CAP)元件以及Schematic下的Add Port和Add Ground画出符合要求的低通滤波器的电路图,如下图所示。

4.指定仿真频率。

单击右侧窗口左下方的Proj 标签,在出来的窗口中找到Project Options,双击它,在弹出的工作窗中选择Frequency Value 标签,确定仿真频率始自100MHz,终于1000MHz,间距为10MHz,点击Apply,再点OK。

5.右击Graphs,选择添加一个Graph,命名为“s21 and s11”。

6.双击“s21 and s11”项,选择“Add Measurement”,在弹出的窗口中设定各参数,如下图所示。

7点击Analyze按钮进行仿真。

仿真结果如下图所示。

8.调试电路。

单击工具箱中的Tume Tool按钮。

移动图标到电路图的L1,:L4,C1,C3元器件上,点击它们的数值,使之变色。

9在Simulate下选Tune。

弹出一个工作窗。

修改参数使之如下图所示。

10. 在Schematic下选Add Equation。

在原理图出现的方框中输入“Lin=15”。

重复一次,输入“Cin=8”。

并在原理图中将L1,L4,C1,C3的值分别改为Lin,Lin,Cin,Cin。

11. 单击右侧窗口左下方的Var 标签。

在出现的窗口中点“lpf”下的“lpf Equations”,在其下的窗口中的Lin,Cin均点“O”,将两者都定为变量。

如图所示。

12.加上优化目标。

点Proj标签,右击Optimizer Goals,选Add Opt Goal。

然后出现如下图所示窗口。

13.设定lpf:DB(|S[1,1])为当频率f<500MHz时,s11<-17dB。

awr微波实验报告设计低通滤波器

awr微波实验报告设计低通滤波器awr微波实验报告设计低通滤波器篇一:AR微波实验报告实验一A 整流器非线性分析一.实验目的1. 了解非线性二极管整流器工作原理2. 学会AR对电路进行非线性分析及非线性调节二.实验原理所有整流器类别中最简单的是二极管整流器。

在最简单的型式中,二极管整流器不提供任何一种控制输出电流和电压数值的手段。

为了适用于工业过程,输出值必须在一定范围内可以控制。

通过应用机械的所谓有载抽头变换器可以完成这种控制。

作为典型情况,有载抽头变换器在整流变压器的原边控制输入的交流电压,因此也就能够在一定范围内控制输出的直流值。

通常有载抽头变换器与串联在整流器输出电路中的饱和电抗器结合使用。

通过在电抗器中引入直流电流,使线路中产生一个可变的阻抗。

因此,通过控制电抗器两端的电压降,输出值可以在比较窄的范围内控制。

本次试验要求设计一个非线性二极管整流器,添加测量项,调节电阻,观察电压的变化情况,从而去分析二极管的非线性。

三.实验步骤1、完成非线性二极管整流器电路图如下2、设计模拟频率如下3、添加图表,往图表中添加测量项Vtime,A CVS.V1,V_M eter.VM1,并分析电路4、添加图表,往图表中添加测量项Vtime,ACVS.V1,V_Meter.VM1,并分析电路5、使用 Simula te/Tune tl调节MAG及R参数观察Graph1和Gr aph2变化观察得调节MAG会使得测量项ACVS.V1,V_Meter.VM1的幅值变大,而调节R电路特性变化不大。

四.实验总结通过此次试验,学会如何向工程中添加原理图,并成功绘制符合元件参数的原理图。

学会添加图表,往图表中添加非线性测量项。

学会使用T une tl调节电路中元件的参数,从而观察到改元件参数对电路特性的影响。

AWR微波实验报告(创建一个布局版图)

微波实验报告--------创建一个布局版图实验步骤:1.创建一个工程(project),命名,选择好保存的位置。

2.单击Layout标签,在出现的界面中右击Layer Setup,点Import Process Definition,在出现的工作界面中按C:\Program Files\AWR\AWR2002的路径双击打开,选中MIC-English.lpf,打开它。

3.选Options,再选Layout Options,将Grid spacing和Database unit size的参数分别改为0.1和0.01。

4.右击Cell Libraries(单元库),选择Read GDSII Library。

按C:\Program Files\AWR\AWR2002的路径双击打开,再打开Examples,接下去是Quick Start,选中并打开packages.gds。

5.打开工艺信息文件。

点击Proj标签,右击Data Files(GDSII数据格式中的具体数据文件),选择Import Data File,再出现的工作单元中按C:\Program Files\AWR\AWR2002的路径双击打开,依次下去打开Examples和Quick Start文件夹,点击打开N76038a.s2p。

6右击Circuit Schematics,选择New Schematic,将其名字命为qs layout。

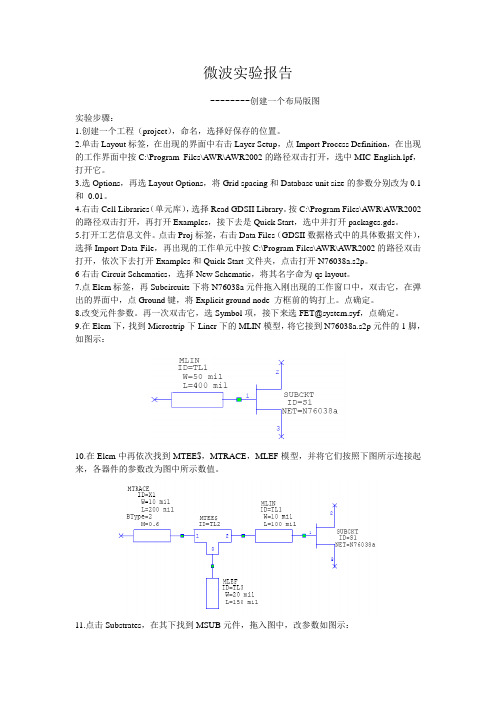

7.点Elem标签,再Subcircuits下将N76038a元件拖入刚出现的工作窗口中,双击它,在弹出的界面中,点Ground键,将Explicit ground node 方框前的钩打上。

点确定。

8.改变元件参数。

再一次双击它,选Symbol项,接下来选FET@system.syf,点确定。

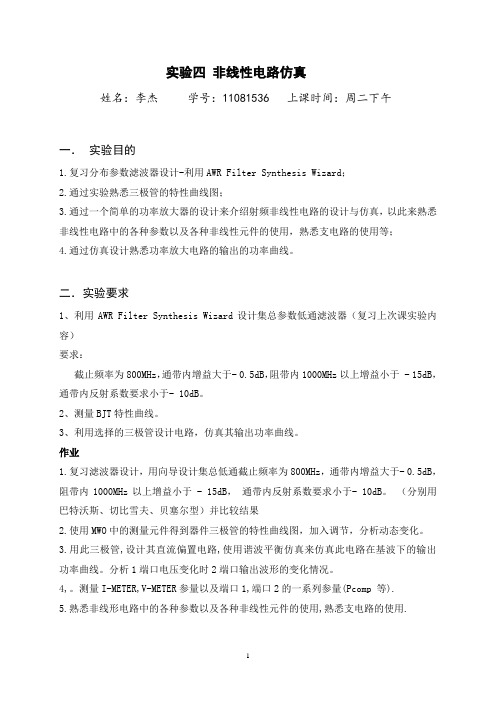

9.在Elem下,找到Microstrip下Liner下的MLIN模型,将它接到N76038a.s2p元件的1脚,如图示:10.在Elem中再依次找到MTEE$,MTRACE,MLEF模型,并将它们按照下图所示连接起来,各器件的参数改为图中所示数值。

微波实验四

实验四非线性电路仿真姓名:李杰学号:11081536 上课时间:周二下午一.实验目的1.复习分布参数滤波器设计-利用AWR Filter Synthesis Wizard;2.通过实验熟悉三极管的特性曲线图;3.通过一个简单的功率放大器的设计来介绍射频非线性电路的设计与仿真,以此来熟悉非线性电路中的各种参数以及各种非线性元件的使用,熟悉支电路的使用等;4.通过仿真设计熟悉功率放大电路的输出的功率曲线。

二.实验要求1、利用AWR Filter Synthesis Wizard设计集总参数低通滤波器(复习上次课实验内容)要求:截止频率为800MHz,通带内增益大于- 0.5dB,阻带内1000MHz以上增益小于 - 15dB,通带内反射系数要求小于- 10dB。

2、测量BJT特性曲线。

3、利用选择的三极管设计电路,仿真其输出功率曲线。

作业1.复习滤波器设计,用向导设计集总低通截止频率为800MHz,通带内增益大于- 0.5dB,阻带内1000MHz以上增益小于 - 15dB,通带内反射系数要求小于- 10dB。

(分别用巴特沃斯、切比雪夫、贝塞尔型)并比较结果2.使用MWO中的测量元件得到器件三极管的特性曲线图,加入调节,分析动态变化。

3.用此三极管,设计其直流偏置电路,使用谐波平衡仿真来仿真此电路在基波下的输出功率曲线。

分析1端口电压变化时2端口输出波形的变化情况。

4,。

测量I-METER,V-METER参量以及端口1,端口2的一系列参量(Pcomp 等).5.熟悉非线形电路中的各种参数以及各种非线性元件的使用,熟悉支电路的使用.三.实验原理1.滤波器类型:巴特沃斯、切比雪夫与贝塞尔滤波器基本概念。

1)巴特沃斯响应(最平坦响应)巴特沃斯响应能够最大化滤波器的通带平坦度。

该响应非常平坦,然后慢慢衰减至截止频率点为-3dB,最终逼近-20ndB/decade的衰减率,其中n为滤波器的阶数。

巴特沃斯滤波器特别适用于低频应用,其对于维护增益的平坦性来说非常重要。

微波技术虚拟实验报告_

微波技术虚拟实验报告班级:1302014学号:一、设计要求设计一个切比雪夫式微波低通滤波器,技术指标为:截止频率c f =2.2GHz ,在通带最大波纹Ar L =0.2dB ,11S 小于-16dB ;在阻带频率s f =4GHz 处,阻带衰减As L 不小于30dB 。

输入、输出端特性阻抗0Z =50Ω。

用微带线实现,基片厚度H=800um ,T=10um ,相对介电常数r ε=9.0;高阻抗线特性阻抗h Z 0=106Ω,低阻抗线l Z 0=10Ω。

计算滤波器的结构尺寸,测量滤波器性能,进行适当调节、优化,使之达到设计指标要求。

记录滤波器的最终优化结果,总结设计、调节经验。

二、实验仪器硬件:PC 机软件:Microwave Office 软件三、设计步骤1.原型滤波器设计(1)利用工程自动生成名为iFilter 的原理图,以及测量图、默认优化目标。

(2)分析,得原型滤波器的仿真结果。

(3)优化:设置优化目标,设置优化参数,执行优化。

(4)优化完成后,将已优化的参数值填入表1。

图1 原型滤波器电路图iFilter (已优化)2.微带线结构滤波器物理尺寸计算 (1)高阻抗线先计算高阻抗线的宽度。

已知条件:r ε=9.0,0f =1.1GHz ,H=800um ,T=10um ,阻抗h Z 0=106Ω,计算得W 、re ε;再计算高阻抗线的长度(手算):reph oh L L v Z L l l ε14-92110310610L00⨯⨯⨯===um (2)低阻抗线先计算低阻抗线的宽度。

已知条件:r ε=9.0,0f =1.1GHz ,H=800um ,T=10um ,阻抗h Z 0=10Ω,计算得W 、re ε;再计算低阻抗线的长度(手算):12140311010310-⨯⨯⨯⨯===Ca Ca v Z l l re pl l C C εum1214021010310-⨯⨯⨯⨯==Cb Cb v Z l repl l C εum将所有计算结果填入表2。

AWR射频微波电路设计与仿真教程实验报告

AWR射频微波电路设计与仿真教程课程实验报告实验名称DBR带通滤波器、功率分配器与耦合器设计i、功率分配器设计一、实验目的设计一个2路等分功率分配器,采用微带电路结构。

输入端特性阻抗Z=50Ω,工作频率f0=3GHz,要求S11、S23<-30dB:基板参数εr=9.8,H=1000um,T=18um。

基本内容:测量特性指标S11、S21、S23(单位dB)与频率(0.5f0~1.5f0)的关系曲线。

调节微带线的尺寸,使功分器的性能达到最佳。

进阶内容:进行版图设计,包括元件封装、布线调节,尤其是 MTRACE2元件的布线扩展内容:利用自动电路提取(ACE)技术,提取电磁模型,进一步缩小版图尺寸。

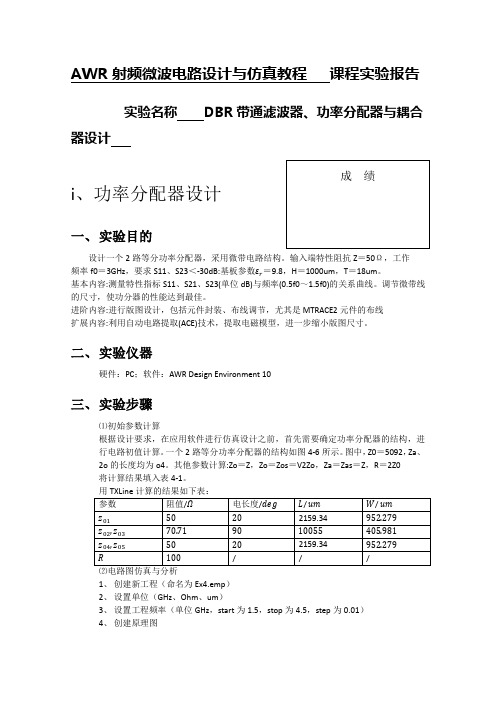

二、实验仪器硬件:PC;软件:AWR Design Environment 10三、实验步骤⑴初始参数计算根据设计要求,在应用软件进行仿真设计之前,首先需要确定功率分配器的结构,进行电路初值计算。

一个2路等分功率分配器的结构如图4-6所示。

图中,Z0=5092,Za、2o的长度均为o4。

其他参数计算:Zo=Z,Zo=Zos=V2Zo,Za=Zas=Z,R=2Z0将计算结果填入表4-1。

⑵电路图仿真与分析1、创建新工程(命名为Ex4.emp)2、设置单位(GHz、Ohm、um)3、设置工程频率(单位GHz,start为1.5,stop为4.5,step为0.01)4、创建原理图5、版图细调检查MTRACE2元件,对该元件进行布线操作,微调之后得到结果如下:6、版图对比分析得到MTRACE2 X1元件参数值为:DB { 2800,1807.134,2412 }umRB { 270,180,270 }W 406L 10004.739BType 2M 0.6对比图表如下:将布线向左侧版图靠拢,会得到不一样的仿真结果。

⑷电磁提取分析一、A CE分析1、添加提取器(STACKUP元件、EXTRACT模块)2、选择提取原件3、提取4、提取出的电磁结构如下图:进行电磁电路联合仿真,得到如下图所示:5、版图小型化调整结果如下:2D结构:6、提取三维电磁电路模型如下:6、进一步压缩版图尺寸得到的模型和分析结果如下:二、A XIEM分析AXIEM分析过程与ACE相似,只是将Simulator项改成AXIEM,不再赘述。

AWR微波实验17通信B1班05陈卫兴

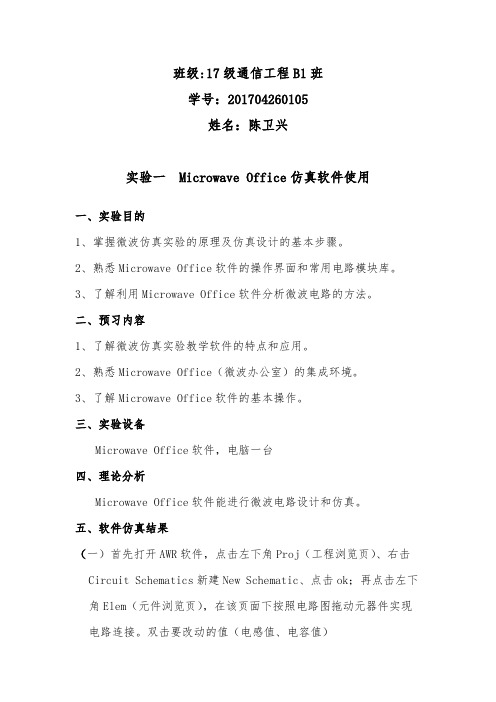

班级:17级通信工程B1班学号:201704260105姓名:陈卫兴实验一 Microwave Office仿真软件使用一、实验目的1、掌握微波仿真实验的原理及仿真设计的基本步骤。

2、熟悉Microwave Office软件的操作界面和常用电路模块库。

3、了解利用Microwave Office软件分析微波电路的方法。

二、预习内容1、了解微波仿真实验教学软件的特点和应用。

2、熟悉Microwave Office(微波办公室)的集成环境。

3、了解Microwave Office软件的基本操作。

三、实验设备Microwave Office软件,电脑一台四、理论分析Microwave Office软件能进行微波电路设计和仿真。

五、软件仿真结果(一)首先打开AWR软件,点击左下角Proj(工程浏览页)、右击Circuit Schematics新建New Schematic、点击ok;再点击左下角Elem(元件浏览页),在该页面下按照电路图拖动元器件实现电路连接。

双击要改动的值(电感值、电容值)(二)设置工作频率:点击左下角Proj(工程浏览页面),双击Project Options,打开界面设置(三)点击左下角Proj(工程浏览页面),右击Graphs的Add Graph、点击OK、右击Graph 1打开Add Measurement界面(勾选DB、点击Add、再点击To Port Lndex上拉2、再点击Add)、点击Analype进行模拟。

(四)调整电路:首先先用螺丝起子点出要修改的参数,才可以调整参数进行观察S参数相应变化。

步骤:点击Schematic 1界面,勾选L1、L4、C1、C3,点Simulate/tune,拖动修改数值,观察S参数变化。

S参数变化情况:调节C2、C3会发现其数值影响S11波谷的数目。

且随得其值的增大,当f>500MHz是,S21会明显下降。

调节L1、L4会发现其值影响S11波谷的尖锐程度,且随着其值的增大,当f>500MHz时,S21会明显下降。

【射频实验报告】 射频电路实验报告(共18页)

【射频实验报告】射频电路实验报告[模版仅供参考,切勿通篇使用]射频电路实验报告学专学生指导学年第学期院:信息与通信工程学院业:电子信息科学与技术姓名:学号:教师:李永红日期: 20xx 年10 月28日实验一滤波器设计一、实验目的掌握基本的低通和带通滤波器的设计方法。

学会使用微波软件对低通和高通滤波器进行设计和仿真,并分析结果。

二、预习内容滤波器的相关原理。

滤波器的设计方法。

三、实验设备microwave office软件四、理论分析滤波器的种类:按通带特性分为低通、高通、带通及带阻四种。

按频率响应分为巴特沃斯、切比雪夫及椭圆函数等。

按使用原件又可分为l-c 性和传输线型。

五、软件仿真设计一个衰减为3db ,截止频率为75mhz 的[切比雪夫型1db 纹波lc 低通滤波器并且要求该滤波器在100mhz 至少有20db 的衰减。

图1-1切比雪夫型1db 纹波lc 低通滤波器电路图图1-2 模拟仿真结果六、结果分析经过仿真,得到了两种滤波器的频率特性的到了结果。

红色的曲线为低通滤波器,蓝色的为带通滤波器,两种滤波器的特性可以鲜明地在图上看出差别。

低通滤波器在低频区域。

是通带,通带非常的平缓,纹波较低,但是截至段不是很陡。

带通滤波器具有较好的陡峭特性,但是相对而言,通带比较窄而且纹波较大。

实验二放大器设计一、实验目的掌握射频放大器的基本原理与设计方法。

学会使用微波软件对射频放大器进行设计和仿真,并分析结果。

二、预习内容放大器的基本原理。

放大器的设计方法。

三、实验设备microwave office软件四、理论分析射频晶体管放大器常用器件为bjt 、fet 、mmic 。

放大器电路的设计主要是输入/输出匹配网络。

输入匹配网络可按低噪声或高增益设计。

输出匹配网络要考虑尽可能高的增益。

五、软件仿真设计一900mhz 放大器。

其中电源为12vdc ,输出入阻抗为50ω。

at4151之s 参表如下列图2-1 900mhz放大器电路图图2-2 模拟仿真结果六、结果分析:本设计是设计一个放大器,其通频段是0到900mhz, 然后根据图上的蓝色和红色曲线可见lc 组成的网络的幅频特性曲线,可见这个网络在900mhz 左右会对信号有一个比较大的衰减,因此必须对输出网络进行阻抗匹配,而且匹配网络的中心频率在900mhz 左右,才可以做好阻抗匹配。

微波技术虚拟实验报告

成绩:

实验2 B 放大器非线性分析

设计要求:设计一放大器,分析其性能。

实验仪器:硬件:PC机,软件:Microwave Office软件

设计步骤:

(1)创建原理图, 添加元件,设置非线性端口激励,输入功率设置为Pwr=-20dbm,完成原理图

(2)添加图表,添加测量项,分析电路,观察功率输出频谱。

(2)计算滤波器的实际尺寸:微带线结构 高阻抗线,已知条件: ,计算 。再由 计算出长度,填入表格;低阻抗线 计算 ,再由 计算长度填入表格。

(3)完成电路,测量各特性指标 创建新原理图,工作频率保持不变完成后分析电路,观察所得曲线。激活实际结构滤波器原理图,观察二维布线图以及三维布线图。记录实际结构滤波器的优化结果。

试验4 集总元件滤波器的线性分析

设计要求:

设计一个电感输入式集总元件滤波器。已知 输入和输出端特性阻抗均为 。工作频率 。

(1)画出原理图,测量 参数(单位dB)与频率的关系曲线。

(2)调节元件值 观察 参数的相应变化。

(3)优化电路,使其满足 时,

时,

记录最终的优化结果:各元件值,便量值及曲线图。

确定滤波器的结构尺寸,测量滤波器的参数 。进行适当调节,使之达到最佳。记录滤波器的最终结构尺寸,总结设计调节经验。

实验仪器:硬件:PC机,软件:Microwave Office软件

设计步骤:

(1)确定原型滤波器 启动软件中的Wizard模块的Filter Synthesie Wizard 功能,输入各项技术指标,即可自带画出原型滤波器的原理图,各个元件值还可以进行优化。 依次选择Lowpass;Chebyshev;在参数定义页,设置N=5,FC=2.2,PP:Ripple(db),PV=0.2,RS=50,RL=50再依次选择Ideal Electrical Model;Lumped Element;Shunt Element First;最后生成名为Filter的原型滤波器的原理图,以及相关的测量图,优化项。将变量名C0 改为Ca,C1 改为Cb ,相应地改变电路中的值,设置工作频率(1~5GHz),分析即得滤波器相应图,包括S参数。 优化 重新设置优化目标: 。进行优化。 优化后将结果填入表1

文献综述 AWR平台下的微波电路设计与仿真分析 文献综述模版

2012 届本科毕业设计(论文)文献综述题目AWR平台下的微波电路设计与仿真分析学院物理与电子工程学院年级2008 专业电子科学与技术班级0502084 学号 050208426姓名张福恒指导教师范瑜职称讲师1、课题要求本毕业设计课题主要研究利用AWR平台进行微波电路的设计、布板,仿真分析与研究,从时域和频域分析有源微波器件特性及其在设计中的各种应用。

课题要求了解有源器件非线性特征的分析与测量;学会AWR中微波电路的分析方法研究与实践;学会微波高频功率放大器的非线性特征分析与参数仿真测试;学会微波高频功率放大器的线性化方法研究与AWR计算仿真分析;掌握AWR平台下的电路设计与布局布板设计。

为完成课题要求我们阅读有关AWR软件平台下Microwave Office的使用并达到熟练掌握的程度。

此外需查阅大量相应的中外有关F类功率放大器的基本资料,掌握其基本构成和基本原理,了解如何提高其效率值以及在不同的频率段设计放大器。

2、文献查阅[1] 格列别尼科夫,射频与微波功率放大器设计。

主要学习了设计射频与微波功率放大器所需的理论、方法、设计技巧,以及将分析计算与计算机辅助设计相结合的优化设计方法。

这些方法提高了设计效率,缩短了设计周期。

[2] 彭沛夫.微波技术与实验。

了解了微波理论和微波技术的技术的基本常识和试验方法,和微波技术今后的发展方向。

[3] 孙绪宝。

微波技术与天线。

微带线是一种重要的微波传输线,它是由介质基片上的导带和基片下的接地板构成。

微带线容易实现微带电路的小型化和集成化。

耦合微带线是由两根平行放置、彼此靠的很近的导带构成,传输的不是纯TEM模,而是具有色散特性的混合模,称为准TEM模。

其具体应用有定向耦合器、滤波器、、变换器等。

[4]倪春,吴先良。

L波段高效率F功率放大器的设计与研究。

F类射频功率放大器是一种新型高效率的放大器,理论效率可以达到100%,在移动通信领域有着广阔的发展前景。

射频微波设计仿真-AWR.Design.Environment.v8.03.doc

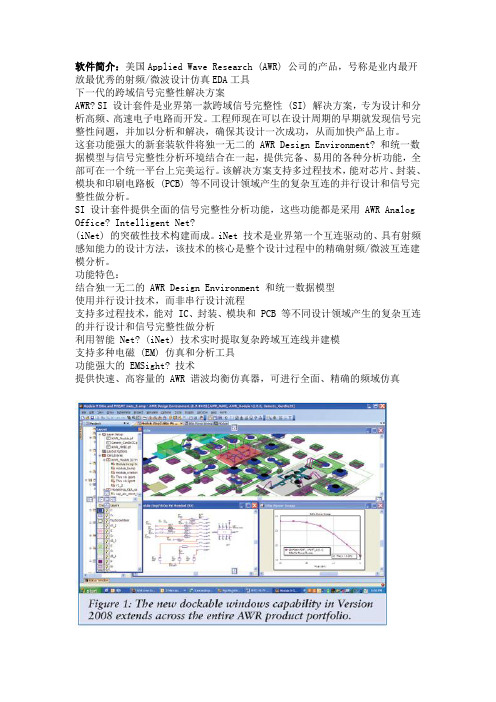

软件简介:美国Applied Wave Research (AWR) 公司的产品,号称是业内最开放最优秀的射频/微波设计仿真EDA工具

下一代的跨域信号完整性解决方案

AWR? SI 设计套件是业界第一款跨域信号完整性 (SI) 解决方案,专为设计和分析高频、高速电子电路而开发。

工程师现在可以在设计周期的早期就发现信号完整性问题,并加以分析和解决,确保其设计一次成功,从而加快产品上市。

这套功能强大的新套装软件将独一无二的 AWR Design Environment? 和统一数据模型与信号完整性分析环境结合在一起,提供完备、易用的各种分析功能,全部可在一个统一平台上完美运行。

该解决方案支持多过程技术,能对芯片、封装、模块和印刷电路板 (PCB) 等不同设计领域产生的复杂互连的并行设计和信号完整性做分析。

SI 设计套件提供全面的信号完整性分析功能,这些功能都是采用 AWR Analog Office? Intelligent Net?

(iNet) 的突破性技术构建而成。

iNet 技术是业界第一个互连驱动的、具有射频感知能力的设计方法,该技术的核心是整个设计过程中的精确射频/微波互连建模分析。

功能特色:

结合独一无二的 AWR Design Environment 和统一数据模型

使用并行设计技术,而非串行设计流程

支持多过程技术,能对 IC、封装、模块和 PCB 等不同设计领域产生的复杂互连的并行设计和信号完整性做分析

利用智能 Net? (iNet) 技术实时提取复杂跨域互连线并建模

支持多种电磁 (EM) 仿真和分析工具

功能强大的 EMSight? 技术

提供快速、高容量的 AWR 谐波均衡仿真器,可进行全面、精确的频域仿真。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

AWR射频微波电路设计与仿真教程课程实验报告实验名称DBR带通滤波器、功率分配器与耦合器设计i、功率分配器设计一、实验目的设计一个2路等分功率分配器,采用微带电路结构。

输入端特性阻抗Z=50Ω,工作频率f0=3GHz,要求S11、S23<-30dB:基板参数εr=9.8,H=1000um,T=18um。

基本内容:测量特性指标S11、S21、S23(单位dB)与频率(0.5f0~1.5f0)的关系曲线。

调节微带线的尺寸,使功分器的性能达到最佳。

进阶内容:进行版图设计,包括元件封装、布线调节,尤其是 MTRACE2元件的布线扩展内容:利用自动电路提取(ACE)技术,提取电磁模型,进一步缩小版图尺寸。

二、实验仪器硬件:PC;软件:AWR Design Environment 10三、实验步骤⑴初始参数计算根据设计要求,在应用软件进行仿真设计之前,首先需要确定功率分配器的结构,进行电路初值计算。

一个2路等分功率分配器的结构如图4-6所示。

图中,Z0=5092,Za、2o的长度均为o4。

其他参数计算:Zo=Z,Zo=Zos=V2Zo,Za=Zas=Z,R=2Z0将计算结果填入表4-1。

⑵电路图仿真与分析1、创建新工程(命名为Ex4.emp)2、设置单位(GHz、Ohm、um)3、设置工程频率(单位GHz,start为1.5,stop为4.5,step为0.01)4、创建原理图5、版图细调检查MTRACE2元件,对该元件进行布线操作,微调之后得到结果如下:6、版图对比分析得到MTRACE2 X1元件参数值为:DB { 2800,1807.134,2412 }umRB { 270,180,270 }W 406L 10004.739BType 2M 0.6对比图表如下:将布线向左侧版图靠拢,会得到不一样的仿真结果。

⑷电磁提取分析一、A CE分析1、添加提取器(STACKUP元件、EXTRACT模块)2、选择提取原件3、提取4、提取出的电磁结构如下图:进行电磁电路联合仿真,得到如下图所示:5、版图小型化调整结果如下:2D结构:6、提取三维电磁电路模型如下:6、进一步压缩版图尺寸得到的模型和分析结果如下:二、A XIEM分析AXIEM分析过程与ACE相似,只是将Simulator项改成AXIEM,不再赘述。

最终得到的结果示例如下图:-四、实验结果分析大多数结果符合预期。

ACE分析的结果的图表两个曲线相差略大,经过分析可能是我做的MTRACE2 X1布局尺寸较小造成的。

在改变耦合距离并记录s11参数时,并未观察到耦合效应,在重做了一遍之后看到了应有的耦合效应。

ii、DBR带通滤波器设计一、实验目的设计一个具有插入损耗小、带宽窄、带外陡峭性高、易于加工等特点的基于DBR结构er 的滤波器,设计一个微波带通滤波器,采用微带线、3阶DBR结构。

指标要求:通带中心频率1GHz,相对带宽5%,S21>-0.1dB:阻带频率分别为875MHz、1125MHz,S21<-40dB,且在低端0.7GHz、0.77GHz、0.85GHz处,高端1.15、1,23、1.3GHz处,均具有传输零点。

基板:介电系数96,厚度1mn双面覆铜,金属厚度08mSs扩展内容:应用 Protel软件,完善硬件版图设计。

二、实验仪器硬件:PC;软件:AWR Design Environment 10三、实验步骤⑴初始参数计算计算条件均为:εr=9.6,H=1mm,T=0.018mm,f0=1GHz将计算结果填入各表中,结果保留一位小数。

表8-1 1阶DBR单元参数表8-2 2阶DBR单元参数⑵原理图仿真创建新工程,命名为 DBR filter. emp。

新建一个电路原理图,命名为DBR。

设置单位:MHz、m:设置工程频率:500~1500MHz;阶长:1MHz。

绘制原理图,添加图表,添加测量项S1、S21。

分析电路,记录初始仿真结果。

调节:手动调节不同DBR单元的元件参数值,观察电路性能变化情况,总结调节特性手动调节x型结构、J变换器的元件参数值,观察电路性能变化情况,总结调节特性。

通过总结调节经验,确定各个DBR单元所对应的传输零点,明确DBR滤波器的设计原理。

优化:参照DBR滤波器的性能指标,设定优化目标;参考调节经验,自行选择相关敏感元件,设定优化参数及其上、下限范围选择适当优化算法,执行优化。

记录优化后的元件参数值及结果图。

考虑电路元件较多,可分组、多次优化,选择最优结果记录参考电路图(L、W值略)及优化结果。

参考电路图如下:优化结果如下:优化结果为:在电路图中加入STACKUP模块和EXTRACT模块,进行ACE提取。

将ACE标签页的最大耦合距离初设为20mm。

不断地改变耦合距离,也得到不同的有ACE提取的结果。

将EXTRACT模块的Simulator项改为AXIEM,进行AXIEM电磁提取分析。

记录提取结果。

二维版图及电磁结构如下图:三维结构如下:四、实验结果分析ACE分析的时候LPF name没有用MIC metric.lpf定义导致出不来结果。

在提取电磁结构之前需要进行模型位置粗调。

电磁分析没有问题,改变耦合距离的时候,分析结果也在随之发生变化。

结果基本符合预期。

iii、耦合器设计一、实验目的基本内容:设计一个具有特定功率分配比的定向耦合器,采用分支线型结构。

指标要求:工作频率为1GHz,输出功率分配比为1.5,输出端隔离度大于30dB,端口特性阻抗均为50Ω。

基板参数:介电系数4.4,基板厚度1mm,覆铜厚度0.035mm。

要求:确定元件参数,调节电路性能,自行调整、压缩版图结构,进行小型化设计:进行ACE分析、AXIEM分析,验证电路性能。

进阶内容:在满足基本内容指标的同时,设计一个具有特定频率抑制点的定向耦合器,采用多个T型结构。

指标要求:频率抑制点在3GHz和4.5GHz,抑制度大于16dB,其他设计指标不变。

要求:确定元件参数,调节电路性能,自行调整、压缩版图结构,进行小型化设计;进行ACE分析、 AXIEN分析,验证电路性能。

扩展内容:硬件版图设计。

将AWR软件设计完成的dxf版图导入 Protel软件,设计符合硬件加工要求的硬件版图。

记录最终版图设计结果。

扩展内容:应用 Protel软件,完善硬件版图设计。

二、实验仪器硬件:PC;软件:AWR Design Environment 10三、实验步骤⑴物理参数计算特定功率比输出、分支线型定向耦合器的结构模型如图所示。

图中,4个端口的连Z0均为52Ω,四分之一波长,其中功率分配比K=1.5,即要求S2n(dB)-Sn(dB)=20lgK =20xlg1.5=32dB。

计算各元件的电参数(阻值、电长度),填入表5-1:再利用 Txline工具计算元件的物理参数(宽F、长),计算条件为:G=4.4,H=1mm,T=0.035m,6=1GHz。

将计算⑵电路原理图仿真1、创建新工程(命名为Ex5.emp)2、设置单位(MHz、mm)3、绘制原理图并创建输出等式(s21、s31、K=s21/s31)4、调节参考电路图如下图所示:测量结果示意图如下图所示:MTEE$ID=TL7MTEE$ID=TL8PORT P=3Z=50 Ohm模型自动连接在电路图中加入STACKUP模块和EXTRACT模块,模块的参数需要自行设置,必须与设计所采用的基板参数相吻合。

将ACE标签页的最大耦合距离初设为20mm,进行ACE 提取。

ACE提取结果如下图:对版图进行小型化设计,缩小版图尺寸。

得到ACE分析结果如下:AXIEM分析结果如下:具有特定功率分配比、特定频率抑制点的定向耦合器采用多个T型结构,需要由分支线型结构向T型结构进行转换计算。

具体转换过程以分支线型的z c1θc1元件为示例进行说明。

通过类似步骤,可以将线性分支结构的z c2θc2元件也转换为T型结构。

具体的转换计算步骤如下:在图5-14中,z c为表5-1中的计算值,θc1=900。

首先将一个z c1θc1微带元件等效变为两个串联的微带元件,等效变换时阻抗z c1不变,串联元件的相位之和必须是θc1的整数倍。

再分别将每一个串联微带元件等效变换为一个T型结构,T型结构的并联枝节Z 元件起到抑制频率的作用。

取θa1=150,继续进行转换计算,最终计算得:Z bj=(1−cosθc1′)cos2θa1tanθbi (cos2θa1−cosθc1′)sinθc1′Z c1再利用TXLine工具,将各个元件的物理参数,计算条件为:εr=4.4,H=1mm,T=0.035mm,f0=1GHz。

将计算结果填入表5-2(保留两位有效数字)分支线阻值/Ω阻值/Ω电长度/deg W/mm L/mmZc1 41.6 Za1 45.47 θa1 15 2.2 6.82 Zb1 25.29 θb1 30 5.12 13.08 Zb2 18.41 θb2 20 7.65 8.56Zc2 75 Za1' 82.01 θa1’15 0.69 7.15 Zb1’45.59 θb1‘30 2.19 13.64 Zb2‘33.19 θb2’20 3.53 8.88端口传输线Z0 50 θ0 / 1.88 10改进版图后模型如下图所示:提取出的电磁结构如下:将ACE模块的最大耦合距离设为60mm,分析电路,观察、记录结果。

进行AXIEM 结果分析,得到下图:四、实验结果分析第一次设置耦合器参数的时候把W和L的顺序弄颠倒了导致了设计失败。

如果四个port设置的不正确的话,也做不出来正确的波形。

Layout要导入MIC-metric.lpf。

给器件画尺寸线需要用标尺圈起来保证准确。

其他大多数结果还是非常符合预期的。

五、实验总结通过这学期的实验,我学习了关于AWR的射频微波电路设计与仿真的相关内容,感觉很大地提升了自己的动手能力、思考能力和实践能力。

这次实验虽然仅有短短的几周,可是学习资料非常丰富,并且经过这个实验我们都得到了知识上的复习和本事上的提高。

正是因为这个实习,加深了我对微波电路仿真的了解,同时对我们专业的发展方向有了初步认识。

这次实习不但巩固了我们平时所学,也为我们日后的专业工作供给了十分实际的便利。

经过这几周,我的动手能力有了明显的提高;它让我养成了课前预习的好习惯。

一直以来就没能养成课前预习的好习惯(虽然一直知道课前预习是很重要的),但经过这半年,让我不仅深深的懂得课前预习的重要,更领会了课前预习的好处。

只有在课前进行了认真的预习,在做实验时效率才会更高,才能收获的更多、掌握的更多;它还提高了我处理数据的能力;做实验就会有数据,有数据就要处理,数据处理的是否得当将直接影响实验成功与否。

课程教学认真到位,内容充实,还有题目测验帮助我们抓住需要掌握的知识点;个人认为该教材非常的详细全面,暂时没有想到可以改进的地方。