用ISE与Modelsim进行FPGA后仿真(时序仿真)的两种方法

搭建Xilinx开发环境(4)------ 使用Modelsim进行后仿真

搭建Xilinx开发环境(4)------ 使用Modelsim进行后仿真在《搭建Xilinx开发环境(2)------ 使用Modelsim进行功能仿真》介绍了如何利用Modelsim进行Xilinx FPGA的功能仿真。

这次介绍一下利用Modelsim进行Xilinx FPGA后仿真的过程。

Step1:在ISE下产生布局布线后的网表,如下图所示操作:执行这一操作后,会在netgen\par文件夹产生两个文件xxx_timsim.v和xxx_timsim.sdf。

前者是用来布局布线后的网表文件,后者布局布线后的时延文件。

Step2:打开Modelsim新建一个工程,将netgen\par文件夹copy到工程目录下,加入xxx_timsim.v文件和testbench文件如果这一步没有讲netgen\par文件夹copy到工程目录,那么仿真时会出一下错误:# ** Error: (vsim-7) Failed to open SDF file "netgen/par/top_timesim.sdf" in read mode.# No such file or directory. (errno = ENOENT)# ** Error: (vsim-SDF-3445) Failed to parse SDF file "netgen/par/top_timesim.sdf".# Time: 0 ps Iteration: 0 Region: /glbl File: F:/FPGA_Project/Xilinx/01_IPcore_test/IPcore_test/work/tes tbench/post/netgen/par/top_timesim.v# Error loading designStep3:添加一个仿真配置文件,并进行配置。

这里主要是添加仿真库,以及制定SDF文件,如何添加仿真库已经在《搭建Xilinx开发环境(2)------ 使用Modelsim进行功能仿真》中介绍过了。

如何在ISE环境中使用ModelSim仿真

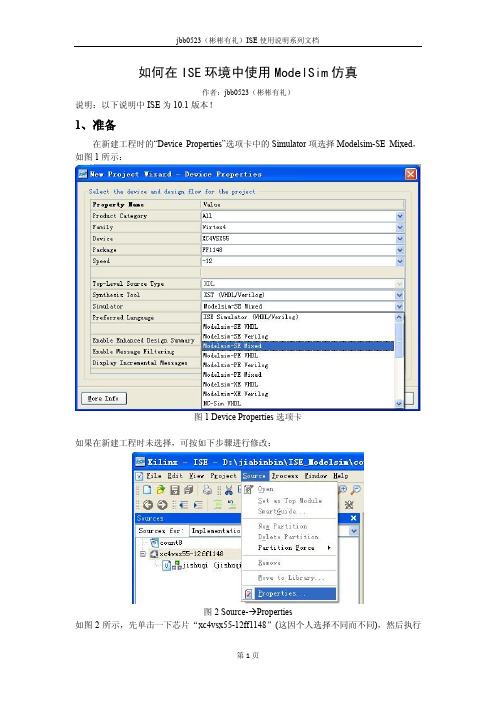

如何在ISE环境中使用ModelSim仿真作者:jbb0523(彬彬有礼)说明:以下说明中ISE为10.1版本!1、准备在新建工程时的“Device Properties”选项卡中的Simulator项选择Modelsim-SE Mixed,如图1所示:图1 Device Properties选项卡如果在新建工程时未选择,可按如下步骤进行修改:图2 Source- Properties如图2所示,先单击一下芯片“xc4vsx55-12ff1148”(这因个人选择不同而不同),然后执行Source——Properties,修改即可。

2、仿真步骤1)如图3所示,在需要仿真的源文件上右击,选择“New Source…”图3 右击---New Source2)如图4所示,在Select Source Type选项卡中选择“Verilog Test Fixture”,输入File name,单周next,直到完成。

图4 Select Source Type3)将source for选择为“Behavioral Simulation”,打开刚刚新建的文件,编辑该文件,输入仿真需要的代码(其实就是对输入信号进行配置)。

然后双击过程管理区的“Simulate Behavioral Model”,即可自动打开ModelSim进行仿真(此时ModelSim不能处于打开状态,否则会出错的),如图5所示(注意图中每一处用红线标记的部分)。

4)如果是首次仿真,ModelSim会出现如下错误:图6 ModelSim error这是一个很普遍的错误,百度此错误中的关键字“Failed to access library 'xilinxcorelib_ver' at "xilinxcorelib_ver".”即可找到解决办法。

如图7所示,Source for中重新选择Implementation,其它按照图中的红线标识单击或选择,然后双击“Compile HDL Simulation Libraries”,等待编译成功结束后,重新执行步骤3)即可。

FPGA初学之前后仿真分析

FPGA初学之前后仿真分析最近在学习FPGA,感觉语⾔的学习到时很容易,但是由于缺乏电路图的硬件知识,所以看起来⽐较难懂,下⾯是对FPGA中仿真的⼀点理解,以后需要学习的地⽅还有很多啊。

⼀、使⽤ISE环境进⾏FPGA系统设计的时候,仿真是⼀个必不可少的步骤,即仿真过程是正确实现设计的关键环节,有两种:1.功能仿真(前仿真):在设计实现前对所创建的逻辑进⾏的验证其功能是否正确的过程,即布局布线以前的仿真。

2.时序仿真(后仿真):指布局布线后仿真,因为加⼊了线延迟信息,所以这⼀步的仿真和真正芯⽚的⾏为最接近,也是⽤于仿真芯⽚时序约束是否添加正确,布局布线后是否还满⾜时序等。

相同:两者仿真使⽤的仿真器是相同的,所需的流程和激励也是相同的;不同:时序仿真加载到仿真器的设计包括基于实际布局布线设计的最坏情况的布局布线延时,并且在仿真结果波形图中,时序仿真后的信号加载了时延,⽽功能仿真没有。

ISE环境中前后仿真的选项:以⼀个ALU的实现功能为例分析前后仿真的不同,其前仿真和后仿真的结果图为:前仿真图后仿真图从时序仿真图可以看出,后仿真存在着延迟。

本实验中存在的延迟也就是⼏ns,但是频率很⾼的时候,延迟可能会达到⼀个或者⼏个周期,这就要求⼯作频率不能超过最⾼⼯作频率。

那么最⾼频率怎么计算呢?⼆、计算最⼤⼯作频率⾸先需要知道FPGA中存在的延时有哪些,下⾯是常⽤的四种:1、纯组合逻辑延时(输⼊引脚到输出引脚),如图:2、输⼊引脚到同步元件之间的延时,如图delay23、同步元件到输出引脚之间的延时,如图delay34、不同时钟Clk1和Clk2之间的异步延时,如图delay4我们知道,⼏乎所有的FPGA设计平台都包含静态时序分析⼯具,利⽤这类⼯具可以获得映射或布局布线后的时序分析报告,从⽽对设计的性能做出评估。

⼯作频率的计算受到时序延时delay1、 delay2、 delay3、 delay4的影响。

在影响⼯作频率的参数中,由于针对某⼀个器件delay2 和delay3 是固定的,因此我们在设计中需要考虑的参数主要就是delay1 和delay4。

用ModelSimSE进行功能仿真和时序仿真的方法(ALTERA篇)

用ModelSimSE进行 功能仿真和时序仿真的方法 (ALTERA篇)黄俊April 2007用ModelSim SE进行功能仿真和时序仿真的方法 (ALTERA篇)软件准备(1) QuartusII,本文截图是QuartusII 6.1界面的。

我个人认为,如果是开发StratixII或CycloneII或MAXII,用QuartusII6.0+SP1+SP2比较稳定。

(2) ModelSim SE. ALTERA仿真库要已经装好,安装仿真库的笔记已记录于《在ModelSimSE中添加ALTERA仿真库的详细步骤》中。

我电脑上装的是ModelSim SE6.1b。

例子程序的制作先在Quartus II里生成一个例子程序,以方便介绍三种仿真的方法。

步骤如下:1、新建一个工程(Project),工程名取lpm_shift, 器件选CycloneII EP2C5Q208C, 第三方的工具暂时都不选。

2、菜单栏上ToolsÆMegaWizard Plug-In Manager, 点Next,在storage中选LPM_SHIFTREG,输出文件格式根据习惯选一种语言,在这里以Verilog的为例,在右边的output file名字中加上lpm_shift。

点Next。

3、这个例子是做一个移位寄存器,调用lpm库,和cycloneII元件库,也正好可以作为对前面建好的ALTERA库的一个验证。

点可以查到该模块的使用说明和详细介绍。

移位寄存器比较简单,就不用细看了。

如下图设置.点Next.4、加上一个异步清零端,点Next,再点Next,最后点Finish.Add/Remove Files in Project…,6、点图标,选中生成的lpm_shift,点打开再点Add都加到项目中去。

7、在这里直接把lpm_shift.v当成顶层文件,就不需要再例化它了。

8、下面写一个简单的TestBench.a)Quartus II工具栏上点图标,选Verilog HDL;b)点,设文件名为top_tb;c)如下所述写一个简单的TestBench.(例子见附件)开始仿真z ModelSim仿真有很多种流程,下面我采用个人感觉比较好一个流程进行仿真验证:基于工程(Project)的流程Step1 新建一个工程Step2 添加文件到工程中去Step3 编译设计文件Step4 启动仿真器,指定顶层设计单元Step5 查看和调试结果z对的设计有三个阶段的仿真。

用ISE与Modelsim进行FPGA后仿真(时序仿真)的两种方法

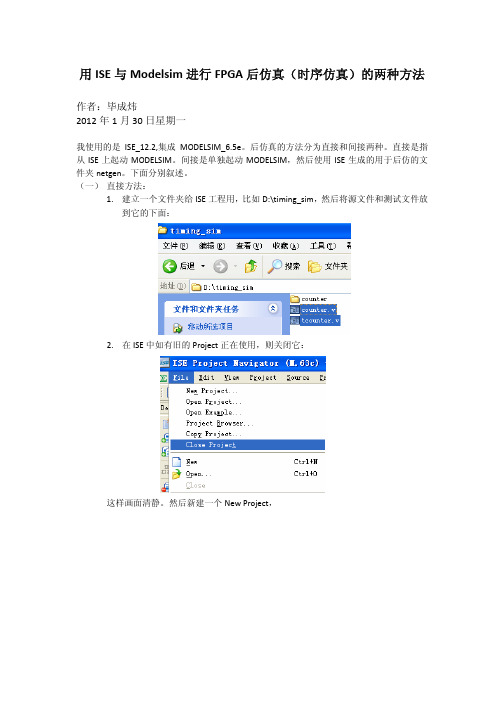

用ISE与Modelsim进行FPGA后仿真(时序仿真)的两种方法作者:毕成炜2012年1月30日星期一我使用的是ISE_12.2,集成MODELSIM_6.5e。

后仿真的方法分为直接和间接两种。

直接是指从ISE上起动MODELSIM。

间接是单独起动MODELSIM,然后使用ISE生成的用于后仿的文件夹netgen。

下面分别叙述。

(一) 直接方法:1.建立一个文件夹给ISE工程用,比如D:\timing_sim,然后将源文件和测试文件放到它的下面:2.在ISE中如有旧的Project正在使用,则关闭它:这样画面清静。

然后新建一个New Project,点Next,选好器件和仿真器:点Next,点Finish.为了能够在ISE中直接唤起MODELSIM,还需要一些设置,主要是两处:双击器件:保证下图红圈处选中你要的仿真器:点OK后,在主菜单中点:保证在红圈处指定好MODELSIM执行文件所在的位置编译仿真库可以在这里双击Compile HDL Simulation Libraries,也可以在C:\Xilinx\12.2\ISE_DS\ISE\bin\nt下面找到,双击它,注意红圈处所标的是你的ISE版本所支持的MODELSIM版本,不能低于它。

否则仿真过程可能出问题。

点Next,点Next,选定你针对什么器件编译仿真库,点Next,点Next,注意,ISE可能最初不带modelsim.ini,它在此步会自动生成这个文件,并且是可写的,即它的“只读”属性是已经自动去掉的。

生成仿真库的映射关系自动写入了ISE的这个modelsim.ini,位于C:\Xilinx\12.2\ISE_DS\ISE\bin\nt,但是,它并不会自动去更新MODELSIM软件的modelsim.ini,而且MODELSIM使用的是它自己的modelsim.ini,位于C:\modeltech_6.5e。

所以需要把ISE的modelsim.ini中的映射关系再COPY到MODELSIM自己的modelsim.ini中。

ISE联合Modelsim进行仿真

参考资料:FPGA应用开发实战技巧精粹

《FPGA应用开发实战技巧精粹》是人民邮电出版社出版的图书,作者是杨跃。 该书介绍了FPGA设计开发的大量技巧,内容包括Xilinx开发软件ISE的使用技巧、Altera开发软 件Quartus的使用技巧、仿真工具ModelSim的使用技巧、综合工具Synplify的使用技巧以及设计 数字电路的一般技巧。

方法/步骤

选择你需要的版本,本版本选择 modelsim SE,选语言,支持的FPGA 芯片,库的类型等

方法/步骤

左图表示了本步骤的内容,以图片内 容为准。

方法/步骤

左图表示了本步骤的内容,以图片内 容为准。

方法/步骤

左图表示了本步骤的内容,以图片内 容为准。

方法/步骤

பைடு நூலகம்

点击生成,这个过程可能需要10多分 钟的时间。

方法/步骤

待库生成完毕后,这个时候回到你的 ISE的安装目录下就会看见一个 Modelsim.ini的文件

(提示在Modelsim的安装目录下也是 有的哦)

方法/步骤

把这个在ISE的安装目录下的 Modelsim.ini打开,把阴影部分的内 容拷贝至你安装好的Modelsim下的 modelsim.ini文件中去(注意:要先 改一下Modelsim下的这个文件的属 性——去掉只读属性)具体见下面几 页的PPT

参考资料:勇敢的芯伴你玩转Xilinx FPGA

《勇敢的芯伴你玩转Xilinx FPGA》是2017年12月1日清华大学出版社出版的图书,作者是吴厚 航。

参考资料:xilinx ise

ISE的全称为Integrated Software Environment,即“集成软件环境”,是Xilinx公司的硬件 设计工具。

modelsim+ISE后仿真流程

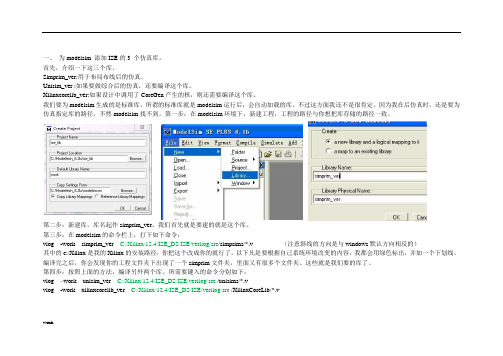

一、为modelsim 添加ISE的3 个仿真库。

首先,介绍一下这三个库。

Simprim_ver:用于布局布线后的仿真。

Unisim_ver :如果要做综合后的仿真,还要编译这个库。

Xilinxcorelib_ver:如果设计中调用了CoreGen产生的核,则还需要编译这个库。

我们要为modelsim生成的是标准库。

所谓的标准库就是modelsim运行后,会自动加载的库。

不过这方面我还不是很肯定。

因为我在后仿真时,还是要为仿真指定库的路径,不然modelsim找不到。

第一步:在modelsim环境下,新建工程,工程的路径与你想把库存储的路径一致。

第二步:新建库,库名起作simprim_ver。

我们首先就是要建的就是这个库。

第三步:在modelsim的命令栏上,打下如下命令:vlog -work simprim_ver C:/Xilinx/12.4/ISE_DS/ISE/verilog/src/simprims/*.v (注意斜线的方向是与windows默认方向相反的)其中的c:/Xilinx是我的Xilinx的安装路径,你把这个改成你的就行了。

以下凡是要根据自己系统环境改变的内容,我都会用绿色标出,并加一个下划线。

编译完之后,你会发现你的工程文件夹下出现了一个simprim文件夹,里面又有很多个文件夹。

这些就是我们要的库了。

第四步:按照上面的方法,编译另外两个库。

所需要键入的命令分别如下:vlog –work unisim_ver C:/Xilinx/12.4/ISE_DS/ISE/verilog/src /unisims/*.vvlog -work xilinxcorelib_ver C:/Xilinx/12.4/ISE_DS/ISE/verilog/src /XilinxCoreLib/*.v第五步:把库建好后,接下来的事情就是使它成为modelsim的标准库。

这只要修改modelsim安装目录下的modelsim.ini文件就可以了。

ISE工程建立和调用modelsim以及仿真波形保存

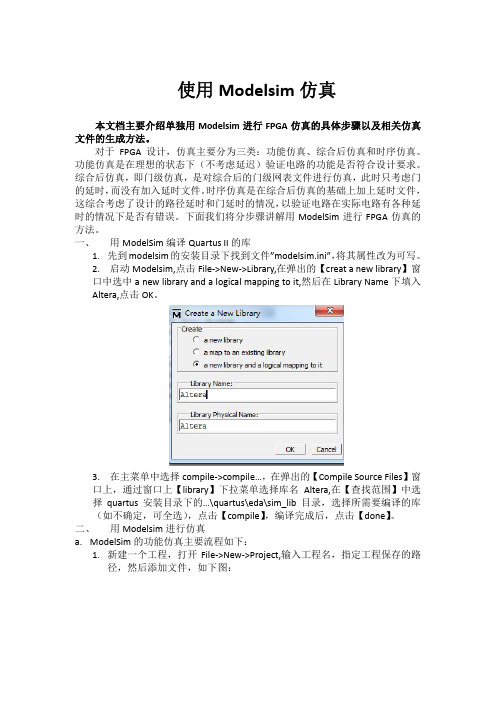

ISE工程建立和调用modelsim 以及仿真波形保存————————————————————————————————作者:————————————————————————————————日期:ISE工程建立和调用modelsim以及仿真波形保存(软件版本:Xilinx ISE Design Suite 12.1和Modelsim SE 6.5c) ISE打开后的默认界面如下图所示图1点击File/New File 或者Project commands框中的New File按键如图2所示,进入图3图2选择合适的工作路径,输入工程名称点击Next如图3所示,结果如图4所示。

图3如下图所示,进入器件属性对话框,如图4所示,本步骤中Family为器件系列,Device为具体器件型号,Package为器件封装,Speed为速度等级,Simulator 选择仿真器。

点击Next进入图5。

点击finish进入图6界面。

图4图5点击左侧的新建文件New Source快捷键,进入图7其中的IP为新建ip核文件,Schematic为新建原理图文件,Verilog Module为新建Verilog文件,Verilog Test Fixture为新建Verilog仿真文件,VHDL Module为新建VHDL文件,VHDL Test Fixture为新建VHDL仿真文件,其他不怎么常用,这里不作介绍。

图6其中的IP为新建ip核文件,Schematic为新建原理图文件,Verilog Module 为新建Verilog文件,Verilog Test Fixture为新建Verilog仿真文件,VHDL Module 为新建VHDL文件,VHDL Test Fixture为新建VHDL仿真文件,其他不怎么常用,这里不作介绍。

图7如下图所示选择建立Verilog文件,右侧输入文件名称,点击Next进入图9图8图9点击Next得到图10点击Finish,进入程序输入界面,如图11所示。

xilinx_ise+model_sim四种仿真

四种Xilinx_ise and Model_sim 仿真1、首先新建一个测试文件,选择Verilog Test Fixture,填入file name 如下:2、添加系统时钟(clk)激励,如下灰色部分,然后点击保存即可。

3、行为仿真(behavioral)选中测试文件,然后再双击下面Simulate Behavioral Model,等待就可以进入ModelSim仿真软件界面4、转换之后的仿真(Post-Translate)(1)首先要生成仿真模型,返回Implementation模式。

双击Implement Design ->Translate -> Generate Post-Translate Simulation Model(2)返回Simulation模式,选中测试文件,双击下面的Simulate Post-Translate Model,就可以进入Post-Translate仿真测试转换之后的仿真描述的是RTL级别的仿真。

从中可以看出数据更新和clk信号有延迟,这也是和行为仿真的区别5、映射之后的仿真(Post-Map)(1)首先要生成仿真模型,返回Implementation模式双击Implement -> Map -> Generate Post-Map SimulationModel(2)返回Simulation模式,选中测试文件,双击下面的Simulate Post-Map Model,就可以进入Post-Map仿真测试(3)Post-Map 仿真测试波形映射之后的仿真能够反映出来器件的工艺和器件之间的一个延时,比上一个转换之后的仿真(Post-Translate)延时更长6、布局布线后仿真(Post-Routes)(1)首先要生成仿真模型,返回Implementation模式双击Implement ->Place & Route -> GeneratePost-Place & Route Simulation Model(2)返回Simulation模式,选中测试文件,双击下面的SimulatePost-Place & Route Model,就可以进入Post-Place & Route仿真测试(3)仿真波形数据有一段时间不稳定,从开始变换到数据稳定,所需时间又比映射之后的仿真(Post-Map)用的时间长。

ISE和Modelsim联合仿真

ISE和Modelsim联合仿真相信很多人会遇到过这个问题,不知如何让ISE调用Modelsim进行仿真。

我也迷糊了不少时间,查查找找,终于弄明白了,所以有了本文,和大家分享一下。

我尽量讲得详细点儿,多多上图。

我的环境:Windows 7 64位,Xilinx ISE Design Suite 13.4(D:\Xilinx\13.4),Modelsim SE-64 10.1a (D:\modeltech64_10.1a,哈,也是64位的)。

不过32位的和64位的设置几乎没有什么区别。

先安装好ISE和Modelsim,网上看过一些文章总说先装ISE再装Modelsim,不过我整过一阵,其实二者的顺序是无关紧要的。

安装过程不在本文的讨论范围内,就不多说了,不过一定要注意版本要合适,Modelsim的版本不要太低,这个可以自己到网上查一查,还有非常重要的一点是安装路径不能有中文或空格。

由于我装的Modelsim SE是通用版的,只自带了少许的仿真库(Simulation Library),所以还要编译一下Xilinx的仿真库。

只有XE才自带Xilinx的仿真库,如果装的是XE版便不必编译仿真库了。

编译库可以用ISE带界面的工具,也可以用命令行下的,前者方便,先讲前者。

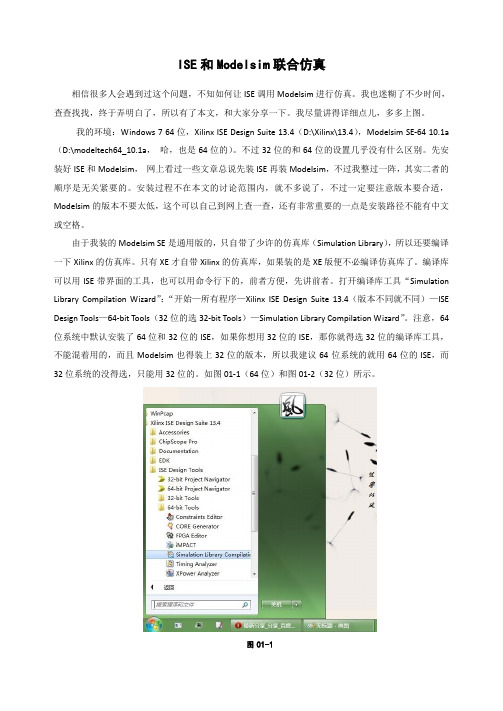

打开编译库工具“Simulation Library Compilation Wizard”:“开始—所有程序—Xilinx ISE Design Suite 13.4(版本不同就不同)—ISE Design Tools—64-bit Tools(32位的选32-bit Tools)—Simulation Library Compilation Wizard”。

注意,64位系统中默认安装了64位和32位的ISE,如果你想用32位的ISE,那你就得选32位的编译库工具,不能混着用的,而且Modelsim也得装上32位的版本,所以我建议64位系统的就用64位的ISE,而32位系统的没得选,只能用32位的。

FPGA设计开发软件ISE使用技巧之:编译与仿真设计工程

FPGA设计开发软件ISE使用技巧之:编译与仿真设计工程6.5 编译与设计工程编写代码完成之后,一个很重要的工作就是验证代码功能的正确性,这就需要对代码举行编译与仿真。

编译主要是为了检查代码是否存在语法错误,仿真主要为了验证代码实现的功能是否正确。

编译和仿真设计工程在囫囵设计中占有很重要的地位。

由于代码功能不正确或代码的编写风格不好对后期的设计会有很大的影响,所以需要花无数时光在设计工程的仿真上。

在这一节中将通过一个详细的实例来介绍如何对编译工程代码以及如何用法ISE自带的仿真工具ISE Simulator举行仿真。

1.编译工程代码编译主要是为了检测代码是否存在语法错误。

在ISE下,源代码的编写是在HDL Editor下完成的,但在HDL Editor下没有特地用于编译代码的选项。

不过在HDL Editor下完成代码的编写后,单击“保存”按钮,HDL Editor就会自动对代码举行编译。

假如代码存在语法错误,就会在信息显示窗中显示出来,用户可以按照显示的提醒,查找语法错误并修改。

6.17所示为在输写代码时遗忘分号,保存后就会有提醒信息。

当不存在错误时,提醒信息就不会浮现“Warning”。

ISE下对于代码的编译功能并不是很强大,有无数错误是检测不出来的。

例如在编写代码时,写case语句时漏写了end case语句,在HDL Editor下是检查不出来的。

但这些错误在仿真或综合阶段是可以检测出来的,因此即使完成了编译没有错误,也一定要举行仿真,检查是否还存在其他的错误。

2.仿真设计工程这里以一个详细的实例来介绍ISE下自带的仿真工具ISE Simulator 的用法,代码参见本书实例代码。

该例程的主要功能是按照拨码开关(sw)输入的值在数码管(seg_led)上显示相应的数值。

图6.17 编译后的出错提醒ISE Simulator的用法主要是借助于ISE的辅助设计工具HDL Bencher(测试激励生成器)来完成的。

Modelsim的功能仿真和时序仿真

FPGA 设计流程包括设计输入,仿真,综合,生成,板级验证等很多阶段。

在整个设计流程中,完成设计输入并成功进行编译仅能说明设计符合一定的语法规范,并不能说明设计功能的正确性,这时就需要通过仿真对设计进行验证。

在FPGA 设计中,仿真一般分为功能仿真(前仿真)和时序仿真(后仿真)。

功能仿真又叫逻辑仿真,是指在不考虑器件延时和布线延时的理想情况下对源代码进行逻辑功能的验证;而时序仿真是在布局布线后进行,它与特定的器件有关,又包含了器件和布线的延时信息,主要验证程序在目标器件中的时序关系。

在有些开发环境中,如Xilinx ISE 中,除了上述的两种基本仿真外,还包括综合后仿真,转换(post-translate)仿真,映射后(post-map)仿真等,这样做完每一步都可进行仿真验证,从而保证设计的正确性。

ModelSim 是Mentor Graphics 子公司MentorTechnology 的产品,是当今最通用的FPGA 仿真器之一。

ModelSim 功能强大,它支持FPGA 设计的各个阶段的仿真,不仅支持VHDL 仿真,Verilog仿真,而且支持VHDL 和Verilog 混合仿真。

它不仅能做仿真,还能够对程序进行调试,测试代码覆盖率,对波形进行比较等。

ModelSim 有很多版本,像ModelSim/SE 是首要版本,除此之外还有ModelSim/XE 和Model Sim/AE,分别是为Xilinx公司和Altera 公司提供的OEM 版,其中已包含各公司的库文件,故用特定公司OEM 版进行仿真时就不需编译该公司的库了。

用ModelSim 进行功能仿真进行功能仿真首先要检查设计的语法是否正确;其次检查代码是否达到设计的功能要求。

下文主要介绍仿真步骤和测试激励的加载。

仿真步骤(1)建立库并映射库到物理目录因为用ModelSim 进行仿真是建立在仿真库的基础上的(此处进行的是功能仿真,因而不用编译特定厂商的库),所以首先要建立库并把库映射到实际的物理路径。

在ise中直接启动modelsim进行后仿真

在ISE中直接启动Modelsim进行后仿真仿真库的命名如果希望从ISE Project Navigator集成开发环境中直接启动Modelsim仿真器,那么对仿真库的命名需要特殊指出,否则Modelsim仿真器无法对仿真库进行映射。

这是因为从ISE 集成开发环境直接调用Modelsim进行仿真时,在工程目录下就会产生一些对Modelsim仿真器有控制作用的文件,这些文件是由ISE在执行过程中通过creatfdo.pl文件生成的,分别使用fdo、tdo、udo 等作为扩展名。

其中udo为用户用户宏文件,用户可以对其进行编译并添加一些对Modelsim的控制指令,而fdo、tdo一般不建议进行编译的。

对verilog进行仿真时,在这些文件中包含了vsim -t lps -L Xinlinxcorelib_ver -L unisims_ver -L simprims_ver -lib work $desunit glbl 命令,对VHDL进行仿真时也有类似的命令。

其中vsim是Modelsim进行仿真的命令,-L 表示仿真时需要的库文件,由此可见,在使用verilog语言编写的工程进行仿真时,默认条件下需要Xinlinxcorelib_ver 、unisims_ver 和simprims_ver三个库文件,其中,Xinlinxcorelib_ver库对应xinlinx提供的软核的功能仿真库,unisims_ver 库对应使用ECS所做原理图的仿真库,simprims_ver 库对应工程布局布线以后的时序仿真库。

VHDL仿真库的命名使用Xinlinxcore、unisims、和simprim三种名称。

在ISE Project Navigator 中编译仿真库使用ISE Project Navigator 集成开发环境,可以很方便的编译需要的仿真库,如果Modelsim当前目录下的modelsim.ini文件为只读,则编译仿真库后在当前工程目录下会自动产生一个modelsim.ini文件为可写,则编译仿真库时直接修改Modelsim目录下的配置文件。

使用ModelSim进行仿真

使用Modelsim仿真本文档主要介绍单独用Modelsim进行FPGA仿真的具体步骤以及相关仿真文件的生成方法。

对于FPGA设计,仿真主要分为三类:功能仿真、综合后仿真和时序仿真。

功能仿真是在理想的状态下(不考虑延迟)验证电路的功能是否符合设计要求。

综合后仿真,即门级仿真,是对综合后的门级网表文件进行仿真,此时只考虑门的延时,而没有加入延时文件。

时序仿真是在综合后仿真的基础上加上延时文件,这综合考虑了设计的路径延时和门延时的情况,以验证电路在实际电路有各种延时的情况下是否有错误。

下面我们将分步骤讲解用ModelSim进行FPGA仿真的方法。

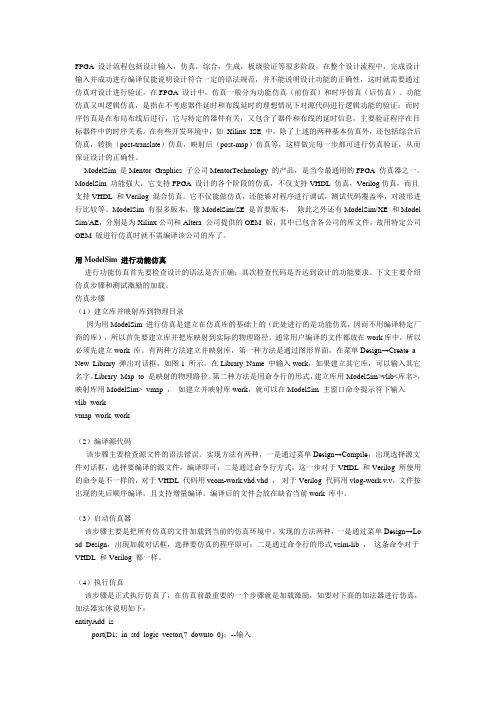

一、 用ModelSim编译Quartus II的库1.先到modelsim的安装目录下找到文件”modelsim.ini”,将其属性改为可写。

2.启动Modelsim,点击File‐>New‐>Library,在弹出的【creat a new library】窗口中选中a new library and a logical mapping to it,然后在Library Name下填入Altera,点击OK。

3.在主菜单中选择compile‐>compile…,在弹出的【Compile Source Files】窗口上,通过窗口上【library】下拉菜单选择库名Altera,在【查找范围】中选择quartus安装目录下的…\quartus\eda\sim_lib目录,选择所需要编译的库(如不确定,可全选),点击【compile】,编译完成后,点击【done】。

二、 用Modelsim进行仿真a.ModelSim的功能仿真主要流程如下:1.新建一个工程,打开File‐>New‐>Project,输入工程名,指定工程保存的路径,然后添加文件,如下图:在project的空白处,单击右键也可以再添加存在的文件或创建新的文件。

2.添加文件到工程中去。

ISE联合modelsim功能仿真和综合后仿真

ISE联合modelsim功能仿真和综合后仿真1、代码输⼊(1)、新建⼀个ISE⼯程,名字为count4。

(2)、新建⼀个verilog⽂件(3)、选择verilog module 输⼊file name为count4,单击next默认知道finish。

(4)、在count4.v⽂件中输⼊以下代码module count4(out,reset,clk);output [3:0] out;input reset,clk;reg [3:0] out;always@(posedge clk) beginif(reset)out<=0;elseout<=out+1;endendmodule(5)、新建⼀个testbench⽂件(综合时,不参与综合),和第(2)步骤相同(6)、选择 verilog Test Fixture。

(7)、创建完成后,输⼊以下代码module count4_tb;reg clk,reset;wire [3:0] out;parameter DELY=100;count4 mycount(.out(out),.reset(reset),.clk(clk));//count4 mycount(out,reset,clk); 若简写,功能仿真正确,时序仿真会因为端⼝不匹配,//会出错always #(DELY/2) clk=~clk;initial beginclk=0;reset=0;#DELY reset=1;#DELY reset=0;#(DELY*200) $finish;endinitial $monitor($time,,,"clk=%d reset=%d out=%d",clk,reset,out);endmodule注:可以修改⽂件的属性,是否为testbench或者为verilog⽂件。

右击要修改的⽂件。

选择source properties修改属性,simulation为testbench .implementation为正常的verilog⽂件2、功能仿真功能仿真放在综合前⾯,是因为⼤型程序综合需要很长的时间,⽽功能仿真不需要综合,可以先功能仿真,确保代码的正确性。

ISE工程实现与Modelsim仿真

ISE工程实现与Modelsim仿真开发环境:ISE 13.2及Modelsim 6.6e1.ISE工程建立和实现1.1 新建工程(1)在ISE软件的菜单栏中选择File->New Project。

(2)在弹出窗口中输入工程名并指定工程目录,点击下一步。

(3)选择所用的器件名和器件参数,点击下一步。

(4)点击Finish,工程建立完成。

1.2 添加设计源文件并进行综合。

(1)在工程设计窗口中右击选择New Source新建源文件或者右击选择ADD Source添加已经编写好的设计源文件和设计约束文件(管脚分配,电平类型,驱动电流等约束)。

(2)添加设计源文件后,在设计窗口的层次结构窗口中选择设计顶层文件,在下面的进程窗口中双击综合选项进行设计综合。

若有错误,则进行修改并重新综合。

若综合后无错误,则可以在Modelsim中进行功能仿真,详细步骤见第二节。

1.3 设计实现综合完成后,在进程窗口中双击Implement Design选项进行设计实现,其中包括翻译,映射,布局布线操作。

1.4 生成编程文件在进程窗口中双击Generate Programming File选项进行生成编程文件。

1.5 下载编程文件(1)在菜单栏中选择Tools->iMPACT,打开编程工具。

(2)将编程器的Cable通过USB连接到计算机并通过JETAG口连接到FPGA器件,在iMPACT 工具中进行编程文件的下载。

2.Modelsim仿真步骤2.1 新建工程(1)在Modelsim菜单栏中选择:File->New->Project。

(2)在弹出窗口中输入工程名并指定工程目录后点击OK。

(3)在弹出窗口中点击ADD Existing File图标添加工程源文件。

(4)点击Browse指定工程源文件目录。

(5)选择设计源文件Counter.v和对应的测试平台Counter_TB.v2.2 编译源文件并开始仿真(1)在工程选项卡下右击选择Compile->Compile All,编译所有设计文件和测试平台文件。

ISEmodelsim联合仿真教程

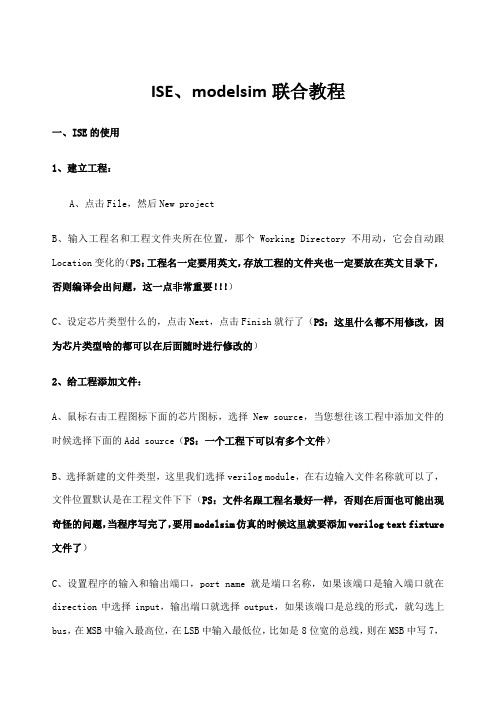

ISE、modelsim联合教程一、ISE的使用1、建立工程:A、点击File,然后New projectB、输入工程名和工程文件夹所在位置,那个Working Directory不用动,它会自动跟Location变化的(PS:工程名一定要用英文,存放工程的文件夹也一定要放在英文目录下,否则编译会出问题,这一点非常重要!!!)C、设定芯片类型什么的,点击Next,点击Finish就行了(PS:这里什么都不用修改,因为芯片类型啥的都可以在后面随时进行修改的)2、给工程添加文件:A、鼠标右击工程图标下面的芯片图标,选择New source,当您想往该工程中添加文件的时候选择下面的Add source(PS:一个工程下可以有多个文件)B、选择新建的文件类型,这里我们选择verilog module,在右边输入文件名称就可以了,文件位置默认是在工程文件下下(PS:文件名跟工程名最好一样,否则在后面也可能出现奇怪的问题,当程序写完了,要用modelsim仿真的时候这里就要添加verilog text fixture 文件了)C、设置程序的输入和输出端口,port name就是端口名称,如果该端口是输入端口就在direction中选择input,输出端口就选择output,如果该端口是总线的形式,就勾选上bus,在MSB中输入最高位,在LSB中输入最低位,比如是8位宽的总线,则在MSB中写7,LSB中写0(PS:这里我用一个之前写的小程序举例子,一个并串转换器,输入有两路,一路是奇数1、3、5、7、9等,一路是偶数2、4、6、8、10等,然后让输出是1、2、3、4、5等,这里我将采取调用IP核的方式,IP核就是ISE封装好的器件,就跟matlab 的内置函数差不多,我们设定好它的参数后直接例化调用它就好了,就不用再自己写了)设置好后点击Next,然后点击Finish即可从这里我们可以看到,刚才设置的参数ISE已经帮我们设置好了,接下来我们开始调用IP 核D、调用IP核,右击practice文件名,选择new source(PS:因为IP核是隶属于verilog 文件的,所以要在文件中添加IP核,这里的隶属关系一定要搞懂!!!)选择那个大灯泡,就是IP核了,同样只需要起名字就行了,不用管位置,名字最好用文件名加个ipcore后缀我们在这个例子中是想用两个fifo来不断的存储和输出数据,通过时钟和读写使能控制fifo实现并串转换,所以我们应该选择fifo的IP核,然后点击next不要点击generate 因为我们还有好多参数要设定这里选择读写不同时钟这里选择读写深度和读写位宽然后这里选择读满、写满等乱七八糟的东西的标志(PS:就是说这个fifo快被写满的时候就会有一个输出端口被拉高或拉低,这里根据个人需求设定,我没有用到就没有勾选)然后选择复位方式然后选择是否使用输出、输入计数端口(就是说要不要用端口来记进入和输出fifo的数据的个数,我们这个例子中并不需要记个数,所以不用勾选),然后点击generate就行了E、例化IP核,找到IP核所在的文件夹,点击左上角的打开按钮找到刚刚设定的IP核名称后缀为.v的文件(我这里是用我之前的文件了,所以是p2s_ipcore.v,如果您按照上述步骤操作这里应该会找到practice_ipcore.v)在该文件中找到下面图中的一段程序把这一段复制到之前创建的主文件中,就是practice.v的文件中的这个位置(在下图),我们发现p2s_ipcore后面多出了一个ipcore1,这个是我们在主程序中给ip核起的名字,就是说,刚才我们在创建ip核时给ip核起的名字是这个ip核在系统中的名字而不是在我们将要编程的文件中的名字,就像在学校别人都叫我们大名,但是在家里父母叫我们小名一样,然后我们也发现上图中的端口名称在下图中也被我们替换掉了,因为我们要给这个fifo输入,并控制它的输出,上图中的端口名只是告诉我们这些端口都是做什么作用,我们肯定是要用我们定义的端口来替换它的,对于不用的端口悬空就行了,比如empty端口我们就没用,悬空就行了,在下图中我们直接把empty删掉了,但是逗号千万不能删,这里有点难理解,您不懂的地方可以随时问我。

ISE与Modelsim进行FPGA后仿真相关操作

ISE与Modelsim进行FPGA后仿真相关操作1.说明工具版本:Win7,ISE13.1,Modelsim SE10.0a2.建立Modelsim SE的Xilinx ISE仿真库的方法1)安装Modelsim和ISE(注册并破解)2)将Modelsim根目录下的modelsim.ini文件的只读属性去掉3)将compxlib文件所在目录(可查看确定默认路径为Xilinx安装目录\Xilinx\13.1\ISE_DS\ISE\bin\nt)添加到环境变量path中(添加环境变量的方法:计算机—右键—属性—高级系统设置—环境变量—选择path—编辑按钮—变量值为:Xilinx安装目录\Xilinx\13.1\ISE_DS\ISE\bin\nt;—确定即可如果变量值已经存在,则不同变量值之间应该以“;”隔开)4)打开Modelsim,在命令窗口(Modelsim下方Transcript)输入:(根据自己的需求)compxlib-s mti_se-arch all-l all-w-lib all(所有语言都编译)compxlib-s mti_se-arch all-l verilog-w-lib all(只编译verilog语言库)compxlib-s mti_se-arch all-l vhdl-w-lib all(只编译VHDL语言库)按回车键,然后请耐心等待一段时间,有可能是30分钟左右,窗口有可能假死。

5)将Modelsim根目录下的modelsim.ini文件属性设为只读6)完成以上步骤,重新启动Modelsim即可在library栏中看到已经生成的Xilinx仿真库3.利用ISE与Modelsim进行FPGA后仿真的方法注:网络上有的文档中提供了两种方法,本文中只对其中一种进行了说明1)Xilinx ISE默认仿真器设置打开ISE,点击Edit—Preference—ISE General下的Integrated Tools,在右侧的Model Tech Simulator中下面将modelsim.exe文件的所在目录C:\modeltech_10.0a\win32\modelsim.exe添加进去。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

用ISE与Modelsim进行FPGA后仿真(时序仿真)的两种方法

作者:毕成炜

2012年1月30日星期一

我使用的是ISE_12.2,集成MODELSIM_6.5e。

后仿真的方法分为直接和间接两种。

直接是指从ISE上起动MODELSIM。

间接是单独起动MODELSIM,然后使用ISE生成的用于后仿的文件夹netgen。

下面分别叙述。

(一) 直接方法:

1.建立一个文件夹给ISE工程用,比如D:\timing_sim,然后将源文件和测试文件放

到它的下面:

2.在ISE中如有旧的Project正在使用,则关闭它:

这样画面清静。

然后新建一个New Project,

点Next,选好器件和仿真器:

点Next,

点Finish.

为了能够在ISE中直接唤起MODELSIM,还需要一些设置,主要是两处:

双击器件:

保证下图红圈处选中你要的仿真器:

点OK后,在主菜单中点:

保证在红圈处指定好MODELSIM执行文件所在的位置

编译仿真库可以在这里双击Compile HDL Simulation Libraries,

也可以在

C:\Xilinx\12.2\ISE_DS\ISE\bin\nt下面找到,双击它,

注意红圈处所标的是你的ISE版本所支持的MODELSIM版本,不能低于它。

否则仿

真过程可能出问题。

点Next,

点Next,

选定你针对什么器件编译仿真库,点Next,

点Next,

注意,ISE可能最初不带modelsim.ini,它在此步会自动生成这个文件,并且是可写的,

即它的“只读”属性是已经自动去掉的。

生成仿真库的映射关系自动写入了ISE的

这个modelsim.ini,位于C:\Xilinx\12.2\ISE_DS\ISE\bin\nt,但是,它并不会自动去更新MODELSIM软件的modelsim.ini,而且MODELSIM使用的是它自己的modelsim.ini,位

于C:\modeltech_6.5e。

所以需要把ISE的modelsim.ini中的映射关系再COPY到MODELSIM自己的modelsim.ini中。

把MODELSIM自己的modelsim.ini的“只读”属性去掉,便可进行

COPY了。

比如ISE的modelsim.ini中,经过点击上图的Launch Compile Process后,

产生了下面的信息:

我们需要把红圈中的信息COPY到MODELSIM自己的modelsim.ini中相应的位置,

如下:

仿真库是编译在了ISE的文件夹下面,MODELSIM可过来使用,虽然可以在编译之前

变换路径,使仿真库编在MODELSIM文件夹下面,但都一样。

现在我们要往工程中填加文件了,

注意View中选的是Impementation,这时要求填加的是可综合的源文件,这里不要把

测试文件加进去,因为测试文件只能加在View的Simulation中,否则加进Impementation在综合的时候会报错,因为测试文件是不能综合的。

注意Association中选定Implementation,点OK。

然后再次填加测试文件,

注意这回Association要选Simulation,这样,测试文件加入后,会体现在View的Simulation中,

上图仿真类型栏中,选上Post‐Route,

然后设定仿真时间长度:

双击下图红圈处的Simulate Post‐Place & Route Model,

便可自动唤醒MODELSIM进行后仿真,出仿真波形的结果。

你不用去管

Implementation之后生成的文件放在哪里。

也不用去设置

MODELSIM,一切都是自动进行的。

ISE能够自动执行后仿真从头到尾的一切流程,

比如综合、实现和唤起MODELSIM。

你所要做的,只是去查看波形。

另外,当查看

的信号不够用时,你要主动去填加信号。

然后保存文件时,会出现

是让你把填加了新信号的WAVE界面保存起来。

下次重新仿真时,需要关掉

MODELSIM,ISE再次唤醒的WAVE界面仍是默认的原始的,未加新信号的。

这时你

可以OPEN先前保存的wave.do文件,出现上次填加了新信号的WAVE界面时,你

要手动去敲执行仿真的命令了。

可从命令行执行run 2000 ns.

(二) 间接方法。

1.源文件加进工程的implementation中,

之后,

双击下图红圈处,

便可在D:\timing_sim\counter\netgen\par下面生成

两个关键文件。

因为D:\timing_sim\counter是ISE的工程路径。

我们要是不想从ISE中唤起

MODELSIM,而是单独起动MODELSIM软件进行仿真,那就需要MODELSIM重新

建一个它自己的工程,我们这里另建一个文件夹,专供MODELSIM的工程所用。

D:\timing_sim\MODELSIM_TEST,建好它以后,很重要的一步是将先前ISE生成的

netgen文件夹考进来,连同netgen里面的内容全部放到MODELSIM工程专用的

根目录下面,D:\timing_sim\MODELSIM_TEST,如下,放进来了:

打开MODELSIM,切换路径至D:\timing_sim\MODELSIM_TEST

点“确定”后,注意红圈处的信息,说明已在所要的路径下。

下面建工程:

工程文件名不一定非要用TOP文件的MODULE名,可以使用任何名,但仍以TOP

文件的MODULE名为最佳。

下面选哪个都无所谓,

但本人选用前者。

点OK后,出现填加文件的页面,

点击Add Existing File,到D:\timing_sim\MODELSIM_TEST\netgen\par里面去找要加

的文件

,

找到counter_timesim.v它是ISE先前生成的专用于后仿的源文件。

点OK后,加进了后仿的源文件。

然后再次填加测试文件,之前已把它放在了

点OK后,可以看到工程中填加了两个文件,一个是专用于后仿的源文件,另一个是测试文件。

不用在这里填加SDF文件,它在另处指定。

此时尚没有进行编译,所以Library中的work下面是空的,

下面将工程中刚才加进去的两个文件进行编译,

成功后,如下:

此时work中出现了三个文件

尤其是多出了一个文件glbl,暂且不用管它。

下面就要进行后仿真了,

加好仿真库,主要是三个:

指定SDF文件的位置。

之前不用往工程中填加,仅在此处指定。

上图的Apply to Region不用去管,有的资料上写上了测试文件的MODULE名/实例名,在我们的例子中,此处如写,可写上

写与不写,经本人的试验,不影响后仿真的进行。

暂且写上吧。

下面选定测试文件和glbl两个文件,不用选源文件,要是全选也一样。

去掉底下的优化选项,

点OK就开始进行后仿真,出现SIGNAL和WAVE画面。

填加信号时,可以

注意不要点dut来进行这样的选择,dut内部信号太多。

我们点test_counter时填加的只是

端口信号。

仿真结果如下:

可以看到时钟到数据有延迟产生。

附源文件和测试文件的源码:

counter.v的内容是:

module counter (count, clk, reset);

output [7:0] count;

input clk, reset;

reg [7:0] count;

always @ (posedge clk or posedge reset)

if (reset)

count <= 8'h00;

else

count <= count + 8'h01;

endmodule

tcounter.v的内容是:

`timescale 1ns/10ps

module test_counter;

reg clk, reset;

wire [7:0] count;

counter dut (.count(count), .clk(clk), .reset(reset));

initial // Clock generator begin

clk = 0;

forever #20 clk = !clk; end

initial // Test stimulus begin

reset = 0;

#5 reset = 1;

#4 reset = 0;

end

endmodule。