Intel XScale(TM) 嵌入式微处理器简介

嵌入式微处理器Intel Atom 处理器

单核处理器

多核与超线程技术比较

多核处理器中的每个物理核有其 独立的AS ,APIC与PER

超线程技术中一个物理核上的2 个逻辑核各自有其独立的AS与 APIC,共享PER

Medfield vs. Clover Trail+

Windows: 有下列模式

Custom Balanced Max Battery Max Performance

D状态案例:内存功耗管理

通过调整内存的D状态,来调节内存电压与性能,达到节能的目的

低功耗应用案例:打印机控制

打印机关闭: 系统通过调节S状态来节能

打印机开启,等待打印任务:通过调节C状态来节能

比传统的S0-S3状态转换更加高效节能。

联网待机:S0ix状态与传统的S3/S4状态 比较

进入“空闲”状态的几个步骤

Dynamic L2 Cache Resizing

在Cache利用率较低时,为了省电, 可以动态关闭L2 Cache的部分 ways, 即从6-way 到 4-way, 再到2way, 再到 0-way (即directmapped cache)。

嵌入式系统

Intel Atom 处理器

部分内容来自Intel产品资料

提纲

提纲

移动计算的两大应用

Atom处理器的大小

基于Atom的智能手机(2012年发布)

基于Atom的平板电脑

Atom处理器的几个版本

Clover Trail: 面向Windows平板电脑 Clover Trail+: 面向Android智能手机与平板电脑 Bay Trail: 2013年底面世 Medfield是单核+超线程技术(hyper-threading),因此共有2个逻辑核;

《嵌入式系统介绍》PPT课件

高度模块化是WinCE的一个鲜为人知的特性,这一特性有 利与它对从掌上电脑到专用的工业控制器的用户电子设备 进行定制。

WinCE操作系统的基本内核需要至少200K的ROM,它支 持 Win32 API子集、多种用户界面硬件、多种的串行和网 络通讯技术、COM/OLE和其他的进程间通讯的先进方法。 Microsoft 公 司 为 Windows CE 提 供 了 Platform Builder 和 Embedded Visual Studio开发工具。

进程调度

网络模块 图形驱动 调度 数据库

模块

驱动程序、硬件抽象层、板级支持包

硬件 (Hardware)

ppt课件

34

图1- 4 RTOS体系结构图

典型嵌入式操作系统介绍

嵌入式操作系统的种类繁多,但大体上可 分为两种——商用型和免费型。

目 前 商 用 型 的 操 作 系 统 主 要 有 VxWorks 、 Windows CE 、 Psos 、 Palm OS 、 OS-9 、 LynxOS、QNX、LYNX等;

电话 无晶体管

BT DECT

1千万个晶体管

3个处理器

诺基亚手机 超过7亿个晶体管

(多数用于存储器) 5-6个处理器

1940

2pp0t课01件

2002

13

计算机的发展

Apple Macintosh

黑白显示器 1 MIP 处理器

Acorn Archimedes 彩色显示器

10 MIP 处理器 … RISC集

ppt课件

8

ARM处理器内核介绍

52v07 ARM普通处理器内核

TM

23

23

2.6 ARM片上总线

AMBA-Advanced Microcontroller Bus Architecture(先进 的微控制器总线体系结构)

AMBA总线定义3种规范

TM

测试芯片 ARM10200E

2

2

IP核、软核、硬核、固核

IP(Intellectual Property)就是常说的知识产权。IP定义为 用于ASIC、ASSP和PLD等当中,并且是预先设计好的电路模块。

IP核模块有行为(Behavior)、结构(Structure)和物理( Physical)三级不同程度的设计,对应描述功能行为的不同分 为三类,即软核(Soft IP Core)、完成结构描述的固核 ( Firm IP Core)和基于物理描述并经过工艺验证的硬核( Hard IP Core)。

52v07 ARM普通处理器内核

TM

18

18

ARM9TDMI 数据通道 (2)

结果 DINFWD

MU 逻辑

B 寄存器 Bank Imm BDATA 移位器

A

乘法器

ALU

PSR

ADATA

锁存

锁存

MU逻辑单元包含有:多路复用器,乘法器和桶形移位器

52v07 ARM普通处理器内核

TM

19

19

ARM9TDMI流水线的变化

52v07 ARM普通处理器内核

TM

16

16

ARM9TDMI

Intel-PXA270嵌入式处理器

XScale StrongARM

家族系列

ARM7 ARM9

处理器内核

ARM7TDMI, ARM7TDMI-S, ARM7EJS,ARM720T ARM920TDMI, ARM922T,ARM940T

结构

ARM V4T ARM V4T

实验教学平台采用的是PXA270微处理器芯片,它是一款集成了32位Intel ARM9E ARM926EJ-S, ARM946E-S, ARM966EJ-S XScale处理器核,多通信信道,LCD控制器、增强型存储器和 PCMCIA/CF控制器,以及通用I/O口的高度集成的应用微处理器。Intel ARM10E ARM1020E, ARM1022E, ARM1026EJ-S XScale微体系结构提供了一种全新的、高性价比、低功耗且基于 ARM11 ARMV6 ARM1156T2-S,ARM1156T2F-S ARMv5TE体系机构的解决方案,并且还支持16位Thumb指令和DSP扩充 指令。基于XSCale技术的微处理器,可用于手机、便携式终端(PDA)、 ARM1176JZ-S 网络存储设备、骨干网(BackBone)路由器等。

英特尔公司于2003年底推出了性能最为强劲的 PXA27x系列嵌入式处理器,PXA27x系列嵌入式处理器 基于ARMv5E的Xscale核心,最高频率可达624MHz。作 为一款性能极其强劲的嵌入式处理器,配合嵌入式Linux 或Wince操作系统,PXA270理论上可以支持任何媒体格 式,并通过软件升级,支持未来媒体格式。但由于媒体播 放对硬件的极高要求,因此单纯依靠PXA270处理器进行 媒体播放是不现实的,实际测试的结果也不理想。因此, 为了满足PXA270的PMP (MP4)功能,必须外加 2700G多媒体加速芯片,配合PXA270进行视频加速与3D 加速。

嵌入式处理器的主要特点

嵌入式处理器的主要特点创易电子整理出品,创易更懂电子, / 全系列阻容感一本全掌控。

2.1嵌入式微处理器的优点2.1.1 低功耗2.1.2功能丰富2.1.2其他2.2嵌入式微处理器的特点三常用处理器概况3.1 处理器分类现状3.1.1嵌入式微处理器(Embedded Microprocessor Unit, EMPU)3.1.2 嵌入式微控制器(Microcontroller Unit, MCU)3.1.3 嵌入式DSP处理器(Embedded Digital Signal Processor, EDSP)3.1.4嵌入式片上系统(System On Chip)3.2 处理器的主要参数3.2.1主频3.2 处理器的缓存四处理器比较4.1 嵌入式控制器和嵌入式处理器的比较4.2 常见处理器简介及特点4.2.1 ARM处理器4.2.2 MIPS4.2.3 Power PC4.2.4 X864.2.5 DSP4.3 应用领域4.3.1 ARM4.3.2 MIPS4.3.3 PowerPC4.3.4 X864.3.5 DSP随着数字信息技术和网络技术高速发展,嵌入式系统已经广泛地渗透到科学研究、工程设计、军事技术、各类产业和商业文化艺术以及人们的日常生活等方方面面中。

国内外各种嵌入式产品进一步开发和推广,嵌入式技术越来越和人们的生活紧密结合。

嵌入式系统的核心部件是各种类型的嵌入式处理器,据不完全统计,目前全世界嵌入式处理器的品种总量已经超过1000多种,流行体系结构有30几个系列,其中8051体系的占有多半。

生产8051单片机的半导体厂家有20多个,共350多种衍生产品,仅Philips就有近100种。

现在几乎每个半导体制造商都生产嵌入式处理器,越来越多的公司有自己的处理器设计部门。

嵌入式处理器的寻址空间一般从64KB到16-32MB,处理速度从O.IMIPS到2000MIPS, 常用封装从8个引脚到144个引脚。

飞思卡尔芯片的嵌入式应用

飞思卡尔芯片的嵌入式应用飞思卡尔(英语:Freescale Semiconductor)是美国的半导体生产厂商。

飞思卡尔于2004年由原摩托罗拉的半导体部门组建。

飞思卡尔的主要产品为面向嵌入和通讯市场的芯片。

其产品包括:微控制器(Kinetis ARM® MCU、Qorivva(5xxx)32位Power Architecture MCU、MAC57Dxxx 32位ARM® MCU、ColdFire+/ColdFire 32位MCU、8位MCU、16位MCU、数字信号控制器、MCU编程中心)、处理器(i.MX ARM®应用处理器Vybrid ARM®控制器解决方案QorIQ处理平台PowerQUICC通信处理器Power Architecture主处理器图像识别处理器加密协处理器StarCore高性能DSPDSP56K/Symphony DSP)、模拟技术与电源管理、射频、传感器嵌入式系统的定义:“用于控制、监视或者辅助操作机器和设备的装置(Devices Used to Control,Monitor or Assist the Operation of Equipment,Machinery or Plants)”。

嵌入式系统包括:1、嵌入式微控制器(16位、8位、以及8位以下的CPU,典型代表就是单片机)2、嵌入式微处理器(32位,以及32位以上的称为处理器,典型为ARM核的处理器)3、DSP(Digital Signal Processing,数字信号处理器)4、SOC(System on Chip,片上系统,就是把所有的模块都做到一块芯片上)飞思卡尔芯片的嵌入式应用实例:一、飞思卡尔为未来智能电网开发解决方案:飞思卡尔不仅提供智能仪表设计所需要的芯片产品,而且提供完美解决方案。

对于公共事业单位如供电厂来说,如何优化配电基础设施,防止可能出现的大面积停电,以及如何有效的为最终用户提供能源服务,都需要智能仪表。

微处理器简介及详细资料

微处理器简介及详细资料基本信息微处理器(英语:Microprocessor,缩写:µP或uP)是可程式化特殊积体电路。

一种处理器,其所有组件小型化至一块或数块积体电路内。

一种积体电路,可在其一端或多端接受编码指令,执行此指令并输出描述其状态的信号。

这些指令能在内部输入、集中或存放起来。

又称半导体中央处理机(CPU),是微型计算机的一个主要部件。

微处理器的组件常安装在一个单片上或在同一组件内,但有时分布在一些不同晶片上。

在具有固定指令集的微型计算机中,微处理器由算术逻辑单元和控制逻辑单元组成。

在具有微程式控制的指令集的微型计算机中,它包含另外的控制存储单元(源自:英汉双解计算机字典)。

用作处理通用数据时,叫作中央处理器。

这也是最为人所知的套用(如:Intel Pentium CPU);专用于作图像数据处理的,叫作Graphics Processing Unit图形处理器(如Nvidia GeForce 7X0 GPU);用于音频数据处理的,叫作Audio Processing Unit音频处理单元(如Creative emu10k1 APU)等等。

物理性来说,它就是一块集成了数量庞大的微型电晶体与其他电子组件的半导体积体电路晶片。

之所以会称为微处理器,并不只是因为它比迷你电脑所用的处理器还要小而已。

最主要的原因,还是因为当初各大晶片厂之制程,已经进入了1 微米的阶段,用1 微米的制程,所产制出来的处理器晶片,厂商就会在产品名称上用“微”字,强调他们很高科技。

就如同现在的许多商业广告一样,很喜欢用“奈米”字眼。

早在微处理器问世之前,电子计算机的中央处理单元就经历了从真空管到电晶体以及再后来的离散式TTL积体电路等几个重要阶段。

甚至在电子计算机以前,还出现过以齿轮、轮轴和杠杆为基础的机械结构计算机。

文艺复兴时期的著名画家兼科学家李奥纳多·达·文西就曾做过类似的设计[来源请求],但那个时代落后的制造技术根本没有能力将这个设计付诸实现。

嵌入式处理器的分类

嵌入式处理器的分类嵌入式处理器的分类全世界嵌入式处理器的品种总量已经超过1000多种,流行的体系结构有30多个系列。

现在几乎每个半导体制造商都生产嵌入式处理器,下面yjbys店铺为大家准备了关于嵌入式处理器的分类,欢迎阅读。

1、嵌入式微处理器(Embedded Microprocessor Unit, EMPU)嵌入式处理器的基础是通用CPU,在应用中,将微处理器装配在专门设计的电路板上,只保留和嵌入式应应用有关的母板功能,这样可以大幅度减少系统体积和功耗。

为了满足嵌入式应用的特殊要求,嵌入式微处理器具有体积小、重量轻、成本低、可靠性高等优点,但是设计中需外加ROM、RAM、总线接口、各种外设等器件,从而降低了系统的可靠性,技术保密性也较差。

嵌入式处理器目前主要有Aml86/88、386EX、SC-400、Power PC、68000、MIPS、ARM系列等。

2、嵌入式微控制器(Microcontroller Unit,MCU)嵌入式微控制器又称单片机,顾名思义,就是将整个计算机系统集成到一片芯片中。

嵌入式微控制器一般以某种微处理器内核为核心,芯片内部集成ROM/EPROM、RAM、总线、总线逻辑、定时/计数器、WatchDog、I/O、串行口、脉冲调制输出、A/D、D/A、Flash等各种必要功能和外设。

和嵌入式微处理器相比,微控制器的最大特点是单片化,体积大大减少,从而使功耗和成本下降、可靠性提高。

嵌入式微控制器是目前嵌入式系统工业的主流。

微控制器的片上外设资源一般比较丰富,适合于控制,故称为微控制器。

嵌入式微控制器目前的品种和数量最多,比较有代表性的`通用系列有8051、P51XA、MCS-251/96、MC68HC05/11/16、68300等。

3、嵌入式DSP处理器(Embedded Digital Signal Processor, EDSP)DSP处理器对系统结构和指令进行了特殊设计,使其适合于执行DSP算法,编译效率较高,指令执行速度快。

Intel网络处理器概述

第十四章Intel网络处理器概述前面我们讨论了网络处理器的一般问题,从本章开始我们将深入讨论一个特定的网络处理器--Intel网络处理器,以便对前面介绍的一般概念提供一个具体的说明。

(1)IXA术语IXA(Internet eXchange Architecture)泛指Intel网络处理器体系结构以及相关的支持芯片。

尽管IXA主要集中在网络处理器硬件,它也包括软件体系结构,因为如果不预想使用硬件的软件,可编程硬件是无法定义的。

IXA包括控制面(慢路径)和数据面(快路径)处理,定义了硬件抽象、应用编程接口和互连机制,但是没有给出细节,IXA只是给出了概念组织。

IXA中有如下三个重要组成部分:●微引擎(Microengine,ME):微引擎是Intel网络处理器的核心部件,也是Intel处理器取得线速处理性能的关键,在其它功能单元的支持下执行快路径上的包处理。

●XScale Core:XScale核是Intel网络处理器的高层控制和管理单元,是与Strong ARM兼容的一种微处理器,负责控制面的处理任务以及异常数据包的处理,上面运行VxWorks、嵌入式Linux等实时操作系统。

●IXA可移植框架(IXA Portability Framework):为基于Intel网络处理器的软件开发提供应用编程接口和硬件抽象,使得运行在XScale核和微引擎上的软件具有良好的可移植性和可重用性。

开发者对新一代网络处理器的要求包括四个方面:灵活性,高性能,可扩展性和可移植性。

IXA能够满足这四个方面的要求。

●灵活性:在IXA架构的网络处理器中,微引擎完全可编程,在低层硬件设备的支持下可实现许多复杂的网络处理功能,具有较好的功能灵活性。

●高性能:IXA架构的网络处理器使用多个可并行操作的微引擎,通过增加微引擎的数目、提高微引擎和XScale核的时钟频率、采用新技术减小存储器访问延时以及增加专用硬件功能单元,可使网络处理器线速处理高达OC-192的网络数据,具备了网络宽带化所要求的高性能。

嵌入式微处理器分类

嵌入式微处理器分类:根据微处理器的字长宽度:微处理器可分为4位、8位、16位、32位、64位。

一般把16位及以下的称为嵌入式微控制器,32位以上的称为嵌入式微处理器。

根据微处理器系统集成度,可划分为两类:一般用途的微处理器,即微处理器内部仅包含单纯的中央处理单元;单芯片微控制器,即将CPU、Rom、RAM及I/O等部分集成到同一个芯片上。

根据嵌入式微处理器的用途:可分为以下几类:1、嵌入式微控制器(MCU),又称为单片机。

微控制器的片上外设资源通常比较丰富,适合于控制,因此称为微控制器。

微控制器芯片内部集成有ROM/EPROM、RAM、总线、总线逻辑、定时/计数器、看门狗、I/O、串行口、脉宽调制输出(PWM)、A/D、D/A、Flash、EEPROM等各种必要功能和外设。

微控制器的最大特点是单片化,功耗成本低,可靠性高。

常用的有8051、MCS系列、C540、MSP430系列等,目前,微控制器占嵌入式系统的约70%的市场份额。

2、嵌入式微处理器(EMPU)。

由通用计算机中的CPU发展而来,主要特点是具有32位以上的处理器,具有比较高的性能,价格也较高。

与计算机CPU不同的是,在实际嵌入式应用中,只保留和嵌入式应用紧密相关的功能硬件,去除其它的冗余功能部分,因此其体积小、重量轻、功耗低、成本低及可靠性高。

通常嵌入式微处理器把CPU、ROM、RAM及I/O等元件做到同一个芯片上,也称为单板计算机。

目前,主要的嵌入式微处理器有ARM、MIPS、POWER PC和基于X86的386EX等。

特点:嵌入式微处理器与通用CPU最大的不同在于嵌入式微处理器大多工作在为特定用户群所专用设计的系统中,它将通用CPU许多由板卡完成的任务集成在芯片内部,从而有利于嵌入式系统在设计时趋于小型化,同时还具有很高的效率和可靠性。

嵌入式微处理器的体系结构可以采用冯·诺依曼体系或哈佛体系结构;指令系统可以选用精简指令系统(Reduced Instruction Set Computer,RISC)和复杂指令系统CISC(Complex Instruction Set Computer,CISC)。

Xscale架构

1

整体框架图

系统休 眠键 复位键

实时时钟 (DS1339) RS232通讯接口

电源及状态 指示灯

PXA255

电源及 电源管理

TFT-LCD 接口

8 背光亮度 调节

数字电位器

32

Flash存储器 SDRAM存储器

32

数据总线

USB主端控 制器 (SL811HS)

触摸屏控制 器 (ADS7843E)

32

7

XScale

Intel Xscale基于 基于ARMv5TE体系 基于 体系 支持Thumb指令 指令 支持 支持DSP扩充 扩充 支持

8

XScale处理器 处理器---- PXA270系列 处理器 系列

PXA270系列最高钟频高达 系列最高钟频高达624MHz!而且,它 系列最高钟频高达 !而且, 还能够同时处理多个无线宽频模式。 还能够同时处理多个无线宽频模式。 PXA270内置的无线 内置的无线MMX技术,可以显著提升 技术, 内置的无线 技术 多媒体性能。 多媒体性能。 PXA270还包含了 还包含了SpeedStep技术。该技术可根 技术。 还包含了 技术 据需要动态调节CPU的性能,从而有效的节约 的性能, 据需要动态调节 的性能 电力!装载了 播放MP3的时间 电力!装载了PXA270的PDA播放 的 播放 的时间 可以延长42%,播放QVGA的视频时间可以延 ,播放 可以延长 的视频时间可以延 长77%!

以太网控制 器 (CS8900A)

四线电阻 触摸屏

2

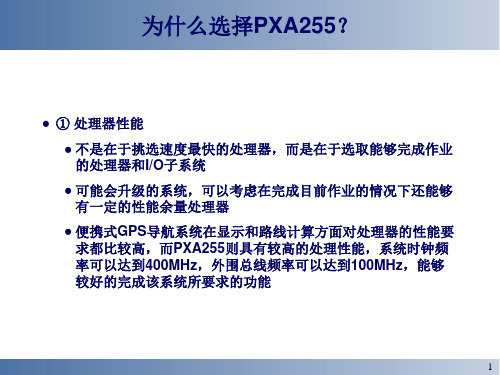

② 集成外围接口 内部有集成的LCD控制器,可以直接支持 位颜色的 控制器, 位颜色的TFT-LCD显示屏 内部有集成的 控制器 可以直接支持16位颜色的 显示屏 有多个UART通讯口,可以方便的扩出与 通讯口,可以方便的扩出与GPS模块通讯的 模块通讯的RS232通讯口 有多个 通讯口 模块通讯的 通讯口 使系统的设计变得相对简单 ③ 功耗 当工作在400MHz时钟频率运行模式下,PXA255的功耗的典型值仅为 时钟频率运行模式下, 的功耗的典型值仅为411mW 当工作在 时钟频率运行模式下 的功耗的典型值仅为 如果降低工作频率, 如果降低工作频率,处理器的功耗会变得更低 PXA255还提供了加速模式、运行模式、待机模式和睡眠模式这四种工作模式 还提供了加速模式、 还提供了加速模式 运行模式、 ,可以方便的进行电源管理 在相应的开发板上做前期的试验评估, 在相应的开发板上做前期的试验评估,确保在软硬件方面都能够满足设计的要求

第1章 嵌入式系统概述1

1.4.5 ARM10E处理器系列

ARM10E系列处理器采用了新的节能模式, 提供了64位的Load/Store体系,支持包括向量 操作的满足IEEE 754的浮点运算协处理器,系 统集成更加方便,拥有完整的硬件和软件开发 工具。ARM10E系列包括ARM1020E、ARM1022E 和ARM1026EJ-S三种类型。

1.嵌入式系统硬件平台

嵌入式系统硬件平台是整个嵌入式操作系 统和应用程序运行的硬件平台,不同的应用通 常有不同的硬件环境。在嵌入式系统中硬件平 台具有多样性的特点。

(1)嵌入式RISC微处理器 (2)嵌入式CISC微处理器

表1-1

RISC和CISC之间主要的区别

RISC 一个周期执行一条指令,通 过简单指令的组合实现复杂 操作;指令长度固定 流水线每周期前进一步 更多通用寄存器 独立的Load和Store指令完成 数据在寄存器和外部存储器 之间的传输 CISC 指令长度不固定,执行需要多 个周期 指令的执行需要调用微代码的 一个微程序 用于特定目的的专用寄存器 处理器能够直接处理存储器中 的数据

Cortex-M3改进了代码密度,减少了中断 延时并有更低的功耗。Cortex-M3中实现了最 新的Thumb-2指令集。MPCore提供了Cache的 一致性,每个支持1~4个ARM11核,这种设计 为现代消费类产品对性能和功耗的需求进行了 很好的平衡。

1.4.10 各种处理器系列之间的比较

表1-3 ARM系列处理器属性比较

ARM9/9E系列

向量浮点运算(Vector Floating Point)系列

ARM系列

ARM10E系列

包含类型

ARM1020E ARM1022E ARM1026EJ-S

ARM11系列

嵌入式系统开发与应用

嵌入式系统的例子

n 汽车:其中的电子系统控制

n 机床:动作控制

n 手机生产线:贴片控制,位置控制

n 洗衣机:回旋,温度, 水流控制

n 数码照相机:读写数据卡 n 打印机:打印强度,颜色,翻页 n 飞机:参数控制 n 。。。

1997年来自美国嵌入式系统大会(Embedded System Conference)的报告指出,未来5年仅基于嵌 入式计算机系统的全数字电视产品,就将在美国产 生一个每年1500亿美元的新市场。 美国汽车大王福特公司的高级经理也曾宣称, “福特出售的‘计算能力’已超过了IBM”,由此 可以想见嵌入式计算机工业的规模和广度。

D、 PowerPC

MPC821

MIPS系列

MIPS (Microprocessor without Interlocked Pipeline Stages) 技术公司是一家设计制造高性能、 高档次及嵌入式32位和64位处理器的厂商。1986 年推出R2000处理器,1988年推出R3000处理器, 1991年推出第一款64位商用微处理器R4000。之 后,又陆续推出R8000(1994年)、R10000 (1996年)和R12000(1997年)等型号。1999 年,MIPS公司发布MIPS 32和MIPS 64架构标准。 2000年,MIPS公司发布了针对MIPS 32 4Kc的新 版本以及未来64位MIPS 64 20Kc处理器内核。

X86系列CPU • Intel公司 • AMD公司 • NS公司

Motorola系列处理器 Motorola公司是世界著名的处理器 制造商,其CPU抗干扰能力强,适合工 业控制/军方应用。 主要处理器: 1)MC68000微处理器占有美国军方市 场的70%。代表产品:DRAGONBALL

软核嵌入处理器MicroBlaze

Coe 在 F G 内 实 现 一 个 完 整 的 、 灵 活 裁 剪 、 参 数 化 配 r。 P A 可 可

技 术论 坛

计 算 机 与 黼 络 创 新 生 活

软核嵌入 处理器 MirB ae co lz

刘永健

( 国电子科技 集 团公 司第五 十 四研 究所 石 家庄 00 8 ) 中 501

【 要】 MirBae Xin 软 核 嵌 入 处理 器 , 用 开发 工 具 IE XP 摘 co l 是 l x的 z i 使 S / S和 相 关 I- oe利 用 F G 内的通 用 资 源 , P C r, PA

置 的 处 理 器 。M irB ae是 Xin co lz X x的 3 i 2位 PI C软 核 嵌 入处  ̄S

用 户 自行 设 计 辅 助 处 理器 A U。总 线 采 用 I M oe n e t P B C rCo n c 标 准 的 3 位 P B 4 ,与 C U 同频 ,并 支 持 XS 、 C XC 2 L v6 P L F B、 L 等 高 速 连 接 。通 过 MUT X 和 MAIB E L OX 模 块 , co l e Mi B a 能 r z

LU o g j n I Y n -i a

(h 4 s r stt o E C, h i h agHee 0 08 , hn) T e t Ree c I tue f T S ia un b i 5 0 1 C i 5h a h ni C jz a

Ab t a t M ir B a e i a s f o e e e d d p o e sro l x U sr c n u et ed v lp n osI E/ S a d r lv n sr c : c o lz s o —c r mb d e r c s f i . e s a s h e eo me tt l S XP n ee a t t o Xi n o

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Intel XScale™嵌入式微处理器简介Intel Xscale内核是和ARM® Architecture V5TE结构兼容的微处理器。

Intel® XScale™core内核集成了多种微结构的特点,从而能够完成更过的性能要求。

这样用户可以根据自己的需求进行配置,实现自己特定的功能。

Intel® XScale™的这些微结构很多应用在存储器当中,主要包括:•当数据缓冲从外部存储器获取数据是,仍然能够执行指令;•写缓冲;•写回数据缓冲(Write-back data cache)•缓冲锁定(Cache locking)•可配置的缓冲方式(X Bit, C Bit for Cacheable, B Bit for Bufferable)Intel Xscale内核的上述特点,使它能够有效的处理语音信号,乘法累加操作还可以完成多种语音和多媒体CODEC算法。

特点改进的性能Intel® 超级流水线技术 7-stage integer/8-stage存储器超级流水线内核获得更高的速度和较低的功耗 Intel®动态电压管理 动态电压和频率允许应用系统对性能和功耗进行合理的折衷 Intel® Media处理技术 多累加协处理器同时完成两个16-bit SIMD 乘法(带40-bit累加),有效的媒体处理; 电源管理单元 通过idle、 sleep、和快速wake-up模式,降低功耗 128-entry Branch TargetBuffer 使流水线载有分支支零时仍能够保持正确 32 KB Instruction Cache 保持重要指令,提高系统性能,降低系统功耗 32 KB Data Cache 保持重要数据,提高系统性能,降低系统功耗 2 KB Mini-Data Cache 在频繁改变数据流时,避免"thrashing" of the D-Cache 32-entry 程序存储器管理单元 使能逻辑到物理地址变换、访问允许和I-Cache attributes 32-entry数据存储器管理单元 使能逻辑到物理地址变换、访问允许和D-Cache attributes 4-entry Fill and Pend Buffers 通过允许数据缓冲的non-blocking和"hit-under-miss"操作,提高内和效率。

性能监测单元 完成两个32-bit event counters和一个32-bit cycle counter foranalysis of hit rates, etc. Debug调试单元 采用硬件断点和256-entry跟踪缓冲调试程序 32-bit CoprocessorInterface 在内核和协处理器间提供高性能的接口 64-bit内和存储器总线,同时32-bit输入和32-bit输出 Gives up to 4.8 GBytes/sec. @ 600 MHz bandwidth for internal accesses 8-entry Write Buffer 当数据写入到存储器是,允许内和继续执行。

ARM兼容性1ARM* Version 5 (V5) Architecture在ARM* Version 4版本基础上增加了很多功能,其中包括浮点指令。

Intel® XScale™内核应用ARM* V5的整型指令,但不提供浮点指令的硬件支持。

Intel® XScale™内核提供ARM* V5T Thumb指令集合ARM* V5E DSP扩展。

为了进一步提高多媒体处理能力, Intel® XScale™内核作为Intel® Media Processing技术的第一个应用,还增加了乘法累加功能。

这些新的操作映射到ARM写处理器空间,和StrongARM兼容。

为了能够满足特定硬件的需要,操作系统需要尽心适当的调整。

Intel® XScale™内核的结构框图Figure 1给出了Intel® XScale™内核的结构框图,该内核支持:l 7 stage integer/8 stage memory流水线操作;l 32Kbyte指令缓冲(32 ways, lockable by line);l 一个32Kbyte数据缓冲(32 ways,write-back or write-through);l 一个2Kbyte mini-data cache (two ways);l 一个分支目标缓冲 a branch target buffer (used by the processor core’s branch prediction logic);l 性能管理单元(Performance Monitoring Unit);l 编辑调试接口(debug port with Branch History table and hardware breakpoints);l 电源管理控制器(Power Management Controller)和JTAG此外,内核还有数据、存储器管理单元(MMU)、带有32传输缓冲( 32 Entry Translation look aside Buffers (TLBs))等。

应用处理器特殊的结构设计提供了灵活的高性能::下图给出了Intel® XScale™内核的主要功能框图,下面概略的介绍个功能模块:2Multiply/Accumulate (MAC)MAC单元支持乘法累加操作,改进了几个硬件结构以支持语音代码算法。

包括40-bit累加器和支持16-bit packed data。

Memory ManagementIntel® XScale™内核采用存储器管理单元结构,具体参见ARM* Architecture Reference Manual。

MMU 提供访问保护和虚拟到物理地址的变换。

MMU构架还确定指令和数据cache的分类原则。

由页配置属性决定的划分方法:•区分代码为cacheable还是non-cacheable;•在mini-data cache或data cache中选择;•write-back或write-through数据缓冲;•使能数据写分配原则;•enabling the write buffer to coalesce stores to external memoryPerformance MonitoringIntel® XScale™内核增加了两个性能监测控志气,监测在Intel® XScale™内核的各种事件的发生。

该事件管理器允许软件开发人员测试cache的效率,监测系统平静并降低程序的重叠缓存等问题。

Power ManagementIntel® XScale™内核集成了一个电源和时钟管理单元,能够辅助ASSP控制时钟,管理电源。

DebugIntel® XScale™内核通过两个指令寻址断点寄存器支持软件调试。

一个数据地址断点寄存器,一个数据地址屏蔽断点寄存,一个mini instruction cache和一个跟踪缓冲器。

Intel® XScale™内核通过JTAG口进行调试。

Intel® XScale™ Enhancements(改进)Intel PXA250应用处理器的Intel XScale内核是在Intel StrongARM处理器Intel SA-1100和 IntelSA-1110应用处理器基础上改进的,和Intel SA-1100和 Intel SA-1110应用处理器不同的是Intel PXA2503应用处理器采用Thumb代码压缩技术。

RISC结构有个弱点就是代码密度问题,代码密度描述了需要存储代码(也就是软件)的空间。

RISC芯片通常情况下要比CISC (Complex Instruction Set Computing) 处理器占用更大的存储空间。

Thumb技术改善了这方面的性能,代码比正常的RISC密度降低30%,该压缩由Intel PXA250应用处理器自动完成。

工程师或程序员不需要更多的设计考虑。

另一个改进的主要部分就是Intel Xscale内核拥有双乘法/累加(dual-MAC)指令,MAC操作对于计算机和微处理器是一个比较新的运算模式,是从数字信号处理器(DSP)中移植过来的。

而MAC操作对于语音、视频和无线应用是非常重要经常用到的。

一个或两个MAC指令能够完成这些多媒体的应用,因此大大的提高了微处理器的运算能力。

Intel Xscale PXA250 ArchitectureIntel PXA250微处理器是下一代手持多媒体应用处理器,基于Xscale结构的高性能低功耗微处理器,广泛应用于无线、手持和Internet设备当中。

Intel PXA250内核是一个32-bit的微处理器,但是在他的结构设计中,处理器内核部分仅占了整个芯片的15%。

绝大部分区域是为了提高其性能的集成程度和增强电源管理,降低芯片甚至是系统的功耗。

Intel PXA250内核是一个Intel Xscale内核微处理器。

Intel Xscale本身是一个32-bit的RISC为结构。

采用先进的ARM技术,是目前世界上交流行得32-bit 嵌入式CPU。

在技术上ARM和Intel Xscale两者完全兼容。

因此在采用Intel PXA250应用处理器进行软件开发时,原来为ARM开发的代码完全可以进行移植,或直接在基于Intel Xscale的微处理器上运行。

当然新的开发工具将会更能利用发挥Intel Xscale技术。

如图所示,Intel PXA250应用处理器包括多种外设,能够完成个人客户终端构架的基本功能。

它包括集成的外围存储器控制器、串行总线、并行总线、无线和有线通信接口、扩展卡接口以及LCD显示接口等。

所有这些实现了一个片上系统。

在具体的用户设计时,有时只需要增加一些电池、存储器、通信子系统和LCD显示屏就可以了。

从而简化并降低了软硬件的设计实现难度,降低系统的成本和功耗,加快了产品推向市场4产品概述移动和无线设备方便了我们的生活,使工作小冷高。

几乎每天都依赖这些先进的设备来进行各种活动。

为了能够满足客户随时随地能够进行通信、访问信息。

生产厂商需要采用高性能、灵活方便、稳定性好、功耗比较低的技术来满足不断增长的需求。

采用Intel Xscale技术的Intel Personal Internet Client Architecture (Intel PCA)应用处理器将手持设备提升到了一个新的高度。