实验一 二输入端与非门的设计EPM7128-bdf_百度文库.

12.二输入与非门的VHDL设计

port (a,b:in std_logic;

y:out std_logic);

end nand2;

architecture nand2_2 of nand2 is

begin

t1: process (a,b)

variable comb:std_logic_vector (1 downto 0);

end process t1;

end nand2_2;

4.项目编译

选择目标器件。选择菜单命令Assign | Device,弹出Device对话框。选择对话框的Device Family下拉列表框中的目标器件(EPM7128SLC84-10)引脚指定,编译。

5.项目时序仿真

创建波形文件—输入信号节点—设置仿真时间—编辑输入节点波形-运行仿真

entቤተ መጻሕፍቲ ባይዱty nand2 is

port (a,b:in std_logic;

y:out std_logic);

end nand2;

architecture nand2_1 of nand2 is

begin

y <= a nand b;

end nand2_1;

旁批栏:

方法二:

library ieee;

use ieee.std_logic_1164.all;

8.实验箱上现象的分析描述与验证。

三.小结:

对学生在实验过程中遇到的问题进行分析,总结,做出合理的评价。

四.作业

将程序输入到MAX+PLUS II软件进行相关操作,完成实验报告。

旁批栏:

二.新课

1.VHDL相关语法理论知识讲解

2.设计任务:设计一个二输入与非门,a, b为数据输入端的端口名,y为输出。

与非门组成故障报警电路实验报告

竭诚为您提供优质文档/双击可除与非门组成故障报警电路实验报告篇一:与非门组成故障报警电路实验任务书实验八与非门组成故障报警电路一、实验目的(1)熟悉组合逻辑电路的特点及一般分析方法。

(2)学习与非门组成故障报警电路的功能及测试。

(3)学习反相器、与门、或非门等集成电路的检测。

(4)提高学生动手操作能力。

(5)提高学生检查及排除电路故障的能力。

(6)增强学生的综合设计和分析能力。

二、实验器材虚拟实验设备?操作系统为windowsxp的计算机1台?electronicsworkbenchmultisim8.x~9.x电子线路仿真软件1套?直流电源Vcc1个?逻辑探头7个?逻辑开关3个?逻辑分析仪1个?逻辑转换器1个?电阻(1KΩ,1/4w)3个?六反相器74Ls042个?二输入端四与门74Ls081个?三输入三正或非门74Ls271个实际工程实验设备?数字系统综合实验箱1台?数字万用表1台?六反相器74Ls042个?二输入端四与门74Ls081个?五输入双正或非门74Ls2601个三、实验原理及实验电路用与非门组成故障报警电路在实际应用中非常广泛和适用。

任何一个系统或设备,在使用中不可能不出现故障,而有些故障是破坏性极强的,一经发生故障,有可能使整个系统处于崩溃状态,其损失不可估量。

如果在这些系统或设备中加上本电路,一旦系统或设备出现故障,它不仅可以报警,还能显示出故障的具体位置,并对系统或设备加以保护。

用与非门组成故障报警电路实验电路如图8-1所示。

图8-1中,指示灯D1、D2、D3分别是由A、b、c经过两次反相以后再输出,其状态分别与A、b、c的状态一致,可以通过三个灯的状态来判断故障具体产生的位置。

其中A、b、c我们称为模拟故障输入端。

当输入为高电平时表示无故障(即正常)状态,当输入为低电平时表示故障状态。

从而,我们可以知道,当A、b、c三个输入端至少有一个输入端输入为低电平时,系统即为故障状态。

二输入端与非门设计.ppt

(6) 引入输入和输出脚:按步骤 (5) 选出2个输入脚

和1个输出脚。

第5章

组合逻辑电路设计

(7) 更 改 输 入 和 输 出 脚 的 脚 位 名 称 : 在 PIN_NAME 处双击鼠标左键,进行更名,输入脚为A、 B,输出脚为C。

Edit画面,2输入端与非门的电路符号如图5-2所示。

第5章

组合逻辑电路设计

(14) 创建电路包含文件:选取窗口菜单 File→Create Default Include File,产生用来代表目前所 设计电路的nand2.inc文件,供其他VHDL编译时使用, 如图5-3所示。 (15) 时间分析:选取窗口菜单Utilities→Analyze

(2) 保存:选取窗口菜单 File→Save ,出现对话框,

键入文件名nand2.gdf,单击OK按钮。

第5章

组合逻辑电路设计

(3) 指定项目名称,要求与文件名相同:选取窗口

菜单File→Project→Name,键入文件名nand2,单击OK 按钮。

(4) 确定对象的输入位置:在图形窗口内单击鼠标

电路的nand2 .inc文件,供其他VHDL编译时使用。 (11) 时间分析:选取窗口菜单Utilities→Analyze

第5章

组合逻辑电路设计

(6) 保存并查错:选取窗口菜单

File→Project→Save&Check,即可针对电路文件进行检查。 (7) 修改错误:针对Massage-Compiler窗口所提供的 信息修改电路文件,直到没有错误为止。 (8) 保存并编译:选取窗口菜单 File→Project→Save&Compile,即可进行编译,产生 nand2.sof烧写文件。

二输入与非门、或非门版图设计

课程名称Course 集成电路设计技术项目名称Item二输入与非门、或非门版图设计与非门电路的版图:.spc文件(瞬时分析):* Circuit Extracted by Tanner Research's L-Edit V7.12 / Extract V4.00 ;* TDB File: E:\cmos\yufeimen, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\morbn20.ext * Extract Date and Time: 05/25/2011 - 10:03.include H:\ml2_125.mdVPower VDD GND 5va A GND PULSE (0 5 0 5n 5n 100n 200n)vb B GND PULSE (0 5 0 5n 5n 50n 100n).tran 1n 400n.print tran v(A) v(B) v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Pad Comment>* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (34,37)* 2 = A (29.5,6.5)* 3 = B (55.5,6.5)* 4 = F (42.5,6.5)* 6 = GND (25,-22)M1 VDD B F VDD PMOS L=2u W=9u AD=99p PD=58u AS=54p PS=30u* M1 DRAIN GATE SOURCE BULK (47.5 14.5 49.5 23.5)M2 F A VDD VDD PMOS L=2u W=9u AD=54p PD=30u AS=99p PS=58u* M2 DRAIN GATE SOURCE BULK (39.5 14.5 41.5 23.5)M3 F B 5 GND NMOS L=2u W=9.5u AD=52.25p PD=30u AS=57p PS=31u * M3 DRAIN GATE SOURCE BULK (47.5 -18 49.5 -8.5)M4 5 A GND GND NMOS L=2u W=9.5u AD=57p PD=31u AS=52.25p PS=30u * M4 DRAIN GATE SOURCE BULK (39.5 -18 41.5 -8.5)* Total Nodes: 6* Total Elements: 4* Extract Elapsed Time: 0 seconds.END与非门电路仿真波形图(瞬时分析):.spc文件(直流分析):* Circuit Extracted by Tanner Research's L-Edit V7.12 / Extract V4.00 ;* TDB File: E:\cmos\yufeimen, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\morbn20.ext * Extract Date and Time: 05/25/2011 - 10:03.include H:\ml2_125.mdVPower VDD GND 5va A GND 5vb B GND 5.dc va 0 5 0.02 vb 0 5 0.02.print dc v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Pad Comment>* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (34,37)* 2 = A (29.5,6.5)* 3 = B (55.5,6.5)* 4 = F (42.5,6.5)* 6 = GND (25,-22)M1 VDD B F VDD PMOS L=2u W=9u AD=99p PD=58u AS=54p PS=30u* M1 DRAIN GATE SOURCE BULK (47.5 14.5 49.5 23.5)M2 F A VDD VDD PMOS L=2u W=9u AD=54p PD=30u AS=99p PS=58u* M2 DRAIN GATE SOURCE BULK (39.5 14.5 41.5 23.5)M3 F B 5 GND NMOS L=2u W=9.5u AD=52.25p PD=30u AS=57p PS=31u * M3 DRAIN GATE SOURCE BULK (47.5 -18 49.5 -8.5)M4 5 A GND GND NMOS L=2u W=9.5u AD=57p PD=31u AS=52.25p PS=30u * M4 DRAIN GATE SOURCE BULK (39.5 -18 41.5 -8.5)* Total Nodes: 6* Total Elements: 4* Extract Elapsed Time: 0 seconds.END与非门电路仿真波形图(直流分析):或非门电路的版图:.spc文件(瞬时分析):* Circuit Extracted by Tanner Research's L-Edit V7.12 / Extract V4.00 ;* TDB File: E:\cmos\huofeimen, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\morbn20.ext * Extract Date and Time: 05/25/2011 - 10:04.include H:\CMOS\ml2_125.mdVPower VDD GND 5va A GND PULSE (0 5 0 5n 5n 100n 200n)vb B GND PULSE (0 5 0 5n 5n 50n 100n).tran 1n 400n.print tran v(A) v(B) v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <Pad Comment>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (34,37)* 2 = A (29.5,6.5)* 3 = B (55.5,6)* 4 = F (42.5,6.5)* 5 = GND (25,-22)M1 6 A VDD VDD PMOS L=2u W=9u AD=54p PD=30u AS=49.5p PS=29u* M1 DRAIN GATE SOURCE BULK (39.5 14.5 41.5 23.5)M2 F B 6 VDD PMOS L=2u W=9u AD=49.5p PD=29u AS=54p PS=30u* M2 DRAIN GATE SOURCE BULK (47.5 14.5 49.5 23.5)M3 F A GND GND NMOS L=2u W=9.5u AD=57p PD=31u AS=104.5p PS=60u * M3 DRAIN GATE SOURCE BULK (39.5 -18 41.5 -8.5)M4 GND B F GND NMOS L=2u W=9.5u AD=104.5p PD=60u AS=57p PS=31u * M4 DRAIN GATE SOURCE BULK (47.5 -18 49.5 -8.5)* Total Nodes: 6* Total Elements: 4* Extract Elapsed Time: 0 seconds.END或非门电路仿真波形图(瞬时分析):.spc文件(直流分析):* Circuit Extracted by Tanner Research's L-Edit V7.12 / Extract V4.00 ;* TDB File: E:\cmos\huofeimen, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\morbn20.ext * Extract Date and Time: 05/25/2011 - 10:04.include H:\CMOS\ml2_125.mdVPower VDD GND 5va A GND 5vb B GND 5.dc va 0 5 0.02 vb 0 5 0.02.print dc v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <Pad Comment>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (34,37)* 2 = A (29.5,6.5)* 3 = B (55.5,6)* 4 = F (42.5,6.5)* 5 = GND (25,-22)M1 6 A VDD VDD PMOS L=2u W=9u AD=54p PD=30u AS=49.5p PS=29u* M1 DRAIN GATE SOURCE BULK (39.5 14.5 41.5 23.5)M2 F B 6 VDD PMOS L=2u W=9u AD=49.5p PD=29u AS=54p PS=30u* M2 DRAIN GATE SOURCE BULK (47.5 14.5 49.5 23.5)M3 F A GND GND NMOS L=2u W=9.5u AD=57p PD=31u AS=104.5p PS=60u * M3 DRAIN GATE SOURCE BULK (39.5 -18 41.5 -8.5)M4 GND B F GND NMOS L=2u W=9.5u AD=104.5p PD=60u AS=57p PS=31u * M4 DRAIN GATE SOURCE BULK (47.5 -18 49.5 -8.5)* Total Nodes: 6* Total Elements: 4* Extract Elapsed Time: 0 seconds.END或非门电路仿真波形图(直流分析):内容(方法、步骤、要求或考核标准及所需工具、设备等)一、实训设备与工具1.PVI计算机一台;2.Tanner Pro集成电路设计软件二、实训方法、步骤与要求1.二输入与非门电路的线路结构2.二输入或非门电路的线路结构3.CMOS倒相器电路的版图4.根据与非门、或非门线路结构,在一个工程中,重新新建两个新CELL,分别对应与非门和或非门版图,并设计与非门、或非版图结构。

实验七反相器,二输入与非门以及二输入或非门版图设计

实验七反相器,⼆输⼊与⾮门以及⼆输⼊或⾮门版图设计学号姓名

实验七1.反相器

反相器EECMOS的schematic图如下所⽰

其中PMOS管L=180nm W=720nm NMOS管L=180nm W=240nm

根据schematic画出的layout图如下所⽰

其中该版图长:2.16um 宽:4.87um

则版图⾯积为S=L*W=2.16*4.87=10.5192(um^2)

经过多此修改后,DRC验证如下

LVS验证如下

2.⼆输⼊与⾮门

⼆输⼊与⾮门nand2的schematic图如下所⽰

其中两个PMOS管的L=180nm W=720nm 两个NMOS管的L=180nm W=720nm 根据schematic图画出的layout版图如下所⽰

其中nand2版图的长:2.76um 宽:5.14um

则版图的⾯积S=L*W=2.76*5.14=14.1864(um^2)

通过改错后,DRC验证结果如下

LVS验证结果如下

3.⼆输⼊或⾮门

⼆输⼊或⾮门nor的schematic图如下所⽰

其中两个PMOS管的L=180nm W=2.51um 两个NMOS管的L=180nm W=500nm

由schematic图画出的layout版图如下所⽰

由于PMOS管的宽度较⼤,为了提⾼能通过的峰值电流,不浪费diff的⾯积,最⼤限度打满了源漏孔

其中该版图的长:2.91um 宽6.65um

则版图⾯积S=L*W=2.91*6.65=19.3531(um^2)

通过改错,DRC验证结果如下

LVS验证结果如下。

小论文数字设计方案模拟一个两输入的异或门数字逻辑设计方案与应用

小论文

一、题目

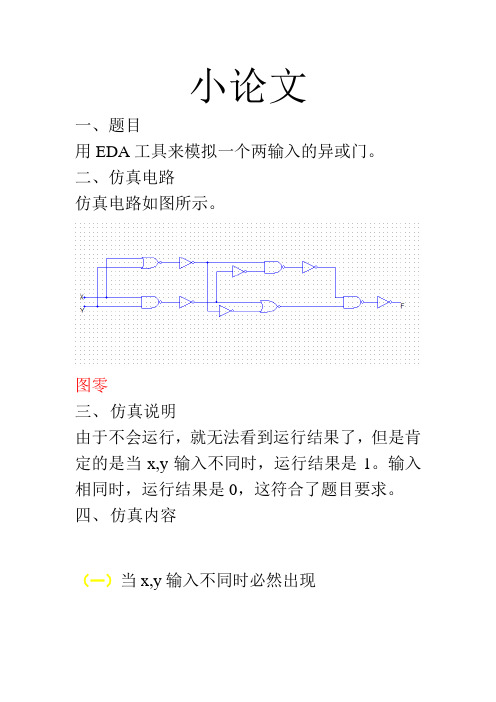

用EDA工具来模拟一个两输入的异或门。

二、仿真电路

仿真电路如图所示。

图零

三、仿真说明

由于不会运行,就无法看到运行结果了,但是肯定的是当x,y输入不同时,运行结果是1。

输入相同时,运行结果是0,这符合了题目要求。

四、仿真内容

(一)当x,y输入不同时必然出现

图一

上面或门(或非-非门)输出1,下面与门(与非-非门)输出0

(二)而1和0接着往下输入

图二

1往右输入仍然是1。

往下输入经过一个非门,变成0。

0往右输入仍然是0,。

往上输入经过一个非门,变成1。

这样,上面的两输入都是1。

下面两输入都是0。

(三)再继续往下一级

图三

两个1经过一个与门(与非-非门)结果只能是1。

两个0经过一个或非门结果只能是1。

(四)两个1再接着下一级

图四

两个1经过一个与门(与非-非门)结果只能是1。

由于以上每步的结果都是唯一的,所以只有当最开始输入的x,y不同时,最后结果就会是1。

而且,可从最后一步倒着推回去会发

现,在步骤(一)也就是图一中往下一级输入的不是上面是1,下面是0,而是另外两种情况:两个1;两个0。

这样往后推到最

(这是x,y输入相同时,后一步的结果就是0。

输出为0的推导)得出结果:输入相同时,最后结果就会是0。

五、仿真结果

输入x,y不同时,结果是1。

输入x,y相同时,结果是0。

六、仿真结论

这个仿真电路符合题目中的要求,是可行的。

与非门的版图设计实验报告参考模板

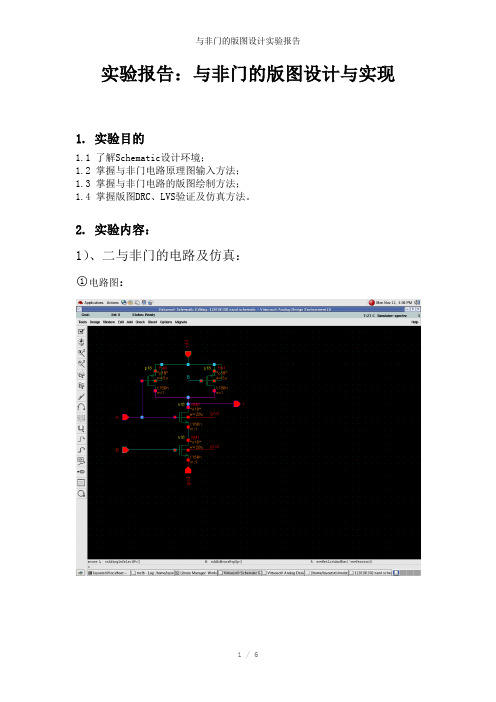

实验报告:与非门的版图设计与实现1. 实验目的1.1 了解Schematic设计环境;1.2 掌握与非门电路原理图输入方法;1.3 掌握与非门电路的版图绘制方法;1.4 掌握版图DRC、LVS验证及仿真方法。

2. 实验内容:1)、二与非门的电路及仿真:○1电路图:○2激励信号(以表格的形式给出)Function DCvoltage/V Voltage1/VVoltage2/VPeriod/SPulsewidth/SVdd dc 1.8 \ \ \ \ gnd dc 0 \ \ \ \A pulse \ 1.8 0 400n 200nB pulse \ 1.8 0 400n 200n ○3电路图的仿真结果。

2)、二与非门的版图及仿真:○1版图(写出版图的面积)版图面积大约为:15*14=210 um2○2版图的后仿提取网表○3激励信号(以表格的形式给出)Function DCvoltage/V Voltage1/VVoltage2/VPeriod/SPulsewidth/SVdd dc 1.8 \ \ \ \ gnd dc 0 \ \ \ \A pulse \ 1.8 0 400n 200nB pulse \ 1.8 0 400n 200n○4版图的仿真结果。

3、收获与感悟:通过这次与非门的实验,我更加熟练地学会了layout的过程,已经能够独立完成电路图、版图的制作和电路的仿真、寄生参数提取、电路后仿真。

这次实验完成后,我在做整个比较器设计的时候,我再次对这次设计的与非门进行了一些修改,主要是优化了面积,改善了输入输出端的位置,使我能在布局比较器的时候更方便。

可见我第一次设计出来的版图还是有很多地方欠考虑的,特别的面积没有做最好的优化,我在后面的实验中做了一些完善,最后还是完成了面积比较理想的完整的比较器。

友情提示:范文可能无法思考和涵盖全面,供参考!最好找专业人士起草或审核后使用,感谢您的下载!。

集成电路-二输入异或门的前仿设计

集成电路课程设计——二输入异或门的前仿设计姓名:胡国勤学号:07063211专业:电子科学与技术指导老师:蔡志民二〇一〇年十二月二十五日二输入异或门的前仿设计一、实验目的1、了解异或门的逻辑单元。

2、二输入异或门电路原理图输入方法。

3、二输入异或门的前仿设计。

二、实验原理1、异或门逻辑单元异或门逻辑功能:F=A⊕B 。

异或门逻辑符号如图1所示:图1 异或门逻辑符号异或门真值表如表一所示:表一异或门真值表A B F0 0 00 1 11 0 11 1 02、异或门功能实现当输入A与B不同时,输出F为1;当输入A与B相同时,输出F为0。

三、实验内容1、建立库文件点击运行程序,弹出运行程序窗口如图2所示。

图2 运行程序然后在运行程序窗口键入icfb后点击运行就会出现CIW(Command Interpreter Window),即命令解释窗如图3所示。

图3 CIW窗口CIW窗口是Cadence软件的控制窗口,是主要的用户界面。

从CIW窗口可以调用许多工具并完成许多任务。

CIW窗口主要包括以下几个部分:①Window Title(窗口标题栏):显示使用软件的名称及Log文件目录。

②Menu Banner(菜单栏):显示命令菜单以便使用设计工具。

③Outbut Area(输出区):显示电路图设计软件时的信息,可以调整CIW 使这个区域显示更多信息。

④Input Line(输入行):原来输入命令。

⑤Mouse Bindings Line :显示捆绑在鼠标左中右3键的快捷键。

⑥Prompt Line :标识号来自当前命令的信息。

2、创建库与视图单元点击CIW窗口的File-new-library,由此可创建库,用来存放单元视图的文件夹。

将库文件的路径设置在cadence目录下,Name栏输入库文件名001(库文件名可定义),右侧Technology File栏中选择Don’t need a techfile,由于现在只是输入原理图,因此可以不需要工艺文件,点击窗口OK,如图4所示。

二输入端与非门设计

第5章 组合逻辑电路设计

(7) 更 改 输 入 和 输 出 脚 的 脚 位 名 称 : 在 PIN_NAME处双击鼠标左键,进行更名,输入脚为A、 B,输出脚为C。

(8) 连接:将A、B脚连接到与非门的输入端,C 脚连接到与非门的输出端,如图5-1所示。

第5章 组合逻辑电路设计

表5-1 2输入端与非门的真值表

输入端

A

B

0

0

0

1

1

0

1

1

输出端 C 1 1 1 0

第5章 组合逻辑电路设计

2.原理图输入 与非门原理图输入法的操作步骤介绍如下。 (1) 建立新文件:选取窗口菜单File→New,出现对 话框,选择Graphic Editor file选项,单击OK按钮,进 入图形编辑画面。 (2) 保存:选取窗口菜单File→Save,出现对话框, 键入文件名nand2.gdf,单击OK按钮。

第5章 组合逻辑电路设计

基本门电路的设计

第5章 组合逻辑电路设计

基本门电路的设计

基本门电路主要用来实现基本的输入/输出之间的 逻辑关系,包括与门、非门、或门、与非门、或非门、 异或门、同或门等,下面以2输入端与非门为例讲解基 本门电路的设计。

第5章 组合逻辑电路设计

1.实验原理 表5-1 2输入端与非门的真值表 2输入端与非门是组合逻辑电路中的基本逻辑器件, 有2个输入端A、B和1个输出端C。其真值表如表5-1所 示。2输入端与非门应具备的脚位: 输入端:A、B; 输出端:C。

第5章 组合逻辑电路设计

(6) 保存并查错:选取窗口菜单 File→Project→Save&Check,即可针对电路文件进行检查。

二输入端与非门设计

二输入端与非门设计

二输入端与非门是一种基本的逻辑门电路,用于将输入的逻辑信号进行反转。

它由两个输入端和一个输出端组成,当两个输入信号中的任意一个为高电平时,输出信号为低电平;只有当两个输入信号都为低电平时,输出信号才会为高电平。

1.原理

在二输入端与非门中,当输入信号的两个输入端之一或者同时为高电平时,输入电阻将会导通,将电流流向负载电阻,并将输出线上的电压拉低,表示低电平。

当输入信号两个输入端都为低电平时,两个输入电阻都截止,负载电阻上没有电流流过,输出线上的电压被拉高,表示高电平。

2.设计

首先,选择一个适合的晶体管,常用的有NPN型和PNP型晶体管。

在这里,我们选择一个NPN型晶体管。

接下来,连接两个输入端。

一个输入端通过电阻接到电源电压(Vcc),另一个输入端通过电阻接到地线,同时这两个输入端也与晶体管的基极连接。

然后,将晶体管的发射极接地,集电极与输出端相连接。

负载电阻连接在输出端到电源电压(Vcc)之间。

最后,根据需要添加外部电路。

例如,可以添加降噪电路、电流限制电路等。

3.工作原理

当输入信号的两个输入端之一或者同时为高电平时,输入电阻导通,晶体管的基极-发射极之间的电压使得晶体管导通,导通时的饱和电压使得输出端电压拉低,表示低电平。

当输入信号的两个输入端都为低电平时,两个输入电阻截止,晶体管的基极-发射极之间的电压使得晶体管截止,输出端上的电压由于负载电阻拉高,表示高电平。

总结:。

CMOS二输入与非门设计

MOS 管集成电路设计》期中论文CMOS 二输入与非门设计日期:2015 年 5 月21 日目录一电路设计1.1与非门基础 (3)1.2 CMOS二输入与非门 (4)二版图设计2.1 LASI7软件介绍 (5)2.2版图设计过程 (5)三规则检查 (8)四LTspice 仿真 (10)4.1电路仿真分析软件简介 (10)4.2 LTspice仿真过程 (11)五总结 (15)六参考文献 (15)摘要MOS(Metal-Oxide-Semiconductor )晶体管是一种金属- 氧化物半导体硅场效应管,分为PMO管和NMO管两种,由NMO和PMOS共同构成的电路即为CMO电路。

和传统的TTL电路相比,MOS H成电路具有功耗较低,速度较快,输入阻抗高,热稳定性好等优点,因而在目前有着广泛的应有,可以预见的是,MOS集成电路代替TTL电路已是大势所趋。

与非门是一种数字电路的基本逻辑电路,可以看做是与门与非门的结合,若当输入均为高电平(1),则输出为低电平(0);若输入中至少有一个为低电平(0),则输出为高电平(1),在数字电路中有着非常重要的作用。

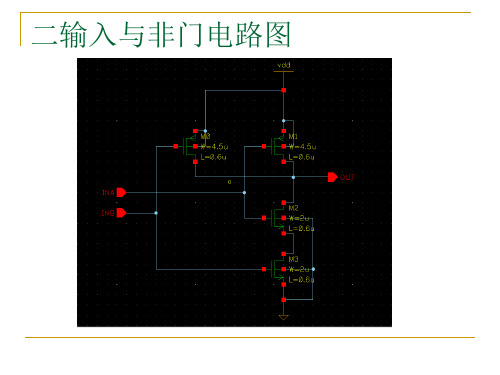

本设计旨在采用CMO设计一个二输入的与非门,根据需要,它由两个PMO(M3和M4和两个NMO(M1和M2构成。

其中,两个PMO作为上拉管,两个NMO作为下拉管,两个输入信号A和B分别加在两对互补的NMO管和PMO管的栅极上,输出从他们的漏极引出。

设计完之后,用LASI7 软件画出版图并进行规则检查。

关键词:CMO、S 与非门、逻辑电路、LASI7一电路设计1.1与非门基础与非门是数字电路中一种重要的逻辑电路,本设计设计的是二输入与非门,它有两个输入端和一个输出端,当输入均为高电平,输出为低电平;若输入中至少有一个为低电平,贝揃出为高电平,其逻辑符号如图1所示图1二输入与非门逻辑符号由于有两个输入,所以真值表中它的组合共有4种形式,如表1所示表1二输入与非门真值表1.2 CMOS二输入与非门二输入与非门的下拉管由串联的NMOST M1和M2组成,上拉管则由并联的PMO管的M3和M4构成。

二输入与非门电路图

题目

1.在集成电路制造工艺中,电隔离的方法 有 、 和 。 2.分立双极管是三层二结结构,而集成双极晶 体管为 结构,集成NPN管中有个寄生 的 管。

本次课主要内容

2.3集成双极晶体管的无源寄生效应 2.4集成电路中的PNP管 2.5集成二极管 2.6SBD和SCT

2.3集成双极晶体管的无源寄生效应

S rs

CjD SBD

M

V I I DS [ EXP( 1)] Vt

I DS R ST EXP( B / Vt)

* 2

SCT

C

Vsm Id和rs的设计

B

SBD的结构和击 穿电压

E

C

E

B

本次课小结

集成双极晶体管的无源寄生效应

横向PNP管 缺点 横向PNP管 原因 解决方法

多集电极横向PNP管 优点 缺点

2.3.1集成NPN晶体管中的寄生电阻

C N+ B E

P+ rc1

rb

res

N+

P

N-epi

P+

rc3 N+-BL

rc2 P-SUB

图2.3-1标有无源电阻寄生元件的集成NPN晶体管结构图

发射极串联电阻res 集电极串联电阻rcs 基区电阻rb

寄生电阻的计算方法

发射极串联电阻res:见黑板 集电极串联电阻rcs 基区电阻rb

25集成二极管一般集成二极管集成齐纳二极管次表面齐纳管26肖特基势垒二极管sbd和肖特基箝位晶体管sctsct本次课小结集成双极晶体管的无源寄生效应pnp管集成二极管齐纳管sbd和sct结构特点和设计注意点vbc反vbe反vbc正vbe反vbc反vbe正vbc正vbe正截止区反向工作区正向工作区饱和区npn截止区正向工作区截止区正向工作区vbc反vbe反vbc反vbe正vbc反vbe反vbc反vbe正pnp22寄生管对晶体管的影响cbenblnnpnepipppsubrc1rc2rc3rbres发射极串联电阻res集电极串联电阻rcs基区电阻rb231集成npn晶体管中的寄生电阻lwblawt20141012101010101012101420101010例题p4822解题过程见黑板berb3rb2rb1cbenblnnpnepipppsub232集成npn晶体管中的寄生电容cjecjscjc24集成电路中的pnp管nblnppppcbesnepipxjc深epi高wbl限制寄生效应nblnppppcbesnepipsub横向npn管工作在正向工作区正偏反偏正偏反偏反偏反偏正向工作区截止cjsnblnppppcbesnepip横向平均基区宽度不可能做太小发射极的注入效率低表面复合影响大基区渡越时间长ft下降增加结深xjc减小le改变掺杂浓度降低有效平均基区宽度复合管pnpnpnft无变化复合管面积大于pnp管cbe无埋层无寄生pnp管ft大于横向npn管小于npn管psub集电极接最负电位sbdcbevsmid和rs的设计sbd的结构和击穿电压

二输入与门的设计

QuartusII实例演示(二输入与门的设计)一、实验目的1.初步掌握QuartusII软件;2.熟悉掌握FPGA的开发流程;3.初步掌握数字实验系统;二、QuartusII软件的具体设计步骤1.建立文件夹在实验室上机时,要求在D盘建立一个自己姓名拼音的文件夹,每次实验内容都在此文件夹下再建立一个文件夹,在这个二级文件夹里存放相应项目、程序文件、仿真波形文件等。

2.建立新工程(1)双击桌面上Quartus II6.0的图标,启动Quartus II6.0软件。

(2)通过 File => New Project Wizard…菜单命令启动新项目向导。

(3)在随后弹出的对话框上点击 Next 按钮,继续。

(4)在 What is the working directory for this project 栏目中设定新项目所使用的路径;在 What is the name of this project 栏目中输入新项目的名字: vote ,点击 Next 按钮。

(5)在这一步,向导要求向新项目中加入已存在的设计文件。

因为我们的设计文件还没有建立,所以点击 Next 按钮,跳过这一步。

(6)为本项目指定目标器件。

(7)在这一步,可以为新项目指定综合工具、仿真工具、时间分析工具。

在这个实验中,我使用 Quartus II6.0 的默认设置,直接点击 Next 按钮,继续。

(8)确认相关设置,点击 Finish 按钮,完成新项目创建。

3.设计输入(1)我们建立一个VHDL文件。

通过 File => New 菜单命令,在随后弹出的对话框中选择 VHDL File选项,点击 OK 按钮。

通过 File => Save As 命令,将其保存,并加入到项目中。

(2)在VHDL界面输入两输入与门程序,然后通过 File => Save As 命令保存。

4.综合和编译(1)选择Processing =>Start Compilation,检查程序语法错误,并生成RTL图。

TEC-8数字逻辑实验

实验五 在系统编程实验1

计算机学院实验中心系统结构实验室

实验四 简单时序电路

实验内容:

1.双D构成的二进制计数器:按设计接线 ,将Q0,Q1,Q2,Q3复位;由时钟端CLK 输入单脉冲,记录输出状态;由时钟端 CLK输入连续脉冲,观测输出波形。 2.用74LS73构成一个二进制计数器,重做 内容1的实验。

计算机学院实验中心系统结构实验室

计算机学院实验中心系统结Leabharlann 实验室实验四 简单时序电路

实验提示: 74LS73引脚11是GND,引脚4是VCC。 D触发器74LS74是上升沿触发,JK触发器 74LS73是下降沿触发。

计算机学院实验中心系统结构实验室

实验四 简单时序电路

D触发器构成的二进制计数器实验电路:

计算机学院实验中心系统结构实验室

计算机学院实验中心系统结构实验室

实验四 简单时序电路

异步十进制计数器输出波形:

计算机学院实验中心系统结构实验室

实验四 简单时序电路

自循环计数器实验电路:

计算机学院实验中心系统结构实验室

实验四 简单时序电路

自循环计数器输出波形:

计算机学院实验中心系统结构实验室

实验四 简单时序电路

实验报告要求: 1.写出实验内容1中,用单次脉冲做计数脉 冲时,Q3,Q2,Q1,Q0的状态转移表; 画出连续时钟下Q3,Q2,Q1,Q0的波形 ; 2./Q3,/Q2,/Q1,/Q0构成计数器吗?如 果是,那么是递增还是递减?

计算机学院实验中心系统结构实验室

实验三 触发器

(2)在(1)的基础上,置CLR, PR引脚为 高电平,D(数据)引脚接电平开关输出, CP(时钟)引脚接单脉冲。在D为高电平和低 电平的情况下,分别按单脉冲按钮,观察 Q,Q′的值,记录下来。

CMOS二输入与非门设计

《MOS管集成电路设计》期中论文CMOS二输入与非门设计日期:2015年5月21日一电路设计1.1 与非门基础 (3)1.2 CMOS二输入与非门 (4)二版图设计2.1 LASI7软件介绍 (5)2.2 版图设计过程 (5)三规则检查 (8)四 LTspice仿真 (10)4.1电路仿真分析软件简介 (10)4.2 LTspice仿真过程 (11)五总结 (15)六参考文献 (15)MOS(Metal-Oxide-Semiconductor)晶体管是一种金属-氧化物半导体硅场效应管,分为PMOS管和NMOS管两种,由NMOS和PMOS共同构成的电路即为CMOS电路。

和传统的TTL电路相比,MOS集成电路具有功耗较低,速度较快,输入阻抗高,热稳定性好等优点,因而在目前有着广泛的应有,可以预见的是,MOS集成电路代替TTL电路已是大势所趋。

与非门是一种数字电路的基本逻辑电路,可以看做是与门与非门的结合,若当输入均为高电平(1),则输出为低电平(0);若输入中至少有一个为低电平(0),则输出为高电平(1),在数字电路中有着非常重要的作用。

本设计旨在采用CMOS设计一个二输入的与非门,根据需要,它由两个PMOS(M3和M4)和两个NMOS(M1和M2)构成。

其中,两个PMOS作为上拉管,两个NMOS作为下拉管,两个输入信号A和B分别加在两对互补的NMOS管和PMOS管的栅极上,输出从他们的漏极引出。

设计完之后,用LASI7软件画出版图并进行规则检查。

关键词:CMOS、与非门、逻辑电路、LASI7一电路设计1.1 与非门基础与非门是数字电路中一种重要的逻辑电路,本设计设计的是二输入与非门,它有两个输入端和一个输出端,当输入均为高电平,输出为低电平;若输入中至少有一个为低电平,则输出为高电平,其逻辑符号如图1所示图1 二输入与非门逻辑符号由于有两个输入,所以真值表中它的组合共有4种形式,如表1所示1.2 CMOS二输入与非门二输入与非门的下拉管由串联的NMOS管M1和M2组成,上拉管则由并联的PMOS管的M3和M4构成。

CMOS两输入与非门

数字集成电路设计

实验报告

院系名称

专业班级

学号

学生姓名

指导老师

时间

一、实验目的

通过实验了解CMOS反相器的工作原理,能自己用CMOS和PMOS 连接电路组合成2输入与非门。

实验求得直流特性曲线分析和瞬态分析。

二、实验内容

1、用软件求出输入输出电压曲线

2、通过设置不同的参数求得瞬态分析。

三、实验原理

四、实验步骤

.include "D:\Tanner\tanner\TSpice70\models\ml2_125.md" .dc lin source v5 0 5 0.1

.dc lin source v6 0 5 0.1

.print dc v(OUT)

VTC曲线

瞬态分析

五、实验心得

本次实验虽与上次实验相似,只是所求不一样。

能自己用CMOS 和PMOS连接电路组合成两输入与非门。

通过改变参数实验求得直流特性曲线分析和瞬态分析。

使我进一步了解mos管。

EPM7128开发板实验指导书

VHDL实验指导书二○○九年十一月李启丙编目录第一节 EPM7128开发板简介 (3)第二节实验指导书 (5)实验一 3-8译码器逻辑设计 (5)实验二 LED彩灯控制器实验 (7)实验三静态数码管显示控制器设计 (8)实验四四位动态数码管显示控制电路设计 (9)实验五键盘实验程序 (10)附录 I Quartus ii 7.1的使用 (11)第一节 EPM7128开发板简介一、套件试验板资源:板上配有一片实验用CPLD可编程器件,并设有下载接口,9V电源输入插口,7段LED显示器四个,输出发光二极管16个,输入(开关)位数8位,按钮8+1个(可用于单步信号产生、复位键、置位键等),输出蜂鸣器一个。

CPLD选用ALTERA公司EPM7128-15芯片,片上资源:密度6000门,封装PLCC84,速度75MHz,I/O口56+4+4=64个。

二、开发试验板结构:结构图:A1、A2、A3、A4——四位LED共阴数码显示器。

D1、D2、D3、----、DE、DF、DG——16个共阳LED指示灯。

电源输入——电源输入插座+9V。

DB25——下载插座,接PC并行口。

OSC——时钟晶体插座。

时钟输出Q14—Q4-------为OSC晶振Fosc的14—4级分频输出,您也可以选择16M时钟,与GCLK输入连接。

S0----产生电平脉冲,并与单脉冲CP输入相连,脉冲特性由‘脉冲选择‘跳线决定(上升或下降)。

拨动开关-----对应K1—K8,在上方为H电平,在下方对应L电平。

S1—S8——脉冲电平按钮,平时为L电平,按下后为H电平(S1-S8上方LED指示灯以标识按键电平,高电平时点亮,低电平熄灭)。

JTAG接口---为在线编程口,当跳线器插上时,JTAG口对应CPLD管脚;当跳线器断开时,用户可通过JTAG口对其它CPLD或FPGA芯片编程。

JP I/O跳线插座跳线器上方端头对应于板间资源(如:LED、S1——S8等)跳线器下方端头对应于CPLD管脚当跳线器插入时则表示CPLD管脚与相应资源连接,相反则断开。

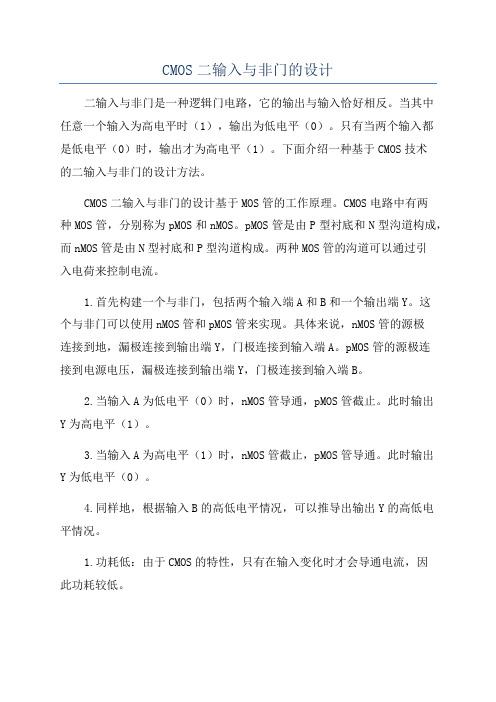

CMOS二输入与非门的设计

CMOS二输入与非门的设计二输入与非门是一种逻辑门电路,它的输出与输入恰好相反。

当其中任意一个输入为高电平时(1),输出为低电平(0)。

只有当两个输入都是低电平(0)时,输出才为高电平(1)。

下面介绍一种基于CMOS技术的二输入与非门的设计方法。

CMOS二输入与非门的设计基于MOS管的工作原理。

CMOS电路中有两种MOS管,分别称为pMOS和nMOS。

pMOS管是由P型衬底和N型沟道构成,而nMOS管是由N型衬底和P型沟道构成。

两种MOS管的沟道可以通过引入电荷来控制电流。

1.首先构建一个与非门,包括两个输入端A和B和一个输出端Y。

这个与非门可以使用nMOS管和pMOS管来实现。

具体来说,nMOS管的源极连接到地,漏极连接到输出端Y,门极连接到输入端A。

pMOS管的源极连接到电源电压,漏极连接到输出端Y,门极连接到输入端B。

2.当输入A为低电平(0)时,nMOS管导通,pMOS管截止。

此时输出Y为高电平(1)。

3.当输入A为高电平(1)时,nMOS管截止,pMOS管导通。

此时输出Y为低电平(0)。

4.同样地,根据输入B的高低电平情况,可以推导出输出Y的高低电平情况。

1.功耗低:由于CMOS的特性,只有在输入变化时才会导通电流,因此功耗较低。

2.高噪声抗干扰特性:由于CMOS门电路的结构特点,能有效抑制噪声和干扰。

3.速度快:由于CMOS电路的响应时间很短,可以实现高速逻辑运算。

4.稳定性好:CMOS电路中的两种MOS管结构互补,可以避免静态功耗(电流流失)。

当然,CMOS二输入与非门还有一些缺点,例如:1.延迟较大:由于需要经过两个MOS管的开关过程,因此比较延迟。

2.静态功耗:尽管CMOS电路的静态功耗较低,但仍然会存在一些功耗。

综上所述,CMOS二输入与非门是一种基于CMOS技术的逻辑门电路。

通过合适的MOS管连接方式,可以实现输入与输出的恰好相反,从而满足与非门的功能要求。

CMOS技术的优点使得该设计具有低功耗、高噪声抗干扰特性、快速响应和稳定性好等特点,但也存在一些缺点,如延迟较大和静态功耗。

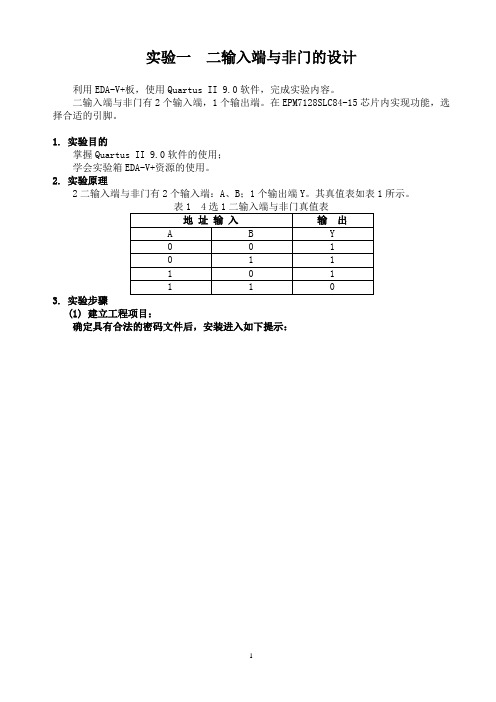

实验一 二输入端与非门的设计EPM7128-bdf

实验一二输入端与非门的设计利用EDA-V+板,使用Quartus II 9.0软件,完成实验内容。

二输入端与非门有2个输入端,1个输出端。

在EPM7128SLC84-15芯片内实现功能,选择合适的引脚。

1. 实验目的掌握Quartus II 9.0软件的使用;学会实验箱EDA-V+资源的使用。

2. 实验原理2二输入端与非门有2个输入端:A、B;1个输出端Y。

其真值表如表1所示。

3. 实验步骤(1) 建立工程项目:确定具有合法的密码文件后,安装进入如下提示:图1 点击NEXT进入建立工程对话窗口:图2或者,从主菜单选取File→New Project Wizard,同样出现图2。

来创建工程。

出现对话框如图4所示。

图4 新建工程更改工程保存的路径为D:\EDA_test\2nand,工程名称为2nand,文件名称为2nand,点击Next,提示是否创建“D:\EDA_test\2nand”?选择“是”,出现:在上图中的File name对话框内输入2nand.bdf,然后,点击右侧的Add。

图3 添加文件到工程中接着点击Next,在下图中选择所使用的器件。

在Family“系列”下拉窗口中选择MAX7000S,在Available devices下选择EPM7128SLC84-15具体器件。

图4 选择器件在图4中,点击Next进入图5。

图5 选择第三方工具在图5中取默认值,直接点击Next进入图6。

图6 工程信息点击Finish完成工程设置,这时在Project Navigator下的实体Entity下出现multi_4v 的工程,见图7所示。

图7 全局窗口综上,建立了一个名称为“2nand”的工程,接下来需要在工程下建立需要的文件。

(2)建立文件:选取窗口菜单File→New,图8 建立文件出现对话框,如图9。

选Block Diagram/Schematic File选项,建立原理图文件。

单击OK 按钮,进入文本编辑画面。

两输入CMOS与非门设计及TPd的测量

两输入CMOS与非门设计及TPd的测量

实验目的:

至少采用4种逻辑类型,分别设计一个两输入的与非门,并测量出它的平均传输延时Tpd。

实验原理:

CMOS逻辑系列有:静态和动态、传输晶体管、无比和有比逻辑等等,请参考教材第6章,至少设计4种类型的两输入与非门,例如互补静态CMOS类型、伪NMOS与非门类型、DCVSL负载类型、动态与非门等等。

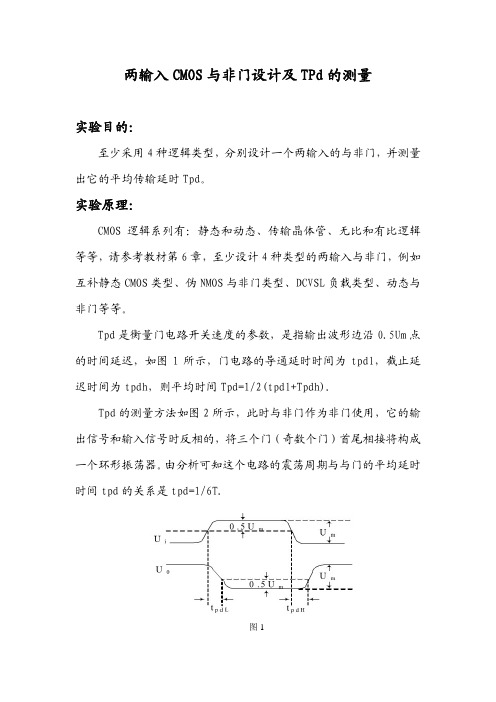

Tpd是衡量门电路开关速度的参数,是指输出波形边沿0.5Um点的时间延迟,如图1所示,门电路的导通延时时间为tpdl,截止延迟时间为tpdh,则平均时间Tpd=1/2(tpdl+Tpdh).

Tpd的测量方法如图2所示,此时与非门作为非门使用,它的输出信号和输入信号时反相的,将三个门(奇数个门)首尾相接将构成一个环形振荡器。

由分析可知这个电路的震荡周期与与门的平均延时时间tpd的关系是tpd=1/6T.

图1

图2 与非门传输延时Tpd测试原理图

实验要求:

(1)采用工艺库tanner\TSpice70\models\ml2_125.md。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验一二输入端与非门的设计

利用EDA-V+板,使用Quartus II 9.0软件,完成实验内容。

二输入端与非门有2个输入端,1个输出端。

在

EPM7128SLC84-15芯片内实现功能,选择合适的引脚。

1. 实验目的

掌握Quartus II 9.0软件的使用;

学会实验箱EDA-V+资源的使用。

2. 实验原理

2二输入端与非门有2个输入端:A、B;1个输出端Y。

其真值表如表1所示。

表1 4选1二输入端与非门真值表

地址输入输出

A B Y

0 0 1

0 11

10 1

110

3. 实验步骤

(1 建立工程项目:

确定具有合法的密码文件后,安装进入如下提示:

图1

点击NEXT进入建立工程对话窗口:

图2

或者,从主菜单选取File→New Project Wizard,同样出现图

2。

来创建工程。

图3 从主下拉菜单主选择路径新建工程项目

出现对话框如图4所示。

图4 新建工程

更改工程保存的路径为D:\EDA_test\2nand,工程名称为2nand,文件名称为2nand,点击Next,提示是否创建“D:\EDA_test\2nand”?

选择“是”,出现:

在上图中的File name对话框内输入2nand.bdf,

然后,点击右侧的Add。

图3 添加文件到工程中

接着点击Next,在下图中选择所使用的器件。

在

Family“系列”下拉窗口中选择MAX7000S,在Available devices 下选择EPM7128SLC84-15具体器件。

图4 选择器件

在图4中,点击Next进入图5。

图5 选择第三方工具

在图5中取默认值,直接点击Next进入图6。

图6 工程信息

点击Finish完成工程设置,这时在Project Navigator下的实体Entity下出现multi_4v的工程,见图7所示。

图7 全局窗口

综上,建立了一个名称为“2nand”的工程,接下来需要在工程下建立需要的文件。

(2建立文件:选取窗口菜单File→New,

图8 建立文件

出现对话框,如图9。

选Block Diagram/Schematic File选项,建立原理图文件。

单击OK按钮,进入文本编辑画面。

图9 建立文件对话框

输入原理图文件内容到编辑窗口。

方法是:在编辑的栅格处,双击鼠标左键,在弹出的对话框中的Name处输入“nand2”元件名,可以看到,NAND2元件的样图显示出来了。

然后,点击“OK”。

一个NAND2元件元件就被放置到了原理图编辑对话框

中了。

图10A 原理图文件输入和编辑对话框

接下来,用同样的方法安放输入和输出引脚。

在编辑栅格的空白处,双击鼠标左键,在弹出的对话框中的Name处键入“INPUT”元件名。

然后,点击“OK”。

一个INPUT元件就被放置到了原理图编辑对话框中了。

同样,再安放“OUTPUT”元件。

图10B 原理图文件输入和编辑对话框

接下来,进行连线。

鼠标移动到元件的引脚旁时,会出现连线的标志,此时按住鼠标左键,在目标处放开鼠标左键,一条连线就画成功了。

完成下图的连线。

图10 原理图

编辑引脚的名称。

如双击一条“INPUT”引脚,如下图。

在“Pin name(s”处输入“A”。

另一输入引脚,和一个输出引脚,同样编辑。

最后形成下图所示的电路。

(3 保存:选取窗口菜单File→Save as,出现对话框,键入文件名2nand.bdf,

图11 文件保存

单击“保存”按钮保存文件。

(4编译:选取窗口菜单Processing→Start Compila tion,或点击快捷按钮进行编译。

图12 编译工程选项

编译工程需要一段时间,见图13的编译过程进程显示。

图13 编译工程进程

图14 编译结束

需要排除编译中产生的所有错误,某些警告可以忽略。

点击“确定”。

(5 引入输入/输出脚:选取窗口菜单Assignments → Pins,图13对话框。

图15 引入输入/输出脚对话框

图16 编辑引入输入/输出脚对话框

在图14中,拖动A、B、Y引脚到图中的引脚。

在此选:

A→9→D1

B→10→D2

Y→11→LED1

将Node Name下的名称(如A一个一个地拖动到Pin Planner对应的引脚标号处(如15)。

图17 引脚分布

此步骤不用保存,将上面的对话框关到最小即可。

这时,再查看原理图,已经

有了对应的引脚。

在主菜单Assignments→Pins或Assignments→Pin Planner均可打开图20,

用以观察引脚分布。

或

图18 引脚分布图观察操作

(6 编辑输入/输出脚之后,再执行项目编译:选取窗口菜单

Processing→Start Compilation,或点击快捷按钮进行编译。

这样,可以形成对应编辑好引脚的对应文件,包括烧写文件等。

编译之后,就可以将程序代码烧写到CPLD或FPGA中,这一步我们放到第(8)步进行。

(7建立波形仿真文件:选取窗口菜单File→New,出现对话框,如图19。

选Vector Waveform File选项,单击OK按钮,进入波形图编辑画面。

图19 建立波形仿真文件窗口

图20 建立波形仿真文件窗口

在引脚输入的“Name”区,点击鼠标右键,如图21在波形窗口中插入引脚。

图21 在波形窗口中插入引脚

可以在图22的“Name”区,输入引脚的名称,然后点击“OK”。

这种方式一次只能输入一个引脚。

下图是输入引脚“A”的示例,在此引脚的书写不分大小

写。

逐一输入即可。

图22 一次输入一个引脚

或者在上图中,点击“Node Finder”,出现图23。

图23 批量一次性输入所有引脚到波形编辑窗口

在图23中,点击“List”。

图24 引入引脚

点击“≥”,将左侧发现的引脚选择有用的逐一添加到右侧窗口中,或者点击“》”,将左侧发现的引脚全部一次性地添加到右侧窗口中,在此点击“》”。

见

图25。

图25 引入引脚对话框

点击OK,进入图26。

图26 引入引脚对话框

点击OK,进入图27。

图27 引入引脚

选中引脚图标,见图28,信号源图标变成实体。

图28 将各个引脚引入信号源信号源可以选择图标,如图29、30。

图29 引脚引入信号源设置

图30 引脚引入信号源设置

点击“确定”。

同样,输入B引脚的波形。

或者选择图标,自编各个引脚的波形。

引脚波形的构造要与系统的功能状态相吻合,便于验证系统功能。

图31 引脚引入信号保存波形文件。

图32 保存波形文件波形仿真操作,如图33。

图33 波形仿真操作

或直接点击快捷图标。

图34 仿真波形

自行从波形图上验证逻辑状态。

(8)将程序下载到CPLD或FPGA中,在此时下载到CPLD中。

执行Tools→Programmer,如图35所示。

图35 程序下载操作

在弹出的图36中,查看文件、器件、硬件设置几个选项,均真确无误后,选中Program/Configure方形选框之后,点击“Start”按钮。

图36 下载的相关信息

图37 下载的相关信息

图38 JTAG口设置对话框

图39 程序下载进程对话框(9)在EDA-V+实验箱上按照表2可验证设计器件的功能。

表2 4选1二输入端与非门的实验结果

地址线输出(10)可以观察芯片资源的利用情况,如图40所示。

思考:

1.上面实验选择的型号EPM7128SLC84-15(属于CPLD期间,也可改成其它信号的CPLD 或FPGA芯片;

2.利用可编程逻辑芯片验证其它组合逻辑电路。