第3章Verilog设计入门

第3章 Verilog设计入门

(3)赋值符号“<=” 说明:只能用于顺序语句中

• 改错:

module mux41a (a,b,c,d,s1,s0,y) input a,b,c,d,s1,s0; output y; reg a,b,c,d; always @ * begin : mux41 case({s1,s0}) 2'b1: y=a; 2'b2: y=b; 2'b3: y=c; 2'b4: y=d; endcase endmodule

Verilog中的四种基本数值:

0:即二进制数0、低电平、逻辑0、事件为伪 的判断结果; 1:即二进制数1、高电平、逻辑1、事件为真 的判断结果; z或Z:高阻态,或高阻值,还可用“?”表示。 x或X:不确定,或未知的逻辑状态。

3.assign连续赋值语句

由assign引导的赋值语句方式也称为数据流描述方式,即当等号右侧 的驱动表达式中的任一信号发生变化时,表达式被计算一遍,赋给左 侧的目标变量;

当一个模块中有多个assign语句时,不允许有多个不同赋值表 达式,即在同一个模块中,wire型变量不允许有多个驱动源。 如果驱动表达式为高阻态,是可以允许的。

2.等式操作符

(1)当关系为真时,等式操作的结果为1,当关系为假时,结果为0; (2) ==等于操作符,两个二进制数比较必须每一位都相等,结果才为1, 否则为0,且如果其中有的位是未知值X或高阻值z都判断为假,输出0; (3)全等比较操作符===,将两个比较值当成确定的值进行比较,当表述 相同为1.

3.1.3 4选1多路选择器及其数据流描述方式

数据流描述方式:即直接用布尔逻辑表达式来描述模块的功能。

第3章 Verilog设计入门

元件的输出。

格式

wire 数据名1,数据名2, ……,数据名n;

wire型向量(总线)

wire[n-1:0] 数据名1,数据名2, ……,数据名m; 或 wire[n:1] 数据名1,数据名2, ……,数据名m;

总 结

Verilog HDL程序是由模块构成的。每个模块嵌套在module 和endmodule声明语句中。模块是可以进行层次嵌套的。

每个模块要进行端口定义,并说明输入输出端口,然后对模 块的功能进行行为逻辑描述。 程序书写格式自由,一行可以写几个语句,一个语句也可以 分多行写。

Verilog HDL关键字

and always assign begin buf bufif0 bufif1 case casex casez cmos deassign default defparam disable edge else end endcase endfunction endprimitive endmodule endspecify endtable endtask event for force forever fork function highz0 highz1 if ifnone initial inout input integer join large macromodule medium module nand

与C 语言一致

规范的书写格式

规定了文本布局、命名和注释的约定,以提 高源代码的可读性和可维护性。

最顶层的module_endmodule模块放在最左 侧 低一层次的语句向右靠一个TAB键的距离 同一语句关键字对齐

《Verilog设计入门》PPT课件

精选PPT

18

3.1 组合电路的Verilog描述

3.1.2 4选1多路选择器及其case语句表述方式 6.赋值操作符 “<=”,只能用于顺序语句,不能用于assign引 导的并行语句

两种过程赋值操作: (1)阻塞式赋值“=”:语句执行结束,右侧表达式的值立刻赋给左侧 目标变量。

对于always引导的块语句中含有多条阻塞式赋值语句时,当执行某 一条语句时,其它语句不允许执行,被阻塞了,具有顺序执行的特点。

精选PPT

23

3.1 组合电路的Verilog描述

3.1.4 4选1多路选择器及其if语句描述方式

精选PPT

24

3.1 组合电路的Verilog描述

3.1.4 4选1多路选择器及其if语句描述方式 1.if_ else条件语句 if(表达式) begin 语句1;语句2;…..语句n; end else begin 语句n+1;语句n+2;…..语句n+n; end

input a,b;

output so,co;

assign so = a ^ b;

assign co = a & b;

endmodule

精选PPT

28

3.1 组合电路的Verilog描述

3.1.5 加法器及其Verilog描述

2.基于always @引导的过程语句和逻辑操作符的描述

module h_adder2(a,b,so,co);

endmodule

精选PPT

34

3.1 组合电路的Verilog描述

3.1.5 加法器及其Verilog描述 5. 全加器描述----用半加器、或门模块及例化语句描述

精选PPT

verilog学习

关系运算符是用来确定指定的两个操作数之间的关系是 否成立的, 如果成立, 结果为1(真); 如果不成立, 结果 为0(假)。 假设:m =19; n = 5; a=x

那么: m > n

m<n m<a

结果为1 (真)

结果为0 (假) 结果为x

第3章 Verilog HDL的基本语法

4. 等值运算符

== (逻辑相等) != (逻辑不等) === (全等) !== (非全等)

第3章 Verilog HDL的基本语法

例如: reg [7:0] a; reg b b=&a; 程序中, “b=&a;” 语句与“b=a[0] & a[1] & a [2] & a[3] & a[4] & a[5] & a[6] & a [ 7];”语 句等价。

第3章 Verilog HDL的基本语法

X={a[7:4], b[3], c[2:0]} 表示X是由a的第7~4位、 b的第3位和c的第2~0位拼接而 成的。

第3章 Verilog HDL的基本语法

10. 运算符的优先级 在一个表达式中出现多种运算符时, 运算的优先级顺序如下:

!a

!b

判断一个数是否为真时, 以0代表“假”, 以非0代表“真”。 假设: ABus = ′b0111; BBus = ′b0101;那么 ! ABus 0(假)

ABus || BBus 1(真)

ABus && BBus 1(真)

第3章 Verilog HDL的基本语法

3. 关系运算符

< > (小于) (大于) <= >= (小于等于) (大于等于)

EDA 第3章 Verilog设计入门

www.themBiblioteka

5.注释符号

3.1.4 4选1多路选择器及其if语句描述方式

1.if_ else条件语句

执行过程:当if后的条件表达式为真时,执行赋值语句, 否则执行else后的If语句,如此数据的执行下去,直到完 成所有if语句。 同样,如果执行多条语句时,应该用begin-end块语句将 它们括起来。

5.并位操作和数字表达

(1)并位操作

大括号{}:并位运算符,将两个或多个信号按二进制位拼接起来, 作为一个信号使用。

(2)数字表示 表示二进制数的一般格式:

说明: 1. B表示二进制,O表示八进制,H表示十六进制,D表示十进制,且 不分大小写。 2. verilog2001规定可定义有符号二进制数,如8„b10111011和 8‟sb10111011是不一样的。前者是普通无符号数,后者是有符号数,最 高位1是符号。

3.1.2 4选1多路选择器及其case语句表述方式

1.reg型变量定义

(1)verilog中最常用的变量:寄存器型变量(reg)和网线型变量 (wire)。 (2)模块中功能描述涉及的所有信号都必须定义相应的变量类型, 如果没有在模块中显式地定义信号的类型,verilog默认定义为 wire型。 (3)当需要信号为寄存器型信号时必须使用reg进行显示定义,在 过程语句always@引导的顺序语句中规定必须是reg型变量。 (4)输入或双向口信号不能定义为寄存器型信号类型

(2)条件数值虽为整数1、2、3的表达式,但综合器自 动转化为case的变量{a,b}与对应数据类型的数值进 行比较判定。

说明:例3.8直接使用了加法算术操作符“+”的描述方式。

Verilog HDL 3

图3-2 值变化快于时延间隔

上面例子中的时延值只出现了一个,事实上这只 是一个“上升时延”,连续赋值语句中的时延可 以指定3类时延值:上升时延、下降时延和关闭时 延(值变为x的时延)。这是一种更加精细的时延 定义方式,其语法形式如下: assign # (rise, fall, turn-off ) LHS_target=RHS_expression; 其中rise是上升时延,fall是下降时延,turn-off是关 闭时延。

其具体含义可以根据下面的例子看出来: assign Bus = MemAddr [7:4]; // 没有定义时延, 则所有时延都是0 assign #4 Ask = Quiet || Late; // 只有1个时延 值,表示上升时延、下降时延和关闭时延都是4 assign # (4,8) Ask = Quick ; /* 有2个时延值, 表示上升时延是4,下降时延是8,关闭时延是 4和8之中的较小值,即4 */ assign # (4,8,6) Arb = & DataBus; // 有3个时延值, 表示上升时延是4,下降时延是8,关闭时延是6

3.2 顺序行为建模

顺序行为建模是Verilog HDL行为建模的主 要方法,也是Verilog HDL最能体现其高级 编程语言之处,如果学过其他高级变成语 言(如C语言),就会对本节介绍的诸如ifelse、for循环之类的语法结构非常熟悉。

此外,本节还将介绍过程赋值的特点和用 法。就像连续赋值用于数据流行为建模一 样,过程赋值用于顺序行为建模。

如下例: assign Mux = (S = = 0)? A : 'bz; assign Mux = (S = = 1)? B : 'bz; assign Mux = (S = = 2)? C : 'bz; assign Mux = (S = = 3)? D : 'bz;

Verilog教程-夏宇闻(共178张)

第13页,共178页。

3.2 Verilog HDL基本(jīběn)结构

二、Verilog HDL模块的结构

▪ Verilog的基本设计单元是“模块 (block) ” 。 ▪ Verilog 模块的结构由在module和endmodule关键词

之间的4个主要部分组成:

1 端口定义 2 I/O说明

(3)用 “always” 块语句 结构说明语句

always @(posedge clk) // 每当时钟上升沿到来时执行一遍块内语句

begin

if(load)

out = data; // 同步预置数据 else

out = data + 1 + cin; // 加1计数

end

❖注1:“always” 块语句常用于描述时序逻辑,也可 描述组合逻辑。

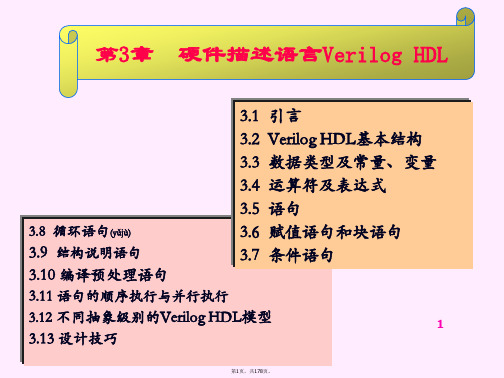

3.12 不同抽象级别的Verilog HDL模型

1

3.13 设计技巧

第1页,共178页。

引言 3.1

(yǐnyán)

内容概要

一、什么是Verilog HDL 二、Verilog HDL的发展历史 三、不同层次的Verilog HDL抽象

四、Verilog HDL的特点

2

第2页,共178页。

3.1 引言(yǐnyán)

❖ Verilog HDL模块的模板(仅考虑用于逻辑综合的部分)

module <顶层模块名> (< 输入输出端口列表>) ;

output 输出端口列表;

input 输入端口列表;

//(1)使用assign语句定义逻辑功能

wire 结果信号名;

assign <结果信号名> = 表达式 ;

verilogHDL培训教程华为

VerilogHDL培训教程——华为第一章:引言随着电子设计自动化(EDA)技术的不断发展,硬件描述语言(HDL)在数字电路设计领域扮演着越来越重要的角色。

VerilogHDL 作为一种主流的硬件描述语言,因其强大的功能、灵活的语法和广泛的应用范围,已成为数字集成电路设计工程师必备的技能之一。

本教程旨在帮助读者掌握VerilogHDL的基本概念、语法和设计方法,为华为等企业培养合格的数字电路设计人才。

第二章:VerilogHDL基础2.1VerilogHDL简介VerilogHDL是一种用于数字电路设计的硬件描述语言,它可以在多个层次上对数字系统进行描述,包括算法级、寄存器传输级(RTL)、门级和开关级。

VerilogHDL的设计初衷是为了提高数字电路设计的可重用性、可移植性和可维护性。

2.2VerilogHDL编程环境(1)文本编辑器:Notepad++、SublimeText等;(2)仿真工具:ModelSim、IcarusVerilog等;(3)综合工具:XilinxISE、AlteraQuartus等。

2.3VerilogHDL语法基础(1)关键字:VerilogHDL中的关键字具有特定含义,如module、endmodule、input、output等;(2)数据类型:包括线网类型(wire)、寄存器类型(reg)、整数类型(integer)等;(3)运算符:包括算术运算符、关系运算符、逻辑运算符等;(4)模块与端口:模块是VerilogHDL设计的基本单元,端口用于模块之间的信号传递;(5)行为描述与结构描述:行为描述用于描述电路的功能,结构描述用于描述电路的结构。

第三章:VerilogHDL设计流程3.1设计流程概述(1)需求分析:明确设计任务和功能要求;(2)模块划分:根据需求分析,将设计任务划分为若干个模块;(3)编写代码:使用VerilogHDL编写各个模块的代码;(4)仿真验证:对设计进行功能仿真和时序仿真,确保设计正确;(5)综合与布局布线:将VerilogHDL代码转换为实际电路,并进行布局布线;(6)硬件测试:在FPGA或ASIC上进行实际硬件测试。

Verilog设计入门

2.等式操作符

等式运算符

(==)和 (!=)不比较x和z位 (===)和(!==)将x 和 z 当确定值进 行比较 例:(3==4)=0;(3!=4)=1; (4’b1010==4’b1010)=1; (4’b0z1x===4’b0z1x)=1; (4’b0z1x==4’b0z1x)=0;

3.assign连续赋值语句

常量

下画线 - 下画线可以提高程序的可读性,只能用在具 体的数字之间。 例: 16’b1010_1011_1111_1010 //合法 8’b_0011_1010 //非法格式

3.1.2 4选1多路选择器及其case语句表述方式

练习3 写出2选1多路选择器Verilog描述(用always结构,

3.块语句begin_ end

4.case条件语句和4种逻辑状态

3.1.2 4选1多路选择器及其case语句表述方式

5.并位操作和数字表达

数字表达

常量 数字的表达方式 <位宽> <进制> <数字> 例: 8’b10101100 8’ha2 , 4’b1010 , 3’d5 位宽默认(32)位,进制默认(十进制)

3.2.6 Verilog的时钟过程表述的特点和规律 对于边沿触发型时序模块,遵循以下规律: 1.某信号被定义成边沿敏感时钟信号,则posedge A或

negedge A放敏感表中,但always结构块中不能再出现信

号A了。 2.若B被定义成对应于时钟的电平敏感异步控制信号,则除

posedge B或negedge B放敏感表中,always块中必须

____ muxtwo (out, __, __, __ ); input __, __, __; ____ out; reg out; always@ (sl or a or b) if (! sl) out=a; else out=b; ____

Verilog HDL基础知识

tri tri0 tri1 triand trior trireg unsigned vectored wait wand weak0 weak1 while wire wor xnor xor

第3章 Verilog HDL基础知识

3.2 数 据 类 型

Verilog HDL支持两种形式的注释符:/*……*/与//。其中, /*……*/为多行注释符,用于对多行语句注释;//为单行注释符, 只对注释符所在的行有效。下面是一个使用注释符对1位加法器 进行说明的例子。

第3章 Verilog HDL基础知识

【例3-2】注释符的例子。

/* 该例利用一位加法器来说明单行注释符与多行注释符的

第3章 Verilog HDL基础知识

1. 字符串变量的声明 Verilog HDL中采用寄存器变量来存储字符串,寄存器变量的 位数要大于字符串的最大长度。需要注意的是,Verilog HDL中并 不需要特殊位来存储终止符。 【例3-6】字符串变量的声明。

reg [8*12:1] stringvar; initial

'<base_format><number> 符号“'”为基数格式表示的固有字符,该字符不能省略,否 则为非法表示形式;参数<base_format>用于说明数值采用的进制 格式;参数<number>为相应进制格式下的一串数字。这种格式未 指定位宽,其缺省值至少为32位。

第3章 Verilog HDL基础知识

第3章 Verilog HDL基础知识

module addbit (a,b,ci,sum,co);

input

第3章 Verilog中的常量、变量与数据类型

21

3.2 变量

测试代码

module comp2_test; reg clk,ina,inb; wire out1,out2; always begin #10 clk=1; #10 clk=0; end initial begin clk=0;ina=0;inb=0; #100 ina=0;inb=1; #100 ina=1;inb=0; #100 ina=1;inb=1; end comp2 u1(ina,inb,clk,out1,out2);

clk din

shifter[3]

tsetup thold

tsetup thold

30

非阻塞赋值: 4位移位寄存器

31

阻塞赋值: 4位移位寄存器

`timescale 1ns/100ps module shifter(din,clk,reset,dout); input clk,din,reset; output dout; reg[3:0]shifter; always@(posedge clk,posedge reset)

非阻塞赋值用于时序逻辑电路,阻塞赋值用于组合逻辑电路。

1、非阻塞赋值:使用符号“<=”,

特点:在一个块语句内,采用非阻塞赋值的变量在所有语句都执行 完毕后才被赋予新的数值,此前保持原值。

2、阻塞赋值:使用符号“=”,

特点:在一个块语句内,对变量的赋值是立刻生效的。

28

非阻塞赋值: 4位移位寄存器

`timescale 1ns/100ps module shifter(din,clk,reset,dout); input clk,din,reset; output dout; reg[3:0]shifter; always@(posedge clk,posedge reset)

第一部分 Verilog数字设计基础

(4)门级(gate—level):描述逻辑门以及逻辑门之间连接的模型。 与逻辑电路有确定的连接关系,以上四种数字系统设计工程师必须掌 握。 (5)开关级(switch—level):描述器件中三极管和储存节点以及它们 之间连接的模型。

在美国,应用Verilog和VHDL的比例是80%和20%;日本和台湾 与美国相同;而在欧洲VHDL发展的比较好。

Verilog HDL适用的描述层次:

1、系统级(System) 部分可物理实现,主要用于仿真 2、算法级(Alogrthem)部分可物理实现,主要用于仿真 3、寄存器传输级(RTL)可完全物理实现,用于电路设计 4、逻辑级(Logic) 可完全物理实现,用于电路设计 5、门级(Gate) 可完全物理实现,用于电路设计 6、电路开关级(Switch)软件中不涉及,用于芯片设计

§1.6 Verilog HDL的设计流程

1.6 Verilog HDL的设计流程

方法:Top-Down(自顶向下)设计思想。

系统级设计

模块A

模块B

模块C

模块 A1

模块 A2

模块 A3

模块 B1

模块 B2

模块 B3

模块 C1

模块 C2

图1.3 Top-Down设计思想

电路图设计文件

HDL设计文件

注:它是目前应用最广泛的一种硬件描述语言。

目前在美国使用Verilog HDL进行设计的工程师大约有10万多人,全美国有200 多所大学讲授Verilog语言的设计方法。在台湾地区几乎所有著名大学的电子和计 算机工程系都讲授与Verilog有关的课程。

§1.2.2 VerilogHDL的产生及发展

第3章Verilog硬件描述语言-FSM设计举例

5

表1 USB与AES接口模块外部信号说明

信号名称

传输方向 信号含义

clk

输入

rst

输入

load

输出

address<7:0> 输出

keyexpen keyexprdy staenc stadec encdecrdy din<15:0>

输出 输入 输出 输出 输入 输出

时钟信号 复位信号,1有效。 数据装载使能信号,用于控制输入明/密文、密 钥、S盒配置数据等,1有效。 寄存器或RAM地址,用于表示明文/密文/密钥 寄存器、S盒RAM单元。 密钥扩展使能信号,1有效。 密钥扩展完成标识信号,1有效。 开始加密使能信号,1有效。 开始解密使能信号,1有效。 加/解密运算完成标识信号,1有效。 接AES输入数据总线,用于输入明/密文、密钥、 配置数据等。

SLOE、SLRD、 FIFOADR<1:0>

load、address、din、SLOE、 SLRD、FIFOADR<1:0>

load、address、din、SLOE、 SLRD、FIFOADR<1:0> 11

状态转移及控制信号取值表(续1)

当前状态

S2 S2 S3

当前输入

下一状态

密钥扩展结束 S0 密钥扩展没结束 S2 加密S盒配置结束 S0

load、address、din、SLOE、 SLRD、FIFOADR<1:0>

stadec

stadec

shift、FD<15:0>、SLWR、 FIFOADR<1:0>

shift、FD<15:0>、SLWR、

FIFOADR<1:0>

-Verilog-HDL的基本语法

第三章 Verilog HDL的基本语法前言Verilog HDL是一种用于数字逻辑电路设计的语言。

用Verilog HDL描述的电路设计就是该电路的Verilog HDL模型。

Verilog HDL既是一种行为描述的语言也是一种结构描述的语言。

这也就是说,既可以用电路的功能描述也可以用元器件和它们之间的连接来建立所设计电路的Verilog HDL模型。

Verilog模型可以是实际电路的不同级别的抽象。

这些抽象的级别和它们对应的模型类型共有以下五种:•系统级(system):用高级语言结构实现设计模块的外部性能的模型。

•算法级(algorithm):用高级语言结构实现设计算法的模型。

•RTL级(Register Transfer Level):描述数据在寄存器之间流动和如何处理这些数据的模型。

•门级(gate-level):描述逻辑门以及逻辑门之间的连接的模型。

•开关级(switch-level):描述器件中三极管和储存节点以及它们之间连接的模型。

一个复杂电路系统的完整Verilog HDL模型是由若干个Verilog HDL模块构成的,每一个模块又可以由若干个子模块构成。

其中有些模块需要综合成具体电路,而有些模块只是与用户所设计的模块交互的现存电路或激励信号源。

利用Verilog HDL语言结构所提供的这种功能就可以构造一个模块间的清晰层次结构来描述极其复杂的大型设计,并对所作设计的逻辑电路进行严格的验证。

Verilog HDL行为描述语言作为一种结构化和过程性的语言,其语法结构非常适合于算法级和RTL 级的模型设计。

这种行为描述语言具有以下功能:•可描述顺序执行或并行执行的程序结构。

•用延迟表达式或事件表达式来明确地控制过程的启动时间。

•通过命名的事件来触发其它过程里的激活行为或停止行为。

•提供了条件、if-else、case、循环程序结构。

•提供了可带参数且非零延续时间的任务(task)程序结构。

10第三章verilog入门

算术运算符

关系运算符 (双目运算符)

位运算符 (双目运算符)

~ & | ^ ^~ 或 ~^ ! && || {,} {{}}

按位取反 按位与 按位或 按位异或 按位同或 逻辑非 逻辑与 逻辑或 将多个操作数 拼接成为一个 操作数

缩位运算符( 单目运算符)

逻辑运算符 (双目运算符)

移位运算符( 双目运算符) 条件运算符( 三目运算符)

条件语句

根据条件表达式的真假, 确定下一步进行的运算。

(1) if (condition_expr) true_statement;

(2) if (condition_expr)true_statement; else fale_ statement;

(3) if (condition_expr1) true_statement1; else if (condition_expr2) true_statement2; else if (condition_expr3) true_statement3; …… else default_statement;

一、硬件描述语言 Verilog HDL 基础

1. 什么是硬件描述语言

HDL:Hardware Description Language

逻辑电路图 表示 逻辑表达式 复杂数字逻辑系统 易于存储和修改 编写说明文档 不同设计人员交流 被计算机识别 类似于高级 程序设计语 言的文本形 式来描述数 字系统硬件 的结构和行 为的语言。 逻辑仿真 逻辑综合

3. Verilog的基本语法规则

运算符

类型 符号 + * / 功能说明 二进制加 二进制减 2的补码 二进制乘 二进制除 类型 符号 > < >= <= == != & ~& | ~| ^ ^~ 或 ~^ >> << ?: 功能说明 大于 小于 大于或等于 小于或等于 相等 不相等 缩位与 缩位与非 缩位或 缩位或非 缩位异或 缩位同或 右移 左移 根据条件表达 式是否成立,选择 表达式

第3章 Verilog HDL语言基础

Verilog HDL语言基础--本章概述

Verilog的门级描述语句; Verilog编译指示语句; Verilog系统任务和函数; Verilog用户定义任务和函数和Verilog语言模块描 述方式。 本章内容对于初步掌握Verilog语言规则非常重 要。

--Verilog语言概述

Verilog HDL(以下简称Verilog)是一种硬件描述语 言,用于从算法级、门级到开关级的多种抽象设计层次的 数字系统建模。

--Verilog语言概述

Verilog HDL语言具有下述描述能力: 设计的行为特性 设计的数据流特性 设计的结构组成 包含响应监控和设计验证方面的时延和波形产生机制。 所有这些都使用同一种建模语言。此外,Verilog HDL语言提供了编程语言接口,通过该接口可以在模拟、 验证期间从设计外部访问设计,包括模拟的具体控制和运 行。

Verilog程序结构

--逻辑功能定义

逻辑功能定义是Verilog程序结构中最重要的部分, 逻辑功能定义用于实现模块中的具体的功能。 主要的方法有: 1.assign连续赋值语句 赋值语句是最简单的逻辑功能描述,用assign赋值语 句定义: 【例3.4】赋值语句用于逻辑功能定义的例子。 assign F=~((A&B)|(~(C&D)));

Verilog HDL硬件描述语言功能

4.提供显式语言结构指定设计中的端口到端口的时 延及路径时延和设计的时序检查。

5.可采用三种不同方式或混合方式对设计建模。这

些方式包括:

行为描述方式—使用过程化结构建模;

数据流方式—使用连续赋值语句方式建模;

结构化方式—使用门和模块实例语句描述建模。

Verilog程序结构

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第3章Verilog设计入门

3.2 时序模块及其Verilog表述

3.2.2 电平触发型锁存器及其Verilog表述

第3章Verilog设计入门

3.2 时序模块及其Verilog表述

3.2.2 电平触发型锁存器及其Verilog表述

第3章Verilog设计入门

第3章Verilog设计入门

3.1 组合电路的Verilog描述

3.1.5 加法器及其Verilog描述 3. 8位加法器描述

第3章Verilog设计入门

3.2 时序模块及其Verilog表述

3.2.1 边沿触发型触发器及其Verilog表述

第3章Verilog设计入门

3.2 时序模块及其Verilog表述

3.2.4 同步复位型触发器及其Verilog表述

第3章Verilog设计入门

3.2 时序模块及其Verilog表述

3.2.4 同步复位型触发器及其Verilog表述

第3章Verilog设计入门

3.数据表示方式

第3章Verilog设计入门

3.1 组合电路的Verilog描述

3.1.5 加法器及其Verilog描述 1. 半加器描述

第3章Verilog设计入门

3.1 组合电路的Verilog描述

3.1.5 加法器及其Verilog描述 1. 半加器描述

第3章Verilog设计入门

3.1 组合电路的Verilog描述

描述

3.1.4 4选1多路选择器及其if语句描述方式

第3章Verilog设计入门

3.1 组合电路的Verilog描述

3.1.4 4选1多路选择器及其if语句描述方式 1.if_ else条件语句

2.过程赋值语句 (1)阻塞式赋值 (2)非阻塞式赋值

3.2 时序模块及其Verilog表述

3.2.3 含异步复位/时钟使能型触发器及其Verilog表述

第3章Verilog设计入门

3.2 时序模块及其Verilog表述

3.2.3 含异步复位/时钟使能型触发器及其Verilog表述

第3章Verilog设计入门

3.2 时序模块及其Verilog表述

3.1.3 4选1多路选择器及其数据流描述方式 4.wire定义网线型变量

第3章Verilog设计入门

3.1 组合电路的Verilog描述

3.1.3 4选1多路选择器及其数据流描述方式

第3章Verilog设计入门

3.1 组合电路的Verilog描述

3.1.3 4选1多路选择器及其数据流描述方式 5.注释符号

3.1.5 加法器及其Verilog描述 2. 全加器顶层文件设计和例化语句

第3章Verilog设计入门

3.1 组合电路的Verilog描述

3.1.5 加法器及其Verilog描述 3. 8位加法器描述

第3章Verilog设计入门

3.1 组合电路的Verilog描述

3.1.5 加法器及其Verilog描述 3. 8位加法器描述

第3章 Verilog设计入门

第3章Verilog设计入门

3.1 组合电路的Verilog描述

3.1.1 2选1多路选择器及其Verilog描述

第3章Verilog设计入门

3.1 组合电路的Verilog描述

3.1.1 2选1多路选择器及其Verilog描述

第3章Verilog设计入门

3.1 组合电路的Verilog描述

第3章Verilog设计入门

3.1 组合电路的Verilog描述

3.1.5 加法器及其Verilog描述 1. 半加器描述

第3章Verilog设计入门

3.1 组合电路的Verilog描述

3.1.5 加法器及其Verilog描述 2. 全加器顶层文件设计和例化语句

第3章Verilog设计入门

3.1 组合电路的Verilog描述

3.1.1 2选1多路选择器及其Verilog描述 1.模块表达

2.端口语句、端口信号名和端口模式

第3章Verilog设计入门

3.1 组合电路的Verilog描述

3.1.1 2选1多路选择器及其Verilog描述 3.赋值语句和条件操作符

4.关键字 5.标识符 6.规范的程序书写格式 7.文件取名和存盘

3.1.5 加法器及其Verilog描述 1. 半加器描述

第3章Verilog设计入门

3.1 组合电路的Verilog描述

3.1.5 加法器及其Verilog描述 1. 半加器描述

第3章Verilog设计入门

3.1 组合电路的Verilog描述

3.1.5 加法器及其Verilog描述 1. 半加器描述

3.1.2 4选1多路选择器及其case语句表述方式 5.并位操作和数字表达

2b’10,4D’9, O,H,D

第3章Verilog设计入门

3.1 组合电路的Verilog描述

3.1.3 4选1多路选择器及其数据流描述方式

第3章Verilog设计入门

3.1 组合电路的Verilog描述

3.1.3 4选1多路选择器及其数据流描述方式 1.按位逻辑操作符

第3章Verilog设计入门

3.1 组合电路的Verilog描述

3.1.2 4选1多路选择器及其case语句表述方式

第3章Verilog设计入门

3.1 组合电路的Verilog描述

3.1.2 4选1多路选择器及其case语句表述方式

第3章Verilog设计入门

3.1 组合电路的Verilog描述

3.1.2 4选1多路选择器及其case语句表述方式 1.reg型变量定义

2.过程语句

第3章Verilog设计入门

3.1 组合电路的Verilog描述

3.1.2 4选1多路选择器及其case语句表述方式 3.块语句begin_ end

4.case条件语句和4种逻辑状态

第3章Verilog设计入门

3.1 组合电路的Verilog描述

第3章Verilog设计入门

3.1 组合电路的Verilog描述

3.1.3 4选1多路选择器及其数据流描述方式 2.等式操作符

第3章Verilog设计入门

3.1 组合电路的Verilog描述

3.1.3 4选1多路选择器及其数据流描述方式 3.assign连续赋值语句

第3章Verilog设计入门

3.1 组合电路的Verilog描述