集成运放参数测试仪[2005年电子大赛一等奖

毕业设计133集成运放参数测试仪

集成运放参数测试仪——程序设计内容摘要:该课题设计的运算放大器闭环参数测试系统是基于MSC-51单片机控制模块,并且由LCD(Liquid Crystal Display)显示模块,键盘模块,数据采集和转换模块,采用DDS芯片(AD9851)实现了40kHz~4MHz的扫频输出模块等五部分组成。

采用辅助运放测试方法,可对运放的输入失调电压、输入失调电流、交流差模开环电压增益和交流共模抑制比以及单位增益带宽进行测量。

在软件上,用C语言来编程实现。

其要实现的功能包括:对来自TLC2543A/D转换的数字信号进行接收、分析、计算和对结果的显示;通过不同键值的接收、分析来控制对不同对象的测量,并在LCD上显示对应的人机界面;对来自DDS的高频信号源的频率进行控制来实现对集成运放的带宽参数的测试和显示。

而且具有自动量程转换、自动测量功能和良好的人机交互性。

关键词:单片机 C语言 DDS LCD 人机交互界面The Instrument for testing the Parameters of IntegratedOperation Amplifier——program designAbstract:This system is designed based on C51 microcontroller to measure the close loop parameters of the operation amplifier. The system conclude five modules: LCD (liquid crystal display) display module, keyboard module, data collection module, conversion module, and the module of generating sweep sine-wave signal with frequency range from 40 kHz to 4 MHz, using the DDS chip of AD9851. The system can measure the input offset voltage、the input offset current、the open loop AC differential mode voltage gain、the AC common mode rejection ratio and unit gain bandwidth,using the measure method of assistant amplifier. The data can be display on the LCD which is using of C program. And the function concludes: receiving, analysing and calculating the digital signals from TLC2543A/D then send them to show; accepting different key value on keyboards, analysing and processing it for controlling the measurement of different target and display on the LCD with different computer interface; controlling the bandwidth of HF signal source from DDS chip to measure the integrated transport bandwidth parameters and display the result. What’s more C51 microcontroller can control relays to complete auto measurement range switching ,auto measuring and good interface.Key Words:MCU CLanguage DDS LCD interface目 录前言 ............................................................................. 1 一、系统原理框图 ................................................................. 1 二、硬件单元电路设计与实现 . (2)(一) ioc V 、io I 、vd A 、cmr K 四个参数的测试电路 ................................ 2 (二) 单位增益带宽测量电路 ................................................. 3 (三) 测试vd CMR A K 、的信号源 ................................................ 3 (四) 峰峰值检测电路的设计 . (4)(五) A/D 采样电路 ......................................................... 4 (六) 扫频信号源 ........................................................... 4 (七) 键盘接口电路 ......................................................... 5 (八) 显示接口电路 ......................................................... 5 三、软件设计 (6)(一) 软件功能设计 ......................................................... 6 (二) 系统软件框图和程序流程图 ............................................. 6 (三) 软件模块设计 ......................................................... 7 四、系统测试 .. (19)(一)程序调试方法 .......................................................... 19 (二)软件调试 .............................................................. 19 (三)联机调试 .............................................................. 20 五、结束语 ...................................................................... 20 六、感谢词 ...................................................................... 20 参考文献 ........................................................................ 20 附录一 .......................................................................... 21 附录二 .......................................................................... 22 附录三 .. (36)(一)TLC2543 ............................................................... 36 (二)LCD 液晶显示器 ......................................................... 36 附录四 .. (38)集成运放参数测试仪——程序设计前言目前国内外市场上各种型号的集成运放参数测试仪已经相当多,而且普遍性都采用“辅助放大器的测量方法”,使测试仪的整个系统具有稳定性好,精确度高,范围大的特点,而且测试仪测试参数一般包括:正向最大输出电压+opp V ,负向最大输出电压-opp V ,正向最大共模输出电压+icm V ,负向最大共模输出电压-icm V ,正转换速率+ r S ,负转换速率-r S ,静态工作电流q I ,输入失调电压ioc V ,共模抑制比cmr K ,开环增益带宽乘积BW ,输入失调电流Iio ,开环电压增益vd A ,基极偏置电流ib I 等15项。

数字集成电路参数测试仪报告(精)

重庆大学本科学生课程设计指导教师评定成绩表说明:1、学院、专业、年级均填全称。

2、本表除评语、成绩和签名外均可采用计算机打印。

重庆大学本科学生课程设计任务书说明:1、学院、专业、年级均填全称。

2、本表除签名外均可采用计算机打印。

本表不够,可另附页,但应在页脚添加页码。

目录一、设计目的 (5)二、设计要求 (5)三、方案设计与论证比较 (5)四、硬件设计 (6)4.1、DA 模块 THS5651工作原理及电路设计4.2、放大模块14.3、ADC0809工作原理及电路设计4.4、Iil 模块4.5、Iol 模块4.6、12864模块五、软件设计.....................................5.1、数值显示模块5.1.1、分频模块5.1.2 十位数据波形发生模块5.1.3 去抖模块5.1.4 文本显示模块5.1.5 按键切换模块5.1.6 ADC0809驱动模块5.2 图形显示模块5.2.1 输入输出电压采样模块5.2.2 输入输出电压数据转换模块5.2.3 显示模块5.2.4 波形显示的整体电路六、系统功能测试及结果..............................6.1测试方法6.1.1 Vol,Voh,Vil,Vih的测试方法6.1.2Vil的测试方法6.1.3Vol的测试方法6.2测试结果6.3测试精度分析七、设计过程总结与体会........................... 参考文献........................................ 附件一系统电路图:附件二元器件清单:附件三一、设计目的在当今社会中,电子技术发展迅速,数字集成电路的应用广泛,而74系列逻辑芯片在数字电路中又有着非常广泛的应用,因而数字电路设计中必须要求所用的数字电路芯片逻辑功能完整,但在数字电路芯片测试中又有很多不便,实际测试较繁琐。

针对上述需要,我们针对常用的74系列逻辑芯片设计了一种数字电路芯片测试仪,用来检测常用74系列芯片的型号和逻辑功能的好坏,从而给数字电路的设计、制作带来方便。

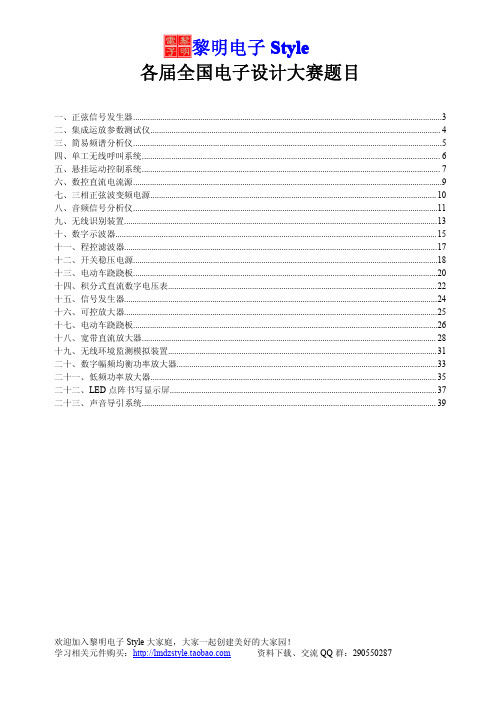

各届全国电子设计大赛题目

各届全国电子设计大赛题目一、正弦信号发生器 (3)二、集成运放参数测试仪 (4)三、简易频谱分析仪 (5)四、单工无线呼叫系统 (6)五、悬挂运动控制系统 (7)六、数控直流电流源 (9)七、三相正弦波变频电源 (10)八、音频信号分析仪 (11)九、无线识别装置 (13)十、数字示波器 (15)十一、程控滤波器 (17)十二、开关稳压电源 (18)十三、电动车跷跷板 (20)十四、积分式直流数字电压表 (22)十五、信号发生器 (24)十六、可控放大器 (25)十七、电动车跷跷板 (26)十八、宽带直流放大器 (28)十九、无线环境监测模拟装置 (31)二十、数字幅频均衡功率放大器 (33)二十一、低频功率放大器 (35)二十二、LED点阵书写显示屏 (37)二十三、声音导引系统 (39)一、正弦信号发生器一、任务设计制作一个正弦信号发生器。

二、要求1、基本要求(1)正弦波输出频率范围:1kHz~10MHz;(2)具有频率设置功能,频率步进:100Hz;(3)输出信号频率稳定度:优于10-4;≥1V;(4)输出电压幅度:在负载电阻上的电压峰-峰值Vopp(5)失真度:用示波器观察时无明显失真。

2、发挥部分在完成基本要求任务的基础上,增加如下功能:=6V±1V;(1)增加输出电压幅度:在频率范围内负载电阻上正弦信号输出电压的峰-峰值Vopp可在10%~100%之间程控调节,(2)产生模拟幅度调制(AM)信号:在1MHz~10MHz范围内调制度ma步进量10%,正弦调制信号频率为1kHz,调制信号自行产生;(3)产生模拟频率调制(FM)信号:在100kHz~10MHz频率范围内产生10kHz最大频偏,且最大频偏可分为5kHz/10kHz二级程控调节,正弦调制信号频率为1kHz,调制信号自行产生;(4)产生二进制PSK、ASK信号:在100kHz固定频率载波进行二进制键控,二进制基带序列码速率固定为10kbps,二进制基带序列信号自行产生;(5)其他。

集成运放参数测试仪设计报告

集成运放参数测试仪(B题)设计报告参赛学校:扬州大学学院:信息工程学院作者:刘中奇张传法邱玉强集成运放参数测试仪(B题)摘要:本设计采用AT89C55WD单片机和可编程逻辑器件(FPGA)作为其测试和控制核心,能够测试通用运放的基本参数并实现自动量程转换等功能。

运放测试电路参照了任务书中所给电路,用单片机控制继电器进行切换,可编程逻辑器件FPGA控制A/D采样,单片机实现顶层的控制,使整个系统能够协调工作,以完成题目要求。

另外,本设计也对发挥部分进行了一定的设计,完成了增益带宽测试和自动循环测试功能。

设计中采用了模块化设计方法,提高了设计和调试效率。

关键词:集成运放,可编程器件(FPGA),单片机(AT89C55WD),继电器1. 系统方案选择和论证1.1系统基本方案根据题目要求,系统可以划分为控制模块、测试模块和信号源模块。

模块框图如图1.1.1所示。

为实现各模块的功能,分别做了几种不同的设计方案并进行了论证。

图1.1.1 测试仪的基本模块方框图1.1.1各模块方案选择和论证(1) 控制器模块根据题目要求,控制器主要用于控制测试电路的切换、控制A/D转换模块、信号源的控制和对显示模块的控制。

对于控制器的选择有以下三种方案。

方案一:采用FPGA(现场可编程门阵列)作为系统的控制核心。

FPGA可以实现复杂的逻辑功能,规模大,密度高,它将所有器件集成在一块芯片上,减小了体积,提高了稳定性,并且可应用EDA软件仿真、调试,易于进行功能扩展。

FPGA采用并行的输入输出方式,提高了系统的处理速度,适合作为大规模实时系统的控制核心。

由测试模块输出的信号并行输入FPGA,FPGA通过程序设计控制A/D转换,并进行输出,但由于本设计对数据处理的速度要求不高,FPGA的高速处理的优势不能得到充分的体现,并且由于其集成度高,硬件量大、设计复杂且难度大,可能会影响完成任务的进度。

方案二:采用单片机(AT89C51)作为系统的控制核心。

实验五---集成运算放大器的参数测试

实验五 集成运算放大器的参数测试一、实验目的1、学会集成运放失调电压U IO 的测试方法。

2、学会集成运放失调电流I IO 的测量方法。

3、掌握集成运放开环放大倍数Aod 的测量方法。

4、学会集成运放共模抑制比K CMR 的测试方法。

二、实验仪器及设备1、DZX-1B型电子学综合实验台 一台2、XJ4323 双踪示波器 一台3、集成运放 uA741 一片 三、实验电路1、测量失调电压U IO 。

2、测量失调电流I IO 。

I IO =RR R U U O O ⎪⎪⎭⎫ ⎝⎛+-12121式中的U O1为测失调电压U IO 时的U O1 ,U O 2 为下面电路中测得的U O 。

U IO =211R R R+U O1R2 5.1KR2 5.1K3、测量开环放大倍数Aod 。

4、共模抑制比K CMR 。

注意:Ui 必须小于最大共模输入电压U iCM =12V四、实验内容及步骤 1、测量失调电压U IO(1) 按图接好电路,检查电路无误后接通电源,用示波器观察输出Uo 有无振荡,若有振荡,应采用适当措施加以消除。

(2) 测量输出电压,记做U O1,并计算失调电压U IO 。

2、测失调电流I IO(1) 按图接好电路,检查电路无误后接通电源,用示波器观察输出Uo 有无振荡,若有振荡,应采用适当措施加以消除。

(2) 测量输出电压,记做U O2,并计算失调电流I IO 。

3、测量开环放大倍数Rf 5.1KA Od =UiR R R U O 323+URf 5.1KK CMR = OCO A A d=UoU R R F i1•(1) 按图接好电路,接通电源。

(2) 在输入端加入Us =1V ,f =20Hz 的交流信号,用毫伏表测量Uo 和Ui ,计算出Aod 。

4、测量共模抑制比(1) 按图接好电路,接通电源。

(2) 在输入端加入一定幅值的频率为20Hz 的交流信号,用毫伏表测量Uo 和Ui ,计算出K CMR 。

设计报告-集成运放测试仪

集成运放参数测试仪摘要本系统参照片上系统的设计架构、采用FPGA与stm32相结合的方法,以stm32单片机为进程控制和任务调度核心;FPGA做为外围扩展,内部自建系统总线,地址译码采用全译码方式。

FPGA内部建有DDS控制器,单片机通过系统总线向规定的存储单元中送入正弦表;然后DDS控制器以设定的频率,自动循环扫描,生成高精度,高稳定的5Hz基准测量信号。

扫频信号通过对30MHz 的FPGA系统时钟进行分频和高速DA产生高频率稳定度、幅值稳定度的扫频信号。

放大器参数测量参照GB3442-82标准,信号幅度的测量通过AD536效值芯片转化为直流信号测得。

A/D转换TI 公司的高精度12逐次比较AD TLV2543。

stm32主要实现用户接口界面(键盘扫描、液晶显示、数据打印以及其他服务进程的调度)、AD转换以及测量参数(Vio Iio Kcmr Avd BWG Tr)计算、与上位机通信等方面的功能。

上位机主要实现向下位机发送测量指令、与下位机交换测量数据、以及数据的存储、回放、统计。

abstract:with reference to the system on a chip system design architecture, using the method of combining the FPGA with stm32 stm32 microcontroller as core process control and task scheduling; The FPGA as peripheral expansion, internal self-built system bus, address decoding adopts the whole decoding method. Built inside the FPGA DDS controller, single chip microcomputer to the specified storage unit through the system bus into sine table; Then DDS controller at a set frequency, the automatic cycle scan, generate high precision, high stability of 5 hz measuring signal. Frequency sweep signal by FPGA to 30 MHZ system clock frequency division and external phase-locked loop (FPGA using FLEX10K10 without internal phase-locked loop) multiple frequency, high frequency stability and frequency sweep signal amplitude stability. Amplifier parameters measurement reference GB3442-82 standard, the low frequency signal amplitude measurement take high-speed AD sampling, then digital processing method; The range of the high frequency signal directly measured using integrated RMS conversion chip. A/D conversion of TI company high-precision 12 successive comparative AD TLV2543. Achieve stm32 main user interfaces (keyboard scanning, LCD display, data printing, and other service process scheduling), AD transform and measurement parameters (Vio Iio Kcmr Avd BWG Tr) calculation, and the function of the upper machine communication, etc. PC main implementation down a machine to send instructions, and the lower machine exchange measurement data, and data storage, playback and statistics.关键词:参数测量运算放大器 DDS FPGA stm32数字信号处理一、方案比较设计与论证(一)测量电路模块1、测试信号源部分方案一:利用传统的模拟分立元件或单片压控函数发生器MAX038,可产生三角波、方波、正弦波,通过调整外围元件可以改变输出频率、幅度,但采用模拟器件由于元件分散性太大,即使用单片函数发生器,参数也与外部元件有关,外接电阻电容对参数影响很大,因而产生的频率稳定度较差、精度低、抗干扰能力差、成本也较高。

集成运放参数测试仪毕业设计论文

摘要集成运放测试仪是电子专业中一种常用的芯片测试设备。

目前,市场上出售的集成运放测试仪比较少,而且价格昂贵。

一般实验室都没有此类测试仪器。

本课题针对这种现状,特意研制一台质量优良、成本低廉的集成运放测试仪。

集成运放测试仪主要用于测试运放芯片的参数和功能。

本测试仪以STC12C5A60S2单片机作为控制核心,对运放测试电路的输入输出信号进行检测、处理,并将测试波形及参数显示到TFT彩屏上。

集成运放测试仪的研究遵循一般的电子作品研究过程:首先进行系统理论分析与方案设计;然后分模块设计、测试;最后进行系统调试、测试。

论文整体分为硬件设计和软件设计两大部分。

然后从系统角度将测试仪分为单片机控制部分,功能按键输入部分、显示部分、信号源部分、运放测试部分和电源部分分别进行介绍。

研究结果表明自行研制的集成运放测试仪简单、实用,能够满足大多数专业人员的要求。

测试仪摈弃了繁琐的功能,仅仅设置了四个按键、两种模式,并且采用TFT彩屏显示,方便专业人员观察测试结果。

同时,本测试仪还存在一些不足,如不能做到通用、电路设计不完善等,需要继续深入研究。

关键词集成运算放大器单片机芯片测试TFT彩屏AbstractIntegrated op-amp tester is a commonly used in electronic chip test equipment. At present, the market integration op-amp tester is less, and the price is high. General laboratory both does not have this kind of test equipment. This subject is based on the present situation, we have developed a good quality, low cost integrated op-amp tester.Integrated op-amp tester is used to test op-amp chip parameters and function. This tester is to STC12C5A60S2 single chip microcomputer as control core, the test circuit to put their input and output signal detection and treatment, and will test the waveform and parameter display to TFT colour screens. Integrated op-amp tester research following general electronic work study process: first system theory analysis and design; And then points module design, test; The last system commissioning, testing. The whole paper into hardware design and software design of two parts. And then from the system will be divided into single chip microcomputer control Angle tester part, the function of keystroke, display section, the signal source part, op-amp testing part and power supply part introduced respectively.The results of the study show that the developed by integrated op-amp tester is simple, practical, and can satisfy the requirements of most professionals. Ditched the function of trival tester, just set the four buttons, two kinds of patterns, and the TFT color display, convenient professional observation test results. Meanwhile, the tester still existed some shortage, such as general motors, cannot do circuit design is not perfect and so on, needs to continue to study. Key words integrated operational amplifier single-chip microcomputerchip test TFT colour screens目录第1章绪论 (1)1.1课题背景及国内外研究概况 (1)1.2集成电路测试仪概述 (2)1.3本课题的研究内容及研究意义 (2)1.3.1 本课题的研究内容 (2)1.3.2 本课题的研究意义 (2)第2章集成运放测试仪总体方案设计 (3)2.1集成运放测试仪测试参数选择 (3)2.1.1输入失调电压 (3)2.1.2 输入失调电流I IO (3)2.1.3 开环差模放大倍数Aod (4)2.1.4 共模抑制比KCMR (4)2.1.5 最大输出电压U OPP (5)2.2集成运放测试仪测试芯片选择 (5)2.2.1 OP07简介 (5)2.2.2 LM324简介 (6)2.2.3 LM358简介 (7)2.3集成运放测试仪整体设计 (8)2.3.1 集成运放测试仪系统结构图 (8)2.3.2 集成运放测试仪各部分说明 (9)第3章集成运放测试仪硬件设计 (12)3.1单片机控制部分 (12)3.2显示部分 (13)3.3信号源部分 (14)3.4运放测试部分 (16)3.5电源部分 (16)第4章集成运放测试仪软件设计 (17)4.1软件使用说明 (17)4.1.1 编程软件keil (17)4.1.2 目标程序下载软件STC_ISP_V483 (17)4.2软件设计说明 (17)4.2.1 整体软件流程图 (17)4.2.2 信号源(AD9850)部分软件设计 (19)4.2.3 TFT彩屏显示部分软件设计 (20)4.2.4 AD转换部分软件设计 (21)4.2.5 按键功能部分软件设计 (24)4.3小结 (24)第5章集成运放测试仪调试 (25)5.1集成运放测试电路调试 (25)5.2信号源模块调试 (27)5.3TFT彩屏模块调试 (28)5.4电源模块调试 (28)5.5整体调试 (29)第6章结论 (30)致谢 (31)参考文献 (32)附录..................................................................................................... 错误!未定义书签。

微机控制的集成运放参数测试仪

微机控制的集成运放参数测试仪

赵九捷;赵一群

【期刊名称】《电测与仪表》

【年(卷),期】1991(028)011

【总页数】3页(P28-30)

【作者】赵九捷;赵一群

【作者单位】不详;不详

【正文语种】中文

【中图分类】TN722.77

【相关文献】

1.基于GB3442-82的集成运放参数测试仪设计 [J], 刘宪力;田应伟

2.基于FPGA的集成运放参数测试仪 [J], 汪正勇;陈杨;汤强;张灿;陈万培;马志;张正华

3.集成运放参数测试仪 [J], 李白;舒鹏飞;杨静竹;陶启成

4.基于C8051F020的集成运放参数测试仪设计 [J], 郝玉君;甘露

5.基于C8051F020的集成运放参数测试仪设计 [J], 郝玉君; 甘露

因版权原因,仅展示原文概要,查看原文内容请购买。

全国大学生电子设计方案竞赛国家奖作品集锦(山东赛区)

目录

一、山东科技大学-单工无线呼叫系统1

二、海军航空工程学院-悬挂运动控制系统1

三、中国海洋大学-悬挂运动控制系统(1>1

四、中国海洋大学-悬挂运动控制系统(2>1

五、山大学-集成运放参数测试仪(1-1>1

六、山东大学-数控直流电流源(1-2>1

七、山东大学-悬挂运动控制系统(2-1>1

八、山东大学-数控直流电流源(2-2>1

九、山东大学-悬挂运动控制系统(2-3>1

一、山东科技大学-单工无线呼叫系统

二、海军航空工程学院-悬挂运动控制系统

三、中国海洋大学-悬挂运动控制系统(1>

四、中国海洋大学-悬挂运动控制系统(2>

五、山大学-集成运放参数测试仪(1-1>

六、山东大学-数控直流电流源(1-2>

七、山东大学-悬挂运动控制系统(2-1>

八、山东大学-数控直流电流源(2-2>

九、山东大学-悬挂运动控制系统(2-3>

更多资料请参加凌阳科技大学计划网站

凌阳科技大学计划刘传登整理。

集成运放参数测试仪的设计

湖北工业大学毕业设计(论文)题目集成运放参数测试仪的设计姓名与学号柯航 0 9 2 5 1 1 2 2 1 2指导老师张志强指导老师职称高级讲师年级专业班级机电一体化专业(2)班所在学院商贸学院摘 要该集成运放参数测试系统参照GB3442-82标准,采用辅助放大器测试集成运算放大器主要参数的方法,以单片机(AT89S55)为控制核心,结合可编程逻辑器件FPGA ,使用多量程自动切换的方式,实现了对通用集成运放V IO (输入失调电压)、 I IO (输入失调电流)、A VD (交流差模开环电压增益)、K CMR (交流共模抑制比)和BW G (单位增益带宽)的高精度自动测量,使用128*128液晶显示、打印测量结果。

在自制测试A VD 、 K CMR 信号源部分,采用DDS(直接数字式频率合成)技术,合成高稳定度5Hz 参数测量正弦信号;并在测试参数BW G 时,使用 DDS 专用芯片AD9851,合成40kHz 至4MHz 扫频信号源。

整个系统集成度高,具有友好人机交互界面。

关键字: 集成运算放大器 参数测试 DDSAbstractThe paper is entitled “based on the stepping motors P89C51RA Movement ControlSystem Applications and Research“,which suggest the use of stepper motors governor SCC(Single chip computer) control through click on stepper motors to achieve,then carrying outto stop to the start of the stepper motor,positive and negative turn、accelerate、deceleratiaon,such as the slowdown in movement control.System using Philips series SCC,Protel DXP uVision2 development tools and development environment,with the basic language machines,compiled language for system conteol. In real-time detection and automatic control SCC applications,SCC as a core component to use only SCC knowledge is not enough and should be based on specific hardware structure,the specific characteristics of the target application and integration software to further improve.Text first introduces the working principle of stepper motor,embedded microcontroller development tools and development environment;Focus described system hardware to design,including the ISP circuit,keyboards show circuit,driving circuit hardware to achieve until the final hardware debugging,and attached to circuit theory,and the current design of the equipment used to the work and principles of the realization of functions.Keywords:Single chip computer stepper motors P89C51RA目录摘要 (I)Abstract (II)目录 (III)引言 (1)1、方案论证与选择 (2)1.1.题目任务要求 (2)1.1.1、任务 (2)1.1.2.1基本要求 (2)1.2 题目任务分析 (3)1.3 方案的比较选择与论证 (3)1.3.1 测试信号产生方案: (3)1.3.2 运放参数测量电路方案 (5)2、系统总体设计与实现 (7)2.1 系统总体设计 (7)2.2总体实现框图 (7)3、理论分析与计算 (8)3.1 运放参数测量电路设计 (8)3.1.1 标准测量电路的设计: (9)3.1.2 系统自动测量电路的设计: (9)V的测量: (9)3.1.2.1输入失调电压IOI的测量 (10)3.1.2.2输入失调电流IOA的测量: (11)3.1.2.3差模开环交流电压增益VDK的测量 (12)3.1.2.4共模抑制比CMR3.1.2.5. 3dB带宽的测量 (13)3.2 DDS的实现 (13)3.2.1 DDS实现理论分析 (13)4.1 信号源产生电路设计: (15)4.1.1 D/A转换电路 (15)4.1.2、低通滤波电路 (16)4.1.3 AD9851产生扫频信号电路图 (17)4.1.3.1 .1AD9851原理及扫频输出实现 (17)4.1.3.2 AD9851电路设计 (18)4.1.3.3滤波电路设计 (18)4.2 AGC电路与设计: (19)4.2.1 AGC电路设计 (19)4.2.2 后级放大电路设计 (20)4.3信号采集处理电路 (20)4.3.1AD637峰值检波电路 (20)4.3.3 放大电路 (22)4.3.4 A/D转换电路 (23)5. 系统软件设计 (24)5.1 FPGA设计 (24)5.1.1 AD9851扫频模块 (24)5.1.2.MAX197采样模块 (24)5.1.3.LCD显示模块以及键盘扫瞄模块 (25)5.1.4 DDS信号产生模块 (25)5.1.5继电器与程控放大控制模块 (26)5.2单片机设计部分 (26)6系统调试及测试数据与分析 (28)6.1测试条件 (28)6.2 测试方法及测试结果 (28)6.3测试数据分析 (29)6.4抗干扰措施 (29)结束语 (30)参考文献 (32)致谢 (33)绪论集成运放以其价格低廉.性能优越等特点在个人数据助理.通讯.汽车电子.音响产品.仪器仪表.传感器等领域得到广泛应用。

2005年全国大学生电子设计大赛(A题:正弦信号发生器)

2005年全国大学生电子设计大赛A题:正弦信号发生器目录1.A组题1 (2)2.A组题2 (17)3.A组题3 (32)4.A组题4 (41)5.A组题5 (86)正弦信号发生器1华南理工大学电子与信息学院摘要这个正弦信号发生器利用最新的频率合成技术,实现了1KHz~30MHz的正弦波输出,频率步进可达到1Hz,可输出调制度可调的AM信号,5KHz、10KHz 最大频偏的FM信号,100KHz固定频率载波、码速10kbps的PSK,ASK信号。

采用了超宽带、超低噪声的高速运放,提高了输出电压的幅度。

整个系统以ADuC841为控制中心,有很高的精确度和稳定度。

双CPU结构,大大增强了信息的处理能力;行列式键盘输入,大屏幕LCD输出,操作简便,人机界面友好。

AbstractThis sine wave generator, based on the DDS new technique, can generate a sine wave with a frequency ranging from 1KHz to 30MHz,which has a frequency step of 1Hz!The system can also output an AM signal with an adjustable modulation index, an FM signal with a frequency deviation of 5kHz or 10kHz, controlled by the keyboard input. Meanwhile it has a function of outputting PSK or ASK signals, with a code rate of 10kps and 100KHz carrier. Applying the low noise, high speed ,wide pass band Op Amp, increases the output voltage amplitude. The whole system has anADuC841 as its controller center, which provides a high precision and stabilization. Two CPUs enhance the ability of processing. Matrix keyboard and large screen LCD display provide a friendly interface, which makes the operating more easy.一、方案设计与论证1.1 方案比较本题目的要求是设计一个正弦信号发生器,并且能够输出模拟幅度调制(AM)信号,模拟频率调制(FM)信号,二进制PSK、ASK信号。

基于C8051F020的集成运放参数测试仪设计

Ab t a t C 0 1 0 0 mir c n ml rb s d c o e - o p o e a in la l e e in p r me e so e ts se , s sr c : 8 5 F 2 c o o t l a e l s d lo p r t a mp i rd sg a a t r ft s y t ms t t e o i f e meh d sn u i a y o mp, a h p a n u f e o tg ip to s tc re td f r n il mo e e c a g n to su iga xl r pa i c n t e o mp i p to s t l e, u f e u r n , i e e t — d x h n e a d v a n a

Hale Waihona Puke 为核心 , 运用辅助运算放大器法测量集成运算放 大器的参数 , 设计 出具有 自动量程转 换、 自动测量功能的集成运放参数测

试 仪 。 [

抑制 自激 现象的发生 。C 3 C 1 , 7的值 由实验获得 , 将数百皮法

2015全国大学生电子设计大赛F题一等奖--数字频率计

2015 年全国大学生电子设计竞赛全国一等奖作品设计报告部分错误未修正,软件部分未添加竞赛选题:数字频率计(F 题)摘要本设计选用FPGA 作为数据处理与系统控制的核心,制作了一款超高精度的数字频率计,其优点在于采用了自动增益控制电路(AGC)和等精度测量法,全部电路使用P CB 制版,进一步减小误差。

AGC 电路可将不同频率、不同幅度的待测信号,放大至基本相同的幅度,且高于后级滞回比较器的窗口电压,有效解决了待测信号输入电压变化大、频率范围广的问题。

频率等参数的测量采用闸门时间为1s 的等精度测量法。

闸门时间与待测信号同步,避免了对被测信号计数所产生±1 个字的误差,有效提高了系统精度。

经过实测,本设计达到了赛题基本部分和发挥部分的全部指标,并在部分指标上远超赛题发挥部分要求。

关键词:FPGA 自动增益控制等精度测量法目录摘要 (1)目录 (2)1. 系统方案 (3)1.1. 方案比较与选择 (3)宽带通道放大器 (3)正弦波整形电路 (3)主控电路 (3)参数测量方案 (4)1.2. 方案描述 (4)2. 电路设计 (4)2.1. 宽带通道放大器分析 (4)2.2. 正弦波整形电路 (5)3. 软件设计 (6)4. 测试方案与测试结果 (6)4.1. 测试仪器 (6)4.2. 测试方案及数据 (7)频率测试 (7)时间间隔测量 (7)占空比测量 (8)4.3. 测试结论 (9)参考文献 (9)1. 系统方案1.1. 方案比较与选择宽带通道放大器方案一:OPA690 固定增益直接放大。

由于待测信号频率范围广,电压范围大,所以选用宽带运算放大器 OPA690,5V 双电源供电,对所有待测信号进行较大倍数的固定增益。

对于输入的正弦波信号,经过 OPA690 的固定增益,小信号得到放大,大信号削顶失真,所以均可达到后级滞回比较器电路的窗口电压。

方案二:基于 VCA810 的自动增益控制(AGC)。

2005年电子大赛一等奖 悬挂运动控制系统2

悬挂运动控制系统[2005年电子大赛一等奖]文章来源:凌阳科技教育推广中心作者:浙江大学杜维张建敏陈勋发布时间:2006-5-26 18:21:59摘要:本系统采用凌阳16位单片机(SPCE061A)作为悬挂控制系统的检测和控制核心,实现通过人机界面对物体所作运动进行设定,通过LCD实时显示此时画笔所在的坐标值;系统具有可画出相应的运动轨迹,可自动跟踪曲线运动,语音播报是否完成任务等功能。

运动参数的设定通过无线键盘输入,系统通过比较当前画笔所在位置与设定位置的差异以及运动类型,控制步进电机完成相应运动;曲线的跟踪采用红外传感器来实现;语音播报采用凌阳单片机自带的语音模块来实现;在软件控制上采用了Divide & Conquer 和"探测、预测"相结合的方法把画笔所要作的复杂运动分解成简单的直线运动,然后控制电机实现。

关键字:Divide & Conquer、步进电机、红外传感、SPCE061A一、方案论证根据题目要求,系统由图1.1中模块组成。

图1.1 系统模块框图1、控制器模块方案一:采用ATMEL公司的AT89C51作为控制器的方案。

单片机运算能力强,软件编程灵活,自由度大。

但是如果系统需要增加语音播放功能,还需外接语音芯片,实现较为复杂。

另外51单片机需要仿真器来实现软硬件调试,较为烦琐。

方案二:采用SPCE061A单片机来实现,此单片机内置8路10位ADC和2路DAC,避免了外接A/D转换芯片和D/A转换芯片,并且I/O接口比较多,易于扩展外围电路,开发板集成了语音播报的硬件,通过软件编程即可以用于语音采集和播报。

集成开发环境中配有很多语音API函数,实现语音播放比较简单,另外方便的是该芯片内置在线仿真,编程接口,可以方便实现在线调试,这大大简化了系统的开发和调试的复杂度。

2、曲线跟踪模块方案一:通过开关型霍尔传感器来实现,但是由于该方法只能跟踪磁性物质组成的曲线,成本高、安装起来比较麻烦,而且容易受环境中磁性物质的干扰,抗干扰性能不好。

集成运放参数测试仪设计报告

集成运放参数测试仪摘要:本集成运放参数测试仪以MSC-51单片机为核心,由被测电路、信号源、0809A/D转换器、液晶显示器、键盘等组成。

采用DDS芯片AD9835产生40kHz~4MHz扫频信号和5Hz的输入信号,它能对LM358及与之引脚兼容的其他集成运放(例如LM353、LM741)的基本参数VIO 、IIO、AVD、KCMR及BWG进行测试和数字显示。

关键字:集成运放;单片机;DDS一、系统方案设计1.方案论证与选择(1)信号源部分方案一:利用函数发生器,可产生三角波、方波、正弦波。

通过调整外围元件可以改变输出频率、幅度,但采用模拟器件由于元件分散性太大,即使用单片函数发生器,参数也与外部元件有关,外接电阻电容对参数影响很大,因而产生的频率稳定度较差、精度低、抗干扰能力差。

方案二:采用锁相式频率合成方案。

锁相式频率合成是将一个高稳定度和高精度的标准频率经过运算,产生同样稳定度和精确度的大量离散频率的技术,他在一定程度上满足了既要频率稳定精确,又要在大范围内变化的矛盾。

但其波形幅度稳定度较差,在低频内波形不理想。

方案三:采用直接数字频率合成(DDS)技术。

由于DDS采用全数字方式实现频率合成,直接对参考正弦波时钟进行抽样和数字化,然后通过数字计算技术进行频率合成,因此具有模拟频率合成技术无法比拟的优点。

DDS不仅频率转换速率快、频率分辨率高、相位噪声低、输出相位可连续变化,而且易编程,体积小、功耗低。

DDS直接频率合成器件的诸多优点使其逐渐成为未来信号源发展方向。

方案拟采用DDS专用集成芯片AD9835。

它的串行控制方式,使电路简单、编程方便;内部有一个32位相位累加器,用于存放频率控制字,可实现1Hz的频率调节。

我们需要5Hz的单一稳定频率,要求其频率,幅度稳定。

综合考虑,我们采用方案三,实现了高精度,高稳定度的5Hz测试信号源。

(2)信号采集模块方案一:用AD736 RMS真有效值转换芯片,AD736的响应频率在0~10KHZ,采用该器件只需将被测的信号加到它的输入端上,就可以得到它的有效值,无需软件处理,测试非常的方便。

集成运放参数测试仪

目录一.方案比较与论证-----------------------------------------------3二.理论与分析计算-----------------------------------------------4三.电路图及设计文件--------------------------------------------6 1.硬件实现-----------------------------------------------------6 2.软件实现-----------------------------------------------------8四.测试数据与结果分析-----------------------------------------9五.参考文献--------------------------------------------------------9六.附录-------------------------------------------------------------10附录A测试仪器---------------------------------------------10附录B参考文献--------------------------------------------10附录C软件程序--------------------------------------------10集成运放参数测试仪摘要:此集成运放测试仪采用“辅助放大器”的测量方法,能测试V IO(输入失调电压)、I IO(输入失调电流)、A VD(交流差模开环电压增益)和K CMR(交流共模抑制比)四项基本参数,符合了题目的要求。

可对各种通用型集成运放主要参数进行测量,具有较好的精度,稳定度和测量范围。

本设计由四个模块电路组成:集成运放参数测试电路、信号源发生电路、单片机控制电路、显示与键盘电路。

一实验目的熟悉由集成运算放大器组成的反相比例运算电市名师优质课赛课一等奖市公开课获奖课件

R3 = RF 时, 输出为:

(1.8.5)

电路实现了对 vi2 和 vi1 加权相减。当满足R1 =R2 =R3= RF 条件时,输 出为:当R1 =R2、R3 = RF 时, 输出为:电路实现了对 vi2 和 vi1 加权相 减。当满足R1 =R2 =R3= RF 条件时,输出为这时,电路实现了对输入信 号 vi2 和 vi1 直接相减关系。

试验8 集成运算放大器组成基 本运算电路

一 试验目标

1. 熟悉由集成运算放大器组成反相百分比运算电路、同相 百分比运 算电路、加法运算电路、减法运算电路、积分 运算电路。

2. 验证以上几个电路性能,掌握它们调试方法。

1/17

二 试验原理

1. 关于运算放大器

集成运算放大器实际上是高增益多级直流放大器。在其输出端和输入端之 间接入不一样负反馈网络,就能实现各种不一样电路功效。本试验只讨论由 运算放大器组成信号放大和模拟运算电路。

5/17

由 F007 组成反相百分比运算电路如图 1.8.2 所表示:

3. 同相百分比运算电路

同相百分比运算电路如图 1.8.3 所表示。其闭环增益为:

同相百分比运算电路属电压串联负反馈,含有输入阻抗高,输出 阻抗低特点。在多级放大电路中,常做缓冲或隔离级。尤其是当 R1 开路RF 短路时,同相放大器就变成了同相跟随器。其用途与射极 跟随器相同。

3. 绘制积分运算和微分运算试验中输入、输出波形。

17/17

15/17

4. 积分运算电路

(1) 调零 按照图 1.8.6 接好电源并调零。 (2) 输入频率为 1kHz 、幅度为 1V 方波信号,用示波器观察输出信号 v0 波形。

5. 微分运算电路

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

集成运放参数测试仪[2005年电子大赛一等奖]摘要:本系统参照片上系统的设计架构、采用FPGA与SPCE061A相结合的方法,以SPCE061A单片机为进程控制和任务调度核心;FPGA做为外围扩展,内部自建系统总线,地址译码采用全译码方式。

FPGA内部建有DDS控制器,单片机通过系统总线向规定的存储单元中送入正弦表;然后DDS控制器以设定的频率,自动循环扫描,生成高精度,高稳定的5Hz基准测量信号。

扫频信号通过对30MHz的FPGA系统时钟进行分频和外部锁相环(FPGA采用FLEX10K10无内部锁相环)倍频,产生高频率稳定度、幅值稳定度的扫频信号。

放大器参数测量参照GB3442-82标准,低频信号幅度的测量采取AD高速采样,然后进行数字处理的方法;高频信号的幅度直接采用集成有效值转换芯片测得。

A/D 转换采用SPCE061A内部自带的10位AD。

SPCE061A主要实现用户接口界面(键盘扫描、液晶显示、数据打印以及其他服务进程的调度)、AD转换以及测量参数(Vio Iio Kcmr Avd BWG Tr)计算、与上位机通信等方面的功能。

上位机主要实现向下位机发送测量指令、与下位机交换测量数据、以及数据的存储、回放、统计。

关键词:参数测量运算放大器 DDS FPGA SPCE061A 数字信号处理一、方案比较设计与论证(一)测量电路模块1、测试信号源部分方案一:利用传统的模拟分立元件或单片压控函数发生器MAX038,可产生三角波、方波、正弦波,通过调整外围元件可以改变输出频率、幅度,但采用模拟器件由于元件分散性太大,即使用单片函数发生器,参数也与外部元件有关,外接电阻电容对参数影响很大,因而产生的频率稳定度较差、精度低、抗干扰能力差、成本也较高。

方案二:采用锁相式频率合成方案。

锁相式频率合成是将一个高稳定度和高精度的标准频率经过运算,产生同样稳定度和精确度的大量离散频率的技术,他在一定程度上满足了既要频率稳定精确,又要在大范围内变化的矛盾。

但其波形幅度稳定度较差,在低频内波形不理想。

方案三:采用DDS技术。

DDS以Nyquist时域采样定理为基础,在时域内进行频率合成,其相位、幅度都可以实现程控,而且用FPGA来实现非常简单。

在这里我们只需要一个5Hz的单一稳定频率,要求其频率,幅度稳定。

综合考虑,我们采用方案三,实现了高精度,高稳定度的5Hz测试信号源。

2、主测试电路方案一:将测试放大器参数的实现分成4个电路检测。

该方案实现各个参数的测量比较好,且有利于各个参数调试。

但是对于要实现智能测试该方案较复杂,在电路中所用的继电器太多,很容易引起电磁干扰,不利于系统的整体性能提高,且不能实现电路的智能测试。

方案二:采用一级运放。

该电路经过仔细的分析会发现它设计的非常的巧妙调试也很方便,不会产生自激、饱和等情况。

缺点就是对与精度较高的运算放大器该方案实现不了。

方案三:采用试题中所给的电路。

这是一个二级的电路,测试精度非常的高。

但在调试中我们发现它很容易出现自激,为了使整个电路保持稳定,我们采取了一系列的稳定措施,如采用雕刻机雕刻线路,并实现大面积的接地,辅助运放加入补偿矫正网络等。

综合上述,为了实现自动测量,保证测试有更高的精度,采用方案三。

3、信号放大电路方案一:采用普通的运算放大器放大电路。

运算放大器放大电路成熟可靠,选用不同的运算放大器,能够对各种信号进行很好放大。

但其放大值固定,不能动态调整,不便于处理大范围变化信号。

方案二:采用程控可增益放大器。

程控可增益放大器可用单片机方便的进行增益设定,十分有利于处理大动态范围信号。

由于测量信号动态范围大,要有效的采样处理,就要求放大器增益可动态调整,由此我们选用方案二,采用可编程增益放大器AD625和数字电位器AD737组成程控增益放大器,实现对测量信号的有效放大。

4、滤波电路方案一:采用二阶切比雪夫低通滤波器或二阶巴特沃斯低通滤波器。

切比雪夫滤波器的幅度响应在通带内是在两值之间波动,在通带内波动的次数取决于滤波器的阶数。

理想的在靠近截止频率的范围内比巴特沃斯有更接近矩形的频率响应。

但这一点是一在频带内允许波动为代价的。

巴特沃斯低通滤波器幅频响应是单调下降的,其N阶低通滤波器的前(2N-1)阶导数在频率为零处始终为零,故又称为最大平坦幅度滤波器。

方案二:采用数字滤波。

数字滤波有极大的灵活性,可以在不增加任何硬件成本的基础上对信号进行有效的滤波,而且可以实现模拟器件难以实现的高阶滤波。

但要进行高效率的滤波,对AD采样要求有较高的采样速率和时实性,对单片机要求有较高的数据运算速度。

方案三:采用模拟滤波器加数字滤波。

先用模拟滤波器对信号进行简单的滤波处理,然后AD采样,进行数字滤波。

这样既可以更加有效的对信号进行滤波,使有效信号更为纯净,便于后级数据处理,又降低了对ADC及单片机的要求,使得利用SPCE061A可以较轻松的实现在本题中,测量输出有效信号同样为5Hz,但伴有大量的高频及较严重的50Hz工频干扰,为了保持通带内有效信号的平坦性及纯净,我们选用方案三,模拟用二阶巴特沃斯低通滤波器,数字滤波采用有限冲击响应法设置了低通滤波器及50Hz陷波器。

(二)信号采集模块方案一:用AD736 RMS真有效值转换芯片,AD736的响应频率在0~10KHZ,采用该器件只需将被测的信号加到它的输入端上,就可以得到它的有效值,无需软件处理,测试非常的方便。

但是我们在调试中现在AD736 在响应低频的时候不是很稳定,这样对整个系统会带来不稳定。

因此我们没有选用这个方案。

方案二:采用A/D转换,将模拟信号数字化,然后进行数据处理。

凌阳16位单片机内置有8路10位的A/D,运用起来非常的方便。

无需外围的电路,转换精度也比较高,因此我们采用了方案二。

(三)用户接口模块1、显示方案:方案一:采用LED或字符型LCD显示。

LED可以用移位寄存器74164或者专用芯片MAX7219驱动,字符型LCD也可以才用74LS164通过同步串口驱动。

优点是控制比较简单,而且串行显示只占用很少的I/O口。

但也有一个很大的缺点,只能显示一些简单的ASCII码字符,显示的信息量十分的有限,对于本系统较复杂的功能不太适合。

方案二:采用点阵型LCD显示。

点阵型LCD虽然占用的I/O口资源较多,控制也较复杂,但其功能却是强大的,显示信息量大,可以保证良好的用户模式。

且我们在系统中用FPGA设计的总线方式,扩展了I/O资源,就无须考虑I/O资源的限制了。

经过综合考虑我们选择方案二,不需要很复杂的电路就可以实现并扩展非常强大的显示功能。

2、键盘输入方案:方案一:采用7289芯片与键盘相结合,键盘的整个控制只需4条控制线。

程序的编写也比较简单且容易同LED显示接口。

方案二:不使用任何专用芯片,用一块74LS138译码输出8路扫描信号,3路扫描返回信号线接I/O口输入(我们设计的是3*8的键盘)。

这种设计方案电路设计非常的简单,但是软件的编写要考虑软件去抖等,会比较复杂而且占用大量的CPU资源。

方案三:在FPGA内部构造一键盘扫描控制器,专门用以处理按键信息,并进行初步的处理(如键盘去抖),通过中断把键值发送给单片机。

由于我们在FPGA内部已经建立了系统总线,扩展键盘非常简单。

而且采用此方法外部硬件电路的设计也非常简单。

比较三者的优缺点我们选择了方案三,这样充分利用CPLD的功能硬件与软件设计都比较简单。

二、整机工作原理与功能实现图2-1-1 系统整体结构示意图系统电路原理图如图5-3-1所示。

通过继电器的切换实现四个基本参数和大量程的转换。

测量开环放大倍数和共模抑制比的基准信号采用DDS合成技术产生(DDS合成控制器通过硬件编程在FPGA内部生成)。

信号的幅值通过精密整流后的响应信号高速采样,再经过数字信号处理的方法获得。

采样信号的幅值测量采用等精度测量方法,通过程控放大器将采样信号的幅度控制在1-3.3V之间,这样可以使小信号测量时有效位数增多,又克服了测量大信号量程不足的限制。

-3dB带宽的测量,通过FPGA与外部锁相环对30MHz信号进行分频与倍频,产生高精确度的扫频信号,然后通过隔直电容加到被测放大器的同相输入端(放大器通过继电器切换接成单位增益组态),放大器的输出信号通过隔直电容加到有效值转换芯片的输入端。

扫频信号从40kHz开始逐渐增大,同时通过AD检测有效值转换芯片的输出电压,当输出电压下降到原来的0.707倍时记下此时的频率值既是-3dB带宽截止频率。

上升时间的测量,单片机向某一特定地址中写入任意值,启动上升时间测量功能。

接着FPGA输出一阶跃信号给被测放大器(被测放大器也接成单位增益组态),同时启动高速计数,放大器的输出信号送给一比较电平设为0.9Vdd的高速比较器,当放大器输出端的信号增大到0.9Vdd时比较器输出高电平,FPGA内部计数器停止计数。

如图2-1-2根据此计数值和计数时钟的频率便可以得到上升时间。

图2-2-1无操作系统与有操作系统的区别设计到很多的硬件、软件及其混合的设计。

采用操作系统的架构来组织,将非常有利于我们小组各个成员之间的协作开发。

有的人专注于服务进程以及用户界面和数据处理,有人专注于FPGA系统总线和外围器件以及底层驱动程序的设计。

Mini OS是一款拥有可裁剪、多任务的占先式内核的操作系统。

它的任务调用及中断时间是可知道的,因此,采用Mini OS操作系统将大幅改善软件设计的环境,提高软件设计的规范。

且该系统的底层模块完全采用汇编语言编写,然后采用操作系统调度的方法,很大程度上提高了系统的实时性和执行效率。

如图2-2-2图2-2-2 Mini OS 各进程示意图(三)其他系统扩展1、语音播报方案为了丰富人机的接口我们增加了语音的播报利用凌阳SPCE061位单片机的语音处理功能。

只须调用库函数即可以实现音频编程或自己录制语音资源就可以实现语音播放以及语音报警功能。

2、打印功能为了能够将测量数据打印出来,我们采用了TL58打印机,该打印机小型、轻便、我们使用并口打印,控制也非常的方便。

它带国家一、二级字库,可以满足一般打印的需求。

3、串口通信功能为了适应网络化的趋势,为了能够进行大批量的数据统计与分析我们设计了此与上位机进行通讯的串行数据接口。

我们可以通过此串行接口,将一批运放的测量参数上传到上位机,然后进行统计分析,对这一批运放的性能参数给出有效的估计。

这在实际的科研、生产中比只测量一两个放大器的参数具有更大的意义。

我们还可以通过上位机控制下位机测量相应的参数,并在显示屏上显示下位机无法显示的参数(如波特图、对正弦信号相应的频谱)具有虚拟仪器的功能。

三、各子模块的设计(一)输入电压4~40mV、输入电流0~4mA量程转换:量程转换通过继电器和程控放大器相结合实现。