10.9W双通道任意限幅功放IC HT876_Datasheet_V0.6

高精度10V参考电源AD587说明书

FUNCTIONAL BLOCK DIAGRAMREV.CInformation furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.aHigh Precision 10 V ReferenceAD587One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: 617/329-4700Fax: 617/326-8703FEATURESLaser Trimmed to High Accuracy:10.000 V ؎5 mV (L and U Grades)Trimmed Temperature Coefficient:5 ppm/؇C max, (L and U Grades)Noise Reduction CapabilityLow Quiescent Current: 4 mA max Output Trim CapabilityMIL-STD-883 Compliant Versions AvailablePRODUCT HIGHLIGHTSser trimming of both initial accuracy and temperature coefficients results in very low errors over temperature with-out the use of external components. The AD587L has amaximum deviation from 10.000 V of ±8.5 mV between 0°C and +70°C, and the AD587U guarantees ±14 mV maximum total error between –55°C and +125°C.2.For applications requiring higher precision, an optional fine trim connection is provided.3.Any system using an industry standard pinout 10 volt refer-ence can be upgraded instantly with the AD587.4.Output noise of the AD587 is very low, typically 4 µV p-p. A noise reduction pin is provided for additional noise filtering using an external capacitor.5.The AD587 is available in versions compliant with MIL-STD-883. Refer to the Analog Devices Military Products Databook or current AD587/883B data sheet for detailed specifications.PRODUCT DESCRIPTION The AD587 represents a major advance in the state-of-the-art in monolithic voltage references. Using a proprietary ion-implanted buried Zener diode and laser wafer trimming of high stability thin-film resistors, the AD587 provides outstanding perfor-mance at low cost.The AD587 offers much higher performance than most other 10 V references. Because the AD587 uses an industry standard pinout, many systems can be upgraded instantly with the AD587. The buried Zener approach to reference design pro-vides lower noise and drift than bandgap voltage references. The AD587 offers a noise reduction pin which can be used to further reduce the noise level generated by the buried Zener.The AD587 is recommended for use as a reference for 8-, 10-,12-, 14- or 16-bit D/A converters which require an external precision reference. The device is also ideal for successiveapproximation or integrating A/D converters with up to 14 bits of accuracy and, in general, can offer better performance than the standard on-chip references.The AD587J, K and L are specified for operation from 0°C to +70°C, and the AD587S, T and U are specified for –55°C to +125°C operation. All grades are available in 8-pin cerdip. The J and K versions are also available in an 8-pin Small Outline IC (SOIC) package for surface mount applications, while the J, K and L grades also come in an 8-pin plastic package.NOISE V OUTTRIMGNDNOTE:PINS 1,3 AND 7 ARE INTERNAL TEST POINTS.NO CONNECTIONS TO THESE POINTS.AD587–SPECIFICATIONS(T A = +25؇C, V IN = +15 V unless otherwise noted)Model AD587J/S AD587K/T AD587L/UMin Typ Max Min Typ Max Min Typ Max Units OUTPUT VOLTAGE9.99010.0109.99510.0059.99510.005VOUTPUT VOLTAGE DRIFT10°C to +70°C20105ppm/°C –55°C to +125°C20105GAIN ADJUSTMENT+3+3+3%–1–1–1LINE REGULATION113.5 V ≤ + V IN≤ 36 VT MIN to T MAX100100100±µV/VLOAD REGULATION1Sourcing 0 < I OUT < 10 mAT MIN to T MAX100100100±µV/mA Sourcing –10 < I OUT < 0 mA2T MIN to T MAX100100100QUIESCENT CURRENT242424mAPOWER DISSIPATION303030mWOUTPUT NOISE0.1 Hz to 10 Hz444µV p-pSpectral Density, 100 Hz100100100nV/√HzLONG-TERM STABILITY151515±ppm/1000 Hr. SHORT-CIRCUIT CURRENT-TO-GROUND305030503050mASHORT-CIRCUIT CURRENT-TO-V IN305030503050mA TEMPERATURE RANGESpecified Performance (J, K, L)0+700+700+70°COperating Performance (J, K, L)3–40+85–40+85–40+85Specified Performance (S, T, U)–55+125–55+125–55+125Operating Performance (S, T, U)3–55+125–55+125–55+125NOTES1Spec is guaranteed for all packages and grades. Cerdip packaged parts are 100% production test.2Load Regulation (Sinking) specification for SOIC (R) package is ±200 µV/mA.3The operating temperature ranged is defined as the temperatures extremes at which the device will still function. Parts may deviate from their specified performance outside their specified temperature range.Specifications subject to change without notice.ORDERING GUIDEInitial Temperature Temperature PackageModel1Error Coefficient Range Options2AD587JQ10 mV20 ppm/°C0°C to +70°C Q-8AD587JR10 mV20 ppm/°C0°C to +70°C SO-8AD587JN10 mV20 ppm/°C0°C to +70°C N-8AD587KQ 5 mV10 ppm/°C0°C to +70°C Q-8AD587KR 5 mV10 ppm/°C0°C to +70°C SO-8AD587KN 5 mV10 ppm/°C0°C to +70°C N-8AD587LQ 5 mV 5 ppm/°C0°C to +70°C Q-8AD587LN 5 mV 5 ppm/°C0°C to +70°C N-8AD587SQ10 mV20 ppm/°C–55°C to +125°C Q-8AD587TQ10 mV10 ppm/°C–55°C to +125°C Q-8AD587UQ 5 mV 5 ppm/°C–55°C to +125°C Q-8AD587JCHIPS10 mV20 ppm/°C0°C to +70°CNOTES1For details on grade and package offerings screened in accordance with MIL-STD-883, refer to theAnalog Devices Military Products Databook or current AD587/883B data sheet.2N = Plastic DIP; Q = Cerdip; SO = SOIC.–2–REV. CAD587REV. C –3–ABSOLUTE MAXIMUM RATINGS*V IN to Ground . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36 V Power Dissipation (+25°C) . . . . . . . . . . . . . . . . . . . . .500 mW Storage Temperature . . . . . . . . . . . . . . . . . . .–65°C to +150°C Lead Temperature (Soldering, 10 sec) . . . . . . . . . . . . .+300°C Package Thermal ResistanceθJC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22°C/W θJA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .110°C/W Output Protection: Output safe for indefinite short to ground and momentary short to V IN .*Stresses above those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.DIE SPECIFICATIONSThe following specifications are tested at the die level for AD587JCHIPS. These die are probed at +25°C only.(T A = +25°C, V IN = +15 V unless otherwise noted)AD587JCHIPS Parameter Min Typ Max UnitsOutput Voltage 9.99010.010V Gain Adjustment –13%Line Regulation13.5 V < + V IN < 36 V 100±µV/V Load RegulationSourcing 0 < I OUT < 10 mA 100µV/mA Sinking –10 < I OUT < 0 mA 100µV/mA Quiescent Current24mA Short-Circuit Current-to-Ground 50mA Short-Circuit Currrent-to-V OUT50mANOTES 1Both V OUT pads should be connected to the output.2Sense and force grounds must be tied together.Die Thickness:The standard thickness of Analog Devices Bipolar dice is 24 mils ± 2 mils.Die Dimensions: The dimensions given have a tolerance of ±2 mils.Backing : The standard backside surface is silicon (not plated). Analog Devices does not recommend gold-backed dice for most applications.Edges: A diamond saw is used to separate wafers into dice thus providing perpendicular edges half-way through the die.In contrast to scribed dice, this technique provides a more uniform die shape and size . The perpen-dicular edges facilitate handling (such as tweezer pick-up) while the uniform shape and size simplifies substrate design and die attach.Top Surface: The standard top surface of the die is covered by a layer of glassivation . All areas are covered except bonding pads and scribe lines.Surface Metalization: The metalization to Analog Devices bipolar dice is aluminum. Minimum thickness is 10,000Å.Bonding Pads: All bonding pads have a minimum size of 4 mils by 4 mils. The passivation windows have 3.5 mils by 3.5 mils minimum.DIE LAYOUTPIN CONFIGURATIONTP *TRIMV OUTTP *NOISEREDUCTION+V IN TP *GND *TP DENOTES FACTORY TEST POINT. NO CONNECTIONS SHOULD BE MADE TO THESE PINS.Die Size: 0.081 × 0.060 InchesAD587REV. C–4–THEORY OF OPERATIONThe AD587 consists of a proprietary buried Zener diode refer-ence, an amplifier to buffer the output and several high stability thin-film resistors as shown in the block diagram in Figure 1.This design results in a high precision monolithic 10 V output reference with initial offset of 5 mV or less. The temperature compensation circuitry provides the device with a temperature coefficient of under 5 ppm/°C.NOISE V OUTTRIM GNDNOTE:PINS 1,3 AND 7 ARE INTERNAL TEST POINTS.NO CONNECTIONS TO THESE POINTS.Figure 1.AD587 Functional Block Diagram A capacitor can be added at the NOISE REDUCTION pin (Pin 8) to form a low-pass filter with R S to reduce the noise contribu-tion of the Zener to the circuit.APPLYING THE AD587The AD587 is simple to use in virtually all precision reference applications. When power is applied to Pin 2, and Pin 4 is grounded, Pin 6 provides a 10 V output. No external compo-nents are required; the degree of desired absolute accuracy is achieved simply by selecting the required device grade. The AD587 requires less than 4 mA quiescent current from an oper-ating supply of +15 V.Fine trimming may be desired to set the output level to exactly 10.000 V (calibrated to a main system reference). System cali-bration may also require a reference voltage that is slightly differ-ent from 10.000 V, for example, 10.24 V for binary applications.In either case, the optional trim circuit shown in Figure 2 can offset the output by as much as 300 mV, if desired, with mini-mal effect on other device characteristics.OUTPUTC Figure 2.Optional Fine Trim ConfigurationNOISE PERFORMANCE AND REDUCTIONThe noise generated by the AD587 is typically less than 4 µV p-p over the 0.1 Hz to 10 Hz band. Noise in a 1 MHz band-width is approximately 200 µV p-p. The dominant source of this noise is the buried Zener which contributes approximately 100 nV/√Hz . In comparison, the op amp’s contribution is negli-gible. Figure 3 shows the 0.1 Hz to 10 Hz noise of a typical AD587. The noise measurement is made with a bandpass filter made of a 1-pole high-pass filter with a corner frequency at 0.1 Hz and a 2-pole low-pass filter with a corner frequency at 12.6 Hz to create a filter with a 9.922 Hz bandwidth.Figure 3.0.1 Hz to 10 Hz NoiseIf further noise reduction is desired, an external capacitor may be added between the NOISE REDUCTION pin and ground as shown in Figure 2. This capacitor, combined with the 4 k Ω R S and the Zener resistances, form a low-pass filter on the output of the Zener cell. A 1 µF capacitor will have a 3 dB point at 40 Hz, and it will reduce the high frequency (to 1 MHz) noise to about 160 µV p-p. Figure 4 shows the 1 MHz noise of a typi-cal AD587 both with and without a 1 µF capacitor.Figure 4.Effect of 1 µF Noise Reduction Capacitor on Broadband Noise TURN-ON TIMEUpon application of power (cold start), the time required for the output voltage to reach its final value within a specified error band is defined as the turn-on settling time. Two components normally associated with this are: the time for the active circuits to settle, and the time for the thermal gradients on the chip to stabilize. Figure 5 shows the turn-on characteristics of theAD587. It shows the settling to be about 60 µs to 0.01%. Note the absence of any thermal tails when the horizontal scale is ex-panded to 1 ms/cm in Figure 5b.AD587REV. C–5–DYNAMIC PERFORMANCEThe output buffer amplifier is designed to provide the AD587 with static and dynamic load regulation superior to less com-plete references.Many A/D and D/A converters present transient current loads to the reference, and poor reference response can degrade the converter’s performance.Figure 6 displays the characteristics of the AD587 output ampli-fier driving a 0 mA to 10 mA load.Output turn-on time is modified when an external noise reduc-tion capacitor is used. When present, this capacitor acts as an additional load to the internal Zener diode’s current source, re-sulting in a somewhat longer turn-on time. In the case of a 1 µF capacitor, the initial turn-on time is approximately 400 ms to 0.01% (see Figure 5c).a.Electrical Turn-Onb.Extended Time Scalec.Turn-On with 1 µF C N Figure 5.Turn-On CharacteristicsFigure 6a.Transient Load Test Circuit Figure rge-Scale Transient Response Figure 6c.Fine Scale Settling for Transient LoadOUTAD587REV. C–6–In some applications, a varying load may be both resistive and capacitive in nature, or the load may be connected to the AD587 by a long capacitive cable.Figure 7 displays the output amplifier characteristics driving a 1000 pF, 0 mA to 10 mA load.V OUTFigure 7a.Capacitive Load Transient /Response Test CircuitFigure 7b.Output Response with Capacitive Load LOAD REGULATIONThe AD587 has excellent load regulation characteristics. Figure 8 shows that varying the load several mA changes the output by only a few µV.Figure 8.Typical Load Regulation Characteristics TEMPERATURE PERFORMANCEThe AD587 is designed for precision reference applications where temperature performance is critical. Extensive tempera-ture testing ensures that the device’s high level of performance is maintained over the operating temperature range.Some confusion exists in the area of defining and specifying ref-erence voltage error over temperature. Historically, references have been characterized using a maximum deviation per degree Centrigrade; i.e., ppm/°C. However, because of nonlinearities in temperature characteristics which originated in standard Zener references (such as “S” type characteristics), most manufactur-ers have begun to use a maximum limit error band approach to specify devices. This technique involves the measurement of the output at three or more different temperatures to specify an out-put voltage error band.Figure 9 shows the typical output voltage drift for the AD587L and illustrates the test methodology. The box in Figure 9 is bounded on the sides by thc operating temperature extremes,and on the top and the bottom by the maximum and minimum output voltages measured over the operating temperature range.The slope of the diagonal drawn from the lower left to the upper right corner of the box determines the performance grade of the device.Figure 9.Typical AD587L Temperature DriftEach AD587J, K, L grade unit is tested at 0°C, +25°C and +70°C. Each AD587S, T, and U grade unit is tested at –55°C,+25°C and +125°C. This approach ensures that the variations of output voltage that occur as the temperature changes within the specified range will be contained within a box whose diago-nal has a slope equal to the maximum specified drift. The posi-tion of the box on the vertical scale will change from device to device as initial error and the shape of the curve vary. The maxi-mum height of the box for the appropriate temperature range and device grade is shown in Figure 10. Duplication of these results requires a combination of high accuracy and stable temperature control in a test system. Evaluation of the AD587will produce a curve similar to that in Figure 9, but output readings may vary depending on the test methods and equip-ment utilized.Figure 10.Maximum Output Change in mVAD587REV. C –7–NEGATIVE REFERENCE VOLTAGE FROM AN AD587The AD587 can be used to provide a precision –10.000 V output as shown in Figure 11. The V IN pin is tied to at least a +3.5 V supply, the output pin is grounded, and the AD587 ground pin is connected through a resistor, R S , to a –15 V supply. The –10 V output is now taken from the ground pin (Pin 4) instead of V OUT . It is essential to arrange the output load and the sup-ply resistor R S so that the net current through the AD587 is be-tween 2.5 mA and 10.0 mA. The temperature characteristics and long-term stability of the device will be essentially the same as that of a unit used in the standard +10 V output configuration.1nF–15V–10VL <10mASFigure 11.AD587 as a Negative 10 V Reference USING THE AD587 WITH CONVERTERSThe AD587 is an ideal reference for a wide variety of 8-, 12-,14- and 16-bit A/D and D/A converters. Several representative examples follow.10 V REFERENCE WITH MULTIPLYING CMOS D/A OR A/D CONVERTERSThe AD587 is ideal for applications with 10- and 12-bit multi-plying CMOS D/A converters. In the standard hookup, as shown in Figure 12, the AD587 is paired with the AD754512-bit multiplying DAC and the AD711 high-speed BiFET Op Amp. The amplifier DAC configuration produces a unipolar 0 V to –10 V output range. Bipolar output applications and other operating details can be found on the individual product data sheets.Figure 12.Low Power 12-Bit CMOS DAC ApplicationThe AD587 can also be used as a precision reference for mul-tiple DACs. Figure 13 shows the AD587, the AD7628 dual DAC and the AD712 dual op amp hooked up for single supply operation to produce 0 V to –10 V outputs. Because both DACsare on the same die and share a common reference and output op amps; the DAC outputs will exhibit similar gain TCs.Figure 13. AD587 as a 10 V Reference for a CMOS Dual DACPRECISION CURRENT SOURCEThe design of the AD587 allows it to be easily configured as a current source. By choosing the control resistor R C in Figure 14,you can vary the load current from the quiescent current (2 mA typically) to approximately 10 mA.+V I L = + I BIAS10VR CFigure 14. Precision Current SourceAD587REV. C –8–P R I N T E D I N U . S . A . C 1 1 3 6 a –1 5–1 0 / 8 8PRECISION HIGH CURRENT SUPPLYFor higher currents, the AD587 can easily be connected to a power PNP or power Darlington PNP device. The circuit in Figure 15 can deliver up to 4 amps to the load. The 0.1 µF capacitor is required only if the load has a significant capacitive component. If the load is purely resistive, improved high fre-quency supply rejection results can be obtained by removing thecapacitor.Figure 15a. Precision High-Current Current Source Figure 15b.Precision High-Current Voltage SourceCerdip (Q-8) PackageMini-DIP (N-8) Package Small Outline (R-8) PackageOUTLINE DIMENSIONSDimensions shown in inches and (mm).。

艾为电子技术 AW8731 超大音量、防破音、超低 EMI、K 类音响功率放大器 产品手册

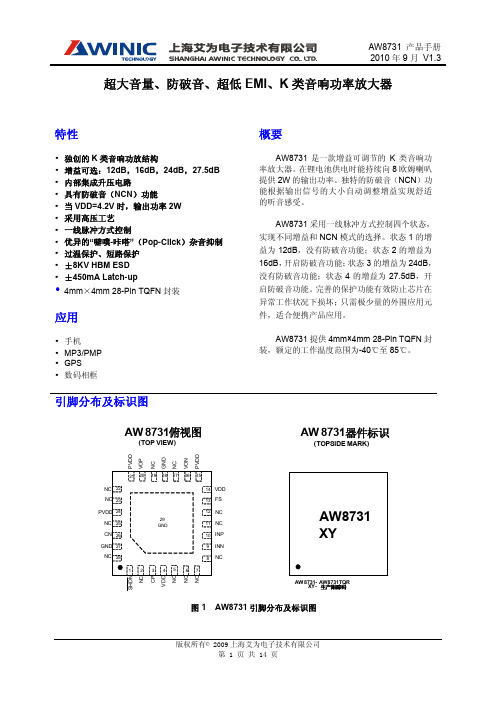

超大音量、防破音、超低EMI 、K 类音响功率放大器引脚分布及标识图S H D NN C V D N N N NCINN INP NC NC FS VDD P V D DV O PN CG N DN CV O NP V D DAW 8731 (TOP VIEW)AW 8731 (TOPSIDE MARK)AW 8731 - AW8731TQRXY -生产跟踪码器件标识俯视图图 1 AW8731引脚分布及标识图特性y 独创的K 类音响功放结构y 增益可选:12dB ,16dB ,24dB ,27.5dB y 内部集成升压电路y 具有防破音(NCN )功能y 当VDD=4.2V 时,输出功率2W y 采用高压工艺y 一线脉冲方式控制y 优异的“噼噗-咔嗒”(Pop-Click )杂音抑制 y 过温保护、短路保护 y ±8KV HBM ESD y±450mA Latch-upy 4mm ×4mm 28-Pin TQFN 封装 应用y 手机y MP3/PMP y GPS y 数码相框概要AW8731是一款增益可调节的K 类音响功率放大器。

在锂电池供电时能持续向8欧姆喇叭提供2W 的输出功率。

独特的防破音(NCN )功能根据输出信号的大小自动调整增益实现舒适的听音感受。

AW8731采用一线脉冲方式控制四个状态,实现不同增益和NCN 模式的选择。

状态1的增益为12dB ,没有防破音功能;状态2的增益为16dB ,开启防破音功能;状态3的增益为24dB ,没有防破音功能;状态4的增益为27.5dB ,开启防破音功能。

完善的保护功能有效防止芯片在异常工作状况下损坏;只需极少量的外围应用元件,适合便携产品应用。

AW8731提供4mm×4mm 28-Pin TQFN 封装,额定的工作温度范围为-40℃至85℃。

典型应用图图 2AW8731差分输入方式应用图订购信息产品型号工作温度范围封装形式器件标识发货形式AW8731TQR -40℃~85℃4mmX4mm28-Pin TQFNAW8731卷带包装3000 片/盘引脚定义及功能序号符号描述——————关断引脚,低有效;支持一线脉冲方式控制。

KT0913_datasheet_V1.2

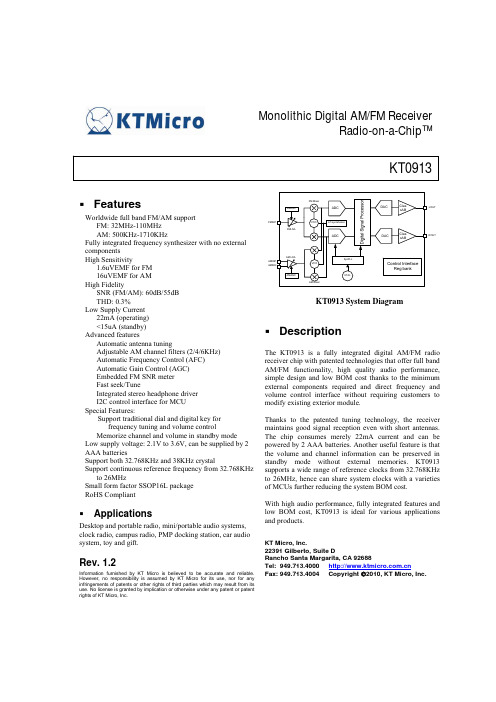

Monolithic Digital AM/FM Receiver Radio-on-a-Chip™KT0913FeaturesWorldwide full band FM/AM support FM: 32MHz-110MHz AM: 500KHz-1710KHz Fully integrated frequency synthesizer with no external components High Sensitivity 1.6uVEMF for FM 16uVEMF for AM High Fidelity SNR (FM/AM): 60dB/55dB THD: 0.3% Low Supply Current 22mA (operating) <15uA (standby) Advanced features Automatic antenna tuning Adjustable AM channel filters (2/4/6KHz) Automatic Frequency Control (AFC) Automatic Gain Control (AGC) Embedded FM SNR meter Fast seek/Tune Integrated stereo headphone driver I2C control interface for MCU Special Features: Support traditional dial and digital key for frequency tuning and volume control Memorize channel and volume in standby mode Low supply voltage: 2.1V to 3.6V, can be supplied by 2 AAA batteries Support both 32.768KHz and 38KHz crystal Support continuous reference frequency from 32.768KHz to 26MHz Small form factor SSOP16L package RoHS CompliantFMINP FMLNA FM Mixer FMAGCADCDACClas sABLOUTVCOLO syntehsizerADCDACClas sABROUTAM LNA AMINP AMINN VCOSysPLLControl Interface Reg bankAMAGC AM MixerXTALKT0913 System DiagramDescriptionThe KT0913 is a fully integrated digital AM/FM radio receiver chip with patented technologies that offer full band AM/FM functionality, high quality audio performance, simple design and low BOM cost thanks to the minimum external components required and direct frequency and volume control interface without requiring customers to modify existing exterior module. Thanks to the patented tuning technology, the receiver maintains good signal reception even with short antennas. The chip consumes merely 22mA current and can be powered by 2 AAA batteries. Another useful feature is that the volume and channel information can be preserved in standby mode without external memories. KT0913 supports a wide range of reference clocks from 32.768KHz to 26MHz, hence can share system clocks with a varieties of MCUs further reducing the system BOM cost. With high audio performance, fully integrated features and low BOM cost, KT0913 is ideal for various applications and products.KT Micro, Inc. 22391 Gilberto, Suite D Rancho Santa Margarita, CA 92688 Tel: 949.713.4000 Fax: 949.713.4004 Copyright ©2010, KT Micro, Inc.ApplicationsDesktop and portable radio, mini/portable audio systems, clock radio, campus radio, PMP docking station, car audio system, toy and gift.Rev. 1.2Information furnished by KT Micro is believed to be accurate and reliable. However, no responsibility is assumed by KT Micro for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of KT Micro, Inc.Table of Content1. Electrical Specification............................................................................................................................ 4 2. Pin List .................................................................................................................................................... 6 3. Function Description ............................................................................................................................... 7 3.1. Overview ............................................................................................................................................. 7 3.2. FM Receiver........................................................................................................................................ 7 3.3. AM Receiver ....................................................................................................................................... 7 3.4. Operation Bands................................................................................................................................. 7 3.5. Standby ............................................................................................................................................... 7 3.6. Crystal and reference clock............................................................................................................... 8 3.7. Digital Signal Processing ................................................................................................................... 8 3.7.1. FM Stereo Decoder ........................................................................................................................ 8 3.7.2. Mute / Softmute.............................................................................................................................. 8 3.7.3. Stereo / Mono Blending ................................................................................................................. 9 3.7.4. Bass ................................................................................................................................................ 9 3.7.5. Stereo DAC, Audio Filter and Driver............................................................................................. 9 3.7.6. AM Bandwidth............................................................................................................................... 9 3.7.7. TUNE ............................................................................................................................................. 9 3.7.8. SEEK.............................................................................................................................................10 3.8. User-Machine Interface ....................................................................................................................10 3.8.1. Programmable band.......................................................................................................................10 3.8.2. Key Mode......................................................................................................................................10 3.8.3. Dial Mode......................................................................................................................................11 3.9. I2C Control Interface .......................................................................................................................13 3.10. Register Bank ....................................................................................................................................15 3.10.1. CHIP ID (Address 0x01)...............................................................................................................16 3.10.2. SEEK (Address 0x02) ...................................................................................................................16 3.10.3. TUNE (Address 0x03)...................................................................................................................16 3.10.4. VOLUME (Address 0x04) ............................................................................................................16 3.10.5. DSPCFGA (Address 0x05) ...........................................................................................................17 3.10.6. LOCFGA (Address 0x0A) ............................................................................................................18 3.10.7. LOCFGC (Address 0x0C).............................................................................................................18 3.10.8. RXCFG (Address 0x0F)................................................................................................................18 3.10.9. STATUSA (Address 0x12) ...........................................................................................................19 3.10.10. STATUSB (Address 0x13) ...........................................................................................................19 3.10.11. STATUSC (Address 0x14) ...........................................................................................................19 3.10.12. AMSYSCFG (Address 0x16)........................................................................................................20 3.10.13. AMCHAN (Address 0x17) ...........................................................................................................21 3.10.14. AMCALI (Address 0x18) .............................................................................................................21 3.10.15. GPIOCFG (Address 0x1D) ...........................................................................................................21 3.10.16. AMDSP (Address 0x22) ...............................................................................................................21 3.10.17. AMSTATUSA (Address 0x24).....................................................................................................22 3.10.18. AMSTATUSB (Address 0x25) .....................................................................................................22 3.10.19. SOFTMUTE (Address 0x2Eh)......................................................................................................22 3.10.20. USERSTARTCH (Address 0x2F).................................................................................................23 3.10.21. USERGUARD (Address 0x30).....................................................................................................23 3.10.22. USERCHANNUM (Address 0x31) ..............................................................................................23 3.10.23. AMCFG (Address 0x33) ...............................................................................................................24 3.10.24. AMCFG2 (Address 0x34h) ...........................................................................................................24 3.10.25. VOLGUARD (Address 0x3Ah) ....................................................................................................24 3.10.26. AFC (Address 0x3Ch)...................................................................................................................25 4. Typical Application Circuit ....................................................................................................................26 5. Package Outline......................................................................................................................................27 6. Revision History.....................................................................................................................................28Copyright ©2010, KT Micro, Inc.27.Contact Information................................................................................................................................28Copyright ©2010, KT Micro, Inc.31. Electrical SpecificationParameter Power Supply Ambient Temperature Symbol AVDD Ta Table 1: Operation Condition Operating Condition Min Relative to AVss 2.1 -30 Table 2: DC Characteristics Symbol Test/Operating Min Condition IFM IAM IAPD Typ 3.3 25 Max 3.6 70 Units V ℃Parameter Current Consumption Standby Current FM Mode AM ModeTyp 21.3 22 14.5Max -Units mA mA μATable 3: FM Receiver Characteristics (Unless otherwise noted Ta = -30~70℃, AVDD= 2.1V to 3.6V) Parameter Symbol Test/Operating Min Typ Max Condition FM Frequency Range Frx 110 32 Sensitivity1,2,3 Sen (S+N)/N=26dB 1.6 2 Input referred 3rd Order IIP3 85 Intermodulation Production4,5 Adjacent Channel Selectivity 35 51 ±200KHz Alternate Channel Selectivity 50 70 ±400KHz Image Rejection Radio 35 AM suppression 50 RCLK frequency 32.768 32.768 26000 RCLK frequency Range8 -100 100 Audio Output Voltage1,2,3,4 32ohm load 90 100 110 Audio Band Limits1,2,4 30 15k ±3dB 1,4,6 Audio Stereo Separation 35 Audio Mono S/N1,2,3,4 55 60 Audio Stereo S/N1,4,6,7 DBLND=1 64 Audio THD1,2,4,6 0.3 De-emphasis Time Constant DE=0 75 DE=1 50 Audio Common Mode Voltage 0.85 Audio Output Load Resistance RL Single-ended 32 Seek/Tune Time 50 Power-up Time 600 Notes: 1. FMOD=1KHz, 75us de-emphasis 2. MONO=1 3. △F=22.5KHz 4. VEMF=1mV, Frequency=32MHz~110MHz 5. AGCD=1 6. △F=75KHz 7. VOLUME<4:0>=11111 8. The supported RCLK frequency is not continuous. Please refer to application notes.Units MHz uVemf dBuVE MF dB dB dB dB KHz ppm mVRMS Hz dB dB dB % μs μs V Ω ms msCopyright ©2010, KT Micro, Inc.4Table 4: AM Receiver Characteristics (Unless otherwise noted Ta = -30~70℃, AVDD= 2.1V to 3.6V) Parameter Symbol Test/Operating Min Typ Condition AM Frequency Range Frx 500 Sensitivity1,2 Sen (S+N)/N=26dB 15 Audio Output Voltage1,2,3,4 32ohm load 60 Audio Mono S/N1,2,3,4 55 Audio THD1,2,4,6 0.3 Antenna inductance L 280 350 Notes: 1. FMOD=1KHz 2. Modulation index is 30% 3. VEMF=1mV, Frequency=500KHz~1710KHz 4. VOLUME<4:0>=11111Max 1710Units KHz uVemf mVRMS dB % uH0.6 420Copyright ©2010, KT Micro, Inc.52. Pin ListTable 5: Pin listPin Num 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16Pin Name CH DVSS ROUT LOUT AVSS AVDD XI/RCLK XO ENABLE AMINN AMINP RFINP RFGND SCL SDA VOLDescription Channel adjustment. Digital ground. Right channel audio output. Left channel audio output. Analog ground. Power supply. Crystal input/Reference clock input. Crystal output. Chip enable. Tied to an internal 600kohm pull down resistor. AM RF negative input. AM RF positive input. FM RF input. RF ground. SCL of I2C interface. Tied to an internal 47kohm pull-up resistor. SDA of I2C interface. Tied to an internal 47kohm pull-up resistor. Volume adjustment.Figure 1: KT0913 Pin assignment (Top view)Copyright ©2010, KT Micro, Inc.63. Function Description3.1. OverviewKT0913 offers a true single-chip, full-band FM/AM and versatile radio solution by minimizing the external components and offering a variety of configurations.3.2. FM ReceiverKT0913 enters FM mode by setting register AM_FM to 0. The FM receiver is based on the architecture of KT Micro’s latest generation FM receiver chips in mass production. There are no external filters or frequency-tuning devices thanks to a proprietary digital low-IF architecture consisting of a fully-integrated LNA, an automatic gain control (AGC), a set of high-performance ADCs, high-quality analog and digital filters, and an on-chip low-noise self-tuning VCO. The on-chip high-fidelity Class-AB driver further eliminates the need for external audio amplifiers and can drive stereo headphones directly.3.3. AM ReceiverKT0913 enters AM mode by setting register AM_FM to 1. The AM Receiver employs a similar digital low IF architecture and share many circuits with the FM receiver. The AM receiver supports a wide band from 500KHz to 1710KHz also known as the popular AM bands. The AM channel spacing can be set to 1KHz, 9KHz or 10KHz to address different applications. The bandwidth of the channel filter can be set to 2KHz, 4KHz or 6KHz to suit various requirements. The AM receiver in KT0913 can provide accurate and automatic AM tuning without manual alignment. It supports 350uH ferrite loop antenna with +/- 25% tolerance.3.4. Operation BandsKT0913 supports wide FM band and AM bands. The FM receiver covers frequencies from 32MHz to 110MHz. The 32MHz to 64MHz is defined as Campus Band in KT0913 and can be enabled by setting CAMPUSBAND_EN register to 1. The AM band is from 500KHz to 1710KHz.3.5. StandbyKT0913 supports both Software Standby mode and Hardware Standby mode. To enter Software Standby, the STANDBT register shall be set to 1 through I2C interface. To enter Hardware Standby, the ENABLE pin is pulled down to ground. In the standby modes, the internal state (channel, volume) is preserved and can be recovered when the chip wakes up from the standby.Copyright ©2010, KT Micro, Inc.73.6. Crystal and reference clockKT0913 integrates a low frequency crystal oscillator that supports 32.768KHz and 38KHz crystals. Alternatively a CMOS level external reference clock may be used by setting the RCLK_EN register to 1 and setting REFCLK<3:0> according to the frequency of the reference clock.3.7. Digital Signal Processing3.7.1. FM Stereo DecoderThe digitized IF signal is fed to the FM demodulator which demodulates the signal and outputs a digital multiplexed (MPX) signal consisting of L+R audio, L-R audio, 19KHz pilot tone and RDS signal. The left channel signal and the right channel signal can be extracted from the MPX signal by simply adding and subtracting the L+R signal and L-R signal. The spectrum diagram is shown in Figure 2.Figure 2: Spectrum diagram of the MPX signal3.7.2. Mute / SoftmuteKT0913 can be hard muted by setting DMUTE to 0 and the output of the audio signal is set to the common mode voltage. There is also a Soft Mute feature that is enabled by setting FMDSMUTE to 0 in FM mode and AMDSMUTE to 0 in AM mode. In this mode, the audio volume is gradually attenuated when the signal reception is bad (i.e. when the RSSI is below a certain level as defined by FM_SMTH<2:0> and AM_SMTH<2:0>, respectively.) The attenuation attack rate and depth can be configured through SMUTER<1:0> and SMUTEA<1:0>, Copyright ©2010, KT Micro, Inc. 8respectively. The target volume can be configured through VOLUMET<4:0>. SNR value can also be used as the judgment threshold in FM mode by setting SMMD to 1.3.7.3. Stereo / Mono BlendingIn order to provide a comfortable listening experience, KT0913 blends the stereo signal with mono signal gradually when in weak reception in FM mode. The signal level range over which the blending occurs is set by BLNDADJ<1:0>. The blending is disabled when DBLND is set to 1. MONO playback mode can be forced by setting the MONO to 1. If the MONO bit and the INV_LEFT_AUDIO bit are both set to 1, then a fully differential signal will be output at the LOUT and ROUT.3.7.4. BassKT0913 provides bass boost feature for audio enhancement. The gain of the bass boost can be programmed through BASS<1:0>. With BASS<1:0>=00, this feature is disabled.3.7.5. Stereo DAC, Audio Filter and DriverTwo high-quality single-bit ΔΣ audio digital-to-analog converters (DAC) are integrated along with high-fidelity analog audio filters and class AB drivers. Headphones with impedance as low as 16ohms can be directly driven without adding external audio drivers. An integrated anti-pop circuit suppresses the click-and-pop sound during power up and power down. For different load capacitor, user can set different anti-pop configuration through POP<1:0>.3.7.6. AM BandwidthKT0913 provide programmable AM channel bandwidth through AM_BW<1:0>.3.7.7. TUNEThe fully integrated LO synthesizer supports wide band operation. Channel tuning is started when the register AMTUNE/FMTUNE is set to 1. In FM mode, the channel frequency is set by FMCHAN<11:0> and is defined as Freq(MHz) = 50KHz × FMCHAN<11:0> In AM mode, the channel frequency is set by AMCHAN<10:0> and is defined as Freq(KHz) = 1KHz × AMCHAN<10:0>Copyright ©2010, KT Micro, Inc.93.7.8. SEEKKT0913 offers an effective software based seek algorithm. Refer to application notes for more information.3.8. User-Machine InterfaceChannel and volume can be adjusted not only by setting corresponding FMCHAN, AMCHAN and VOLUME registers, but also by using built-in user-machine interface. Two types of user-machine interface, Key Mode and Dial Mode, are provided by KT0913. In these modes, the channel and volume are controlled by KT0913 itself.3.8.1. Programmable bandKT0913 supports programmable arbitrary frequency range of the operation band by setting register USERBAND to 1. Information of the current band, such as AM/FM mode, upper and lower edge of the band, channel step and the number of guard channel used in Dial Mode, should be written to KT0913 once the band is chosen, which is sensed by MCU. The number of channels and start channel are defined in register USER_CHAN_NUM<11:0> and USER_START_CHAN<14:0>. In FM mode, where register AM_FM is set to 0, the lower and upper bound of the current band can be express as: f bot = USER _ START _ CHAN < 14 : 0 > ×50 KHzf top = f bot + USER _ CHAN _ NUM < 11 : 0 > × f step Where f step is the channel step, which can be configured by register FMSPACE<1:0>. In AM mode, where register AM_FM is set to 1, the corresponding lower and upper bound of the band are: f bot = USER _ START _ CHAN < 14 : 0 > ×1KHzf top = f bot + USER _ CHAN _ NUM < 11 : 0 > × f stepWhere f step is the channel step, which can be configured by register AMSPACE<1:0>.3.8.2. Key ModeKT0913 allows user to control the channel and volume by using keys/buttons to send digital control signals to CH and VOL pins. Please refer to Section 4 for a typical application circuit. The key mode is enabled by setting GPIO1<1:0> and GPIO2<1:0> to 01.Copyright ©2010, KT Micro, Inc.10Each time VOLP/VOLM key is pressed, the volume increases/decreases by 2dB. If the VOLP/VOLM key is pressed and held, the volume will continue to increase/decrease at 2dB steps until the key is released. When configured in Key Mode, KT0913’s channel selection has two working modes. Mode A: If KEY_MODE<1:0> is set to 00, Mode A is selected. In this mode, each time the CHP (CHM) is pressed, the channel frequency increases (decreases) by one step. The step sizes are defined by FMSPACE<1:0> and AMSPACE<1:0>. If the CHP (CHM) key is pressed for and held for a certain time (defined by TIME1<1:0>), the channel frequency will continue to increase (decrease) automatically at a certain pace (as defined by TIME2<2:0>) until the key is released. Mode B: If KEY_MODE<1:0> is set to 01, Mode B is selected. In this mode, each time the CHP (CHM) is pressed, the channel increases (decreases) by one step. The step sizes are defined by FMSPACE<1:0> and AMSPACE<1:0>. If the CHP (CHM) key is pressed and held for a specific time (TIME1<1:0>), the channel will continue to increase (decrease) automatically at a certain pace (TIME2<2:0>) even if the key is released. The movement is stopped when the key is pressed again.3.8.3. Dial ModeKT0913 supports a unique Dial Mode whose application circuit is shown in Figure 3. The dial is implemented by a variable resistor with the center tap connected to the chip. KT0913 measures the divider ratio of two parts of the variable resistor and maps the result to the real control parameters, such as channel frequency, volume, etc. The channel controller enters dial mode by setting register GPIO1<1:0> to 10. The illustration circuit is shown in Figure 3 错误!未找到引用源。

富满电子集团TC8871 5W单通道F类音频功率放大器说明书

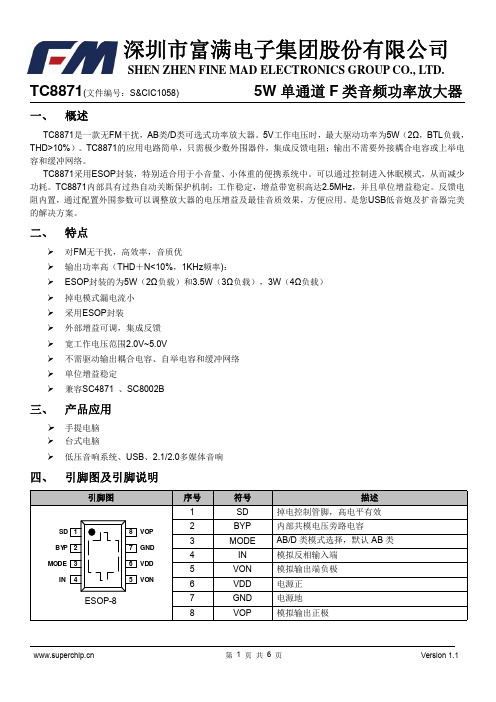

TC8871(文件编号:S&CIC1058)5W 单通道F 类音频功率放大器一、概述TC8871是一款无FM 干扰,AB 类/D 类可选式功率放大器。

5V 工作电压时,最大驱动功率为5W (2Ω,BTL 负载,THD>10%)。

TC8871的应用电路简单,只需极少数外围器件,集成反馈电阻;输出不需要外接耦合电容或上举电容和缓冲网络。

TC8871采用ESOP 封装,特别适合用于小音量、小体重的便携系统中。

可以通过控制进入休眠模式,从而减少功耗。

TC8871内部具有过热自动关断保护机制;工作稳定,增益带宽积高达2.5MHz ,并且单位增益稳定。

反馈电阻内置,通过配置外围参数可以调整放大器的电压增益及最佳音质效果,方便应用。

是您USB 低音炮及扩音器完美的解决方案。

二、特点对FM 无干扰,高效率,音质优输出功率高(THD +N<10%,1KHz 频率):ESOP 封装的为5W (2Ω负载)和3.5W (3Ω负载),3W (4Ω负载) 掉电模式漏电流小 采用ESOP 封装外部增益可调,集成反馈 宽工作电压范围2.0V~5.0V不需驱动输出耦合电容、自举电容和缓冲网络 单位增益稳定兼容SC4871、SC8002B三、产品应用手提电脑台式电脑低压音响系统、USB 、2.1/2.0多媒体音响四、引脚图及引脚说明TC8871(文件编号:S&CIC1058)5W 单通道F 类音频功率放大器七、电气参数八、TC8871D 类模式应用说明MODE 功能TC8871是一款AB 类/D类可选的音频功率放大器,通过MODE 功能键可对功放进行AB类D类的选择。

MODE 芯片功能模式高电平D 类功率放大器低电平AB 类功率放大器输入电阻(Ri )通过选择输入电阻的参数值可以配置放大器的增益:阻抗匹配对于放大器来说很重要,输出与反馈的平衡取决于电路的阻抗匹配情况,CMRR ,PSRR 和二次谐波失真的消除也可以得到优化。

RDA5876p_datasheet_v1.11

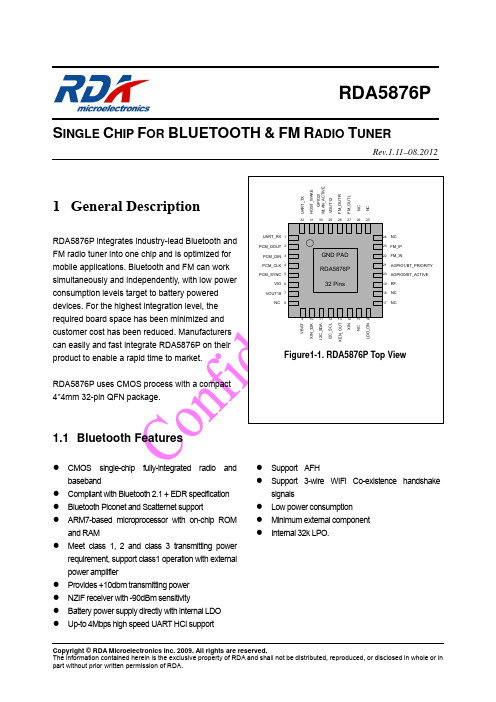

RDA5876PSINGLE CHIP FOR BLUETOOTH & FM RADIO TUNERRev.1.11–08.2012GPIO2/ WLAN_ACTIVEHOST_WAKEFM_OUTR1 General DescriptionRDA5876P integrates industry-lead Bluetooth and FM radio tuner into one chip and is optimized for mobile applications. Bluetooth and FM can work simultaneously and independently, with low power consumption levels target to battery powered devices. For the highest integration level, the required board space has been minimized and customer cost has been reduced. Manufacturers can easily and fast integrate RDA5876P on their product to enable a rapid time to market. RDA5876P uses CMOS process with a compact 4*4mm 32-pin QFN package.UART_RX 1 PCM_DOUT 2 PCM_DIN 3 PCM_CLK 4 PCM_SYNC 5 VIO 6 VOUT18 7 NC8UART_TXFM_OUTLVOUT12NC26323130292827NC2524 23NC FM_IP FM_IN AGPIO1/BT_PRIORITY AGPIO0/BT_ACTIVE RF NC NCGND PAD RDA5876P 32 Pins22 21 20 19 18 17910111213141516XIN_32KI2C_SDAXEN_OUTFigure1-1. RDA5876P Top View1.1 Bluetooth FeaturesCMOS single-chip fully-integrated radio and baseband Compliant with Bluetooth 2.1 + EDR specification Bluetooth Piconet and Scatternet support ARM7-based microprocessor with on-chip ROM and RAM Meet class 1, 2 and class 3 transmitting power requirement, support class1 operation with external power amplifier Provides +10dbm transmitting power NZIF receiver with -90dBm sensitivity Battery power supply directly with internal LDO Up-to 4Mbps high speed UART HCI supportCopyright © RDA Microelectronics Inc. 2009. All rights are reserved. The information contained herein is the exclusive property of RDA and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of RDA.Support AFH Support 3-wire WIFI Co-existence handshake signals Low power consumption Minimum external component Internal 32k LPO.LDO_ONI2C_SCLVBATXINNCRDA Microelectronics, Inc.RDA5876P Datasheet V1.111.2 FM FeaturesCMOS single-chip fully-integrated FM tuner Low power consumption Total current consumption lower than 20mA at 3.0V power supply Support worldwide frequency band 50 -115 MHz Support flexible channel spacing mode 100KHz, 200KHz, 50KHz and 25KHz Support RDS/RBDS Digital low-IF tuner Image-reject down-converter High performance A/D converter IF selectivity performed internally Fully integrated digital frequency synthesizer Fully integrated on-chip RF and IF VCO Fully integrated on-chip loop filter Autonomous search tuning Support 32.768KHz crystal oscillator Digital auto gain control (AGC) Digital adaptive noise cancellation Mono/stereo switch Soft mute High cutProgrammable de-emphasis (50/75 μs) Receive signal strength indicator (RSSI) Bass boost Volume control Line-level analog output voltage I2C control bus interface Directly support 32Ω resistance loading Integrated LDO regulator 1.8 to 5.5 V operation voltage1.3 ApplicationsMobile handset MP3,MP4 and PMP PDA Cordless phoneThe information contained herein is the exclusive property of RDA and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of RDA. Page 2 of 22RDA Microelectronics, Inc.RDA5876P Datasheet V1.112 Table of Contents1 General Description ....................................................................................................................................1 1.1 Bluetooth Features .............................................................................................................................1 1.2 FM Features........................................................................................................................................2 1.3 Applications ........................................................................................................................................2 Table of Contents.........................................................................................................................................3 Bluetooth Section Functional Description.................................................................................................4 Bluetooth Section Features.........................................................................................................................5 Bluetooth Section Electrical Characteristics ............................................................................................6 Bluetooth Section Radio Characteristics...................................................................................................8 FM Section Functional Description .........................................................................................................10 FM Section Electrical Characteristics.....................................................................................................12 FM Section Receiver Characteristics ......................................................................................................13 Pins Description.........................................................................................................................................14 Application Circuit....................................................................................................................................17 Package Physical Dimension ....................................................................................................................17 PCB Land Pattern.....................................................................................................................................18 Change List................................................................................................................................................21 Contact Information .................................................................................................................................222 3 4 5 6 7 8 9 10 11 12 13 14 15The information contained herein is the exclusive property of RDA and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of RDA. Page 3 of 22RDA Microelectronics, Inc.RDA5876P Datasheet V1.113 Bluetooth Section Functional DescriptionVBATDC/DCBBModemA AΦ BT_RF PLLx xRFLDOROMROMDEnvelonFM_IP LDO_ONPORRAMRAMFM_IN GPIO_FM1AHB ARM TRAP SPI2 FMGPIO_FM2 GPIO_FM3 FM_OUTRVICI2C_SDA I2C_SCLSCUFM_OUTLI2C DMA TIMER PLLXINUART_TX UART_RXUARTAPB BRIDGEAPB GPIO 32K/LPOXIN_32KFigure3-1. RDA5876P Bluetooth Block Diagram RDA5876P is designed for use in UART HCI with handset chipsets. As shown in Figure3-1, RDA5876P integrates radio unit, baseband core, ARM7 core and memory which provides a complete lower Bluetooth protocol stack including the LC, LM and HCI interface.The information contained herein is the exclusive property of RDA and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of RDA. Page 4 of 22RDA Microelectronics, Inc.RDA5876P Datasheet V1.114 Bluetooth Section FeaturesRadio♦ ♦ ♦ ♦ ♦ ♦ ♦ Build-in TX/RX switch Fully integrated synthesizer without any external component Support external reference clock direct input Class1, 2 and class3 transmit output power supported and over 30dB dynamic control range Supports π/4 DQPSK and 8DPSK modulation High performance in receiver sensitivity and over 80dB dynamic range Integrated channel filterAuxiliary features♦ ♦ ♦ ♦ ♦ On-chip regulator to support battery power supply directly Power management support low power mode Support share handset system reference clock Support 3-wire wifi cooperation handshake protocol Support external class1 PA and antenna switchBaseband♦ ♦ ♦ ♦ ♦ Internal RAM allows fully speed data transfer, mixed voice and data, and fully piconet operation Logic for forward error correction, header error control, access code correlation, CRC, demodulation , encryption bit stream generation, whitening and transmit pulse shaping Support eSCO and AFH Support up to Bluetooth v2.1 + EDR Support A-law, μ-law and CVSD digitize audio CODEC in PCM interfaceInterface♦ ♦ ♦ ♦ Provides UART HCI interface, up-to 4Mbps Provides I2C interface for host to do configuration Provides PCM audio interface Provides 3-wire and 2-wire WIFI Co-existence handshake interfaceBluetooth Stack♦ Compliant with Bluetooth 2.1 + EDR specificationThe information contained herein is the exclusive property of RDA and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of RDA. Page 5 of 22RDA Microelectronics, Inc.RDA5876P Datasheet V1.115 Bluetooth Section Electrical CharacteristicsTable 5-1SYMBOLDC Electrical Specification (Recommended Operation Conditions):DESCRIPTION Supply Voltage from battery or LDO Ambient Temperature CMOS Low Level Input Voltage CMOS High Level Input Voltage CMOS Threshold Voltage MIN 3.3 -20 0 0.7*VIO 0.5*VIO TYP 4.0 27 MAX 4.2 +50 0.3*VIO VIO UNIT V ℃ V V VVBAT Tamb VIL VIH VTHNotes:1. VIO=1.8~3.3VTable 5-2SYMBOLDC Electrical Specification (Absolute Maximum Ratings):DESCRIPTION Ambient Temperature Input Current Input Voltage LNA Input Level MIN -20 -10 -0.3 TYP MAX +60 +10 VIO+0.3 +5 UNIT °C mA V dBmTamb IIN VIN VlnaTable 5-3LDOPower consumption specification(VBAT = 4.0 V, VIO = 2.8V, TA = +27℃, RF 9dBm, LDO mode unless otherwise specified) STATE Headset voice Headset SNIFF HCI only active Both SCAN DeepSleep internal LDO off 1.28S cycle 26Mhz crystal off LDO_ON off INQUIRE and PAGE SCAN DESCRIPTION HV3 type 500ms cycle NO INQUIRE and PAGE SCAN Condition TYP 18 0.5 5.7 1.0 118 7 UNIT mA mA mA mA μA μAIvbat=105uA,Ivio=13uA,External 32K input Ivbat=6uA,Ivio=1uAThe information contained herein is the exclusive property of RDA and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of RDA. Page 6 of 22RDA Microelectronics, Inc.RDA5876P Datasheet V1.116 Bluetooth Section Radio CharacteristicsTable 6-1 Receiver Characteristics ------ Basic Data Rate(VBAT = 4.0 V, TA = 27°C, unless otherwise specified) SYMBOL PARAMETER CONDITIONS MIN / 0 / F=F0 + 1MHz F=F0 - 1MHz Adjacent channel selectivity C/I F=F0 + 2MHz F=F0 - 2MHz F=F0 + 3 MHz F=F0 - 3MHz Adjacent channel selectivity C/I F=Fimage 30MHz–2000MHz Out-of-band blocking performance 2000MHz–2400MHz 2500MHz–3000MHz 3000MHz–12.5GHz Intermodulation Spurious output level / / / / / / / -10 -27 -27 -10 -35 -150 TYP -90 / +10 / / / / / / / / / / / / / MAX / / / -5 0 -33 -30 -45 -40 0 / / / / / / UNIT dBm dBm dB dB dB dB dB dB dB dB dBm dBm dBm dBm dBm dBm/HzGeneral specificationsSensitivity @0.1% BER Maximum received signal@0.1% BER C/I c-channelNotes:Table 6-2Transmit Characteristics ------ Basic Data Rate(VBAT = 4.0V, TA = 27 °C, unless otherwise specified) SYMBOL General specifications PARAMETER CONDITIONS MIN / 20 / F=F0 + 1MHz F=F0 - 1MHz F=F0 + 2MHz F=F0 - 2MHz F=F0 + 3MHz F=F0 - 3MHz F=F0 + >3MHz / / / / / / / TYP +4 / 0.9 -20 -20 -35 -35 -40 -40 / MAX +10 / / / / / / / / -46 UNIT dBm dB MHz dBm dBm dBm dBm dBm dBm dBmMaximum RF transmit power RF power control range 20dB band widthAdjacent channel transmit powerThe information contained herein is the exclusive property of RDA and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of RDA. Page 7 of 22RDA Microelectronics, Inc.F=F0 - >3MHz △f1avg Maximum modulation △f2max Minimum modulation △f2avg/△f1avg ICFT Drift rate Drift (1 slot packet) Drift (5 slot packet) -46 / / 0.80 / / / /RDA5876P Datasheet V1.11 / 164 145 / +4 0.1 -2 -2 / / / / / / / / dBm kHz kHz / kHzkHz/50uskHz kHzNotes:Table 6-3Receiver Characteristics ------ Enhanced Data Rate(VBAT = 4.0 V, TA = 27°C, unless otherwise specified) PARAMETER CONDITIONS MIN / 0 / F=F0 + 1MHz F=F0 - 1MHz Adjacent channel selectivity C/I F=F0 + 2MHz F=F0 - 2MHz F=F0 + 3MHz F=F0 - 3MHz Adjacent channel selectivity C/I F=Fimage / / / / / / / TYP -86 / / / / / / / / / MAX / / +13 +5 0 -20 -20 -40 -40 -7 UNIT dBm dBm dB dB dB dB dB dB dB dBπ/4 DQPSK Sensitivity @0.01% BER Maximum received signal@0.1% BER C/I c-channel8DPSKSensitivity @0.01% BER Maximum received signal@0.1% BER C/I c-channelF=F0 + 1MHz F=F0 - 1MHz Adjacent channel selectivity C/I F=F0 + 2MHz F=F0 - 2MHz F=F0 + 3MHz F=F0 - 3MHz Adjacent channel selectivity C/I F=Fimage/ 0 / / / / / / / /-83 / / / / / / / / // / +18 +5 +5 -20 -20 -35 -35 0dBm dBm dB dB dB dB dB dB dB dBNotes:The information contained herein is the exclusive property of RDA and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of RDA. Page 8 of 22RDA Microelectronics, Inc.RDA5876P Datasheet V1.11Table 6-4Transmit Characteristics ------ Enhanced Data Rate(VBAT = 4.0 V, TA = 27°C, unless otherwise specified) PARAMETER General specifications CONDITIONS MIN / / / / / / / / RMS DEVM / / / / / / / / / / / / / / 99% DEVM Peak DEVM RMS DEVM TYP +2 -1.6 +7.4 +6.7 +2.4 +7.1 +4.4 +2.7 4.7 / 8.8 4.6 / 11.3 -14.7 -15.2 -51.0 -51.2 -30 -30 / 100 MAX / / / / / / / / / 30 / / 20 / / / / / / / -32 / UNIT dBm dB kHz kHz kHz kHz kHz kHz kHz % % % % % % dBm dBm dBm dBm dBm dBm dBm %Maximum RF transmit powerRelative transmit controlπ/4 DQPSK max w0 π/4 DQPSK max wi π/4 DQPSK max |wi + w0| 8DPSK max w0 8DPSK max wi 8DPSK max |wi + w0| π/4 DQPSK Modulation Accuracy8DPSK Modulation Accuracy99% DEVM Peak DEVM F=F0 + 1MHz F=F0 - 1MHz F=F0 + 2MHzIn-band spurious emissionsF=F0 - 2MHz F=F0 + 3MHz F=F0 - 3MHz F=F0 +/- > 3MHzEDR Differential Phase CodingNotes:The information contained herein is the exclusive property of RDA and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of RDA. Page 9 of 22RDA Microelectronics, Inc.RDA5876P Datasheet V1.117 FM Section Functional DescriptionLOUTI PGALNAP LNAN LNA +I ADCAudio DSP Coredigital filter MPX decoder stereo/mono audioL DACLimiterQ PGAQ ADCR DACROUT32.768 KHzVCO SynthesizerRDS /RBDS RSSIGPIOGPIORCLK 2.7-5.5 V VDDSCLKMCU LDOInterface Bus SDIO VIOFM ReceiverFigure 7-1. RDA5876P FM Tuner Block Diagram The PGA amplifies the mixer output IF signal and then digitized with ADCs. The DSP core finishes the channel selection, FM demodulation, stereo MPX decoder and output audio signal. The MPX decoder can autonomous switch from stereo to mono to limit the output noise. The DACs convert digital audio signal to analog and change the volume at same time. The DACs has low-pass feature and -3dB frequency is about 30 KHz. Synthesizer The frequency synthesizer generates the local oscillator signal which divide to quadrature, then be used to downconvert the RF input to a constant low intermediate frequency (IF). The synthesizer reference clock is 32.768 KHz. The synthesizer frequency is defined by bits CHAN[9:0] with the range from 50MHz to 115MHz.The receiver uses a digital low-IF architecture that avoids the difficulties associated with direct conversion while delivering lower solution cost and reduces complexity, and integrates a low noise amplifier (LNA) supporting the FM broadcast band (50 to 115MHz), a quadrature image-reject mixer, a programmable gain control (PGA), a high resolution analog-to-digital converters (ADCs), an audio DSP and a highfidelity digital-to-analog converters (DACs). The LNA has differential input ports (LNAP and LNAN) and supports any input port by set according registers bits (LNA_port_sel[1:0]). It default input common mode voltage is GND. The limiter prevents overloading and limits the amount of intermodulation products created by strong adjacent channels. The quadrature mixer down converts the LNA output differential RF signal to low-IF, it also has image-reject function.The information contained herein is the exclusive property of RDA and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of RDA. Page 10 of 22RDA Microelectronics, Inc. Power Supply The RDA5876P FM section integrated LDO which supplies power to the chip. The external supply voltage range is 1.8-5.5 V. RESET and Control Interface select The RDA5876P FM section is RESET itself When VIO is Power up. And also support soft reset by trigger 02H BIT1 from 0 to 1. The control interface is I2C. Control Interface The I2C interface is compliant to I2C Bus Specification 2.1. It includes two pins: SCL and SDA. A I2C interface transfer begins with START condition, a command byte and data bytes, each byte has a followed ACK (or NACK) bit, and ends with STOP condition. The command byte includes a 7-bit chip address (0010000b) and a R/W bit. The ACK (or NACK) is always sent out by receiver. When in write transfer, data bytes is written out from MCU, and when in read transfer, data bytes is read out from RDA5876P. There is no visible register address in I2C interface transfers. The I2C interface has a fixed start register address (0x02h for write transfer and 0x0Ah for read transfer), and an internal incremental address counter. If register address meets the end of register file, 0x3Ah, register address will wrap back to 0x00h. For write transfer, MCU programs registers from register 0x02h high byte, then register 0x02h low byte, then register 0x03h high byte, till the last register. RDA5876P always gives out ACK after every byte, and MCU gives out STOP condition when register programming is finished. For read transfer, after command byte from MCU, RDA5876P sends out register 0x0Ah high byte, then register 0x0Ah low byte, then register 0x0Bh high byte, till receives NACK from MCU. MCU gives out ACK for data bytes besides last data byte. MCU gives out NACK for last data byte, and then RDA5876P will return the bus to MCU, and MCU will give out STOP condition. Details please refer to RDA5876P Programming Guide and RDA5802N Programming Guide and Datasheet.RDA5876P Datasheet V1.11The information contained herein is the exclusive property of RDA and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of RDA. Page 11 of 22RDA Microelectronics, Inc.RDA5876P Datasheet V1.118 FM Section Electrical CharacteristicsTable 8-1 DC Electrical Specification (Recommended Operation Conditions): SYMBOL VBAT VIO Tamb VIL VIH VTHNotes: 1. VIO=1.8~3.3VDESCRIPTION Supply Voltage Interface Supply Voltage Ambient Temperature CMOS Low Level Input Voltage CMOS High Level Input Voltage CMOS Threshold VoltageMIN 3.3 1.5 -20 0 0.7*VIOTYP 4.0 3.0 27MAX 4.2 3.6 +75 0.3*VIO VIOUNIT V V ℃ V V V0.5*VIOTable 8-2 DC Electrical Specification (Absolute Maximum Ratings): SYMBOL VIO Tamb IIN VIN Vlna Notes: 1. For Pin: SCL, SDA DESCRIPTION Interface Supply Voltage Ambient Temperature Input Current (1) Input Voltage(1) LNA FM Input Level MIN -0.5 -40 -10 -0.3 TYP MAX +3.6 +90 +10 VIO+0.3 +10 UNIT V °C mA V dBmTable 8-3 Power Consumption Specification (VBAT = 4.0 V, VIO=1.5 to 3.6V, TA = -25 to 85 ℃, unless otherwise specified) SYMBOL IA IVIO IAPD IVIO DESCRIPTION Analog Supply Current Interface Supply Current Analog Powerdown Current Interface Powerdown Current Condition ENABLE=1 SCL and SDA inactive ENABLE=0 ENABLE=0 TYP 20 90 5 10 UNIT mA μA μA μAThe information contained herein is the exclusive property of RDA and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of RDA. Page 12 of 22RDA Microelectronics, Inc.RDA5876P Datasheet V1.119 FM Section Receiver CharacteristicsTable 9-1 Receiver Characteristics (VBAT = 4.0 V, VIO= 3.0V, TA = 25 °C, unless otherwise specified)SYMBOL PARAMETER FM Input Frequency Range CONDITIONS Adjust BAND Register 50MHz 65MHz 88MHz 98MHz 108MHz 115MHz MIN 50 80 60 50 60 55 53 35 Single-ended Volume[3:0] =1111 Rload=1KΩ Rload=32Ω 32 Volume[3:0]=0000 1KHz=0dB ±3dB point Low Freq9TYPMAX 115UNIT MHzGeneral specificationsFin1.4 1.2 1.2 1.3 1.3 1.3 70 85 360 57 55 0.15 0.2 100 141.8 1.5 1.5 1.5 1.5 1.8 0.2 0.05 dBμV dB dB dB mV dB dB Ω % dB dB Hz μV EMFVrfSensitivity1,2,3S/N=26dBIP3inInput IP34AGCD=11,2αamS200 S400 VAFL; VAFR S/NAM Suppressionm=0.3 ±200KHz ±400KHz1,2Adjacent Channel Selectivity 400KHz Selectivity Audio L/R Output Voltage (Pins LOUT and ROUT) Maximum Signal to Noise Ratio1,2,3,5Volume [3:0] =1111 Mono2 Stereo6αSCS RLTHDStereo Channel Separation Audio Output Loading Resistance Audio Total Harmonic Distortion1,3,6αAOIRmute BWaudioAudio Output L/R Imbalance1,6 Mute Attenuation Ratio1 Audio Response160 -High FreqPins LNAN, LNAP, LOUT, ROUT and NC(22,23)Vcom_rfin Vcom Vcom_ncPinsLNAN/LNAPInputCommon Mode Voltage Audio Output Common Mode Voltage8 Pins NC ( 22,23 ) Common Mode Voltage 1.00 1.05 1.1V V VFloatingNotes:1. Fin=65 to 115MHz; Fmod=1KHz; de-emphasis=75μs; MONO=1; L=R unless noted otherwise;2. Δf=22.5KHz; 3. BAF = 300Hz to 15KHz, RBW <=10Hz; 6. Δf=75KHz,fpilot=10% 5. PRF=60dBUV; 8. At LOUT and ROUT pins 4. |f2-f1|>1MHz, f0=2xf1-f2, AGC disable, Fin=76 to 108MHz; 7. Measured at VEMF = 1 m V, f RF = 65 to 108MHz 9. AdjustableThe information contained herein is the exclusive property of RDA and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of RDA. Page 13 of 22RDA Microelectronics, Inc.RDA5876P Datasheet V1.1110 Pins DescriptionGPIO2/ WLAN_ACTIVE HOST_WAKEFM_OUTRUART_TXFM_OUTLVOUT12323130292827NC26UART_RX 1 PCM_DOUT 2 PCM_DIN 3 PCM_CLK 4 PCM_SYNC 5 VIO 6 VOUT18 7 NC 8NC2524 23NC FM_IP FM_IN AGPIO1/BT_PRIORITY AGPIO0/BT_ACTIVE RF NC NCGND PAD RDA5876P 32 Pins22 21 20 19 18 17910111213141516XIN_32KI2C_SDAXEN_OUTFigure10-1. RDA5876P Top ViewThe information contained herein is the exclusive property of RDA and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of RDA. Page 14 of 22LDO_ONI2C_SCLVBATXINNCRDA Microelectronics, Inc.RDA5876P Datasheet V1.11Table 10-1RDA5876P Pins DescriptionPINNO.DESCRIPTIONUART_RX PCM_DOUT PCM_DIN PCM_CLK PCM_SYNC VIO VOUT18 NC VBAT XIN_32K I2C_SDA I2C_SCL XEN_OUT XIN NC LDO_ON NC NC RF AGPIO0 AGPIO1 FM_IN FM_IP NC NC NC FM_OUTL FM_OUTR VOUT12 GPIO2 HOST_WAKE UART_TX1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32UART data input Synchronous data output Synchronous data input Synchronous data clock Synchronous data sync IO power supply Analog voltage output, connected with decouple capacitor Should be not connected Bluetooth and FM power supply 32.768K clock input I2C interface Data signal I2C interface Clock signal Clock request output For 26Mhz external clock input Should be not connected Internal LDO power on Should be not connected Should be not connected Bluetooth Radio signal Programmable I/O Also used ad bt_active when using WIFI co-existence handshake interface. Programmable I/O. Also used as bt_priority when using WIFI co-existence handshake interface. LNA input port. For single-ended input, LNAN should be connected to RFGND LNA input port. For single-ended input, LNAN should be connected to RFGND Should be not connected Should be not connected Should be not connected Left audio output Right audio output Digital voltage output, connected with decouple capacitor Programmable I/O. Also used as wl_active when using WIFI co-existence handshake interface. Output to wakeup host UART data outputThe information contained herein is the exclusive property of RDA and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of RDA. Page 15 of 22RDA Microelectronics, Inc.RDA5876P Datasheet V1.1111 Application CircuitThe information contained herein is the exclusive property of RDA and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of RDA. Page 16 of 22RDA Microelectronics, Inc.RDA5876P Datasheet V1.1112 Package Physical DimensionFigure12-1illustratesthepackage RoHS-compliant. details for the RDA5876P. The package is lead-free andThe information contained herein is the exclusive property of RDA and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of RDA. Page 17 of 22RDA Microelectronics, Inc. Figure12-1. 32-Pin 4x4 Quad Flat No-Lead (QFN)RDA5876P Datasheet V1.1113 PCB Land PatternFigure13-3.Classification Reflow ProfileTable 13-1Classification Reflow ProfilesSn-Pb Eutectic Assembly 3 ℃/second max. Pb-Free Assembly 3 ℃/second max.Profile Feature Average Ramp-Up Rate (TSmax to Tp) Preheat -Temperature Min (Tsmin) -Temperature Max (Tsmax) -Time (tsmin to tsmax) Time maintained above: -Temperature (TL) -Time (tL) Peak /Classification Temperature(Tp) Time within 5 oC of actual Peak Temperature (tp) Ramp-Down Rate Time 25 oC to Peak100 ℃ 100 ℃ 60-120 seconds 183 ℃ 60-150seconds See Table 9-2 10-30 seconds 6 ℃/second max. 6 minutes max.150 ℃ 200 ℃ 60-180 seconds 217℃ 60-150 seconds See Table 9-3 20-40 seconds 6 ℃/seconds max. 8 minutes max.The information contained herein is the exclusive property of RDA and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of RDA. Page 18 of 22RDA Microelectronics, Inc. TemperatureRDA5876P Datasheet V1.11Table 13-2 Pb-free Process – Package Peak Reflow Temperatures Package Thickness Volume mm3 <350<2.5mm ≥2.5mm 240 + 0/-5 ℃ 225 + 0/-5 ℃Volume mm3 ≥350 225 + 0/-5 ℃ 225 + 0/-5 ℃Table 13-3 Pb-free Process – Package Classification Reflow Temperatures Package Volume mm3 Volume mm3 Volume mm3 Thickness 350-2000 <350 >2000<1.6mm 1.6mm – 2.5mm ≥2.5mm 260 + 0 ℃ * 260 + 0 ℃ * 250 + 0 ℃ * 260 + 0 ℃ * 250 + 0 ℃ * 245 + 0 ℃ * 260 + 0 ℃ * 245 + 0 ℃ * 245 + 0 ℃ **Tolerance : The device manufacturer/supplier shall assure process compatibility up to and including the stated classification temperature(this mean Peak reflow temperature + 0 ℃. For example 260+ 0 ℃ ) at the rated MSL Level. Note 1: All temperature refer topside of the package. Measured on the package body surface. Note 2: The profiling tolerance is + 0 ℃, - X ℃ (based on machine variation capability)whatever is required to control the profile process but at no time will it exceed – 5 ℃. The producer assures process compatibility at the peak reflow profile temperatures defined in Table 13-3. Note 3: Package volume excludes external terminals(balls, bumps, lands, leads) and/or non integral heat sinks. Note 4: The maximum component temperature reached during reflow depends on package the thickness and volume. The use of convection reflow processes reduces the thermal gradients between packages. However, thermal gradients due to differences in thermal mass of SMD package may sill exist. Note 5: Components intended for use in a “lead-free” assembly process shall be evaluated using the “lead free” classification temperatures and profiles defined in Table13-1, 13-2, 13-3 whether or not lead free.RoHS CompliantThe product does not contain lead, mercury, cadmium, hexavalent chromium, polybrominated biphenyls (PBB) or polybrominated biphenyl ethers (PBDE), and are therefore considered RoHS compliant.ESD SensitivityIntegrated circuits are ESD sensitive and can be damaged by static electricity. Proper ESD techniques should be used when handling these devices.The information contained herein is the exclusive property of RDA and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of RDA. Page 19 of 22。

诺瓦科技JT100交通多媒体播放器规格书

西安媒体播放器 规格书

目录

目录

目录..................................................................................................................................................... ii

4.2 尺寸图 ......................................................................................................................................................... 7

6 产品规格........................................................................................................................................10

7 音视频解码规格............................................................................................................................ 12

科 3.2 支持双 WiFi 模式 ......................................................................................................................................... 4 子 3.2.1 WiFi AP 模式............................................................................................................................................. 4 电 3.2.2 WiFi Sta 模式 ............................................................................................................................................ 5 瓦 3.2.3 WiFi AP+Sta 模式 ..................................................................................................................................... 5

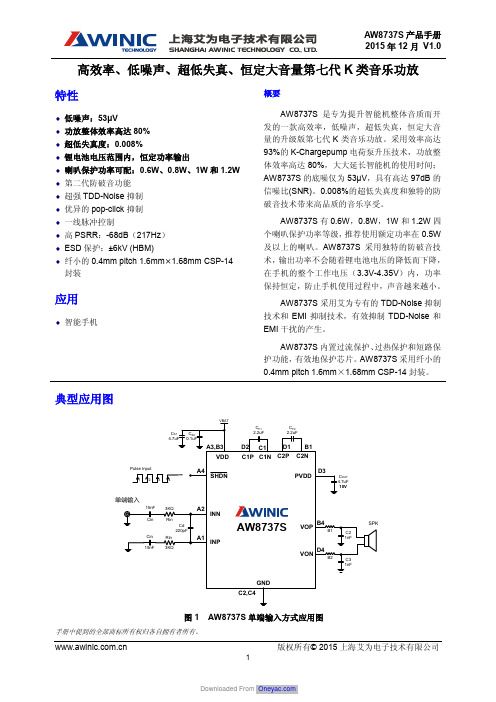

AW8737S 产品手册说明书

高效率、低噪声、超低失真、恒定大音量第七代K类音乐功放特性♦低噪声:53μV♦功放整体效率高达80%♦超低失真度:0.008%♦锂电池电压范围内,恒定功率输出♦喇叭保护功率可配:0.6W、0.8W、1W和1.2W ♦第二代防破音功能♦超强TDD-Noise抑制♦优异的pop-click抑制♦一线脉冲控制♦高PSRR:-68dB(217Hz)♦ESD保护:±6kV (HBM)♦纤小的0.4mm pitch 1.6mm×1.68mm CSP-14 封装应用♦智能手机概要AW8737S是专为提升智能机整体音质而开发的一款高效率,低噪声,超低失真,恒定大音量的升级版第七代K类音乐功放。

采用效率高达93%的K-Chargepump电荷泵升压技术,功放整体效率高达80%,大大延长智能机的使用时间;AW8737S的底噪仅为53μV,具有高达97dB的信噪比(SNR)。

0.008%的超低失真度和独特的防破音技术带来高品质的音乐享受。

AW8737S有0.6W,0.8W,1W和1.2W四个喇叭保护功率等级,推荐使用额定功率在0.5W 及以上的喇叭。

AW8737S采用独特的防破音技术,输出功率不会随着锂电池电压的降低而下降,在手机的整个工作电压(3.3V-4.35V)内,功率保持恒定,防止手机使用过程中,声音越来越小。

AW8737S采用艾为专有的TDD-Noise抑制技术和EMI抑制技术,有效抑制TDD-Noise和EMI干扰的产生。

AW8737S内置过流保护、过热保护和短路保护功能,有效地保护芯片。

AW8737S采用纤小的0.4mm pitch 1.6mm×1.68mm CSP-14封装。

典型应用图图 1AW8737S单端输入方式应用图手册中提到的全部商标所有权归各自拥有者所有。

引脚分布及标识图1234AB CAW8737SCSR TOP VIEW(俯视图)AW8737SCSR MARKING(器件标识图)K37S –AW8737SCSR XXXX –生产跟踪码1234AB CD图 2 AW8737S 引脚分布俯视图及器件标识图引脚定义及功能艾为同系列产品对比功能框图图 3AW8737S功能框图典型应用图图 4AW8737S单端输入方式应用图(注1)Note1:单端输入时,可以从INN、INP任意一输入端输入音频信号,另一输入端通过输入电阻、电容接地。

WT8576(电压2.7-6.2V, 功率4Ω 4W双)

RL=8Ω 1.6W(每通道)

RL=8Ω 1.4W(每通道)

RL=4Ω 3.20W(每通道) RL=4Ω 2.80W(每通道)

Po at% THD+N VDD=3.6V Po at 10% THD+N,

RL=8Ω 0.9W(每通道)

RL=8Ω 0.8W(每通道)

RL=4Ω 1.7W(每通道)

RL=4Ω 1.5W(每通道)

AB类模 式

THD+N=10%,f=1KHZ RL=4Ω,VOD=6V THD+N=1%, f=1 KHZ. RL=4Ω, VDD=6V THD+N=10%,f=1 KHZ, RL=4Ω, VDD=5V THD+N=1%,f=1 KHZ, RL=4Ω, VDD=5V

VDD=5.0V, Bypass=2. 2UF

4.00

W

3.20

W

2.80

W

2.30

W

400

MS

0.1

%

67

DB

90

DB

98

DB

4

典型特征曲线(D类曲线)

WT8576

5

典型特征曲线(D类曲线)

WT8576

6

典型特征曲线(D类模式)

WT8576

7

典型特征曲线(D类模式)

WT8576

8

典型特征曲线(D类模式)

WT8576

9

典型特征曲线(AB类模式)

订购信息 产品型号

WT8576

封装形式 ESOP10L

器件标识

数值 6.5 -0.3 to VDD+0.3 40to150 220 -65to150

数值

2.7~6.2

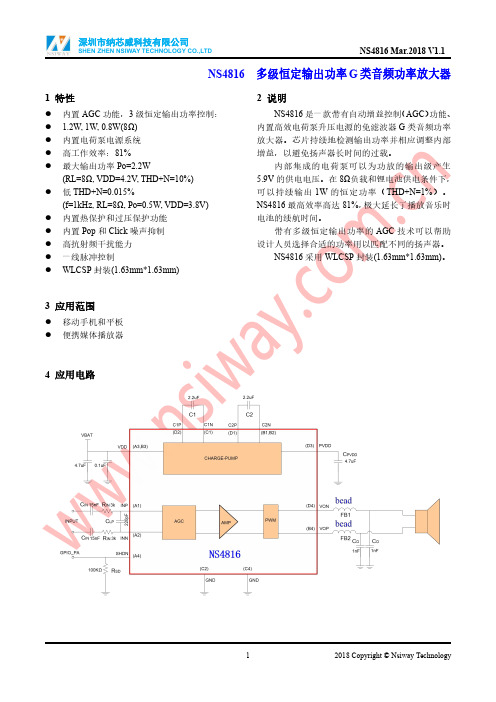

纳芯威LTD NS4816多级恒定输出功率G类音频功率放大器说明书

NS4816多级恒定输出功率G类音频功率放大器1特性●内置AGC功能,3级恒定输出功率控制:● 1.2W,1W,0.8W(8Ω)●内置电荷泵电源系统●高工作效率:81%●最大输出功率Po=2.2W(RL=8Ω,VDD=4.2V,THD+N=10%)●低THD+N=0.015%(f=1kHz,RL=8Ω,Po=0.5W,VDD=3.8V)●内置热保护和过压保护功能●内置Pop和Click噪声抑制●高抗射频干扰能力●一线脉冲控制●WLCSP封装(1.63mm*1.63mm)3应用范围●移动手机和平板●便携媒体播放器2说明NS4816是一款带有自动增益控制(AGC)功能、内置高效电荷泵升压电源的免滤波器G类音频功率放大器。

芯片持续地检测输出功率并相应调整内部增益,以避免扬声器长时间的过载。

内部集成的电荷泵可以为功放的输出级产生5.9V的供电电压。

在8Ω负载和锂电池供电条件下,可以持续输出1W的恒定功率(THD+N=1%)。

NS4816最高效率高达81%,极大延长了播放音乐时电池的续航时间。

带有多级恒定输出功率的AGC技术可以帮助设计人员选择合适的功率用以匹配不同的扬声器。

NS4816采用WLCSP封装(1.63mm*1.63mm)。

4应用电路5管脚配置NS4816WLCSP的俯视图如下图所示:NS4816管脚说明:管脚编号管脚名称管脚说明A1INP音频信号输入正端A2INN音频信号输入负端A3,B3VDD电源A4SHDN一线脉冲控制端B1,B2C2N电荷泵C2电容负端B4VOP音频放大器输出正端C1C1N电荷泵C1负端C2,C4GND地D1C2P电荷泵C2正端D2C1P电荷泵C1正端D3PVDD音频功放级电源D4VON音频放大器输出负端6极限工作参数参数最小最大单位供电电压范围VDD-0.3 5.2V输入电压范围INP.INN.SHDN-0.3VDD+0.3V工作温度范围-4085℃工作结温范围-40150℃储存温度范围-65150℃最小负载阻抗4ΩHBM ESD8000VMM ESD200VθJA15-ball WLCSP 1.63x1.63mm70℃/W注:如果器件工作条件超过上述极限值,可能对器件造成永久性损坏。

功放芯片HT6872_Datasheet_CN_V0.3

参数

符号

条件

最小值

典型值

最大值 单位

输出功率

总谐波失真加噪声 输出噪声 信噪比 电源抑制比

PO

THD+N VN SNR

PSRR

RL=4Ω, VDD=3.6V RL=4Ω, VDD=5.0V RL=4Ω, VDD=6.5V

f=1kHz, THD+N=1%

RL=4Ω, VDD=3.6V RL=4Ω, VDD=5.0V RL=4Ω, VDD=6.5V

电源电压

VDD

2.5

5

工作环境温度 扬声器阻抗

Ta

tSD (Min.)=50ms

-20

tSD (Min.)=80ms

-30

25

RL

2*4

4

注3: VDD的上升时间应当超过1μs。 注4:扬声器阻抗为2欧姆应选取SOP8-PP封装,增加散热性能,并且不推荐工作在VDD=3.6~5V范围之外。

最大值 6.5

100

10

1

VDD=6.5V

ACF-Off

RL =4Ω

0.1

f =1kHz GAIN=23.5dB

ACF-On

0.01 0

0.2 0.4 0.6 0.8

交流特性(AC)

VSS=0V, VDD =2.5 to 6.5V, Ta=-30℃~85℃, 除非特殊说明.

参数

符号

条件

上电启动时间 (或从关断唤醒时间) 输入截止频率 ACF 启动时间 ACF 释放时间 唤醒模式设置时间

关断设置时间

各模式设置时间 (除关断外) 载波调制频率

tSTUP fC tAT1 tRL1 tWK

Vin( V)

HT862_Datasheet技术文档规格书

此外,HT862内部集成免滤波器调制技术,能够 直接驱动扬声器,内置的关断功能使待机电流最小 化,还集成了输出端过流保护、片内过温保护和电源 欠压异常保护等功能。

・保护功能:过流/过热/欠压异常保护功能

・无铅无卤封装,TSSOP20L-PP

典型特性曲线.........................................................................................................................................11 AGC ......................................................................................................................................................11 BOOST + Class D ............................................................................................................................... 13

使输出音频信号限制在固定失真水平内

・内置自适应同步升压 - 小音乐信号时不升压,可大幅提高系统效率,延 长电池续航时间 - 外围无需二极管

・内置自动限温控制功能 -特别适用于升压8.5V+D类,升压+AB类状态下及

环境温度较高的情况,显著提升音乐峰值功率

CX108V 和 CX168 8路扬声器功率放大器说明书

Professional Power Amplifiers

CX168 | CX108V

Designed for permanently installed sound systems where rackspace is at a premium, QSC’s CX108V and CX168 provide unprecedented levels of channel density for multichannel amplifiers. The CX108V and CX168 provide 100 watts per channel at 70 volts and 90 watts per channel at 8 ohms respectively. With both models, each pair of channels may be bridged to configure these amplifiers as 4, 5, 6 or 7 channel units. Like the entire CX Series, the 8 channel models feature DataPorts for remote amplifier management or signal processing, incorporate QSC’s legendary PowerLight™ technology, and deliver our unmatched reputation for quality and reliability.

70V / 20 Hz – 20 kHz / 0.2% THD

Bridge-Mono Mode

16Ω / 20 Hz – 20 kHz / 0.1% THD

HT876两节锂电池串联立体声2x10W音频放大解决方案

HT876两节锂电池串联立体声2x10W音频放大解决方案随着音箱功能和性能的迅速提升,消费者对功率及音质的要求也越来越高,在室外应用场景下,单节锂电池计划已经越来越难满足设计需求了,对于音箱的设计者来说,两节锂电池串联设计已是更优的挑选。

两节锂电串联可以为音箱系统提供更高的供电,从而提高功放的输出功率。

现在市场上能够满足两节锂电供电的双声道音频功放的型号,比如TI的TPA3130D2/TPA3138D2/AD52068等,没有带AB/D类切换功能,无法彻低避开FM收音干扰;国内一些厂家也针对两节锂电的应用推出一些单声道AB/D类切换的功放IC,在两颗组合应用于驱动双音圈喇叭音响的时候,因每个芯片内部为D类功放调制提供时钟的都是自立的振荡源,芯片之间总有一定范围的频率偏差以及相位偏差,共同激励于一个喇叭上的两个自立的音圈共同的纸盘以及弹波时,尤其在功放输出没经过挺直接喇叭的状况下,喇叭的纸盘以及弹波就会浮现正常音乐以外的振动,终于浮现音乐以外的异响,即杂音。

为此,深圳市永阜康科技有限公司力推带随意限幅的高保真D类/AB类切换10W立体声功放IC-HT876,2.5V-9.8V宽泛的工作电压、完善适用于两节锂电串联的高端蓝牙音箱及双音圈拉杆音响等产品。

概述HT876是一款立体声D类和AB类音频功率。

在D类模式,VDD = 9.0V、THD+N=10%、4Ω负载、1kHz信号条件下,能延续输出2×10.9W功率。

HT876具有可随意配置的限幅(Limiter)功能。

限幅功能开启后,即使输入信号很大,音乐输出也能被限制在指定的功率和THD+N之内,满足不同音质体验和庇护喇叭的需求。

HT876还具有自动限温控制(TFB)功能,在高功率输出、高环境温度、AB类模式低效率等状况下导致芯片片内温度较高时,芯片能自动降低系统增益,避开芯片进入过温关断庇护模式,在保证音乐品质的前提下显著提升音乐峰值功率。

XL7046 1.0A 100KHz 100V降压型DC-DC转换器说明书

1.0A 100KHz 100V 降压型DC-DC转换器XL7046特点⏹最高输入电压100V⏹最大占空比85%⏹最小压差2.0V⏹输出电压从1.25V至20V可调⏹5V输出时最大1.0A输出电流⏹15V输出时最大0.5A输出电流⏹固定100KHz开关频率⏹最大输出功率小于8W⏹EN脚TTL关断功能⏹内置高压功率MOSFET⏹效率高达91%⏹出色的线性与负载调整率⏹内置限流功能⏹内置输出短路保护功能⏹SOP8-EP封装应用⏹电动车控制器供电⏹通信描述XL7046是一款高效、高压降压型DC-DC转换器,固定100KHz开关频率,可提供最高1.0A输出电流能力,低纹波,出色的线性调整率与负载调整率。

XL7046内置固定频率振荡器与频率补偿电路,简化了电路设计。

PWM控制环路可以调节占空比从0~85%之间线性变化。

图1. XL7046封装1.0A 100KHz 100V 降压型DC-DC 转换器 XL7046引脚配置CSNCSP VCVINSWENGNDFB12345678图2. XL7046引脚配置表1.引脚说明引脚号 引脚名 描述1 CSN 电流检测负端引脚。

2 CSP 电流检测正端引脚。

3 VC 内部电压调节器旁路电容引脚,需要在VIN 与VC 引脚之间连接1个1uF 电容。

4 VIN 电源输入引脚,需要在VIN 与GND 之间并联电容以消除噪声。

5 SW 功率开关输出引脚。

6 EN 使能引脚,高电平关机,低电平开机,悬空时为低电平,默认与GND 连接。

7 GND 接地引脚。

8FB反馈引脚,通过外部电阻分压网络,检测输出电压进行调整。

参考电压为1.25V 。

背部焊盘为SW1.0A 100KHz 100V 降压型DC-DC 转换器 XL7046方框图EABias current & Voltage ReferenceVINGND75mV 1.25VEA COMPOscillator100KHz/25KHzSWRS Latch and DriverFBStart Up UVLOCSNSwitchENVCocsCSP图3. XL7046方框图典型应用XL7046L1 100uH/2ACIN 47uF 100VC2105R210K 1%R13.3K 1%D1S310SWFBGNDVINVIN4587CFF 10nF COUT 100uF 35VR30.075Ω 1%C1104VOUT 5.0V/0~1.0AOUTPUT 5.0V/0~1.0A VOUT=1.25*(1+R2/R1)CSP 21CSNCC 105VC36ENR3用于限制最大输出电流,当VOUT ≤5V 时,R3选择0.075欧姆;当VOUT>5V 时,R3选择0.082欧姆。

NS4216 10W×2 D 类音频功率放大器 数据手册说明书

NS421610W×2D类音频功率放大器1特性●工作电压范围:5V-9V●输出功率:7W×2(7.4V/4Ω,THD=10%)10W×2(9V/4Ω,THD=10%)●最高可达92%效率(9V/8Ω)●电平设置工作模式●无需输出滤波器●差分输入●优异的“上电,掉电”噪声抑制●过流保护、过热保护、欠压保护●eTSSOP-24封装2应用范围●蓝牙音响●移动音箱扩音器●其他消费类音频设备3说明NS4216是一款差分输入,超低EMI,无需滤波器,20W(10W×2)双声道D类音频功率放大器。

芯片有两个控制端分别控制芯片的左右声道,可通过高低电平控制芯片的工作模式:LCTRL/RCTRL 脚电压为高电平时,芯片的L/R通道进入工作模式,低电平时芯片关断,应用灵活方便。

NS4216采用先进的技术,在全带宽范围内极大地降低了EMI干扰,最大限度地减少了对其他外部元件的影响。

其输出无需滤波器的PWM调制结构减少了外部元件、PCB面积和系统成本。

NS4216在9V的工作电压时,能够向4Ω负载提供高达20W(10W×2)的输出功率,90%以上的效率更加适合便携式音频系统。

NS4216内置过流保护、过热保护及欠压保护功能,有效保护芯片在异常工作状况下不被损坏。

NS4216提供eTSSOP-24封装,额定的工作温度范围为-40℃至85℃。

4典型应用电路5管脚配置编号管脚名称管脚描述1,2,13,14GND地3,4VOPL左声道正输出5VREFL左声道电压基准6LCTRL左模式控制端7RINN右声道负输入8RINP右声道正输入9,10VONR右声道负输出11,12,23,24PVCC功率电源输入15,16VOPR右声道正输出17VREFR右声道电压基准18RCTRL右模式控制端19LINN左声道负输入20LINP左声道正输入21,22VONL左声道负输出6极限工作参数●输入电压范围5V~9V ●CTRL管脚电压0V~5V ●ESD电压2000V ●工作温度范围-40℃~+150℃●存储温度范围-65℃~+150℃●最大结温+150℃●焊接温度(10s内)+260℃●θJC/θJA10/60o C/W 注:超过上述极限工作参数范围可能导致芯片永久性的损坏。

8760电子产品数据手册说明书

Product: 8760 Electronic, 2 C #18 Str TC, PE Ins, OS, PVC Jkt, CM