ATMEL公司24系列EEPROM编程举例

串行EEPROM AT24CXX芯片资料

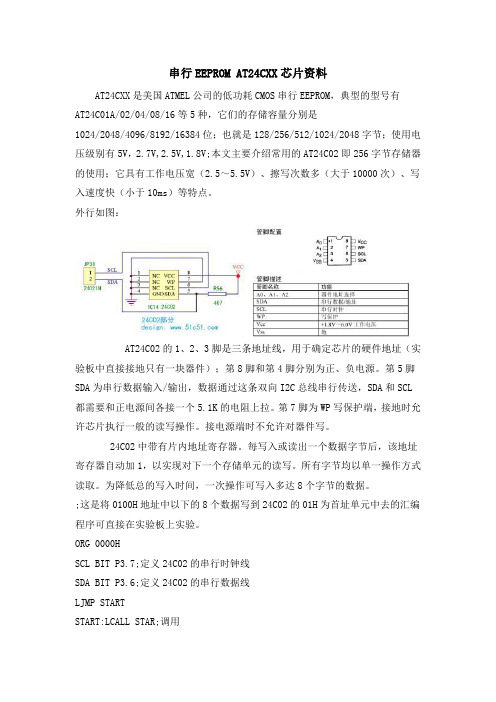

串行EEPROM AT24CXX芯片资料AT24CXX是美国ATMEL公司的低功耗CMOS串行EEPROM,典型的型号有AT24C01A/02/04/08/16等5种,它们的存储容量分别是1024/2048/4096/8192/16384位;也就是128/256/512/1024/2048字节;使用电压级别有5V,2.7V,2.5V,1.8V;本文主要介绍常用的AT24C02即256字节存储器的使用;它具有工作电压宽(2.5~5.5V)、擦写次数多(大于10000次)、写入速度快(小于10ms)等特点。

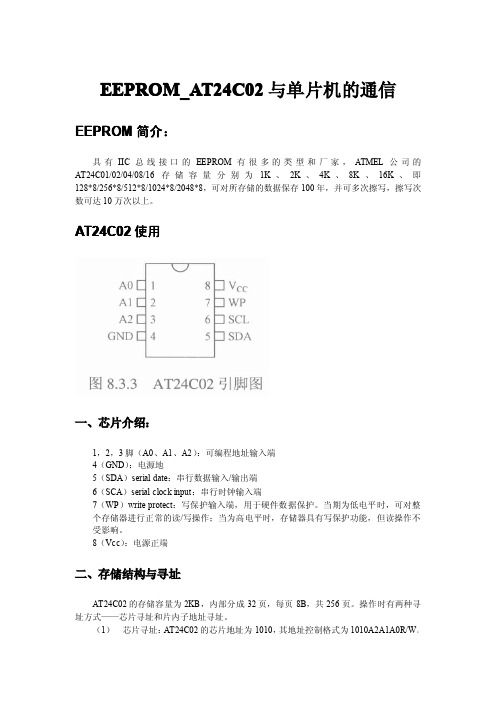

外行如图:AT24C02的1、2、3脚是三条地址线,用于确定芯片的硬件地址(实验板中直接接地只有一块器件);第8脚和第4脚分别为正、负电源。

第5脚SDA为串行数据输入/输出,数据通过这条双向I2C总线串行传送,SDA和SCL都需要和正电源间各接一个5.1K的电阻上拉。

第7脚为WP写保护端,接地时允许芯片执行一般的读写操作。

接电源端时不允许对器件写。

24C02中带有片内地址寄存器。

每写入或读出一个数据字节后,该地址寄存器自动加1,以实现对下一个存储单元的读写。

所有字节均以单一操作方式读取。

为降低总的写入时间,一次操作可写入多达8个字节的数据。

;这是将0100H地址中以下的8个数据写到24C02的01H为首址单元中去的汇编程序可直接在实验板上实验。

ORG 0000HSCL BIT P3.7;定义24C02的串行时钟线SDA BIT P3.6;定义24C02的串行数据线LJMP STARTSTART:LCALL STAR;调用MOV R2,#08H;一个数据有8位MOV DPTR,#0100H;定义源数据的位置LOOP:MOV A,#00HMOVC A,@A+DPTRLCALL SDATALCALL ACKJC LOOPINC DPTRDJNZ R2,LOOPLCALL STOP;调用停止子程序STAR:SETB SDASETB SCLNOPNOPNOPNOPCLR SDANOPNOPNOPNOPCLR SCLRETSDATA:MOV R0,#08HLOOP0:RLC AMOV SDA,CNOPNOPSETB SCLNOPNOPNOPCLR SCLDJNZ R0,LOOP0 RETACK:SETB SDA NOPNOPSETB SCL NOPNOPNOPNOPMOV C,SDA CLR SCLRETSTOP:CLR SDA NOPNOPNOPNOPSETB SCL NOPNOPNOPNOPSETB SDANOPNOPNOPRETORG 0100HDB 0A0H,10H,01H,02H,03H,04H,05H,06HEND读写子程序如下:;写串行E2PROM子程序XEPR; R3=10100000(命令1010+器件3位地址+读/写。

串行eepromat24cxx芯片资料

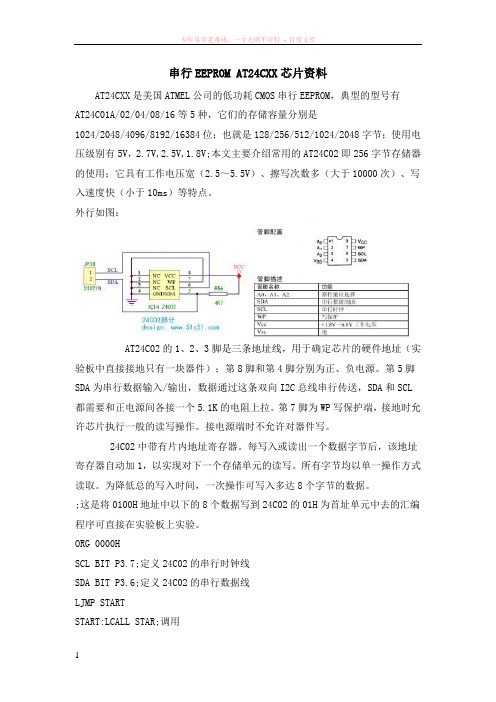

串行EEPROM AT24CXX芯片资料AT24CXX是美国ATMEL公司的低功耗CMOS串行EEPROM,典型的型号有AT24C01A/02/04/08/16等5种,它们的存储容量分别是1024/2048/4096/8192/16384位;也就是128/256/512/1024/2048字节;使用电压级别有5V,2.7V,2.5V,1.8V;本文主要介绍常用的AT24C02即256字节存储器的使用;它具有工作电压宽(2.5~5.5V)、擦写次数多(大于10000次)、写入速度快(小于10ms)等特点。

外行如图:AT24C02的1、2、3脚是三条地址线,用于确定芯片的硬件地址(实验板中直接接地只有一块器件);第8脚和第4脚分别为正、负电源。

第5脚SDA为串行数据输入/输出,数据通过这条双向I2C总线串行传送,SDA和SCL 都需要和正电源间各接一个5.1K的电阻上拉。

第7脚为WP写保护端,接地时允许芯片执行一般的读写操作。

接电源端时不允许对器件写。

24C02中带有片内地址寄存器。

每写入或读出一个数据字节后,该地址寄存器自动加1,以实现对下一个存储单元的读写。

所有字节均以单一操作方式读取。

为降低总的写入时间,一次操作可写入多达8个字节的数据。

;这是将0100H地址中以下的8个数据写到24C02的01H为首址单元中去的汇编程序可直接在实验板上实验。

ORG 0000HSCL BIT P3.7;定义24C02的串行时钟线SDA BIT P3.6;定义24C02的串行数据线LJMP STARTSTART:LCALL STAR;调用MOV R2,#08H;一个数据有8位MOV DPTR,#0100H;定义源数据的位置LOOP:MOV A,#00HMOVC A,@A+DPTRLCALL SDATALCALL ACKJC LOOPINC DPTRDJNZ R2,LOOPLCALL STOP;调用停止子程序STAR:SETB SDASETB SCLNOPNOPNOPNOPCLR SDANOPNOPNOPNOPCLR SCLRETSDATA:MOV R0,#08HLOOP0:RLC AMOV SDA,CNOPNOPSETB SCLNOPNOPNOPCLR SCLDJNZ R0,LOOP0 RETACK:SETB SDA NOPNOPSETB SCL NOPNOPNOPNOPMOV C,SDA CLR SCLRETSTOP:CLR SDA NOPNOPNOPNOPSETB SCL NOPNOPNOPNOPSETB SDANOPNOPNOPRETORG 0100HDB 0A0H,10H,01H,02H,03H,04H,05H,06HEND读写子程序如下:;写串行E2PROM子程序XEPR; R3=10100000(命令1010+器件3位地址+读/写。

EEPROM AT24C02 实验

EEPROM AT24C02 实验实验要求利用24C02 断电以后存储的数据不消失的特点,可以做一个断电保护装置。

首先利用单片机做一个0-99 秒的自动计时器。

然后随机关断电源,在通电以后计时器接着断电前的状态继续计时。

实验目的掌握IIC 总线工作原理及其操作方法,视频中有一讲专门讲IIC。

说明:首先简单的说明以下I2C 总线,I2C 总线是一种串行数据总线,只有二根信号线,一根是双向的数据线SDA,另一根是时钟线SCL。

在I2C 总线上传送的一个数据字节由八位组成。

总线对每次传送的字节数没有限制,但每个字节后必须跟一位应答位。

数据传送首先传送最高位(MSB)。

首先由主机发出启动信号“S”(SDA 在SCL 高电平期间由高电平跳变为低电平),然后由主机发送一个字节的数据。

启动信号后的第一个字节数据具有特殊含义:高七位是从机的地址,第八位是传送方向位,0 表示主机发送数据(写),1 表示主机接收数据(读)。

被寻址到的从机设备按传送方向位设置为对应工作方式。

标准I2C 总线的设备都有一个七位地址,所有连接在I2C 总线上的设备都接收启动信号后的第一个字节,并将接收到的地址与自己的地址进行比较,如果地址相符则为主机要寻访的从机,应答在第九位时钟脉冲时向SDA 线送出低电平作为应答。

除了第一字节是通用呼叫地址之外第二字节开始即数据字节。

数据传送完毕,由主机发出停止信号“P”(SDA 在SCL 高电平期间由低电平跳变为高电平)。

AT24C 系列串行E2PROM 具有I2C 总线接口功能,功耗小,宽电源电压(根据不同型号2.5V~6.0V),工作电流约为3mA,静态电流随电源电压不同为30μA~110μA。

由于I2C 总线可挂接多个串行接口器件,在I2C 总线中每个器件应有唯一的器件地址,按I2C 总线规则,器件地址为7 位数据(即一个I2C 总线系统中理论上可挂接128 个不同地址的器件),它和1 位数据方向位构成一个器件寻址字节,最低位D0 为方向位(读/写)。

ATMEL 24c02使用详解(汇编及C程序都有)

ATMEL 24c02使用详解原文地址: /Blog/cns!2FEAB5F0F11F7A67!296.entryATMEL 24c02使用详解I2C总线是一种用于IC器件之间连接的二线制总线。

它通过SDA(串行数据线)及SCL (串行时钟线)两根线在连到总线上的器件之间传送信息,并根据地址识别每个器件:不管是单片机、存储器、LCD驱动器还是键盘接口。

1.I2C总线的基本结构采用I2C总线标准的单片机或IC器件,其内部不仅有I2C 接口电路,而且将内部各单元电路按功能划分为若干相对独立的模块,通过软件寻址实现片选,减少了器件片选线的连接。

CPU不仅能通过指令将某个功能单元电路挂*或摘离总线,还可对该单元的工作状况进行检测,从而实现对硬件系统的既简单又灵活的扩展与控制。

I2C总线接口电路结构如图1所示。

2.双向传输的接口特性传统的单片机串行接口的发送和接收一般都各用一条线,如MCS51系列的TXD和RXD,而I2C总线则根据器件的功能通过软件程序使其可工作于发送或接收方式。

当某个器件向总线上发送信息时,它就是发送器(也叫主器件),而当其从总线上接收信息时,又成为接收器(也叫从器件)。

主器件用于启动总线上传送数据并产生时钟以开放传送的器件,此时任何被寻址的器件均被认为是从器件。

I2C总线的控制完全由挂接在总线上的主器件送出的地址和数据决定。

在总线上,既没有中心机,也没有优先机。

总线上主和从(即发送和接收)的关系不是一成不变的,而是取决于此时数据传送的方向。

SDA和SCL均为双向I/O线,通过上拉电阻接正电源。

当总线空闲时,两根线都是高电平。

连接总线的器件的输出级必须是集电极或漏极开路,以具有线“与”功能。

I2C总线的数据传送速率在标准工作方式下为100kbit/s,在快速方式下,最高传送速率可达400kbit/s。

3.I2C总线上的时钟信号在I2C总线上传送信息时的时钟同步信号是由挂接在SCL 时钟线上的所有器件的逻辑“与”完成的。

24C02 EEPROM存储器的C语言操作【范本模板】

#include 〈reg51。

h〉#ifndef false#define false 0#endif#ifndef true#define true 1#endif#define WriteDeviceAddress 0xa0#define ReadDviceAddress 0xa1sbit SDA = P3 ^ 5; //根据实际连接的管脚定义sbit SCL = P3 ^ 4;sbit led = P1^0;sbit led2 = P1^1;unsigned char code Num[21]={0xc0,0xf9,0xa4,0xb0,0x99,0x92,0x82,0xf8,0x80,0x90,0x40,0x79,0x24,0x30,0x19,0x12,0x02,0x78,0x00,0x10,0x89};unsigned char code Disdigit[4]= {0x7F,0xBF,0xDF,0xEF};unsigned char Disbuf[4];unsigned char code write_data[5] = { 5,2,5,1,8 };unsigned char read_data[5];//--—-————-—--——--—--—-—-——-—--—-—-——-—----——————-—-----———-——-—--————-—-———void Delayus(unsigned int number){for(;number!=0;number-—){}}//-—----—-----—---———--—-—--—----—--——----———-—--—--—--—--—----—---————--——-void DelayMs(unsigned int number){unsigned char temp;for(;number!=0;number——){for(temp=112;temp!=0;temp-—){}}}//—---————----—--—---——----———---—--——-——-----—-——--—---—---—--———-----——-——void Start(){SDA=1;Delayus(4);SCL=1;Delayus(4);SDA=0;Delayus(4);SCL=0;Delayus(4);}//---—-----—————--—-——---——---—-—-------—----—-—-——-——————---—--------------void Stop(){SCL=0;Delayus(4);SDA=0;Delayus(4);SCL=1;Delayus(4);SDA=1;Delayus(4);}//--—-—-————-—---—-——--———-—-———--———--——-————-—--———-————-—-———--————-—----void Ack(){SDA=0;Delayus(4);SCL=1;Delayus(4);SCL=0;Delayus(4);Delayus(4);}//—--——-—-———-——-—-—-—-——-——-——--————--—--—----—-——-—--———--—---————-———--——void NoAck(){SDA=1;Delayus(4);SCL=1;Delayus(4);SCL=0;Delayus(4);SDA=0;//}//-——----———-————————-—-—-——--—-——-—-——-—--—--—-———-——---—————-—----——-—--——bit TestAck(){bit ErrorBit;SDA=1;Delayus(4);SCL=1;Delayus(4);ErrorBit=SDA;Delayus(4);SCL=0;return(ErrorBit);}//-——-———-—-——--—-——----————-—-—--————-—-——-—-—---———————------——-—--—-—----void Write8Bit(unsigned char input){unsigned char temp;for(temp=8;temp!=0;temp-—){SDA=(bit)(input&0x80);Delayus(4);Delayus(4);SCL=0;Delayus(4);input=input〈〈1;}}//—-——--———----—-—-————--——---—---—---——---—-----——-——-——-————-—--—---———-—-unsigned char Read8Bit(){unsigned char temp,rbyte=0;for(temp=8;temp!=0;temp-—){SCL=1;Delayus(4);rbyte=rbyte<〈1;rbyte=rbyte|((unsigned char)(SDA));SCL=0;}return(rbyte);}void Write24c02(unsigned char *Wdata,unsigned char RomAddress,unsigned char number){Start();Write8Bit(WriteDeviceAddress);TestAck();Write8Bit(RomAddress);TestAck();for(;number!=0;number—-){Write8Bit(*Wdata);TestAck();Wdata++;}Stop();DelayMs(10);}void Read24c02(unsigned char *RamAddress,unsigned char RomAddress,unsigned char bytes){Start();Write8Bit(WriteDeviceAddress);TestAck();Write8Bit(RomAddress);TestAck();Start();Write8Bit(ReadDviceAddress);TestAck();while(bytes!=1){*RamAddress=Read8Bit();Ack();RamAddress++;bytes——;}*RamAddress=Read8Bit();NoAck();Stop();}void Display(void) //显示{unsigned int i = 0;unsigned int temp,count;temp = Disdigit[count];P2 =temp;temp = Disbuf[count];temp = Num[temp];P0 =temp;count++;if (count==4)count=0;}void time1() interrupt 3 using 2{Display();TH1 = (65535 - 2000)/256;TL1 = (65535 - 2000)%256;}void main(){TMOD = 0x15;TR1 = 1;EA = 1;ET1 = 1;Write24c02(write_data,0x00,3); DelayMs(200);Read24c02(read_data,0x00,4); while(1){Disbuf[0] = read_data[0];Disbuf[1]= read_data[1];Disbuf[2]= read_data[2];Disbuf[3] = read_data[3];}}。

24Cxx I2C EEPROM字节读写驱动程序

_nop_();_nop_();_nop_();_nop_();_nop_();_nop_(); //Thd:STA

SCL=0; //START

write_8bit(0xa0 | page); //写页地址和操作方式,对于24C32-24C256,page不起作用

ACK(ห้องสมุดไป่ตู้;

if(eepromtype>IIC24C16) //如果是24C01-24C16,地址为一字节;24C32-24C256,地址为二字节

调用方式:void WriteIIC_24CXX(enum EEPROMTYPE eepromtype,unsigned int address,unsigned char ddata) ﹫2001/09/18

函数说明:对于IIC芯片24CXX,在指定地址address写入一个字节ddata

SDA=0;

_nop_();_nop_();_nop_();_nop_();_nop_();_nop_(); //Thd:STA

SCL=0; //START

write_8bit( (address<<1) | 0x01); //写页地址和操作方式

ACK();

while (i--)

{

SDA=1;

#include "reg51.h"

#include "intrins.h"

sbit SCL= P2^7;

sbit SDA= P2^6;

enum EEPROMTYPE {IIC24C01,IIC24C01A,IIC24C02,IIC24C04,IIC24C08,IIC24C16,IIC24C32,IIC24C64,IIC24C128,IIC24C256};

at24c128程序范例

AT24C128是一种串行EEPROM(电可擦可编程只读存储器)芯片,通常用于存储小量的数据,比如配置参数或设备状态。

它可以通过I2C总线与微控制器进行通信。

以下是一个简单的示例程序,展示了如何使用AT24C128 EEPROM芯片。

这个例子使用的是C语言,适用于常见的微控制器,如基于AVR或PIC的微控制器。

请注意,你需要根据你的具体硬件和开发环境来调整代码。

```c#include <i2c.h> // 包含I2C库函数// 定义AT24C128的I2C地址#define EEPROM_SLAVE_ADDRESS 0x50// 定义要写入的数据uint8_t data_to_write[2] = {0x01, 0x02};// 定义EEPROM的页大小#define EEPROM_PAGE_SIZE 32// 定义EEPROM的页地址uint8_t page_address = 0;// 函数声明void write_byte(uint8_t address, uint8_t value);void write_data(uint8_t page, uint8_t *data, uint8_t length);int main() {// 初始化I2C总线i2c_init();// 写入数据到EEPROMwrite_data(page_address, data_to_write, sizeof(data_to_write));// 其他代码...// 主循环while(1) {// 读取EEPROM中的数据// 其他代码...}}// 函数定义void write_byte(uint8_t address, uint8_t value) {// 写入一个字节到EEPROM的指定地址// 实现细节取决于你的硬件和I2C库}void write_data(uint8_t page, uint8_t *data, uint8_t length) {// 将数据写入EEPROM的指定页面// 实现细节取决于你的硬件和I2C库// 确保写入的数据不超过EEPROM页的大小if (length > EEPROM_PAGE_SIZE) {length = EEPROM_PAGE_SIZE;}// 写入数据// 实现细节取决于你的硬件和I2C库}```请注意,这个示例程序是非常基础的,它没有包含错误检查和处理,也没有实现具体的I2C 通信细节。

24c02参考实例程序

{

Scl=0; _nop_();_nop_();_nop_();_nop_();_nop_(); Scl=1; _nop_();_nop_();_nop_();_nop_();_nop_(); if(Sda)

temp=temp|0x01; else

temp=temp&0xfe;

if(BitCounter-1) { temp1=temp<<1; temp=temp1; } BitCounter--; }

Ack();

*(PData+i)=Read();//读数据

Scl=0;

NoAck();

Stop();

}

}

/*------------------------------------------------

主程序

------------------------------------------------*/

sbit Sda=P1^2; sbit Scl=P1^1; sbit WP=P1^0;

//定义总线连接端口 //写保护,这里不使用

/*-----------------------------------------------延时程序

------------------------------------------------*/ void mDelay(unsigned char j) { unsigned int i; for(;j>0;j--) { for(i=0;i<125;i++) {;} } }

void main()

{

unsigned char Number[4]={0x06,0x5b,0x4f,0x66};// 显示码值 1234

I2C总线编程实例(k1-k4:写入、读取、加+、清零)【EEPROM-AT24C02】

I2C总线编程实例(k1-k4:写⼊、读取、加+、清零)【EEPROM-AT24C02】(1)AT24C02是⼀种EEPROM元器件,是⼀种只读寄存器,断电保持,可保存数据100年, 是⼀种可擦除读写的芯⽚,相当于ROM硬盘,在下⾯实验中充当从机⾓⾊;(2)51在下⾯实验中充当主机⾓⾊;(3)在IIC总线标准协议上,进⾏51单⽚机(主机)和AT24C02(从机)的相互读写数据的操作。

⼩结:51单⽚机和各种EEPROM芯⽚之间可以通过IIC总线标准协议进⾏数据交互(通信)的。

实验:四个独⽴按键对应四个不同的功能,k1:将数据写⼊单⽚机,断电保存k2:读取上次保存的数据,断电后仍可读取上次保存的数据k3:当前数据+1k4:当前数据清零------------------------------------------------------------- 采⽤多⽂件的框架模式 -------------------------------------------------------------i2c.h:/*这个⽂件进⾏宏定义:定义I2C串⾏总线的相关数据端⼝、⽅法函数,以及定义⼀些使⽤频率较⾼的元素*/#ifndef _I2C_H_ // 如果没有定义宏#define _I2C_H_ // 定义⼀个宏// 需要⽤到51单⽚机的管脚,所以需要引⼊库⽂件#include <reg52.h>// 查单⽚机原理图可知(其中,SCL是时钟线,SDA是数据线)sbit SCL=P2^1;sbit SDA=P2^0;/* 相关函数 */// I2C的起始信号函数void I2cStart();// I2C的终⽌信号函数void I2cStop();// I2C发送(写⼊)字节函数,成功返回1,失败返回0unsigned char I2cSendByte(unsigned char dat);// I2C接收(读取)字节函数,返回读取的数据unsigned char I2cReadByte();// AT24C02芯⽚的写⼊数据函数void At24c02Write(unsigned char addr, unsigned dat);// AT24C02芯⽚的读取数据函数,返回读取的数据unsigned char At24c02Read(unsigned char addr);#endif // 结束i2c.c:/* 这个⽂件专门针对I2C模块的编程,其他模块可以新建另外⼀个⽂件 */#include <i2c.h> // 引⼊I2C的库⽂件/******************************************************************************** 函数名 : Delay10us()* 函数功能 : 延时10us* 输⼊ : ⽆* 输出 : ⽆*******************************************************************************/void Delay10us() //误差 0usunsigned char a,b;for(b=1;b>0;b--)for(a=2;a>0;a--);}/******************************************************************************** 函数名 : I2cStart()* 函数功能 : 起始信号:在SCL时钟信号在⾼电平期间SDA信号产⽣⼀个下降沿* 输⼊ : ⽆* 输出 : ⽆* 备注 : 起始之后SDA和SCL都为0,表⽰总线被主机占⽤*******************************************************************************/void I2cStart(){// 根据各个单⽚机的时序图来写SDA=1;Delay10us();SCL=1;Delay10us(); // 建⽴时间是SDA保持时间>4.7usSDA=0;Delay10us(); // 保持时间是>4usSCL=0;Delay10us();}/******************************************************************************** 函数名 : I2cStop()* 函数功能 : 终⽌信号:在SCL时钟信号⾼电平期间SDA信号产⽣⼀个上升沿* 输⼊ : ⽆* 输出 : ⽆* 备注 : 结束之后保持SDA和SCL都为1;表⽰总线处于空闲状态*******************************************************************************/void I2cStop(){// 根据各个单⽚机的时序图来写SDA=0;Delay10us();SCL=1;Delay10us(); // 建⽴时间是SDA保持时间>4.7usSDA=1;Delay10us(); // 保持时间是>4us}/******************************************************************************** 函数名 : I2cSendByte(unsigned char dat)* 函数功能 : 通过I2C发送⼀个字节。

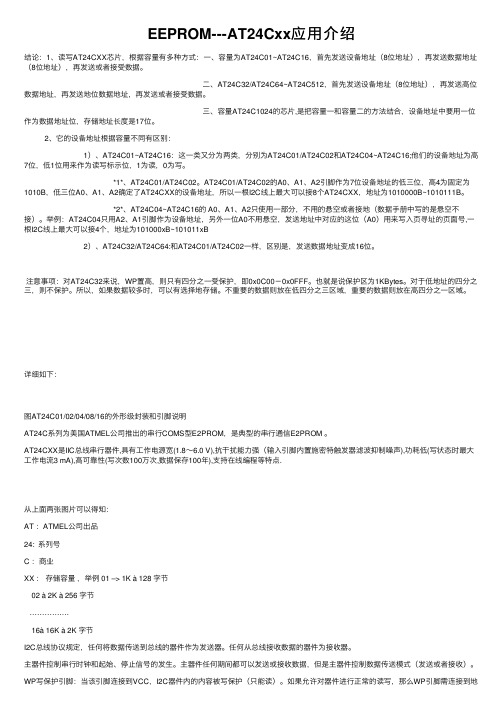

EEPROM---AT24Cxx应用介绍

EEPROM---AT24Cxx应⽤介绍结论:1、读写AT24CXX芯⽚,根据容量有多种⽅式:⼀、容量为AT24C01~AT24C16,⾸先发送设备地址(8位地址),再发送数据地址(8位地址),再发送或者接受数据。

⼆、AT24C32/AT24C64~AT24C512,⾸先发送设备地址(8位地址),再发送⾼位数据地址,再发送地位数据地址,再发送或者接受数据。

三、容量AT24C1024的芯⽚,是把容量⼀和容量⼆的⽅法结合,设备地址中要⽤⼀位作为数据地址位,存储地址长度是17位。

2、它的设备地址根据容量不同有区别: 1)、AT24C01~AT24C16:这⼀类⼜分为两类,分别为AT24C01/AT24C02和AT24C04~AT24C16;他们的设备地址为⾼7位,低1位⽤来作为读写标⽰位,1为读,0为写。

*1*、AT24C01/AT24C02。

AT24C01/AT24C02的A0、A1、A2引脚作为7位设备地址的低三位,⾼4为固定为1010B,低三位A0、A1、A2确定了AT24CXX的设备地址,所以⼀根I2C线上最⼤可以接8个AT24CXX,地址为1010000B~1010111B。

*2*、AT24C04~AT24C16的 A0、A1、A2只使⽤⼀部分,不⽤的悬空或者接地(数据⼿册中写的是悬空不接)。

举例:AT24C04只⽤A2、A1引脚作为设备地址,另外⼀位A0不⽤悬空,发送地址中对应的这位(A0)⽤来写⼊页寻址的页⾯号,⼀根I2C线上最⼤可以接4个,地址为101000xB~101011xB 2)、AT24C32/AT24C64:和AT24C01/AT24C02⼀样,区别是,发送数据地址变成16位。

注意事项:对AT24C32来说,WP置⾼,则只有四分之⼀受保护,即0x0C00-0x0FFF。

也就是说保护区为1KBytes。

对于低地址的四分之三,则不保护。

所以,如果数据较多时,可以有选择地存储。

EEPROM_AT24C02_笔记

AT24C02 使用

一、芯片介绍:

1,2,3 脚(A0 、A1 、A2 ) :可编程地址输入端 4(GND) :电源地 5(SDA)serial date:串行数据输入/输出端 6(SCA)serial clock input :串行时钟输入端 7(WP )write protect:写保护输入端,用于硬件数据保护。当期为低电平时,可对整 个存储器进行正常的读/写操作;当为高电平时,存储器具有写保护功能,但读操作不 受影响。 8(Vcc) :电源正端

}

二、存储结构与寻址

AT24C02 的存储容量为 2KB ,内部分成 32 页,每页 8B,共 256 页。操作时有两种寻芯片地址为 1010, 其地址控制格式为 1010A2A1A0R/W 。

其中 A2 、A1 、A0 为可编程地址选择位。A2 、A1、A0 引脚接高、低电平得到 确定的三位编码,与 1010 形成 7 位编码,即为该器件的地址码。R/W 位芯片 读写控制位,该位为 0,表示对芯片进行写操作;该位为 1,表示对芯片进行读 操作。 (2) 片内子地址寻址:芯片寻址可对内部 256B 中的任一个进行读/写操作,其寻址 范围为 00~FF,共 256 个寻址单位。

(2)指定地址连续读,此种方式的读地址控制与前面指定地址读相同,单片机接 收到每一个字节数据后应做出应答,只要 EEPROM 检测到应答信号,其内部的地址寄 存器就自动加 1,指向下一个单元,并顺序将指向的单元的数据送到 SDA 串行数据线 上。 当需要结束读操作时, 单片机接收到数据后在需要应答的时刻发送一个非应答信号, 接着再发送一个停止信号即可。这种读操作的数据帧格式如图 8.3.8 所示。

芯片操作时序图:对应后面的程序理解

总线时序图

AT24C1024B 1024K EEPROM 产品说明书

Features•Low-voltage Operation–1.8V(V CC=1.8V to3.6V)–2.5V(V CC=2.5V to5.5V)•Internally Organized131,072x8•Two-wire Serial Interface•Schmitt Triggers,Filtered Inputs for Noise Suppression•Bidirectional Data Transfer Protocol•400kHz(1.8V)and1MHz(5V,2.5V)Clock Rate•Write Protect Pin for Hardware and Software Data Protection•256-byte Page Write Mode(Partial Page Writes Allowed)•Random and Sequential Read Modes•Self-timed Write Cycle(5ms Typical)•High Reliability–Endurance:1,000,000Write Cycles/Page–Data Retention:40Years•8-lead PDIP,8-lead JEDEC SOIC,8-lead EIAJ SOIC,8-lead TSSOP,8-lead Ultra Thin Small Array(SAP),and8-ball dBGA2Packages•Die Sales:Wafer Form,Tape and Reel and Bumped DieDescriptionThe AT24C1024B provides1,048,576bits of serial electrically erasable and program-mable read only memory(EEPROM)organized as131,072words of8bits each.The device’s cascadable feature allows up to four devices to share a common two-wire bus.The device is optimized for use in many industrial and commercial applications where low-power and low-voltage operation are essential.The devices are available in space-saving8-lead PDIP,8-lead JEDEC SOIC,8-lead EIAJ SOIC,8-lead TSSOP, 8-ball dBGA2and8-lead Ultra Thin SAP packages.In addition,the entire family is available in1.8V(1.8V to3.6V)and2.5V(2.5V to5.5V)versions.8-lead PDIP12348765NCA1A2GNDVCCWPSCLSDA8-lead TSSOP12348765VCCWPSCLSDANCA1A2GND8-lead SOIC12348765NCA1A2GNDVCCWPSCLSDA8-lead Ultra-Thin SAPBottom ViewVCCWPSCLSDANCA1A2GND123487658-lead dBGA2Bottom ViewVCCWPSCLSDANCA1A2GND1234876525194F–SEEPR–1/08AT24C1024B1.Absolute Maximum Ratings**NOTICE:Stresses beyond those listed under “Absolute Maximum Ratings”may cause permanent dam-age to the device.This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied.Exposure to absolute maximum rating conditions for extended periods may affect device reliability.35194F–SEEPR–1/08AT24C1024BFigure 1-1.Block Diagram2.Pin DescriptionSERIAL CLOCK (SCL):The SCL input is used to positive edge clock data into each EEPROM device and negative edge clock data out of each device.SERIAL DATA (SDA):The SDA pin is bi-directional for serial data transfer.This pin is open-drain driven and may be wire-ORed with any number of other open-drain or open-collector devices.DEVICE/ADDRESSES (A1/A2):The A1,A2pin is a device address input that can be hardwired or left not connected for hardware compatibility with other AT24Cxx devices.When the A1,A2pins are hardwired,as many as four 1024K devices may be addressed on a single bus system (device addressing is discussed in detail under the Device Addressing section).If the A1/A2pins are left floating,the A1/A2pin will be internally pulled down to GND if the capacitive coupling to the circuit board V CC plane is <3pF.If coupling is >3pF,Atmel recommends connecting the A1/A2pin to GND.WRITE PROTECT (WP):The write protect input,when connected to GND,allows normal write operations.When WP is connected high to V CC ,all write operations to the memory are inhibited.If the pin is left floating,the WP pin will be internally pulled down to GND if the capacitive cou-pling to the circuit board V CC plane is <3pF.If coupling is >3pF,Atmel recommends connecting the pin to GND.Switching WP to V CC prior to a write operation creates a software write-protectfunction.VCC GND WP SCL SDAA 2A 1A 045194F–SEEPR–1/08AT24C1024B3.Memory OrganizationAT24C1024B,1024K SERIAL EEPROM:The 1024K is internally organized as 512pages of 256bytes each.Random word addressing requires a 17-bit data word address.IL IH Table 3-1.Pin Capacitance (1)Table 3-2.DC CharacteristicsTable 3-3.AC Characteristics (Industrial Temperature)Applicable over recommended operating range from T AI =-40︒C to +85︒C,V CC =+1.8V to +3.6V,CL =100pF (unless oth-55194F–SEEPR–1/08AT24C1024B2.AC measurement conditions:R L (connects to V CC ):1.3k Ω(2.5V,5V),10k Ω(1.8V)Input pulse voltages:0.3V CC to 0.7V CC Input rise and fall times:≤50nsInput and output timing reference voltages:0.5V CC4.Device OperationCLOCK and DATA TRANSITIONS:The SDA pin is normally pulled high with an external device.Data on the SDA pin may change only during SCL low time periods (see Figure 4-4on page 7).Data changes during SCL high periods will indicate a start or stop condition as defined below.START CONDITION:A high-to-low transition of SDA with SCL high is a start condition which must precede any other command (see Figure 4-5on page 8).Table 3-3.AC Characteristics (Industrial Temperature)Applicable over recommended operating range from T AI =-40︒C to +85︒C,V CC =+1.8V to +3.6V,CL =100pF (unless oth-65194F–SEEPR–1/08AT24C1024BSTOP CONDITION:A low-to-high transition of SDA with SCL high is a stop condition.After a read sequence,the Stop command will place the EEPROM in a standby power mode (see Fig-ure 4-5on page 8).ACKNOWLEDGE:All addresses and data words are serially transmitted to and from the EEPROM in 8-bit words.The EEPROM sends a zero during the ninth clock cycle to acknowl-edge that it has received each word.STANDBY MODE:The AT24C1024B features a low-power standby mode which is enabled:a)upon power-up and b)after the receipt of the stop bit and the completion of any internal operations.SOFTWARE RESET:After an interruption in protocol,power loss or system reset,any 2-wire part can be protocol reset by following these steps:(a)Create a start bit condition,(b)clock 9cycles,(c)create another start bit followed by stop bit condition as shown below.The device is ready for next communication after above steps have been completed.Figure 4-1.Software ResetFigure 4-2.Bus Timing (SCL:Serial Clock,SDA:Serial Data I/O ®)SCLSDASCLSDA INSDA OUT75194F–SEEPR–1/08AT24C1024BFigure 4-3.Write Cycle Timing (SCL:Serial Clock,SDA:Serial Data I/O)Note:1.The write cycle time t WR is the time from a valid stop condition of a write sequence to the end of the internal clear/write cycle.Figure 4-4.DataValiditySTOP CONDITIONSTART CONDITIONSCLSDASDASCLDAT A STABLEDAT A STABLEDAT A CHANGE85194F–SEEPR–1/08AT24C1024BFigure 4-5.Start and Stop DefinitionFigure 4-6.Output Acknowledge5.Device AddressingThe 1024K EEPROM requires an 8-bit device address word following a start condition to enable the chip for a read or write operation (see Figure 7-1on page 11).The device address word con-sists of a mandatory one,zero sequence for the first four most significant bits as shown.This is common to all two-wire EEPROM devices.The 1024K uses the two device address bit,A1,A2,to allow up to four devices on the same bus.These A1,A2bits must compare to the corresponding hardwired input pins.The A1,A2pin uses an internal proprietary circuit that biases it to a logic low condition if the pin is allowed to float.The seventh bit (P 0)of the device address is a memory page address bit.This memory page address bit is the most significant bit of the data word address that follows.The eighth bit of the device address is the read/write operation select bit.A read operation is initiated if this bit is high and a write operation is initiated if this bit is low.Upon a compare of the device address,the EEPROM will output a zero.If a compare is not made,the device will return to astandby state.SDASCLSTART STOPSCLDAT A INDAT A OUTSTART ACKNOWLEDGE98195194F–SEEPR–1/08AT24C1024BDATA SECURITY:The AT24C1024B has a hardware data protection scheme that allows the user to write-protect the entire memory when the WP pin is at V CC .6.Write OperationsBYTE WRITE:To select a data word in the 1024K memory requires a 17-bit word address.The word address field consists of the P 0bit of the device address,then the most significant word address followed by the least significant word address (see Figure 7-2on page 11)A write operation requires the P 0bit and two 8-bit data word addresses following the device address word and acknowledgment.Upon receipt of this address,the EEPROM will again respond with a zero and then clock in the first 8-bit data word.Following receipt of the 8-bit data word,the EEPROM will output a zero.The addressing device,such as a microcontroller,then must terminate the write sequence with a stop condition.At this time the EEPROM enters an internally timed write cycle,T WR ,to the nonvolatile memory.All inputs are disabled during this write cycle and the EEPROM will not respond until the write is complete (see Figure 7-2on page 11).PAGE WRITE:The 1024K EEPROM is capable of 256-byte page writes.A page write is initiated the same way as a byte write,but the microcontroller does not send a stop condition after the first data word is clocked in.Instead,after the EEPROM acknowledges receipt of the first data word,the microcontroller can transmit up to 255more data words.The EEPROM will respond with a zero after each data word received.The microcontroller must ter-minate the page write sequence with a stop condition (see Figure 7-3on page 11).The data word address lower 8bits are internally incremented following the receipt of each data word.The higher data word address bits are not incremented,retaining the memory page row location.When the word address,internally generated,reaches the page boundary,the follow-ing byte is placed at the beginning of the same page.If more than 256data words are transmitted to the EEPROM,the data word address will “roll over”and previous data will be overwritten.The address “rollover”during write is from the last byte of the current page to the first byte of the same page.ACKNOWLEDGE POLLING:Once the internally timed write cycle has started and the EEPROM inputs are disabled,acknowledge polling can be initiated.This involves sending a start condition followed by the device address word.The read/write bit is representative of the operation desired.Only if the internal write cycle has completed will the EEPROM respond with a zero,allowing the read or write sequence to continue.7.Read OperationsRead operations are initiated the same way as write operations with the exception that the read/write select bit in the device address word is set to one.There are three read operations:current address read,random address read and sequential read.CURRENT ADDRESS READ:The internal data word address counter maintains the last address accessed during the last read or write operation,incremented by one.This address stays valid between operations as long as the chip power is maintained.The address “rollover”during read is from the last byte of the last memory page,to the first byte of the first page.105194F–SEEPR–1/08AT24C1024BOnce the device address with the read/write select bit set to one is clocked in and acknowledged by the EEPROM,the current address data word is serially clocked out.The microcontroller does not respond with an input zero but does generate a following stop condition (see Figure 7-4on page 11).RANDOM READ:A random read requires a “dummy”byte write sequence to load in the data word address.Once the device address word and data word address are clocked in and acknowledged by the EEPROM,the microcontroller must generate another start condition.The microcontroller now initiates a current address read by sending a device address with the read/write select bit high.The EEPROM acknowledges the device address and serially clocks out the data word.The microcontroller does not respond with a zero but does generate a follow-ing stop condition (see Figure 7-5on page 12).SEQUENTIAL READ:Sequential reads are initiated by either a current address read or a ran-dom address read.After the microcontroller receives a data word,it responds with an acknowledge.As long as the EEPROM receives an acknowledge,it will continue to increment the data word address and serially clock out sequential data words.When the memory address limit is reached,the data word address will “roll over”and the sequential read will continue.The sequential read operation is terminated when the microcontroller does not respond with a zero,but does generate a following stop condition (see Figure 7-6on page 12).115194F–SEEPR–1/08AT24C1024BFigure 7-1.Device AddressFigure 7-2.Byte WriteFigure 7-3.Page WriteFigure 7-4.Current AddressReadSIGNIFICANTMOSTSIGNIFICANTLEAST125194F–SEEPR–1/08AT24C1024BFigure 7-5.Random ReadFigure 7-6.Sequential Read135194F–SEEPR–1/08AT24C1024BNotes: 1.“-B”denotes bulk2.“-T”denotes tape and reel.SOIC =4K per reel.TSSOP and dBGA2=5K per reel.SAP =3K per reel.EIAJ =2K per reel.3.Available in tape and reel and wafer form;order as SL788for inkless wafer form.Bumped die available upon request.Pleasecontact Serial Interface Marketing.Ordering Information145194F–SEEPR–1/08AT24C1024B8.Part marking scheme8.18-SOIC(1.8V)8.28-SOIC(2.5V)TOP MARKSeal YearY = SEAL YEARWW = SEAL WEEK | Seal Week6: 2006 0: 2010 02 = Week 2 | | |7: 2007 1: 2011 04 = Week 4 |---|---|---|---|---|---|---|---| 8: 2008 2: 2012 :: : :::: : A T M L H Y W W 9: 2009 3: 2013:: : :::: :: |---|---|---|---|---|---|---|---| 50 = Week 50 2 G B 152 = Week 52|---|---|---|---|---|---|---|---| * Lot NumberLot Number to Use ALL Characters in Marking |---|---|---|---|---|---|---|---| |BOTTOM MARKPin 1 Indicator (Dot)No Bottom MarkTOP MARKSeal YearY = SEAL YEARWW = SEAL WEEK | Seal Week6: 2006 0: 2010 02 = Week 2 | | |7: 2007 1: 2011 04 = Week 4 |---|---|---|---|---|---|---|---| 8: 2008 2: 2012 :: : :::: : A T M L H Y W W 9: 2009 3: 2013:: : :::: :: |---|---|---|---|---|---|---|---| 50 = Week 50 2 G B 252 = Week 52|---|---|---|---|---|---|---|---| * Lot NumberLot Number to Use ALL Characters in Marking |---|---|---|---|---|---|---|---| |BOTTOM MARKPin 1 Indicator (Dot)No Bottom Mark155194F–SEEPR–1/08AT24C1024B8.38-TSSOP(1.8V)8.48-TSSOP(2.5V)TOP MARKPin 1 Indicator (Dot)Y = SEAL YEAR WW = SEAL WEEK |6: 2006 0: 2010 02 = Week 2 |---|---|---|---| 7: 2007 1: 2011 04 = Week 4 * H Y W W 8: 2008 2: 2012 :: : :::: : |---|---|---|---|---| 9: 2009 3: 2013:: : :::: :: 2 G B 1 50 = Week 50 |---|---|---|---|---| 52 = Week 52BOTTOM MARK|---|---|---|---|---|---|---| P H|---|---|---|---|---|---|---| A A A A A A A |---|---|---|---|---|---|---| <- Pin 1 IndicatorTOP MARKPin 1 Indicator (Dot)Y = SEAL YEAR WW = SEAL WEEK |6: 2006 0: 2010 02 = Week 2 |---|---|---|---| 7: 2007 1: 2011 04 = Week 4 * H Y W W 8: 2008 2: 2012 :: : :::: : |---|---|---|---|---| 9: 2009 3: 2013:: : :::: :: 2 G B 2 50 = Week 50 |---|---|---|---|---| 52 = Week 52BOTTOM MARK|---|---|---|---|---|---|---| P H|---|---|---|---|---|---|---| A A A A A A A |---|---|---|---|---|---|---| <- Pin 1 Indicator165194F–SEEPR–1/08AT24C1024B8.58-PDIP(1.8V)8.68-PDIP(2.5V)8.78-Ultra Thin SAP (1.8V)TOP MARKSeal YearY = SEAL YEARWW = SEAL WEEK | Seal Week6: 2006 0: 2010 02 = Week 2 | | |7: 2007 1: 2011 04 = Week 4 |---|---|---|---|---|---|---|---| 8: 2008 2: 2012 :: : :::: : A T M L U Y W W 9: 2009 3: 2013:: : :::: :: |---|---|---|---|---|---|---|---| 50 = Week 50 2 G B 152 = Week 52|---|---|---|---|---|---|---|---| * Lot NumberLot Number to Use ALL Characters in Marking |---|---|---|---|---|---|---|---| |BOTTOM MARKPin 1 Indicator (Dot)No Bottom MarkTOP MARKSeal YearY = SEAL YEARWW = SEAL WEEK | Seal Week6: 2006 0: 2010 02 = Week 2 | | |7: 2007 1: 2011 04 = Week 4 |---|---|---|---|---|---|---|---| 8: 2008 2: 2012 :: : :::: : A T M L U Y W W 9: 2009 3: 2013:: : :::: :: |---|---|---|---|---|---|---|---| 50 = Week 50 2 G B 252 = Week 52|---|---|---|---|---|---|---|---| * Lot NumberLot Number to Use ALL Characters in Marking |---|---|---|---|---|---|---|---| |BOTTOM MARKPin 1 Indicator (Dot)No Bottom MarkTOP MARKSeal Year| Seal Week Y = SEAL YEARWW = SEAL WEEK | | |6: 2006 0: 2010 02 = Week 2 |---|---|---|---|---|---|---|---| 7: 2007 1: 2011 04 = Week 4 A T M L H Y W W 8: 2008 2: 2012 :: : :::: : |---|---|---|---|---|---|---|---| 9: 2009 3: 2013:: : :::: :: 2 G B 150 = Week 50 |---|---|---|---|---|---|---|---| 52 = Week 52Lot Number|---|---|---|---|---|---|---|---| * |Pin 1 Indicator (Dot)175194F–SEEPR–1/08AT24C1024B8.88-Ultra Thin SAP (2.5V)8.9dBGA2TOP MARKSeal Year| Seal Week Y = SEAL YEARWW = SEAL WEEK | | |6: 2006 0: 2010 02 = Week 2 |---|---|---|---|---|---|---|---| 7: 2007 1: 2011 04 = Week 4 A T M L H Y W W 8: 2008 2: 2012 :: : :::: : |---|---|---|---|---|---|---|---| 9: 2009 3: 2013:: : :::: :: 2 G B 250 = Week 50 |---|---|---|---|---|---|---|---| 52 = Week 52Lot Number|---|---|---|---|---|---|---|---| * |Pin 1 Indicator (Dot)TOP MARKLINE 1-------> 2GBU LINE 2-------> PYMTC|<-- Pin 1 This CornerP = COUNTRY OF ORIGINY = ONE DIGIT YEAR CODE 4: 2004 7: 20075: 2005 8: 20086: 2006 9: 2009M = SEAL MONTH (USE ALPHA DESIGNATOR A-L) A = JANUARY B = FEBRUARY " " """"""" J = OCTOBER K = NOVEMBER L = DECEMBERTC = TRACE CODE (ATMEL LOT NUMBERS TO CORRESPONDWITH ATK TRACE CODE LOG BOOK)185194F–SEEPR–1/08AT24C1024B9.Packaging Information 8P3–PDIP195194F–SEEPR–1/08AT24C1024B8S1-JEDEC SOIC205194F–SEEPR–1/08AT24C1024B8S2–EIAJ SOICAT24C1024B 8A2-TSSOP2122AT24C1024B8U4-1-dBGA2AT24C1024B 8Y7–SAP2324AT24C1024B10.Revision HistoryHeadquarters InternationalAtmel Corporation 2325Orchard Parkway San Jose,CA95131 USATel:1(408)441-0311 Fax:1(408)487-2600Atmel AsiaRoom1219Chinachem Golden Plaza77Mody Road TsimshatsuiEast KowloonHong KongTel:(852)2721-9778Fax:(852)2722-1369Atmel EuropeLe Krebs8,Rue Jean-Pierre TimbaudBP30978054Saint-Quentin-en-Yvelines CedexFranceTel:(33)1-30-60-70-00Fax:(33)1-30-60-71-11Atmel Japan9F,Tonetsu Shinkawa Bldg.1-24-8ShinkawaChuo-ku,Tokyo104-0033JapanTel:(81)3-3523-3551Fax:(81)3-3523-7581Product ContactWeb SiteTechnical Support******************Sales Contact/contactsLiterature Requests/literatureDisclaimer:The information in this document is provided in connection with Atmel products.No license,express or implied,by estoppel or otherwise,to any intellectual property right is granted by this document or in connection with the sale of Atmel products.EXCEPT AS SET FORTH IN ATMEL’S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL’S WEB SITE,ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS,IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING,BUT NOT LIMITED TO,THE IMPLIED WARRANTY OF MERCHANTABILITY,FITNESS FOR A PARTICULAR PURPOSE,OR NON-INFRINGEMENT.IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT,INDIRECT,CONSEQUENTIAL,PUNITIVE,SPECIAL OR INCIDEN-TAL DAMAGES(INCLUDING,WITHOUT LIMITATION,DAMAGES FOR LOSS OF PROFITS,BUSINESS INTERRUPTION,OR LOSS OF INFORMATION)ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT,EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice.Atmel does not make any commitment to update the information contained herein.Unless specifically provided otherwise,Atmel products are not suitable for,and shall not be used in,automotive applications.Atmel’s products are not intended,authorized,or warranted for use as components in applications intended to support or sustain life.©2008Atmel Corporation.All rights reserved.Atmel®,logo and combinations thereof,are registered trademarks or trademarks of Atmel Cor-poration or its subsidiaries.Other terms and product names may be trademarks of others.。

AT24Cxx系列EEPROM应用笔记

4.1.开始 START CONDITION

主器件通过发送一个起始信号启动发送过程。这个信号的时序要求是当 SCL 为高时,SDA 出现一个由低到高的跳变。时序图如下(图 3)。

图 4 开始时序

4.2.应答信号 ACKNOWLEDGE

I²C 总线数据传送时,每成功地传送一个字节数据后,接收器都必须产生一个应答信号。 应答的器件在第 9 个时钟周期时将 SDA 线拉低(发送一个 0),表示其已收到一个 8 位数据。 AT24Cxx 在接收到起始信号和从器件地址之后响应一个应答信号,如果器件已选择了写操作, 则在每接收一个 8 位字节之后响应一个应答信号。

-6-

PDF 文件使用 "pdfFactory Pro" 试用版本创建

7. 读操作

AT24Cxx 系列 EEPROM 应用笔记

对 AT24Cxx 读操作的初始化方式和写操作时一样,仅把 R/W 位置为 1,有三种不同的读操 作方式:读当前地址内容、读随机地址内容、读顺序地址内容。

AT24Cxx 系列 EEPROM 是由美国 Mcrochip 公司出品,1-512K 位的支持 I2C 总线数据传送 协议的串行 CMOS E2PROM,可用电擦除,可编程自定时写周期(包括自动擦除时间不超过 10ms, 典型时间为 5ms)的。串行 E2PROM 一般具有两种写入方式,一种是字节写入方式,还有另一 种页写入方式。允许在一个写周期内同时对 1 个字节到一页的若干字节的编程写入,1 页的大小 取决于芯片内页寄存器的大小。其中,AT24C01 具有 8 字节数据的页面写能力,AT24C02/04/08/16 具有 16 字节数据的页面写能力,AT24C32/64 具有 32 字节数据的页面写能力。

ATMEL 爱特梅尔汽车级EEPROM 存储器AT24C04B 数据手册

1Features•Standard-voltage Operation –2.7 (V CC = 2.7V to 5.5V)•Automotive Temperature Range –40°C to 125°C•Internally Organized 128 x 8 (1K), 256 x 8 (2K), 512 x 8 (4K),1024 x 8 (8K) or 2048 x 8 (16K)•Two-wire Serial Interface•Schmitt Trigger, Filtered Inputs for Noise Suppression •Bidirectional Data Transfer Protocol •400 kHz Compatibility•Write Protect Pin for Hardware Data Protection•8-byte Page (1K, 2K), 16-byte Page (4K, 8K, 16K) Write Modes •Partial Page Writes are Allowed •Self-timed Write Cycle (5 ms max)•High-reliability–Endurance: 1 Million Write Cycles –Data Retention: 100 Years•8-lead JEDEC SOIC and 8-lead TSSOP PackagesDescriptionThe AT24C01A/02/04/08A/16A provides 1024/2048/4096/8192/16384 bits of serial electrically erasable and programmable read-only memory (EEPROM) organized as 128/256/512/1024/2048 words of 8 bits each. The device is optimized for use in many automotive applications where low-power and low-voltage operation are essential.The AT24C01A/02/04/08A/16A is available in space-saving 8-lead JEDEC SOIC and 8-lead TSSOP packages and is accessed via a two-wire serial interface. In addition,the entire family is available in 2.7V (2.7V to 5.5V) versions.Table 1. Pin ConfigurationsPin Name Function A0 − A2Address Inputs SDA Serial Data SCL Serial Clock Input WP Write Protect NCNo ConnectBDTIC www.BDTIC .com/ATMEL2AT24C01A/02/04/08A/16A5092D–SEEPR–4/07Figure 1. Block DiagramPin DescriptionSERIAL CLOCK (SCL): The SCL input is used to positive edge clock data into each EEPROM device and negative edge clock data out of each device.SERIAL DATA (SDA): The SDA pin is bi-directional for serial data transfer. This pin is open-drain driven and may be wire-ORed with any number of other open-drain or open-collector devices.DEVICE/PAGE ADDRESSES (A2, A1, A0): The A2, A1 and A0 pins are device address inputs that are hard wired for the AT24C01A and the AT24C02. As many as eight 1K/2K devices may be addressed on a single bus system (device addressing is discussed in detail under the Device Addressing section).The AT24C04 uses the A2 and A1 inputs for hard wire addressing and a total of four 4K devices may be addressed on a single bus system. The A0 pin is a no connect.Absolute Maximum RatingsOperating Temperature ......................................−55°C to +125°C *NOTICE:Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent dam-age to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.Storage Temperature .........................................−65°C to +150°C Voltage on Any Pinwith Respect to Ground ........................................−1.0V to +7.0V Maximum Operating Voltage..........................................6.25V DC Output Current........................................................5.0 mA3AT24C01A/02/04/08A/16A5092D–SEEPR–4/07The AT24C08A only uses the A2 input for hardwire addressing and a total of two 8K devices may be addressed on a single bus system. The A0 and A1 pins are no connects.The AT24C16A does not use the device address pins, which limits the number of devices on a single bus to one. The A0, A1 and A2 pins are no connects.WRITE PROTECT (WP): The AT24C01A/02/04/08A/16A has a Write Protect pin that provides hardware data protection. The Write Protect pin allows normal read/write oper-ations when connected to ground (GND). When the Write Protect pin is connected to V CC , the write protection feature is enabled and operates as shown in the following table.Memory OrganizationAT24C01A, 1K SERIAL EEPROM: Internally organized with 16 pages of 8 bytes each,the 1K requires a 7-bit data word address for random word addressing.AT24C02, 2K SERIAL EEPROM: Internally organized with 32 pages of 8 bytes each,the 2K requires an 8-bit data word address for random word addressing.AT24C04, 4K SERIAL EEPROM: Internally organized with 32 pages of 16 bytes each,the 4K requires a 9-bit data word address for random word addressing.AT24C08A, 8K SERIAL EEPROM: Internally organized with 64 pages of 16 bytes each, the 8K requires a 10-bit data word address for random word addressing.AT24C16A, 16K SERIAL EEPROM: Internally organized with 128 pages of 16 bytes each, the 16K requires an 11-bit data word address for random word addressing.Table 2. Write ProtectWP Pin Status Part of the Array Protected24C01A 24C0224C0424C08A 24C16A At V CC Full (1K) ArrayFull (2K) ArrayFull (4K) ArrayFull (8K) ArrayFull (16K) ArrayAt GNDNormal Read/Write Operations4AT24C01A/02/04/08A/16A5092D–SEEPR–4/07Note:1.This parameter is characterized and is not 100% tested.Note:1.V IL min and V IH max are reference only and are not tested.Table 3. Pin Capacitance (1)Applicable over recommended operating range from T A = 25°C, f = 1.0 MHz, V CC = +2.7VSymbol Test ConditionMax Units Conditions C I/O Input/Output Capacitance (SDA)8pF V I/O = 0V C IN Input Capacitance (A 0, A 1, A 2, SCL)6pFV IN = 0VTable 4. DC CharacteristicsApplicable over recommended operating range from: T A = −40°C to +125°C, V CC = +2.7V to +5.5V (unless otherwise noted)Symbol Parameter Test ConditionMin TypMax Units V CC1Supply Voltage2.75.5V I CC Supply Current V CC = 5.0V Read at 100 kHz 0.4 1.0mA I CC Supply Current V CC = 5.0V Write at 100 kHz 2.0 3.0mA I SB1Standby Current V CC = 2.7V V IN = V CC or V SS 1.6 4.0µA I SB2Standby Current V CC = 5.0V V IN = V CC or V SS 8.018.0µA I LI Input Leakage Current V IN = V CC or V SS 0.10 3.0µA I LO Output Leakage Current V OUT = V CC or V SS0.05 3.0µA V IL Input Low Level (1)−0.6V CC x 0.3V V IH Input High Level (1)V CC x 0.7V CC + 0.5V V OL2Output Low Level V CC = 3.0V I OL = 2.1 mA 0.4V V OL1Output Low Level V CC = 1.8VI OL = 0.15 mA 0.2V5AT24C01A/02/04/08A/16A5092D–SEEPR–4/07Note:1.This parameter is characterized and is not 100% tested (T A = 25°C).2.This parameter is characterized.Device OperationCLOCK and DATA TRANSITIONS: The SDA pin is normally pulled high with an exter-nal device. Data on the SDA pin may change only during SCL low time periods (see to Figure 4 on page 7). Data changes during SCL high periods will indicate a start or stop condition as defined below.START CONDITION: A high-to-low transition of SDA with SCL high is a start condition which must precede any other command (see to Figure 5 on page 7).STOP CONDITION: A low-to-high transition of SDA with SCL high is a stop condition.After a read sequence, the stop command will place the EEPROM in a standby power mode (see Figure 5 on page 7).ACKNOWLEDGE: All addresses and data words are serially transmitted to and from the EEPROM in 8-bit words. The EEPROM sends a “0” to acknowledge that it has received each word. This happens during the ninth clock cycle.STANDBY MODE: The AT24C01A/02/04/08A/16A features a low-power standby mode which is enabled: (a) upon power-up and (b) after the receipt of the STOP bit and the completion of any internal operations.Table 5. AC CharacteristicsApplicable over recommended operating range from T A = −40°C to +125°C, V CC = +2.7V to +5.5V, CL = 1 TTL Gate and 100 pF (unless otherwise noted)Symbol ParameterAT24C01A/02/04/08A/16AUnits MinMax f SCL Clock Frequency, SCL 400kHz t LOW Clock Pulse Width Low 1.2µs t HIGH Clock Pulse Width High 0.6µs t I Noise Suppression Time (1)50ns t AA Clock Low to Data Out Valid 0.10.9µs t BUF Time the bus must be free before a new transmission can start (2) 1.2µs t HD.STA Start Hold Time 0.6µs t SU.STA Start Set-up Time 0.6µs t HD.DAT Data In Hold Time 0µs t SU.DAT Data In Set-up Time 100ns t R Inputs Rise Time (2)300ns t F Inputs Fall Time (2)300ns t SU.STO Stop Set-up Time 0.6µs t DH Data Out Hold Time 50ns t WRWrite Cycle Time 5ms Endurance (2) 5.0V, 25°C, Page Mode1M Write Cycles6AT24C01A/02/04/08A/16A5092D–SEEPR–4/07MEMORY RESET: After an interruption in protocol, power loss or system reset, any two-wire part can be reset by following these steps:1.Clock up to 9 cycles.2.Look for SDA high in each cycle while SCL is high.3.Create a start condition.Bus TimingFigure 2. SCL: Serial Clock, SDA: Serial Data I/OWrite Cycle TimingFigure 3. SCL: Serial Clock, SDA: Serial Data I/ONote:1.The write cycle time t WRis the time from a valid stop condition of a write sequence to the end of the internal clear/write cycle.7AT24C01A/02/04/08A/16A5092D–SEEPR–4/07Figure 4. Data ValidityFigure 6.Output Acknowledge8AT24C01A/02/04/08A/16A5092D–SEEPR–4/07Device AddressingThe 1K, 2K, 4K, 8K and 16K EEPROM devices all require an 8-bit device address word following a start condition to enable the chip for a read or write operation (see to Figure 7 on page 9).The device address word consists of a mandatory “1”, “0” sequence for the first four most significant bits as shown. This is common to all the Serial EEPROM devices.The next 3 bits are the A2, A1 and A0 device address bits for the 1K/2K EEPROM.These 3 bits must compare to their corresponding hardwired input pins.The 4K EEPROM only uses the A2 and A1 device address bits with the third bit being a memory page address bit. The two device address bits must compare to their corre-sponding hardwired input pins. The A0 pin is no connect.The 8K EEPROM only uses the A2 device address bit with the next two bits being for memory page addressing. The A2 bit must compare to its corresponding hardwired input pin. The A1 and A0 pins are no connect.The 16K does not use any device address bits but instead the three bits are used for memory page addressing. These page addressing bits on the 4K, 8K and 16K devices should be considered the most significant bits of the data word address which follows.The A0, A1 and A2 pins are no connect.The eighth bit of the device address is the read/write operation select bit. A read opera-tion is initiated if this bit is high and a write operation is initiated if this bit is low.Upon a compare of the device address, the EEPROM will output a “0”. If a compare is not made, the chip will return to a standby state.Write OperationsBYTE WRITE: A write operation requires an 8-bit data word address following the device address word and acknowledgment. Upon receipt of this address, the EEPROM will again respond with a “0” and then clock in the first 8-bit data word. Following receipt of the 8-bit data word, the EEPROM will output a “0” and the addressing device, such as a microcontroller, must terminate the write sequence with a stop condition. At this time the EEPROM enters an internally timed write cycle, t WR , to the nonvolatile memory. All inputs are disabled during this write cycle and the EEPROM will not respond until the write is complete (see Figure 8 on page 10).PAGE WRITE: The 1K/2K EEPROM is capable of an 8-byte page write, and the 4K, 8K and 16K devices are capable of 16-byte page writes.A page write is initiated the same as a byte write, but the microcontroller does not send a stop condition after the first data word is clocked in. Instead, after the EEPROM acknowledges receipt of the first data word, the microcontroller can transmit up to seven (1K/2K) or fifteen (4K, 8K, 16K) more data words. The EEPROM will respond with a “0”after each data word received. The microcontroller must terminate the page write sequence with a stop condition (see Figure 9 on page 10).The data word address lower three (1K/2K) or four (4K, 8K, 16K) bits are internally incremented following the receipt of each data word. The higher data word address bits are not incremented, retaining the memory page row location. When the word address,internally generated, reaches the page boundary, the following byte is placed at the beginning of the same page. If more than eight (1K/2K) or sixteen (4K, 8K, 16K) data words are transmitted to the EEPROM, the data word address will “roll over” and previ-ous data will be overwritten.ACKNOWLEDGE POLLING: Once the internally timed write cycle has started and the EEPROM inputs are disabled, acknowledge polling can be initiated. This involves send-9AT24C01A/02/04/08A/16A5092D–SEEPR–4/07ing a start condition followed by the device address word. The read/write bit is representative of the operation desired. Only if the internal write cycle has completed will the EEPROM respond with a “0”, allowing the read or write sequence to continue.Read OperationsRead operations are initiated the same way as write operations with the exception that the read/write select bit in the device address word is set to “1”. There are three read operations: current address read, random address read and sequential read.CURRENT ADDRESS READ: The internal data word address counter maintains the last address accessed during the last read or write operation, incremented by one. This address stays valid between operations as long as the chip power is maintained. The address “roll over” during read is from the last byte of the last memory page to the first byte of the first page. The address “roll over” during write is from the last byte of the cur-rent page to the first byte of the same page.Once the device address with the read/write select bit set to “1” is clocked in and acknowledged by the EEPROM, the current address data word is serially clocked out.The microcontroller does not respond with an input “0” but does generate a following stop condition (see Figure 10 on page 10).RANDOM READ: A random read requires a “dummy” byte write sequence to load in the data word address. Once the device address word and data word address are clocked in and acknowledged by the EEPROM, the microcontroller must generate another start condition. The microcontroller now initiates a current address read by sending a device address with the read/write select bit high. The EEPROM acknowledges the device address and serially clocks out the data word. The microcontroller does not respond with a “0” but does generate a following stop condition (see Figure 11 on page 11).SEQUENTIAL READ: Sequential reads are initiated by either a current address read or a random address read. After the microcontroller receives a data word, it responds with an acknowledge. As long as the EEPROM receives an acknowledge, it will continue to increment the data word address and serially clock out sequential data words. When the memory address limit is reached, the data word address will “roll over” and the sequen-tial read will continue. The sequential read operation is terminated when the microcontroller does not respond with a “0” but does generate a following stop condition (see Figure 12 on page 11).Figure 7.Device Address10AT24C01A/02/04/08A/16A5092D–SEEPR–4/07Figure 8. Byte WriteFigure 9. Page Write(* = DON’T CARE bit for 1K)Figure 10.Current Address Read11AT24C01A/02/04/08A/16A5092D–SEEPR–4/07Figure 11. Random Read(* = DON’T CARE bit for 1K)Figure 12.Sequential Read12AT24C01A/02/04/08A/16A5092D–SEEPR–4/07Note:1.This device is not recommended for new design. Please refer to AT24C01B Automotive datasheet.AT24C01A Ordering Information (1)Ordering Code Package Operation RangeAT24C01A-10SQ-2.7AT24C01A-10TQ-2.78S18A2Lead-free/Halogen-free/AutomotiveTemperature (−40°C to 125°C)Package Type8S18-lead, 0.150" Wide, Plastic Gull Wing Small Outline (JEDEC SOIC)8A28-lead, 0.170" Wide, Thin Shrink Small Outline Package (TSSOP)Options−2.7Low-voltage (2.7V to 5.5V)13AT24C01A/02/04/08A/16A5092D–SEEPR–4/07Note:1.This device is not recommended for new design. Please refer to AT24C02B Automotive datasheet.AT24C02 Ordering Information (1)Ordering Code Package Operation RangeAT24C02N-10SQ-2.7AT24C02-10TQ-2.78S18A2Lead-free/Halogen-free/AutomotiveTemperature (−40°C to 125°C)Package Type8S18-lead, 0.150" Wide, Plastic Gull Wing Small Outline (JEDEC SOIC)8A28-lead, 0.170" Wide, Thin Shrink Small Outline Package (TSSOP)Options−2.7Low-voltage (2.7V to 5.5V)14AT24C01A/02/04/08A/16A5092D–SEEPR–4/07AT24C04 Ordering InformationOrdering Code Package Operation RangeAT24C04N-10SQ-2.7AT24C04-10TQ-2.78S18A2Lead-free/Halogen-free/AutomotiveTemperature (−40°C to 125°C)Package Type8S18-lead, 0.150" Wide, Plastic Gull Wing Small Outline (JEDEC SOIC)8A28-lead, 0.170" Wide, Thin Shrink Small Outline Package (TSSOP)Options−2.7Low-voltage (2.7V to 5.5V)15AT24C01A/02/04/08A/16A5092D–SEEPR–4/07Note:For 2.7V devices used in the 4.5V to 5.5V range, please refer to performance values in the AC and DC characteristics tables (Table 4 on page 4 and Table 5 on page 5).AT24C08A Ordering InformationOrdering Code Package Operation Range AT24C08AN-10SQ-2.7AT24C08A-10TQ-2.78S18A2Lead-free/Halogen-free/Automotive Temperature(−40°C to 125°C)Package Type8S18-lead, 0.150" Wide, Plastic Gull Wing Small Outline (JEDEC SOIC)8A28-lead, 0.170" Wide, Thin Shrink Small Outline Package (TSSOP)Options−2.7Low Voltage (2.7V to 5.5V)16AT24C01A/02/04/08A/16A5092D–SEEPR–4/07Note:For 2.7V devices used in the 4.5V to 5.5V range, please refer to performance values in the AC and DC characteristics tables (Table 4 on page 4 and Table 5 on page 5).AT24C16A Ordering InformationOrdering Code Package Operation Range AT24C16AN-10SQ-2.7AT24C16A-10TQ-2.78S18A2Lead-free/Halogen-free/Automotive Temperature(−40°C to 125°C)Package Type8S18-lead, 0.150" Wide, Plastic Gull Wing Small Outline (JEDEC SOIC)8A28-lead, 0.170" Wide, Thin Shrink Small Outline Package (TSSOP)Options−2.7Low Voltage (2.7V to 5.5V)17AT24C01A/02/04/08A/16A5092D–SEEPR–4/07Packaging Information8S1 – JEDEC SOIC18AT24C01A/02/04/08A/16A5092D–SEEPR–4/078A2 – TSSOP19AT24C01A/02/04/08A/16A5092D–SEEPR–4/07Revision HistoryDoc. Rev.Date Comments5092D 4/2007Added ‘Not recommended for new design’ notes to AT24C01A and AT24C02 on pages 1, 12 and 13.5092C2/2007Implemented revision history.Removed PDIP offering and parts.Added ‘AT24C02 Not Recommended for New Design’ note to page 1.。

24c02程序2 24c04系列存储器是常用的存储器,可以保存数据一百年。这程序包括了,“开始”,“停止”,

/* 这里举出一个实例(读写串行EEPROM芯片at2402)24C04和24C02是差不多的,

04的最高位地址是在Device Address里的,比如你要写00-ff的空间你就这样

WriteI2CByte(0xa0); 要写100-1ff的空间就这样WriteI2CByte(0xa2);

/* Version: 1.1.1 */

/* Others: None */

/************************************************************************/

#include<string.h>

#include<reg52.h>

SDA=0;

SCL=1;

DELAY(DELAY_TIME);

SDA=1;

DELAY(DELAY_TIME);

SCL=0;

DELAY(DELAY_TIME);

}

void SEND_0(void) /* SEND ACK */

{

/*发送0,在SCL为高电平时使SDA信号为低*/

SDA=0;

SCL=1;

DELAY(DELAY_TIME);

SCL=0;

DELAY(DELAY_TIME);

}

void SEND_1(void)

{

/*发送1,在SCL为高电平时使SDA信号为高*/

SDA=1;

SCL=1;

DELAY(DELAY_TIME);

SDA=1;

SCL=1;

DELAY(DELAY_TIME);

EEPROM------AT24C01A_IIC总线驱动读写程序

/*河北工程大学信电学院自动化系调试成功EEPROM------A T24C01A_IIC总线驱动读写程序晶振:6MHz目标板:STC90C52AD编译环境:Keil C uVision V2.38a*/#include <reg52.h>#include <intrins.h>//由于是01A,1Kbit,故此这里第一个字节的读写格式是1010,A2,A1,A0,R/W #define Read_Addr 0xa1#define Write_Addr 0xa0#define uchar unsigned char//总线的定义,时钟线P1.0,数据线P1.1sbit SCL=P1^0;sbit SDA=P1^1;//短码数组uchar tab[]={2,5,6};void Start(){SDA=1;_nop_();SCL=1;_nop_();SDA=0;_nop_();SCL=0; //可以视作第一个SCL=0}void Stop(){SDA=0;_nop_();SCL=1;_nop_();SDA=1;}//------------------------------------------------------------------------- bit Write_Byte(uchar DA TA){bit Ack;uchar i;for(i=0;i<8;i++){SDA=(bit)(DA TA&0x80);_nop_();SCL=1;_nop_();_nop_();SCL=0; //第九个SCL=0DA TA<<=1;}SDA=1; //主机释放SDA_nop_();_nop_();SCL=1; //第九个SCL=1_nop_();//SDA=1; //对程序好像没出来影响Ack=SDA; //前面是否先置1,特别注意是否是准双向口SCL=0; //下一个字节的第一个SCL=0return (Ack);}uchar Read_Byte(){uchar DA TA,i;for(i=0;i<8;i++){SCL=1;DA TA<<=1;//注意强制类型转换SDA=1; //对程序好像没出来影响DA TA|=(uchar)SDA;//前面是否先置1,特别注意是否是准双向口SCL=0;}return(DA TA);}//-------------------------------------------------------------------------//读当前地址的数据uchar Read_Current_Addr(){uchar DA TA;Start();Write_Byte(Read_Addr);DA TA=Read_Byte();Stop();return(DA TA);}//向指定地址读数据uchar Read_Random_Addr(uchar addr) //256*8byte=1024Kbit,uchar类型正好合适{uchar DA TA;Start();Write_Byte(Write_Addr);Write_Byte(addr);DA TA=Read_Current_Addr();return(DA TA);}/*-------------------------------------------------------------功能:从EEPROM中给定一个地址连续读NLEN个字节数据存放在以指针nContent开头的往下内容。

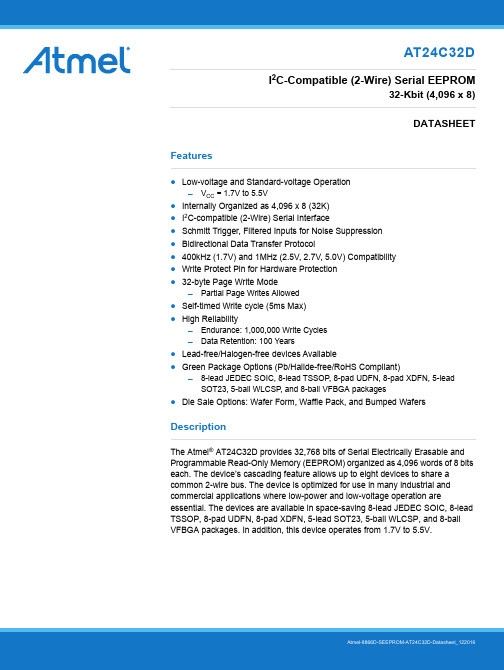

安特尔AT24C32D 32K Serial EEPROM数据手册说明书

AT24C32DI2C-Compatible (2-Wire) Serial EEPROM32-Kbit (4,096 x 8)DATASHEET Features●Low-voltage and Standard-voltage OperationV CC = 1.7V to 5.5V●Internally Organized as 4,096 x 8 (32K)●I2C-compatible (2-Wire) Serial Interface●Schmitt Trigger, Filtered Inputs for Noise Suppression●Bidirectional Data Transfer Protocol●400kHz (1.7V) and 1MHz (2.5V, 2.7V, 5.0V) Compatibility●Write Protect Pin for Hardware Protection●32-byte Page Write ModePartial Page Writes Allowed●Self-timed Write cycle (5ms Max)●High ReliabilityEndurance: 1,000,000 Write CyclesData Retention: 100 Years●Lead-free/Halogen-free devices Available●Green Package Options (Pb/Halide-free/RoHS Compliant)8-lead JEDEC SOIC, 8-lead TSSOP, 8-pad UDFN, 8-pad XDFN, 5-leadSOT23, 5-ball WLCSP, and 8-ball VFBGA packages●Die Sale Options: Wafer Form, Waffle Pack, and Bumped Wafers DescriptionThe Atmel® AT24C32D provides 32,768 bits of Serial Electrically Erasable and Programmable Read-Only Memory (EEPROM) organized as 4,096 words of 8 bits each. The device’s cascading feature allows up to eight devices to share a common 2-wire bus. The device is optimized for use in many industrial and commercial applications where low-power and low-voltage operation are essential. The devices are available in space-saving 8-lead JEDEC SOIC, 8-lead TSSOP, 8-pad UDFN, 8-pad XDFN, 5-lead SOT23, 5-ball WLCSP, and 8-ball VFBGA packages. In addition, this device operates from 1.7V to 5.5V.AT24C32D [DATASHEET]Atmel-8866D-SEEPROM-AT24C32D-Datasheet_12201621.Pin Configurations and PinoutsTable 1-1.Pin Configuration Note:When using the 5-lead SOT-23 or the 5-ball WLCSP , the software bits A2, A1, and A0 must be set to Logic 0 to properly communicate with the device.2.Absolute Maximum Ratings*8-pad UDFN/XDFNV CC WP SCL SDAA 0A 1A 2GND123487658-ball VFBGABottom View8-lead SOIC8-lead TSSOPTop View12348765A 0A 1A 2GNDV CC WP SCL SDATop View Top ViewA 0A 1A 2GND V CC WP SCL SDA87651234SCL GND SDA123545-lead SOT23WPV CC* Note: Drawings are not to scale5-ball WLCSPBall Side View(1)A 0A 1A 2GNDV CC WP SCL SDA12348765(1)Operating Temperature . . . . . . . . . . .-55°C to +125°C Storage Temperature . . . . . . . . . . . . -65°C to + 150°C Voltage on any pinwith respect to ground . . . . . . . . . . . . . . .-1.0 V +7.0V Maximum Operating Voltage . . . . . . . . . . . . . . . 6.25V DC Output Current. . . . . . . . . . . . . . . . . . . . . . .5.0mA*Notice:Stresses beyond those listed under “AbsoluteMaximum Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification are not implied. Exposure to absolute maximum rating conditions forextended periods may affect device reliability.3AT24C32D [DATASHEET]Atmel-8866D-SEEPROM-AT24C32D-Datasheet_1220163.Block Diagram4.Pin DescriptionsSerial Clock (SCL): The SCL input is used to positive-edge clock data into each EEPROM device and negative-edge clock data out of each device.Serial Data (SDA): The SDA pin is bidirectional for serial data transfer. This pin is open drain driven and may be wire-ORed with any number of other open-drain or open-collector devices.Device Addresses (A 2, A 1, A 0): The A 2, A 1, and A 0 pins are device address inputs that are hard wired (directly to GND or to V CC ) for compatibility with other Atmel AT24C devices. When the pins are hard wired, as many as eight 32K devices may be addressed on a single bus system. (Device addressing is discussed in detail in Section 7., “Device Addressing” on page 9). A device is selected when a corresponding hardware and software match is true. If these pins are left floating, the A 2, A 1, and A 0 pins will be internally pulled down to GND. However, due to capacitive coupling that may appear during customer applications, Atmel recommends always connecting the address pins to a known state. When using a pull-up resistor, Atmel recommends using 10k Ω or less.Write Protect (WP): The Write Protect input, when connected to GND, allows normal write operations. When WP is connected directly to V CC , all Write operations to the memory are inhibited. If the pin is left floating, the WP pin will be internally pulled down to GND; however, due to capacitive coupling that may appear during customerapplications, Atmel recommends always connecting the WP pins to a known state. When using a pull-up resistor, Atmel recommends using 10k Ω or less.Table 4-1.Write ProtectV CC GND WP SCL SDAA 2A 1A 0AT24C32D [DATASHEET]Atmel-8866D-SEEPROM-AT24C32D-Datasheet_12201645.Memory OrganizationAT24C32D, 32K Serial EEPROM : The 32K is internally organized as 128 pages of 32-bytes each. Random word addressing requires a 12-bit data word address.5.1Pin CapacitanceTable 5-1.Pin Capacitance (1)Note:1.This parameter is characterized and is not 100% tested.5.2DC CharacteristicsTable 5-2.DC CharacteristicsNote:1.V IL min and V IH max are reference only and are not tested.Applicable over recommended operating range from: T A = 25°C, f = 1.0MHz, V CC = 5.5V.Applicable over recommended operating range from: T AI = -40°C to +85°C, V CC = 1.7V to 5.5V (unless otherwise noted).5AT24C32D [DATASHEET]Atmel-8866D-SEEPROM-AT24C32D-Datasheet_1220165.3AC CharacteristicsTable 5-3.AC Characteristics (Industrial Temperature)Notes:1.This parameter is ensured by characterization and is not 100% tested.2.AC measurement conditions:●R L (connects to V CC ): 1.3k Ω (2.5V, 5.5V), 10k Ω (1.7V)●Input pulse voltages: 0.3V CC to 0.7V CC ●Input rise and fall times: ≤ 50ns ●Input and output timing reference voltages: 0.5 x V CCApplicable over recommended operating range from: T AI = -40°C to +85°C, V CC = 1.7V to 5.5V, CL = 100pF (unless otherwise noted). Test conditions are listed in Note 2.AT24C32D [DATASHEET]Atmel-8866D-SEEPROM-AT24C32D-Datasheet_12201666.Device OperationClock and Data Transitions: The SDA pin is normally pulled high with an external device. Data on the SDA pin may change only during SCL low time periods. Data changes during SCL high periods will indicate a Start or Stop condition as defined below.Figure 6-1.Data ValidityStart Condition : A high-to-low transition of SDA with SCL high is a Start condition that must precede every command.Stop Condition: A low-to-high transition of SDA with SCL high is a Stop condition. After a Read sequence, the Stop condition will place the EEPROM in a standby power mode.Figure 6-2.Start Condition and Stop Condition DefinitionSDASCLData ChangeData StableData StableSDASCLStart Condition Stop Condition7AT24C32D [DATASHEET]Atmel-8866D-SEEPROM-AT24C32D-Datasheet_122016Acknowledge: All addresses and data words are serially transmitted to and from the EEPROM in 8-bit words. The receiving device sends a zero during the ninth clock cycle to acknowledge that it has received each word. This zero response is referred to as an Acknowledge.Figure 6-3.Output AcknowledgeStandby Mode: AT24C32D features a low-power standby mode that is enabled upon power-up and after the receipt of the Stop condition and the completion of any internal operations.Software Reset : After an interruption in protocol, power loss or system reset, any 2-wire part can be protocol reset by following these steps:1.Create a Start condition (if possible).2.Clock nine cycles.3.Create another Start condition followed by Stop condition as shown below.The device should be ready for the next communication after above steps have been completed. In the event that the device is still non-responsive or remains active on the SDA bus, a power cycle must be used to reset the device.Figure 6-4.Software ResetSCLData InData OutStart ConditionAcknowledge981SCLSDAAT24C32D [DATASHEET]Atmel-8866D-SEEPROM-AT24C32D-Datasheet_1220168Figure 6-5.Bus TimingFigure 6-6.Write Cycle TimingNote: 1.The Write cycle time t WR is the time from a valid Stop condition of a Write sequence to the end ofthe internal Clear/Write cycle.SCLSDA InSDA OutSCLSDAStop ConditionStart Condition9AT24C32D [DATASHEET]Atmel-8866D-SEEPROM-AT24C32D-Datasheet_1220167.Device AddressingThe 32K EEPROM requires an 8-bit device address word following a Start condition to enable the chip for a Read or Write operation. The device address word consists of a mandatory ‘1010’ sequence for the first four most significant bits which is known as the device type identifier. These four bits are bit 7, bit 6, bit 5, and bit 4 as seen in Figure 7-1. This is common to all 2-wire Serial EEPROM devices.The next three bits are the A2, A1, and A0 hardware address select bits which allow as many as eight devices on the same bus. These bits must compare to their corresponding hard wired input pins, A 2, A 1, and A 0. The A 2, A 1, and A 0 pins use an internal proprietary circuit that biases them to a logic low condition if the pins are allowed to float.When utilizing the 5-ball WLCSP or the 5-lead SOT-23 packages, the A 2, A 1, and A 0 pins are not available. The A 2, A 1, and A 0 pins are internally pulled to ground and thus the A2, A1, and A0 device address bits must always be set to a Logic 0 to communicate with the device. This condition is depicted in Figure 7-1 below.The eighth bit of the device address is the Read/write operation select bit. A Read operation is initiated if this bit is a Logic 1, and a Write operation is initiated if this bit is a Logic 0.Upon a successful comparison of the device address, the EEPROM will output a zero during the following clock cycle. If a compare is not made, the device will not acknowledge and will instead return to a standby state.Figure 7-1.Device AddressingData Security: The AT24C32D has a hardware data protection scheme that allows the user to write protect the whole memory when the WP pin is at V CC .AT24C32D [DATASHEET]Atmel-8866D-SEEPROM-AT24C32D-Datasheet_122016108.Write OperationsByte Write : A Write operation requires two 8-bit data word addresses following the device address word and acknowledgment. Upon receipt of this address, the EEPROM will again respond with a zero then clock in the first 8-bit data word. Following receipt of the 8-bit data word, the EEPROM will output a zero. The addressing device, such as a microcontroller, must then terminate the write sequence with a Stop condition. At this time, the EEPROM enters an internally-timed Write cycle, t WR , to the nonvolatile memory (See Figure 6-6). All inputs are disabled during this Write cycle and the EEPROM will not respond until the Write is complete.Figure 8-1.Byte WriteNote:* = Don’t care bit.Page Write: The 32K EEPROM is capable of 32-byte Page Writes.A Page Write is initiated the same way as a Byte Write, but the microcontroller does not send a Stop condition after the first data word is clocked in. Instead, after the EEPROM acknowledges receipt of the first data word, the microcontroller can transmit up to 31 more data words. The EEPROM will respond with a zero after each data word received. The microcontroller must terminate the Page Write sequence with a Stop condition.The data word address lower five bits are internally incremented following the receipt of each data word. The higher data word address bits are not incremented, retaining the memory page row location. When the word address, internally generated, reaches the page boundary, the following byte is placed at the beginning of the same page. If more than 32 data words are transmitted to the EEPROM, the data word address will roll-over and the previously loaded data will be altered. The address roll-over during Write is from the last byte of the current page to the first byte of the same page.Figure 8-2.Page WriteNote:* = Don’t care bit.Acknowledge Polling : Once the internally-timed Write cycle has started and the EEPROM inputs are disabled, acknowledge polling can be initiated. This involves sending a Start condition followed by the device address word. The Read/Write bit is representative of the operation desired. Only if the internal Write cycle has completed will the EEPROM respond with a zero, allowing the Read or Write sequence to continue.S T A R TW R I T ES T O PDevice Address FirstWord Address Second Word AddressDataSDA LineM S BA C KR /W A C KA C KA CKSDA LineS T A W R I BK/W KKKKS T9.Read OperationsRead operations are initiated the same way as Write operations with the exception that the Read/Write select bit in the device address word is set to one. There are three Read operations:●Current Address Read ●Random Address Read ●Sequential ReadCurrent Address Read : The internal data word address counter maintains the last address accessed during the last Read or Write operation, incremented by one. This address stays valid between operations as long as the chip power is maintained. The address roll-over during read is from the last byte of the last memory page, to the first byte of the first page.Once the device address with the Read/Write select bit set to one is clocked in and acknowledged by theEEPROM, the current address data word is serially clocked out. The microcontroller does not respond with an zero but does generate a Stop condition.Figure 9-1.Current Address ReadRandom Read: A Random Read requires a dummy Byte Write sequence to load in the data word address. Once the device address word and data word address are clocked in and acknowledged by the EEPROM, the microcontroller must generate another Start condition. The microcontroller now initiates a Current Address Read by sending a device address with the Read/write select bit high. The EEPROM acknowledges the device address and serially clocks out the data word. The microcontroller does not respond with a zero but does generate a Stop condition.Figure 9-2.Random ReadNote:* = Don’t care bit.SDA LineS T A R TDevice AddressR E A DS T O PM S BA C KR /W N O A C KDataSDA LINES T A R TS T A R TR E A DW R I T ES T O PDevice Address Second Word Address Device AddressFirst Word Address Data (n)M S BA C KA C KAC KL S B A C KN O A C KR /W Dummy WriteR /W12Sequential Read: Sequential Reads are initiated by either a Current Address Read or a Random Address Read. After the microcontroller receives a data word, it responds with an acknowledge. As long as the EEPROM receives an acknowledge, it will continue to increment the data word address and serially clock out sequential data words. When the memory address maximum address is reached, the data word address will roll-over and the Sequential Read will continue from the beginning of the array. The Sequential Read operation is terminated when the microcontroller does not respond with a zero but does generate a Stop condition.Figure 9-3.Sequential ReadNote:* = Don’t care bit.SDA LINESTARTSTARTREADWRITESTOP DeviceAddressSecond WordAddressDeviceAddressFirst WordAddressData (n + 1)Data (n + 2)Data (n + x)Data (n)MSBACKACKACKLSBACKACKACKACKNOACKR/WDummy Write. . .. . .R/AT24C32D [DATASHEET]10.Ordering Code DetailAtmel DesignatorProduct FamilyDevice DensityDevice RevisionShipping Carrier OptionOperating VoltagePackage Option32 = 32K24C = Standard I 2C-compatibleSerial EEPROMB = Bulk (Tubes)T = Tape and Reel, Standard Quantity Option E = Tape and Reel, Expanded Quantity OptionM = 1.7V to 5.5VSS = JEDEC SOIC X = TSSOP MA = UDFN ME = XDFN ST = SOT23U = 5-ball, 3x3 Grid Array, WLCSP C = VFBG A WWU = Wafer UnsawnWDT = Die in Tape and ReelPackage Device Grade or Wafer/Die ThicknessH = Green, NiPdAu Lead Finish, Industrial Temperature Range (-40°C to +85°C)U = Green, Matte Sn Lead Finish or SnAgCu Solder Ball Finish, Industrial Temperature Range (-40°C to +85°C)11= 11mil Wafer ThicknessA T 24C 32D -S S H M -TAT24C32D [DATASHEET]1411.Part MarkingsNotes: 1.WLCSP Package: CAUTION: Exposure to ultraviolet (UV) light can degrade the data stored in the EEPROM cells. Therefore, customers who use a WLCSP product must ensure that exposure to ultraviolet lightdoes not occur.2.Contact Atmel Sales for Wafer sales.13.18S1 — 8-lead JEDEC SOICAT24C32D [DATASHEET]1613.28X — 8-lead TSSOP13.38MA2 — 8-pad UDFNAT24C32D [DATASHEET] 1813.48ME1 — 8-pad XDFNAT24C32D [DATASHEET]2013.55TS1 — 5-lead SOT2321AT24C32D [DATASHEET]Atmel-8866D-SEEPROM-AT24C32D-Datasheet_12201613.65U-3 — 5-ball, WLCSPAT24C32D [DATASHEET]Atmel-8866D-SEEPROM-AT24C32D-Datasheet_1220162213.78U2-1 — 8-ball VFBGA23AT24C32D [DATASHEET]Atmel-8866D-SEEPROM-AT24C32D-Datasheet_12201614.Revision HistoryX X X X X XAtmel Corporation1600 Technology Drive, San Jose, CA 95110 USAT: (+1)(408) 441.0311F: (+1)(408) 436.4200|© 2015 Atmel Corporation. / Rev.: Atmel-8866D-SEEPROM-AT24C32D-Datasheet_122016.Atmel ®, Atmel logo and combinations thereof, Enabling Unlimited Possibilities ®, and others are registered trademarks or trademarks of Atmel Corporation in U.S. and other countries. Other terms and product names may be trademarks of others.DISCLAIMER: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended,authorized, or warranted for use as components in applications intended to support or sustain life.SAFETY-CRITICAL, MILITARY, AND AUTOMOTIVE APPLICATIONS DISCLAIMER: Atmel products are not designed for and will not be used in connection with any applications where the failure of such products would reasonably be expected to result in significant personal injury or death (“Safety-Critical Applications”) without an Atmel officer's specific written consent. Safety-Critical Applications include, without limitation, life support devices and systems, equipment or systems for the operation of nuclear facilities and weapons systems.Atmel products are not designed nor intended for use in military or aerospace applications or environments unless specifically designated by Atmel as military-grade. Atmel products are not designed nor intended for use in automotive applications unless specifically designated by Atmel as automotive-grade.。

实战24C02读写

实战24C02读写AT24C02是美国ATMEL公司的低功耗CMOS串行EEPROM,它是内含256×8位存储空间,具有工作电压宽(2.5~5.5V)、擦写次数多(大于10000次)、写入速度快(小于10ms)等特点。

24C02与单片机的联接参见原理图 ,读写程序如下,运行此程序,可以看到其中之一数码管循环显示0,1,2,3,4,5,6,7,8,9的效果。

其根本是,先往24C02中写数据,然后,读出数据,在数码管中显示,这样直观明了,详细说明,请看程序中注解。

此程序是针对24c02的,其实,可以扩展来其他i2c的eeprom.这由你们来完成吧。

#include <at89x51.h>#include <intrins.h> //此文件中有_nop_()空操作函数#define uchar unsigned char#define uint unsigned int#define OP_READ 0xa1 // 器件地址以及读取操作#define OP_WRITE 0xa0 // 器件地址以及写入操作uchar code display[10]={0x28,0xEB,0x32,0xA2,0xE1,0xA4,0x24,0xEA,0x20,0xA0};//数码管0,1,2,3,4,5,6,7,8,9的编码sbit SDA = P2^0; //位定义sbit SCL = P2^1; //位定义void LED_display(uchar i);//数码管显示编码获取函数,例如,i=0,则P0=display[0],即显示数字“0”void start();//开始位void stop();//停止位uchar shin();//从AT24C02移入数据到MCUbit shout(uchar write_data);//从MCU移出数据到AT24C02void write_byte( uchar addr, uchar write_data); //在指定地址addr处写入数据write_datavoid fill_byte(uchar fill_size,uchar fill_data);//填充数据fill_data到EEPROM内fill_size字节void delayms(uchar ms); // 延时子程序uchar read_current(); // 在当前地址读取uchar read_random(uchar random_addr);// 在指定地址读取void LED_display(uchar i){P0 = display[i];}main(void){uchar i;uint j;SDA = 1;SCL = 1;fill_byte(11,0xff); // 将前10字节填充0xfffor(i = 0 ; i < 10; i++) //写入显示代码到AT24C02{write_byte(i, i);P2_7 = 0; //打开数码管1的显示for(i =0 ;i <10 ; i++){LED_display(read_random(i));for (j = 0; j<35000;j++);//延时}}void start()//开始位{SDA = 1;SCL = 1;_nop_();_nop_();SDA = 0;_nop_();_nop_();_nop_();_nop_();SCL = 0;}void stop()// 停止位{SDA = 0;_nop_();_nop_();SCL = 1;_nop_();_nop_();_nop_();_nop_();SDA = 1;}uchar shin()// 从AT24C02移入数据到MCU {uchar i,read_data;for(i = 0; i < 8; i++){SCL = 1;read_data <<= 1;read_data |= (uchar)SDA;SCL = 0;return(read_data);}bit shout(uchar write_data)// 从MCU移出数据到AT24C02{uchar i;bit ack_bit;for(i = 0; i < 8; i++) // 循环移入8个位{SDA = (bit)(write_data & 0x80);_nop_();SCL = 1;_nop_();_nop_();SCL = 0;write_data <<= 1;}SDA = 1; // 读取应答_nop_();_nop_();SCL = 1;_nop_();_nop_();_nop_();_nop_();ack_bit = SDA;SCL = 0;return ack_bit; // 返回AT24C02应答位}void write_byte(uchar addr, uchar write_data)// 在指定地址addr处写入数据write_data{start();shout(OP_WRITE);shout(addr);shout(write_data);stop();delayms(10); // 写入周期}void fill_byte(uchar fill_size,uchar fill_data)// 填充数据fill_data到EEPROM内fill_size字节{uchar i;for(i = 0; i < fill_size; i++){write_byte(i, fill_data);}}uchar read_current()// 在当前地址读取{uchar read_data;start();shout(OP_READ);read_data = shin();stop();return read_data;}uchar read_random(uchar random_addr) // 在指定地址读取{start();shout(OP_WRITE);shout(random_addr);return(read_current());}void delayms(uchar ms)// 延时子程序{uchar i;while(ms--){for(i = 0; i < 120; i++);}}。

ATMEL24c02使用详解(汇编及C程序都有)

ATMEL 24c02使用详解(汇编及C程序都有)1000字ATMEL 24c02是一种串行EEPROM存储器,具有2KB的存储容量,可通过I2C总线进行读写操作。

使用ATMEL 24c02时,需先设置I2C总线的通信速率和设备地址。

然后,可以使用汇编语言或C语言编写程序进行读写数据操作。

汇编语言程序示例:1. 设置I2C总线通信速率及设备地址```LDAA #$0 ;设置I2C总线通信速率为100kHzSTAA SCLDIVLDAA #$A0 ;设置EEPROM的设备地址为0xA0STAA SLA```2. 写入数据到EEPROM```BYTE_WRITE PROCLDAA #$00 ;设置数据的存储地址为0x00STAA DADDRLDAA #$A5 ;设置需要写入的数据为0xA5STAA DATAJSR I2C_WRITE ;调用I2C总线写入函数RTSBYTE_WRITE ENDP```3. 从EEPROM读取数据```BYTE_READ PROCLDAA #$00 ;设置数据的读取地址为0x00STAA DADDRJSR I2C_START ;发送起始信号LDAA #$A1 ;设置EEPROM的设备地址为0xA1,读操作时需要在地址末位添加1JSR I2C_SEND ;发送EEPROM设备地址LDAA #$00 ;设置要读取的数据长度为1JSR I2C_READ ;调用I2C总线读取函数LDA DATA ;将读取到的数据保存到DATA寄存器中RTSBYTE_READ ENDP```C语言程序示例:1. 在main函数中,调用I2C_Init()函数,设置I2C总线速率和设备地址。

```void main(){I2C_Init(); //设置I2C总线速率和设备地址}```2. 写入数据到EEPROM```void Write_Byte(unsigned char addr, unsigned char dat) {I2C_Start(); //发送起始信号I2C_SendByte(0xa0); //写入EEPROM的设备地址I2C_SendByte(addr); //设置存储地址I2C_SendByte(dat); //写入数据I2C_Stop(); //发送停止信号}```3. 从EEPROM读取数据```unsigned char Read_Byte(unsigned char addr){unsigned char res;I2C_Start(); //发送起始信号I2C_SendByte(0xa0); //写入EEPROM的设备地址I2C_SendByte(addr); //设置读取地址I2C_Start(); //发送起始信号I2C_SendByte(0xa1); //设置EEPROM的设备地址为读取模式 res = I2C_ReadByte(); //读取数据I2C_Stop(); //发送停止信号return res; //返回读取的数据}```即可进行EEPROM的读写操作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。