郭天祥51单片机开发板原理图

单片机开发板电路原理图

D Connector 9

MAX232D

VCC C4

16

C8

2

C11

6

14 7 PC-RXD 12 9 RXD_M

2

VCC

VCC

R10 Res2 1K

R11 Res2 1K

1

1

TXD Power-led

RXD Power-led

2

ADᣝ䬂

R7

1.5K ে R12 SW-PB 4.7K

R8

1K ϟ SW-PB

40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21

Download D0 D1 D2 D3 D4 D5 D6 D7 Download MCUALE DS18B20_0UT CS_Du CS_Wei CS_LED RW EN RS CSA CSB

P5

12 34 56 78 9 10 11 12 13 14 15 16

Header 8X2

DIODEUS6

1 2 3 4 5 6 7 8

IN1 OUT1 IN2 OUT2 IN3 OUT3 IN4 OUT4 IN5 OUT5 IN6 OUT6 IN7 OUT7 GND DIODES

ULN2003

P6

ԡ

VCC

R5

GND

R6

VCC

1K

P3

1K

1

RESTA

1 3

2 4

56

RESTB Power

2

Header 3X2 VCC

GND

RESTB

B

R14

R15

R16

Pl2303 USB䕀Іষ

KST-51开发板原理图

J5

J7

D

单片机电路

LED2 LED3 LED4 LED5 LED6 LED7 LED8 LED9 LEDC1 R41 1K Q11 9012 DB0 LED DB1 LED DB2 LED DB3 LED DB4 LED DB5 LED DB6 LED DB7 LED

+5

USB供电电路 单片机复位电路

LEDC4

R48 1K

ADDR0

ADDR1

ADDR2

74HC138 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 15 14 13 12 11 10 9 7 LEDC0 LEDC1 LEDC2 LEDC3 LEDC4 LEDC5 LEDC6 LEDC7

LEDC5

R49 1K

Q19 9012

1 7 2

+5 U11 11 12 R1 R2 R3 R4 DB9-TX DB9-RX C7 0.1uF C27 0.1uF C1 +5 0.1uF 2 16 10 9 1 3 T1IN R1OUT T2IN R2OUT C1+ C1V+ VCC MAX232 T1OUT R1IN T2OUT R2IN C2+ C2VGND 14 13 TO-PC-RX 7 8 4 5 6 15 TO-PC-TX C32 0.1uF C33 0.1uF 1 6 2 7 3 8 4 9 5 RS-232 J1 ADDR0 ADDR1 ADDR2 ADDR3

1 2 +5 3 ADDR0 4 ADDR1 5 ENLCD1 6 DB_0 7 DB_1 8 DB_2 9 DB_3 10 DB_4 11 DB_5 12 DB_6 13 DB_7 14 15 +5 16

郭天祥新概念51单片机C语言教程例题Word版

目录例2.2.1 编写程序,点亮第一个发光二极管(part2_1.c P27 ) .................. - 4 -例2.5.1利用for语句延时特性,编写第一个发光二极管以间隔1S亮灭闪动的程序(part2_3.c P42) ............................................................................................. - 5 -例2.6.1编写程序使第一个发光二极管以间隔500ms亮灭闪动。

(part2_4.c P48) .................................................................................................................................. - 5 -例2.7.1编写程序使第一个二极管以亮200ms、灭800ms的方式闪动。

(part2_5.c P49) ........................................................................................................................... - 6 -例2.8.3利用C51自带库_crol_(),以间隔500ms,实现流水灯程序(part2_6.c P53) .................................................................................................................................. - 6 -例3.2.1编写程序使第一个数码管显示8(part2.1_.1c P59) ......................... - 7 -例3.2.2让实验板上6个数码管同时点亮,依次显示0到F,时间间隔为0.5ms,循环下去。

51单片机C语言教程-郭天祥-PDF转word版第二章

本章详细介绍单片机程序常用编译软件Keil的用法,包括用Kei建立工程、工程配置、C51单片机程序软件仿真、单步、全速、断点设置、变量查看等。同时还介绍如何使用SST89E516RD单片机进行计算机与TX-IC单片机学习板之间的硬件仿真。用一个完整的C51程序来操作发光二极管的点亮与熄灭,然后调用C51库函数来方便地实现流水灯,最后为大家补充蜂鸣器与继电器的操作方法及集电极开路与漏极开路的概念。从这一章开始我们将手把手地讲解单片机C语言编程。认真学好本章,对于初学者来说将会是一个非常好的开头。

REG52.H

Header generic 80C52 and 80C32 microcontroller.

Copyright (c) 1988-2001 Keil Elektronik GmbH and Keil Software, Inc. All rights reserved.

--------------------------------------------------------------------------*/

tx1c实验板上发光二极管处连接锁存器的目的是因为发光二极管通过锁存器连接到单片机的p1口而板上ad芯片的数据输出端也连接到单片机的p1口当我们在做ad实验时ad芯片的数据输出端的数据就会实时发生变化而若不加锁存器那么发光二极管的阴极电平也跟随ad的数据输出的变化而变化这样就会看见发光管无规则闪动为了在做ad实验时不影响发光二极管我们在发光二极管与单片机之间加入一个锁存器用以隔离当做ad实验时我们可通过单片机将此锁存器的锁存端关闭而此时无论单片机p1口数据怎么变化发光二极管也不会闪动

完后续的代码而引发出更多的错误。解决办法如下:我们须将错误信息窗口右侧的滚动条拖到最上面,双击第一条错误信息,可以看到Keil软件自动将错误定位,并且在代码行前面出现一个蓝色的箭头。需要说明的是,有些错误连Keil软件自身也不能准确显示错误信息,更不能准确定位,它只能定位到错误出现的大概位置,我们根据这个大概位置和错误提示信息自己再查找和修改错误。双击图2.2.3中第一条错误信息后,显示如图2.2.4所示。

郭天祥单片机教程 第5章中断

第5章 MCS - 51单片机的中断

例 2 多中断源。 MCS - 51 单片机 有两个外部中断输入 端, 当有 2 个以上中 断源时, 它的中断输 入端就不够了。此时, 可以采用中断与查询 相结合的方法来实现。 可以使每个中断源都 接在同一个外部中断 输入端上, 同时利用 输入口线作为多中断 源情况下各中断源的 识别线。

EA X X X ET2 PT2 ES PS ET1 EX1 ET0 EX0 PT1 PX1 PT0 PX0

第5章 MCS - 51单片机的中断

5.2.3 中断响应 1. 中断响应的条件

在下列情况下,中断响应会受到阻断: (1) 同级或高优先级的中断已在进行中; (2) 当前的机器周期还不是正在执行指令的最后一个机 器周期(换言之, 正在执行的指令完成前, 任何中断请求 都得不到响应); (3) 正在执行的是一条 RETI或者访问特殊功能寄存器 IE或 IP的指令(换言之, 在 RETI或读写 IE或 IP之后, 不会 马上响应中断请求, 而至少执行一条其它指令之后才会响应)。

0 0

(LSB)

PS

PT1

PX1

PT0

PX0

中 中断 IP B8H 总 允 许 断 器 时

定 串 行 口

定 时 部 器 断 1 中

外 时 器

定 部 中 断

外

2

0 1 0

第5章 MCS - 51单片机的中断 表 5.2 同级内第二优先级次序

第5章 MCS - 51单片机的中断 例如, 某软件中对寄存器IE、 IP设置如下: MOV IE, # 8FH MOV IP, # 06H 则此时该系统中: * CPU中断允许; * 允许外部中断0、外部中断1、定时器 /计数器0、定时器/计 数器1中断申请; * 中断源的优先次序为: 定时器0 > 外部中断1 > 外部中断0 > 定时器1。

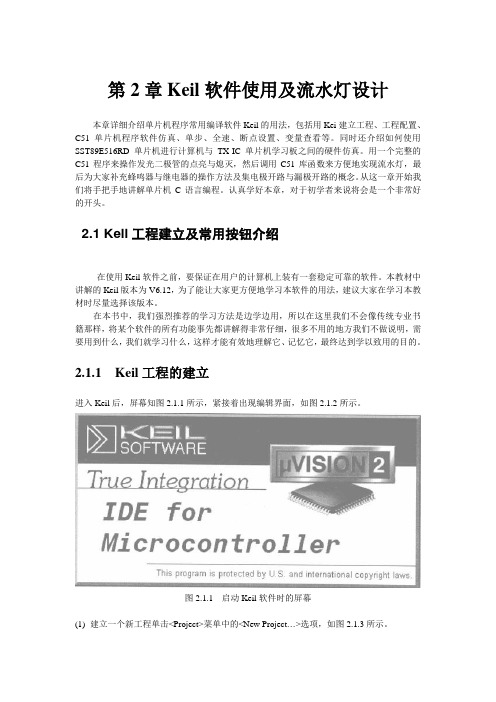

51单片机最小系统原理图PCB

回想自己自己当初学习单片机的历程倍感艰辛,大一开始就进入实验室,学过51单片机、MSP430单片机、C8051F单片机、PIC单片机、ZIGBEE(CC2530处理器,个人觉得比单片机层次更高一些,可以应用的协议栈系统比较丰富),后来又学习了DSP、FPGA、ARM,参加过很多电子设计大赛,做了不少项目,也申请了几个专利。

当然,这期间的付出也非常非常多,大学七年里面几乎没有歇息过,放弃了寒暑假,一直呆在实验室里面,双休日也很少出去玩......所以我想说的是做技术确实很辛苦,需要坚韧不拔的毅力,需要付出很多很多。

当然这期间也走了不少的弯路,撞来撞去,像个丈二和尚摸不着头脑,哈哈。

所以希望分享一些有用的东西给大家,希望对大家有所帮助吧。

以前做了不少的PCB板子,现在也用的不多了,共享给大家,希望对大家有所帮助。

以后有时间,我会定期分享给大家一些做单片机方面的资料,还有如果哪位师弟师妹嫌买的学习板太贵的话,可以多几个人一起找我,我给大家做PCB电路板,大家自己买元器件,自己焊接调试,我想这样可能你们会学到的更多一些,而且还能少华一点钱。

今天我先把51单片机的最小系统原理图还有PCB文件共享给大家,这个是我以前做的PCB,大家可以直接拿去做PCB板子,如果那里有什么不懂的可以找我。

资料我上传到了“大牙兔工程师论坛,在STC板块就可以找到,或者直接搜索‘免费开源共享了,原理图+PCB+实物,教会大家做单片机最小系统’也可以找到”,也可以添加群234717900要资料。

1.最小系统原理图:2.PCB顶层设计3.PCB底层设计4.实物图6.基于Altium designer的原理图文件原理图文件.rar(10.12 KB, 下载次数: 1286) 7.基于Alitum designer的PCB文件PCB文件.rar(47.56 KB, 下载次数: 1569)。

郭天祥pdf

跑飞的情况,因此我们也很难人为制造出使单片机程序跑乱的情况,下面的

程序演示利用看门狗的溢出时间来使程序自动复位运行。

【例】:在 TX-1C 实验板上实现如下描述:程序启动后设定看门狗溢

出时间为 2 秒左右,然后点亮第一个发光二极管,稍延时一会,然后熄灭发

光二极管,使程序进入等待死循环状态,并且在死循环中大约每隔 1 秒喂狗

一次,看程序运行是否正常。

新建文件 part3.4.2.c,程序代码如下:

#include <reg52.h>

//52 系列单片机头文件

#define uchar unsigned char

#define uint unsigned int

sfr WDT_CONTR=0xe1;

sbit led1=P1^0;

上图设置存储器模式为 large 模式 其次,为安全起见,当程序中定义多于 128 字节的其它变量时,最好申明为 xdata 型,如 uchar xdata table[100];意思为定义一个 100 个字节容量的数组,将其在扩展 RAM 中分配存储空间。另外 一定要注意,在 large 模式下,编写程序时,定义的变量总数千万不要超过对应单片机的内部最大

倍速与双倍速的设置在下载程序软件界面上有设置选择,大家可自行

下载测试程序运行速度。预分频数的值由 PS2、PS1 和 PS0 的组合确

定,如表 4.2.2 所示。晶振频率即为当前系统的时钟频率。

下面我们通过两个例子来进一步讲解使用看门狗和不使用看门狗时程

序运行的区别,由于 STC 单片机的高抗干扰特点,至今我还未曾遇到过程序

ቤተ መጻሕፍቲ ባይዱRAM 字节数,因为即使超过了,编译器也不会提示错误,但是程序必定会出错。

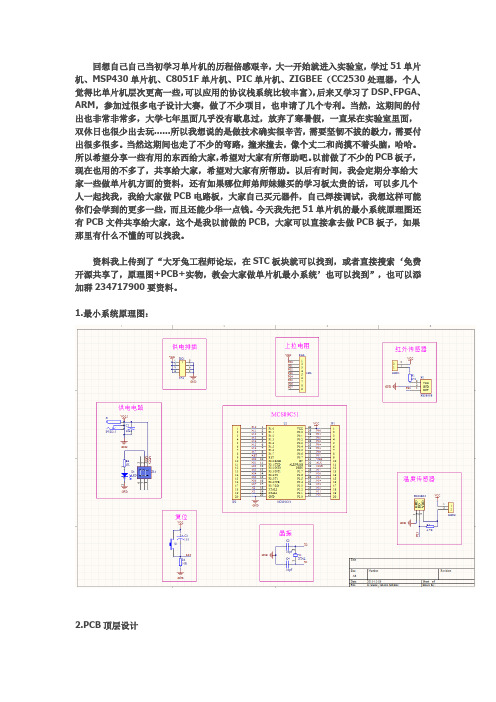

51单片机第四节数码管

51单⽚机第四节数码管本笔记默认学习者已拥有:1.Keil5和stc 烧写⼯具 等各种软件、驱动、环境;2.有⼀个属于⾃⼰的 51单⽚机开发板及相关零件 ;3.认识C 语⾔的语法;本⼈使⽤的51开发板为 郭天祥C51 TX-1C 增强版开发板 ;本笔记根据B 站up 主:江科⼤⾃化协的教学视频 整理得到ヾ(•ω•)4-1 静态数码管显⽰上图为TX-1C 的 数码管及LED 模块 原理图138译码器和74HC245 都是⽤来控制 数码管显⽰ 的;单数码管1.上图为 ⼀位数码管,数码管有两种连接⽅式(对应 右边上下两幅图);2.右上图的原理图,8个LED的阴极都连在⼀个引脚上,称为共阴极连接;3.右下图的原理图,8个LED的阳极都连在⼀个引脚上,称为共阳极连接;TX-1C 开发板的连接⽅式是 共阴极连接;4.左下⾓的 左边图⽚ ,定义了8个LED的名称;5.左下⾓的 右边图⽚ ,定义了引脚的名称,与右图的引脚名称⼀⼀对应假设数码管连接⽅式为 共阳极连接,观察可以发现,数码管中的 LED 的引脚引出,使⽤的是就近原则;假设数码管连接⽅式为 共阴极连接,如果上数码管显⽰ 数字6 ?1.要让数码管显⽰ 数字6,让要 LED-A、C、D、E、F、G亮起;2.共阴极的公共端 要接地(给数据‘0’,或者是低电平);3.阳极(称为位选端)根据LED的亮灭需求给 数据0或1(1亮、0灭) ,称为 段码(阳码) (1011 1110 即为段码);如果 共阳极连接,共阳极端 要接到 VCC (⾼电平),阴极给 数据0或1 (1灭,0亮),称为 段码(阴码),和共阴极正好是相反关系;共阳极连接→共阳极端接VCC 并选中→阴极(位选端)传递(阴码)段码(1亮、0灭)→数码管显⽰共阴极连接→共阴极端接GND 并选中→阳极(位选端)传递(阳码)段码(1灭、0亮)→数码管显⽰四位⼀体数码管开发板上即为 四位⼀体的数码管,且有两个,正好组成了 ⼋位数码管;⽽TX-1C 上 包含的是六位数码管,⽽⾮⼋位;1.四位数码管 也有 两种连接⽅式,即 共阴极连接 和 共阳极连接 ;{Processing math: 100%2.四位数码管,(每位的公共端 单独引出来,位选端全部连在⼀起(所有A段连在⼀起、所有B段连在⼀起……),总共有12个引脚;假设数码管连接⽅式为共阴极连接,如何在第三位显⽰数字1 ?1.给第三位的公共端 赋值 0(低电平),给其他位的公共端 赋值 1(⾼电平);这样等同于 其他位的公共端(负极)接到了正极上,⽆论如何都亮不了;只有第三位能亮;2.这样给 LED-B、C 的位选端 赋值 1,其他 位选端 赋值0共阳极连接即为公共端赋值 1(⾼电平)亮,其他以此类推;3.发现这样⼀个现象,数码管⽆法在同⼀时间显⽰多个数字,其在同⼀时刻下只能有⼀个显⽰,只有⼀个数码管能被点亮,即使有多个被选中的数码管,显⽰的数字也是相同的;这种共⽤引脚的现象,是为了减少控制数码管IO⼝;(四位数码管有32个LED,如果都采⽤共阴极连接的⽅式,也要32+1(公共端)=33个引脚;)(采⽤这种链接,就只需要12个引脚即可控制四位数码管;)如何让数码管多位显⽰不同数字(动态数码管显⽰)?1.利⽤ ⼈眼视觉的暂留 和 数码管显⽰的余辉 的原理先让第⼀位数码管显⽰1,然后很快地让第⼆位数码管显⽰2,再很快地让第三位数码管显⽰3,让它不断地扫描,重复显⽰1、2、3的过程,这样三个数字就“同时”显⽰了;原理分析138译码器1.观察到 原理图右图 与数码管有关的,有138译码器(74LS138)和74HC245两枚芯⽚;TX-1C的原理图为左图,也有两个74HC573芯⽚与数码管有关;芯⽚名称与功耗、电压、说明符号有关,具体内容不做分析;2.如图,数码管连接⽅式为 共阴极连接,这样传输数据,就能让第三位显⽰ 数字1 了;3.⽽上⾯的 LED1 ~ 8,其实接在了138译码器的输出端,138译码器正好可以实现让LED1 ~ 8输出 0或1;LED1 ~ 8 对应了 TX-1C 六位数码管的SEG DS 1 ~ 6;4.138译码器可将LED 1 ~ 8的⼋个端⼝ 转化为 由 3个端⼝ (P22、P23、P24)控制,⽽G1、G2A、G2B端⼝ 被 称为 使能端;使能端相当于⼀种开关,如果电平有效,它就可以⼯作;如果电平⽆效,它就不⼯作;观察原理图发现,使能端是已经接好 VCC 和 GND 的,也就是说,其上电其实就会⼯作TX-1C的74HC573也是同理,但其并未压缩控制端⼝的数量;5.138译码器也叫“38线译码器”,是由3个线到8个线,其中C是⾼位、A是低位,CBA组成的数符合8进制,控制着Y0 ~ Y7 这8个端⼝;6.所以,138译码器的作⽤就是⽤来选中某⼀位数码管的74HC2451.74HC245是⼀种 双向数据缓冲器,VDD、GND都可视为电源,OE为使能(其 接地 就⼯作);2.DIR(direction),是⽅向的意思,它接到了VCC(⾼电平)上,将数据从左边输出到右边,从右边将数据读取回左边;DIR若接到低电平上,会将数据从右边输出到左边,从左边将数据读取回右边;3.单⽚机的⾼电平 驱动能⼒有限,其输出的最⼤电流不能太⼤;其低电平 驱动能⼒强;因此,LED模块才采⽤了低电平点亮的模式;4.如果⽤⾼电平 直接点亮 数码管,电流会很⼩,灯会很暗;所以其加⼀个缓冲器,缓冲器可以提⾼ 其驱动能⼒,如果直接将 数据 输出 给 数码管,数据就会被视为 驱动数据;现在增加了缓冲器,数据 就变成了 控制信号,控制信号 只需要很微弱,缓冲器 就可以接收到,缓冲器再通过⾃⼰接到的电源,输出 数据 到引脚上,这样控制的电流只需要⾮常⼩,就能驱动数码管 以⽐较亮的形式显⽰;2电容 是⽤来 稳定电源的,叫电源滤波;6.图右有 ⼀ 排阻,阻值为100R(即为100Ω),作⽤为 限流电阻 ,防⽌数码管的电流过⼤;TX-1C既没有电容,也没有排阻;原理总结1.⽤ 138译码器 使 数码管 的某⼀位 被选中;2.再给P0⼝⼀个 段码数据;TX-1C虽然⽤P0⼝控制段码输⼊,但也⽤P0⼝控制位选;需要先⽤ P2.6⼝和P2.7⼝控制输⼊数据是段码还是位选;P2.6⼝控制段码的输⼊;P2.7⼝控制位选的输⼊;例,给P2.6 数据1 (⾼电压)、给P2.7 数据 0 (低电压),就可以确定现在给数据是段码;1.由TX-1C的原理图可知,数码管内 LED灯 与 P0端⼝ 的顺序关系:(1)LED的名称定义是通⽤⽆疑的;(2)数码管本⾝的引脚名称不重要,重要的是 LED与哪个 P0 的 引脚 相连;2.由TX-1C的原理图可知, P0.0引脚 控制 数码管的最左位,P0.5引脚控制 数码管的最右位,剩余引脚是没有控制 数码管 位选 的作⽤的,哪个P0 的 引脚 控制 六位数码管的 哪位 很重要;代码实现静态数码管显⽰(让数码管第三位显⽰3).c#include<reg51.h>sbit D=P2^6; //段码⼝sbit W=P2^7; //位选⼝void main(){D=0;W=1;P0=0xFB;//1111 1011W=0;D=1;P0=0x4F;//0100 1111while(1);}下⾯写出了⼀个通⽤函数,可以让数码管在 第⼏个位置 显⽰ 哪个数#include<reg51.h>#define uchar unsigned charsbit D=P2^6;sbit W=P2^7;void NixieTube(uchar wei,uchar duan){ //NixieTube是数码管的英⽂uchar WEI,DUAN; //(Nixie是⼥⽔妖的意思)D=0;W=1;switch(wei){ //位选部分case 1:WEI=0xFE; break;case 2:WEI=0xFD; break;case 3:WEI=0xFB; break;case 4:WEI=0xF7; break;case 5:WEI=0xEF; break;case 6:WEI=0xDF; break;}P0=WEI;W=0;D=1;switch(duan){ //段码部分case 0:DUAN=0x3F; break;case 1:DUAN=0x06; break;case 2:DUAN=0x5B; break;case 3:DUAN=0x4F; break;case 4:DUAN=0x66; break;case 5:DUAN=0x6D; break;case 6:DUAN=0x7D; break;case 7:DUAN=0x07; break;case 8:DUAN=0x7F; break;case 9:DUAN=0x6F; break;case 10:DUAN=0x77; break; //Acase 11:DUAN=0x7F; break; //Bcase 12:DUAN=0x39; break; //Ccase 13:DUAN=0x3F; break; //Dcase 14:DUAN=0x79; break; //Ecase 15:DUAN=0x71; break; //Fcase 16:DUAN=0x80; break; //.}P0=DUAN;}void main(){NixieTube(3,3);while(1);}运⾏结果如下:4-2 动态数码管显⽰1.如果只是单纯让其显⽰完⼀个再显⽰⼀个,代码如下:#include<reg51.h>#define uchar unsigned charsbit D=P2^6;sbit W=P2^7;uchar Nixiewei[]={0,0xFE,0xFD,0xFB,0xF7,0xEF,0xDF};uchar Nixiecode[]={0x3F,0x06,0x5B,0x4F,0x66,0x6D,0x7D,0x07,0x7F,0x6F,0x77,0x7F,0x39,0x3F,0x79,0x71,0x80};//将两个switch改进为数组void NixieTube(uchar wei,uchar duan){D=0;W=1;P0=Nixiewei[wei];W=0;D=1;P0=Nixiecode[duan];}void main(){while(1){NixieTube(1,1);NixieTube(2,2);NixieTube(3,3);}}运⾏结果如下:2.这是⼀个数码管的常见问题,称为 数码管的消影 ;位选-->段选-->位选-->段选-->位选-->......在这⼀位的段选(输⼊段码)结束,进⾏下⼀位的位选时,很短的时间内,上⼀位的数据会串到下⼀位数据⾥⾯去;所以我们在段选和位选之间,增加⼀个 P0 清零的操作;动态数码管显⽰(数码管同时显⽰123).c#include<reg51.h>#define uchar unsigned charsbit D=P2^6;sbit W=P2^7;uchar Nixiewei[]={0,0xFE,0xFD,0xFB,0xF7,0xEF,0xDF};uchar Nixiecode[]={0x3F,0x06,0x5B,0x4F,0x66,0x6D,0x7D,0x07,0x7F,0x6F,0x77,0x7F,0x39,0x3F,0x79,0x71,0x80};void Delayms(unsigned int x){unsigned int j;for(;x>0;x--) for(j=110;j>0;j--);}void NixieTube(uchar wei,uchar duan){D=0;W=1;P0=Nixiewei[wei];W=0;D=1;P0=Nixiecode[duan];Delayms(1); //让数码管稳定显⽰,⽴刻清零会让数码管显⽰较暗P0=0; //清零操作}void main(){while(1){NixieTube(1,1);NixieTube(2,2);NixieTube(3,3);}}运⾏结果如下:相关知识1.在运⾏某些代码时,TX-1C的LED点阵模块会乱闪2.将左下⾓ DOT-OE旁的跳线帽 拔下来即可 断开LED点阵模块,3.拔下来的跳线帽不要乱丢,可以 只插⼀个脚放在原处,也可以妥善保管在其他地⽅上图即为拔下来的跳线帽1.此元件为电容;2.104的数量规则与 第⼆节 所讲的电容是相同的,其单位是pF1000pF=1nF, 1000nF=1uF, 1000uF=1000mF, 1000mF=1FF 是⼀个很⼤的单位,正常电容都是uF、nF级别的;超级电容能达到1 ~ 2 F,其⼀般作为备⽤电池;3.TX-1C的原理图上,电容的量都是直接⽤单位标记好的。

51单片机原理图

2.3 51单片机增强型学习系统各组成部份原理图及功能简介2.3.1 共阴极数码管动态扫描控制图2.2 51单片机增强型学习系统的四位共阴极数码管动态扫描硬件连接原理图AT89S51单片机P0口是一组8位漏极开路型双向I/O 口,也即地址/数据总线复用口。

作为输出口用时,每位能驱动8个TTL 逻辑门电路,对端口写“1”可作为高阻抗输入端用。

在访问外部数据存储器或程序存储器时,这组口线分时转换地址(低8位)和数据总线复用,在访问期间激活内部上拉电阻。

在Flash 编程时,P0口接收指令字节,而在程序校验时,输出指令字节,校验时,要求外接上接电阻。

AT89S51单片机P2口是一个带有内部上拉电阻的8位双向I/O 口,P2的输出缓冲级可驱动(吸收或输出电流)4个TTL 逻辑门电路。

对端口写“1”,通过内部的上拉电阻把端口拉到高电平,此时可作输入口,作输入口使用时,因为内部存在上拉电阻,某个引脚被外部信号拉低时会输出一个电流。

在访问外部程序存储器或16位地址的外部数据存储器(例如执行MOVX @DPTR 指令)时,P2口送出高8位地址数据。

在访问8位地址的外部数据存储器(如执行MOVX @Ri 指令)时,P2口线上的内容(也即特殊功能寄存器SFR 区中P2寄存器的内容),在整个访问期间不改变。

Flash 编程或校验时,P2亦接收高位地址和其它控制信号。

在上面的硬件连接原理图里,我们用到的是P0和P2口控制四位数码管显示的。

四位数码管显示的方式是动态扫描显示,动态扫描显示是单片机中应用最为广泛的一种显示方式之一。

其接口电路如上图是把所有显示器的8个笔划段a-h同名端连在一起由单51单片机增强型学习系统片机的P0.0~P0.7控制,而每一个数码管的公共极(阴极)是各自独立地受单片机P2.7~P2.4控制。

CPU向字段输出口P0口送出字形码时,所有数码管接收到相同的字形码,但究竟是那个数码管亮则取决于P2.7~P2.4的输入结果,所以我们就可以自行决定何时显示哪一位了。

郭天祥十天学会单片机PPT课件

十天学会单片机 完整版

五个中断源的中断控制系统; 一个全双工UART(通用异步接收发送器) 的串行I/O口,用于实现单片机之间或单片机 与微机之间的串行通信; 片内振荡器和时钟产生电路,石英晶体和微 调电容需要外接。最高振荡频率取决于单片 机型号及性能。

C51知识

C语言是一种编译型程序设计语言,它兼顾 了多种高级语言的特点,并具备汇编语言的 功能。目前,使用C语言进行程序设计已经 成为软件开发的一个主流。用C语言开发系 统可以大大缩短开发周期,明显增强程序的 可读性,便于改进、扩充和移植。而针对 8051的C语言日趋成熟,成为了专业化的实 用高级语言。

非总线型

RST P3.0/RXD P3.1/TXD XTAL2 XTAL1 P3.2/INT0 P3.3/INT1 P3.4/T0 P3.5/T1 GND 1 2 3 4 5 6 7 8 9 10 20 19 18 17 16 15 14 13 12 11 VCC P1.7 P1.6 P1.5 P1.4 P1.3 P1.2 P1.1/AIN1 P1.0/AIN0 P3.7

C-51数据的存储类型

例:

数据类型 变量名

char var1; bit flags; unsigned char vextor[10]; int wwww; 注意:变量名不能用C语言中的关 键字表示。

◆单板机 将CPU芯片、存储器芯片、I/O接口芯片和 简单的I/O设备(小键盘、LED显示器)等装 配在一块印刷电路板上,再配上监控程序(固 化在ROM中),就构成了一台单板微型计算 机(简称单板机)。

STC89C51单片机介绍

资料多 郭天祥视频选用STC89C51型号 本学院大部分同学研究51单片机时以 STC89C51为基础

VCC,GND XTAL1:内部振荡电路反相放大器输入端,使用外部 晶体是连接晶体,使用外部振荡源时接地 XTAL2:与XTAL1不同是输出端 ALE/PROG:地址锁存信号输出引脚 PSEN:外部程序程序存储器读选通引脚 RST/VDD:复位信号引脚 EA/VPP:高电平,程序从外部程序存储器开始执行; 低电平从内存开始

IO引脚:P0,P1,P2和P3,其中P2P0组成了16位数据总线,P2位 高位,P0还可以复用为8位数据总线,P0,P1,P2可做普通IO口, P3具有第3功能 P3:P3.0:RXD串行口输入 P3.1:TXD串行口输出 P3.2:INT0外部中断0输入 P3.3:INT1外部中断1输入 P3.4:T0定时器0外部输入 P3.5:T1定时器1外部输入 P3.6:WR外部写控制 P3.7:RD外部读控制

Leabharlann 何为I/O口

I: 输入(input) 输入高低电平 O:输出(output) 输出高低电平

IO口是单片机最为重要的控制端口,是单片机实 现功能的基础,有输入输出的电流限制。输入 电流过大会烧坏管脚

我的大学六年(郭天祥原创老王强烈推荐)

我的大学六年(单片机大师郭天祥原创)在哈尔滨工程大学五年,我在学校电子创新实验室呆了四年,这四年里创新实验室给我提供了良好的学习环境和完善的实验设备;在这里与众多电子爱好者的交流中,使我学到了更多的专业知识;在学校老师们的教导下,让我学会了如何做一名合格的大学生。

因此,在这里我要感谢哈尔滨工程大学的历任领导,我今天成绩的取得得益于他们不断完善的教育体制;衷心地感谢曾经教导过我的刁鸣教授、付永庆教授、王松武教授,没有他们对我的培养,也就没有我的今天。

同时我也希望能有更多的电子爱好者加入创新实验室,在完善自我的同时,在电子行业做出更突出的业绩。

2007年,我以全新的教学方式推出了一套讲述51单片机的教学视频课程——“十天学会单片机”(就是我们现在看的那套视频),该视频自从网上发布后,得到了电子爱好者的一致好评,诸多的单片机初学者通过这套视频走上了单片机开发之路。

有很多学员来信或打电话希望我能够将视频中的内容著书出版,让更多的人受益。

为此,从2007年9月至2008年7月,我用了近十个月的时间将书《新概念51单片机C语言教程-入门、提高、开发、拓展全攻略》(预计08年11月上市,全国各大新华书店有售)写完。

本书的写作风格与我在教学视频中的讲课风格相似,它与传统讲授单片机的书籍完全不同,我以学单片机“过来人”的思路,抱着如何才能更容易掌握单片机的态度,理论与实践完全结合的方式清晰地讲解了单片机部分。

其余大部分内容为我多年做项目的经验积累,也有部分内容来自于网络电子高手们的精华总结,应当说,在本书中有太多的知识是大家平时在书本上所学不到的。

在这里,先将我在大学期间的学习和生活经历与大家分享,借此鼓舞大家珍惜大学时光,多学习文化知识,开创更加美好的明天。

写这篇文章的时候,我正处于硕士研究生毕业论文的准备阶段,眼睁睁看着我的大学生活即将画上句号,再看看身边有很多低年级的学生们一天天把时间白白荒费掉,我在心里替他们惋惜,在即将结束我的大学生活之际,我将我的大学几年的有意义的生活与大家分享,看过这篇文章后也许能让那些有梦想的同学为了实现自己的人生目标少走些弯路,大家要相信,大学校园——将为你提供一生最好的学习环境。

经典的51单片机最小系统电路原理图:国产STC系列(51内核)

什么是51单片机?1980年,Intel推出了首款单片机8051,之后又陆续推出了与8051指令完全相 同的8031、8032、8052等系列的单片机,初步形成了MCS-51系列。 1984年,Intel出售了51 核,此后,世界上出现了上千种51单片机,如爱特梅尔、飞利浦,华邦,还有国内的宏晶 (STC micro)等。51单片机泛指所有兼容 8051指令的单片机。

有个问题,单片机的工作时钟从哪里来?之前8051那时候的单片机一般都需要外部晶振电路提 供工作时钟,然而现在单片机一般在芯片内部都集成了RC振荡电路,通过软件可以启用单片机 内部的RC振荡器脉冲作为单片机的内部工作时钟,这样不仅电路简单,而且还节省了产品的成 本。不过在一些精度要求比较高的应用场合,例如对外异步串口通讯、电子钟等,对时钟精度 要求比较高,这时候就必须用外部晶振电路了。

该单片机在VCC引脚上给它5V电,这就够了,不需要其它ቤተ መጻሕፍቲ ባይዱ加电路。

该单片机的程序下载是通过P3.0和P3.1两个引脚实现的,利用的是这两个引脚的串口功能。因 此这两个引脚在实际应用时一般用作串口功能,不做其它用途。当然,如果引脚数量比较紧 张,必须启用这两个引脚,也不是不可以,但尽量用作输入口。

图中框框部分是程序下载器电路,可以直接设计到产品电路板上,以后就可以直接用USB口下 载软件;也可以将其省略,只是在下载软件时必须通过一个下载器进行。实际上下载器内部电 路就是这个图框里面的电路。如果你把这个框框里面的电路做成电路板,就可以自己做一个程 序下载器。

结束语:单片机起源于51,世界上最经典的单片机非51莫属,至今我还有很多项目都是用51单 片机做的,除了成本考虑之外,现在很多芯片厂家已经在51内核基础上扩展了很多非常实用的 外设(例如LIN和CAN通讯模块,增强型PWM模块,电机控制和驱动模块等等),这用起来其 实很方便