数字集成电路1

集成电路概念1

集成电路概念11.什么是特征尺⼨和集成度?它们之间有什么关系?集成度是指⼀个IC 芯⽚所包含的芯⽚数⽬(晶体管或门数,包括有源或⽆源元件)。

为了提⾼集成度,采取了增⼤芯⽚⾯积,缩⼩器件特征尺⼨,改进电路即结构设计等措施。

特征尺⼨定义为器件中最⼩线条宽度(对MOS 器件⽽⾔通常指器件栅电极所决定的沟道⼏何长度)也可定义为最⼩线条宽度与线条间距之和的⼀半。

减⼩特征尺⼨是提⾼集成度改进器件性能的关键。

2.什么是摩尔定律?预测了什么?摩尔定律:每两年芯⽚功能翻⼀番。

根据预测今后20年时间内集成电路的集成技术及其产品仍将遵守这⼀定律3.简述MOSFET 的种类及各⾃电流电压特性?根据MOSFET 器件沟道材料掺杂类型的不同MOS 器件可分为N 型MOS 器件和P 型MOS 器件其电流电压特性分别为:N 型线性区:]21)[(2DS DS T GS OX n d V V V V L W C I ??=µ饱和区:2)(21T GS OX n d V V LWC I ?=µ4.什么是MOS 器件的阈值电压?受哪些因素影响?形成沟道所对应的栅极电压成为阈值电压,在半导体中定义为半导体表⾯处的平衡勺⼦浓度等于体内平衡多⼦浓度时的栅极电压:OXSOX OX F US T C Q C Q V ??+=φφ2其中US φ是多晶硅或⾦属栅和衬底功函数差。

)ln()(isub FN N q kT =φ为衬底费⽶能势,OX C 是栅氧化层电容,OX Q 是栅氧化层内有效电荷⾯密度,S Q 半导体的电荷⾯密度。

阈值电压受这些因素的影响同时可通过沟道中注⼊杂质来调整阈值电压。

5.伴随着MOSFET 的沟道长度的减⼩许多原来可忽略的效应变得显著起来甚⾄成为主导因素,结果导致器件的特性和长沟道模型发⽣偏离这种偏离即短沟道效应,本质是电特性的改变,⽽不是长度的变化。

发⽣条件:当MOSFET 源,漏结耗尽层宽度与沟道长度相当时短沟道开始显现。

集成逻辑门1数字集成电路的分类

第3章 集 成 逻 辑 门

e1 N e2 N e3 N P N P型衬底 (a ) UCC R1 b e1 e2 e3 A BC c A e1 B e2 C e3 (b ) R1 V1 V2 V3 b P1 V4 c UCC b c

图 3-2 多射极晶体管的结构及其等效电路

第3章 集 成 逻 辑 门

② 中间级。由V2、R2、R3组成,在V2的集电极与

发射极分别可以得到两个相位相反的电压,以满足输

出级的需要。 ③ 输出级。由 V3 、 V4 、 V5和R4、R5 组成,这种电 路形式称推拉式电路,它不仅输出阻抗低,带负载能 力强, 而且可以提高工作速度。

超大规模集成电路(VLSI-Very Large Scale Integration),

每片组件内含100 000个元件(或1000个以上等效门)。

第3章 集 成 逻 辑 门

目前常用的逻辑门和触发器属于SSI, 常用的译码器、 数据选择器、 加法器、 计数器、 移位寄存器等组件属 于MSI。 常见的LSI、 VLSI有只读存储器、 随机存取存 储器、 微处理器、 单片微处理机、 位片式微处理器、

第3章 集 成 逻 辑 门

1. 输入全部为高电位(3.6 V) 当输入端全部为高电位3.6V时,由于V1的基极电压 Ub1 最多不能超过 2.1V(Ub1=Ubc1+Ube2+Ube5) ,所以 V1 所有 的发射结反偏;这时 V1 的集电结正偏, V1 管的基极电流 Ib1流向集电极并注入V2的基极,

CMOS 概述 (一)

CMOS(Complementary Metal Oxide Semiconductor)指互补金属氧化物(PMOS管和NMOS管)共同构成的互补型MOS集成电路制造工艺,它的特点是低功耗。

由于CMOS中一对MOS组成的门电路在瞬间看,要么PMOS导通,自1958年美国德克萨斯仪器公司(TI)发明集成电路(IC)后,随着硅平面技术的发展,二十世纪六十年代先后发明了双极型和MOS型两种重要的集成电路,它标志着由电子管和晶体管制造电子整机的时代发生了量和质的飞跃。

MOS是:金属-氧化物-半导体(Metal-Oxide-Semiconductor)结构的晶体管简称MOS晶体管,有P 型MOS管和N型MOS管之分。

由MOS管构成的集成电路称为MOS集成电路,而由PMOS管和NMOS管共同构成的互补型MOS集成电路即为CMOS-IC( Complementary MOS Integrated Circuit)。

目前数字集成电路按导电类型可分为双极型集成电路(主要为TTL)和单极型集成电路(CMOS、NMOS、PMOS等)。

CMOS电路的单门静态功耗在毫微瓦(nw)数量级。

CMOS发展比TTL晚,但是以其较高的优越性在很多场合逐渐取代了TTL。

以下比较两者性能,大家就知道其原因了。

1.CMOS是场效应管构成,TTL为双极晶体管构成2.CMOS的逻辑电平范围比较大(5~15V),TTL只能在5V下工作3.CMOS的高低电平之间相差比较大、抗干扰性强,TTL则相差小,抗干扰能力差4.CMOS功耗很小,TTL功耗较大(1~5mA/门)5.CMOS的工作频率较TTL略低,但是高速CMOS速度与TTL差不多相当。

集成电路中详细信息:1,TTL电平:输出高电平>2.4V,输出低电平<0.4V。

在室温下,一般输出高电平是3.5V,输出低电平是0.2V。

最小输入高电平和低电平:输入高电平>=2.0V,输入低电平<=0.8V,噪声容限是0.4V。

常用数字集成电路

常用数字集成电路常用数字集成电路是指在数字电子技术中常用的各种电路,用于实现数字信号的处理、存储和传输。

这些电路广泛应用于计算机、通信、控制系统等领域,是现代数字系统的核心组成部分。

本文将从数字电路的基本组成、常见的数字集成电路和其应用等方面进行阐述。

数字电路由数字元件、数字线路和数字设备组成。

数字元件包括逻辑门、触发器、计数器、移位寄存器等。

逻辑门是实现逻辑运算的基本元件,包括与门、或门、非门等。

触发器是用于存储和传输二进制信息的元件,常见的有RS触发器、D触发器、JK触发器等。

计数器用于计数和计时,常见的有二进制计数器、BCD计数器等。

移位寄存器用于数据的移位和存储,常见的有移位寄存器、移位寄存器等。

常见的数字集成电路包括门电路、触发器电路、计数器电路、显示器电路等。

门电路由逻辑门组成,可以实现与、或、非等逻辑运算。

触发器电路用于存储和传输信息,可以实现时序逻辑功能。

计数器电路可以实现计数和计时功能,广泛应用于时钟、频率分频等领域。

显示器电路用于将数字信号转化为可视化的信号,常见的有数码管显示器、液晶显示器等。

数字集成电路在各个领域有着广泛的应用。

在计算机中,数字集成电路用于实现中央处理器、存储器、输入输出设备等。

在通信系统中,数字集成电路用于实现编解码器、调制解调器、数字滤波器等。

在控制系统中,数字集成电路用于实现控制器、传感器、执行器等。

数字集成电路的应用使得数字系统具备了高速、高精度、高可靠性的特点。

总结起来,常用数字集成电路是数字电路中的重要组成部分,用于实现数字信号的处理、存储和传输。

它们由数字元件、数字线路和数字设备组成,包括逻辑门、触发器、计数器、移位寄存器等。

常见的数字集成电路有门电路、触发器电路、计数器电路、显示器电路等。

它们在计算机、通信、控制系统等领域有着广泛的应用。

数字集成电路的发展使得数字系统具备了高速、高精度、高可靠性的特点,推动了数字技术的不断进步。

数字电路第一章

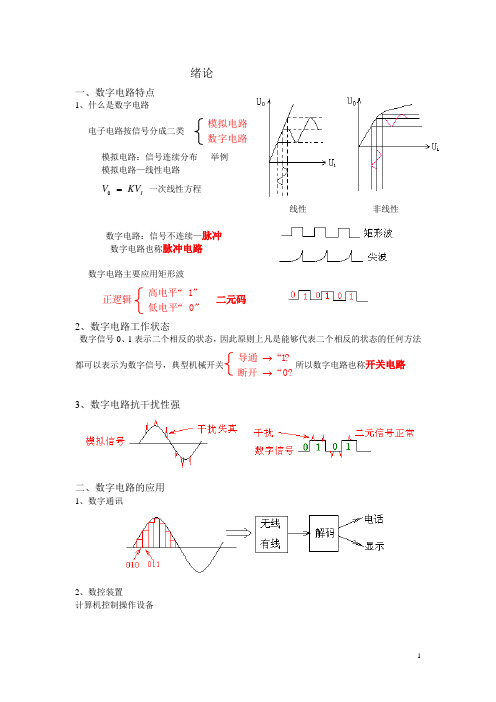

绪论一、数字电路特点1、什么是数字电路电子电路按信号分成二类模拟电路数字电路模拟电路:信号连续分布 举例模拟电路—线性电路 0IV K V = 一次线性方程 线性 非线性数字电路:信号不连续—脉冲数字电路也称脉冲电路数字电路主要应用矩形波正逻辑高电平 1低电平 0“”“”二元码2、数字电路工作状态数字信号0、1表示二个相反的状态,因此原则上凡是能够代表二个相反的状态的任何方法都可以表示为数字信号,典型机械开关 导通“1 断开“0→→所以数字电路也称开关电路3、数字电路抗干扰性强二、数字电路的应用1、数字通讯2、数控装置 计算机控制操作设备3、数字计算机(最广泛、最杰出的应用)算盘1857年,Hill计数器1890年人口普查使用的制表机第二代1951年,IBM开始决定开发商用电脑,聘请冯·诺依曼担任公司的科学顾问,1952年12月研制出IBM第一台存储程序计算机,也是通常意义上的电脑,这是IT历史上一个重要的里程碑。

它叫IBM 701。

第一代1946年启动“埃尼阿克”(ENIAC)计算机1958年8月16日第一个集成电路第三代1964年4月7日,IBM主席Tom Watson,System 360。

Jr.亲自发布System 360。

超级计算机IBM蓝色基因落户德日计算相当于1.5万台PC( 2006年)第一章逻辑代数基础前面二进制数表示方法不讲,其它学科介绍,本书不用这些概念。

二进制逢二进一1101,110 ++右面给出常用的四位二进制逐一递增的8.4.2.1码。

§1.1 基本概念公式和定理1.1.1 基本和常用逻辑运算一、三种基本逻辑运算1、 与逻辑(与运算、逻辑乘)与逻辑—全部条件具备,事件发生。

下图用机械开关来表示与逻辑运算。

功能表开、关,亮、灭是一个二元状态,可以用0、1码表示 ②真值表 ①赋值合,亮断10,灭→→③与逻辑式 YA B =⋅④逻辑图(符号)多端输入(多个开关) Y ABC =上述逻辑运算的器件称“门” 对应与逻辑称“与门”2、 或逻辑(逻辑加)或逻辑— 一个或一个以上条件具备,事件发生。

2024新高考浙江版高中通用技术专题九 电子控制技术知识点归纳讲解PPT

外观与符号

特点 阻值基本不变

阻值可调

正偏时可导通(类似普通二极 管);反偏时具有稳压特性

4.二极管正负引脚的判断

1)普通二极管与稳压二极管: ①带符号的按符号判断正、负极; ②靠近色环的电极为负极; ③子弹状的子弹朝向即电流方向。

2)发光二极管与光敏二极管: ①长脚为正极,短脚为负极; ②内部金属区大的为负极,小的为正极。 五、三极管 1.含义:半导体三极管(transistors)又称晶体三极管,简称三极管。在一块 半导体基片上制作2个极靠近的PN结,构成三极管的管芯。 2.结构与符号

模拟信号 数字信号

特征 连续变化 不连续变化

描述 连续变化的直线或曲线 柱状图或数字

3.数字信号的优点:容易处理、处理精度高、便于记录保存等。

二、逻辑门电路 1.基本逻辑门电路

逻辑 表达式

与门 F=A·B

逻辑 符号

真值表

逻辑关 系文字 表达

有0出0 全1出1

或门 F=A+B

有1出1 全0出0

非门 F= A

2.测量电阻步骤 1)机械调零:将电表水平放置,进行机械调零; 2)挡位选择:估测大致阻值,选择合适挡位(欧姆调零)进行测量; 3)挡位调整:合理调节挡位(每次换挡需欧姆调零),使指针尽可能靠近刻 度盘的中央位置; 4)连接待测元器件:将待测元器件与电路断开,与电表连接(采用电表电 源);红表笔为内置电源负极,黑表笔为内置电源正极; 5)读数:示数×挡位倍率(不估读); 6)整理仪器:使用完毕后拔出表笔,并将开关旋至OFF挡或交流电压最高 挡。

vlsi数字集成电路一般设计流程

vlsi数字集成电路一般设计流程VLSI数字集成电路一般设计流程数字集成电路(VLSI)是现代电子技术领域的重要组成部分,广泛应用于计算机、通信、消费电子等领域。

VLSI数字集成电路的设计流程是一个系统性的过程,涉及到从需求分析到电路设计、验证、布局布线等多个环节。

本文将介绍VLSI数字集成电路的一般设计流程。

一、需求分析需求分析是VLSI数字集成电路设计的第一步,主要目的是明确设计要求和功能需求。

在需求分析阶段,设计团队与客户或项目经理进行沟通,了解项目的背景、功能要求、性能指标等。

同时,还需要考虑电路的功耗、面积、可靠性等因素,以确定设计的整体目标。

二、框架设计在框架设计阶段,设计团队根据需求分析的结果,确定整个电路的结构和功能模块。

框架设计需要考虑各个模块之间的连接方式、数据传输方式、时序要求等。

同时,还需要确定使用的逻辑门、存储器、寄存器等基本元件,并进行初步的电路图设计。

三、逻辑设计逻辑设计是VLSI数字集成电路设计的核心环节,主要目的是将框架设计的功能模块转化为逻辑电路。

在逻辑设计阶段,设计团队使用硬件描述语言(如Verilog、VHDL)进行电路的建模和描述,利用逻辑门、时序电路等元件进行电路的逻辑实现。

四、验证验证是确保电路设计正确性的重要环节。

在验证阶段,设计团队需要使用仿真工具对电路进行功能仿真,并设计测试用例进行验证。

通过仿真和测试,可以发现电路设计中的错误或潜在问题,并对其进行修复和优化。

五、布局布线布局布线是将逻辑电路转化为物理电路的过程。

在布局布线阶段,设计团队将逻辑电路转化为实际的布局图,确定各个元件的位置和相互之间的连线关系。

同时,还需要考虑电路的面积、功耗、信号延迟等因素,并进行布线优化。

六、物理验证物理验证是检验布局布线结果的环节。

在物理验证阶段,设计团队对布局布线后的电路进行电气规则检查(DRC)和电磁规则检查(ERC),以确保电路的物理完整性和可靠性。

根据验证结果,可以对布局布线进行调整和优化。

数字电路实验报告-实验一[总结]

![数字电路实验报告-实验一[总结]](https://img.taocdn.com/s3/m/da4b06729a6648d7c1c708a1284ac850ad0204e0.png)

实验一数字电路实验基础一、实验目的⑴掌握实验设备的使用和操作⑵掌握数字电路实验的一般程序⑶了解数字集成电路的基本知识二、预习要求复习数字集成电路相关知识及与非门、或非门相关知识三、实验器材⑴直流稳压电源、数字逻辑电路实验箱、万用表⑵74LS00、74LS02、74LS48四、实验内容和步骤1、实验数字集成电路的分类及特点目前,常用的中、小规模数字集成电路主要有两类。

一类是双极型的,另一类是单极型的。

各类当中又有许多不同的产品系列。

⑴双极型双极型数字集成电路以TTL电路为主,品种丰富,一般以74(民用)和54(军用)为前缀,是数字集成电路的参考标准。

其中包含的系列主要有:▪标准系列——主要产品,速度和功耗处于中等水平▪LS系列——主要产品,功耗比标准系列低▪S系列——高速型TTL、功耗大、品种少▪ALS系列——快速、低功耗、品种少▪AS系列——S系列的改进型⑵单极型单极型数字集成电路以CMOS电路为主,主要有4000/4500系列、40H系列、HC系列和HCT系列。

其显著的特点之一是静态功耗非常低,其它方面的表现也相当突出,但速度不如TTL集成电路快。

TTL产品和CMOS产品的应用都很广泛,具体产品的性能指标可以查阅TTL、CMOS集成电路各自的产品数据手册。

在本实验课程中,我们主要选用TTL数字集成电路来进行实验。

2、TTL集成电路使用注意事项⑴外形及引脚TTL集成电路的外形封装与引脚分配多种多样,如附录中所示的芯片封装形式为双列直插式(DIP)。

芯片外形封装上有一处豁口标志,在辨认引脚分配时,芯片正面(有芯片型号的一面)面对自己,将此豁口标志朝向左手侧,则芯片下方左起的第一个引脚为芯片的1号引脚,其余引脚按序号沿芯片逆时针分布。

⑵电源每片集成电路芯片均需要供电方能正常使用其逻辑功能,供电电源为+5V单电源。

电源正端(+5V)接芯片的VCC引脚,电源负端(0V)接芯片的GND引脚,两者不允许接反,否则会损坏集成电路芯片。

清华大学《数字集成电路设计》周润德 第1章(课件)绪论

2004-9-15

清华大学微电子所《数字大规模集成电路》 周润德

第1章第3页

评分规则(Grading Policy)

(1)作业: 20%

第 4 周起,每周一次,一周完成,上课时交,迟交无效

(2)期中考试:20%

100

P6 Pentium ® proc

10

8086 286

486

386

8085

1

8080

8008

4004

0.1 1971

1974

1978 1985 年

1992

最先进微处理器的功耗持续增长

2000

资料来源: Intel

2004-9-15

清华大学微电子所《数字大规模集成电路》 周润德

第 1 章 第 21 页

2004-9-15

清华大学微电子所《数字大规模集成电路》 周润德

第 1 章 第 17 页

微处理器单个芯片尺寸的增长趋势

100

单个芯片尺寸 (mm)

P6

10

486 Pentium ® proc 386

8080

286 8086

8085

8008

4004

资料来源: Intel

1 1970

1980

1990 年

每1.96年翻一倍!

Pentium® III

Pentium® II

Pentium® Pro

Pentium® i486

i386

80286

10

1 1975

8086

1980

1985 1990

1995

2000

资料来源: Intel

数字集成电路设计 第3章 器件1

四、VT 的影响因素 1、当考虑衬底接负偏压时 Vs=|-2VF+VSB|= |2VF+VBS|

因为当衬底接负偏压时,会使得发生强 反型时的Vs增加,这要求要有更大的VT 才能满足这一效果。所以,衬底接的负 偏压越多,VT 增加

0.9 0.85 0.8 0.75 0.7 0.65 0.6 0.55 0.5 0.45 0.4 -2.5 -2 -1.5 VBS (V) -1 -0.5 0

Qi ( x) Cox [VGS V ( x) VT ]

根据电流是载流子的漂移速度和所存在电荷的积,可得:

I D n ( x)Qi ( x)W

又因为:

dV n un ( x) un dx

I D dx unCoxW (VGS V VT )dV

在沟道的全长L上积分得到晶体管的电压-电 流关系: ID = k’n W/L [(VGS – VT)VDS – VDS2/2] k’n = nCox = nox/tox 当VDS的值较小时,公式中的平方项可以忽 略,于是我们可以看到ID和VDS 之间的线性 关系,此时工作的区域称为电阻区或线性 区,表现出来的特点是它在源区和漏区之 间表现为一条连续的导电沟道。

Transistor in Linear Mode

Assuming VGS > VT

VGS

S

G D n+

- V(x) +

VDS

ID

n+

x

B The current is a linear function of both VGS and VDS

在沿沟道的X处,电压为V(x),在X点处栅至沟 道的电压等于VGS –V(x),并假设这一电压沿整 个沟道都超过VT ,那么在X处所感应出的每单 位面积的沟道电荷可表示为:

(完整word版)数电1-10章自测题及答案(2)

第一章绪论一、填空题1、根据集成度的不同,数字集成电路分位以下四类:小规模集成电路、中规模集成电路、大规模集成电路、超大规模集成电路。

2、二进制数是以2为基数的计数体制,十六体制数是以16为基数的计数体制。

3、二进制数只有0和1两个数码,其计数的基数是2,加法运算的进位规则为逢二进一。

4、十进制数转换为二进制数的方法是:整数部分用除2取余法,小数部分用乘2取整法,十进制数23。

75对应的二进制数为10111.11。

5、二进制数转换为十进制数的方法是各位加权系数之和,二进制数10110011对应的十进制数为179。

6、用8421BCD码表示十进制时,则每位十进制数可用四位二进制代码表示,其位权值从高位到低位依次为8、4、2、1。

7、十进制数25的二进制数是11001,其对应的8421BCD码是00100101。

8、负数补码和反码的关系式是:补码=反码+1。

9、二进制数+1100101的原码为01100101,反码为01100101,补码为01100101。

-1100101的原码为11100101,反码为10011010,补码为10011011。

10、负数-35的二进制数是—100011,反码是1011100,补码是1011101。

二、判断题1、二进制数有0~9是个数码,进位关系为逢十进一。

()2、格雷码为无权码,8421BCD码为有权码。

(√)3、一个n位的二进制数,最高位的权值是2^n+1. (√)4、十进制数证书转换为二进制数的方法是采用“除2取余法”. (√)5、二进制数转换为十进制数的方法是各位加权系之和。

(√)6、对于二进制数负数,补码和反码相同。

()7、有时也将模拟电路称为逻辑电路。

()8、对于二进制数正数,原码、反码和补码都相同. (√)9、十进制数45的8421BCD码是101101。

()10、余3BCD码是用3位二进制数表示一位十进制数. ( )三、选择题1、在二进制技术系统中,每个变量的取值为(A )A、0和1B、0~7C、0~10D、0~F2、二进制权值为(B )A、10的幂B、2的幂C、8的幂D、16的幂3、连续变化的量称为( B )A、数字量B、模拟量C、二进制量D、16进制量4、十进制数386的8421BCD码为(B )A、0011 0111 0110B、0011 1000 0110C、1000 1000 0110D、0100 1000 01105、在下列数中,不是余3BCD码的是( C )A、1011B、0111C、0010D、10016、十进制数的权值为(D )A、2的幂B、8的幂C、16的幂D、10的幂7、负二进制数的补码等于(D )A、原码B、反码C、原码加1D、反码加18、算术运算的基础是(A )A、加法运算B、减法运算C、乘法运算D、除法运算9、二进制数-1011的补码是(D )A、00100B、00101C、10100D、1010110、二进制数最高有效位(MSB)的含义是( A )A 、最大权值B 、最小权值C 、主要有效位D 、中间权值第二章 逻辑代数基础一、填空题1、逻辑代数中三种最基本的逻辑运算是与运算、或运算、非运算。

数字集成电路——电路、系统与设计

IC,这些微小但强大的芯片,是我们电子设备的无名英雄,从我们口袋里的光滑智能无线终端,到我们桌子上的强大的截肢者,甚至我们车上最先进的汽车系统。

当它到数字集成电路时,全部是创建顶尖的系统,来传递心跳的性能,而吸电就像一个花哨的鸡尾酒,永远,永远,投球在可靠性上。

这些电路是数据处理、信号处理和控制系统的摇滚巨星,使得我们技术精湛的世界开始运转。

但是,在所有的滑翔和魅力背后,工作上有大量的脑力。

设计数字集成电路就像开始一个令人惊叹的冒险,任务包括设定舞台有规格,通过模型化将人物带入生命,在模拟中通过脚步化,通过合成来伤害它们的存在,最后通过彻底的验证确保一切的平稳航行。

就像是数字交响乐的策划者,进行电路,系统和设计技术的和谐混合,在区块上创建最高效和可靠的集成电路。

这是一个疯狂的旅程,但有人必须做到这一点!设计数字集成电路需要使用不同的工具和方法来开发和改进数字系统。

首先要弄清楚数字系统需要做什么以及它需要多好的表现我们用维利洛格和VHDL等特殊语言创建模型并测试数字系统。

接下来,我们把模型变成逻辑门列表,我们努力确保设计符合所有要求。

我们用半导体制造来制造实际的电路。

这涉及到根据设计创建布局和建造电路。

数字集成电路领域是一个不断发展和动态的研究领域,其特点是设计方法、技术和应用方面不断取得进展。

随着数字系统继续在各种电子装置和系统中发挥重要作用,对数字集成电路设计专业人才的需求日益增加。

对这一领域感兴趣的个人必须在数字电路、系统和设计原则方面奠定坚实的基础,并随时了解数字集成电路技术的最新发展。

只要具备必要的知识和技能,就能够有助于创造创新的数字集成电路,推动技术进步,提高电子系统的性能。

数字集成电路可测性设计(DFT)讲义第1讲

Good chip appears to be faulty (fails test)

EE141 VLSI Test Principles and Architectures

11

Introduction

Electronic System Manufacturing

A

system consists of

Moore’s Law: scale of ICs doubles every 18 months

Growing size and complexity poses many and new testing challenges

VLSI M LSI

1960s 1970s 1980s 1990s 2000s

EE141 VLSI Test Principles and Architectures

5

Introduction

Importance of Testing

Moore’s Law results from decreasing feature size (dimensions)

from 10s of µm to 10s of nm for transistors and interconnecting wires

8

Introduction

Testing During VLSI Development

Design verification targets design errors

Corrections made prior to fabrication

Design Specification Design Fabrication Packaging Quality Assurance Design Verification Wafer Test Package Test Final Testing

(参考资料)数字集成电路课后习题1-4章作业解析

QB0 =−3×10−7 C / cm××1100−−76

=−0.188 V

= QOX COX

6= ×1011.16××11.60−×610−19

0.06 V

VT0 =−0.99 − (−0.88) − (−0.188) − 0.060 =+0.018 V

计算 PMOS 器件的阈值电压:

VGS −VT + EC L

(1.2 − 0.4)(6)(0.2) 1.2 − = 0.4 + (6)(0.2)

0.48V

VDS = 0.2V

∴ VDS < VDSAT

d. 饱和

VGS>VT,VD > VG 肯定工作在饱和区。对于长沟道器件,如果满足这个关系 就工作在饱和区。而发生速度饱和的短沟道器件的 VDSAT 比长沟道器件的要 小,如果电压偏置能使长沟道器件饱和,那么肯定能使速度饱和的短沟道器件 饱和。

VGS = VG −VS = 1.2 −1.1 = 0.1V V=T V= T 0 0.4V ∴ VGS < VT

c. 线性

VGS = VG −VS = 1.2 − 0 = 1.2V V=T V= T 0 0.4V ∴ VGS > VT

不在饱和区的判断依据:

= VDSAT

(= VGS −VT ) EC L

(N 型)

对于(b)中的 PMOS 器件:

NI

= − QI q

= − (1.6

×10−6 )(1.24 1.6 ×10−19

−

0.4)

= 8.4 ×1012 ions / cm2

(P 型)

d) 从上面的计算可以看到,NMOS 用 N 型多晶硅栅和 PMOS 用 P 型多晶硅栅算得的阈值 电压比较小,在沟道区使用与衬底相同的离子掺杂即可调整到期望值(NMOS:P 型注 入;PMOS:N 型注入)。如果我们在 MOS 管的栅极中采用跟衬底相同类型的离子注 入,得到的阈值电压很大,偏离期望值很多,调整起来比较困难。另外,源极和漏极 的制作过程采用自对准工艺,如果栅极的注入类型和源漏一致,一步即可完成离子注 入,简化了器件制作的工艺流程。

为什么计算机只认0和1?

为什么计算机只认0和1?

我们⽬前主要使⽤的计算机都是⼤规模集成电路机,是采⽤⼤规模和超⼤规模的集成电路作为逻辑元件的。

集成电路,按其功能、结构的不同,可以分为模拟集成电路、数字集成电路和数/模混合集成电路三⼤类。

⽽我们的计算机主要是采⽤数字集成电路搭建的。

逻辑门是数字逻辑电路的基本单元。

常见的逻辑门包括“与”门,“或”门,“⾮”门,“异或”等等。

通过逻辑门可以组合使⽤实现更为复杂的逻辑运算和数值运算。

逻辑门可以通过控制⾼、低电平,从⽽实现逻辑运算。

电源电压⼤⼩的波动对其没有影响,温度和⼯艺偏差对其⼯作的可靠性影响也⽐模拟电路⼩得多。

所以相对稳定。

因为数字计算机是由逻辑门组成,⽽逻辑电路最基础的状态就是两个——开和关。

所以,数字电路是以⼆进制逻辑代数为数学基础。

⼆进制的基本运算规则简单,运算操作⽅便,这样⼀来有利于简化计算机内部结构,提⾼运算速度。

⽽且在逻辑代数⽅⾯,⼆进制只有0和1两个数码,正好与逻辑代数中的“真”和“假”相吻合。

数字集成电路设计入门(从HDL到版图)1-5

•

RTL级/功能级

– – 用功能块内部或功能块之间的数据流和控制信号描述系统 基于一个已定义的时钟的周期来定义系统模型

•

结构级/门级

– – 用基本单元(primitive)或低层元件(component)的连接来描述系 统以得到更高的精确性,特别是时序方面。 在综合时用特定工艺和低层元件将RTL描述映射到门级网表

抽象级(Levels of Abstraction)

• 设计工程师在不同的设计阶段采用不同的抽象级

– 首先在行为级描述各功能块,以降低描述难度,提高仿真速度。 – 在综合前将各功能模块进行RTL级描述。 – 用于综合的库中的大多数单元采用结构级描述。在本教程中的结 构级描述部分将对结构级(门级)描述进行更详细的说明。

Cadence Verilog仿真器

• Verilog-XL和NC Verilog仿真器都是基于事件算法的 仿真器。仿真器读入Verilog HDL描述并进行仿真以 反映实际硬件的行为。 • Verilog-XL和NC Verilog仿真器遵循IEEE 1364 Verilog规范制定的基于事件的调度语义 • 仿真器可用于

• 实验,24学时

– Verilog (5) – Synthesis (2) – Place &Route (1)

• 考试,3学时

参考书目

• • • • Cadence Verilog Language and Simulation Verilog-XL Simulation with Synthesis Envisia Ambit Synthesis 《硬件描述语言Verilog》 清华大学出版社,Thomas &Moorby,刘明业等译,2001.8

• • • •

苏教版(2019) 选择性必修1 课时4 数字集成电路 练习(含答案)

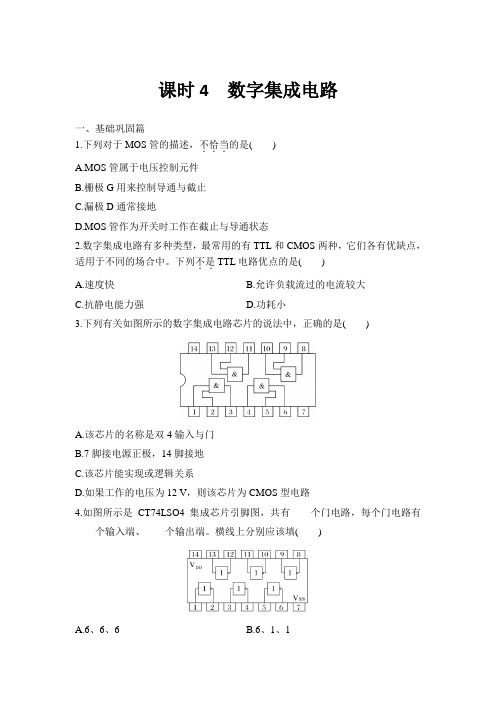

课时4数字集成电路一、基础巩固篇1.下列对于MOS管的描述,不恰当...的是()A.MOS管属于电压控制元件B.栅极G用来控制导通与截止C.漏极D通常接地D.MOS管作为开关时工作在截止与导通状态2.数字集成电路有多种类型,最常用的有TTL和CMOS两种,它们各有优缺点,适用于不同的场合中。

下列不是..TTL电路优点的是()A.速度快B.允许负载流过的电流较大C.抗静电能力强D.功耗小3.下列有关如图所示的数字集成电路芯片的说法中,正确的是()A.该芯片的名称是双4输入与门B.7脚接电源正极,14脚接地C.该芯片能实现或逻辑关系D.如果工作的电压为12 V,则该芯片为CMOS型电路4.如图所示是CT74LSO4集成芯片引脚图,共有____个门电路,每个门电路有____个输入端、____个输出端。

横线上分别应该填()A.6、6、6B.6、1、1C.1、6、6D.1、1、15.晶体管电路如图所示,请完成以下任务:(1)三极管型号是________(在①NPN型;②PNP型中选择合适的选项,将序号填写在“______”处);(2)将开关断开,LED1和LED2分别为________和________(在①熄灭;②点亮中选择合适的选项,将序号填写在“________”处);将开关闭合,LED1和LED2分别为______和______(在①熄灭;②点亮中选择合适的选项,将序号填写在“______”处);(3)开关闭合时,三极管基极和发射极之间的电压为__________ V,三极管处于__________状态(在①饱和;②截止中选择合适的选项,将序号填写在“________”处);集电极和发射极之间________(在①导通;②截止中选择合适的选项,将序号填写在“______”处),LED2被________(在①短路;②开路中选择合适的选项,将序号填写在“______”处)。

二、素养提升篇1.如图所示是数字集成电路CC4001引脚排列及功能图,在实际使用中,下列说法中不正确...的是()A.该集成电路是TTL类型B.如果电路中只需用一个或非门,可任选其中一组C.把其中一组或非门的两个输入端并接后,可以实现非门的功能D.把该集成块中的或非门加以组合,可以实现与门功能2.如图所示的集成逻辑门电路引脚图(V CC=5 V),关于该电路描述错误..的是()A.该集成电路属于TTL类型B.该集成电路的名称为四2输入与非门C.该集成电路由普通晶体三极管构成D.该集成电路的四个与非门作用各不相同3.如图a所示为小明设计的湿度警示实验电路,R S为负系数湿敏电阻,电路中所用芯片为四2输入与非门74LS00。

数字集成电路5章[1]习题1

![数字集成电路5章[1]习题1](https://img.taocdn.com/s3/m/1d84a8ea710abb68a98271fe910ef12d2af9a9cc.png)

说明:[难度等级(E容易M中等C难),需要的设计工具,与之相关的章节]第5章CMOS反相器4. [E, None, 3.3.3]对于图5.3中的输出负载为3pF的反相器:a. 计算t plh,t phl和t pb. 上升延时和下降延时是否相等?为什么?c. 计算静态和动态功耗,假设门的时钟频率尽可能的快。

图5.3 电阻负载反相器7. 考虑图5.5中的电路。

器件M1是一个标准的NMOS器件。

器件M2除了阈值电压为负并且其值为-0.4V之外,和M1有共同的特性。

假设耗尽型器件M2的所有电流公式和不等式(来决定工作模式)与规范的NMOS器件相同。

并假设输入IN有0V到2.5V的摆幅。

图5.5 一个耗尽型负载的NMOS反相器a.器件M2的栅极和源极相连。

如果V IN =0V,那么输出电压是多少?在稳态,对于这个输入,器件M2的工作模式是什么?b.计算V IN =2.5V时的输出电压。

为简化计算,你可以假设V OUT很小。

在稳态,对于这个输入,器件M2的工作模式是什么?c.假设Pr(LN=0)=0.3,这个电路的静态功耗是多少?8. [M, None, 3.3.3]一个NMOS晶体管用来向一个大电容充电,如图5.6所示:a. 确定这个电路的t pLH,假设输入节点有一个0到2.5V的理想阶跃信号。

b. 假设一个5kΩ的电阻R S用来对电容放电至地,确定t pHL的值。

c. 确定在对电容充电期间从电源得到多少能量。

其中多少能量在M1中被消耗?在放电期间,多少能量在下拉电阻上消耗?当R S减小至1kΩ时又是多少?d. NMOS晶体管用一个PMOS器件代替,k p和原先NMOS的k n相等。

替换后的结构是否比以前快?解释为什么。

图5.6 注明W/L比的电路图12. 考虑图5.9的低摆幅驱动:a. 输出节点(V out)的电压摆幅是多少?假设γ =0。

b. 输入端有一个从0V 到2.5V的翻转,估算(i)来自于电源的能量和(ii)能量损耗。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

10 1

0.1 0.01 0.001

P6 486 Pentium® proc

386 286

8085 8086 8080

8008 4004

1970

1980

1990 Year

2000

2010

每代领先的微处理器的晶体管数目每2年增加一倍

摩尔定律——芯片尺寸

100

Die size (mm)

10

486 PenPti6um ® proc 386

能量的传递和耗散将变得不可能

功率密度

Power Density (W/cm2)

10000 1000 100

火箭喷嘴温度 核反应温度

10 4004 8086 电炉温度

P6

8008 8080

8085286

386

Pentium® proc 486

1

1970

1980

1990 Year

14 13

April 19, 1965.

12 11

Gordon Moore

10

9

单片集成晶体

8 7

管数目每18或

6

24个月增长一

5 4

倍

3 2

半导体工艺的

1

效力每18个月

0

增长一倍

复杂度的演变——存储器

晶体管数目

K 1,000,000

十亿颗晶体管!

100,000 10,000 1,000 100

第一台电气计 算机(1946) ENIAC(电子 数字积分计算 机)

18000个真空 管

问题:可靠性, 功耗,成本

1.2 集成电路产业的简要历史

第一个晶 体管

1947,贝 尔实验 室

1.2 集成电路产业的简要历史

第一块集成电路 ECL(射极耦合逻 辑) 3输入逻辑门 Motorola,1966年

高速:Intel 4004/8080

功耗:NMOS让位于CMOS

1.2 集成电路产业的简要历史

CMOS

1970年:工艺进步导致好的性价比 集成规模增大功耗瓶颈

其它工艺

Bi-CMOS

高速存储器和门阵列

SOI

面积/功耗/速度优,成本高

GaAs/SiGe/超导

速度优

摩尔定律(Moore’s Law)

8080

286

8086 8085

每年约增加7%

8008 4004

每10年约增加2倍

1 1970

1980

1990 Year

2000

2010

要符合摩尔定律,芯片尺寸每年需增长14%

摩尔定律——工作频率

Frequency (Mhz)

10000 1000

每2年增加1倍

100 10 8085

P6

Pentium ® proc 486 8086 286 386

1

8080

8008 0.1 4004

1970

1980

1990 Year

2000

2010

每代领先的微处理器工作频率每2年翻一番

摩尔定律——功耗

Power (Watts)

100

P6 Pentium ® proc

10

8086 286

486

386

8085

1

8008 8080

4004

0.1 1971

1974

LOG2 OF THE NUMBER OF COMPONENTS PER INTEGRATED FUNCTION

1959 1960 1961 1962 1963 1964 1965 1966 1967 1968 1969 1970 1971 1972 1973 1974 1975

16 15

Electronics,

1960年代是双极型 电路时代

1.2 集成电路产业的简要历史

双极型

1947年:晶体管(Bardeen/Bell Lab) 1949年:双极型晶体管(Schockley) 1956年:数字逻辑门(Harris) 1962 年 : TTL ( 晶 体 管 - 晶 体 管 逻 辑 ) 系 列

(Beeson/Fairchild) 1974年:ECL(射极耦合逻辑)高速系列(Masaki) 1972年:I2L(集成注入逻辑)低功耗高密度系列(Hart) 功耗问题:让位于MOS(metal-oxide-semiconductor)

门级设计

通过综合工具实现

版图设计

通过版图设计工具实现,通常以GDS-Ⅱ格式表示

制造

包括流片、封装、测试等

1.2 集成电路产业的简要历史

第一台机械计算机 1832年,Babbage的 差动引擎 (Difference Engine Ⅰ)工作部件

问题:设计复杂,成 本高

1.2 集成电路产业的简要历史

功能增加灵活 规模/速度随工艺按比例下降而优化 对工艺/电压/温度不敏感

1.1 绪论

电路设计应考虑:

可靠性 速度 功耗 面积 成本

1.1 绪论

数字系统设计

规格说明书(spec)

包含整个系统所需要的特性,定义输入、输出、环境条件、 操作速度等

寄存器传输级(RTL)设计

用Verilog或VHDL实现

Pentium® III

Pentium® II Pentium® Pro Pentium® i486 i386

80286

10

1 1975

8086

1980

1985 1990

1995 2000

Source: Intel

2005 2010

Projected

摩尔定律——微处理器

1000

100

Transistors (MT)

第一章 深亚微米数字集成电路设计

1.1 绪论 1.2 集成电路产业的简要历史 1.3 数字逻辑门设计的回顾 1.4 数字集成电路设计 1.5 数字电路的计算机辅助设计 1.6 面临的挑战

1.1 绪论

集成电路的应用

高性能计算 仪表和工业控制 通信 消费电子

数字电路与模拟电路相比的优势

1.2 集成电路产业的简要历史

MOS

1925年:IGFET绝缘栅场效应晶体管(Lilienfeld)

缺乏对材料的了解和栅稳定性问题的认识

1963年:CMOS逻辑门(Wanlass)

工艺复杂性

1970年:PMOS计算器 1970年:NMOS存储器

高密度:4Kbit

1972/74年:NMOS微处理器

1978 1985 Year

1992

2000

每代领先的微处理器功耗持续增长

功耗将成为主要问题

Power (Watts)

100000 10000

18KW 5KW

1.5KW

1000

500W

P0885086286386486

8080

1

8008 4004

0.1 1971 1974 1978 1985 1992 2000 2004 2008 Year