基于SOC的系统设计

SOC系统的结构设计

网络通信接口设计能够实现数据的网络传输 ,具有传输距离远、可连接多个设备等优点 。

详细描述

网络通信接口设计通常采用TCP/IP等协议, 通过互联网或局域网实现数据的远程传输。 在SOC系统中,网络通信接口设计可以方便 地实现设备之间的数据共享和远程控制,提

高系统的可扩展性和灵活性。

无线通信接口设计

电源与散热设计

总结词

电源与散热设计是保障SOC系统稳定运行的重要环节。

详细描述

电源设计需要考虑电压、电流、功率等因素,散热设计需要考虑散热方式、散热效率等因素。良好的电源与散热 设计能够降低系统功耗和减少故障率。

03

软件结构设计

操作系统选择与定制

操作系统选择

根据SOC系统需求,选择合适的操作系 统,如Linux、Android等。

能。

汽车电子

在汽车电子领域,SOC系统可以 用于实现车载信息娱乐系统、安

全控制系统等功能。

SOC系统的基本构成

处理器

01

SOC系统中的微处理器是系统的核心,负责执 行指令和处理数据。

存储器

02

存储器用于存储程序代码和数据,包括只读存 储器(ROM)、随机存取存储器(RAM)等。

输入输出接口

03

输入输出接口用于实现芯片与其他设备或系统 的通信和交互。

总结词

详细描述

无线通信接口设计能够实现数据的无线传输, 具有无需布线、移动方便等优点。

无线通信接口设计通常采用WiFi、蓝牙、 ZigBee等无线协议,通过无线信号实现数 据的传输。在SOC系统中,无线通信接口设 计可以方便地实现设备的无线连接和控制, 提高系统的便捷性和移动性。

05

安全防护设计

基于SoC的红外双波段图像融合系统的设计

s i b e f re e d n h o b e wa e b n fa e em a ma i g s se wa e i n d Ba i d s n u t l o mb d i g t e d u l - v a d i r r d t r l a n h i g n y tm s d sg e . sc e i g

中图分类 号 :T 1.3 N9 1 7 文献 标识码 :A 文 章编 号 :10—8 12 1)807—4 0 189 (0 00 —4 90

A e i n o fI Dua nd m a eFuso yse s d o o D sg fo R l Ba sI g i n S t m Ba e n S C

接 收 到 的 中波 和 长 波 图像 数 据 存 放 在 S AM1 和 R

S AM2 中 ,非均 匀校 正模 块从 S AM1及 S M2 R R A R

景细 节较 为模糊 ;长波 红外 图像 目标较 为模 糊 ,背 景 信息较 为 丰富L ,本 文 设计 的系 统针对 中波红 外与 长 2 J

波红外 图像 ,综 合利 用两 个波 段 图像 的优 势信 息 ,达 到对 目标及 背景 的更 为全面 的描述 。 图像 融 合 技 术应 用 的 障碍 之 一 是 融合 的速 度 问

ofs se p n i l n a o rsoff nci n we ei to uc d y t m r c p ea d v r uspa t i i u to r n r d e . Ke r : f so y t m , So , d u ewa nd R ma e y wo ds u i n s se C o bl veba sI i g

【优秀毕业论文】基于soc系统的12位saradc的设计

上海交通大学硕士学位论文基于S O C系统的12位SARADC 的设计DESIGN OF A 12 BIT SUCCESSIVE APPROXIMATION REGISTER ADC IN SOC SYSTEM硕士姓名:沈奇臻专业:电路与系统学号: 1060349010指导教师:戎蒙恬上海交通大学二零零八年十二月DESIGN OF A 12 BIT SUCCESSIVE APPROXIMATION REGISTER ADC IN SOC SYSTEMByShen QizhenADVISOR: Prof. Rong MengtianA THESIS SUBMITTED TOSHANGHAI JIAO TONG UNIVERSITYIN PARTIAL FULFILLMENT OF THE REQUIREMENTSFOR THE DEGREEOF MASTER OF SCIENCEDepartment of Electrical Engineering ofShanghai Jiao Tong UniverisityDecember 2008II基于S O C系统的12位SARADC 的设计摘 要在现在的各种应用SoC系统中,由于系统的高性能、低功耗、低成本要求,一定会把数模转换器(ADC)模块作为一个必不可少的组成部分和其他的模拟模块以及数字模块一起集成于一块芯片上,这已经是种必然的趋势。

正是由于这个原因,一种能够与数字工艺兼容的ADC的设计就变得很必要。

SARADC是一种常见的ADC的结构,由于其本身的小尺寸低功耗的特点,非常适合应用于SoC系统。

本文设计的就是这样一个应用于SoC系统的,能够面向触摸屏应用的ADC模块。

它基于TSMC 0.18um 的1P5M工艺,总共包括了模拟电路中的比较器电路、DAC电路、触摸屏驱动电路,输入通道选择电路以及数字电路的移位逻辑控制电路和时钟频率转换电路。

针对高速低功耗抖动要求,本文给出一种电流按比例缩放结构的DAC结构,并采用温度码和二进制码的分段组合,在明显提高DAC的精度,降低电路的失配和毛刺现象的同时减小芯片的面积和功耗。

基于 SoC的现代电子系统设计课程创新研究

( De p a r t me n t o f Au t o ma t i o n ,Ts i n g h u a Un i v e r s i t y, Be i j i n g 1 0 0 0 8 4,Ch i n a )

关 键 词 :S o C;电子 系 统 设 计 ; 课 程 中 图分 类号 : G 6 4 2 . 0 文 献 标 志 码 :A 文 章 编 号 :1 0 0 2 — 4 9 5 6 ( 2 0 1 4 ) 1 — 0 1 6 6 — 0 3

Re s e a r c h o n i n n o v a t i o n o f Mo d e r n E l e c t r o n i c S y s t e m D e s i g n c o u r s e b a s e d o n S o C

Vo 1 . 3 1 No . 1 J a l 1 . 2 0 1 4

基于 S o C的现 代 电子系统设计课程创新研究

叶 朝 辉 ,周 永 明 ,林 博 ,张 燕

( 清 华 大学 自动 化 系 ,北 京 1 0 0 0 8 4 )

摘

要: 随着 S o C( S y s t e m o n C h i p ) 应用越来越广泛 , 现 代 电子 系 统 大 多 以 S o C 为基 础 进 行 设 计 。 首 先 调 研

目前 的 S o C电子系统设计课程 , 在 此 基础 上 介 绍 了 内 容 上 和 教 学 模 式 上 具 有 一 定 创 新 的 现 代 电 子 系 统 设 计 相关课程 , 并 详 细 介 绍 了课 程 的教 学 指 导思 想 、 教 学 内容 和 教 学 模 式 及 课 程 开 设 的 效 果 。

基于SoC的非对称数字系统算法设计与实现

基于SoC的非对称数字系统算法设计与实现姜智;肖昊【期刊名称】《合肥工业大学学报(自然科学版)》【年(卷),期】2024(47)5【摘要】文章提出一种在片上系统(System on Chip,SoC)实现高吞吐率的有限状态熵编码(finite state entropy,FSE)算法。

通过压缩率、速度、资源消耗、功耗4个方面对所提出的编码器和解码器与典型的硬件哈夫曼编码(Huffman coding,HC)进行性能比较,结果表明,所提出的硬件FSE编码器和解码器具有显著优势。

硬件FSE(hFSE)架构实现在SoC的处理系统和可编程逻辑块(programmable logic,PL)上,通过高级可扩展接口(Advanced eXtensible Interface 4,AXI4)总线连接SoC 的处理系统和可编程逻辑块。

算法测试显示,FSE算法在非均匀数据分布和大数据量情况下,具有更好的压缩率。

该文设计的编码器和解码器已在可编程逻辑块上实现,其中包括1个可配置的缓冲模块,将比特流作为单字节或双字节配置输出到8 bit 位宽4096深度或16 bit位宽2048深度的块随机访问存储器(block random access memory,BRAM)中。

所提出的FSE硬件架构为实时压缩应用提供了高吞吐率、低功耗和低资源消耗的硬件实现。

【总页数】6页(P655-659)【作者】姜智;肖昊【作者单位】合肥工业大学微电子学院【正文语种】中文【中图分类】TN762;TN764【相关文献】1.基于IEEE 1500的数字SOC测试系统的设计与实现2.基于片上系统SoC的孤立词语音识别算法设计3.OMA DRM 2数字版权保护终端系统的SoC设计方案及其VLSI实现4.无线通信系统数字变频算法设计与实现因版权原因,仅展示原文概要,查看原文内容请购买。

一种基于soc的处理器最小系统设计方法

SOC 芯片需要的时钟信号为 PSCLK遥 PSCLK 为系 统 时 钟 输 入 袁 驱 动 PLL 单 元 袁 通 过 PLL 配 置 可 提 供 ARM 内核时钟和其他功能接口的时钟遥 PSCLK 输入范 围为 30~60MHz袁 设计中采用 50MHz 时钟输入作为系统 时钟遥 3.4 复位电路

DDR3 供 电 电 压 1.5 V 依75 mV袁 以 太 网 IO 电 压 1.8V依90mV遥

该 SOC 芯片要求各电源上电顺序依次为从小到大 上电袁 即 1.0V 先上电袁 然后依次是 1.5V尧 1.8V尧 3.3V袁 且下电顺序正好相反遥 设计采用 2 片双通道 DC/DC 实 现 1.0V尧 1.5V尧 1.8V尧 3.3V 电压转换袁 各通道均由 5V 转换袁 对各通道 DC/DC 的转换控制端配置不同的软启 动电容袁 以控制不同电压的上下电顺序满足 SOC 芯片 供电要求遥

1 概述 处理器最小系统是指某一类嵌入式计算机系统的公

共核心单元袁 该核心单元具备最基础的软硬件功能袁 并 且可以对外扩展出处理器的全部资源遥 开发设计某类嵌 入式计算机系统袁 首先要设计其最小系统遥 根据这一需 求袁 提供了一种基于 SOC 芯片构建的处理器最小系统 的设计方案袁 方案具有集成度高尧 处理能力强尧 功耗低 等优点遥 2 处理器最小系统架构

一种基于 SOC 的处理器最小系统设计方法

秦冲,朱耀国 (航空工业西安航空计算技术研究所,西安 710065)

基于SOC的嵌入式系统设计

基于SOC的嵌入式系统设计随着时代的发展和科技的进步,嵌入式系统被广泛应用到我们日常生活中的各个领域。

而基于SOC(System on Chip)的嵌入式系统设计已成为嵌入式系统设计中不可或缺的一部分。

本文将介绍基于SOC的嵌入式系统设计的基本概念、优势和应用场景。

一、基于SOC的嵌入式系统设计的基本概念SOC是指在一个微处理器芯片上集成了整个系统所需的各种硬件设备和软件系统的一种芯片。

它通常包括CPU、存储器、输入输出接口、计时器、中断控制器、外设控制器、DMA控制器等硬件模块,并预装有操作系统、中间件、应用程序等软件系统。

因此,SOC可以实现多种应用模式和应用场景,并能够在安全和高效的条件下实现复杂的计算和通信操作。

基于SOC的嵌入式系统设计是指将SOC应用到嵌入式系统设计中,以实现更高的集成度、更低的功耗和更高的运算性能。

基于SOC的嵌入式系统设计还能够缩短设计周期、降低开发成本和提高产品品质。

二、基于SOC的嵌入式系统设计的优势1.高度集成基于SOC的嵌入式系统设计能够将整个系统的各种硬件模块和软件系统集成在一个单一的芯片中,实现更高的集成度和更低的功耗。

这样不仅能够降低系统整体成本,还能够提高产品品质和稳定性。

2.灵活性和可编程性基于SOC的嵌入式系统设计还具有较高的灵活性和可编程性。

通过配置不同的硬件模块和软件系统,可以定制不同的应用场景和应用模式。

这样可以满足不同用户的需求,并为系统扩展提供了很大的空间。

3.低延时和高运算性能基于SOC的嵌入式系统设计具有低延时和高运算性能的特点。

由于整个系统集成在一个芯片中且硬件模块和软件系统高度匹配,因此整个系统可以最大化地发挥性能。

这样可以实现更稳定的通信和更高速的计算。

三、基于SOC的嵌入式系统设计的应用场景1.物联网在物联网领域,基于SOC的嵌入式系统设计可以应用于各种传感器、智能设备、控制器等场景。

通常,物联网设备需要具备低功耗、小体积、高可靠性和高度集成的特点。

SOC系统的设计与实现

SOC系统的设计与实现第一章引言SOC(System on Chip)是一种将多种类型的电子器件和部件集成到单个芯片上的设计方案。

SOC 的设计和实现可以实现系统的快速更新和迭代,并大幅降低系统成本。

本文将介绍 SOC 系统的设计和实现,包括系统级设计和物理级实现。

第二章 SOC 系统的设计2.1 需求分析SOC 系统设计首先需要进行需求分析,明确系统的需求和目标。

需求分析应该包括对系统功能、性能、功耗、可靠性、安全性等方面的考虑。

设计者需要从多个方面进行权衡,确保系统能够满足需求,并具备可扩展性和可维护性。

2.2 架构设计在需求分析的基础上,设计者需要确定 SOC 系统的架构。

架构设计应该考虑到系统功能模块的划分、模块之间的接口定义、系统总线设计等问题。

此外,架构设计还涉及到存储器系统、时钟和复位控制等问题。

2.3 IP 集成与接口设计SOC 系统的设计包含大量的 IP (Intellectual Property)集成。

设计者需要从多个 IP 提供商中选取适合项目需求的 IP,并对 IP进行集成和定制。

IP 集成也需要进行接口设计,确保不同 IP 之间的数据传输正确无误。

2.4 电源管理设计SOC 系统是一种低功耗、高性能的电子芯片,需要进行有效的电源管理。

设计者需要考虑电源管理单元的设计,以及电源开关、电源监控、电源序列控制等问题。

2.5 总线设计总线设计是 SOC 系统设计中比较重要的环节。

设计者需要选择适合项目需求的总线标准,并确定总线拓扑结构、总线速率和总线带宽等参数。

第三章 SOC 系统的实现3.1 物理实现流程SOC 系统的实现需要进行物理布局设计和物理验证。

物理实现流程包括 RTL(Register Transfer Level)到 gate-level 的综合、布局与布线等过程。

设计者需要遵循物理实现规范,确保芯片布局和布线符合设计要求。

3.2 时钟和时序分析时钟和时序分析是 SOC 系统实现中的一个重要环节。

基于ARM926EJ-S的SoC系统设计的开题报告

基于ARM926EJ-S的SoC系统设计的开题报告一、研究背景现代计算机在嵌入式系统中的应用越来越广泛,如智能手机、平板电脑、智能家居等等。

随着技术的不断发展,如何设计一款高性能、低功耗、低成本的SoC(System on Chip)系统成为一个关键的问题。

本项目基于ARM926EJ-S处理器设计一个完整的SoC系统,探索如何在保持低成本和低功耗的同时兼顾性能和可扩展性的问题。

二、研究内容1. ARM926EJ-S处理器的架构及特性分析:对ARM926EJ-S处理器进行详细的介绍,包括处理器的架构、指令集、中断处理、时钟控制等方面的特性分析。

2. SoC系统架构设计:根据设计需求,选择适当的外设,如LCD、网络通信接口、键盘、触摸屏等,同时完成外设驱动程序设计、系统初始化以及中断处理等功能。

3. 系统软件设计:在嵌入式系统中,软件系统的设计是关键的,必须充分考虑代码大小、性能和可移植性等方面的问题。

本项目将采用uC/OS-II操作系统来完成系统软件的设计,通过任务管理、中断处理和系统调度等功能,提高系统的可靠性和可移植性。

4. SoC系统代码实现:在进行上述架构设计和软件设计之后,将对实现代码进行编写和测试,采用Verilog语言进行模块设计,通过模块之间的联调来完成SoC系统的实现。

三、研究意义本项目的研究具有重要的应用价值和学术价值:1. 提升嵌入式系统的设计技术:本项目将从处理器核的架构设计到系统软件设计、模块设计等方面进行研究,为开发人员提供参考和思路,提升嵌入式系统的设计技术。

2. 探索SoC系统在实际应用中的问题和解决方法:在探索高性能、低功耗、低成本的SoC系统设计问题的同时,更加深入地理解SoC系统在实际应用中的问题和解决方法。

3. 科学研究的意义:本项目将对ARM926EJ-S处理器进行详细的研究和剖析,从而更好地探索现代处理器设计的原理和方法,对于计算机体系结构和计算机组成原理的研究具有重要的科学意义。

第五讲SOC系统的结构设计

第五讲SOC系统的结构设计

SOC系统是一种多核系统,它具有良好的计算性能,能够满足现代复

杂的应用和系统所需。

SOC系统的结构设计是一个复杂的过程,它具有灵

活性,可以满足多种应用场景的需要。

1、SOC系统的架构

总的来说,SOC系统的架构包括控制器、外设、存储器、连接器和

I/O接口。

控制器是SOC系统中的核心部件,主要由处理器、中央处理器、总线控制器、定时器/计数器、DMA控制器、中断控制器等组成。

外设与

控制器之间通过总线链接,主要由多个外设模块组成,包括视频处理器、

图像处理器、音频处理器等,用于处理多媒体数据。

存储器与控制器之间

的关系,存储器是存储系统中的重要部件,主要由RAM和ROM组成,它们

在控制器中负责数据的存储和访问。

连接器是SOC系统的重要部件,它在SOC系统中提供多核连接,主要包括多核和多芯的连接器。

最后,I/O接

口负责将SOC系统与外部系统连接,它可以是USB接口、I2C接口、PS/2

接口等。

2、SOC系统的设计

SOC系统的设计是一个复杂的过程,需要考虑多个因素,如系统的尺寸、能耗、功能、性能和成本等。

首先,SOC系统的处理器需要根据应用

的功能来确定,它的尺寸和功耗也会影响SOC系统的性能。

基于ARM_Cortex-M3的SoC系统设计_

核发出中断请求信号,包含最多240个中断请求,以及1个不可屏蔽中断。

NVIC是与CPU紧密耦合的,它还包含了若干个系统控制寄存器。

2.2.3 总线系统总线系统用于将Cortex-M3内部的各个功能部件连接在一起。

总线系统包括:①内部总线系统;②处理器核内部的数据通道;③AHB Lite接口单元。

2.2.4 调试子系统作为Cortex-M3处理器重要的一部分,调试子系统提供下面的功能。

①管理调试控制、程序断点、以及数据监控点。

②当产生调试事件时,它将处理器核设置为停止状态。

此时,可以在该点分析处理器的状态,如寄存器值和标志。

2.3 异常处理与中断向量表设计Cortex-M3在内核水平上搭载了一个异常响应系统,支持为数众多的系统异常和外部中断。

向量中断控制器(NVIC)以存储器映射的方式来访问,除了包含控制寄存器和中断处理的控制逻辑之外,NVIC还包含了MPU的控制寄存器、SysTick定时器以及调试控制。

2.4 地址译码器和多路复用器设计本系统基于AHB-Lite所构建的Cortex-M3 SoC系统设计包含了地址译码器和多路复用器。

在系统中,来自不同从设备的响应信号,包括:HRDATA、HREADY和HRESP连接到多路复用器的输入,根据地址译码器所生成的选择信号,多路复用器将选择的从设备响应信号送给主设备。

其中HRDATA[31:0]是来自多路复用器到主设备的读数据,由多路复用器指向主设备;HREADY是来自多路复用器到主设备的准备信号,由多路复用器指向主设备和从设备,当该位为高时,该信号表示到主设备和先前完成传输的所用从设备。

2.5 APB子系统该APB子系统的顶层是AHB-Lite总线接口,可以与内核的AHB总线进行连接。

子系统内部包括的外设有定时器、UART、双输入定时器、看门狗电路、AHB到APB的桥接器、异步中断信号等。

表2为APB系统IRQ分配表。

表2 APB系统IRQ分配IRQ Device0UART 0 receive interrupt1UART 0 transmit interrupt2UART 1 receive interrupt3UART 1 transmit interrupt4UART2 receive interrupt5UART 2 transmit interrupt8Timer 09Timer 110Dual-input timer11Not used12UART 0 overflow interrupt13UART1 overflow interrupt14UART 2 overflow interrupt15Not used in APB subway16-31Not used in APB subway a: Reserved for GPIO in AHBb: Reserved for DMA2.6 时钟和复位电路设计本系统片上SoC系统主要包含HCLK、PCLK、PCLKG等三个时钟,HCLK时钟主要用于内核的工作时钟以及驱动片内高性能总线上挂载的外设。

基于SoC单片机温度控制系统的设计

科 之 学 友

Fnfieme rd e au i cc tr e o nA s S

0 () 6 1国 ,8 q

基 于 S C单 片 机 温 度 控 制 系统 的设 计 o

于志 强

( 太原钢铁公 司 ,山西 太原 000 ) 30 3

较器 ,4 6 K字节 F A H存 储器 以及 与 8 5 LS 0 1兼容 的微控 制器 内 核。因此 , 以不用外接 AD及 DA转换芯片 , 可 / / 大大简化 电路 。 本系统的工作过程是 : 由热 电偶对温度进行 采样 , 其输 出热 电势经放 大器 使输 出为 0 24 ~ .V的电压信号 ,送 人 1 的 AD 2位 /

中图 分 类 号 :T 23 P 7

文 献 标 识 码 :A

文章 编 号 :10 — 162 0)8 00 — 2 0 0 8 3 ( 81— 19 0 0

在工业控制系统 中, 温度是最主要 的被控参数之一 。但是大 多数传统温度控制系统都只 能测 量单点温度 。本文针对这些存 在的问题 , 设计出了基 于 SCSs m o hp单片机 的温度控制 o ( t nC i ye ) 器。 由于在设计 时增加 了通 信功能 , 因此本温度控制 器具有 比传 统温度控制器更强大的功能 ,不 仅可 以用 于工 业现场对温度进 行控制 ,还能通过 C N总线 的传输 能力在几个站点之 间进行数 A 据传 输和数据交换 。本系统属 于嵌人式温度控制系统 , 可应用于 任何需要控制温度的场合 , 因此具有通用性 。在设计 中 , 采用 了

摘

要 :文章介 绍 了一种 利用 C 0 10 0S C) 8 5 F 4 (o 单片机作为主机控制 器, 对被控对 象的温

度 进 行 调 控 的 测控 系统 。它 主要 由数据 采 集 、 制 决 策 及控 制输 出三 大部 分 组成 。整 个 系 控

基于SOC的多核图像处理算法的设计与实现

基于SOC的多核图像处理算法的设计与实现近年来随着科技的不断发展,计算机科学与技术领域也在不断的创新与发展中,多核处理器技术的崛起,对于图像处理技术的提升起到了重要的作用。

现在已经有很多广泛使用的多核处理器,其中最常见的就是SoC系统,在SoC架构的基础上,可以实现高效的多核图像处理算法。

本文将对基于SoC的多核图像处理算法的设计与实现进行深入地探讨。

一、 SoC多核芯片的概述SoC全称System on Chip(系统单芯片),是将整个系统的功能集成到一个芯片中,就可以实现高度集成、高性能、低功耗和小体积的特点。

比如,电视机板卡、智能手机、电子书、车载系统等,这些芯片都采用了SoC架构,可以显著提升整个设备的功耗效率和性能。

SoC芯片采用了ARM内核和多个IP核的集成技术,内核支持Quickstart,可以快速调整软件策略以优化SoC体系结构的性能。

而多核处理器同样选择SoC架构,可以充分利用多个CPU核心,在处理图像数据时可以实现高效的并行计算和数据传输。

为了解决SoC芯片中存在的多个控制器和处理器之间的通信问题,一些解决方案采用了片上数据总线(On-chip Bus,OCB)来实现设备之间的连接。

二、多核图像处理算法的需求当设计多核处理架构时,处理与修改大量的图像数据是非常重要的应用。

为了高效地实现图像处理功能,需要以特殊的方式对系统进行设计。

多核图像处理算法的设计和实现也面临许多挑战,如如何合理地利用不同核的并行计算,并在多个核之间进行任务划分和数据传输,从而提高图像数据处理的帧速率。

基于此,需要进行大量的研究和算法优化,以完善并实现高效的多核图像处理算法。

三、多核图像处理算法的设计基于SoC的多核图像处理算法需要依赖于适当的软硬件启动环境和支持软件开发工具,同时还需要综合考虑各种算法的性能和适用性。

除此之外,还需要选择合适的操作系统、内核和驱动程序以支持多核处理器的并行计算和数据传输。

基于SoC单片机的小型化SLD光源数字控制系统设计

d g t l D o t o l o i m ,d g t a i n a d m i i t rz t n a e r a ie n t i s s e ii a PI c n r l g rt a h i ii t n n a u ia i r e l d i h s y t m. Th z o o z e

c n r l n y tm f LD d p e ne gn ei gp o u to .B s do o s se n c i) o to l g s s e o i S i a o td i n ie rn r d cin a e nS C( y tm o h p s

关键 词 : L S D;S C单 片机 ; N8 3 ;小型化 o AD 8 1

中图分 类号 : 5 文 献标识码 : TN 2 A d i 1 . 9 9ji n 1 0—60 2 1. 2 04 o : 0 3 6/.s . 0 55 3. 0 0 0 . 1 s

De in fm i a u ea i ia o r li g s se f sg o nit r nd d g t lc nto ln y tm o

引 言

相 比于与传统 的模拟 控制 方法 , 光纤 陀螺光 源数 字化 控制 操 作更 加 方便 , 处理 数 据更 加 简便 , 能够 实

现更复杂的控制, 因而近年得到了广泛的研究 。但 目 的研究多侧重于提高光源控制精度方面, 前 电路设

系统芯片SOC设计

SOC的设计流程

SOC的设计流程

SOC采用的是Top-to-Down方法,整体考虑了SoC芯片软/硬件系统设计的 要求,将系统需求、处理机制、芯片体系结构、各层次电路及器件、算 法模型、软件结构、协同验证紧密结合起来,从而用单个或极少几个芯 片完成整个系统的功能。设计流程分为以下几个主要步骤:

1. 系统总体方案设计:芯片系统功能、指标定义、需求分析、产品市场定位、软/硬 件划分、指标分解等整体方案论证。

设计从面向逻辑的设计向面向互连的设 计方法转变。 将嵌入式软件集成到SOC中。

在设计阶段需要进行软硬件划分,以使 软硬件可以同时进行设计调试。 对设计阶段的验证提出了很高的要求。

设计人员的经验十分重要。

因此,从硬件角度看,SoC是 在一个芯片上由于广泛使用预 定制IP模块而得以快速开发的 集成电路;

(2)SoC芯片以MPU(Micro Processing Unit )/MCU(Micro Controller Unit )/DSP(Digital Signal Processing)为核心,通过总 线与其它模块相互连接,实现数据交换和通讯控制等功能,形成一个完 整的计算机系统。

(3)软件存储在Flash ROM中,由MPU/MCU/DSP 解释、执行,完成 相应的处理功能。

单击添加副标题

系统芯片 (SOC)

设计

2023

系统芯片(SOC)是微电子技术发展的必然。

目前,集成电路工业发展的一大特征是产业分工,形成了设计、 制造、封装及测试独立成行的局面。另一大特征是系统设计和 IP(Intellectual Property,知识产权)设计发生分工。

并且,随着深亚微米集成电路制造工艺的普及,大量的逻辑功 能可以通过单一芯片实现,同时一些消费类的电子行业要求进 行百万门级的IC设计。这些系统的设计时间和产品投放时间等 尽可能短,产品质量尽可能高。在这种情况下,一种新的概念 SOC(系统芯片,也称片上系统)应运而生。

基于可配置处理器的SoC系统级设计方法

软件 开发 平 台。 实验 结 果表 明 , 方 法 不仅 灵活 , 且设 计 周 期 短 , 少 了设 计 工 作 量 。 该 而 减

关键 词 片上 系统 S C 系统 级设 计 软 硬 件 协 同设 计 指令 集扩 展 o

文 章 编 号 10 — 3 1 ( 0 6 2 — 0 6 0 文献 标 识 码 A 0 2 8 3 一 2 0 )6 0 9 — 3 中图 分 类 号 T 3 P6

维普资讯

基 于 可 配 置处 理 器 的 S C 系统 级 设 计 方法 o

邵 洋 1 单 , 2 睿 张铁 军 ‘ 侯 朝焕

‘中国科 学院 声学研 究所 , 京 10 8 ) ( 北 000

( 中国科 学院研 究生 院 , 北京 10 3 ) 0 0 9

E— i: n y h @g i c n mal mid s y mal o .

摘

要

论 文 对 一 种 经 过 改进 的 S C 系统 级 快 速 设 计 方 法进 行 了介 绍 和 研 究。 o 该设 计 基 于 可 配 置 处理 器核 , 设 计 早 期 在

阶段 对 S C 系统 快 速 建 模 . 获得 针 对 具 体 应 用 算 法 的 最优 性 能 。 时 , 用软 硬 件 协 同设 计 方 法 , 到 硬件 结构 模 型 和 o 以 同 利 得

系统芯片SOC设计

根据项目需求和内核版本,选择合适的驱动框架,如字符设备驱动、平台设备驱动、总线 驱动等。

调试技巧

使用printk、debugfs等调试手段,结合内核日志分析工具(如dmesg、logcat等),进 行驱动调试和问题定位。

系统集成测试方案制定和执行

测试计划制定

根据项目需求和测试目标,制定 详细的系统集成测试计划,包括 测试范围、测试环境、测试方法、

接口与通信协议制定

接口类型选择

根据应用需求和性能要求, 选择合适的接口类型,如 GPIO、SPI、I2C等。

通信协议制定

制定芯片内部及与外部设 备之间的通信协议,确保 数据传输的准确性和可靠 性。

接口电路设计

设计合理的接口电路,实 现接口的物理连接和数据 传输功能。

04

硬件设计实现

逻辑电路设计与仿真验证

针对不同厂商和市场需求,提供 定制化的SOC解决方案,如特定

的处理器架构、加密算法等。

高速数据传输

采用先进的互连技术,实现芯片 内部各模块间的高速数据传输,

提升整体性能。

物联网终端设备SOC应用实例剖析

低功耗优化

针对物联网设备长时间运行、低功耗的需求,进行芯片级功耗优 化,如采用低功耗处理器、休眠模式等。

逻辑电路设计

根据系统需求,采用硬件描述语言 (如Verilog或VHDL)进行逻辑电路 设计,包括处理器核、内存接口、外 设接口等模块的设计。

仿真验证

利用专业的EDA工具进行逻辑电路的 仿真验证,检查设计的功能正确性和 性能指标是否满足要求。

物理电路布局布线优化

物理电路布局

在确定逻辑电路设计无误后,进行物理电路的布局规划,考虑芯片面积、功耗、 信号完整性等因素,合理安排各功能模块的位置。

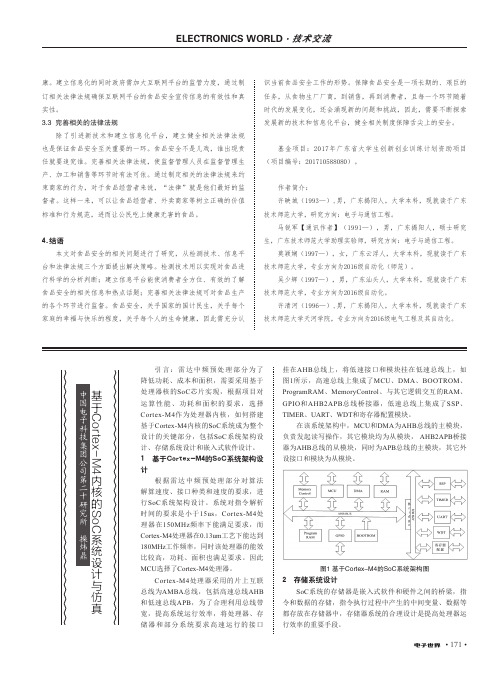

基于Cortex-M4内核的SoC系统设计与仿真

• 171•康。

建立信息化的同时政府需加大互联网平台的监管力度,通过制订相关法律法规确保互联网平台的食品安全宣传信息的有效性和真实性。

3.3 完善相关的法律法规除了引进新技术和建立信息化平台,建立健全相关法律法规也是保证食品安全至关重要的一环。

食品安全不是儿戏,谁出现责任就要追究谁。

完善相关法律法规,使监督管理人员在监督管理生产、加工和销售等环节时有法可依。

通过制定相关的法律法规来约束商家的行为,对于食品经营者来说,“法律”就是他们最好的监督者。

这样一来,可以让食品经营者、外卖商家等树立正确的价值标准和行为规范,进而让公民吃上健康无害的食品。

4.结语本文对食品安全的相关问题进行了研究,从检测技术、信息平台和法律法规三个方面提出解决策略。

检测技术用以实现对食品进行科学的分析判断;建立信息平台能使消费者全方位、有效的了解食品安全的相关信息和热点话题;完善相关法律法规可对食品生产的各个环节进行监督。

食品安全,关乎国家的国计民生,关乎每个家庭的幸福与快乐的程度,关乎每个人的生命健康,因此需充分认识当前食品安全工作的形势。

保障食品安全是一项长期的、艰巨的任务,从食物生厂厂商,到销售,再到消费者,且每一个环节随着时代的发展变化,还会涌现新的问题和挑战,因此,需要不断探索发展新的技术和信息化平台,健全相关制度保障舌尖上的安全。

基金项目:2017年广东省大学生创新创业训练计划资助项目(项目编号:201710588080)。

作者简介:许映城(1993—),男,广东揭阳人,大学本科,现就读于广东技术师范大学,研究方向:电子与通信工程。

马锐军【通讯作者】(1991—),男,广东揭阳人,硕士研究生,广东技术师范大学助理实验师,研究方向:电子与通信工程。

莫颖娴(1997—),女,广东云浮人,大学本科,现就读于广东技术师范大学,专业方向为2016级自动化(师范)。

吴少辉(1997—),男,广东汕头人,大学本科,现就读于广东技术师范大学,专业方向为2016级自动化。

基于SOC架构的智能图像处理和外设控制系统设计

0 引 言

随着人工智能的崛起,对深度学习、大数据、神经网 络芯片等相关技术成果的集成应用,人工智能的智能化水 平进一步提 升,对 未 来 战 争 将 产 生 全 方 位、颠 覆 性 的 影 响 。 [1] 弹载计算机 SoC 处 理 芯 片 作 为 制 导 武 器 的 重 要 组 成 部分,采用高精度制导与控制系统,利用人工智能的训练 和推理,通过对各种传感器获取的目标信息,以及对信息 分析和处理后实时修正、控制导弹的飞行轨迹,完成对目 标的有效攻击 。 [2]

· 90 ·

计算 机 测 量 与 控 制 .2021.29(4) 犆狅犿狆狌狋犲狉 犕犲犪狊狌狉犲犿犲狀狋 牔 犆狅狀狋狉狅犾

控制技术

文章编号:1671 4598(2021)04 0090 05 DOI:10.16526/j.cnki.11-4762/tp.2021.04.018 中图分类号:TP391.41 文献标识码:A

目前,以卷积 神 经 网 络 为 代 表 的 深 度 学 习 算 法 在 形 式 上模拟了人脑的学习过程,也就是重复训练强化其智能思 维,大大提升了 人 工 智 能 系 统 的 运 行 效 率 。 [3] 然 而, 深 度 学习算法需 要 专 用 硬 件 平 台 才 能 发 挥 其 性 能 。 [4] 现 有 的 人 工智能芯片的 技 术 路 线 大 致 可 以 分 为 三 类:1) 通 用 型 的 CPU 及 GPU 芯片;CPU 的 架 构 和 指 令 对 神 经 网 络 计 算 的 兼容度不够,性价 比 与 运 算 效 率 偏 低;2)FPGA 芯 片; 具 有可定制、可编程的特点,且并行效率适应神经网络运算。 3)专用 ASIC 芯 片; 对 特 定 计 算 的 运 行 效 率 极 高,不 具 备

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

? SOC单片机 ? 单片机又称微控制器,是设备中的核心部件。用户选

择单片机一般从以下几个指标考虑:价格、速度、位数、 电压、功耗、系统扩展与驱动能力等。另外,软件开发的 难易也会在很大程度上影响age 13

MSP430

ADuC812

?

? Cygnal C8051F系列单片机具有与MCS-51内核及指令集完 全兼容的微控制器除了具有标准8051的数字外设部件之外片 内还集成了数据采集和控制系统中常用的模拟部件和其它数 字外设及功能部件

包括模拟多路选择器 ? 可编程增益放大器 ? ADC、DAC、电压比较器、电压基准 ? 温度传感器 ? 可编程计数器/定时器阵列PCA定时器数字

Page 14

TI公司的MSP430系列单片机是一种超低功耗的混合信号 控制器,其灵活的时钟源选择可最大限度的延长电池寿命。

MSP430系列单片机的不同型号针对不同应用领域,集成了 丰富的外围模块,包括:

Page 16

12.4 系统设计方法与对象的变化

Top-Down、Bottom-Up设计方法 ? 自顶向下法:首先确定大框架结构,再确定模块结构,最

后是详细的子电路结构

特点:可靠性高,便于标准化管理,信息传输关 系层次清楚

? 自底向上法:首先给出各个模块的详细结构,然后再利用 各个模块构建整个系统

? 看门狗(WDT)、

? 定时器A(Timer-A)、

? 定时器B(Timer-B)、

? 比较器、

? 串口硬件乘法器、

? 液晶驱动器、

? 8路10/12/14位ADC、

? 基本定时器(Basic Timer)。 Page 15

MSP430F149芯片

? ADuC812是美国ADI(Analog Device Inc)公司生产的高性能 单片机,是全集成的12位数据采集系统。

? 1 ? E?1

? E是材料的弹性模量,对于确定的材料为一常数。 ? 所以测得应变可以得到零部件所受的应力。

Page 22

Page 8

? ispPAC20器件的结构图 ? 能实现放大、求和、 ? 积分、滤波等功能

Page 9

(3)PSoC ? Cypress PSoC的特点在于:除了 ? 嵌入CPU内核, ? 用户可用的模拟模块有:DAC、ADC、比较器、运算放

大器等。 ? PSoC采用了混合信号设计和基于平台设计的理念。 ? 可组成多种数字和模拟器件, ? 集成的模拟和数字外围器件阵列都是动态可配置,利用芯

第12章 基于SoC 的系统设计

测试系统的微型化

1

模、数及混合集成技术

2

SoC 概 述

3

系统设计方法与对象的变化

4

SoC的设计流程与步骤

5

设计举例

6

Page 2

12.1 测试系统的微型化

系统及器件发展 ? 系统及器件功能日趋复杂,体积、功耗逐渐减小

? 新器件逐渐可替代传统的系统功能 ? SOPC ? DSP ? SOC单片机 ? PSOC

Page 5

模拟集成技术的发展

(1)现场可编程模拟阵列( FPAA ) ?核心是CAB可编程模拟单元 . ?CAB一般由运放或跨导放大器和外围可编程电容

阵列、电阻阵列、开关阵列等共同构成,其中各 元件的取值及相互连接关系等均受配置数据的控 制

Page 6

? 单个CAB即可实现整流器、放大器、可编程比较器和一阶 滤波器等信号调理功能;将多个CAB加以组合、连接,便 可实现高阶滤波器、脉宽调制器等更为复杂的电路

Page 7

(2)在系统可编程模拟电路

? Lattice 公司ispPAC系列 ? 包括ispPAC10、ispPAC20、ispPAC30等通用型器件和

ispPAC80 、ispPAC82 等ISP滤波器 ? ispPAC80器件,该器件包含了各种滤波器电路,例如:

巴特沃斯、切比雪夫、椭圆滤波、高斯滤波和线性相位滤 波等,设计者可根据设计指标从中选择、配置电路

特点:适合于小规模系统设计

Page 17

12.5 SoC的设计流程与步骤

? 传统的SoC设计流程

Page 18

Page 19

基于IP 模块的SoC设计流程

Page 20

软硬件协同设计流程

12.6 基于SoC单片机的应变测试仪设计

? 一、测试总体方案

Page 21

二、应力、应变的测试方法

? 在杆件受到拉伸(或压缩)的情况下,只有一个主应力 σ1,它的方向与外加载荷F的方向平行,该方向的应变为 ε1。并且有:

Page 3

12.2 模、数及混合集成技术 ?集成技术发展关系

Page 4

高集成度数字器件

? 20世纪80年代中期Altera公司----EPLD ? 20世纪80年代末Lattice公司----CPLD ? 1985年Xilinx公司首家推出了----FPGA ? SoPC =FPGA+MCU+DSP ? Xilinx公司的SoPC芯片型号为:

片内部的可编程互联阵列,可以有效的配置芯片上的模拟 和数字资源

Page 10

PSoC数字模块、模拟模块配置图

Page 11

12.3 SoC 概 述

? SoC是集成电路设计方法学中的新技术,是指以嵌入 式系统为核心,以IP复用技术为基础,集软、硬件于一体, 并追求产品系统最大包容的集成芯片。

Page 12

? 它在芯片内集成了高性能的自校准多通道ADC(8通道12位 高精度)、

? 2个12位DAC以及可编程的8位MCU(与8051兼容)。 ? 片内有8kB的闪速/电擦除程序存储器和在线下载/调试/编程

的功能、640B的闪速/电擦除数据存储器、256B片内数据存 储器以及与8051兼容的内核。 ? MCU内核和模拟转换器均有正常、空闲和掉电工作模式,在 工业温度范围内器件可在3V和5V两种电压下工作,提供了 适合于低功耗应用的灵活的电源管理方案。

Spartan、Spartan-II、Virtex、Virlex-II、XC4000和 XC9500 ? Altera公司的SoPC系列有: APEX EP20KE Nios软核带有DSP功能块,在 Nios 核中还可得到定时器/计 数器、PIO、SPI、PWM 控制器、10/100 M以太网 MAC 和 SDRAM控制器等资源。