详细介绍modelsim的使用方法共30页

modelsim使用指南.

执行仿真 (UI)

选择 timesteps数量就 可以执行仿真

Restart – 重装任何已改动 的设计元素并把仿真时间设 为零 COM) restart

38

run 命令参数

可选的参数

– -<timesteps> <time_unit> • 指定运行的timesteps数量 • 单位可用{fs, ps, ns, ms, sec}

用户界面 (UI)

– 能接受菜单输入和命令行输入 – 课程主要讨论

批处理模式

– 从DOS或UNIX命令行运行批处理文件 – 不讨论

13

基本仿真步骤

1 Ö 建立库

2 Ö 映射库到物理目录

3 Ö 编译源代码 - 所有的HDL代码必须被编译 - Verilog和VHDL是不同的

4 Ö 启动仿真器 5 Ö 执行仿真

UI) Design -> Compile Cmd) vlog -work <library_name> <file1>.v <file2>.v

– 文件按出现的顺序被编译 – 文件的顺序或者编辑的顺序不重要

支持增量式编译 缺省编译到work库

– 例如. vlog my_design.v

– -sdfmin | -sdftyp | -sdfmax <instance>=<sdf_filename> • 注释SDF文件 • 可选项 • 使用实例名也是可选项; 如果没有使用, SDF用于顶级

36

5 Ö 执行仿真

UI) Run COM) run <time_step> <time_units> 按timesteps指定的时间长度执行仿真

modelsim使用手册

Modelsim 6.0 使用教程2006.12qq:535796211一.Modelsim简介Modelsim仿真工具是Model公司开发的。

它支持Verilog、VHDL以及他们的混合仿真,它可以将整个程序分步执行,使设计者直接看到他的程序下一步要执行的语句,而且在程序执行的任何步骤任何时刻都可以查看任意变量的当前值,可以在Dataflow窗口查看某一单元或模块的输入输出的连续变化等,比Quartus自带的仿真器功能强大的多,是目前业界最通用的仿真器之一。

ModelSim分几种不同的版本:SE、PE和OEM,其中集成在Actel、Atmel、Altera、Xilinx以及Lattice等FPGA厂商设计工具中的均是其OEM版本。

比如为Altera提供的OEM版本是ModelSim-Altera,为Xilinx提供的版本为ModelSim XE. SE版本为最高级版本,在功能和性能方面比OEM版本强很多,比如仿真速度方面,还支持PC 、UNIX 、LIUNX混合平台.2为什么要学Modelsim?1.Modelsim是专业的HDL语言仿真器,比Quartus自带的仿真器功能强大的多.2. Quartus simulator不支持Testbench ,只支持波形文件.vwfvwf文件全称是矢量波形文件(Vector Waveform File),是Quartus II中仿真输入、计算、输出数据的载体。

一般设计者建立波形文件时,需要自行建立复位、时钟信号以及控制和输入数据、输出数据信号等。

其中工作量最大的就是输入数据的波形录入。

比如要仿真仅1KB的串行输入数据量,则手工输入信号的波形要画8000个周期,不仅费时费力而且容易出错怎样入门?对于初学者,modelsim自带的教程是一个很好的选择,在Help->SE PDF Documentation->Tutorial里面.它从简单到复杂、从低级到高级详细地讲述了modelsim的各项功能的使用,简单易懂。

验证基础及modelsim使用方法PPT课件

随机验证

平台自动产生随机测试用例,通过覆盖率保证 测试完备性。

覆盖验证

覆盖验证

使用覆盖率工具,可检查验证是否全面,代码 是否冗余,往往可以发现隐藏的bug。

自动化验证

自动产生测试用例 自动进行数据格式转换 自动运行仿真,打印数据,保存波形 自动数据比对,打印错误信息 自动文件管理 。。。 。。。

将映射信 息打印到 脚本命令

窗口

打开使能/ 关闭控制 ,初始状 态为使能

init_signal_spy("/top/uut/inst1/sig1","/top/top_sig1",1,1);

wait;

end process spy_process;

...

spy_enable_disable : process(enable_sig)

引用util library

将内部信号/top/uut/inst1/sig1的值 映射到顶层信号/top/top_sig1上

end;

architecture only of top is signal top_sig1 : std_logic; begin

... spy_process : process begin

直接验证

将文件中的数据导入到RAM中

mem load -i input_data_file memory_instance_name

直接在RAM中产生调试数据

mem load -skip skip_data_number -filltype data_generate_type\ -filldata first_data -fillradix radix memory_instance_name

详细介绍modelsim的使用方法

ModelSim产品简介(13)

Signals 窗口

• 紧跟Structure窗口 – 显示Structure窗口的当前层HDL项的名称和 值 • 层次 - (+)可展开的, (-)已展开的 • VHDL 信号,Verilog 线网, 寄存器变量和已命名 的时间

• 可拖放到Wave和List窗口

ModelSim产品简介(14)

ModelSim产品简介(11)

Process 窗口 • 显示外部和内部的处理 • View -> Active

– 显示当前仿真众所有在执行前预定的 processes

• View -> In Region

– 显示在Structure 窗口中选定的所有 processes 的名字

ModelSim产品简介(12)

ModelSim产品简介(17)

Variables窗口

• 列出 HDL 项的名称 – VHDL – 常数, generics 和变量 – Verilog – 寄存器变量 • 到当前过程的路径被显示在左下 • 树层次 - (+)可展开的, (-)已展开的 • 可改变 – 选择HDL项改变值 • 可浏览 – 在Wave 或 List 窗口 或 log 文件的项 – 选择变量或层中的变量

ModelSim产品简介(9)

Source 窗口

ModelSim产品简介(10)

Source 窗口 • 描述

– 显示所选的HDL项的信息

• 检查

– 显示所选HDL项当前仿真值

1) 高亮信号, 变量, 常数, 线网, 或寄存器 2) 右击鼠标 (或 Object Menu -> Examine/Description)

ModelSim/XE

Modelsim使用说明

Modelsim 使用简明指南1 前言作为一种简单易用,功能强大的逻辑仿真工具,Modelsim 具有广泛的应用。

这里对ModelSim 作一个入门性的简单介绍。

首先介绍ModelSim 的代码仿真,然后介绍门级仿真和时序验证。

和时序验证。

2 代码仿真在完成一个设计的代码编写工作之后,可以直接对代码进行仿真,检测源代码是否符合功能要求。

这时,仿真的对象为HDL 代码,比较直观,速度比较快,可以进行与软件相类似的多种手段的调试(如单步执行等)。

在设计的最初阶段发现问题,在设计的最初阶段发现问题,可以节省大量的精力。

可以节省大量的精力。

2.1 代码仿真需要的文件1.设计HDL 源代码:源代码:新建一个“文本文档”文件,在记事本中输入HDL 源代码,使用V erilog 语言编程。

语言编程。

2.测试激励代码:.测试激励代码:在同一个文件中,根据设计要求输入/输出的激励程序,由于不需要进行综合,书写具有很大的灵活性。

有很大的灵活性。

3.保存该文件后退出,然后重命名该文件,.保存该文件后退出,然后重命名该文件,使该文件后缀名由使该文件后缀名由.txt 变为.v 。

如:t81.v 。

4. 该文件保存在你所建立的工作目录中,如:D\VLSItext\t1如果要修改该文件,仍然可以选择用仍然可以选择用记事本记事本打开编辑再保存,记事本相当于是一源代码输入软件。

输入软件。

注:所有的文件名及目录名均要求是英文,无中文字符。

2.2 代码仿真步骤1.建立工程:在ModelSim 中建立Project 。

如图2.1所示,点击File ðNew ðProject ,得到Creata Project 的弹出窗口,如图2.2所示。

在Project Name 栏中填写你的项目名字,建议和你的顶层文件名字一致,如t81。

Project Location 是你的项目目录,你可通过Brose 按钮来选择或改变,建议项目目录选择为你所保存源代码的目录,如:D\VLSItext\t1。

ModelSim操作方法

ModelSim

在105的xterm中输入命令:vsim & 即启动ModelSim. 然后点击界面上方的File——New——Project,出现如下界面:

在Project Name中输入想要建立的工程的名字,在Project Location中输入想要建立工程的路径,其他都是默认值即可,填好后点击OK.出现如下界面:

如果想填入已经写好的代码,则点击Add Existing File,找到文件路径进行添加,设置好文件格式(.v文件选择Verilog,.txt文件选择Text),点击OK则添加完毕。

如果想要重新写代码,则点击Creat New File,写好代码后保存即可。

把文件添加到工程后,点击工具栏上方的编译按钮,如下图所示:

编译不成功则改代码中的错误,直到全部编译成功为止。

编译成功后点击编译按钮后面的Simulate按钮:

出现如下对话框,选择Work中的testbench文件,点击OK 即可进行仿真。

然后执行View——Wave,View——Objests,将Objests中想要观察的信号拖进Wave窗口,最后点击运行按钮Run-All(如下图),

等仿真完毕后按红色的小叉按钮Break来停止仿真。

此时观察Wave窗口即有仿真波形。

modelsim使用教程

modelsim使用教程ModelSim是一款常用的硬件描述语言(HDL)仿真工具,本教程将向您介绍如何使用ModelSim进行仿真。

步骤1:安装ModelSim首先,您需要下载和安装ModelSim软件。

在您的电脑上找到安装程序并按照提示进行安装。

步骤2:创建工程打开ModelSim软件,点击"File"菜单中的"New",然后选择"Project"。

在弹出的对话框中,选择工程的存储位置,并为工程命名。

点击"OK"完成工程创建。

步骤3:添加设计文件在ModelSim的工程窗口中,右键点击"Design"文件夹,选择"Add Existing File"。

然后选择包含您的设计文件的目录,并将其添加到工程中。

步骤4:配置仿真设置在工程窗口中,右键点击"Design"文件夹,选择"Properties"。

在弹出的对话框中,选择"Simulation"选项卡。

在"Top level entity"字段中,选择您的设计的顶层模块。

点击"Apply"和"OK"保存设置。

步骤5:运行仿真在ModelSim的工具栏中,找到"Simulate"按钮,点击并选择"Start Simulation"。

这将打开仿真窗口。

在仿真窗口中,您可以使用不同的命令来控制和观察设计的行为。

步骤6:查看仿真结果您可以在仿真窗口中查看信号波形、调试设计并分析仿真结果。

在仿真窗口的菜单栏中,您可以找到一些常用的查看和分析工具,如波形浏览器、信号分析器等。

步骤7:结束仿真当您完成仿真时,可以选择在仿真窗口的菜单栏中找到"Simulate"按钮,并选择"End Simulation"以结束仿真。

modelsim的详细使用方法

一、简介ModelSim是一款由美国Mentor Graphics公司推出的集成电路仿真软件,广泛应用于数字电路和系统设计领域。

它提供了强大的仿真和验证功能,能够帮助工程师快速高效地进行电路设计与验证工作。

本文将详细介绍ModelSim的使用方法,以帮助读者更好地掌握这一工具的操作技巧。

二、安装与配置1. 下载ModelSim安装包,并解压到指定目录2. 打开终端,进入ModelSim安装目录,执行安装命令3. 安装完成后,配置环境变量,以便在任何目录下都能够调用ModelSim程序4. 打开ModelSim,进行软件注册和授权,确保软件可以正常运行三、工程创建与管理1. 新建工程:在ModelSim主界面点击“File” -> “New” -> “Project”,输入工程名称和存储路径,选择工程类型和目标设备,点击“OK”完成工程创建2. 添加文件:在工程目录下右键点击“Add Existing”,选择要添加的源文件,点击“OK”完成文件添加3. 管理工程:在ModelSim中可以方便地对工程进行管理,包括文件的增删改查以及工程参数的设置等四、代码编写与编辑1. 在ModelSim中支持Verilog、VHDL等多种硬件描述语言的编写和编辑2. 在ModelSim主界面点击“File” -> “New” -> “File”,选择要新建的文件类型和存储位置,输入文件名称,点击“OK”完成文件创建3. 在编辑器中进行代码编写,支持代码高亮、自动缩进、语法检查等功能4. 保存代码并进行语法检查,确保代码符合规范,没有错误五、仿真与调试1. 编译工程:在ModelSim中进行代码编译,生成仿真所需的可执行文件2. 设置仿真参数:在“Simulation”菜单下选择“S tart Simulation”,设置仿真时钟周期、输入信号等参数3. 运行仿真:点击“Run”按钮,ModelSim将开始对设计进行仿真,同时显示波形图和仿真结果4. 调试设计:在仿真过程中,可以通过波形图和仿真控制面板对设计进行调试,查找并解决可能存在的逻辑错误六、波形查看与分析1. 查看波形:在仿真过程中,ModelSim会生成相应的波形文件,用户可以通过“Wave”菜单查看波形并进行波形分析2. 波形操作:支持波形的放大、缩小、平移、选中等操作,方便用户对波形进行分析和观察3. 波形保存:用户可以将波形结果保存为图片或文本文件,以便日后查阅和分析七、性能优化与验证1. 时序优化:在设计仿真过程中,可以通过观察波形和性能分析结果,对设计进行优化,提高设计的时序性能2. 逻辑验证:通过对仿真的结果进行逻辑验证,确保设计符合预期的逻辑功能3. 时序验证:对设计的时序性能进行验证,确保信号传输和时钟同步的正确性八、项目输出与文档整理1. 输出结果:在仿真和验证完成后,可以将仿真结果、波形图和性能分析结果输出为文本文件或图片,方便后续的文档整理和报告撰写2. 结果分析:对仿真结果和验证结果进行详细的分析,确定设计的性能和功能是否符合设计要求3. 文档整理:根据仿真和验证结果,进行文档整理和报告撰写,为后续的设计和优化工作提供参考九、总结与展望ModelSim作为一款专业的集成电路仿真软件,具有着强大的功能和丰富的特性,可以帮助工程师进行电路设计与验证工作。

Modelsim详细使用教程

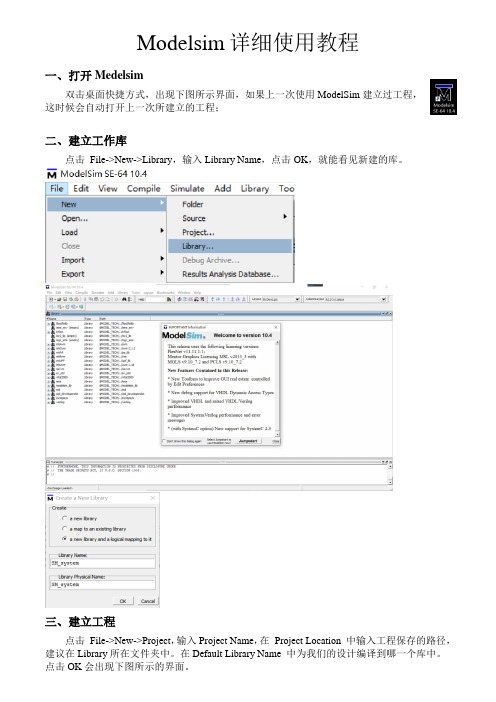

Modelsim详细使用教程一、打开Medelsim双击桌面快捷方式,出现下图所示界面,如果上一次使用ModelSim建立过工程,这时候会自动打开上一次所建立的工程;二、建立工作库点击File->New->Library,输入Library Name,点击OK,就能看见新建的库。

三、建立工程点击File->New->Project,输入Project Name,在Project Location 中输入工程保存的路径,建议在Library所在文件夹中。

在Default Library Name 中为我们的设计编译到哪一个库中。

点击OK会出现下图所示的界面。

四、为工程添加文件Create New File 为工程添加新建的文件;Add Existing File为工程添加已经存在的文件;Create Simulation为工程添加仿真;Create New Folder为工程添加新的目录。

这里我们点击Create New File,来写仿真代码。

输入File Name,再输入文件类型为Verilog (默认为VHDL,Modelsim也可以仿真System Verilog代码),Top Level表示文件在刚才所设定的工程路径下。

点击OK,并点击Close关闭Add items to the Project窗口。

这时候在Workspace窗口中出现了Project选项卡,里面有8_11.v,其状态栏有一个问号,表示未编译,双击该文件,这时候出现8_11.v的编辑窗口,可以输入我们的Verilog代码。

五、编写Verilog代码写完代码后,不能马上就编译,要先File->Save保存,否则,编译无效。

然后选择Compile->Compile All。

Transcript脚本窗口出现一行绿色字体Compile of 8_11.v was successful. 说明文件编译成功,并且该文件的状态栏显示绿色的对号。

modelsim使用手册

5.装载文件 (1)双击libray 中work中的count_tp装载 (2)点击simulate – start simulation 按右图设置by Foxit PDF Creator © Foxit Software For evaluation only.

vwf文件全称是矢量波形文件(Vector Waveform File),是Quartus II中仿真 输入、计算、输出数据的载体。一般设计者建立波形文件时,需要自行建立 复位、时钟信号以及控制和输入数据、输出数据信号等。其中工作量最大的 就是输入数据的波形录入。比如要仿真仅1KB的串行输入数据量,则手工输入 信号的波形要画8000个周期,不仅费时费力而且容易出错

Modelsim的安装 同许多其他软件一样,Modelsim SE同样需要合法的 License,通常我们用Kengen产生license.dat。 ⑴ 解压安装工具包开始安装,安装时选择Full product 安装。当出现Install Hardware Security Key Driver时 选择否。当出现Add Modelsim To Path选择是。出现 Modelsim License Wizard时选择Close。 ⑵ 在C盘根目录新建一个文件夹flexlm,用Keygen产生一 个license.dat,然后复制到该文件夹下。 ⑶ 修改系统的环境变量。右键点击桌面我的电脑图标, 属性->高级->环境变量->(系统变量)新建。按下图所示 内容填写,变量值内如果已经有别的路径了,请用“;” 将其与要填的路径分开。LM_LICENSE_FILE = c:\flexlm\license.dat 4

Generated by Foxit PDF Creator © Foxit Software For evaluation only.

ModelSim的简要使用方法

第一章 介 绍ModelSim的简要使用方法第一课 Create a Project1.第一次打开ModelSim会出现Welcome to ModelSim对话框,选取Create a Project,或者选取File\New\Project,然后会打开Create Project对话框。

2.在Create Project对话框中,填写test作为Project Name;选取路径Project Location作为Project文件的存储目录;保留Default Library Name设置为work。

3.选取OK,会看到工作区出现Project and Library Tab。

4.下一步是添加包含设计单元的文件,在工作区的Project page中,点击鼠标右键,选取Add File to Project。

5.在这次练习中我们加两个文件,点击Add File to Project对话框中的Browse 按钮,打开ModelSim安装路径中的example目录,选取counter.v和tcounter.v,再选取Reference from current location,然后点击OK。

6.在工作区的Project page中,单击右键,选取Compile All。

7.两个文件编译了,鼠标点击Library Tab栏,将会看到两个编译了的设计单元列了出来。

看不到就要把Library的工作域设为work。

8.最后一不是导入一个设计单元,双击Library Tab中的counter,将会出现Sim Tab,其中显示了counter设计单元的结构。

也可以Design\Load design 来导入设计。

到这一步通常就开始运行仿真和分析,以及调试设计,不过这些工作在以后的课程中来完成。

结束仿真选取Design \ End Simulation,结束Project选取File \ Close \ Project。

modelsim教程

準備事項1.ModelSim試用版下載2.範例程式下載(史丹佛大學一門課的期末專題Implememtation of ViterbiDecoder:constrain length K=3, code rate R=1/2,register-exchange)整個project共含7個Verilog程式:system.v (top-level)|-- clkgen.v|-- chip_core.v|-- controller.v|-- spu.v|-- acs4.v|-- acs1.v(或是另外一個Verilog的簡單例子,可以從C:\ SynaptiCAD\ Examples\ TutorialFiles\VeriLoggerBasicVerilo gSimulation\ add4.v and add4test.v)(或是另外一個VHDL的簡單例子,可以從C:\ Modeltech_5.7e\ examples\ adder.vhd and testadder.vhd)ModelSim PE /LE /SE 差別在哪?本篇文章內容主要在教導軟體使用,以Verilog程式為範例。

假設各位讀者已經熟悉Verilog,廢話不多說,讓我們馬上來見識一下ModelSim ...快速上手四部曲:建立Project、引進HDL Files、Compile、模擬(Simulate/Loading and Run)1.建立一個新的Project1-1 第一次執行程式時,可以從[開始] \ [程式集] \ ModelSim SE \ ModelSim;或是執行ModelSim在桌面的捷徑在Library標籤頁中,展開各Library就可以看到其下含的所有Package (for VHDL),進一步以Edit打開,可檢視該Package與Package Body內容1-2File \ New \ Project ...輸入project name and Location按OK鍵後•指定的路徑下會產生一個叫"work"的預設子資料夾,還有Viterbi.cr.mti、Viterbi.mpf 兩個檔案•主操作畫面左邊的Workspace內,在原本的Library標籤外,會出現另一個Project標籤(但此時裡面內容是空的)•還會蹦出另一個"Add items.mpf 檔儲存的是此project的相關資料,下次要開啟此project 就是利用File \ Open \Project... 開啟此.mpf若要移除之前建立的project,請從File \ Delete \Project... 移除2.載入Project 的HDL source codes按"Add items to the Project"視窗中的"Add Existing File" (或是從File \ Add to Project \ Existing Files ...)HDL files擺放的位置,路徑名稱不能有中文,否則軟體會抓不到files關掉"Add items to the Project"視窗,此時的Project下出現了HDL File,一堆問號表示這些檔案都還沒compile。

Modelsim软件的使用方法

5. 点击simulate-start simulation,选中design标签 work库下testbench文件,点击ok。 6. workspace窗口出现sim标签,右键testbench文 件,选择add to wave ,然后点击开始仿真按钮 即可,执行仿真,仿真结果如下图:

4.2.4 综合后仿真(续1)

图10.28 打开EDA tools settings

图10.29 设置网表输出项目

4.2.4 综合后仿真(续1)

图10.30 设置网表输出项目

4.2.4 综合后仿真(续2)

3.启动仿真器,加载仿真文件counter_tb,进行仿真,观察 仿真波形。本次需要Altera仿真库的元件库cycloneII,如 果资料库中没有,则需要加载该库。 仿真结果如下:

4.2.2 Modelsim仿真步骤(续5)

4、 启动仿真器并加载设计顶层

(2)在主窗口中出 现Object窗口,右键单 击Object窗口中的任 意信号,选择add to wave/ signals in region 或者是右键选中sim 窗口中加载的顶层设 计名,选中add to wave, 就可以打开波形窗口, 并将所有信号都加载 到波形窗口当中 。 如右图所示。

3、时序仿真 • 时序仿真也称为布局布线后仿真或者后仿真,是指电路已经映射到特

定的工艺环境后,综合考虑电路的路径延时与门延时的影响,验证电 路的行为是否能够在一定时序条件下满足设计构想的功能。 布线抽象出的门级网表、Testbench以及扩展名为SDO的标准延时文 件。 际运行情况是否一致,确保设计的可靠性和稳定性。

4.2.5 时序仿真

时序仿真的步骤跟综合后仿真大致相同,所不同的是 添加的文件不完全一样。其具体步骤如下: 1、在工作库work下建立一个工程project_shx,方法和功能 仿真中建立prtoject_gn一样; 2、工程中需要添加的文件有顶层设计文件counter,测试文 件counter_tb、QuartusII中编译生成的网表文件和延时 文件_vhd.sdo; _vhd.sdo文件的生成可以参考综合后仿真中网表 文件的生成方法,所不同的是在图10.30的设置中将 Generate netlist functional simulate only置为 “off”,点击OK保存设置,回到QuartusII主窗口后编译 文件,编译完成后,在counter文件夹下面能看到一个名 为counter_vhd.sdo文件,这个文件就是综合后仿真所需 要的延时文件。

modelsim详细图文使用教程(菜鸟基础教程)

版权所有,翻录必究!

天津大学

电子信息工程学院

戴鹏

总结:

建立工程编写主程序和测试程序编译仿真观察波形。 写了很多,但是应该讲得很详细了吧,希望对大家的学习有所帮 助。

版权所有,翻录必究!

写完代码后,不能马上就编译,要先保存,否则,编译无效。我们会看到“保存”的 图标是两色的,而且 half_clk.v 后的“?”还存在,这说明你没有保存文件,

这时,只需要点击保存,就会发现“保存”的图标变成了阴影,这样编译才有效,而 就是这么不起眼但至关重要的一步“保存” ,往往被很多初学者忽视,最终怀疑程序和

出现下框, 写入测试程序的名字 half_clk_tb, tb 是 testbench 的意思, 注意选 verilog, Ok。

这样就把 half_clk_tb.v 加载到了 project 中,双击 half_clk_tb.v 在右边的程序编辑区 中编写代码: `timescale 1ns/1ns

天津大学

电子信息工程学院

戴鹏

Modelsim 详细使用方法

很多的 modelsim 教程中都讲得很丰富,但忽视了对整个仿真过程的清晰解读,而且都 是拿 counter 范例举例子,有些小白就不会迁移了。这里我们着眼于能顺利的跑通一个自己 写的程序,一步一步的讲解,如果你是一个初学者,这再适合你不过了,虽然貌似字写得比 较多,那是因为写得相当的详细,一看就会啦 O(∩_∩)O~

版权所有,翻录必究!

天津大学

软件问题。其实只是没保存。

电子信息工程学院

戴鹏

2、写测试程序(testbench):每一个主程序(实现我们需要的某种功能的程序) ,都要 配套的编写一个测试程序,为什么?这里不打算细说,testbench 是给主程序提供时钟和 信号激励,使其正常工作,产生波形图,具体请参看 verilog 教课书。 在 half_clk.v 下方的空白区域内右键,选择 Add to Project New File

modelsim详细使用教程(一看就会)

Modelsim详细使用方法很多的modelsim教程中都讲得很丰富,但忽视了对整个仿真过程的清晰解读,而且都是拿counter范例举例子,有些小白就不会迁移了。

这里我们着眼于能顺利的跑通一个自己写的程序,一步一步的讲解,如果你是一个初学者,这再适合你不过了,虽然貌似字写得比较多,那是因为写得相当的详细,一看就会啦O(∩_∩)O~一、建立工程1、在建立工程(project)前,先建立一个工作库(library),一般将这个library命名为work。

尤其是第一次运行modelsim时,是没有这个“work”的。

但我们的project 一般都是在这个work下面工作的,所以有必要先建立这个work。

File→new→library点击library后会弹出一个对话框,问是否要创建work,点击OK。

就能看见work.2、如果在library中有work,就不必执行上一步骤了,直接新建工程。

File→new→project会弹出在Project Name中写入工程的名字,这里我们写一个二分频器,所以命名half_clk,然后点击OK。

会出现由于我们是要仿一个自己写的程序,所以这里我们选择Create New File。

在File Name中写入文件名(这里的file name和刚刚建立的project name可以一致也可以不一致)。

注意Add file as type 要选择成Verilog(默认的是VHDL),然后OK。

发现屏幕中间的那个对话框没有自己消失,我们需要手动关闭它,点close。

并且在project中出现了一个half_clk.V的文件,这个就是我们刚刚新建的那个file。

这样工程就建立完毕了。

二、写代码:1、写主程序:双击half_clk.v文件会出现程序编辑区,在这个区间里写好自己的程序,这里我们写一个简单的二分频的代码:module half_clk_dai(clk_in,rst,clk_out);input clk_in;input rst;output clk_out;reg clk_out;always @(posedge clk_in or negedge rst)beginif(!rst)clk_out<=0;elseclk_out<=~clk_out;endendmodule写完代码后,不能马上就编译,要先保存,否则,编译无效。

modelsim使用方法

Using ModelSim to Simulate LogicCircuits for Altera FPGA Devices1IntroductionThis tutorial is a basic introduction to ModelSim,a Mentor Graphics’simulation tool for logic circuits.We show how to perform functional and timing simulations of logic circuits implemented by using Quartus II CAD software.The reader is expected to have the basic knowledge of Verilog hardware description language,and the Altera Quartus II CAD software.Contents:•Introduction to simulation•What is ModelSim?•Functional simulation using ModelSim•Timing simulation using ModelSim1 Altera Corporation-University ProgramSeptember20102BackgroundDesigners of digital systems are inevitably faced with the task of testing their designs.Each design can be composed of many modules,each of which has to be tested in isolation and then integrated into a design when it operates correctly.To verify that a design operates correctly we use simulation,which is a process of testing the design by applying inputs to a circuit and observing its behavior.The output of a simulation is a set of waveforms that show how a circuit behaves based on a given sequence of inputs.The generalflow of a simulation is shown in Figure1.Figure1.The simulationflow.There are two main types of simulation:functional and timing simulation.The functional simulation tests the logical operation of a circuit without accounting for delays in the circuit.Signals are propagated through the circuit using logic and wiring delays of zero.This simulation is fast and useful for checking the fundamental correctness of the designed circuit.The second step of the simulation process is the timing simulation.It is a more complex type of simulation,where logic components and wires take some time to respond to input stimuli.In addition to testing the logical operation of the circuit,it shows the timing of signals in the circuit.This type of simulation is more realistic than the functional simulation;however,it takes longer to perform.2Altera Corporation-University ProgramSeptember2010In this tutorial,we show how to simulate circuits using ModelSim.You need Quartus II CAD software and ModelSim software,or ModelSim-Altera software that comes with Quartus II,to work through the tutorial.3Example DesignOur example design is a serial adder.It takes8-bit inputs A and B and adds them in a serial fashion when the g o input is set to1.The result of the operation is stored in a9-bit sum register.A block diagram of the circuit is shown in Figure2.It consists of three shift registers,a full adder,aflip-flop to store carry-out signal from the full adder and afinite state machine(FSM).The shift registers A andB are loaded with the values of A and B.After the st ar t signal is set high,these registers are shifted right one bit at a time.At the same time the least-significant bits of A and B are added and the result is stored into the shift register sum.Once all bits of A and B have been added,the circuit stops and displays the sum until a new addition is requested.Figure2.Block diagram of a serial-adder circuit.The Verilog code for the top-level module of this design is shown in Figure3.It consists of the instances of the shift registers,an adder and afinite state machine(FSM)to control this design.3 Altera Corporation-University ProgramSeptember20101.module serial(A,B,start,resetn,clock,sum);2.input[7:0]A,B;3.input resetn,start,clock;4.output[8:0]LEDR;5.6.//Registers7.wire[7:0]A_reg,B_reg;8.wire[8:0]sum;9.reg cin;10.11.//Wires12.wire reset,enable,load;13.wire bit_sum,bit_carry;14.15.//Confrol FSM16.FSM my_control(start,clock,resetn,reset,enable,load);17.18.//Datapath19.shift_reg reg_A(clock,1’b0,A,1’b0,enable,load,A_reg);20.shift_reg reg_B(clock,1’b0,B,1’b0,enable,load,B_reg);21.22.//a full adder23.assign bit_carry,bit_sum=A_reg[0]+B_reg[0]+cin;24.25.always@(posedge clock)26.begin27.if(enable)28.if(reset)29.cin<=1’b0;30.else31.cin<=bit_carry;32.end33.34.shift_reg reg_sum(clock,reset,9’d0,bit_sum,enable,1’b0,sum);35.defparam reg_sum.n=9;36.endmoduleFigure3.Verilog code for the top-level module of the serial adder.The Verilog code for the FSM is shown in Figure4.The FSM is a3-state Mealyfinite state machine,where thefirst and the third state waits for the st ar t input to be set to1or0,respectively.The computation of the sum of A and B4Altera Corporation-University ProgramSeptember2010happens during the second state,called WORK_STATE.The FSM completes computation when the counter reachesa value of8,indicating that inputs A and B have been added.The state diagram for the FSM is shown in Figure5.1.module FSM(start,clock,resetn,reset,enable,load);2.parameter WAIT_STATE=2’b00,WORK_STATE=2’b01,END_STATE=2’b11;3.input start,clock,resetn;4.output reset,enable,load;5.6.reg[1:0]current_state,next_state;7.reg[3:0]counter;8.9.//next state logic10.always@(*)11.begin12.case(current_state)13.WAIT_STATE:14.if(start)next_state<=WORK_STATE;15.else next_state<=W AIT_STATE;16.WORK_STATE:17.if(counter==4’d8)next_state<=END_STATE;18.else next_state<=WORK_STATE;19.END_STATE:20.if(∼start)next_state<=W AIT_STATE;21.else next_state<=END_STATE;22.default:next_state<=2’bxx;23.endcase24.end25.26.//state registers and a counter27.always@(posedge clock or negedge resetn)28.begin29.if(∼resetn)30.begin31.current_state<=W AIT_STATE;32.counter=’d0;33.end34.else35.beginFigure4.Verilog code for the FSM to control the serial adder(Part a).5 Altera Corporation-University ProgramSeptember201036.current_state<=next_state;37.if(current_state==W AIT_STATE)38.counter<=’d0;39.else if(current_state==WORK_STATE)40.counter<=counter+1’b1;41.end42.end43.//Outputs44.assign reset=(current_state==WAIT_STATE)&start;45.assign load=(current_state==W AIT_STATE)&start;46.assign enable=load|(current_state==WORK_STATE);47.endmoduleFigure4.Verilog code for the FSM to control the serial adder(Part b).Figure5.State diagram.The Verilog code for the shift register is given in Figure6.It consists of synchronous control signals to allow data to be loaded into the shift register,or reset to0.When enable input is set to1and the data is not being loaded or reset, the contents of the shift register are moved one bit to the right(towards the least-significant bit).6Altera Corporation-University ProgramSeptember20101.module shift_reg(clock,reset,data,bit_in,enable,load,q);2.parameter n=8;3.4.input clock,reset,bit_in,enable,load;5.input[n-1:0]data;6.output reg[n-1:0]q;7.8.always@(posedge clock)9.begin10.if(enable)11.if(reset)12.q<=’d0;13.else14.begin15.if(load)16.q<=data;17.else18.begin19.q[n-2:0]<=q[n-1:1];20.q[n-1]<=bit_in;21.end22.end23.end24.endmoduleFigure6.Verilog code for the shift register.The design is located in the example/functional and example/timing subdirectories provided with this tutorial.A Quartus II project for this design has been created as well.In the following sections,we use the serial adder example to demonstrate how to perform simulation using Mod-elSim.We begin by describing a procedure to perform a functional simulation,and then discuss how to perform a timing simulation.4Functional Simulation with ModelSimWe begin this tutorial by showing how to perform a functional simulation of the example design.We start by opening the ModelSim program.7 Altera Corporation-University ProgramSeptember2010Figure7.ModelSim window.The ModelSim program window,shown in Figure7,consists of four sections:the main menu at the top,a set of workspace tabs on the left,a work area on the right,and a command prompt at the bottom.The menu is used to access functions available in ModelSim.The workspace contains a list of modules and libraries of modules available to you,as well as details of the project you are working on.The work area on the right is the space where windows containing waveforms and/or textfiles will be displayed.Finally,the command prompt at the bottom shows feedback from the simulation tool and allows users to enter commands.To perform simulation with ModelSim follow a basicflow shown in Figure1.We begin by creating a project where all designfiles to be simulated are included.We compile the design and then run the simulation.Based on the results of the simulation,the design can be altered until it meets the desired specifications.4.1Creating a ProjectTo create a project in ModelSim,select New>Project...from the File menu.A create project window shown in Figure8will appear.8Altera Corporation-University ProgramSeptember2010Figure8.Creating a new project.The create project window consists of severalfields:project name,project location,default library name,and copy settingsfield.Project name is a user selected name and the location is the directory where the sourcefiles are located.For our example,we choose the project name to be serial,to match the top-level module name of our example design,and the location of the project is the example/functional subdirectory.The default library namefield specifies a name by which ModelSim catalogues designs.For example,a set offiles that describe the logical behaviour of components in an Altera Cyclone II device are stored in the cycloneii library. This allows the simulator to include a set offiles in simulation as libraries rather than individualfiles,which is particularly useful for timing simulations where device-specific data is required.For the purpose of this tutorial, specify tutorial as the library name for your project.The lastfield in the create project window is the copy settingsfield.This allows default settings to be copied from the initializationfile and applied to your project.Now,click OK to proceed to addfiles to the project using the window shown in Figure9.Altera Corporation-University Program September20109Figure9.Add afile to project window.The window in Figure9gives several options to addfiles to the project,including creating newfiles and directories, or adding existingfiles.Since thefile for this tutorial exists,click Add Existing File and select serial.vfile.Once thefile is added to the project,it will appear in the Project tab on the left-hand side of the screen,as shown in Figure10.Figure10.Workspace window after the project is created.Now that all designfiles have been included in the project,click Close to close the window in Figure9.10Altera Corporation-University ProgramSeptember20104.2Compiling a ProjectOnce the project has been created,it is necessary to compile pilation in ModelSim checks if the project files are correct and creates intermediate data that will be used during simulation.To perform compilation,select Compile All from the Compile menu.When the compilation is successful,a green check mark will appear to the right of the serial.vfile in the Project tab.4.3SimulationTo begin a simulation of the design,the software needs to be put in simulation mode.To do this,select Start Simulation...from the Simulate menu.The window in Figure11will appear.Figure11.Start simulation mode in ModelSim.The window to start simulation consists of many tabs.These include a Design tab that lists designs available for simulation,VHDL and Verilog tabs to specify language specific options,a Library tab to include any additional libraries,and timing and other options in the remaining two tabs.For the purposes of the functional simulation,we only need to look at the Design tab.In the Design tab you will see a list of libraries and modules you can simulate.In this tutorial,we want to simulate a module called serial,described in serial.vfile.To select this module,scroll down and locate the tutorial library and click on the plus(+)sign.You will see three modules available for simulation:FSM,serial,and shift_reg.Select the serial module,as shown in Figure11and click OK to begin simulation.When you click OK,ModelSim will begin loading the selected libraries and preparing to simulate the circuit.For the example in this tutorial,the preparation should complete quickly.Once ModelSim is ready to simulate your design, you will notice that several new tabs on the left-hand side of the screen and a new Objects window have appeared, as shown in Figure12.Figure12.New displays in the simulation mode.A key new tab on the left-hand side is the sim tab.It contains a hierarchical display of design units in your circuit in a form of a table.The columns of the table include the instance name,design unit and design unit type names. The rows of the table take a form of an expandable tree.The tree is rooted in the top-level entity called serial.Each module instance has a plus(+)sign next to its name to indicate it can be expanded to allow users to examine the contents of that module instance.Expanding the top-level entity in this view gives a list of modules and/or constructs within it.For example,in Figure12the top-level entity serial is shown to contain an instance of the FSM module,called my_control,three instances of a shift_reg module,four assign statements and an always block.Double-clicking on any of the constructs will cause ModelSim to open a sourcefile and locate the given construct within it.Double-clicking on a module instance will open a sourcefile and point to the description of the module in the sourcefile.In addition to showing modules and/or constructs,the sim tab can be used to locate signals for simulation.Notice that when the serial module is highlighted,a list of signals(inputs,outputs and local wires)is shown in the Objects window.The signals are displayed as a table with four columns:name,value,kind and mode.The name of a signal may be preceded by a plus(+)sign to indicate that it is a bus.The top-level entity comprises signals A,B,resetn, start,and clock as inputs,a sum output and a number of internal signals.12Altera Corporation-University ProgramWe can also locate signals inside of module instances in the design.To do this,highlight a module whose signals you wish to see in the Objects window.For example,to see the signals in the my_control instance of the FSM module, highlight the my_control instance in the sim tab.This will give a list of signals inside of the instance as shown in Figure13.Figure13.Expanded my_control instance.Using the sim tab and the Objects window we can select signals for simulation.To add a signal to simulation, right-click on the signal name in the Objects window and select Add>T o Wave>Selected items from the pop-up ing this method,add signals A,B,clock,resetn,start,sum,and current_state to the simulation.When you do so,a waveform window will appear in the work area.Once you have added these signals to the simulation, press the Undock button in the top-right corner of the waveform window to make it a separate window,as shown in Figure14.Figure14.A simulation window.Before we begin simulating the circuit,there is one more useful feature worth noting.It is the ability to combine signals and create aliases.It is useful when signals of interest are not named as well as they should be,or the given names are inconvenient for the purposes of simulation.In this example,we rename the start signal to go by highlighting the start signal and selecting Combine Signals...from the Tools menu.The window in Figure15will appear.14Altera Corporation-University Programbine signals window.In the textfield labeled Result name type go and press the OK button.This will cause a new signal to appear in the simulation window.It will be named go,but it will have an orange diamond next to its name to indicate that it is an alias.Once the go alias is created,the original start input is no longer needed in the simulation window,so removeit by highlighting it and pressing the delete key.Your simulation window should now look as in Figure16.Figure16.Simulation window with aliased signals.Now that we set up a set of signals to observe we can begin simulating the circuit.There are two ways to run a simulation in ModelSim:manually or by using scripts.A manual simulation allows users to apply inputs and advance the simulation time to see the results of the simulation in a step-by-step fashion.A scripted simulation allows the user to create a script where the sequence of input stimuli are defined in afile.ModelSim can read thefile and apply input stimuli to appropriate signals and then run the simulation from beginning to end,displaying results only when the simulation is completed.In this tutorial,we perform the simulation manually.In this simulation,we use a clock with a100ps period.At every negative edge of the clock we assign new values to circuit inputs to see how the circuit behaves.To set the clock period,right-click on the clock signal and select Clock...from the pop-up menu.In the window that appears,set the clock period to100ps and thefirst edge to be the falling edge,as shown in Figure17.Then click OK.16Altera Corporation-University ProgramFigure17.Set the clock period.We begin the simulation be resetting the circuit.To reset the circuit,set the resetn signal low by right-clicking on it and selecting the Force...option from the pop-up menu.In the window that appears,set Value to0and click OK. In a similar manner,set the value of the go signal to0.Now that the initial values for some of the signals are set,wecan perform thefirst step of the simulation.To do this,locate the toolbar buttons shown in Figure18.The toolbar buttons shown in Figure18are used to step through the simulation.The left-most button is the restartbutton,which causes the simulation window to be cleared and the simulation to be restarted.The textfield,shownwith a100ps string inside it,defines the amount of time that the simulation should run for when the Run button(tothe right of the textfield)is pressed.The remaining three buttons,Continue,Run-All and Break,can be used toresume,start and interrupt a simulation,respectively.We will not need them in this tutorial.To run a simulation for100ps,set the value in the textfield to100ps and press the Run button.After the simulationrun for100ps completes,you will see the state of the circuit as shown in Figure19.Figure19.Simulation results after100ps.In thefigure,each signal has a logic state.Thefirst two signals,A and B,are assigned a value between0and1in a blue color.This value indicates high impedance,and means that these signals are not driven to any logic state.The go and resetn signals is at a logic0value thereby resetting the circuit.The clock signal toggles state every50ps, starting with a falling edge at time0,a rising edge at time50ps and another falling edge at100ps.Now that the circuit is reset,we can begin testing to see if it operates correctly for desired inputs.To test the serial adder we will add numbers143and57,which should result in a sum of200.We can set A and B to143and57, respectively,using decimal notation.To specify a value for A in decimal,right-click on it,and choose Force... from the pop-up menu.Then,in the Valuefield put10#143.The10#prefix indicates that the value that follows is specified in decimal.Similarly,set the value of input_B to57.To see the decimal,rather than binary,values of buses in the waveform window we need to change the Radix of A and B to unsigned.To change the radix of these signals,highlight them in the simulation window and select Radix >Unsigned from the Format menu,as shown in Figure20.Change the radix of the sum signal to unsigned as well.18Altera Corporation-University ProgramFigure20.Changing the radix of A,B and sum signals.Now that inputs A and B are specified,set resetn to1to stop the circuit from resetting.Then set go to1to begin serial addition,and press the Run button to run the simulation for another100ps.The output should be as illustrated in Figure21.Notice that the values of inputs A and B are shown in decimal as is the sum.The circuit also recognizeda go signal and moved to state01to begin computing the sum of the two inputs.Figure21.Simulation results after200ps.To complete the operation,the circuit will require9clock cycles.To fast forward the simulation to see the result,specify900ps in the textfield next to the run button,and press the run button.This brings the simulation to time1100ps,at which point a result of summation is shown on the sum signal,as illustrated in Figure22.Figure22.Simulation results after1100ps.We can see that the result is correct and thefinite state machine controlling the serial adder entered state11,in which it awaits the go signal to become0.Once we set the go signal to0and advance the simulation by100ps,the circuit will enter state00and await a new set of inputs for addition.The simulation result after1200ps is shown inFigure23.Figure23.Simulation results after1200ps.At this point,we can begin the simulation for a new set of inputs as needed,repeating the steps described above.Wecan also restart the simulation by pressing the restart button to begin again from time0.By using the functional simulation we have shown that the serial.vfile contains an accurate Verilog HDL description20Altera Corporation-University Programof a serial adder.However,this simulation did not verify if the circuit implemented on an FPGA is correct.This is because we did not use a synthesized,placed and routed circuit as input to the simulator.The correctness of the implementation,including timing constraints can be verified using timing simulation.5Timing Simulation with ModelSimTiming simulation is an enhanced simulation,where the logical functionality of a design is tested in the presence of delays.Any change in logic state of a wire will take as much time as it would on a real device.This forces the inputs to the simulation be realistic not only in terms of input values and the sequence of inputs,but also the time when the inputs are applied to the circuit.For example,in the previous section we simulated the sample design and used a clock period of100ps.This clock period is shorter than the minimum clock period for this design,and hence the timing simulation would fail to produce the correct result.To obtain the correct result,we have to account for delays when running the simulation and use a clock frequency for which the circuit operates correctly.For Altera FPGA-based designs the delay information is available after the design is synthesized,placed and routed, and is generated by Quartus II CAD software.The project for this part of the tutorial has been created for you in the example/timing subdirectory.5.1Setting up a Quartus II Project for Timing Simulation with ModelSimTo perform timing simulation we need to set up Quartus II software to generate the necessary delay information for ModelSim by setting up EDA Tools for simulation in the Quartus II project.To set up EDA Tools for simulation, open the Quartus II project in example/timing subdirectory,and select Settings...from the Assignments menu.A window shown in Figure24will appear.The window in thefigure consists of a list on the left-hand side to select the settings category and a window area on the right-hand side that displays the settings for a given category.Select Simulation from the EDA Tool Settings category to see the screen shown on the right-hand side of Figure24.The right-hand side of thefigure contains the tool name at the top,EDA Netlist Writer settings in the middle,and NativeLink settings at the bottom.The tool name is a drop-down list containing the names of simulation tools for which Quartus II can produce a netlist with timing information automatically.This list contains many well-known simulation tools,including ModelSim.From the drop-down list select ModelSim-Altera.Once a simulation tool is selected,EDA Netlist Writer settings become available.These settings configure Quartus II to produce input for the simulation tool.Quartus II will use these parameters to describe an implemented design using a given HDL language,and annotate it with delay information obtained after compilation.The settings we can define are the HDL language,simulation time scale that defines time step size for the simulator to use,the location where the writer saves design and delay information,and others.For the purpose of this tutorial,only thefirst three settings are used.Set these settings to match those shown in Figure24and click OK.With the EDA Tools Settings specified,we can proceed to compile the project in Quartus II.The compilation process synthesizes,places,and routes the design,and performs timing analysis.Then it stores the compilation result in theFigure24.Quartus II EDA simulation tool settings.simulation directory for ModelSim to use.Take a moment to examine thefiles generated for simulation using a text editor.The two mainfiles are serial.vo,and serial_v.sdo.The serial.vofile is a Verilogfile for the design.Thefile looks close to the original Verilogfile,except that the design now contains a wide array of modules with a cycloneii_prefix.These modules describe resources on an Altera Cyclone II FPGA,on which the design was implemented using lookup tables,flip-flops,wires and I/O ports. The list delays for each module instance in the design is described in the serial_v.sdofile.22Altera Corporation-University Program5.2Running a Timing SimulationTo simulate the design using timing simulation we must create a ModelSim project.The steps are the same as in the previous section;however,the project is located in the example/timing/simulation/modelsim subdirectory,and the sourcefile is serial.vo.We do not need to include the serial_v.sdofile in the project,because a reference to it is included in the serial.vofile.Once you added the sourcefile to the project,compile it by selecting Compile All from the Compile menu.The next step in the simulation procedure is to place the ModelSim software in simulation mode.In the previous section,we did this by selecting Start Simulation...from the Simulate menu,and specifying the project name. To run a timing simulation there is an additional step required to include the Altera Cyclone II device library in the simulation.This library contains information about the logical operation of modules with cycloneii_prefix.To include the Cyclone II library in the project,select Start Simulation...from the Simulate menu and select the Library tab as shown in Figure25.Figure25.Including Altera Cyclone II library in ModelSim project.The Altera Cyclone II library is located in the altera/verilog/cycloneii directory in the ModelSim-Altera software. To add this library to your project,include the altera/verilog/cycloneii directory using the Add...button.Then,clickon the Design tab,select your project for simulation,and click OK.When the ModelSim software enters simulation mode,you will see a significant difference in the contents of the workspace tabs on the left-hand side of the window as compared to when you ran the functional simulation.In particular,notice the sim tab and the Objects window shown in Figure26.The list of modules in the sim tab is larger,and the objects window contains more signals.This is due to the fact that the design is constructed using components on an FPGA and is more detailed in comparison to an abstract description we used in the previous section of the tutorial.Figure26.Workspace tabs and Objects window for timing simulation.We simulate the circuit by creating a waveform that includes signals A,B,go,and resetn aliases as before.In addition,we include the clock,reg_sum|q,reg_A|q,and reg_B|q signals from the Objects window.Signals reg_A|q and reg_B|q are registers that store A and B at the positive edge of the clock.The reg_sum|q signal is a register that stores the resulting sum.Begin the simulation by resetting the circuit.To do this,set go and resetn signals to0.Also,set the clock input to have a period of20ns,whosefirst edge is a falling edge.To run the simulation,set the simulation step to20ns and press the Run button.The simulation result is shown in Figure27.24Altera Corporation-University Program。

ModelSim教程

微电子学实验室实验教程VerilogHDL/VHDL仿真器ModelSim实验2006-7西安交通大学微电子学实验室目录1. ModelSim概览.......................................................................................错误!未定义书签。

2.基本的使用步骤 (3)2.1 建立ModelSim库(物理库) (3)2.2 建立工程管理 (3)2.3 编译源代码 (6)2.4 启动仿真器 (7)2.5 运行仿真器 (9)3.ModelSim的用户界面 (13)3.1 ModelSim的Debug窗口 (13)3.2 Main窗口 (13)3.3 Wave窗口 (15)3.4 Process窗口 (16)3.5 Objects窗口 (17)3.6 Locals窗口 (17)3.7 Watch窗口 (18)3.8 List窗口 (18)3.9 Dataflow窗口 (19)3.10 ModelSim调试窗口特点 (20)4.功能仿真和时序仿真 (21)4.1 功能仿真 (21)4.2 时序仿真 (24)5.高级功能 (28)5.1 波形追踪(ChaseX) (28)5.2 代码覆盖(Code Coverage) (32)ModelSim实验1. 前言ModelSim仿真软件是由MentorGraphic公司的子公司Model技术公司开发的工业界上最为通用的仿真器之一,它可以用于Verilog仿真,VHDL仿真或者两者的混合仿真。

ModelSim仿真软件产品的类型很多,我们在这里要介绍的是ModelSim/SE,它是ModleSim主要的版本,功能最为强大,包含了ModelSim/PLUS的所有功能及其附加功能。

ModelSim/SE随着时间的推移不断地推出新的版本,我们要介绍的是Mentor Graphis公司于2005年6月推出的ModelSim/Se 6.1版本的使用。

modelsim使用教程

modelsim使用教程Modelsim6.0使用教程Modelsim简介Modelsim仿真工具是Model公司开发的。

它支持Verilog、VHDL以及他们的混合仿真,它可以将整个程序分步执行,使设计者直接看到他的程序下一步要执行的语句,而且在程序执行的任何步骤任何时刻都可以查看任意变量的当前值,可以在Dataflow窗口查看某一单元或模块的输入输出的连续变化等,比Quartus自带的仿真器功能强大的多,是目前业界最通用的仿真器之一。

ModelSim分几种不同的版本:SE、PE和OEM,其中集成在Actel、Atmel、Altera、Xilinx以及Lattice等FPGA厂商设计工具中的均是其OEM版本。

比如为Altera提供的OEM版本是ModelSim-Altera,为Xilinx提供的版本为ModelSimXE.SE版本为最高级版本,在功能和性能方面比OEM版本强很多,比如仿真速度方面,还支持PC、UNIX、LIUNX混合平台.为什么要学Modelsim?1.Modelsim是专业的HDL语言仿真器,比Quartus自带的仿真器功能强大的多.2.Quartussimulator不支持Testbench,只支持波形文件.vwfvwf文件全称是矢量波形文件(VectorWaveformFile),是QuartusII中仿真输入、计算、输出数据的载体。

一般设计者建立波形文件时,需要自行建立复位、时钟信号以及控制和输入数据、输出数据信号等。

其中工作量最大的就是输入数据的波形录入。

比如要仿真仅1KB的串行输入数据量,则手工输入信号的波形要画8000个周期,不仅费时费力而且容易出错怎样入门?对于初学者,modelsim自带的教程是一个很好的选择,在Help->SEPDF Documentation->Tutorial里面.它从简单到复杂、从低级到高级详细地讲述了modelsim的各项功能的使用,简单易懂。