理工毕业论文ISP技术在高速数据采集模块中的应

CPLD在高速数据采集系统中的应用

CPLD在高速数据采集系统中的应用是复杂的PLD,专指那些集成规模大于1000门以上的可编程规律器件。

它由与阵列、或阵列、输入缓冲、输出宏单元组成,具有门电路集成度高、可配置为多种输入输出形式、多时钟驱动、内含ROM或FLASH(部分支持在系统编程)、可加密、低、低功耗以及支持混合编程技术等突出特点。

而且CPLD的规律单元功能强大,普通的规律在单元内均可实现,因而其互连关系容易,电路的延时就是单元本身和集总的延时(通常在数纳秒至十数纳秒),并且可以预测。

所以CPLD比较适合于规律复杂、输入变量多但对触发器的需求量相对较少的规律型系统。

MAX7000系列产品与高速数据采集系统的要求相符,非常适合于高速设计。

由MAX7000系列CPLD设计的高速数据采集系统已经应用在电力系统某精确故障定位系统中。

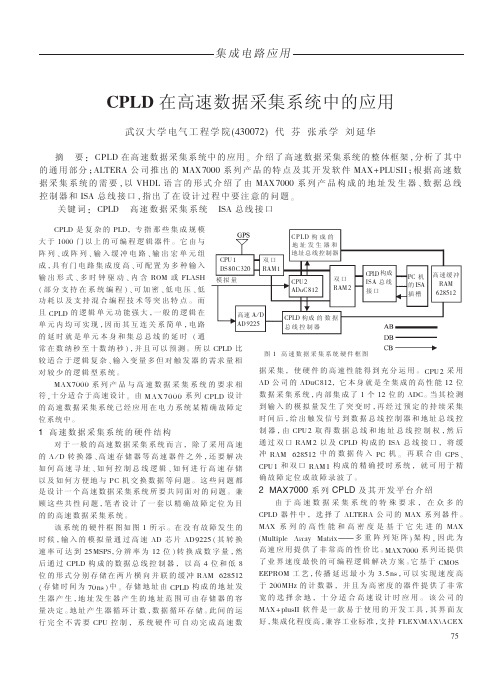

1 高速数据采集系统的硬件结构对于普通的高速数据采集系统而言,除了采纳高速的A/D转换器、高速存储器等高速器件之外,还要解决如何高速寻址、如何控制总线规律、如何举行高速存储以及如何便利地与PC机交换数据等问题。

这些问题都是设计一个高速数据采集系统所要共同面向的问题。

兼顾这些个性问题,笔者设计了一套以精确故障定位为目的的高速数据采集系统。

该系统的硬件框图1所示。

在没有故障发生的时候,输入的模拟量通过高速AD芯片AD9225(其转换速率可达到25MSPS,辨别率为12位)转换成数字量,然后通过CPLD构成的数据总线控制器,以高4位和低8位的形式分离存储在两片横向并联的缓冲RAM 628512(存储时光为70ns)中。

存储地址由CPLD构成的地址发生器产生,地址发生器产生的地址范围可由存储器的容量打算。

地址产生器循环计数,数据循环存储。

此间的运行彻低不需要CPU控制,系统硬件可自动完成高速数据采集,使硬件的高速性能得到充分运用。

CPU2采纳AD公司的AduC812,它本身就是全集成的高性能12位数据采集系统,内部集成了1个12位的。

基于cpld的高速数据采集系o

基于cpld的高速数据采集系统丁炜(河北省秦皇岛市职业技术学校,河北秦皇岛 066209)摘要:在超声波探伤中,超声波频率很高。

指出了超声波探伤面临的主要问题,提出了应用单片机加CPLD的结构,进行高速采样,并通过特殊算法,将采集数据进行存储的解决方案。

关键词:单片机;CPLD;高速数据;采集;存储在数据采集系统中,数据的高速采集及数据的存储一直是困扰科研人员的一个问题。

科研人员面临如何准确采集高速数据、如何存储数据等诸多问题。

利用超声波探伤就是高速数据采集及存储的一个典型实例。

1 超声波探伤面临的主要问题1.1 采样系统的设计难度众所周知,超声波的频率在20kHz以上。

超声波本身频率很高,这样对数据采集的速度要求很高。

应用超声波探伤,对超声波频率的要求更高,为能够远距离探伤,甚至要求超声波的频率达到几兆赫兹。

这样,我们就需要更高的采样频率进行采样。

这给设计采样系统带来了极大的难度。

1.2 高速数据采集所得庞大的数据如何处理在高速数据采集系统中,不但要面临高速采样问题,而且对高速数据采集所得到的庞大数据的处理是设计师面临的更大难题。

目前比较先进的单片机的时钟频率也就达到几十兆Hz,而真正的指令周期最高也就能达到10MHz左右。

处理数据不是几条指令可以完成的。

这样带来的直接后果就是单片机的速度无法满足高速数据的处理。

1.3 处理后的数据如何进行实时存储数据存储器分为掉电保持数据和掉电丢失数据两种存储器。

掉电保持存储器速度较慢,无法满足高速存储问题。

掉电丢失的存储器,虽然存储数据很快,但是无法保持数据,这样采集的数据在系统断电后就会丢失。

而从现场情况来看,超声波探伤设备需要能够长时间存储探伤数据,以供日后校对。

这样,就要求探伤设备不但能够高速存储数据,还要求数据能够在一起掉电后长久保持数据。

2 超声波探伤技术的解决方案2.1 结构图为解决以上问题,提出如下结构图:作者简介:丁炜(1980),男,学历:本科,职称:中教二级,职务:教师,研究方向:单片机应用。

基于CPLD的高速数据采集系统的设计与实现

基于CPLD的高速数据采集系统的设计与实现摘要:高速数据采集系统在信息科学的各个领域中应用越来越广泛,而基于单片机、ARM的数据采集技术已经很成熟,在对速度要求越来越苛刻的当代社会,这些技术已经显得有些力不从心,我们必须开发新的更高速的数据采集系统才能跟上信息产业发展的脚步,而随着可编程逻辑器件这些年来的迅猛发展,它以其极高的集成度,稳定的性能以及高速、易用的特点,在信息科学的各个领域都得到了广泛的应用,本文提出了一种基于CPLD的高速数据采集系统的设计方法。

关键词:基于CPLD;高速数据;采集系统;设计与实现1、前言数据采集技术是数字系统的重要部分,它与传感器技术、信号处理技术、计算机技术一起构成了现代检测技术的基础。

目前数据采集系统已经被广泛的应用。

在很多实际应用中,传统的采集系统已经不能满足采集要求,需要采样速度很高的甚至是超高采集系统。

本文提出了一种基于CPLD的高速数据采集系统的设计方法。

通过CPLD控制数据连续采集、缓冲,然后通过MCU(C8051F430)读取缓存在SRAM中数据,并且通过USB2.0将缓冲区数据转移到硬盘管理卡,由硬盘管理卡将数据存入海量硬盘。

再利用PC机的强大数据处理功能,MicrosoftVisualC++6.0的MFC类库,设计出一套集数据采集、处理和分析的高速数据采集的可视化系统。

2、系统结构设计本文设计的高速数据采集系统主要由数据采集、数据显示处理和数据传输接口三部分组成。

数据采集系统要解决的问题主要是数据的采集和传输问题。

为了增强设计的灵活性和可扩展性,系统采用CPLD来实现对AD转换器、数据缓存器SRAM、时钟、数据传输的控制逻辑。

系统功能框图如图1。

图1如上图所示,数据采集方案采用的是:带USB2.0控制器的高速单片机+USB传输的方式,目前有一款非常好的自带USB2.0控制器,并且具有51内核的高效率单片机C8051F340,这款单片机的执行速度可达到25MHz,且不用分频,故选用它可高速传输数据到PC机的同时,还可以对RAM进行读取控制。

DSP-CPLD和单片机高速数据采集装置设计论文

DSP\CPLD和单片机高速数据采集装置设计研究分析摘要:数据采集的速度不断的需要提高,为了满足对频率和分辨率技术上的要求,利用dsp、cpld及单片机技术构建一种高速采集装置。

下面就以这些电器元件为核心设计了一个高速信息采集装置。

关键词:dsp;cpld;分组处理;系统构成;usb选择中图分类号:tp274.2 文献标识码:a文章编号:1007-9599 (2011) 24-0000-01dsp, cpld and mcu high-speed data acquisition device design research and analysissheng zhen,niu dou(northeast dianli university,jilin132012,china)abstract:data acquisition speed constant need to improve,in order to meet the frequency and resolution of technical requirements,the use of dsp,cpld and single chip computer technology to build a high-speed acquisition device.here’s to the electrical components as the core to design a high speed data acquisition device.keywords: dsp;cpld;packet processing;systemstructure;usb selection一、dsp、cpld及单机片数据采集装置的组成目前电子技术不断发展,人们对自动化数据处理与采集的频率和分辨率都提出了更加严格的要求,因此高速度的数据采集装置就成为了需求的热点。

《利用FIFO的高速数据采集系统设计》毕业论文

《利用FIFO的高速数据采集系统设计》毕业论文————————————————————————————————作者:————————————————————————————————日期:吴轩昂 070105432王利 机电工程学院 探测制导与控制技术毕业设计说明书利用FIFO 的高速数据采集系统设计学生姓名: 学号:学 院:专 业:指导教师:2011 年 5 月利用FIFO的高速数据采集系统设计摘要高速数据采集存储技术在通信、航天、气象等领域中有广泛的应用。

随着各领域的不断发展,对数据采集的速率及容量要求越来越高。

高速数据采集主要包括数据接收与存储、串口总线应用、程序驱动等,实时、高速、连续、大量地采集存储数据.寻找一种使用方便的A/D转换器件,通过简单FIFO电路在单片机的控制下得到性能优良的高速数据采集系统,是本次设计的目标.本文介绍了本项研究目标与总体现状,在国民经济中的实用价值。

正文部分给出了系统设计中利用单片机控制下的FIFO电路的必要的理论分析及实验装置。

最后总结了本次的设计工作,指出进一步研究的方向.【关键词】:高速数据采集,A/D转换,FIFO,单片机High—speed Data Acquisition &Storage System using FIFOAbstractHigh—speed data acquisition & storage systems is widely used in many fields such as communication,navigation and meteorology.As the developing of the science technology in many fields,data storage systems of high—speed and large capacity have been increasingly focused.High-speed data acquisition & storage systems involves lots of key technologies such as data acquisition and storage,computer bus application and driver programming,with many critical issues such as high-speed,real-time,large capacity and continuation.Designing a high performance high—speed data acquisition system using A/D conversion chip and easy FIFO-circuit under control of a microcontroller is the target of this design.个人收集整理,勿做商业用途本文为互联网收集,请勿用作商业用途The purpose ,the situation of current data acquisition field , and its value in our social economy is discussed.In the main passage,the necessary way by using a FIFO with a microcontroller to analysis and testing is given. The general work of this paper is summarized, and the further research direction is pointed out at last.【Keywords】:High-speed data acquisition & storage,A/D conversion,FIFO,microcontroller目录1 引言 01.1 研究背景与意义 01。

高速数据采集与处理系统设计与验证研究

高速数据采集与处理系统设计与验证研究摘要:高速数据采集与处理系统在许多领域中具有重要的应用,如通讯、工业控制、医疗诊断等。

本文旨在通过设计与验证研究,探讨高速数据采集与处理系统的各个组成部分及其相互之间的关系,以及如何优化系统性能。

该研究可为高速数据采集与处理系统的设计与应用提供理论依据和实践指导。

1. 引言高速数据采集与处理系统是指能够以高速率采集大量数据并进行实时处理的系统。

在许多领域中,如科学研究、工业控制、医疗诊断等,高速数据采集与处理系统都起着关键作用。

然而,由于数据量大、采样频率高,对系统的设计与验证提出了很大的挑战。

2. 高速数据采集系统设计高速数据采集系统的设计包括硬件和软件两个方面。

硬件方面主要包括采集设备的选择和配置、模拟电路设计、高速采样模块的设计等。

软件方面主要包括数据采集控制程序的设计和开发、数据传输协议的制定等。

2.1 采集设备的选择和配置在设计高速数据采集系统时,首先需要选择合适的采集设备。

常见的采集设备有采集卡、采集模块和数据采集仪器等。

根据实际需求,选择具有高采样率、高精度和稳定性的采集设备。

2.2 模拟电路设计模拟电路设计是高速数据采集系统设计的重要组成部分。

通过合理设计模拟电路,可以保证从传感器或信号源输入到采集设备的信号质量。

常见的模拟电路设计技术包括放大器设计、滤波器设计和抗干扰设计等。

2.3 高速采样模块的设计高速采样模块是高速数据采集系统中的核心部分,它负责将模拟输入信号转换为数字信号,并通过总线接口传输给处理部分。

高速采样模块的设计需要考虑采样率、分辨率、存储容量等因素,并采用合适的数模转换器和存储器。

3. 高速数据处理系统设计高速数据处理系统设计主要包括数据接收、数据处理和数据存储三个环节。

3.1 数据接收数据接收是指将高速采样模块采集到的数据传输到数据处理部分。

在数据接收过程中,需要考虑数据传输速率、数据稳定性和数据完整性等问题。

常见的数据传输技术有PCIe、USB和以太网等。

高速公路信息采集与处理技术研究

高速公路信息采集与处理技术研究随着社会和经济的发展,交通路网的建设不断扩大和提升。

其中高速公路的建设已经成为现代化交通网络建设的重要组成部分。

高速公路具有安全、快速、舒适等优点,是人们出行的首选交通方式。

为了满足人们对于高速公路行车安全与畅通的需求,信息技术在高速公路信息采集与处理方面的应用也不断推进,其意义重大。

一、高速公路信息采集技术信息采集是高速公路收集车辆运行状态和交通情况的基础,是智能交通系统运作的核心。

在高速公路上,信息采集技术应包括实时车流数采集、车速和密度采集、重载运输车辆数量采集、爆胎和撞击事故采集、违法行为采集等。

1.实时车流数采集技术实时车流数采集技术是通过调配采集设备,对车道内车辆进行实时车流数采集,以实现车流数实时监测和车辆通行速度、拥堵情况信息的采集。

车流量监测系统主要利用车流量检测器、地磁线圈、光电传感器和微波探测等技术手段,通过非接触、无感、无损和高精度等采集车辆数目和位置信息,可实现对车道内车辆进行实时的监测和计算。

2.车速和密度采集技术车速和密度采集技术是在实时车流数采集技术的基础上,衍生出的一种车辆信息采集技术,用于采集车辆通行速度和密度信息,并对车载GPS导航进行升级,利用手机APP等方式,提供车辆通行状态、路段拥堵情况和预测等信息。

3.重载运输车辆数量采集技术重载运输车辆数量采集技术是一种针对国道公路、高速公路等重载运输车辆密集路段的信息采集技术,可直观地为过路车辆提供当前高速公路通行情况。

采集技术一般采用图像识别、车牌识别技术、视频监控技术等,其数据可具有自动上传、存储、显示等功能。

4.爆胎、撞击事故信息采集技术爆胎和撞击事故信息采集技术主要是针对高速公路上由于轮胎爆炸、疲劳驾驶、刹车故障、侧翻等原因导致的路面事故进行信息采集和传递,信息采集技术一般为图像识别技术和视频监控技术。

5.违法行为信息采集技术违法行为信息采集技术是指利用卡口、视频监控、电子警察等黑科技手段,对高速公路上不遵守交通规则行为的车辆、驾驶人员等信息进行采集,以保证道路交通安全。

基于CPLD与单片机的高速数据采集系统[1]

![基于CPLD与单片机的高速数据采集系统[1]](https://img.taocdn.com/s3/m/89dcfa03bed5b9f3f90f1ccc.png)

邮局订阅号:82-946360元/年技术创新PLD CPLD FPGA 应用《PLC 技术应用200例》您的论文得到两院院士关注基于CPLD 与单片机的高速数据采集系统High Speed Data Acquisition System based on CPLD and MCU(江苏工业学院)万军何宝祥储开斌马正华WAN Jun HE Bao-xiang CHU Kai-bin MA Zheng-hua摘要:本文针对新型匝间耐压测试仪中需要高速采集数据的问题提出了一种结合CPLD 与单片机的高速数据采集系统设计方案。

CPLD 产生A/D 芯片的控制时序以及SRAM 的读写控制时序,单片机输出给CPLD 控制A/D 转换的启动信号,并通过CPLD 读取SRAM 中的采样数据。

该系统具有较好的可移植性。

关键词:数据采集;A/D 转换;SRAM;CPLD;单片机中图分类号:TP368文献标识码:BAbstract:Aiming at the acquisition data problem existing in the new turn -to -turn withstand voltage tester,this paper designs a high speed data acquisition system based on CPLD and MCU.CPLD generates the control timings for A/D chip and SRAM chip.MCU outputs the start signals to CPLD to control A/D conversion,reads the sampled data in SRAM via CPLD.This system can be used widely for high speed data acquisition.Key words:Data acquisition;A/D convert;SRAM;CPLD;MCU文章编号:1008-0570(2009)04-2-0225-031引言高速数据采集系统广泛应用于图像信号采集、雷达、软件无线电等技术领域。

CPLD在高速数据采集系统中的应用

" #$%&’’’ 系 列 ()*+ 及 其 开 发 平 台 介 绍

由于高速数据采集系统的特殊要求# 在众多的

!"0% 器 件 中 # 选 择 了 -0CD,- 公 司 的 .-< 系 列 器 件 ! .-< 系 列 的 高 性 能 和 高 密 度 是 基 于 它 先 进 的 .-<

&& 多 重 阵 列 矩 阵 O 架 构 # 因 此 为 E.1FGHIFJ -KKLM .LGKHN & 高 速 应 用 提 供 了 非 常 高 的 性 价 比 ! .-<=>>> 系 列 还 提 供 了 业 界 速 度 最 快 的 可 编 程 逻 辑 解 决 方 案 ! 它 基 于 !.9&

集成电路应用

!"#$ 在高速数据采集系统中的应用

武 汉 大 学 电 气 工 程 学 院 EUV>>WXO 代 芬 张 承 学 刘 延 华

要 ! !"0% 在 高 速 数 据 采 集 系 统 中 的 应 用 ! 介 绍 了 高 速 数 据 采 集 系 统 的 整 体 框 架 " 分 析 了 其 中 的 通 用 部 分 # -0CD,- 公 司 推 出 的 .-<W>>> 系 列 产 品 的 特 点 及 其 开 发 软 件 .-<S"0#&33 # 根 据 高 速 数 据 采 集 系 统 的 需 要 " 以 Y;%0 语 言 的 形 式 介 绍 了 由 .-<W>>> 系 列 产 品 构 成 的 地 址 发 生 器 $ 数 据 总 线 控 制 器 和 3&- 总 线 接 口 " 指 出 了 在 设 计 过 程 中 要 注 意 的 问 题 ! 关 键 词 ! !"0% 高速数据采集系统 摘

UBS高速数据采集系统论文

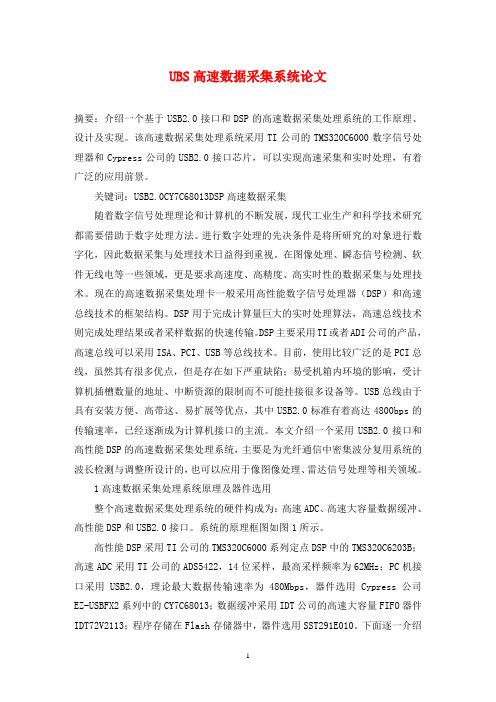

UBS高速数据采集系统论文摘要:介绍一个基于USB2.0接口和DSP的高速数据采集处理系统的工作原理、设计及实现。

该高速数据采集处理系统采用TI公司的TMS320C6000数字信号处理器和Cypress公司的USB2.0接口芯片,可以实现高速采集和实时处理,有着广泛的应用前景。

关键词:USB2.0CY7C68013DSP高速数据采集随着数字信号处理理论和计算机的不断发展,现代工业生产和科学技术研究都需要借助于数字处理方法。

进行数字处理的先决条件是将所研究的对象进行数字化,因此数据采集与处理技术日益得到重视。

在图像处理、瞬态信号检测、软件无线电等一些领域,更是要求高速度、高精度、高实时性的数据采集与处理技术。

现在的高速数据采集处理卡一般采用高性能数字信号处理器(DSP)和高速总线技术的框架结构。

DSP用于完成计算量巨大的实时处理算法,高速总线技术则完成处理结果或者采样数据的快速传输。

DSP主要采用TI或者ADI公司的产品,高速总线可以采用ISA、PCI、USB等总线技术。

目前,使用比较广泛的是PCI总线,虽然其有很多优点,但是存在如下严重缺陷;易受机箱内环境的影响,受计算机插槽数量的地址、中断资源的限制而不可能挂接很多设备等。

USB总线由于具有安装方便、高带这、易扩展等优点,其中USB2.0标准有着高达4800bps的传输速率,已经逐渐成为计算机接口的主流。

本文介绍一个采用USB2.0接口和高性能DSP的高速数据采集处理系统,主要是为光纤通信中密集波分复用系统的波长检测与调整所设计的,也可以应用于像图像处理、雷达信号处理等相关领域。

1高速数据采集处理系统原理及器件选用整个高速数据采集处理系统的硬件构成为:高速ADC、高速大容量数据缓冲、高性能DSP和USB2.0接口。

系统的原理框图如图1所示。

高性能DSP采用TI公司的TMS320C6000系列定点DSP中的TMS320C6203B;高速ADC采用TI公司的ADS5422,14位采样,最高采样频率为62MHz;PC机接口采用USB2.0,理论最大数据传输速率为480Mbps,器件选用Cypress公司EZ-USBFX2系列中的CY7C68013;数据缓冲采用IDT公司的高速大容量FIFO器件IDT72V2113;程序存储在Flash存储器中,器件选用SST291E010。

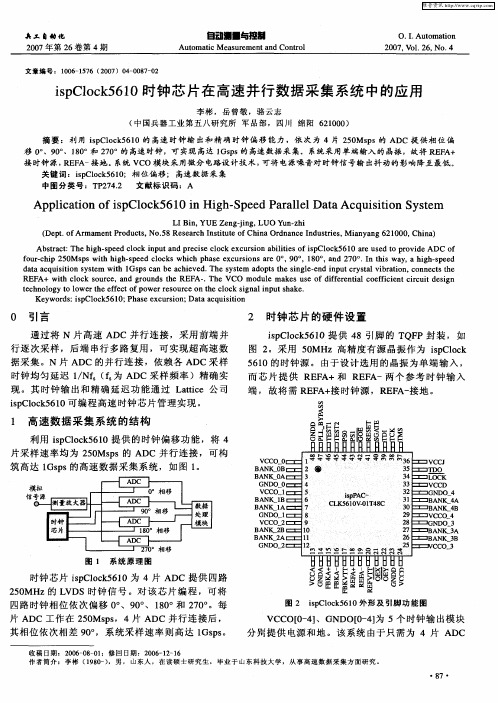

ispClock5610时钟芯片在高速并行数据采集系统中的应用

2 0 , o . 6 No 4 0 7 V 12 , .

i C ok 6 0时钟芯 片在 高速 并 行 数据 采 集 系统 中 的应 用 s lc 5 1 p

李 彬 , 岳 曾敬 ,骆 云 志 ( 国兵 器 工业 第 五八 研 究所 军 品 部 , 四川 绵 阳 6 1 0 ) 中 2 0 0

中图分 类号 :T 2 42 文 献标 识 码 :A P7 .

Ap l ai n o p o k 61 g — p e a a ll t q ii o y tm p i to fi Cl c 5 i Hi h S e d P r l c s n 0 e Da aAc u st n S se i

Ab t a t Th i h s e d c o k i p t n r c s l c x u s o b lt so p o k 6 0 a e u e o p o i e ADC f sr c : e h g . p e l c n u d p e ie c o k e c r i n a iii fi Cl c 5 1 r s d t r v d a e s o f u . h p 2 0 s s wi i h s e d c o ks wh c h s x u so s a e 0 ,9 。 8 。 n 7 。 n t i y i h s e d o rc i 5 M p t h g - p e l c i h p a e e c r i n r 。 0 ,1 0 ,a d 2 0 .I h s wa ,a h g . p e h d t c u sto y t m t G s s c n b c e d Th y t m d p st e sn l . n n u r s a i r to , o n c st e a a a q i ii n s se wih 1 p a e a hive . e s se a o t h i g e e d i p t y t l b a i n c n e t h c v

基于PCI总线的高速实时数据采集系统的设计

基于 &.’ 总线的高速实时数据采集系统的设计

基于 &.’ 总线的高速实时数据采集系统的设计

陈庚锋 吴顺君 王翠平 西安电子科技大学雷达信号处理国家重点实验室( =133=1 )

#$%&’()& ’T -UKL *+*VWXYV MVL,WKSV -UV MVLKZT +TM K)*[V)VT-+-K(T (\ UKZU]L*VVM WV+[ -K)V M+-+ +,IJKLK-K(T LHL-V) S+LVM (T &.’ SJLA^V MV+[ YK-U -UV MVLKZT (\ L-(W+ZV +TM -W+TL)KLLK(T (\ M+-+ +,IJKLK-K(T LHL-V)A *+,-.’/%_&.’ NJLX.&.’ NJLXCKZU F*VVM ‘V+[ <K)V 8+-+ 6,IJKLK-K(T FHL-V)XP’PEX.&>8

O

,5 转换 前 F 个周期 /

使能 &’&( 写允许 写时钟 .3-/、 信号 .012

/

传送 !H#< 长字结束

O

数据采集结束

/

O / &’&( 半满 信号 *& 有效 O / +0’AHB# 准备好

O

结束

!

数据采集系统控制和 "#$% 设计 对 &’&( 的控 0+15 对系统的控制包括对 ,5A"#! 的控制、

摘 解决方案以及该系统的控制逻辑的实现。

PCI总线接口技术及其在高速数据采集系统中的应用

PCI总线接口技术及其在高速数据采集系统中的应用数据采集是数字信号处理中非常重要的环节。

对于不同的任务,数据采集要达到的技术指标也不相同。

对于瞬态信号,雷达信号和图像处理都需要几MB/s 甚至几十MB/s 的超高速采集速率。

目前用于PC 机的数据采集卡大部分是基于ISA 总线的,这种结构的最大缺点是传输速率太低,不能实现数据的实现高速传输。

PCI 总线推出后,以其突出的性能备受计算机和通信业界的青睐,将取代以往的总线, 成为高档机及高性能工作站外部件的基石。

PCI 作为局部总线,一边与处理器和存储器总线接口;另一边为外设扩展提供了高速通道。

33MHz、32 位的PCI 总线可以实现132MB/s 的数据传输速率;64 位的PCI 总线性能加倍。

开发以PCI 总线为基础的数据采集设备是技术发展的必然要求。

在实际工作中,利用PCI 总线将采集数据直接传到系统内存,可有效解决数据的实时传输和存储,为信号的实时处理提供方便。

1 数据采集系统的结构与功能本数据采集系统应用于雷达视频回波信号的处理。

信号由两路正交视频回波信号组成,故采用双通道。

采集指标:2 路采集信号,采样率为40M 个样本, A/D 采样字长是10 位。

每路数字信号字长取16 位,两路合成路共32 位,将32 位数据分别传入系统内存的不同区域,以便后续处理。

系统设计以PCI 总线控制器为基础,通过DMA 方式分别将32 位数据传输系统内存的不同区域。

主要功能模块有:PCI 总线控制器、双口SRAM、采集控制芯片EPLD、A/D 部分。

系统框图如图1 所示。

2 PCI 总线控制器的实现PCI 总线是一个地址/数据、命令/字节选择信号复用的总线。

它采用主从。

光纤通信网络在高速数据采集系统中的应用

Ab s t r a c t A h i g h— s p e e d d a t a a c q u i s i t i o n s y s t e m i s d e s i g n e d b a s e d o n a n o p t i c a l i f b e r c o mmu n i c a t i o n n e t wo r k . By wa y o f mu l t i — c h a n n e l d a t a a c q u i s i t i o n, a n d c o mb i n e d wi t h ib f e r — o p t i c c o mmu n i c a t i o n s n e t wo r k, t h e h i g h — s p e e d

c e s s e d b y a n a l o g il f t e r a n d s a mp l i n g nd a t h e n t r a n s mi t t e d b y t h e p r o c e s s o r . Ex p e r i me n t s o n t h e o p t i c a l d a t a a c q u i s i —

a 叶技 2 0 1 5 年 第 2 8 卷 第2 期

El e c t r o n i c S c i . &T e c h . / F e b . 1 5. 2 0 1 5

光纤通信网络在高速数据采集系统中的应用

光纤通信网络在高速数据采集系统中的应用【摘要】随着科技的不断发展,光纤通信技术在高速数据采集系统中扮演着越来越重要的角色。

本文将从光纤通信技术的发展、高速数据采集系统的需求、光纤通信网络在高速数据采集系统中的优势、光纤传感器在高速数据采集系统中的应用以及光纤通信网络在高速数据采集系统中的实际应用等方面细致探讨。

通过分析这些内容,可以看到光纤通信网络在高速数据采集系统中具有巨大的潜力和优势。

未来,光纤通信网络在高速数据采集系统中的应用前景十分广阔,其重要性也日益凸显。

光纤通信网络将在高速数据采集系统中扮演着不可或缺的角色,为数据传输提供更快、更稳定、更可靠的解决方案。

【关键词】关键词:光纤通信网络、高速数据采集系统、优势、光纤传感器、应用、发展、重要性、应用前景1. 引言1.1 光纤通信网络在高速数据采集系统中的应用光纤通信网络在高速数据采集系统中起着至关重要的作用。

随着科技的进步和信息量的急剧增加,高速数据采集系统的需求变得日益迫切。

而光纤通信技术的发展为高速数据传输提供了强大的支持。

光纤通信网络具有高带宽、低延迟、抗干扰等优势,能够满足高速数据采集系统对数据传输速度和稳定性的要求。

光纤传感器的应用也使得数据采集更加精准和可靠,进一步提高了系统的性能和效率。

在实际应用中,光纤通信网络已经广泛应用于各种高速数据采集系统中,包括工业生产、医疗诊断、环境监测等领域。

未来,随着技术的不断进步,光纤通信网络在高速数据采集系统中的应用前景更加广阔,将为数据传输和采集系统带来更多创新和发展机遇。

光纤通信网络在高速数据采集系统中的重要性不言自明,它已经成为现代信息社会中不可或缺的一部分,并将继续发挥着重要的作用。

2. 正文2.1 光纤通信技术的发展光纤通信技术自问世以来,经历了多年的快速发展和不断创新,成为了现代通信领域中不可或缺的一部分。

光纤通信技术的发展主要包括以下几个方面:光纤通信技术的传输速度不断提升。

高速数据采集与信号处理

是ASIC和ASSP的替代品。

ASIC是用户根据某一专门应用设计的,ASSP是用来实现特定功能的器件。

由于大批量的生产采用了先进的工艺技术,使PLD的价格不断降低。

Altera公司提供的器件在集成度、密度、性能和成本方面都可与ASIC相比。

这些因素与产品投放市场的时间和可编程的灵活性相结合,不断地推动着高密度PLD在电子系统开发和生产中的应用。

在可编程逻辑器件的学习和使用中,我认识到可编程逻辑器件的学习和应用已不仅仅是单纯地基于某种特定器件的开发过程,而是一种极富挑战性和创造性的劳动,使目前许多处于计算机辅助设计(CAD)和规划的纯软件活动变成了实实在在的设计和实体,这些设计在计算机上仿真通过后,几乎即可应用于实际电路,大大地简化了设计方法和调试过程【”川。

3.3.2MAX7000系列在本设计中采用了Altera公司的EPM7128STCl00—15。

其内部逻辑控制框图见图3—11。

图3—11EPM7128STCl00-15结构方块图一30一为了调试方便,将内部模块间的某些输出关系也通过引脚引出,这样在时序仿真的时候便于测试、观察。

如地址计数器的控制引脚,象计数器使能EN_CNT、计数器复位RESET_CNT和计数器加一脉冲ADD—INC、计数器溢出ADD_FULL等内部、外部功能“引脚”,无论外部需要与否,都将其接至外部输出引脚以便测试、观察。

图3-13^D转换与存储控制模块和地址计数器模块框图(1)引脚及功能介绍详细连接图见图3—13。

BUTTON:数据采集开启/停止按钮信号输入端,高电平启动,低电平停止。

GBCLK:CPLD的全局时钟信号输入端,实验初期暂时采用20MHz,以免对于调试过程给予过高苛求。

ADCLK:CPLD输送给AD转换器的时钟节拍。

一35—。

最新-ISP技术在高速数据采集模块中的应 精品

ISP技术在高速数据采集模块中的应摘要提出了一种基于技术实现高速数据采集的方法,给出了使用语言和原理图完成数据采集模块中地址发生器和比较电路的部分逻辑设计,只要将所设计的程序下载到可编程器件2032中即可实现预期功能。

同时,2032器件的高密度和可编程性也提高了硬件电路的集成性、可靠性及保密性。

关键词在系统可编程;;高速采集;2032随着深亚微米及纳米半导体制造技术的进步,可编程逻辑器件在电路设计中的应用已十分广泛。

ISP在系统可编程器件是先进的可编程器件,范文先生网收集整理它的优点是不需要编程器即可直接对安装在用户目标板上的ISP器件进行编程,而且编程、调试都很方便。

当产品升级换代时,只要通过软件对ISP器件重新编程即可,便可使其具有新的逻辑功能,而不需要增加硬件投入。

目前,ISP芯片内部资源越来越多,速度也越来越快,开发的软件功能也更加完善。

VHDL就是随着PLD发展起来的一种硬件描述语言,是一种应用于电路设计的高层次描述语言。

本文将介绍一种在高速数据采集模块中部分电路采用ISP技术进行设计的方法。

1高速数据采集模块的实现高速数据采集模块的系统框图如图1所示。

括了地址信号产生、锁存、ADC转换数据的比较、数据存储器的读写控制以及-pLSI2032内部进行2分频以得到6MHz的采样时钟。

数据线和控制线。

两个端口可分别与ispLSI2032和单片机的P0口连接。

用is-pLSA/D转换数据写入RAM。

当A/D转换的数据超出某一上下限时,系统会将地址数据写入is-pL0口,单片机由此地址读出RAM中相应地址的数据,并通过RS232口传送到PC机或其它外设。

图2所示是该数据采集系统的基本硬件电路图。

图中的A/D转换芯片选用的是美国MAXIM公司的12位A/D转换器MAX120,它有全控制模式、独立模式、慢存储模式、ROM模式和连续转换模式5种工作模式。

在此电路中,MAX120工作于连续转换模式,由于MAX120芯片的MODE=DGND,因此,它的INT/BUSY为BUSY输出。

ISP技术在高速数据采集模块中的应用

ISP技术在高速数据采集模块中的应用

龚兰芳;张昱

【期刊名称】《国外电子元器件》

【年(卷),期】2004(000)006

【摘要】提出了一种基于ISP技术实现高速数据采集的方法,给出了使用VHDL语言和原理图完成数据采集模块中地址发生器和比较电路的部分逻辑设计,只要将所设计的程序下载到可编程器件is-pLSI2032中即可实现预期功能.同时,ispLSI2032器件的高密度和可编程性也提高了硬件电路的集成性、可靠性及保密性.

【总页数】4页(P64-67)

【作者】龚兰芳;张昱

【作者单位】武汉理工大学,湖北,武汉,430063;武汉理工大学,湖北,武汉,430063【正文语种】中文

【中图分类】TTN79+.1

【相关文献】

1.ISP技术及其在高速数据采集系统中的应用 [J], 肖俊武;许正望;陈文电

2.基于ISP技术的环形缓冲在高速数据采集系统中的应用 [J], 梁四洋;崔少辉

3.ISP技术及其在高速数据采集系统中的应用 [J], 庞彩霞;张谦

4.基于ISP技术的环形缓冲在高速数据采集系统中的应用 [J], 梁四洋;崔少辉

5.AD9480在高速数据采集模块中的应用 [J], 王丹;赵孔新

因版权原因,仅展示原文概要,查看原文内容请购买。

高速数据采集缓冲系统

高速数据采集缓冲系统

丁祖高

【期刊名称】《紫金山天文台台刊》

【年(卷),期】1991(010)002

【摘要】本文介绍一种在强噪声下弱信号检测中的高速数据采集缓冲系统.它具有速度高(10us),缓冲时间长(2.5h)、容量大(2K×32bit)等特点.能进行多种谱分析仪(如多通道滤波器、声表面波滤器、声光频谱分析仪等)及多路传感与计算机通信,本系统曾试用于紫台13.7m毫米波望远镜的AOS系统.

【总页数】6页(P151-156)

【作者】丁祖高

【作者单位】无

【正文语种】中文

【中图分类】P111.2

【相关文献】

1.基于ISP技术的环形缓冲在高速数据采集系统中的应用 [J], 梁四洋;崔少辉

2.基于ISP技术的环形缓冲在高速数据采集系统中的应用 [J], 梁四洋;崔少辉

3.基于环形缓冲区的高速数据采集系统 [J], 庄哲民;蔡清福

4.缓冲系统设计及缓冲性能测试 [J], 徐楠;王美娜;褚福常

5.缓冲系统设计及缓冲性能测试 [J], 徐楠;王美娜;褚福常

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ISP技术在高速数据采集模块中的应

随着深亚微米及纳米半导体制造技术的进步,可编程逻辑器

件在电路设计中的应用已十分广泛。

ISP(在系统可编程)器

件是先进的可编程器件,它的优点是不需要编程器即可直接对安

装在用户目标板上的ISP器件进行编程,而且编程、调试都很

方便。

当产品升级换代时,只要通过软件对ISP器件重新编程即可,便可使其具有新的逻辑功能,而不需要增加硬件投入。

目前,

ISP芯片内部资源越来越多,速度也越来越快,开发的软件功

能也更加完善。

VHDL就是随着PLD发展起来的一种硬件描

述语言,是一种应用于电路设计的高层次描述语言。

本文将介绍

一种在高速数据采集模块中部分电路采用ISP技术进行设计的

方法。

1高速数据采集模块的实现高速数据采集模块的系统框

图如图1所示。

图中的ispLSI2032是整个数据采集系

统的控制核心?它内部包括了地址信号产生、锁存、ADC转换数

据的比较、数据存储器的读写控制以及大部分控制逻辑?晶振电路

产生的12MHz时钟可直接在is-pLSI2032内部进行

2分频以得到6MHz的采样时钟。

高速数据缓存部分由两片S

RAM构成?该SRAM可提供自己的地址线、数据线和控制线。

两个端口可分别与ispLSI2032和单片机的P0口连接。

用is-pLSI2032可递增RAM的地址?同时可提供写入

脉冲以将A/D转换数据写入RAM。

当A/D转换的数据超出

某一上下限时,系统会将地址数据写入is-pLSI2032内

部的锁存器中?并在其后打开锁存,同时将地址送到单片机的P0口,单片机由此地址读出RAM中相应地址的数据,并通过RS

232口传送到PC机或其它外设。

图2所示是该数据采集系统

的基本硬件电路图。

图中的A/D转换芯片选用的是美国MAX

IM公司的12位A/D转换器MAX120,它有全控制模式、

独立模式、慢存储模式、ROM模式和连续转换模式5种工作模式。

在此电路中,MAX120工作于连续转换模式,由于MA

X120芯片的MODE=DGND,因此,它的INT/BU

SY为BUSY输出。

单片机启动转换时,INT/BUSY变

为低电平,同时将INT0(P3.2)置低,以使计数器的计

数状态与MAX120的INT/BUSY信号一致,也就是说,每转换完一次,计数器就加以产生新的存储器地址;转换结束后,INT/BUSY转变为高电平,数据在引脚D0~D11处有效,此时WE信号为低,存储器写端口打开,并将ADC所转换

的数据写入与计数器所产生地址对应的存储单元。

继而INT/

BUSY信号再次变低,MAX120进入下一次转换。

直到采

集的数据超出某一上下限,ADC模块中的比较器产生一信号使

单片机外部中断,进而转入中断数据处理。

其后单片机将读取存

储在锁存器中的地址信号,并将其存储;同时由此地址读出存储

在存储器中的超出上下限的数据。

单片机定时取数时,先将IN

T0(P3.2)置高,此时地址产生器的累加由单片机控制

(通过T0口,即P3.4)。

单片机控制计数器重新计数并产

生地址数据,产生的地址送到单片机P0口,并由此地址读取存

储器中相应地址的数据,最后通过RS232口传送到PC或其

它外设。

随着深亚微米及纳米半导体制造技术的进步,可编程逻辑器

件在电路设计中的应用已十分广泛。

ISP(在系统可编程)器

件是先进的可编程器件,它的优点是不需要编程器即可直接对安

装在用户目标板上的ISP器件进行编程,而且编程、调试都很

方便。

当产品升级换代时,只要通过软件对ISP器件重新编程即可,便可使其具有新的逻辑功能,而不需要增加硬件投入。

目前,ISP芯片内部资源越来越多,速度也越来越快,开

发的软件功能也更加完善。

VHDL就是随着PLD发展起来的

一种硬件描述语言,是一种应用于电路设计的高层次描述语言。

本文将介绍一种在高速数据采集模块中部分电路采用ISP技术

进行设计的方法。

1高速数据采集模块的实现

高速数据采集模块的系统框图如图1所示。

图中的ispL

SI2032是整个数据采集系统的控制核心?它内部包括了地址

信号产生、锁存、ADC转换数据的比较、数据存储器的读写控

制以及大部分控制逻辑?晶振电路产生的12MHz时钟可直接在

is-pLSI2032内部进行2分频以得到6MHz的采样时钟。

高速数据缓存部分由两片SRAM构成?该SRAM可提供自

己的地址线、数据线和控制线。

两个端口可分别与ispLSI

2032和单片机的P0口连接。

用is-pLSI2032可递

增RAM的地址?同时可提供写入脉冲以将A/D转换数据写入R

AM。

当A/D转换的数据超出某一上下限时,系统会将地址数

据写入is-pLSI2032内部的锁存器中?并在其后打开锁存,同时将地址送到单片机的P0口,单片机由此地址读出RA

M中相应地址的数据,并通过RS232口传送到PC机或其它

外设。

图2所示是该数据采集系统的基本硬件电路图。

图中的A/

D转换芯片选用的是美国MAXIM公司的12位A/D转换器

MAX120,它有全控制模式、独立模式、慢存储模式、RO

M模式和连续转换模式5种工作模式。

在此电路中,MAX12

0工作于连续转换模式,由于MAX120芯片的MODE=D

GND,因此,它的INT/BUSY为BUSY输出。

单片机

启动转换时,INT/BUSY变为低电平,同时将INT0

(P3.2)置低,以使计数器的计数状态与MAX120的I

NT/BUSY信号一致,也就是说,每转换完一次,计数器就

加以产生新的存储器地址;转换结束后,INT/BUSY转变

为高电平,数据在引脚D0~D11处有效,此时WE信号为低,

存储器写端口打开,并将ADC所转换的数据写入与计数器所产

生地址对应的存储单元。

继而INT/BUSY信号再次变低,

MAX120进入下一次转换。

直到采集的数据超出某一上下限,ADC模块中的比较器产生一信号使单片机外部中断,进而转入

中断数据处理。

其后单片机将读取存储在锁存器中的地址信号,

并将其存储;同时由此地址读出存储在存储器中的超出上下限的

数据。

单片机定时取数时,先将INT0(P3.2)置高,此

时地址产生器的累加由单片机控制(通过T0口,即P3.4)。

单片机控制计数器重新计数并产生地址数据,产生的地址送到单

片机P0口,并由此地址读取存储器中相应地址的数据,最后通

过RS232口传送到PC或其它外设。