温度采集报警系统

基于51单片机的温度报警系统设计

基于51单片机的温度报警系统设计温度报警系统是一种常见的安全监控系统,它可以监测环境温度,并在温度达到设定阈值时发出警报。

本文将介绍一个基于51单片机的温度报警系统的设计。

一、系统设计目标和功能本系统的设计目标是实时监测环境温度,并在温度达到预设阈值时发出警报。

具体功能包括:1.温度采集:通过温度传感器实时采集环境温度。

2.温度显示:将采集到的温度值通过数码管显示出来。

3.温度比较:将采集到的温度值与预设的阈值进行比较。

4.报警控制:当温度超过预设的阈值时,触发警报控制器。

5.报警指示:通过蜂鸣器或者LED灯等方式进行报警提示。

二、硬件设计本系统的硬件设计包括主控部分和外围部分。

1. 主控部分:使用51单片机作为主控芯片,通过AD转换器和温度传感器实现温度数据采集。

采用片内RAM和Flash存储器对数据进行处理和存储。

2.外围部分:包括数码管显示和报警指示。

使用数码管模块将温度值进行显示,使用LED灯或者蜂鸣器进行报警指示。

三、软件设计本系统的软件设计包括程序的编写和算法的设计。

1.程序编写:使用C语言编写单片机的程序。

程序主要包括温度采集、温度比较、报警控制和报警指示等功能。

2.算法设计:根据采集到的温度值与预设阈值进行比较,判断是否触发警报控制器。

同时,根据警报控制器的状态,控制报警指示的开关。

四、系统测试完成硬件和软件设计后,需要进行系统测试以验证系统的正确性和稳定性。

1.硬件测试:对硬件电路进行测试,包括电源、信号传输和外围器件等方面。

测试时需要注意电源的稳定性,信号的准确性和外围部件的工作状态。

2.软件测试:进行程序的运行测试,检查各功能是否正常运行。

特别关注温度采集和比较、报警控制和报警指示等功能。

五、系统性能分析对系统的性能进行分析,包括温度采集的准确性、报警控制的响应时间和报警指示的稳定性等方面。

1.温度采集准确性:主要受温度传感器的精度和ADC转换的准确性影响。

在设计中要选择合适的传感器和ADC。

基于LabVIEW的温度采集报警系统

基于LabVIEW的温度采集报警系统李文方;李海霞【摘要】温度作为一种物理参量,是工业生产中最普遍最重要的参数之一.为了能灵活地对温度进行测量,同时可以方便地改变控制范围的参数、增加可调节性,提出了本设计.本设计以LabVIEW软件为工具,在分析系统功能需求的基础上,介绍了包括前面板、流程图以及图标/连结器在内的虚拟温度采集报警系统的设计,同时介绍了数据采集的理论及虚拟仪器(VI)设计的相关技术,并给出了本系统的仿真结果.经仿真,本温度采集报警系统能很好地实现温度数据的采集,显示以及上下限的报警,并可以灵活地在0℃至100℃之间设定上下限报警温度,达到了设计的目的.【期刊名称】《电子设计工程》【年(卷),期】2015(023)005【总页数】3页(P71-73)【关键词】虚拟仪器;数据采集;温度;LabVIEW【作者】李文方;李海霞【作者单位】黄河科技学院河南郑州450063;黄河科技学院河南郑州450063【正文语种】中文【中图分类】TN98传统的温度采集主要由温度传感器,信号处理电路(放大、滤波),A/D转换电路,显示电路等构成,在微处理器如单片机的控制下,进行温度数据的采集以及显示,同时可以有上下限报警等功能。

传统的温度检测设备对设备本身和检测人员的技能要求都较高,且不方便自我检测,增加了设备维修成本和用户购买成本。

而虚拟仪器主要采用数据采集卡将数据送入计算机,然后通过LabVIEW中的软件设计和界面设计来完成对应的信息处理和显示功能[1-3]。

虚拟仪器能够根据用户不同的要求对其进行修改和扩展,在测量过程中还可以方便地改变控制范围的参数,增加可调节性。

本设计利用数据采集卡和LabVIEW软件,完成了温度数据的采集、显示、分析、报警等,从而实现了一个温度采集器的基本功能。

1 系统构成所有的LabVIEW应用程序,即虚拟仪器(VI),包括前面板(Front Panel)、流程图(Block Diagram)以及图标/连结器(Icon/Connector)3 部分[4]。

温度、湿度实时监测与报警系统的设计与实现

. . . 日 曰 . 圈 巴 巴口. . . .. 日 国 理口 口皿豆口口

河a 大学_学硕十学位论文 匕 「

方式还有一个弊端 — 共应1i)有很大的局限性,二 1 ,r 1 ) t 〕作人员不可能直接测!地‘电缆 A h 的表面温度; 去提取存有炸药、 炮等危险箭仓库温湿度数据的工作人员还要 鞭 : 承担一定

关键词 单总线;单片机; R 校验; e h CC Dli p ;通信协议

Ab ta t src

Ab ta t sr c

T i ppr rdcs k d r lie oir g s m r pr u ad h ae i oue a n o e -m m noi s t f t ea r n s n t i f t a t n ye b e m t e hmit cnrld cmpt, i icn ue f m n api t n. ppr u dy o t l b o u rw c s a b sd ay la osT e e i oe y e h h e o r p ci h a cm le bt t sf a ad d a ds n o p t oh o w r n hrw r ei . es h t e a e e g T e t a p 一 r e o nt R 8 t s so m o t 1 Wi s sr ad 45 nmii nt hi e May h ss y e d s e n e n S r a s n etcn u. n e q snos cnet t 1 r bs i ei n t mi l T e t clco s t n esr ae nc d 一Wi u a n lg t n s h d a l tn i r o e o e s le e a . a o e i t o t r a gte a b s . h a l tr epnilfr g n T e nl a clc r a r l ue Ec dtclc ir os e a i . kreo dt o et h s l s a a oe o s s b o r o h e e f a l o i MC , i t e ca e mesrm n, t l cm ui tn t t hs s U w c a s r o h h k h g f a e et cnr ad m nc i w h ot u o o n o ao i h e cnol. R 45 nmsi nt d u o t dt cl co s tn w i cn ot lrT e 8 t s i o eimae f a ol t n i , c a re h S r a s n s p h a e i t o h h e a

stm32f1温度报警系统实验报告

stm32f1温度报警系统实验报告STM32F1温度报警系统实验报告1. 引言1.1 背景1.2 目的1.3 实验内容2. 实验器材和方法2.1 实验器材2.2 实验方法3. 硬件设计3.1 硬件连接图3.2 温度传感器选型和连接方式4. 软件设计4.1 系统架构图4.2 主程序流程图4.3 温度采集和处理算法5. 实验结果与分析5.1 温度采集结果显示界面截图及解释5.2 温度报警功能测试结果与分析6. 讨论与改进方向6.1 讨论实验中可能出现的问题及解决方案6.2 对实验系统的改进方向提出建议7. 结论8. 参考文献9. 致谢1 引言本报告旨在介绍STM32F1温度报警系统的设计与实现。

通过该系统,可以实时监测环境温度,并在温度超过设定阈值时触发报警。

本报告将详细介绍硬件设计、软件设计、实验结果与分析等内容。

1.1 背景温度监测与报警系统在工业生产、仓储物流等领域具有重要应用价值。

通过实时监测环境温度,可以及时采取措施避免设备过热、产品损坏等问题的发生。

1.2 目的本实验旨在利用STM32F1单片机设计一个温度报警系统,能够实时采集环境温度,并在温度超过设定阈值时触发报警。

1.3 实验内容本实验的主要内容包括:- 设计硬件电路连接,包括STM32F1单片机与温度传感器的连接;- 编写软件程序,实现温度采集和处理算法;- 测试系统功能,包括温度采集结果显示和报警功能。

2 实验器材和方法2.1 实验器材本实验使用的主要器材包括:- STM32F1开发板- 温度传感器模块- 电阻、电容、LED等元件- 面包板、杜邦线等连接线2.2 实验方法根据硬件连接图进行电路搭建,并将STM32F1开发板与计算机连接。

编写软件程序并烧录到STM32F1开发板上。

通过串口或LCD显示屏等方式,实时监测温度采集结果,并测试报警功能。

3 硬件设计3.1 硬件连接图(此处应插入硬件连接图)3.2 温度传感器选型和连接方式根据实验要求,我们选择了DS18B20数字温度传感器作为温度采集模块。

基于单片机的温度采集报警系统的设计

基于单片机的温度采集报警系统的设计王熔熔;刘海霞【期刊名称】《计算机光盘软件与应用》【年(卷),期】2011(000)024【摘要】设计了一种基于单片机AT89S51和DS18820温度传感器的温度采集报警系统。

该系统性能可靠,结构简单,能实现安全温度内正常显示温度值,超出设定的温度上限则进行声光报警。

%It designs a microcontroller based onAT89S51 and DS 18B20 temperature sensor temperature collection and alarm system.The system has reliable performance,simple structure,can achieve safe temperature within a normal display temperature exceeds the set temperature,upper limit,sound and light alarm.【总页数】3页(P181-183)【作者】王熔熔;刘海霞【作者单位】内蒙古机电职业技术学院,呼和浩特010070;内蒙古机电职业技术学院,呼和浩特010070【正文语种】中文【中图分类】TP311.52【相关文献】1.基于单片机数字式多路温度采集语音报警系统 [J], 陈正军;邬华;王谢玮2.基于单片机温度和烟雾检测报警系统的设计 [J], 蒋松云3.基于AT89C52单片机和DS18B20传感器的温度报警系统设计 [J], 毕韬4.基于单片机温度采集与报警系统的研究 [J], 张国容;滕瑞宁;杨升正5.基于单片机的配电箱温度监测和火灾报警系统设计 [J], 刘江虹;吴俊锋;梁艺珍;邱明明;魏琪楠;康俊特因版权原因,仅展示原文概要,查看原文内容请购买。

温度报警系统设计

温度报警系统设计温度报警系统是一种用于监测和报警温度异常的系统。

它广泛应用于工业生产、仓储、实验室等场合,以确保人员和设备的安全。

温度报警系统的设计需要考虑传感器的选择、数据采集与处理、报警方式等方面。

以下是对温度报警系统设计的详细阐述。

一、传感器的选择在温度报警系统中,传感器的选择是非常重要的。

常见的温度传感器有热敏电阻温度传感器(PT100)、热电偶和红外线温度传感器等。

这些传感器具有不同的测量范围、精度和适用环境。

在选择传感器时,需要根据实际需要考虑到测量范围、精度要求和环境条件等因素,以确保传感器的可靠性和准确性。

二、数据采集与处理数据采集与处理是温度报警系统中的核心技术,它直接影响到系统的性能和可靠性。

数据采集可以通过模拟电路或数字电路实现。

在模拟电路中,采用模拟信号调理电路将传感器信号转换成可测量的电压或电流信号。

在数字电路中,采用模数转换器(ADC)将模拟信号转换成数字信号。

数据处理可以通过嵌入式系统或PC机实现。

在嵌入式系统中,采用微处理器或单片机进行数据处理和分析,并通过串口、网络接口或无线通信模块将数据发送给监控中心或其他设备。

在PC机中,采用计算机软件进行数据处理和分析,通过串口、网络接口或USB接口与其他设备进行通信。

三、报警方式声音报警可以通过蜂鸣器或扬声器实现,当温度异常时,系统会发出响亮的声音以引起人们的注意。

光闪报警可以通过LED灯或闪光灯实现,当温度异常时,系统会发出强烈的光信号以引起人们的注意。

手机短信报警可以通过GSM模块或无线通信模块实现,当温度异常时,系统会发送短信给相关人员以及监控中心,及时进行处理。

四、监控与管理温度报警系统的监控与管理是确保系统正常运行的关键环节。

监控与管理可以通过监控中心或计算机软件实现。

监控中心需要实时监测传感器数据、报警信息和设备状态,并进行相应的处理和记录。

计算机软件可以通过远程接入和数据分析等功能,实现对温度报警系统的远程监控、数据记录和报表输出等。

基于51单片机的万年历与温度检测报警系统

基于51单片机的万年历与温度检测报警系统摘要随着社会发展需求的改变,电子万年历是一个应用非常广泛的实用日常计时工具,带有显示世纪,年,月,日,星期,时,分,秒和按键可调时间及其按键设置闹钟的功能,同时具有月末自动更新,闰年补偿功能等多种功能。

温度检测报警系统也是在日常生活和工业应用非常广泛的工具,能实时采集周围的温度信息进行显示,程序内部设定有报警上下限,根据应用环境不同可设定不同的报警上下限。

此系统是基于STC89C52单片机设计的,包含液晶显示模块,DS12C887实时时钟模块,DS18B20温度采集模块,键盘扫描模块,报警模块,HX1838红外接收头模块。

STC89C52作为控制核心,具有功耗低,功能强等特点,电压可选5VUSB 供电。

显示模块采用12864液晶动态显示,相对数码管而言经济实用,占用空间小,对于显示数字、字母最为合适,而且与单片机连线简单,占用IO口相对较少。

实时时钟芯片DS12C887是一款与DS12C885实时时钟兼容的替代产品,该器件提供RTC/日历、定时闹钟等功能,如果检测到主电源故障,该器件可自动切换到备用电源供电,DS12C887将石英晶体与电池集成在一起,在断电后仍可精确走10年。

温度检测报警模块采用数字式温度传感器DS18B20,该芯片具有精度高,测量范围广等优点,易与单片机连接,模块电路组成简单并同时具有温度报警功能。

关键词:STC89C52,DS12C887,DS18B20,12864液晶显示,电子万年历,采集周围设备温度、温度报警一、设计要求与方案论证1.1设计要求设计一个能够实现世纪,年,月,日,星期,小时,分,秒显示附带温度检测显示的实时时钟电子万年历,同时具有时间调节和闹钟设置功能,以及时间预设报警、温度报警、报警解除等功能。

该产品共设有四个按键,每个按键具有多种功能,充分利用各个按键。

也可利用红外遥控来进行实时调节,体现时尚方便的特性,并且通过编程还可以控制12864液晶显示,随心所欲。

室内温度报警控制系统设计

室内温度报警控制系统设计一、概述二、系统组成与工作原理1.温度传感器:负责对室内温度进行实时监测,并将采集到的数据传输给控制器。

2.控制器:接收温度传感器采集的数据,并与预设的温度阈值进行比较。

当温度超出设定范围时,控制器将触发报警器,并发送控制信号给执行机构。

3.报警器:当控制器发出报警信号时,报警器会发出声光警报,以引起人们的注意。

4.执行机构:根据控制器的指令,执行机构负责进行温控操作,可以通过开关制冷设备或加热设备等方式,将室内温度恢复到设定范围内。

系统工作原理如下:1.温度传感器实时监测室内温度,并将温度数据传输给控制器。

2.控制器接收到温度数据后,与预设的温度阈值进行比较。

3.如果温度超出设定范围,控制器触发报警器,并发送控制信号给执行机构。

4.报警器发出声光警报,提醒人们注意室内温度异常。

5.执行机构根据控制器的指令,开启或关闭相应的温控设备,使室内温度恢复到设定范围内。

三、系统设计要点1.温度传感器选择:根据实际需要选择合适的温度传感器,如热敏电阻、热电偶或半导体传感器等。

要考虑传感器的测量范围、测量精度以及信号输出等特性。

2.控制器设计:控制器应具备接收温度传感器数据、比较温度阈值、触发报警器、发送控制信号等功能。

可以采用微控制器或单片机实现控制器的功能。

3.报警器选择:报警器应具备发出声光警报的能力,可以选择蜂鸣器或喇叭作为声音输出装置,并配置相应的指示灯作为光源。

4.执行机构设计:执行机构应根据不同的温度控制需求选择合适的设备,如空调、暖气等。

要考虑设备的功率、响应速度以及控制方式等特性。

5.系统可靠性设计:在设计室内温度报警控制系统时,要考虑系统的可靠性。

例如,在温度传感器故障或通信故障时,系统应能够进行故障检测并发出相应的报警。

四、总结室内温度报警控制系统设计涉及到温度传感器的选择、控制器的设计、报警器的选择、执行机构的设计以及系统可靠性设计等方面。

通过合理的设计和选择,可以实现对室内温度的有效监测和控制,提高室内温度的舒适度,并保证系统的可靠性和安全性。

冷链物流温度监控与报警系统设计

冷链物流温度监控与报警系统设计冷链物流是指在物流过程中对易变质产品进行温度控制和监控,以确保产品的质量和安全。

在冷链物流过程中,温度监控和报警系统起着至关重要的作用,可以实时监测温度变化,并在温度异常时及时报警,以保证产品的品质和安全性。

本文将探讨冷链物流温度监控与报警系统的设计原理和关键技术。

一、冷链物流温度监控系统设计原理冷链物流温度监控系统的设计原理是通过传感器实时采集环境温度数据,并将采集到的数据通过通信网络传输到中央控制系统。

中央控制系统根据预设的温度范围进行数据分析和处理,并在温度超出设定范围时触发报警机制。

下面将介绍冷链物流温度监控系统设计的主要技术要点。

1. 传感器选择和布置在冷链物流过程中,合适的传感器是实现温度监控的关键。

常用的温度传感器有热电偶、热敏电阻和半导体温度传感器等。

根据实际需求选择适合的传感器,并合理布置在货物密集的区域,以确保准确采集到温度数据。

2. 数据采集与传输温度数据的采集与传输是冷链物流温度监控系统设计的核心。

可采用无线传感器网络技术,利用无线传感器节点采集环境温度数据,并通过无线通信模块将数据传输到中央控制系统中。

此外,还可以使用物联网技术和云计算技术实现数据的远程采集和传输,以提高系统的智能化和便捷性。

3. 数据分析与处理中央控制系统接收到温度数据后,需要进行数据分析和处理。

首先,对采集到的数据进行实时监测和记录,以便进行后期的分析和溯源。

其次,将采集到的数据与预设的温度范围进行比对,如果温度超出设定范围,就触发报警机制。

最后,对温度数据进行历史记录和统计分析,为冷链物流过程中的质量控制和管理提供支撑。

4. 报警机制设计报警机制是冷链物流温度监控系统设计的重要部分。

当温度超出设定范围时,系统会自动触发报警,通知相关人员进行处理。

报警方式可以包括声音报警、短信报警、邮件报警等,以确保及时采取措施避免温度对产品造成损害。

二、冷链物流温度监控系统设计关键技术冷链物流温度监控系统设计需要涉及多个关键技术,下面将重点介绍其中的几个关键技术。

温度采集报警系统的设计和实现

特 点可 造成 N位 同时显 示的 效果 。

21年3 干 O 0 月

商品与质 量

理 研究 论

温度采集报警系统的设计和实现

口胡 思远

( 西北 民族大学数学与计算机 科学学院 甘 肃兰州 703 ) 300

摘 要: 本文对温度 采集与报 警系统的现状与适用性进行 分析, 并针对 目前温度 采集报 警系统 的缺 陷与不足 进行改进 , 主要在 上 面做 了部 分 改 进 。 关键词 : 温度采集; 警系统适 用性 报

该系 统采 用 A 8C l 为微控 制器 , 用 4 4矩 阵式键 盘作 T95 作 使  ̄ 为用户输 入设 备 , 用 D 1B 0 为温 度 感应 设备 。系统 从键盘 采 S 82 作 录 入用户 输入 的数据 并保 存 到数据 存 储器 中, 温度 感 应器 所采 将 集到 的温度 根据 用户 设 定 的模 式 与用 户 的数据 进行 比较 , 用两 并 位 L D 将所 采集 到 的温 度 值进 行 显示 , E 在一 定控制 模式 下 , 当温

高 的显 示亮度 , 占用 C U 时 间少 , P 编程 简单 等优 点 , 其 占用的端 但 口线 多 , 硬件 电路 复杂 。

机 之后 对各个 功 能部件 进行 初始 化 ,之 后读 取温 度值 信息 ,并在 L D 数码 管上显 示 出来 , E 如此 在读 数. 示 之间 循环 , 盘输 入采 显 键 用 中断方 式 ,当用户 想设 置或 者更 改模 式 时只 需从键 盘 上进 行操 作 , 不需 对系 统进 行复 位操 作 , 而 每次 输入 三个 数据 [ 格式 为 : 设 预

基于DS18B20的Mega16单片机温度采集系统

基于DS18B20的Mega16单片机温度报警系统陆和亮(2010800631)袁彦凯(2011110144)滕木(2011110111)王锐英(2011110132)设计思想:这次设计的是基于DS18B20的数字温度计,它具有读数方便,测温范围广,测温精确,数字显示,适用范围宽等特点。

1.设计中选用Mega16型单片机作为主控制器件。

2.采用DS18B20数字温度传感器作为测温元件,通过4位共阳极LED数码显示管并行传送数据,实现温度显示。

3.ADC0808和一个LF351运放构成电压放大器,实现温度和电压的转换。

工作流程:Mega16通过DS18B20直接读取被测温度值,送入单片机进行数据处理,之后单片机进行判断和比较并且输出6位LED数码管,并且将读取到的温度值进行比例运算输出ADC0808和运算放大器结合输出合适的温度。

最终完成了数字温度计的总体设计。

其系统构成简单,信号采集效果好,数据处理速度快,便于实际检测使用。

设计内容简介:本设计的内容主要对系统硬件部分的设计,包括温度采集电路和显示电路;再次对系统软件部分的设计,应用C语言实现温度的采集与显示。

并且附上部分源代码。

设计要求:温度报警器设计,具体要求如下:1.将被测温度(0~100摄氏度)转换为电压值;2.小于10摄氏度或大于30摄氏度,光报警(LED亮);3.可采用电阻组成测量电桥、具体方案:1、根据设计要求,选用Mega16单片机为核心器件;2、温度检测器件采用DS18B20数字式温度传感器,利用单总线式连接方式与单片机的串行接口PORTD.2引脚相连;3、显示电路采用6个LED数码管显示器接口和PORTD,PORTC口相连并行显示温度值一.单片机外围电路设计Mega16单片机系统包括晶体振荡电路、复位开关和电源部分。

下图为Mega16单片机的最小系统。

二.温度测量模块温度测量传感器采用DALLAS公司DS18B20的单总线数字化温度传感器,测温范围为-55℃~125℃,可编程为9位~12位A/D转换精度,测温分辨率达到0.0625℃,采用寄生电源工作方式,CPU只需一根口线便能与DS18B20通信,占用CPU口线少,可节省大量引线和逻辑电路三.显示报警模块显示部分选用4位Led数码管。

采集数据报警系统方案

采集数据报警系统方案引言在各种行业中,对于实时数据的采集和监控至关重要。

随着物联网技术的发展,采集数据报警系统成为了保障数据安全和运行稳定的重要组成部分。

本文将介绍一种简单而高效的采集数据报警系统方案,该方案基于物联网技术,能够实时采集数据并在异常情况下触发报警。

系统架构采集数据报警系统的架构由以下几个关键组件组成:•传感器:用于采集各种环境参数的传感器,例如温度、湿度、压力等。

•网关设备:负责将传感器采集到的数据利用物联网技术发送给云平台。

•云平台:接收传感器数据并进行存储、处理和分析。

同时,云平台还负责监控数据,并在异常情况下触发报警。

•报警设备:根据云平台发送的报警信息进行相应的报警,例如声音报警、短信报警等。

系统工作流程1.传感器采集数据:传感器实时采集环境参数数据。

2.数据传输至网关设备:传感器通过物联网技术将采集到的数据传输至网关设备。

3.网关设备传输数据至云平台:网关设备将采集到的数据通过网络传输至云平台。

4.云平台存储和处理数据:云平台接收到数据后,会进行存储、处理和分析。

5.数据监控和异常检测:云平台会对采集到的数据进行实时监控,并检测是否存在异常情况。

6.报警触发:如果云平台检测到数据异常,会触发相应的报警机制。

7.报警设备响应:报警设备根据报警信息进行相应的报警,例如触发声音报警器或发送短信报警。

系统优势采集数据报警系统方案具有以下几个优势:1.实时性:借助物联网技术,传感器采集到的数据可以实时传输至云平台,实现对数据的即时监控和报警。

2.高效性:采用云平台存储和处理数据,可以对大量数据进行高效处理和分析,提高报警的准确性和响应速度。

3.智能化:通过云平台的数据处理和分析,可以实现对数据的智能化监控和异常检测,减少误报率,提高数据的安全性。

4.灵活性:系统具有良好的可扩展性和可配置性,可以根据实际需求对传感器、网关设备、云平台和报警设备进行灵活部署和配置。

系统应用采集数据报警系统方案可以应用于各种行业和领域,例如:1.工业监测:对于工业生产过程中的关键环境参数进行监测,如温度、湿度、压力等,及时发现异常情况,保证生产的安全和稳定。

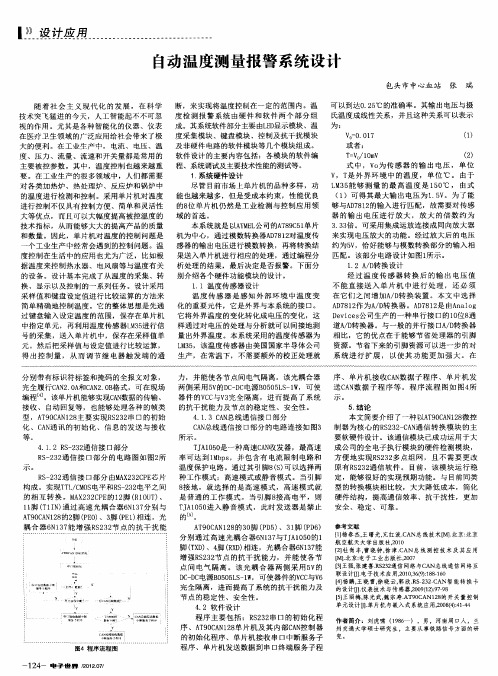

自动温度测量报警系统设计

包 头市 中心 血 站 张 瑞 .5 随 着 社 会 主 义 现 代 化 的发 展 ,在 科 学 断 ,来 实现将 温度 控制 在一 定 的范 围内 。温 可 以到达 0 2 ℃ 的准确 率 。其输 出 电压与 摄 技术 突飞猛 进 的今 天 ,人工 智能 起不 不可 忽 度 检 测 报 警 系 统 由硬 件 和 软 件 两 个 部 分 组 氏温度 成线 性关 系 ,并且这 种关 系可 以表 示 E 显示模块 、温 为 : 视的 作用 。尤 其 是各种 智 能化 的仪器 、仪表 成 。其系统 软件部 分主要 由LD V= . 1 O 0 7 () 1 在医 疗卫 生领 域 的广泛 应用 给社 会 带来 了极 度采集 模块 、键 盘模 块 、控 制及 抗干 扰模 块 或者 : 大 的便 利 。在工 业生 产 中, 电流 、电压 、温 及非 硬件 电路 的软件 模块 等 几个模块 组 成 。 T V/ 0 V = o 1m () 2 度 、压 力 、流量 、流 速和 开关 量都 是常 用的 软件 设计 的主 要 内容包括 :各 模块 的软 件编 式 中 ,v 为 传 感 器 的输 出 电 压 , 单 位 o 主要被 控 参数 。其 中 ,温度控 制 也越来 越重 程 、系统调 试及主要技术性 能的测试等 。 v T 外界 环 境 中 的温 度 ,单 位 ℃ 。 由于 , 是 要 。在工 业生 产 的很 多领域 中 ,人们都 需要 1 系统硬 件设 计 M5 5℃ 对各 类加 热炉 、热 处理 炉 、反应 炉和锅 炉 中 尽 管 目 市 场上 单片机 的 品种 多样 ,功 L 3 能 够 测 量 的最 高温 度 是 1 0 , 由式 前 能 也越 来越 多 ,但是 受成本 约束 ,性 能优 良 ( )可 得 其最 大输 出 电压 为 1 5 。为 了能 1 .V 的温 度进 行检 测和 控制 。采 用单 片机 对温 度 D8 2 进 行控制 不仅 具有 控制 方便 、简 单和 灵 活性 的8 单片 机仍 然 是 工业 检 测与 控 制应 用 领 够 与A 7 1 的输 入进 行 匹配 ,故需 要对 传感 位 器 的输 出 电压 进 行 放 大 ,放 大 的倍 数 约 为 大等 优 点 ,而且 可 以大 幅度 提 高被控 温度 的 域 的 首选 。 本系 统就是 以A M L T E 公司 的A 8 C l T 9 5 单片 3 3 倍 。可采 用集成 运放 连接 成 同向放 大器 .3 技 术指标 ,从而 能够 大大 的提 高产 品的 质量 和 数量 。 因此 ,单片 机对 温度 的控制 问题是 机为 中心 ,通 过模数 转换 器A 7 1 对温度 传 来实 现 电压放 大的 功能 。经过 放大 后 的 电压 D 82 V 个 工业 生产 中经 常会遇 到 的控制 问题 。温 感器 的输 出 电压进 行模数 转换 ,再将转 换结 约 为5 ,恰好 能够 与模 数转 换部 分 的输入 相 所 度 控 制在 生活 中 的应 用 也尤 为广泛 ,比如根 果送 入单 片机 进行 相应 的处 理 ,通过编 程分 匹 配 。该部分 电路 设计 如 图l 示 。

无线温湿度监控报警系统概要

无线温湿度监控报警系统设计思路 本系统由温湿度监控中心 CMS(Central Monitoring System)(内部嵌入8051核的nRF905构成)和温湿度采集终端 RTU(Remote Terminal Unit)(由带有射频模块的nRF905构成)构成点对多点无线数据传输系统。

系统的组成结构见图 1。

CMS 由上位机和无线发射/接收器组成 ,无线 发射/接收器负责与每个 RTU 通信,读取 RTU 保存的温湿度值,并通过 RS-232通信接口把采集的数据送到上位机 ,由上位机显示更新。

为了避免同频段 的通信干扰,无线发射/接收器采用TDMA(Time Division Multiple Access)通信 方 式 ,分 时与每个 RTU 通信。

RTU 由无线发射/接收电路和温湿度采集保存 电路组 成 ,RTU 采集温湿度后把温湿度数据保存在外部 E2PROM 存储器中等待温湿度监控中心( CMS )的数据收发器来读取。

方案设计系统总体框图各模块实现硬件电路nRF9E5射频接收发射器电路CMS的无线发射/接收器和 RTU的无线发射/接收器都是由 51兼容的射频 SoC 芯片 nRF9E5完成的引。

nRF9E5是挪威 Nordic公司的产品,该芯片内置 nRF9O5433/868/915MHz 收发器、8051兼容微控制器、4输入 1O位 80kspsA/D转换器和 8个通用 I/O;同时还集成了 4KBRAM 存储器、UART和定时器。

该芯片采用 +1.9V~3.6V供电,QFN5×5ram 封装。

内置的 nRF905收发器采用 GFSK调制,数据传输速率为 100Kbps。

特有的ShockBurst工作模式可最大限度的降低功耗。

nRF9E5的发射功率为 0至 +10 dBm,接收灵敏度为一100 dBm,无遮挡通信距离 200米,可满足本系统要求。

图2是 nRF9E5射频收发器电路图。

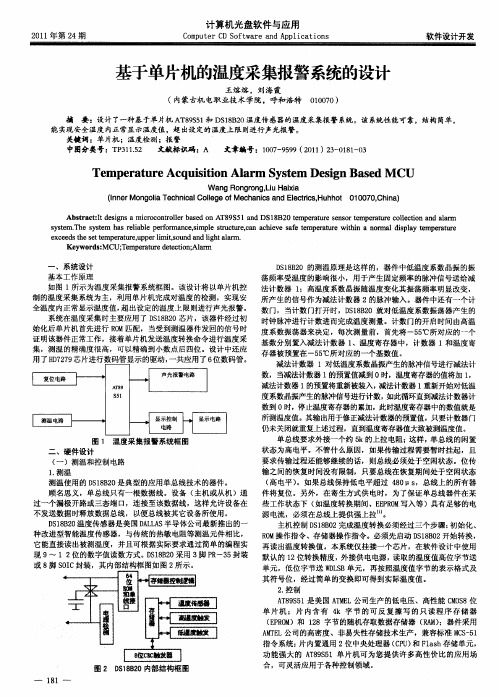

基于单片机的温度采集报警系统的设计

摘 要 :设计了一种基于单片机 A 8S 1 DS8 2 T 9 5 和 1B 0温度传感器的温度采集报警 系统。该系统性能可靠,结构简单, 能 实现 安全 温度 内正常显 示温 度值 ,超 出设 定的 温度上 限 则进 行 声光报 警 。 关键 词 : 2 P 1. 5

一

、

系 统在温 度 采集 时主 要应用 了 D 1B 0芯 片 ,该 器件 经过初 时钟脉 冲进 行 计数进 而完 成温 度测 量 。计数 门 的开启 时 间 由高 温 S 82 始 化后 单片机 首 先进行 R M匹配 ,当 受到测 温器 件发 回 的信 号时 度 系数 振 荡器 来决 定 ,每 次测 量前 ,首先将 一5 ℃所 对应 的 一个 O 5 证 明该 器件 正常 工作 ,接 着单 片机 发送温 度 转换 命令 进行温 度采 基数 分别 置入 减法 计数器 1 、温 度 寄存器 中 ,计数器 1 温度 寄 和 集 ,测 温 的精确 度很 高 ,可 以精确 到 小数 点后 四位 。设计 中还应 存器被 预 置在 一5 ℃所对 应 的一个 基数值 。 5 用 了H 7 7 芯 片进 行数 码管 显示 的驱动 , 共应用 了 6 数码 管 。 D2 9 一 位 减 法计数 器 1对 低温度 系数 晶振产 生的脉 冲信号 进行减 法计 数 ,当减 法计数 器 1的预 置值减 到 0 ,温 度寄存 器的值将加 1 时 , A 9 T8 减法计 数器 1 的预置将重 新被装入 , 减法计 数器 1 新开始对低 温 重 S 5l 度系数 晶振产 生的脉冲信 号进行计 数 , 如此循 环直到 减法计 数器计 数到 0时 , 停止 温度 寄存 器 的累加 , 时温度 寄存器 中的数值 就是 此 所测温 度值 。 输 出用 于修正减法 计数器 的预置值 ,只要计 数器 门 其 仍未 关闭就重 复上述过程 ,直到温 度寄存器 值大致被 测温度值 。 单 总线要 求外 接一 个约 5 k的上拉 电阻 : 样 , 总线 的闲 置 这 单 图 1 温度 采集 报警 系统 框 图 状 态为 高 电平 。不管什 么 原因 ,如 果传输 过程 需要 暂 时挂起 , 且 二 、硬件 设计 要 求传 输过程 还 能够继 续 的话 ,则 总线必 须处 于空 闲状 态 。位传 ( )测 温和 控制 电路 一 1 测 温 . 输 之 间的恢 复 时间没有 限制 ,只要 总线在 恢 复期 间处 于空 闲状态 测温 使用 的 D 1B 0 典型 的应 用单 总线技 术 的器件 。 S82 是 ( 电平 ) 高 。如 果总线 保持 低 电平超 过 40 ,总线 上 的所有 器 8 S u 顾名 思义 ,单 总线 只有 一根 数据 线 。设备 ( 主机或 从机 )通 件 将复 位 。另外 ,在 寄生 方式 供 电时 ,为 了保 证单 总 线器件 在 某 过 一个漏 极 开路或 三态 端 口,连 接 至该数 据线 ,这 样 允许设 备在 些 工作 状态 下 ( 温度 转换 期 间、E PO 如 E RM写入 等 )具有足 够 的 电 不 发送数 据 时释放 数据 总线 , 以便总 线被 其它 设备所 使用 。 源 电流 ,必 须在 总线 上提 供强 上拉 …。 D 1B0 度传 感器 是美 国 DL A 半 导体 公司最 新推 出 的一 S 82 温 AL S 主机控 制 D IB 2 成温 度转 换必须 经过 三个 步骤 : S8 0 完 初始 化 、 种 改进 型智 能温度 传 感器 ,与传 统 的热 敏 电阻等 测温 元件相 比, RM操作指 令 、存储 器操 作指 令 。必须 先启 动 D 1B 2 始转 换 , O S80 开 它 能直 接读 出被 测温 度 ,并且 可根 据 实际要 求通 过简 单的编 程 实 再读 出温度 转 换值 。本 系统仅 挂接 一个 芯 片 ,在 软件 设计 中使 用 现 9 12位 的数字 值读 数方 式 。 S 82 ~ D 1B0采用 3 P 一3 封 装 默认的 1 位转换精度, 脚 R 5 2 外接供电电源, 读取的温度值高位字节送 或 8 SI 脚 OC封装 ,其 内部 结 构框 图如 图 2 示 。 所 单元 ,低位 字 节送 WL B单元 ,再 按照温 度值 字节 的表 示格 式及 DS 其符 号位 ,经 过简 单 的变 换 即可得 到实 际温 度值 。 2控 制 . A8 S 1 美 国 A ML公 司生 产的低 电压 、高 性 能 C O8位 T 95 是 TE MS 单 片 机 ; 片 内含 有 4 字 节 的 可 反 复 擦 写 的 只 读 程 序 存 储 器 k (Po )和 18 字 节 的随机 存取 数据存 储器 (A ) ER M 2 R M ;器 件采 用 A TL公 司的 高密度 、非 易失 性存储 技术 生产 ,兼容标 准 M S 5 ME C一 1 指 令系 统 ; 内置通 用 2 中央处 理器 ( P ) Fah存储 单元 , 片 位 CU 和 ls 功能 强 大 的 A 8S 1单 片机 可 为您 提 供 许 多高性 价 比的应 用 场 T 95 合 ,可灵活 应用 于 各种控 制领 域 。 图 2 D 1B 0内部结 构框 图 S8 2

环境温度监测报警系统

一、引言 随着社会的发展,人们对电机控制的自动化程度要求越 来越高。在早期的 电 机 控 制 中,普 遍 采 用 单 片 机 微 控 制 器, 该控制器运算处 理 速 度 较 慢,内 部 资 源 和 接 口 容 量 有 限,已 不能满足电机快速调速的要求,而导致整个系统精度受到很 大的影响。随着微处理器的技术的快速发展,以高速微处理 器为核心的控制系统已成为电机控制系统的发展趋势。 二、直流双闭环调速系统设计 ( 一) 控制系统的设计。以可编程 DSP 控制器为核心构 成的运动控制系统为了满足世界范围内运动控制系统的需 要,TI 公司推出了 TMS320x24x 系列 DSP 控制器。 基于 DSP 控制器构成的电机控制系统事实上是一个单 片机,因为整个电动机控制所需的各种功能都可以由 DSP 控 制器来实现。因此,可 大 幅 度 缩 小 目 标 系 统 的 体 积,减 少 外

环境温度监测报警系统

□黄光华

【摘 要】本系统主要是由传感器模块,转换放大电路,单片机显示控制模块,语音模块组成。以 AT89C52 单片机为控制芯片, 控制数码管实时显示监测温度,超温报警,语音播报等功能,监测温度曲线液晶屏上显示。

【关键词】ATC89C52; AD590; 实时监测; AD677 【作者单位】黄光华,赣南师范学院科技学院

·72·

直流双闭环调速系统研究

□丛高影

【摘 要】本文是基于 DSP 控制的直流双闭环调速系统,以 TMS320F2407A 为主控制器,它功耗低,控制功能强,同时,配以相应 的接口电路,包括 D / A 转换器、触发电路等。D / A 转换器及触发电路,实现整个系统控制量的输出,达到电动机调速 的目的。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

大庆石油学院课程设计2009年2月日大庆石油学院课程设计任务书课程单片机原理及应用课程设计题目温度采集报警系统的设计专业电子科学与技术姓名杨光学号030901240319主要内容、基本要求、主要参考资料等1、主要内容:根据单片机课程所学内容,结合其他相关课程知识,设计一个温度采集报警系统,以加深对单片机知识的理解,锻炼实践动手能力,为以后的毕业设计和工作打下坚实基础。

2、基本要求:本设计以MCS-51系列单片机为核心,采用常用电子器件设计。

要求可以显示被测的温度并存储,可以设置报警温度,到达报警温度时声光报警。

3、主要参考资料:[1] 张毅坤,陈善久.单片微型计算机原理及应用[M].西安:西安电子科技大学出版社,2002.[2] 张友德,赵志英,徐时亮.单片微机原理应用与实验[M].上海:复旦大学出版社,2000.[3] 蔡美琴,张为民,沈新群,张荣娟.MCS-51系列单片机系统及其应用[M].北京:高等教育出版社,1992.完成期限2007年3月9日指导教师专业负责人2007年3 月2日目录第1章系统设计 (1)1.1温度采集报警系统 (1)第2章硬件设计 (2)2.1测温和控制电路 (2)2.2 显示控制电路 (5)2.3 声光报警电路 (6)第3章软件设计 (8)总结 (9)参考文献 (10)附录1 整体电路图 (11)附录2 源程序 (12)第1章系统设计1.1温度采集报警系统如图1.1所示为温度采集报警系统框图。

该课程设计将以单片机控制的温度采集系统为主,利用单片机完成对温度的检测,实现安全温度内正常显示温度值,超出设定的温度上限则进行声光报警。

系统在温度采集时主要应用了DS18B20芯片,该器件经过初始化后单片机首先进行ROM匹配,当受到测温器件发回的信号时证明该器件正常工作,接着单片机发送温度转换命令进行温度采集,测温的精确度很高,可以精确到小数点后四位。

设计中还应用了HD7279芯片进行数码管显示的驱动,一共应用了6位数码管。

报警电路采用由NE555所组成多谐振荡电路。

图1.1系统框图第2章硬件设计2.1测温和控制电路(1) 测温测温使用的DS18B20是典型的应用单总线技术的器件。

1-wire单总线是Maxim全资子公司Dallas的一项专有技术。

与目前多数标准串行数据通信方式,如SPI/I2C/MICROWIRE不同,它采用单根信号线,既传输数据位,又传输数据位的定时同步信号,而且数据传输是双向的。

大多数1-wire器件不需要额外的供电电源,可直接从单总线上获得足够的电源电流(即寄生供电方式)。

它具有节省I/O口线资源、结构简单、成本低廉、便于总线扩展和维护等诸多优点。

1-wire单总线适用于单个主机系统,能够控制一个或多个从机设备。

当只有一个从机位于总线上时,系统可按照单节点系统操作;而当多个从机位于总线上时,则系统按照多节点系统操作。

为了较为全面地介绍单总线系统,将系统分为三个部分讨论:硬件结构、命令序列和信号方式(信号类型和时序)。

硬件结构:顾名思义,单总线只有一根数据线。

设备(主机或从机)通过一个漏极开路或三态端口,连接至该数据线,这样允许设备在不发送数据时释放数据总线,以便总线被其它设备所使用。

单总线端口为漏极开路,其内部等效电路如图1所示。

单总线要求外接一个约5k的上拉电阻;这样,单总线的闲置状态为高电平。

不管什么原因,如果传输过程需要暂时挂起,且要求传输过程还能够继续的话,则总线必须处于空闲状态。

位传输之间的恢复时间没有限制,只要总线在恢复期间处于空闲状态(高电平)。

如果总线保持低电平超过480μs,总线上的所有器件将复位。

另外,在寄生方式供电时,为了保证单总线器件在某些工作状态下(如温度转换期间、EEPROM写入等)具有足够的电源电流,必须在总线上提供强上拉[1]。

(2)控制At89S51是美国ATMEL公司生产的低电压、高性能CMOS8位单片机;片内含有4k字节的可反复擦写的只读程序存储器(PEROM)和128字节的随机存取数据存储器(RAM);器件采用AMTEL公司的高密度、非易失性存储技术生产,兼容标准MCS-51指令系统;片内置通用2位中央处理器(CPU)和Flash存储单元,功能强大的AT89C51单片机可为您提供许多高性价比的应用场合,可灵活应用于各种控制领域。

功能特性概述AT89S51提供以下标准功能:4k字节Flash闪速存储器、128字节内部RAM、32个I/O口线、两个16位定时/计数器、1个5向量两级中断结构、一个全双工串行通信口、片内振荡器及时钟电路,同时,AT89S51可降至0Hz的静态逻辑操作并支持两种软件可选的节电工作模式;空闲方式停止CPU的工作,但允许RAM、定时/计数器、串行通信口及中断系统继续工作;掉电方式保存RAM中的内容,但振荡器停止工作并禁止其它所有部件工作一直到下个硬件复位[2]。

引脚功能说明Vcc:电源电压GND:地P0口:P0口是一组8位漏极开路型双向I/O口,也即地址/数据总线复用口;作为输出口用时,每位能吸收电流的方式驱动8个TTL逻辑门电路,对端口写“1”可作为高阻抗输入端用。

在访问外部数据存储器或者程序存储器时,这组口线分时转换地址(低8位)和数据总线复用;在访问期间激活内部上拉电阻。

在Flash编程时,P0口接收指令字节,而在程序校验时,输出指令字节,校验时要求外接上拉电阻P1口:P1是一个带内部上拉电阻的8位双向I/O口;P1的输出缓冲级可驱动(吸收或输出电流)4个TTL逻辑门电路,对端口写“1”,通过内部的上拉电阻把端口拉到高电平,此时可作输入口;作输入口使用时,因为内部存在上拉电阻,某个引脚被外部信号拉低会输出一个电流。

Flash编程和程序校验期间,P1接收低8位地址P2口:P2口是一个带有内部上拉电阻的8位双向I/O口;P2的输出缓冲级可驱动个(吸收或输出电流)4个TTL逻辑门电路,对端口写“1”,通过内部的上拉电阻把端口拉到高电平,此时可作输入口;作输入口使用时,因为内部存在上拉电阻,某个引脚被外部信号拉低会输出一个电流。

在访问外部程序存储器或16位地址的外部数据存储器(例如执行MOVX @DPTR 指令)时,P2口送出高8位地址数据;在访问8位地址的外部数据存储器(如执行MOVX @RI)时,P2口线上的内容(即特殊功能寄存器(SFR)区中的R2寄存器的内容),在整个访问期间不改变;Flash编程或校验时,P2亦接收高位地址和其它控制信号。

P3口:P3口是一个带有内部上拉电阻的8位双向I/O口;P2的输出缓冲级可驱动个(吸收或输出电流)4个TTL逻辑门电路,对端口写“1”,通过内部的上拉电阻把端口拉到高电平,此时可作输入口;作输入口使用时,因为内部存在上拉电阻,某个引脚被外部信号拉低会输出一个电流。

P3口除了作为一般的I/O口线外,更重要的用途是它的第二功能;如下表2-1所示:P3口还接收一些用于Flash闪速存储器编程和程序校验的控制信号。

RST:复位输入;当振荡器工作时,RST引脚出现两个机器周期以上高电平将使单片机复位ALE/PROG:当访问外部程序存储器或数据存储器时,ALE(地址锁存允许)输出脉冲用于锁存地址的低8位字节;即使不访问外部存储器,ALE仍以时钟振荡频率的1/6输出固定的正脉冲信号,因此它可对外输出时钟或用于定时目的;要注意的是,每当访问外部数据存储器时将跳过一个ALE脉冲。

如有必要,可通过对特殊功能寄存器(SFR)区中的8EH单元的D0位置位,可禁止ALE操作,该位置位后,只有一条MOVX和MOVC指令ALE才会被激活,此外该引脚会被微弱拉高,单片机执行外部程序时,应该置ALE无效。

EA/VPP:外部访问允许;欲使CPU仅访问外部程学存储器(地址为0000H FFFFH),EA端必须保持低电平(接地)。

需要注意的是,如果加密位LB1被编程,复位时内部会锁存EA端的状态[3]。

如EA端为高电平(接Vcc端),CPU则执行内部程序存储器中的指令。

Flash存储编程时,该引脚加上+12V的编程允许电源Vpp,当然这必须是该器件是使用12V编程电压Vpp。

XTML1:振荡器反相放大器的及内部时钟发生器的输入端。

XTML2: 振荡器反相放大器的输出端。

图2.1测温和控制电路2.2 显示控制电路HD7279A是一片具有串行接口的,可同时驱动8位共阴式数码管(或64个LED 点阵)的智能显示驱动芯片,该芯片同时还可连接多达64键的键盘矩阵。

该芯片内部含有译码器,可直接接受16进制码,HD7279A还同时具有2种译码方式,HD7279(A)还具有多种控制指令,如消隐、闪烁、左移、右移、段寻址等。

HD7279与单片机仅需4条接口线,其中CS为片选信号。

当MCU访问HD7279时,应将片选端置为低电平。

DATA为串行数据/输出端,当向HD7279发送数据时,DATA为输入端;当HD7279A输出键盘代码时,DATA为输出端。

其特点为:-串行接口,无需外围元件可直接驱动LED-各位独立控制译码/不译码及消隐和闪烁属性-(循环)左移/(循环)右移指令-具有段寻址指令,方便控制独立LED-64键键盘控制器,内含去抖动电路-有DIP和SOIC两种封装形式供选择图2.2显示控制电路2.3 声光报警电路555集成定时器是一种模拟和数字电路相混合的集成电路。

它结构简单,使用灵活,用途十分广泛,可以组成多种波形发生器、多谐振荡器、定时延时电路、双稳触发电路、报警电路、检测电路、频率变换电路等。

555定时器的电路原理图及管脚排列图分别如图2.3和2.4所示。

555含有两个比较器A 1、A 2,其中5端为电压控制端,通过外接一个参考电源,可以改变上、下触发电位值,不用时,可通过一个0.01μF 旁路电容接地。

4端为触发器复位端,不用时应接高电平。

总之,555相当于一个可用模拟电压来控制翻转的R-S 触发器。

图2.5就是用555构成的多谐振荡电路,产生的振荡脉冲信号经过三极管放大后驱动扬声器报警,由单片机的P1.5端口输出高电平发出报警。

图2.5 报警电路图2.4 555定时器的引脚图1 电源地5 6图2.3 555定时器的原理图GND DIS TL THVC高触发端 放电端低触发端电压控制端第3章软件设计该课程设计中主要利用了DS18B20芯片进行测温,该芯片是单总线器件,顾名思义单总线只有一根数据线,因此在通信时时序就显得十分重要,我们在编程时也要十分注意这一点。

在程序中测温时首先要对DS18B20进行初始化,初始化过程由单片机发出的复位脉冲和芯片响应的应答脉冲组成,应答脉冲使主机知道,总线上有从机设备,且准备就绪。

由于总线上只挂接了一片测温芯片,因此可直接跳过ROM匹配发出测温命令。