《嵌入式ARM技术及应用》课程实验指导书实验6:外部中断实验,(2014.7.10)

arm中断实验的实验报告

arm中断实验的实验报告ARM中断实验的实验报告引言:ARM中断是一种常用的处理器功能,它可以在特定条件下中断当前的程序执行,转而执行指定的中断服务程序。

本次实验旨在通过ARM中断实验,深入了解中断的原理和应用。

一、实验背景ARM中断是ARM处理器中的一种重要功能,它可以在特定条件下中断当前的程序执行,转而执行指定的中断服务程序。

中断可以分为外部中断和内部中断两种类型。

外部中断是指来自外部设备的中断请求,例如外部设备的输入信号变化;内部中断是指来自处理器内部的中断请求,例如算术溢出、指令错误等。

二、实验目的1. 了解中断的概念和原理;2. 掌握ARM中断的实现方法;3. 学习如何编写中断服务程序。

三、实验步骤1. 准备实验环境:搭建ARM开发板,连接必要的外设;2. 配置中断控制器:根据实验需求,配置中断控制器的相关寄存器,使其能够正确响应中断请求;3. 编写中断服务程序:根据实验需求,编写中断服务程序,实现中断处理的相关功能;4. 运行实验程序:将编写好的程序下载到ARM开发板上,运行程序,观察中断的触发和响应情况;5. 实验结果分析:根据实验结果,分析中断的触发条件、中断服务程序的执行情况等。

四、实验结果与分析通过实验,我们成功实现了ARM中断的功能。

在实验过程中,我们配置了外部设备的中断引脚,当引脚状态发生变化时,中断控制器会产生中断请求,处理器则会立即中断当前的程序执行,转而执行中断服务程序。

在中断服务程序中,我们可以完成一些特定的操作,例如读取外设数据、更新系统状态等。

实验结果表明,中断服务程序能够正确地响应中断请求,并完成相应的操作。

五、实验总结本次实验通过ARM中断的实验,我们深入了解了中断的原理和应用。

中断是一种重要的处理器功能,它可以在特定条件下中断当前的程序执行,转而执行指定的中断服务程序。

掌握了中断的实现方法和编写中断服务程序的技巧,我们可以在实际应用中更好地利用中断功能,提高系统的响应速度和稳定性。

(完整word版)嵌入式-中断实验

实验五中断控制实验(一)实验目的了解中断的作用;掌握嵌入式系统中断的处理流程;掌握ARM中断编程。

(二)实验设备计算机;ARM硬件仿真器;ARM开发板(三)实验硬件设置在做实验之前,先将开发板电源接好,将仿真器的USB连线与电脑相连,通电,然后按核心板的复位键。

(四)实验原理1. 中断的基本概念CPU与外设之间传输数据的控制方式通常有三种:查询方式、中断方式和DMA方式。

DMA 方式将在后续实验中说明。

查询方式的优点是硬件开销小,使用起来比较简单。

但在此方式下,CPU要不断地查询外设的状态,当外设未准备好时,CPU就只能循环等待,不能执行其它程序,这样就浪费了CPU的大量时间,降低了CPU的利用率。

为了解决这个矛盾,通常采用中断传送方式:即当CPU进行主程序操作时,外设的数据已存入输入端口的数据寄存器;或端口的数据输出寄存器已空,由外设通过接口电路向CPU发出中断请求信号,CPU在满足一定的条件下,暂停执行当前正在执行的主程序,转入执行相应能够进行输入/输出操作的子程序,待输入/输出操作执行完毕之后CPU再返回并继续执行原来被中断的主程序。

这样CPU就避免了把大量时间耗费在等待、查询状态信号的操作上,使其工作效率得以大大地提高。

能够向CPU发出中断请求的设备或事件称为中断源。

系统引入中断机制后,CPU与外设(甚至多个外设)处于“并行”工作状态,便于实现信息的实时处理和系统的故障处理。

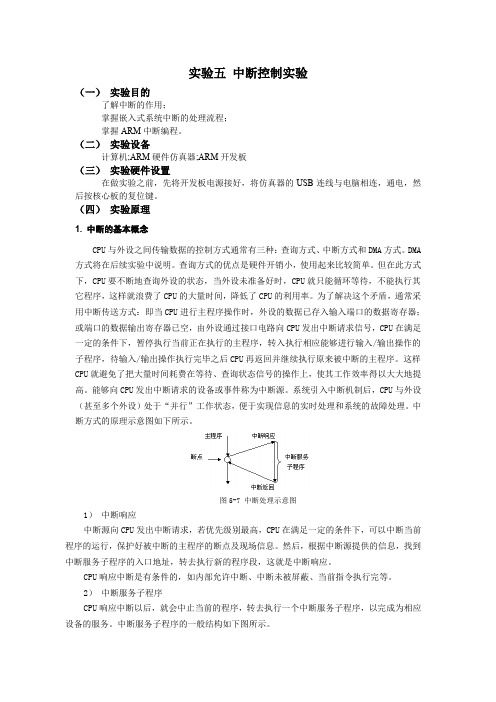

中断方式的原理示意图如下所示。

图5-7 中断处理示意图1)中断响应中断源向CPU发出中断请求,若优先级别最高,CPU在满足一定的条件下,可以中断当前程序的运行,保护好被中断的主程序的断点及现场信息。

然后,根据中断源提供的信息,找到中断服务子程序的入口地址,转去执行新的程序段,这就是中断响应。

CPU响应中断是有条件的,如内部允许中断、中断未被屏蔽、当前指令执行完等。

2)中断服务子程序CPU响应中断以后,就会中止当前的程序,转去执行一个中断服务子程序,以完成为相应设备的服务。

外部中断的实验报告

一、实验目的1. 理解外部中断的概念和作用。

2. 掌握外部中断的编程方法。

3. 熟悉中断处理程序的设计和调试。

二、实验原理外部中断是指由外部设备或信号产生的中断,用于处理与CPU无关的事件。

在微机系统中,外部中断通常用于处理输入/输出设备的中断请求。

外部中断分为可屏蔽中断和不可屏蔽中断两种类型。

三、实验环境1. 开发平台:Keil uVision 52. 微控制器:STM32F103C8T63. 外部设备:按钮、LED灯4. 连接方式:通过GPIO引脚连接四、实验步骤1. 设计外部中断电路(1)将按钮连接到STM32F103C8T6的GPIO引脚,例如PA0引脚。

(2)将LED灯连接到STM32F103C8T6的另一个GPIO引脚,例如PB0引脚。

2. 编写外部中断初始化程序(1)在Keil uVision 5中创建一个新项目,并添加STM32F103C8T6的起始代码。

(2)在主函数中编写初始化程序,包括以下步骤:a. 配置PA0引脚为输入模式,设置为浮空输入。

b. 配置PB0引脚为输出模式,用于控制LED灯。

c. 使能中断,设置中断优先级。

d. 配置NVIC(嵌套向量中断控制器)以允许外部中断。

3. 编写外部中断处理程序(1)在项目中添加一个新的C文件,用于编写外部中断处理程序。

(2)编写外部中断处理函数,当按钮按下时,触发中断,控制LED灯闪烁。

a. 初始化外部中断处理函数,设置中断优先级和中断触发方式。

b. 在外部中断处理函数中,编写LED灯控制代码,实现LED灯闪烁。

4. 编译并下载程序(1)编译项目,生成.hex文件。

(2)将.hex文件下载到STM32F103C8T6开发板上。

5. 测试实验结果(1)将按钮按下,观察LED灯是否闪烁。

(2)松开按钮,LED灯停止闪烁。

五、实验结果与分析1. 实验结果实验过程中,当按钮按下时,LED灯闪烁;松开按钮后,LED灯停止闪烁。

实验结果表明,外部中断能够正确地处理外部设备的中断请求,并控制LED灯的亮灭。

实验外部中断实验说明文档word精品文档6页

实验5外部中断实验说明文档外部中断硬件说明GPIO硬件说明STM32开发板引出了电路长的所有IO口,电路如下图 1 引出的IO口STM32的IO口可以通过软件配置为以下的8种模式(1)GPIO _Mode_AIN 模拟输入(2)GPIO_Mode_IN_FLOATING 浮空输入(3)GPIO_Mode_IPD 下拉输入(4)GPIO_Mode_IPU 上拉输入(5)GPIO_Mode_Out_OD开漏输出(6)GPIO_Mode_Out_PP 推挽输出(7)GPIO_Mode_AF_OD 复用开漏输出(8) GPIO_Mode_AF_PP复用开漏输出STM32的每个IO端口都有7个寄存器来控制,他们分别是:2个32位的端口,配置寄存器CRL和CRH;一个16位的复用寄存器BRR;2个32位的数据寄存器IDR和ODR;1个32位的锁存寄存器LCKR;详细资料可以参见<<STM32中文参考资料>>.LED硬件说明STM32 开发板上的两个LED:LED0 和LED1.如下图:图2 LED 与STM32 连接原理图STM32中硬件电路将PB5管脚与LED0灯连接,而另一LED灯LED1则是连接在PE5.由电路可知,两个LED都是通过灌电流的方式来加电压,所以应将相应的GPIO口配置为输出方式,通过合理的控制其连接的GPIO口的输出电压(置高置低)就能控制灯的闪烁(关于GPIO配置操作请详见GPIO固件库说明文档).BEEP硬件说明STM32 开发板上的一个BEEP.如下图:图1 BEEP与STM32 连接原理图STM32中硬件电路将PB8管脚与BEEP连接,电路中用到NPN三极管(s8050)来驱动蜂鸣器,三极管主要的功能是放大电流,让电路有足够的电流来驱动蜂鸣器.当PB.8输出高电平时,蜂鸣器开始发声,当PB.8输出低电平时,蜂鸣器停止发声.KEY硬件说明STM32 开发板上的4个按钮(WK_UP,KEY0,KEY1,KEY2)如下图:图1 KEY与STM32 连接原理图STM32中硬件电路将PE4与KEY0连接在按钮按下时电路接地为低电平, PE3与KEY1连接在按钮按下时电路接地为低电平, PE2与KEY2连接在按钮按下时电路接地为低电平, PA0与WK_UP连接在按钮按下时电路接地为高电平,由电路可知,本实验通过WK_UP在芯片内部拉低输入模式下检测高电平时控制键蜂鸣器的开关按键KEY0检测为低时候控制LEDO和LED1同时开关,按键KEY1控制LED1的开关,按键KEY2控制LED0的开关,有关配置GPIO口 (关于GPIO配置操作请详见GPIO固件库说明文档).EXTI说明STM32开发板有19个外部中断,在外部的IO口上有16个外部中断,分别如下图 1 GPIO口与外部中断映射图STM32的IO端对应16个外部中断,GPIOx.0- GPIOx.15其中(x=A,B,C,D,E,F)分别对应中断线,每个中断线最多对应七个IO口,而中断线每次只能连接到一个IO口上去,可在软件中去配置STM32上的每个IO口可以自由编程,需要以32位的字访问外部中断软件说明实验中用到了GPIO固件库函数和LED固件库的函数的总和,在引用MCU中的头文件后用到的GPIO函数以及LED函数如下GPIO中的库函数1)使能总线时钟void GpioRccEnable(GPIO_TypeDef* GPIOx);2)配置管脚为输入输出模式void GpioConfig(GPIO_TypeDef* GPIOx,uint16_t GPIO_Pin,GPIOMode_TypeDef mode,GPIOSpeed_TypeDef speed );3)设置某一端口为输入输出模式void GpioSet(GPIO_TypeDef* GPIOx,uint16_t GPIO_Pin,GPIOMode_TypeDef mode,GPIOSpeed_TypeDef speed );4)设置输入模式并初始化void GpioSetInMode(GPIO_TypeDef* GPIOx,uint16_t GPIO_Pin );5)设置输出模式并初始化void GpioSetOutMode(GPIO_TypeDef* GPIOx, uint16_t GPIO_Pin,char init_value);6)管脚的输出的值void GpioSetOutValue(GPIO_TypeDef* GPIOx,uint16_t GPIO_Pin, char init_value);7)读取某一管脚的状态unsigned char GpioInReadPinStatus(GPIO_TypeDef* GPIOx,uint16_t GPIO_Pin);LED中的库函数如下:1)初始化函数void LedInit(char led, char led_init_status);2)指定LED灯亮void LedOn(char led);3)灭掉指定的LED灯void LedOff(char led);BEEP中的库函数如下://功能: 初始化LEEP,并配置初始状态void BeepInit(char beep_init_status);//功能: 选定BEEP为开状态void BeepOn(void);//功能: 选定BEEP为关状态void BeepOff(void);按键中的库函数如下://IO初始化void KeyInit(void);//按键扫描函数u8 KeyScan(void);EXTI库函数如下:// 功能:使能外部时钟中断函数void ExtiRccEnable(uint32_t RCC_APB2Periph);// 功能:配置外部中断参数void ExtiConfig(uint32_t line,EXTIMode_TypeDef mode,EXTITrigger_TypeDef trigger,FunctionalState linecmd); // 功能:外部中断初始化void ExtiInit(void);外部中断应用简述实验中通过外部中断服务函数来检测按键是否按下来控制蜂鸣器和LED灯的亮灭,实验程序如下#include "common.h"int main()Init(); //总初始化while(1)printf("\n外部中断实验\r\n");delay_ms(1000);。

嵌入式技术及应用实验中断实验报告

实验步骤与结果分析1、建立工程1)、在工程文件中包含如下文件(int、doc、user、lib、start)2)、选择STM32F103VB芯片3)、分别添加如下文件2、运行过程(1) 使用Keil uVision3 通过ULINK仿真器连接EduKit-M3实验平台,打开实验例程NVIC_test子目录下的NVIC.Uv2例程,编译链接工程;(2) 点击MDK 的Debug菜单,选择Start/Stop Debug Session项或Ctrl+F5键,远程连接EduKit-M3实验平台并下载调试代码到目标系统的RAM中;(3) 程序正常启动运行后,会有以下结果:当第一次发生EXTI9 中断后(按下EduKit-M3实验平台上Key按钮),SysTick 中断的优先级比EXTI0中断优先级高。

因此当EXTI0中断发生时(按下Wakeup按钮),将先执行主要程序代码分析/* Configure one bit for preemption priority */NVIC_PriorityGroupConfig(NVIC_PriorityGroup_1);主从优先级的选择Group_1,有先占优先级1位,从优先级3位//配置一个比特为抢占优先级/* Enable the EXTI0 Interrupt */ //使能EXTI0中断NVIC_InitStructure.NVIC_IRQChannel = EXTI0_IRQChannel;NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = PreemptionPriorityValue;主优先级的选择PreemptionPriorityValueNVIC_InitStructure.NVIC_IRQChannelSubPriority = 0;//从优先级等于0.NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE;NVIC_Init(&NVIC_InitStructure);/* Enable the EXTI9_5 Interrupt */ //使能EXTI9_5中断NVIC_InitStructure.NVIC_IRQChannel = EXTI9_5_IRQChannel;NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 0;//EXTI9_5主优先级的选择等于0NVIC_InitStructure.NVIC_IRQChannelSubPriority = 1;//EXTI9_5主优先级的选择等于0NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE;NVIC_Init(&NVIC_InitStructure);/* Configure the SysTick Handler Priority: Preemption priority and sub priority */ //配置SysTick处理程序优先级:抢占优先级和子优先级NVIC_SystemHandlerPriorityConfig(SystemHandler_SysTick, !PreemptionPriorityValue, 0);while (1){if(PreemptionOccured != FALSE)//当PreemptionOccured != FALSE)抢占发生{GPIO_WriteBit(GPIOC, GPIO_Pin_6, (BitAction)(1 - GPIO_ReadOutputDataBit(GPIOC, GPIO_Pin_6)));Delay(0x5FFFF);GPIO_WriteBit(GPIOC, GPIO_Pin_7, (BitAction)(1 -GPIO_ReadOutputDataBit(GPIOC, GPIO_Pin_7)));Delay(0x5FFFF);GPIO_WriteBit(GPIOC, GPIO_Pin_8, (BitAction)(1 - GPIO_ReadOutputDataBit(GPIOC, GPIO_Pin_8)));Delay(0x5FFFF);GPIO_WriteBit(GPIOC, GPIO_Pin_9, (BitAction)(1 - GPIO_ReadOutputDataBit(GPIOC, GPIO_Pin_9)));Delay(0x5FFFF);}}void GPIO_Configuration(void){/* Configure PC6, PC7, PC8 and PC9 as output push-pull */ 使能为推挽输出GPIO_InitStructure.GPIO_Pin = GPIO_Pin_6 | GPIO_Pin_7 | GPIO_Pin_8 | GPIO_Pin_9;GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz; //使能其速度为50MHz GPIO_InitStructure.GPIO_Mode = GPIO_Mode_Out_PP; //使能为推挽输出GPIO_Init(GPIOC, &GPIO_InitStructure);/* Configure GPIOA Pin0 as input floating */GPIO_InitStructure.GPIO_Pin = GPIO_Pin_0;GPIO_InitStructure.GPIO_Mode = GPIO_Mode_IN_FLOATING; 使能为浮空输入GPIO_Init(GPIOA, &GPIO_InitStructure);/* Configure GPIOB Pin9 as input floating */GPIO_InitStructure.GPIO_Pin = GPIO_Pin_9;GPIO_InitStructure.GPIO_Mode = GPIO_Mode_IN_FLOATING; 使能为推挽输出入GPIO_Init(GPIOB, &GPIO_InitStructure);}GPIO_EXTILineConfig(GPIO_PortSourceGPIOA, GPIO_PinSource0);/* Configure EXTI Line0 to generate an interrupt on falling edge */ 配置EXTI Line0产生一个中断在下降沿EXTI_InitStructure.EXTI_Line = EXTI_Line0;EXTI_InitStructure.EXTI_Mode = EXTI_Mode_Interrupt;EXTI_InitStructure.EXTI_Trigger = EXTI_Trigger_Falling;EXTI_InitStructure.EXTI_LineCmd = ENABLE;EXTI_Init(&EXTI_InitStructure);(写不完时,可调整表结构。

《嵌入式系统原理与应用》实验报告04-外部中断实验

VICVectAddr=0x00;

}

void EINT3_init(void)//中断的初始化

{

PINSEL1=(PINSEL1 & 0xFFFFCFF)|0x300;

EXTMODE=EXPOLAR & 0x0E;

IO0CLR=0x01;

IO0DIR=0x01;//p0.1设为输出

while(1);

}

五、分析与讨论

六、教师评语

签名:

日期:

成绩

3. 熟悉LPC2000 系列ARM7 微控制器的GPIO控制。

二、实验设备(环境)及要求

硬件:PC机;

软件:PC机操作系统windows XP,ADS1.2集成开发环境,Proteus软件。

三、实验内容与步骤

实验内容:

设置P0.20脚为EINT3功能,初始化为向量中断,并设置为下降沿触发模式,然后等待外部中断。中断服务程序将LED灯控制输出信号取反,然后清除中断标志并退出中断。

《嵌入式系统原理与应用》实验报告

实验序号:4实验项目名称:外部中断实验

学 号

1207012117

姓 名

黄明

专业、班

1

实验地点

实验楼1#318

指导教师

黄鹏程

实验时间

4-28

一、实验目的

1. 掌握LPC2200 专用工程模板的使用;

2.熟悉LPC2000 系列ARM7 微控制器的VIC和外部中断的使用;

实验步骤:

四、实验结果与数据处理

源程序:

#include "config.h"

int i; /*全局变量*/

void __irq EINT3_ISR(void)//中断服务函数

外部中断实验报告

外部中断实验报告外部中断实验报告一、引言外部中断是计算机系统中的一种重要的中断方式,它可以使得计算机在执行某个任务的过程中,根据外部设备的信号来暂停当前任务,转而去处理其他紧急事件。

本实验旨在通过对外部中断的实验,深入了解外部中断的原理和应用。

二、实验目的1. 理解外部中断的概念和原理;2. 学会使用外部中断来处理外部设备的信号;3. 掌握外部中断的编程方法。

三、实验装置和材料1. 计算机硬件平台:使用一台支持外部中断的计算机;2. 软件平台:使用汇编语言进行编程。

四、实验步骤1. 连接外部设备:将外部设备(如键盘、鼠标等)与计算机相连接,确保外部设备可以正常工作;2. 编写中断处理程序:使用汇编语言编写中断处理程序,以响应外部设备的信号;3. 设置中断向量表:将中断处理程序的入口地址存放在中断向量表中,以便系统在接收到外部设备信号时能够正确地跳转到中断处理程序;4. 运行程序并测试:运行程序,触发外部设备的信号,观察中断处理程序是否能够正确执行。

五、实验结果与分析在实验中,我们成功地编写了一个外部中断处理程序,并将其入口地址存放在中断向量表中。

当我们触发外部设备的信号时,系统能够正确地跳转到中断处理程序,并执行相应的操作。

通过这个实验,我们深入了解了外部中断的原理和应用。

六、实验总结通过本次实验,我们对外部中断有了更深入的了解。

外部中断作为计算机系统中的一种重要中断方式,可以使计算机在执行某个任务的过程中,根据外部设备的信号来暂停当前任务,转而去处理其他紧急事件。

在实际应用中,外部中断广泛应用于各种设备的控制和通信系统中,提高了计算机系统的效率和可靠性。

七、实验心得通过本次实验,我深刻认识到了外部中断在计算机系统中的重要性。

在实验中,我不仅学会了编写中断处理程序,还了解了中断向量表的作用。

这次实验让我对计算机系统的工作原理有了更深入的了解,也提高了我的编程能力。

我相信这次实验对我的学习和将来的工作都有很大的帮助。

嵌入式中断实验

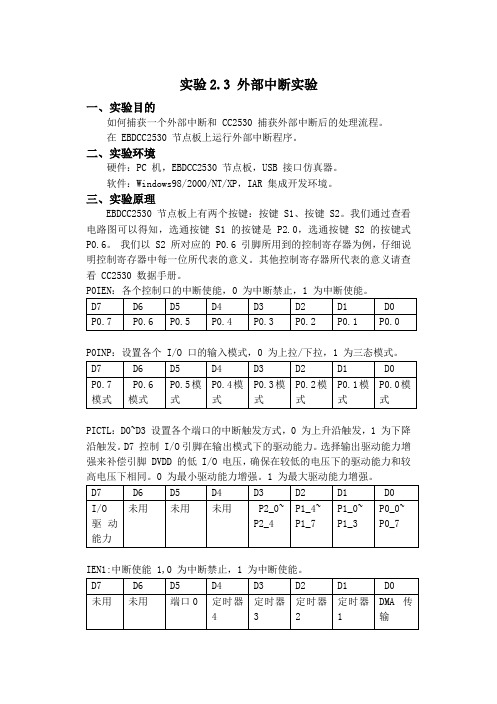

实验2.3 外部中断实验一、实验目的如何捕获一个外部中断和 CC2530 捕获外部中断后的处理流程。

在 EBDCC2530 节点板上运行外部中断程序。

二、实验环境硬件:PC 机,EBDCC2530 节点板,USB 接口仿真器。

软件:Windows98/2000/NT/XP,IAR 集成开发环境。

三、实验原理EBDCC2530 节点板上有两个按键:按键 S1、按键 S2。

我们通过查看电路图可以得知,选通按键 S1 的按键是 P2.0,选通按键 S2 的按键式P0.6。

我们以 S2 所对应的 P0.6 引脚所用到的控制寄存器为例,仔细说明控制寄存器中每一位所代表的意义。

其他控制寄存器所代表的意义请查看 CC2530 数据手册。

P0IEN:各个控制口的中断使能,0 为中断禁止,1 为中断使能。

D7 D6 D5 D4 D3 D2 D1 D0 P0.7 P0.6 P0.5 P0.4 P0.3 P0.2 P0.1 P0.0P0INP:设置各个 I/O 口的输入模式,0 为上拉/下拉,1 为三态模式。

D7 D6 D5 D4 D3 D2 D1 D0P0.7模式 P0.6模式P0.5模式P0.4模式P0.3模式P0.2模式P0.1模式P0.0模式PICTL:D0~D3 设置各个端口的中断触发方式,0 为上升沿触发,1 为下降沿触发。

D7 控制 I/O引脚在输出模式下的驱动能力。

选择输出驱动能力增强来补偿引脚 DVDD 的低 I/O 电压,确保在较低的电压下的驱动能力和较高电压下相同。

0 为最小驱动能力增强。

1 为最大驱动能力增强。

D7 D6 D5 D4 D3 D2 D1 D0I/O 驱动能力未用未用未用 P2_0~P2_4P1_4~P1_7P1_0~P1_3P0_0~P0_7IEN1:中断使能 1,0 为中断禁止,1 为中断使能。

D7 D6 D5 D4 D3 D2 D1 D0未用未用端口0 定时器4 定时器3定时器2定时器1DMA传输P0IFG :中断状态标志寄存器,当输入端口有中断请求时,相应的标志位将置 1。

外中断实验报告

外中断实验报告1. 实验目的本实验的目的是通过外中断的实验,加深对中断概念的理解,并掌握在单片机中使用外中断的方法和技巧。

2. 实验原理外中断是单片机系统中常用的一种中断方式。

当外部输入信号满足一定条件时,可以触发中断请求,从而打断当前正在执行的程序,转而执行中断服务程序。

外中断可以有效地处理实时性要求较高的任务。

3. 实验材料和器件本次实验所需材料和器件如下: - 单片机开发板 - 电脑 - 连接线4. 实验步骤4.1 准备工作首先,将单片机开发板与电脑通过连接线连接好,确保通信正常。

4.2 硬件连接将外部输入信号源连接至单片机的外部中断引脚,确保输入信号与单片机能够正常连接。

4.3 软件编程在单片机开发板上,选择合适的编程软件进行编程。

根据单片机的型号和开发板的特点,选择相应的编程语言进行编写。

4.4 编写中断服务程序根据实验要求,编写一个中断服务程序。

该程序在接收到外部中断请求时,能够对请求进行响应,并执行相应的操作。

4.5 编译和下载编译程序,生成可执行文件,并将该文件下载到单片机开发板上。

4.6 实验操作打开外部输入信号源,触发外部中断请求。

观察单片机开发板的输出,验证中断服务程序是否正确执行。

5. 实验结果与分析根据实验操作,我们成功触发了外部中断请求,并且中断服务程序正确执行。

这表明我们的实验设计和实施都是成功的。

6. 实验总结通过本次实验,我们深入了解了外中断的概念和原理,并通过实际操作掌握了外中断的使用方法和技巧。

外中断在单片机系统中具有广泛的应用场景,通过合理利用外中断,能够提高单片机系统的实时性能。

7. 实验注意事项•在进行硬件连接时,应确保信号连接正确,避免因连接错误导致中断请求无法触发。

•在编写中断服务程序时,应注意处理中断请求的时序和优先级,确保程序的正确性和可靠性。

•在实验过程中,应注意保护实验设备和材料,避免损坏或丢失。

8. 参考资料[1] 单片机原理与应用教程 [2] 51单片机外部中断原理及应用。

嵌入式系统实验报告-1-外部中断

《嵌入式系统技术》实训报告1、实验目的z了解S3C2440A 外部中断的工作原理。

z掌握S3C2440A 外部中断的使用方法。

2、实验设备z PC 机、Multi-ICE 仿真器、2440A 实验箱。

3、实验内容z通过外部K1、K2、K3、K4、K5、K7 按键触发外部中断E INT1、EINT2、EINT3、EINT4、EINT5、EINT74、实验原理4.1 ARM 的异常中断类型在嵌入式系统中外部设备的功能实现主要是靠中断机制来实现的。

中断功能可以解决CPU 内部运行速度远远快于外部总线速度而产生的等待延时问题。

ARM 提供的FIQ 和IRQ 异常中断用于外部设备向C PU 请求中断服务,一般情况下都是采用I RQ 中断。

七种异常中断中断过程框图4.2 异常中断响应过程和返回过程异常中断的响应过程:1).保存处理器当前状态寄存器C PSR 的值到备份程序状态寄存器S PSR 中。

2).设置但前程序状态寄存器CPSR 的值,其中包括:设置CPSR 响应位的值,使处理器进入特定的处理器模式;按要求屏蔽中断,通常应该屏蔽I RQ 中断。

在F IQ 中断时屏蔽F IQ 中断。

3).设置L r 寄存器。

将相应中断模式的L r 寄存器的值设为异常中断的返回地址。

4).处理程序计数器PC,将PC 值设为相应的中断向量的地址,从而实现跳转以执行中断服务程序。

异常中断的返回当处理器执行完以上流程之后,处理器已经从中断向量进入异常处理的状态。

异常中断处理完毕之后,在异常中断程序的末端,处理器进入异常中断的返回状态,其流程如下:1).恢复状态寄存器。

将保存的备份程序状态寄存器SPSR 值赋给当前程序状态寄存器CPSR。

2).将返回地址赋值到程序计数器(PC)。

这样程序将返回到异常中断产生的下一条指令或出现问题的指令处执行。

需要注意的是:对于不同的异常中断,其返回地址的计算方法也是不同的,IRQ 和F IQ 异常中断产生时,程序计数器PC 已经更新,而SWI 中断和未定义指令中断时由当前指令自身产生的,程序计数器P C 尚未更新,所以要计算出下一条指令的地址来执行返回操作;指令预取指中指异常中断和数据访问中断要求,返回到出现异常的执行现场,重新执行操作。

实验6 中断实验

一.中断处理机制

4 实验原理

非向量中断方式 中断源产生中断后,从0x18 处取指执行 0x18 中断服务入口

向量中断方式 中断源产生中断后,跳转到0x18 处,但由处理器 识别中断后自动填充总线,并忽略0x18 处指令, 执行总线上新的指令

0x18 中断服务入口

启动 --- 中断响应

26个中断源

SB3 3 4 GND

中断的产生分别来至按钮SB2和SB3,当按钮按下时, EXINT6或EXINT7和地连接,输入低电平,从而向CPU发出中断 请求。当CPU受理中断后,进入相应的中断服务程序,实现 LED1或LED2的显示功能。

硬件:BUTTON1(SB1202)--EINT6; BUTTON2(SB1203)--EINT7 编写中断服务程序实现LED对外中断号的编 码并在执成中断服务程序时打开蜂鸣器: 例如:EINT6发生,则LED4~1编码为:0110 即:LED4灭,LED3亮,LED2亮,LED1灭

实验3 中断实验

1实验目的 2实验设备 3实验内容 4实验原理 5实验操作步骤

1实验目的

通过实验了解ARM的中断方式和原理 熟悉ARM中断的编程方法。

2实验设备

硬件:Embest S3CEV40实验平台, Embest ARM标准/增强型仿真器套件, PC机。 软件:Embest IDE 2003集成开发环 境,Windows 98/2000/NT/XP。

EXTERNAL INTERRUPT PENDING REGISTER)

实验原理

d) 电路原理

NGCS4 23 R9 5 L E D1 NGCS5 24 R9 6

L E D2 VDD3 3 S3C4 4B0 X R1 11 E XINT 6 1 2 R1 12 E XINT 7 1 2 SB2 3 4 47

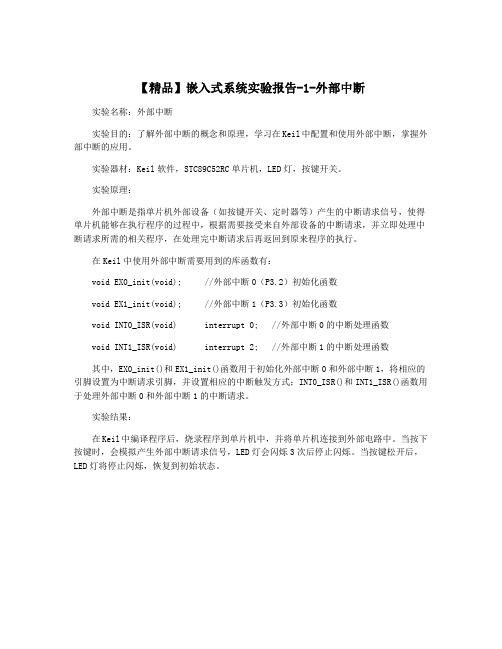

【精品】嵌入式系统实验报告-1-外部中断

【精品】嵌入式系统实验报告-1-外部中断实验名称:外部中断

实验目的:了解外部中断的概念和原理,学习在Keil中配置和使用外部中断,掌握外部中断的应用。

实验器材:Keil软件,STC89C52RC单片机,LED灯,按键开关。

实验原理:

外部中断是指单片机外部设备(如按键开关、定时器等)产生的中断请求信号,使得单片机能够在执行程序的过程中,根据需要接受来自外部设备的中断请求,并立即处理中断请求所需的相关程序,在处理完中断请求后再返回到原来程序的执行。

在Keil中使用外部中断需要用到的库函数有:

void EX0_init(void); //外部中断0(P3.2)初始化函数

void EX1_init(void); //外部中断1(P3.3)初始化函数

void INT0_ISR(void) interrupt 0; //外部中断0的中断处理函数

void INT1_ISR(void) interrupt 2; //外部中断1的中断处理函数

其中,EX0_init()和EX1_init()函数用于初始化外部中断0和外部中断1,将相应的引脚设置为中断请求引脚,并设置相应的中断触发方式;INT0_ISR()和INT1_ISR()函数用于处理外部中断0和外部中断1的中断请求。

实验结果:

在Keil中编译程序后,烧录程序到单片机中,并将单片机连接到外部电路中。

当按下按键时,会模拟产生外部中断请求信号,LED灯会闪烁3次后停止闪烁。

当按键松开后,LED灯将停止闪烁,恢复到初始状态。

实例(7)-外部中断

实验(7) 外部中断一、实验目的:1、了解单片机的中断系统。

2、掌握单片机的外部中断机制。

3、编程实现利用外部中断控制LED和蜂鸣器。

二、实验原理:2.1、中断系统中断是为使CPU具有对外界异步事件的处理能力而设置的。

所谓中断,是指CPU对系统中或系统外发生的某个事件的一种响应过程,即CPU暂时停止现行程序的执行,而自动转动执行预先安排好的处理该事件的服务子程序。

当处理结束后,再返回到被暂停程序的断点处,继续执行原来的程序。

实现这种中断功能的硬件系统和软件系统称为中断系统。

中断系统是计算机的重要组成部分。

实时控制、故障自动处理时往往用到中断系统,计算机与外部设备间传送数据及实现人机联系也常常采用中断方式。

学习中断系统时主要注意三个内容:中断源、中断服务程序、中断优先级。

CPU的中断系统一般允许有多个中断源,当几个中断源同时向CPU请求中断,要求为它服务的时候,这就存在CPU优先响应哪一个中断源请求的问题。

通常根据中断源的轻重缓急排队,优先处理最紧急的事件的中断源请求源,即规定每一个中断源有一个优先级别。

CPU总是先响应优先级别最高的中断请求。

下面两幅图分别是中断处理示意图和中断处理流程图。

图1 图22.2、中断嵌套当CPU正在处理一个中断源请求的时候(执行相应的中断服务程序),发生了另外一个优先级比它还高的中断请求。

如果CPU能够暂停对原来中断源的服务程序,转而去处理优先级更高的中断请求源,处理完之后,再回到原低级中断服务程序,这样的过程称为中断嵌套。

图3为中断嵌套的示意图。

图32.4、51单片机的中断源和中断优先级传统51单片机有5个中断请求,按优先级从高到低排序分别是:外部中断0(/INT0)、定时器0中断、外部中断1(/INT1)、定时器1中断、串口(UART)中断。

而增强型STC 51单片机在保留传统51单片机的中断结构之外,还额外增加了5个中断源。

其优先级仅接着前面5个中断源,从高到低分别是,A/D转换中断、低电压检测(LVD)中断、PCA中断、串口2中断及SPI中断。

外部中断应用实验

外部中断应用实验一、实验目的和要求1、掌握中断系统外部中断源的使用方法。

2、掌握延时程序的编程及使用方法。

3、掌握Proteus软件与Keil软件的使用方法。

4、掌握单片机系统的硬件和软件设计方法。

二、设计要求1、用Proteus软件画出电路原理图,在单片机的P1.0口线上接按键K0 ,作为外部中断源0使用,用于开启波形,在单片机的P1.1口线上接按键K1 ,作为外部中断源1使用,用于关闭波形。

2、在单片机的P1.2口线上产生周期50mS的连续方波,在P 1.2口线上接示波器观察波形。

三、电路原理图实验一电路原理图:实验二电路原理图:四、实验程序流程框图和程序清单汇编程序清单:程序框图:实验一:ORG 0000H START: LJMP MAINORG 0100HLJMP LOOP1;ORG 0003HLJMP EXINT0ORG 0013HLJMP EXINT1 MAIN: SETB EASETB IT0SETB IT1SETB EX0SETB EX1MOV SP, #2FH;MOV TMOD, #01H;MOV TH0, #9EH;MOV TL0, #58H; LOOP1: JNB TF0, LOOP1CPL P1.2;CLR TF0MOV TH0, #9EH;MOV TL0, #58H;EXINT0: SETB TR0RETIEXINT1: CLR TR0RETIEND思考题:ORG 0000HLJMP MAINORG 0003HLJMP EXTER0LJMP IPTOMAIN: MOV SP, #60HMOV TMOD, #01HMOV IE, #83HMOV TH0, #0B1HMOV TL0, #0E0HMOV R1, #02H HERE:LJMP HERE DELAY:SETB TR1HEREY:JNB TF1, HEREYCLR TR1CLR TF1MOV TH1, #0D8HMOV TL1, #0F0HRETEXTER0: JBC F0, LLSETB F0SETB TR0LJMP HHLL:CLR F0CLR TR0HH: RETIIPTO: DJNZ R1, LOOP3CPL P1.2CPL ACC.0JNB ACC.0, LOOP2MOV R1, #03HLJMP LOOP3LOOP2: MOV R1, #02H LOOP3: MOV TH0, #0B1HMOV TL0, #0E0HRETIENDC语言程序清单:#define uchar unsigned char #define uint unsigned int#include <reg52.h>sbit P1_2=P1^2;void delay(void) //误差0us {unsigned char a,b,c;for(c=1;c>0;c--)for(b=38;b>0;b--)for(a=130;a>0;a--); }void main(){EA=1;IT0=1;IT1=1;EX0=1;EX1=1;PX0=1;TMOD=0X01;TH0=0X9E;TL0=0X58;while(1){while(!TF0);P1_2=!P1_2;TF0=0;TH0=0X9E;TL0=0X58;}}void INTT0() interrupt 0{TR0=1;}void INTT1() interrupt 2{TR0=0;} 程序框图:思考题程序清单:#define uchar unsigned char #define uint unsigned int#include <reg52.h>sbit P1_2=P1^2;a=0;void main(){EA=1;IT0=1;EX0=1;PX0=1;TMOD=0X01;TH0=0X63;TL0=0XC0;while(1){while(!TF0);P1_2=!P1_2;TF0=0;TH0=0X15;TL0=0XA0;while(!TF0);P1_2=!P1_2;TF0=0;TH0=0X63;TL0=0XC0;}}void INTT0() interrupt 0{ a++;if(a%2)TR0=1;elseTR0=0;}五、实验结果:程序框图:六、实验总结:本次实验中,我学会了外部中断的使用,用按键控制定时器产生波形的开关,外部中断实验中,应该注意的是通过延时来消除抖动。

外部中断实验报告

一、实验目的1. 理解单片机外部中断的概念和工作原理。

2. 掌握MCS-51单片机外部中断的编程方法。

3. 通过实验验证外部中断在实际应用中的效果。

二、实验环境1. 实验设备:MCS-51单片机实验板、按键、LED灯、面包板、连接线等。

2. 开发环境:Keil uVision5软件。

三、实验原理外部中断是单片机的一个重要功能,用于响应外部事件。

当外部事件发生时,CPU可以暂停当前程序,转而执行中断服务程序,处理外部事件。

MCS-51单片机有两个外部中断源,即INT0和INT1。

四、实验内容1. 硬件连接将按键连接到单片机的INT0或INT1引脚,LED灯连接到单片机的某个I/O口。

具体连接方式如下:- 将按键的一端连接到单片机的INT0或INT1引脚,另一端连接到地。

- 将LED灯的正极连接到单片机的某个I/O口,负极连接到地。

2. 程序设计(1)初始化单片机```cvoid main() {EA = 1; // 开启总中断EX0 = 1; // 开启INT0中断IT0 = 1; // 设置INT0为下降沿触发P1 = 0xFF; // 初始化P1口为高电平,关闭LED灯 while(1) {// 主循环}}```(2)编写中断服务程序```cvoid ext0_isr() interrupt 0 {P1 = 0x00; // 点亮LED灯delay(500); // 延时0.5秒P1 = 0xFF; // 熄灭LED灯}```(3)编写延时函数```cvoid delay(unsigned int ms) {unsigned int i, j;for(i = 0; i < ms; i++)for(j = 0; j < 123; j++);}```3. 实验步骤1. 编写程序,并使用Keil uVision5软件进行编译和烧录。

2. 将程序烧录到单片机中,并连接好硬件电路。

3. 按下按键,观察LED灯是否闪烁。

实验3-外部中断实验报告

实验3-外部中断实验报告实验 3 外部中断实验报告一、实验目的本次实验的主要目的是深入理解外部中断的工作原理和应用,通过实际操作掌握外部中断的配置和编程方法,提高对微控制器中断处理机制的认识和应用能力。

二、实验设备1、开发板:_____型号开发板。

2、编程软件:_____。

3、电脑:具备相应接口和操作系统。

三、实验原理外部中断是指由外部事件引起的微控制器中断。

当外部中断引脚检测到特定的电平变化(如从高电平变为低电平或从低电平变为高电平)时,微控制器会暂停当前正在执行的程序,转而执行中断服务程序(ISR)来处理外部事件。

在本次实验中,我们使用了开发板上的特定引脚作为外部中断输入引脚,并通过配置相关寄存器来设置中断触发方式、优先级等参数。

四、实验步骤1、硬件连接将外部中断源(如按键)连接到开发板的指定引脚。

确保开发板与电脑正确连接,以便进行编程和调试。

2、软件编程打开编程软件,创建新的项目。

配置微控制器的时钟、引脚等基本设置。

编写中断初始化函数,设置中断触发方式、优先级等。

编写中断服务程序,定义在中断发生时需要执行的操作。

3、编译与下载对编写好的程序进行编译,检查是否存在语法错误。

将编译成功的程序下载到开发板中。

4、实验测试按下连接的按键,观察开发板的响应,如指示灯的变化、数据的输出等。

五、实验结果与分析1、当按下按键时,开发板能够准确地响应外部中断,执行中断服务程序。

在中断服务程序中,我们设置了指示灯的状态变化,通过观察指示灯的闪烁情况,可以确认中断是否被正确触发和处理。

2、对不同的中断触发方式(如下降沿触发、上升沿触发等)进行测试,结果均符合预期。

这表明我们对中断触发方式的配置是正确的。

3、调整中断的优先级,观察不同优先级中断之间的响应顺序。

在实验中,高优先级的中断能够优先得到处理,符合微控制器中断处理的优先级机制。

六、遇到的问题及解决方法1、问题:在初次编程时,中断服务程序没有被正确执行。

解决方法:仔细检查中断初始化函数中的参数设置,确保中断触发方式、优先级等配置正确。

外部中断实验实验报告

外部中断实验实验报告外部中断实验实验报告引言外部中断是计算机系统中一种常见的中断方式,可以在程序执行过程中接收外部信号并及时中断当前任务进行处理。

本实验旨在通过搭建外部中断实验电路,了解外部中断的原理和应用,并通过实际操作验证其正确性和可行性。

实验目的1. 了解外部中断的原理和工作方式;2. 掌握外部中断的搭建方法和步骤;3. 验证外部中断的正确性和可行性。

实验器材1. 电脑;2. Arduino开发板;3. 按键开关;4. 连接线。

实验步骤1. 将Arduino开发板与电脑通过USB数据线连接,并打开Arduino开发环境;2. 在Arduino开发环境中,编写一个简单的程序,用于接收外部中断信号;3. 将按键开关的引脚与Arduino开发板的数字引脚相连,确保按键开关可以通过Arduino开发板进行控制;4. 将按键开关的另一端连接到Arduino开发板上的中断引脚(如INT0或INT1);5. 上传程序到Arduino开发板,并确保程序正常运行;6. 按下按键开关,观察程序是否能够正确接收并处理外部中断信号;7. 重复步骤6,多次测试外部中断的可靠性和稳定性。

实验结果经过多次测试和观察,实验结果表明外部中断能够正常工作并正确接收外部中断信号。

当按下按键开关时,程序能够及时中断当前任务,并执行相应的中断处理程序。

实验结果与理论预期相符。

实验分析外部中断是计算机系统中一种重要的中断方式,广泛应用于各种实时控制系统和交互式设备中。

通过本次实验,我们深入了解了外部中断的原理和工作方式,并通过实际操作验证了其正确性和可行性。

在实验过程中,我们使用Arduino开发板搭建了一个简单的外部中断实验电路,并编写了相应的程序进行测试。

通过按下按键开关,我们成功触发了外部中断信号,并观察到程序能够及时中断当前任务,并执行相应的中断处理程序。

这表明外部中断能够在实际应用中起到及时响应外部信号的作用,提高了系统的实时性和可靠性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

地址异常类型进入时的模式进入时 I 的状态进入时 F 的状态0x00000000复位管理禁止禁止0x00000004未定义指令未定义I F 0x00000008软件中断管理禁止F 0x0000000C 中止(预取)中止I F 0x00000010中止(数据)中止I F 0x00000014保留保留--实验三 外部中断实验一、实验目的理解ARM 处理器中断原理;掌握中断服务子程序,中断中现场的保护和恢复以及中断的返回程序的编写方法;利用中断方式,实现键盘中断流程。

二、实验原理本实验以键盘中断为例,介绍 ARM 微处理器中断处理过程。

设定编程预期的实验现象:系统启动后,按 12345678 任意键,相应的八段数码管就会显示相应的数字。

三、主要实验设备1.硬件:宿主机、ARM 教学试验箱;2.软件:Windows 操作系统、ADS1.2集成开发环境。

四、实验内容1.首先设置中断向量表,见表4.1。

表 4.1 ARM 中断向量表每当一个中断发生后,ARM 处理器便强制把程序计数器(PC )指针置为向量表中对应中断类型所对应的地址值。

由于ARM微处理器每个中断向量中只有4个字节的大小,所以通常在中断向量位置存放1条跳转指令或存放1条直接对程序计数器(PC)寄存器赋值的指令,使程序能跳转到相应的异常中断处理程序中执行。

如果中断处理程序所在的物理地址小于32MB,可使用B跳转指令;当跳转范围大于32MB 时,需使用LDR指令。

对于程序中未使用的中断,可使中断异常跳转到一个只含返回指令的哑函数或跳转到自身标号地址处,以防止中断异常引起系统的混乱。

比如:Undefined_HandlerB Undefined_Handler下面代码为 ARM 微处理器中断向量表的初始化过程。

B Reset_Handler ; //跳转复位 0x0000,0000 复位管理模式B Undefined_Handler ; //跳转未定义指令 0x0000,0004 未定义指令未定义模式B SWI_Handler ; //跳转软件中断 0x0000,0008 软件中断管理模式B Prefetch_Handler ; //跳转预取指令 0x0000,000C 预取指令中止模式B DataAbort_Handler ; //跳转数据异常 0x0000,0010 中止模式NOP ; //延时保留B IRQ_Handler ; //跳转 IRQ(中断请求) 0x0000,0018 IRQB FIQ_Handler ; // 跳转 FIQ(快速中断请求) 0x0000,001C FIQ从表4.1分析可知,NOP 一定不能去掉,必须要保证中断向量表正确建立。

当然,ARM 微处理器中断向量表的初始化工作也可以写成如下形式:LDR PC,=Reset_Handler ; //跳转复位 0x0000,0000 复位管理模式LDR PC,=Undef_instrution_Handler ; //跳转未定义指令0x0000,0004 未定义指令未定义模式LDR PC,=SWI_Handler ; //跳转软件中断 0x0000,0008 软件中断管理模式LDR PC,=Prefetch_Handler ; //跳转预取指令 0x0000,000C 预取指令中止模式LDR PC,=Abort_Handler ; //跳转数据异常 0x0000,0010 中止模式NOP ; //延时保留LDR PC,=IRQ_Handler ; //跳转 IRQ(中断请求)0x0000,0018 IRQLDR PC,=FIQ_Handler ; // 跳转 FIQ(快速中断请求)0x0000,001C FIQ2.中断处理过程GPIO、堆栈、内存等初始化过程在实验一中已经介绍过,下面重点对中断初始化过程作详细分析:处理器要对中断进行处理时,需要对CPSR的IRQ和FIQ与ICMR(中断控制器屏蔽寄存器)相应的中断屏蔽位进行正确的配置:即当CPSR的IRQ、FIQ位为“0”时,ARM 处理器可以响应IRQ、FIQ 中断,如果为“1”时,ARM 处理器将不响应IRQ或FIQ中断。

同样,当ICMR的相应位为“1”时,相应的中断被开启,为“0”时,相应的中断被屏蔽。

中断控制器处理中断架构如图4.1所示,该图为某个中断请求进入中断控制器后,被成功响应时的 IRQ 和 FIQ 的流程图。

如果在中断开启的情况下,即中断屏蔽寄存器ICMR相应的位置“1”时,当中断源产生中断时,中断请求寄存器ICPR相应的中断源所对应位会被设置 1。

发出的中断请求通过中断级别控制寄存器ICLR相应的设置将产生IRQ或FIQ中断,同时该中断请求会发送到IRQ中断请求寄存器ICIP或FIQ中断请求ICFR上。

中断请求将以IRQ或FIQ异常中断方式进行处理。

即中断控制器根据中断向量表,跳转到相应的中断服务例程中处理中断请求。

开启IRQ中断,使得ARM处理器可以响应外部中断。

图4.1为中断控制器处理功能架构。

图4.1 中断控制器处理功能架构代码如下:/***************************;Enable & Set Interrupt;***************************/mrs r1, CPSR ; //读取 CPSR 寄存器值bic r1, r1,#0x80 ; //将 r1 的位[7]置 0,可以响应 IRQ 中断msr CPSR_c, r1; //设置 CPSR 寄存器的 I 位为 0,可以响应 IRQ 中断通过mrs指令,将CPSR(当前程序状态寄存器)的值读取到r1寄存器当中,将r1当中的位CPSR[7]设置为“0”,准备开启IRQ外部中断。

通过msr命令,将r1当中的值写入到cpsr寄存器当中,将cpsr[IRQ](CPSR的IRQ)位设置为“0”,使得 ARM 处理器可以响应 IRQ 外部中断。

键盘中断开启过程:ldr r1, =ICMR ; //读取中断控制屏蔽寄存器ldr r2, =init_ICMR ; // init_ICMR=0x00000010str r2,[r1] ; //开启键盘中断,屏蔽其他所有中断上述代码实际上完成将 init_ICMR 值(0x00000010)送到中断屏蔽寄存器 ICMR 中,实现开启键盘中断响应。

表4.2是ICMR中断控制器屏蔽寄存器的位功能表。

表4.2 ICMR中断控制器屏蔽寄存器位功能表ICMR 寄存器用于开启或者屏蔽相应的中断,当将 ICMR 相应的位设置为“1”时,开启相应的中断,将 ICMR 寄存器相应的位设置为“0”时,屏蔽响应的中断,比如将 ICMR[4]设置为“1”时,开启键盘中断之后,ARM 处理器就可以响应键盘中断。

可以参考《Intel PXA27x Processor Family Developer’s Manual》P25-20页。

3.程序流程图主程序流程图如图4.2所示。

图 4.2 主程序流程图从图4.3中断流程图可知,当没有外部中断发生时,程序一直运行在主程序的while循环当中,一旦中断发生,程序运行到中断向量表中,通过中断向量表来判断中断的类型,来判断需要执行哪个中断处理程序。

下面为中断处理程序的 C 语言代码:__irq void IRQ_Handler(void) //中断处理函数{IRQ_Function();}一旦外部中断触发时,ARM处理器通过自己的硬件特性,执行到中断向量表,通过触发的中断类型来判断到底执行两个中断处理函数,在这里只打开了键盘中断,属于外部中断,当键盘被按下,便产生键盘中断,程序跳转到IRQ_Handler函数处运行,即__irq void IRQ_Handler 伪代码处,IRQ_Function()流程图如下图所示:图 4.3 中断服务程序处理流程在执行中断处理程序时,通过矩阵键盘的寄存器的值,获取之后,对获取到的 i 进行判断。

要判断矩阵键盘的哪个值被按下,需要对KPAS 的低 8 位来判断,其中 KPAS 的 0~3 位代表行,KPAS 的 4~7 位代表列被按下。

表4.3 KPAS中断控制器屏蔽寄存器位功能表中断处理程序:void IRQ_Function(void){char i;unsigned short int kbd_buff;i = KPAS_VALUE; //读取矩阵键盘寄存器当中的值,switch (i){ case 0x00: // 键盘的1键被按下kbd_buff=0x8F79; //LED_CS2 = kbd_buff; //第一个数码管显示1,其他数码管为灭 LED_CS3 = 0x8F8F; //break;case 0x01: //键盘的2键被按下LED_CS2 = kbd_buff; //第二个数码管显示2,其他数码管为灭 LED_CS3 = 0x8F8F; //break;case 0x02: //键盘的3键被按下kbd_buff=0x8F30; //LED_CS3 = kbd_buff; //第三个数码管显示3,其他数码管为灭 LED_CS2 = 0x8F8F; //break;case 0x10: //键盘的4键被按下kbd_buff=0x198F; //LED_CS3 = kbd_buff; //第四个数码管显示4,其他数码管显示为灭LED_CS2 = 0x8F8F; //break;case 0x11: //键盘的5键被按下kbd_buff=0x8F12;LED_CS2 = kbd_buff; //第一个数码管显示为5,其他数码管显示为灭LED_CS3 = 0x8F8F; //break;case 0x12: //键盘的6键被按下kbd_buff=0x028F;LED_CS2 = kbd_buff; //第二个数码管显示为6,其他数码管显示为灭LED_CS3 = 0x8F8F; //break;case 0x20: //键盘的7键被按下,LED_CS3 = kbd_buff; //第三个数码管显示为7,其他数码管显示为灭LED_CS2 = 0x8F8F; //break;case 0x21: //键盘的8键被按下kbd_buff=0x008F; //LED_CS3 = kbd_buff; //第四个数码管显示为8,其他数码管显示为灭LED_CS2 = 0x8F8F; //break;default: break;}结合以上说明,对本实验所提供的汇编源代码进行分析,深入理解针对具体的硬件实现,软件是如何配合工作的。

五、实验总结1.根据实验结果,总结编程中的要点。