nRF24LE1F16Q24 Schematic and Layout

毕业论文--智能小区车辆统计技术系统设计[管理资料]

![毕业论文--智能小区车辆统计技术系统设计[管理资料]](https://img.taocdn.com/s3/m/519362b0336c1eb91b375dd7.png)

1绪论随着社会经济的不断发展,国民生活水平的不断提高,兼具速度与舒适的车辆逐渐成为人们的代步工具。

然而对具有着各种大量车辆出入的小区物业而言,车辆的管理日益成为日常事务中的一项重要的工作内容。

由于车辆的激增,尤其是私家车数量的成倍增长,小区内交通堵塞、车辆擦挂等现象常有发生,小区内居民矛盾不断激化。

如何让管理人员了解小区内的车辆状况,对突发事件采取合适的措施,提高工作效率等就成了个小区物业期待解决的一个课题。

信息化是全球的趋势和潮流,是国家社会经济发展的必然选择。

在信息化和数字化的背景下小区物业车辆管理的信息化也将是不可阻挡的发展方向。

加快小区物业车辆管理车辆管理信息化的进程对改进现代化生活具有非同一般的意义。

智能小区车辆统计技术系统就是一款针对小区物业车辆管理的一套系统,它大大提高了小区物业车辆管理人员的工作效率,彻底改变了效率低下、漏洞百出的人工统计方式,也极大地减少了所需要的费用。

只要有车辆进出小区便会自动计数,并且当车辆达到小区所能容纳车辆的上限时便会自动报警,是一种能够为小区物业管理人员极大地减少工作量、节约成本的有效方式。

就当前车辆的数量以及未来国家的发展前景来看,人们对车辆仍然具有极大的需求,不得不说,小区车辆统计系统是一种颇有前景的管理方式。

小区车辆管理现状仍然有诸多问题,而我国目前车辆统计、计数系统只在大的工业环境及高速公路等有限场合存在,而忽略了与人民生活息息相关的小区车辆统计系统;即便个别小区具备了类似的系统而其昂贵的价格使得其难以推广。

因此迫切需要一种即经济实惠,又能解决这一问题的新的方法。

在进行了相关的调查了解后,我有了一些对于车辆统计计数的想法,查找了相关资料后发现,在现在的条件下这些想法是完全可以实现的。

本论文所研究的内容正好弥补了现阶段小区车辆统计的这一空白。

目前国内外在车辆检测系统中,大量应用了电磁传感技术、超声传感技术、视频检测技术、计算机技术、通信技术等高新科学技术。

NRF24LE1_CN简介

立即发布市场联系人:Anne Strand电话:+47 22 51 10 62传真:+47 22 51 10 99电邮地址:Anne.Strand@nordicsemi.no网址:新产品: 2.4GHz超低功耗系统芯片,其中包含nRF24L01+收发器、8位微控制器和闪存Nordic半导体推出世界上最小、集成度最高的单片超低功耗2.4GHz无线系统芯片-nRF24LE1Nordic半导体的nRF24LE1在尺寸方面超过了以前的超低功率(ULP)系统芯片(SoC):它把产业界中最好的2.4GHz收发器核(nRF24L01+)和一个8位混合信号微控制器与闪存集成在一块芯片上,用于超低功耗无线系统。

这个独一无二的芯片使用QFN封装,尺寸为4×4mm,是目前尺寸最小的单片超低功耗无线解决办法。

对于迅速发展的超低功耗无线市场,nRF24LE1是理想的芯片,因为它能够在一块芯片上运行RF协议堆栈和应用层。

挪威奥斯陆-2008年9月9日-Nordic半导体(奥斯陆证件交易所代号:NOD)今日推出nRF24LE1,这是2.4GHz的超低功耗无线系统芯片,用这个办法时,只需要一块芯片就可以实现无线应用系统。

用于超低功耗无线通信的系统芯片在nRF24LE1中,集成了一个功能齐全的2.4GHz收发器核nRF24L01+,并且包含Nordic公司经过实用证明的Enhanced ShockBurst™型硬件链接层。

nRF24LE1的最大电流很小,可以用钮扣电池供电,真正地实现了超低功耗。

在nRF24LE1中,还有一个加强型8051混合信号微控制器核,与以前的8051器件相比,它执行一条指令的时钟周期较少。

大多数指令只需要一个或者两个时钟周期,因而按照MIPS(每秒百万条指令)测试标准,它的性能平均提高了8倍。

这个优异性能与芯片上的16KB闪存和1KB的SRAM结合起来,保证了这个处理平台足以运行RF协议栈和应用层,而且运行起来十分容易。

nrf24l01(2.4G模块)

NRF24L01(2.4G模块)一、模块简介(1)2.4GHz全球开放ISM频段免许可证使用。

(2)最高工作速率2Mbps,高效GFSK调制,抗干扰能力强。

(3)126频道,满足多点通信和跳频通信需要。

(4)内置硬件CRC检错,和点对点通信地址控制。

(5)低功耗,1.9-3.6V工作,待机模式下22uA;掉电模式900nA。

(6)内置2.4GHz天线,体积小巧:15mm×29mm。

(7)模块可软件设置地址,只有收到本机地址时才会输出数据(提供中断提示),可直接接各种单片机使用,软件编程非常方便。

(8)内稳压电路,使用各种电源包括DC/DC开关电源均有很好的通道效果。

(9)2.54mm间距接口,DIP封闭。

(10)工作于Enhanced ShockBurst具有Automatic packet handling,Auto packet transaction handling,具有可选的内置包应答机制,极大地降低丢包率。

(11)与51单片机P0口连接的时候,需要加10K的上拉电阻,与其余口连接不需要。

(12)其他系列的单片机,如果是5V的,请参考该系列单片机IO口输出电流大小,如果超过10mA,需要串联电阻分压,否则容易烧毁模块!如果是3.3V的,可以直接和RF24L01模块的IO口线连接。

比如AVR系列单片机。

如果是5V的一般串接2K的电阻。

二、接口电路说明:1)VCC脚接电压范围为:1.9V-3.6V,不能在这个敬意之外,超过3.6V将会烧毁模块。

推荐电压3.3左右。

2)除电源VCC和接地端,其余脚都可以直接和普通的5V单片机IO口直接相连,无需转换。

当然对3V左右的单片机更加适用了。

3)硬件上面没有SPI的单片机也可以控制本模块,用普通单片机IO口模拟SPI,不需要单片机真正的串口介入,只需要普通的单片机IO口就可以了,当然用串口也可以。

4)如果需要其他封装接口,比如密脚插针,或者其他形式的接口,可联系我们定做。

nRF24LE1H 详细编程电路图 烧写电路

nRF24LE1 Flash/OTP Programming Adapter Kit User Guide Liability disclaimer

Nordic Semiconductor ASA reserves the right to make changes without further notice to the product to improve reliability, function or design. Nordic Semiconductor ASA does not assume any liability arising out of the application or use of any product or circuits described herein.

Figure 1. Kit content nRF24LE1 Flash/OTP Programming Adapter Kit content: • • 1 Programming Adapter Module 1 Printed Getting Started Guide

Revision 1.1

Main office: Otto Nielsens veg 12 7004 Trondheim Norway Phone: +47 72 89 89 00 Fax: +47 72 89 89 89

Revision History

Date December 2011 October 2009 Version 1.1 1.0 Description Removed references to the CD User Guide

nRFgo nRF24LE1 Flash/OTP Programming Adapter Kit

nRF24LE1芯片简单介绍

nRF24LE1芯片简单介绍NRF24LE1特性NRF24LE1采用了NORDIC最新的无线和超低功耗技术,在一个极小封装中集成了包括2.4G无线传输,增强型51 FLASH高速单片机,丰富外设及接口等的单片FLASH芯片,是一个综合了性能及成本的完美结合,很适合应用于各种2.4G的产品设计。

NRF24LE1=2.4GHz+Flash51+ADC+PWM+I2C+RTC+WDT+RNG+AES++COMP+UART+SPI….应用:无线鼠标,无线键盘,无线摇杆,PC外设,玩具,RFID,无线遥控,医学参数监测,线数字语音,工业控制及无线数据采集主要特性:1、内嵌 2.4GHz低功耗无线收发内核NRF24L01+, 250kbps,1Mbps,2Mbps空中速率2、高性能51内核,16kbytes Flash,1Kbyte data RAM,1Kbyte NVRAM3、具有丰富的外设资源,内置128bit AES硬件加密,32位硬件乘除处理器,6-12位ADC,两路PWM,I2C,UART,硬件随机数产生器件,WDT,RTC,模拟比较器4、提供QFN24,QFN32,QFN48多种封装,提供灵活应用选择5、灵活高效的开发手段,支持Keil C,ISP下载,是开发无线外设,RFID,消费产品,无线数传等有力工具及平台。

带Gazell协议Gazell协议是NORDIC专为2.4G无线桌面和其他无线应用设计推出的无线通信协议,配合NRF24LE1/NRF24LU1P使用,客户可以专注于应用设计,无需花费大量的精力在无线链路上。

低功耗Gazell协议是低功耗协议,可设计为纽扣电池供电的应用。

抗干扰性Gazell协议完成自动跳频及抗干扰的无线通信,具有在复杂环境下优异的抗干扰性能。

低延时Gazell协议充分利用NRF高速通信的特性,具有低延时特性,特别满足PC周边及其他应用。

高安全性Gazell协议具有AES 128bit 高强度加密,确保数据传输的安全可靠。

NRF24L01详细教程

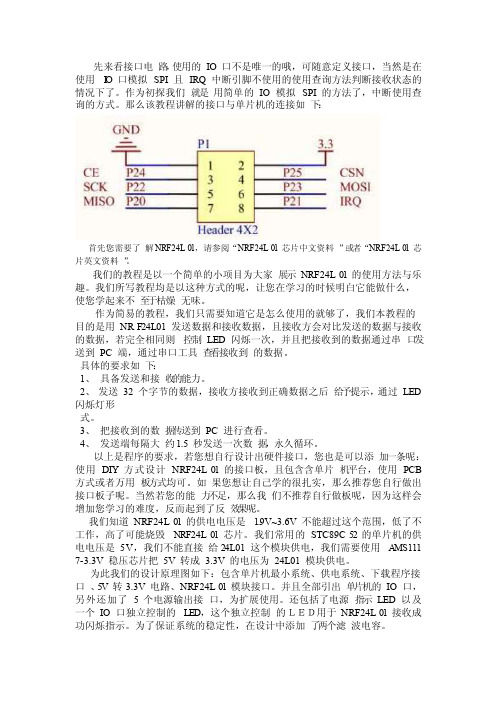

先来看接口电路,使用的IO 口不是唯一的哦,可随意定义接口,当然是在使用 I O 口模拟SPI 且IRQ 中断引脚不使用的使用查询方法判断接收状态的情况下了。

作为初探我们就是用简单的IO 模拟SPI 的方法了,中断使用查询的方式。

那么该教程讲解的接口与单片机的连接如下:首先您需要了解NRF24L01,请参阅“NRF24L01 芯片中文资料”或者“NRF24L01 芯片英文资料”。

我们的教程是以一个简单的小项目为大家展示NRF24L01 的使用方法与乐趣。

我们所写教程均是以这种方式的呢,让您在学习的时候明白它能做什么,使您学起来不至于枯燥无味。

作为简易的教程,我们只需要知道它是怎么使用的就够了,我们本教程的目的是用NRF24L01发送数据和接收数据,且接收方会对比发送的数据与接收的数据,若完全相同则控制LED 闪烁一次,并且把接收到的数据通过串口发送到PC 端,通过串口工具查看接收到的数据。

具体的要求如下:1、具备发送和接收的能力。

2、发送32 个字节的数据,接收方接收到正确数据之后给予提示,通过LED 闪烁灯形式。

3、把接收到的数据传送到PC 进行查看。

4、发送端每隔大约1.5 秒发送一次数据,永久循环。

以上是程序的要求,若您想自行设计出硬件接口,您也是可以添加一条呢:使用DIY 方式设计NRF24L01 的接口板,且包含含单片机平台,使用PCB 方式或者万用板方式均可。

如果您想让自己学的很扎实,那么推荐您自行做出接口板子呢。

当然若您的能力不足,那么我们不推荐自行做板呢,因为这样会增加您学习的难度,反而起到了反效果呢。

我们知道NRF24L01 的供电电压是 1.9V~3.6V 不能超过这个范围,低了不工作,高了可能烧毁 NRF24L01 芯片。

我们常用的STC89C52 的单片机的供电电压是5V,我们不能直接给24L01这个模块供电,我们需要使用 A MS1117-3.3V 稳压芯片把5V 转成3.3V 的电压为24L01 模块供电。

nRF24L01主要参数及电路图

nRF24L01 主要参数及电路图

nRF24L01 是由NORDIC 生产的工作在2.4GHz~2.5GHz 的ISM 频段的单片无线收发器芯片。

无线收发器包括:频率发生器、增强型SchockBurst 模式控制器、功率放大器、晶体振荡器、调制器和解调器。

输出功率频道选择和协议的设置可以通过SPI 接口进行设置。

几乎可以连接到各种单片机芯片,并完成无线数据传送工作。

极低的电流消耗:当工作在发射模式下发射功率为0dBm 时电流消耗为11.3mA ,接收模式时为12.3mA,掉电模式和待机模式下电流消耗更低。

nRF24L01 性能参数

小体积,QFN20 4x4mm 封装

宽电压工作范围,1.9V~3.6V,输入引脚可承受5V 电压输入。

nRF24E1英文

2.4Ghz RF transceiver with embedded8051 compatible microcontroller and 9 input, 10 bit ADC)($785(6•nRF2401 2.4GHz RF transceiver•8051 compatible microcontroller•9 input 10 bit ADC 100Kspls/s•Single 1.9V to 3.6V supply•Internal voltage regulators• 2 µA standby with wakeup ontimer or external pin•Internal VDD monitoring•Supplied in 36 pin QFN (6x6mm)package•7$%/( 2) &217(171GENERAL DESCRIPTION (4)1.1Quick Reference Data (4)1.2Block Diagram (5)1.3Pin Diagram (6)1.4Glossary of Terms (7)2ARCHITECTURAL OVERVIEW (8)2.1Microcontroller (8)2.2PWM (9)2.3SPI (9)2.4Port Logic (9)2.5Power Management (10)2.6RTC Wakeup Timer, Watchdog and RC Oscillator (10)2.7XTAL Oscillator (10)2.8AD Converter (10)2.9Radio Transceiver (11)3I/O PORTS (12)3.1I/O port behavior during RESET (12)3.2Port 0 (P0) (12)3.3Port 1 (P1 or SPI port) (13)4nRF2401 2.4GHz TRANSCEIVER SUBSYSTEM (16)4.1RADIO port (Port 2) (16)4.2Modes of operation (18)4.3Device configuration (24)4.4Data package Description (32)4.5Important RF Timing Data (33)5A/D CONVERTER (38)5.1A/D converter subsystem block diagram (38)5.2A/D converter registers (39)5.3A/D converter usage (40)6PWM (42)7INTERRUPTS (43)7.1Interrupt SFRs (43)7.2Interrupt Processing (46)7.3Interrupt Masking (47)7.4Interrupt Priorities (47)7.5Interrupt Sampling (48)7.6Interrupt Latency (48)7.7Interrupt Latency from Power Down State (48)7.8Single-Step Operation (48)8WAKEUP TIMER AND WATCHDOG (49)8.1Tick calibration (49)8.2RTC Wakeup timer (49)8.3Watchdog (50)8.4Reset (51)9POWER SAVING MODES (52)9.1Idle Mode (53)9.2Stop Mode (53)9.3Power down mode (53)10MICROCONTROLLER (55)10.1Memory Organization (55)10.2Program format in external EEPROM (56)10.3Instruction Set (57)10.4Instruction Timing (63)10.5Dual Data Pointers (63)10.6Special Function Registers (64)10.7SFR registers unique to nRF24E1 (67)10.8Timers/Counters (69)10.9Serial Interface (77)11ELECTRICAL SPECIFICATIONS (86)12PACKAGE OUTLINE (88)13ABSOLUTE MAXIMUM RATINGS (89)14Peripheral RF Information (90)15Table of Figures (91)16Table of Tables (91)17DEFINITIONS (94)*(1(5$/ '(6&5,37,21The nRF24E1 is a nRF2401 2.4GHz radio transceiver with an embedded 8051 compatible microcontroller and a 10-bit 9 input 100 kSPS AD converter. The circuit is supplied by only one voltage in range 1.9V to 3.6V. The nRF24E1 supports the proprietary and innovative modes of the nRF2401 such as ShockBurst™ and DuoCeiver™.4XLFN 5HIHUHQFH 'DWD3DUDPHWHU9DOXH8QLW Minimum supply voltage 1.9V Temperature range-40 to +85° C Maximum RF output power0dBmRF receiver sensitivity-90dBm Maximum RF burst data rate1000kbpsSupply current for microcontroller @ 16MHz @3V3mASupply current for ADC @100 kSPS0.9mASupply current for RF transmit @ -5dBm output power10.5mASupply current for RF receive18mASupply current in Power Down mode2µΑmax CPU clock frequency20MHzmax AD conversion rate100kSPSADC Differential nonlinearity (DNL)±0.5LSBADC Integral nonlinearity (INL)±0.75LSBADC Spurious free dynamic range (SFDR)65dB Package36 pin QFN 6x6Table 1-1 : nRF24E1 quick reference data7\SH 1XPEHU'HVFULSWLRQ9HUVLRQNRF24E1 IC36 pin QFN 6x6ANRF24E1-EVKIT Evaluation kit TBD 1.0 Table 1-2 : nRF24E1 ordering information%ORFN 'LDJUDPFigure 1-1 nRF24E1 block diagram plus external components3LQ 'LDJUDP',2 ',2 '9''',2',2 966;& ;&9669''$,1$,1$,1$5()$17$179''B3$9''',1 $,1 $,1 9669'',5()$,1 $,19663LQ1DPH3LQ IXQFWLRQ'HVFULSWLRQ1VDD Power Power Supply (1.9-3.6 V DC)2AIN0Analog input ADC input 03DVDD2RegulatedpowerDigital Power Supply , must be connected toregulator output DVDD4DIO0Digital I/O P1.0 (Port 1, bit 0)5DIO1Digital I/O P1.1 (Port 1, bit 1)6DIO2Digital I/O P0.0 (Port 0, bit 0)7DIO3Digital I/O P0.1 (Port 0, bit 1)8DIO4Digital I/O P0.2 (Port 0, bit 2)9DIO5Digital I/O P0.3 (Port 0, bit 3)10DIO6Digital I/O P0.4 (Port 0, bit 4)11DIO7Digital I/O P0.5 (Port 0, bit 5)12DIO8Digital I/O P0.6 (Port 0, bit 6)13DIO9Digital I/O P0.7 (Port 0, bit 7)14DVDD RegulatoroutputDigital voltage regulator output fordecoupling and feed to DVVD215VSS Power Ground (0V)16XC2Analog output Crystal Pin 217XC1Analog input Crystal Pin 118VDD_PA Regulatoroutput DC supply (+1.8V) to RF Power Amplifier (ANT1,ANT2) only19ANT1RF Antenna interface 120ANT2RF Antenna interface 221VSS_PA Power Ground (0V)22VDD Power Power Supply (1.9-3.6 V DC)23VSS Power Ground (0V)24AIN7Analog input ADC input 725AIN6Analog input ADC input 626AIN5Analog input ADC input 527IREF Analog input Connection to external Bias reference resistor 28AREF Analog input ADC reference voltage29AIN4Analog input ADC input 430AIN3Analog input ADC input 331VSS Power Ground (0V)32VDD Power Power Supply (1.9-3.6 V DC)33VSS Power Ground (0V)34AIN2Analog input ADC input 235AIN1Analog input ADC input 136DIN0Digital input P1.2 (Port 1, bit 2)Table 1-3 : nRF24E1 pin function*ORVVDU\ RI 7HUPV7HUP'HVFULSWLRQADC Analog to Digital ConverterCLK ClockCRC Cyclic Redundancy CheckCS Chip SelectCE Chip EnableDR Data ReadyGFSK Gaussian Frequency Shift KeyingGPIO General Purpose In OutISM Industrial-Scientific-MedicalkSPS kilo Samples per SecondMCU MicrocontrollerOD OverdriveP0 (or P1)(8051) In / Out Port 0 (or Port 1)PWM Pulse Width ModulationPWR_DWN Power DownPWR_UP Power UpRTC Real Time ClockRX ReceiveSFR(8051) Special Function RegisterSPI Serial Peripheral InterfaceST_BY StandbyTX TransmitXTAL Crystal (oscillator)$5&+,7(&785$/ 29(59,(:This section will give a brief overview of each of the blocks in the block diagram in Figure 1-1.0LFURFRQWUROOHUThe nRF24E1 microcontroller is instruction set compatible with the industry standard 8051. Instruction timing is slightly different from the industry standard, typically each instruction will use from 4 to 20 clock cycles, compared with 12 to 48 for the “standard”. The interrupt controller is extended to support 5 additional interrupt sources; ADC, SPI, RF receiver 1, RF receiver 2 and wakeup timer. There are also 3 timers which are 8052 compatible, plus some extensions, in the microcontroller core. An 8051 compatible UART that can use timer1 or timer2 for baud rate generation in the traditional asynchronous modes is included. The CPU is equipped with 2 data pointers to facilitate easier moving of data in the XRAM area, which is a common 8051 extension. The microcontroller clock is derived directly from the crystal oscillator.0HPRU\ FRQILJXUDWLRQThe microcontroller has a 256 byte data ram (8052 compatible, with the upper half only addressable by register indirect addressing). A small ROM of 512 bytes, contains a bootstrap loader that is executed automatically after power on reset or if initiated by software later. The user program is normally loaded into a 4k byte RAM1 from an external serial EEPROM by the bootstrap loader. The 4k byte RAM may also (partially) be used for data storage in some applications.%RRW ((3520 )/$6+If the mask ROM option is not used, the program code for the device must be loaded from an external non-volatile memory. The default boot loader expects this to be a “generic 25320” EEPROM with SPI interface. These memories are available from several vendors with supply ranges down to 1.8V. The SPI interface uses the pins DIN0 (EEPROM SDO), DIO0 (EEPROM SCK), DIO1 (EEPROM SDI) and DIO2 (EEPROM CSN). When the boot is completed, the DIN0, DIO0 and DIO1 pins may be used for other purposes such as other SPI devices or GPIO.5HJLVWHU PDSThe SFR (Special Function Registers) control several of the features of the nRF24E1. Most of the nRF24E1 SFRs are identical to the standard 8051 SFRs. However, there are additional SFRs that control features that are not available in the standard 8051. The SFR map is shown in the table below. The registers with grey background are registers with industry standard 8051 behavior. Note that the function of P0 and P1 are somewhat different from the “standard” even if the conventional addresses (0x80 and 0x90) are used1Optionally this 4k block of memory can be configured as 2k mask ROM and 2k RAM or 4 k mask ROM; ; ; ; ; ; ; ; ) EIP) B( EIE( ACC' EICON' PSW& T2CON RCAP2L RCAP2H TL2TH2&% IP T1_1V2T2_1V2DEV_OFFSET% RSTREAS SPI_DATASPI_CTRLSPICLKTICK_DVCK_CTRLTEST_MODE$ IE PWMCON PWMDUTYREGX_MSBREGX_LSBREGX_CTRL$ RADIO(P2)ADCCON ADCDATAHADCDATALADCSTATICSCON SBUFP1EXIF MPAGE P0_DIR P0_ALT P1_DIR P1_ALT TCON TMOD TL0TL1TH0TH1CKCON SPC_FNC P0SP DPL0DPH0DPL1DPH1DPS PCONTable 2-1 : SFR Register map3:0The nRF24E1 has one programmable PWM output, which is the alternate functionof PO.7 at pin DIO9.The resolution of the PWM is software programmable to 6, 7 or 8 bits.The frequency of the PWM signal is programmable via a 6 bit prescaler from the XTAL oscillator.The duty cycle is programmable between 0% and 100% via one 8-bit register.63,nRF24E1 features a simple single buffered SPI master. The 3 lines of the SPI bus (SDI, SCK and SDO) are multiplexed (by writing to register SPI_CTRL) between the GPIO pins (DIN0, DIO0 and DIO1) and the RF transceiver. The SPI hardware does not generate any chip select signal. The programmer will typically use GPIO bits (from port P0) to act as chip selects for one or more external SPI devices. When the SPI interfaces the RF transceiver, the chip selects are available in an internal GPIO port, P2.3RUW /RJLFThe device has 1 general purpose input and 10 general purpose bi-directional pins. These are by default configured as GPIO pins controlled by the ports P0 (DIO2 to DIO9) and P1 (DIO0, DIO1, DIN0) of the microcontroller.Most of the GPIO pins can be used for multiple purposes under program control. The alternate functions include two external interrupts, UART RXD and TXD, a SPI master port, three enable/count signals for the timers and the PWM output.3RZHU 0DQDJHPHQWThe nRF24E1 can be set into a low power down mode under program control, and also the ADC and RF subsystems can be turned on or off under program control. The CPU will stop, but all RAM’s and registers maintain their values. The low power RC oscillator is running, and so are the watchdog and the RTC wakeup timer (if enabled by software). The current consumption in this mode is typically 2µA.The device can exit the power down mode by an external pin interrupt (INT0_N or INT1_N) if enabled, by the wakeup timer if enabled or by a watchdog reset.57& :DNHXS 7LPHU :DWFKGRJ DQG 5& 2VFLOODWRUThe nRF24E1 contains a low power RC oscillator which can not be disabled, so it will run continuously as long as VDD 9RTC Wakeup Timer and Watchdog are two 16 bit programmable timers that run on the RC oscillator LP_OSC clock. The resolution of the watchdog and wakeup timer is programmable from approximately 300µs to approximately 80ms. By default the resolution is 10ms. The wakeup timer can be started and stopped by user software. The watchdog is disabled after a reset, but if activated it can not be disabled again, except by another reset;7$/ 2VFLOODWRUBoth the microcontroller, ADC and RF front end run on a crystal oscillator generated clock. A range of crystals frequencies from 4 to 20 MHz may be utilised, but 16 MHz is recommended since it gives best over all performance. For details, please see Crystal Specification on page 90. The oscillator may be started and stopped as requested by software.$' &RQYHUWHUThe nRF24E1 AD converter has 10 bit dynamic range and linearity with a conversion time of 48 CPU instruction cycles per 10-bit result.The reference for the AD converter is software selectable between the AREF input and an internal 1.22V bandgap reference.The converter has 9 inputs selectable by software. Selecting one of the inputs 0 to 7 will convert the voltage on the respective AIN0 to AIN7 pin.Input 8 enables software to monitor the nRF24E1 supply voltage by converting an internal input that is VDD/3 with the 1.22V internal reference selected.The AD converter is typically used in a start/stop mode. The sampling time is then under software control.The converter is by default configured as 10 bits. For special requirements, the AD converter can be configured by software to perform 6, 8 or 12 bit conversions. The converter may also be used in differential mode with AIN0 used as inverting input and one of the other 7 external inputs used as noninverting input. In that case the conversion time can be reduced to approximately 2 µs.5DGLR 7UDQVFHLYHUThe transceiver part of the circuit has identical functionality to the nRF2401 single chip RF transceiver. It is accessed through an internal parallel port and / or an internal SPI. The data ready signals for each DuoCeiver™ receiver output can be programmed as interrupts to the microcontroller or polled via a GPIO port.nRF2401 is a radio transceiver for the world wide 2.4 - 2.5 GHz ISM band. The transceiver consists of a fully integrated frequency synthesizer, a power amplifier, a modulator and two receiver units. Output power and frequency channels and other RF parameters are easily programmable by use of the RADIO register, SFR 0xA0. RF current consumption is only 10.5 mA in TX mode (output power -5dBm) and 18 mA in RX mode. For power saving the transceiver can be turned on / off under software control. Further information about the nRF2401 chip can be found at our website KWWS ZZZ QYOVL QR, 2 32576The nRF24E1 have two IO ports located at the default locations for P0 and P1 in standard 8051, but the ports are fully bi-directional CMOS and the direction of each pin is controlled by a _DIR and an _ALT bit for each bit as shown in the table below.Pin Default function Alternate=1SPI_CTRL=01DIN0P1.2SPI_DIDIO0P1.0T2 (timer2 input)SPI_SCKDIO1P1.1SPI_DODIO2P0.02EEPROM_CSNDIO3P0.1RXD (UART)DIO4P0.2TXD (UART)DIO5P0.3INT0_N(interrupt)DIO6P0.4INT1_N(interrupt)DIO7P0.5T0 (timer0 input)DIO8P0.6T1 (timer1 input)DIO9P0.7PWMTable 3-1 : Port functions, 2 SRUW EHKDYLRU GXULQJ 5(6(7During the period the internal reset is active (regardless of whether or not the clock is running), all the port pins are configured as inputs. When program execution starts, the DIO ports are still configured as inputs and the program will need to set the _ALT and/or the _DIR register for the pins that should be used as outputs.3RUW 3P0_ALT and P0_DIR control the P0 port function in that order of priority. If the alternate function for port p0.n is set (by P0_ALT.n = 1) the pin will be input or output as required by the alternate function (UART, external interrupt, timer inputs or PWM output), except that the UART RXD direction will still depend on P0_DIR.1.To use INT0_N or INT1_N, the corresponding alternate function must be activated,P0_ALT.3 / P0_ALT.4When the P0_ALT.n is not set, bit ‘n’ of the port is a GPIO function with the direction controlled by P0_DIR.n.P0.0 is always a GPIO. It will be activated by the default boot loader after reset and should be connected to the CSN of the boot flash.2Reserved for use as EEPROM_CSN, works as GPIO P0.0 independent of the “Alternate setting”'DWD LQ 3 B$/7 Q 3 B',5 Q3LQP0.0(DIO2)P0.0Out P0.0In P0.0Out P0.0InP0.1(DIO3)RXD Out RXD In P0.1Out P0.1InP0.2(DIO4)TXD Out TXD Out P0.2Out P0.2InP0.3(DIO5)INT0_N In INT0_N In P0.3Out P0.3InP0.4(DIO6)INT1_N In INT1_N In P0.4Out P0.4InP0.5(DIO7)T0In T0In P0.5Out P0.5InP0.6(DIO8)T1In T1In P0.6Out P0.6InP0.7(DIO9)PWM Out PWM Out P0.7Out P0.7In Table 3-2 : Port 0 (P0) functionsPort 0 is controlled by SFR-registers 0x80, 0x94 and 0x95 listed in the table below.$GGU 6)5 KH[ 5 : ELW,QLWKH[1DPH)XQFWLRQ80R/W8FF P0Port 0, pins DIO9 to DIO294R/W8FF P0_DIR Direction for each bit of Port 00: Output, 1: InputDirection is overridden if alternatefunction is selected for a pin.95R/W800P0_ALT Select alternate functions for each pin ofP0, if corresponding bit in P0_ALT is set,as listed in Table 3-2 : Port 0 (P0)functions, P0.0 has no alternatefunction,as it is intended as CS forexternal boot flash memory. It willfunction as a GPIO bit regardless ofP0_ALT.0Table 3-3 : Port 0 control and data SFR-registers3RUW 3 RU 63, SRUWThe P1 port consists of only 3 pins, one of which is an hardwired input. The function is controlled by SPI_CTRL.When SPI_CTRL is 01, the port is used as a SPI master port. The GPIO bits in port P0may be used as chip select(s).When not used as SPI port, P0_ALT.0 will force P1.0 to be the timer T2 input, P1.1 is now a GPIO. When P0_ALT.0 is 0, also P1.0 is a GPIO.P1.2 (DIN0) is always an input.63,B&75/3 B$/7 Q3LQ63,B&75/3 B$/7 Q3 B',5 Q 3 B',5 Q P1.0(DIO0)SCK Out T2In P1.0In P1.0Out P1.1(DIO1)SDO Out P1.1In 3P1.1In P1.1Out P1.2(DIN0)SDI In P1.2InP1.2InP1.2InTable 3-4 : Port 1 (P1) functionsPort 1 is controlled by SFR-registers 0x90, 0x96 and 0x97, and only the 3 lower bits of the registers are used.$GGU 6)5 KH[ 5 : ELW ,QLW KH[ 1DPH )XQFWLRQ90R/W 3FF P1Port 1, pins DIN0, DIO1 and DIO096R/W3FFP1_DIRDirection for each bit of Port 10: Output, 1: InputDirection is overridden if alternate function is selected for a pin, or if SPI_CTRL=01.bit0, DIN0 is always input.97R/W 300P1_ALT Select alternate functions for each pin of P1if corresponding bit in P1_ALT is set, as listed in Table 3-4 : Port 1 (P1) functions If SPI_CTRL is ‘01’, the P1 port is used as SPI master data and clock :2 -> MISO – input to nRF24E1 from slave 1 -> MOSI – output from nRF24E1 to slave 0 -> SCK – output from nRF24E1 to slaveTable 3-5 : Port 1 control and data SFR-registers3P1.1 is actually under control of P1_DIR.1 even when P1_ALT.1 is 1, since there is no alternatefunction for this pin.P1 may also be configured as a SPI master port , and is then controlled by the 3 SFR registers 0xB2, 0xB3, 0xB4 as shown in the table below.$GGU 6)5 KH[ 5:ELW,QLWKH[1DPH)XQFWLRQB2R/W80SPI_DATA SPI data input/outputB3R/W20SPI_CTRL00 -> SPI not used no clock generated01 -> SPI connected to port P1 (as for booting)another GPIO must be used as chip select(see also Table 3-4 : Port 1 (P1) functions)10 -> SPI connected to RADIOtransmitter/receiver 1 for TX or RX or fortransceiver configuration11 -> SPI connected to RADIO receiver 2 for RXChip select is a bit of RADIO register (seeTable 4-2 : RADIO register )B4R/W20SPICLK Divider factor from CPU clock to SPI clock00: 1/8 of CPU clock frequency01: 1/16 of CPU clock frequency10: 1/32 of CPU clock frequency11: 1/64 of CPU clock frequencyThe CPU clock is the oscillator generated clockdescribed in Crystal Specification page 90 Table 3-6 : SPI control and data SFR-registersQ5) *+] 75$16&(,9(5 68%6<67(05$',2 SRUW 3RUWThe transceiver is controlled by the RADIO port. The RADIO port uses the address normally used by port P2 in standard 8051. However since the radio transceiver is on chip, the port is not bi-directional. The power on default values in the port “latch” also differs from traditional 8051 to match the requirements of the radio transceiver subsystem.Operation of the transceiver is controlled by SFR registers RADIO and SPI_CTRL:$GGU 6)5 KH[ 5 : ELW,QLWYDOXHKH[1DPH)XQFWLRQA0R/W880RADIO General purpose IO for interface tonRF2401 radio transceiver subsystem B3R/W20SPI_CTRL00 -> SPI not used01 -> SPI connected to port P1 (boot)10 -> SPI connected to nRF2401 CH111 -> SPI connected to nRF2401 RXCH2Table 4-1 : nRF2401 2.4GHz transceiver subsystem control registers - SFR 0xA0 and 0xB3The bits of the RADIO register correspond to similar pins of the nRF2401 single chip, as shown in Table 4-2 : RADIO register . In the documentation the pin names are used, so please note that setting or reading any of these nRF2401 pins, means to write or read the RADIO SFR register accordingly. Please also note that in the transceiver documentation the notation MCU means the onchip 8051 compatible microcontroller. RADIO register bit corresponding pin name onsingle chip nRF24012.4GHz Transceiver5HDG7: 0 (not used)6: DR2, data ready from receiver 2 (available alsoas interrupt)DR25: CLK2, clock for receiver 2 data out CLK24: DOUT2, data out from receiver 2DOUT23: 0 (not used)2: DR1, data ready from receiver 1 (available alsoas interrupt)DR11: CLK1, clock for receiver 1 data out CLK10: DATA, data out from receiver 1DATA:ULWH7: PWR_UP, power on radio PWR_UP6: CE, Activate RX or TX mode CE5: CLK2, clock for receiver 2 data out CLK24: Not used3: CS, Chip select configuration mode CS2: Not used1: CLK1, clock for data input or receiver 1 data out CLK10: DATA, configuration or TX data input DATATable 4-2 : RADIO register - SFR 0xA0Note : Some of the pins are overridden when SPI_CTRL=1x, see Table 4-3 : Transceiver SPI interface.&RQWUROOLQJ WKH WUDQVFHLYHU YLD 63, LQWHUIDFHIt is more convenient to use the built-in SPI interface to do the most common transceiver operations as RF configuration and ShockBurst™ RX or TX. Please see Table 3-6 : SPI control and data SFR-registers for use of SPI interface. The radio port will be connected in different ways to the SPI hardware when SPI_CTRL is ‘1x’. When SPI_CTRL is ‘0x’, all radio pins are connected directly to their respective port pins.SPI signal SPI_CTRL=10 (binary)SPI_CTRL=11CS (active high)RADIO_wr.6 (CE) for ShockBurst™RADIO_wr.3 (CS) for ConfigurationRADIO_wr.6 (CE)SCK nRF2401/CLK1nRF2401/CLK2 SDI nRF2401/DATA nRF2401/DOUT2 SDO nRF2401/DATA not usedShockBurst™ data ready RADIO_rd.2 (DR1)RADIO_rd.6(DR2)Table 4-3 : Transceiver SPI interface.5$',2 SRUW EHKDYLRU GXULQJ 5(6(7During the period the internal reset is active (regardless of whether or not the clock is running), the RADIO outputs that control the nRF2401 transceiver subsystem are forced to their respective default values (RADIO.3=0 (CS), RADIO.6=0 (CE) RADIO.7=1 (PWR_UP)). When program execution starts, these ports will remain at those default levels until the programmer actively changes them by writing to the RADIO register.0RGHV RI RSHUDWLRQ2YHUYLHZThe nRF2401 subsystem can be set in the following main modes depending on three control pins:0RGH PWR_UP CE CSActive (RX/TX)110Configuration101Stand by100Power down0X XTable 4-4 nRF2401 subsystem main modes$FWLYH PRGHVThe nRF2401 subsystem has two active (RX/TX) modes:•ShockBurst™•Direct Mode (not supported by nRF24E1)The device functionality in these modes is decided by the content of a configuration word. This configuration word is presented in the configuration section. Please note that Direct mode is not supported, as this will require a more powerful CPU than 8051.6KRFN%XUVWThe ShockBurst™ technology uses on-chip FIFO to clock in data at a low data rateand transmit at a very high rate thus enabling extremely power reduction.When operating the nRF2401 subsystem in ShockBurst™, you gain access to the high data rates (1 Mbps) offered by the 2.4 GHz band without the need of a costly, high-speed microcontroller (MCU) for data processing.By putting all high speed signal processing related to RF protocol on-chip, thenRF24E1 offers the following benefits:•Highly reduced current consumption•Lower system cost (facilitates use of less expensive microcontroller)•Greatly reduced risk of ‘on-air’ collisions due to short transmission timeThe nRF2401 subsystem can be programmed using a simple 3-wire interface wherethe data rate is decided by the speed of the CPU.By allowing the digital part of the application to run at low speed while maximizingthe data rate on the RF link, the ShockBurst™ mode reduces the average current consumption in applications considerably.4.2.3.1ShockBurst™ principleWhen the nRF2401 subsystem is configured in ShockBurst™, TX or RX operation is conducted in the following way (10 kbps for the example only).TM1Mbps Figure 4-2Clocking in data with CPU and sending with ShockBurst™ technology020406080100120140160180200220240Time mSFigure 4-3 RF Current consumption with & without ShockBurst™ technologyData content of registers:Figure 4-4 Flow Chart ShockBurst™ Transmit of nRF2401 subsystem4.2.3.2ShockBurst™ Transmit:4.2.3.2.1CPU interface pins: CE, CLK1, DATA1.When the application CPU has data to send, set CE high. This activatesRF2401 on-board data processing.2.The address of the receiving node (RX address) and payload data isclocked into the nRF2401 subsystem. The application protocol or CPU setsthe speed <1Mbps (ex: 10kbps).3.CPU sets CE low, this activates a ShockBurst™ transmission.4.ShockBurst™:•RF front end is powered up•RF package is completed (preamble added, CRC calculated)•Data is transmitted at high speed (250 kbps or 1 Mbps configured by user).•nRF2401 subsystem returns to stand-by when finishedData content of registers:Figure 4-5 Flow Chart ShockBurst™ Receive of nRF2401 subsystem4.2.3.3 ShockBurst™ Receive:4.2.3.3.1 CPU interface pins: CE, DR1, CLK1 and DATA (one RX channel receive)1. Correct address and size of payload of incoming RF packages are set when nRF2401 subsystem is configured to ShockBurst™ RX.2. To activate RX, set CE high.3. After 200 µs settling, nRF2401 subsystem is monitoring the air for incoming communication.4. When a valid package has been received (correct address and CRC found),nRF2401 subsystem removes the preamble, address and CRC bits.5. nRF2401 subsystem then notifies (interrupts) the CPU by setting the DR1pin high.6. CPU may set the CE low to disable the RF front end (low current mode).7. The CPU will clock out just the payload data at a suitable rate (ex. 10kbps).8. When all payload data is retrieved nRF2401 subsystem sets DR1 low again, and is ready for new incoming data package if CE is kept high during data download. If the CE was set low, a new start up sequence can begin, see Figure 4-14. 'XR&HLYHU 6LPXOWDQHRXV 7ZR &KDQQHO 5HFHLYH 0RGHIn ShockBurst™ mode the nRF24E1 can facilitate simultaneous reception of two parallel independent frequency channels at the maximum data rate.This means:• nRF24E1 can receive data from two 1 Mbps transmitters (ex: nRF24E1,nRF2401 or nRF2402) 8 MHz (8 frequency channels) apart through one antenna interface.• The output from the two data channels is fed to two separate sets of interface pins.• Data channel 1: CLK1, DATA, and DR1• Data channel 2: CLK2, DOUT2, and DR2The DuoCeiver™ technology provides 2 separate dedicated data channels for RX andreplaces the need for two, stand alone receiver systems.Figure 4-6 Simultaneous 2 channel receive on nRF24E1There is one absolute requirement for using the second data channel. For the nRF24E1to be able to receive at the second data channel the frequency channel must be 8MHz higher than the frequency of data channel 1. The nRF2401 subsystem must be。

nRF24L01无线模块讲解解析

增强型的ShockBurst TM 模式

• nRF24L01配置为增强型的ShockBurst TM 模式 下时,只 要MCU有数据要发送,nRF24L01就会自动启动 ShockBurst TM模式来发送数据。在发送完数据后 nRF24L01转到接收模式,并等待终端的应答信号。如果 没有收到应答信号,nRF24L01将重发相同的数据包,直 到收到应答信号或重发次数超过SETUP_RETR_ARC寄 存器中设置的值为止,如果重发次数超过了设定值,则产 生MAX_RT中断。 • 只要接收到确认信号,nRF24L01就认为最后一包数据已 经发送成功(接收方已经收到数据),把TX FIFO中的数 据清除掉并产生TX_DS中断(IRQ引脚置高)。

增强型ShockBurstTM 接收模式

• 1、 ShockBurstTM 接收模式是通过设置寄存器中 PRIM_RX 位为高来选择的。准备接收数据的通道必须被 使能(EN_RXADDR 寄存器),所有工作在增强型 ShockBurstTM 模式下的数据通道的自动应答功能是由 (EN_AA 寄存器)来使能的,有效数据宽度是由 RX_PW_Px 寄存器来设置的。地址的建立过程见增强型 ShockBurstTM 发送章节。 • 2、 接收模式由设置CE 为高来启动。 • 3、 130us 后nRF24L01 开始检测空中信息。

数据通道

• 数据通道0 是唯一的一个可以配置为40 位自身地址的数据通道。1~5 数据通道都为8 位自身地址和32 位公用地址。所有的数据通道都可以 设置为增强型ShockBurst 模式。

寄存器配置

• nRF24L01所有的寄存器都是通过SPI口进行配置的(寄存器配置详见 附件)。CSN为低后,SPI接口等待指令执行。每一条指令都必须通 过一次CSN由高到低的变化。 • SPI指令格式:

NRF24L01模块系列说明书

答:原厂给的标准收发演示例程,有 51 PIC STM32 的,都是标准 C 语言编写, 因此即使移植其它单片机也很快

14 问:拿到模块和程序后,自己焊接测试电路和移植程序,下载进去后通讯不 了。

答:首先不用怀疑模块的问题。生产工艺成熟,不良率在不测试时候低于 1%, 何况全部测试,不良率低于千分之一。大部分新手自己焊接电路移植程序不良是 因为移植时候硬件错误或者软件增删错误引起,因为即使很小点错误,也能导致 整个程序的失效,所以建议自己移植程序时候要很小心,尽量照搬我们的例程, 等整个程序跑起来再做修改。若实在搞不定,可以借用我们的测试板,或者付出 很少费用就能买到配套的测试板,这样能给客户节省不少的时间。

11 问 NRF24L01 系列模块可以一对多发送或者多对一接收吗?

答:完全可以,70%客户都这么用的。

12 问:我是新手,你们提供哪些方面的技术支持?

答:2.4G 系列模块属于有点技术难度的产品,若完全依靠客户参照规格书 写程序,会浪费客户一个多礼拜的时间,比较幸运的是我们提供了参考程序,并 且提供和程序配套的测试板借用或购买,可以让客户快速体验模块的性能。建议 项目比较急的客户选用,价格每个 20 元成本价格销售,可以给客户节省好几天 的调试时间,很划算。

答:一款原产台湾,一款原产品挪威,随着众多 IC 晶圆厂自己无线 IC 的 推出,兼容模块的价格从 2008 年的 20 元左右一直跌落到目前的 4.5,利润由当 初的 10 元降到现在的 0.5 元以下,其中挪威版的出的最早,价格虽然猛降,但 是始终拼不过台产芯片。

3 问:挪威版本的 NRF24L01+和台产版的哪个使用效果会更好? 答:台产版的完全克隆挪威版的,并在以前的基础上加了+7DB 的功放电路,

NRF24L01调试方法及经验总结

NRF24L01 :在通信中的应用方法,经验总结〔1〕2021-07-31 13:15首先说一下:单片射频收发器件,工作于2.4 GHz~2.5 GHz ISM频段。

内置频率合成器、功率放大器、晶体振荡器、调制器等功能模块,并融合了增强型ShockBurst技术,其中输出功率和通信频道可通过程序进行配置。

nRF24L01功耗低,在以-6 dBm的功率发射时,工作电流也只有9 mA;接收时,工作电流只有12.3 mA,多种低功率工作模式(掉电模式和空闲模式)使节能设计更方便。

是想将这个IC调通,首先要多读一下技术文档:下载技术文档以下C51驱动nRF24.L01 的源代码库〔nRF24.L01.h〕此库文件适合发送端使用,在接收端会有所不同,请看第2 局部的分析在使用过程中,需要引用//****************************************NRF24L01端口定义***************************************sbit CE =P2^0;sbit CSN =P2^1;sbit SCK =P2^2;sbit MOSI =P2^3;sbit MISO =P2^4;sbit IRQ =P2^5;//*********************************************NRF24L01********* ****************************#define TX_ADR_WIDTH 5 // 接收地址宽度,一般设置为5 不要动它#define RX_ADR_WIDTH 5 // 接收地址宽度,一般设置为5 不要动它#define TX_PLOAD_WIDTH 1 //接收数据的数据宽度〔最大为32 字节〕,这里我设置为最小的1 字节,方便调试#define RX_PLOAD_WIDTH 1 //发送数据的数据宽度〔最大为32 字节〕,这里我设置为最小的1 字节,方便调试uchar const TX_ADDRESS[TX_ADR_WIDTH]={0x35,0x43,0x10,0x10,0x03}; // 这里就是设置了5 个字节的本地地址/*此处的地址:在IC内部真实地址是反过来的。

nRF24L01浅谈

NRF24L01经验谈作者:盛多铮单位:安徽师范大学电子创新实验室时间:2010年12月接触无线模块已有一段时间了,还记得第一次调通2个节点的兴奋呵。

前段时间用24L01做的一件作品也在院创新本比赛中拿到了不错的成绩,自己当然也是很高兴的。

难得今晚有空,就把无线模块的经验好好总结一番,一来是方便自己以后阅读,二来嘛,让后来的人少走些弯路吧。

另外,关于寄存器的说明,在本文中谈得很少,因为文档中已经有很详细的说明了。

闲话少说,进入正题:24L01是Nordic公司的一款无线芯片,其引脚如下:CE:使能发射或接收;CSN,SCK,MOSI,MISO:SPI引脚端,微处理器可通过此引脚配置nRF24L01:IRQ:中断;VDD:电源输入端;VSS:电源地:XC2,XC1:晶体振荡器引脚;VDD_PA:为功率放大器供电,输出为1.8 V;ANT1,ANT2:天线接口;IREF:参考电流输入其中跟单片机通信时要用到的引脚有:CE,CSN,SCK,MOSI,MISO以及IRQ。

注意硬件上的电源不要超过3.3V,下面是24L01的时序图SPI读模式SPI写模式由图可知,发送时高位在前,低位在后,每写一个bit,返回一个状态字位,每次写操作都可读回一个完整的状态字。

以下是读回的状态字Status(地址:0x07)保留RX_DRTX_DSMAX_RTRX_P_NOTX_FULLRX_DR:接收数据准备好,接收缓冲区有新的数据到达时被置为1,向该位写1可清除该位TX_DS:缓冲区数据被发送完后被置为1,如果自动应答启用的话,只有在对方应答到达后才会置1,向该位写1可清除该位MAX_RT:若没有收到对方确认,24L01会自动超时重传,当到达最大重传次数后,该位被置1,向该位写1可清除该位。

若不清除该位则无法进一步通信。

RX_P_NO: 3bit,表示正在读取缓冲区数据载荷的数据管道编号。

000~101:数据管道编号。

110:没有使用111:接收缓冲区空注意:接收到新数据,数据发送完毕,重传到达最大次数都会引起中断,通过读取状态字可查询中断事件。

NRF24L01详细教程

NRF24L01详细教程NRF24L01是一款低功耗2.4GHz无线收发模块,广泛应用于各种无线通信项目中。

它可以使微控制器与其他设备进行无线通信,例如Arduino 与Arduino之间的通信、Arduino与无线传感器节点的通信等。

下面是一个详细的NRF24L01教程。

1.NRF24L01的基本介绍NRF24L01是一款由Nordic Semiconductor公司生产的低功耗无线收发模块,采用2.4GHz频段,具有快速的通信速率、低功耗、高阻塞容限等特点。

它可以与各种微控制器(如Arduino)进行通信,是一种理想的无线通信解决方案。

2.NRF24L01的物理连接在开始使用NRF24L01之前,需要将其与微控制器进行物理连接。

NRF24L01模块有8个引脚,分别是:VCC、GND、CE、CSN、SCK、MOSI、MISO和IRQ。

其中,VCC和GND连接到供电电源,CE和CSN连接到微控制器的任意数字引脚,而SCK、MOSI和MISO连接到SPI总线。

3.NRF24L01的库文件安装在编程之前,需要安装与NRF24L01相关的库文件。

可以在Arduino IDE的库管理器中并安装"nRF24L01"库。

安装完成后,就可以在程序中引用该库文件了。

4.NRF24L01的基本设置在程序中,首先需要进行NRF24L01的基本设置。

首先,在程序开头引入"NRF24L01.h"库文件。

然后,在setup(函数中,通过调用"NRF24L01"类的对象进行初始化设置。

设置包括设置CE与CSN引脚、设置通信频率、设置收发地址等。

5.NRF24L01的通信在进行基本设置之后,可以开始进行NRF24L01的通信。

通信包括发送数据和接收数据两个方面。

对于发送数据,可以使用"NRF24L01"类的write(函数将数据发送给另外一个NRF24L01模块;对于接收数据,则可以使用available(函数判断是否有数据接收到,并使用read(函数读取数据。

nRF24LE1中文数据手册

nRF24LE1 是一款高性价比且内置微控制器的智能 2.4GHz 射频收发器家族中的一员。 nRF24LE1 为提供超低功耗无线应用而作了优化。处理器能力,内存,低功耗晶振,实时实 名,计数器,AES 加密加速器,随机数发生器和节电模式的组合为实现射频协议提供了理 想的平台。使用 nRF24LE1 的好处包括严密的协议时序,安全性,低功耗和改善共存的性能。 对于应用层,nRF24LE1 提供了一个丰富的外设包括:SPI,IIC,UART,6 至 12 位 ADC, PWM 和一个用于电压等级系统唤醒的超低功耗模拟比较器。 nRF24LE1 三种封装的差异 超紧凑 4*4mm 24 脚 QFN 封装(7 个通用 IO 引脚),主要用于对大小有严格要求的应用场 合,如 穿戴式运动传感器和手册 5*5mm 32 脚 QFN 封装(15 个通用 IO 引脚)适用于无线鼠标,远程控制和玩具 7*7mm 48 脚 QFN 封装(31 个通用 IO 引脚)为对 I/O 数量要求很高的产品而设计,如无线 键盘

IREF VDD_PA

ANT1 ANT2 XC1 XC2 衬底

模拟输入 设备参考电流输出,接一电阻到 PCB

电源输出 射频功放电源供应(+1.8V),调试时,

只要有发射此引脚就会有一个脉冲

射频

差分天线连接(发送和接收)

模拟输入 连接 16MHz 晶振

电源/散热 QFN48 和 QFN32 接地,QFN24 不要

9

nRF24LE1 nRF24LU1 模块 多功能编程器 RMB88

号进行解调,当地址与自身地址一致且 CRC 校验正确时,有效数据被送到 RX FIFOs.如果 RX FIFOs 已满,则数据包被丢弃。

射频收发器保持在接收模式直到 MCU 配置其进入待机模式 1 或掉电模式。如果自动应答特 性被开启,则收发器可以进入其他模式,如进入发送模式发送应答确认。

nRF24L01中文全数据手册翻译

图 4:在微处理器中的数据时钟形式 与

无线射频发送技术

下图中分别示意了在没有无线射频发送时,数据传输速率由 MCU 决定 以及 有无线 射频发送时的时钟状态:

图 5:nRF2401 工作在无线射频时或非无线射频时的电流损耗

图 6:nRF2401 以无线射频模式进行数据发送的流程图

nRF2401 以无线射频发送数据时的条件: 相关 MCU 接口引脚:CE、CLK1、DATA � 当运行 MCU 并有数据发送时,置高 CE。接下来便激活 nRF2401 进行发送数据的 处理 � 接收机地址与所需传输的数据在系统时钟下写入 nRF2401,此时芯片运行速率或 MCU 运行速率小于 1Mbps(例如只有:10kbps) � 在上述情况完成后,MCU 置低 CE,这一行为便激活 nRF2401 以无线射频方式进 行数据发送 � nRF2401 的无线射频发送: � 射频前端上电 � 射频数据包完成(数据开始位添加成功,CRC 校验计算完成) � 数据以高速进行发送(用户可以配置发送速率为:250kbps 或 1Mbps) � 当数据发送完成,nRF2401 进入睡眠模式

nRF2401 运行模式:

概述: 通过不同的设置 PWR_UP、CE、CS 这三个引脚,nRF2401 可以工作在一下主要工作模式:

表 6:nRF2401 主要工作模式 � 激活模式(接收/发送) :PWR_UP—CE—CS(110) � 配置模式:PWR_UP—CE—CS(101) � 睡眠模式:PWR_UP—CE—CS(100) � 掉电模式:PWR_UP—CE—CS(0XX) 对于完整概述 nRF2401 输入/输出引脚的不同工作模式的设置请参照表 7。 激活模式: nRF2401 有两种接收/发送工作模式: � 无线射频模式 � 直接发送模式 nRF2401 工作于何种激活模式完全依照于配置字的组成,而配置字存在于专有的配置区域。 无线射频模式( Shock Burst) : 无线射频技术使用片上的先入先出( FIFO)功能来记录低速的数据写入,并以非常高 的速率进行数据发送,因此这样可以极大的减少电能损耗。 当 nRF2401 工作在无线射频模式时, 你可以通过由 2.4GHz 的频带来获得高速的数据传 输速率 (1Mbps) 而不需要额外的费用, 而这些数据的传输加工均由高速的微处理器来完成。 通过片上的无线射频协议来处理高速信号的传输,nRF2401 具有如下优势: � 大大减小电流的损耗 � 更低的系统花费(使用相对便宜的微处理器) � 通过短时间传输大大减低信号在空中的因传输干扰而产生的危险 nRF2401 可以通过使用 3 线接口来对其进行编程处理, 其数据的传输速率由微处理器的 处理速率决定。 当无线射频连接在最大数据传输速率时, 让芯片会把运行状态下的数字处理部分工作在 最低速率,此时 nRF2401 工作在无线射频模式下时可以在相当大的范围内减小平均电流声 损耗。 无线射频传输规则( Shock Burst Principle) : 当 nRF2401 配置为无线射频模式时(Shock Burst mode) ,其数据的发送或接收遵循如 下组成方式(以 10kbps 为范例) :

【精品】新型高速无线射频器件nRF24L01及其应用

新型高速无线射频器件nRF24L01及其应用作者:时间:2007-10-18 来源:国外电子技术阅读:281 n RF24L01概述n RF24.L01是一款新型单片射频收发器件,工作于2.4 GHz~2.5 GHz ISM频段。

内置频率合成器、功率放大器、晶体振荡器、调制器等功能模块,并融合了增强型ShockBurst技术,其中输出功率和通信频道可通过程序进行配置。

n RF24L01功耗低,在以-6 dBm的功率发射时,工作电流也只有9 mA;接收时,工作电流只有12.3 mA,多种低功率工作模式(掉电模式和空闲模式)使节能设计更方便。

n RF24L01主要特性如下:GFSK调制:硬件集成OSI链路层;具有自动应答和自动再发射功能;片内自动生成报头和CRC校验码;数据传输率为l Mb/s或2Mb/s;SPI速率为0 Mb/s~10 Mb/s;125个频道:与其他n RF24系列射频器件相兼容;QFN20引脚4 mm×4 mm封装;供电电压为1.9 V~3.6 V。

2 引脚功能及描述n RF24L01的封装及引脚排列如图1所示。

各引脚功能如下:CE:使能发射或接收;CSN,SCK,MOSI,MISO:SPI引脚端,微处理器可通过此引脚配置n RF24L01:IRQ:中断标志位;VDD:电源输入端;VSS:电源地:XC2,XC1:晶体振荡器引脚;VDD_PA:为功率放大器供电,输出为1.8 V;ANT1,ANT2:天线接口;IREF:参考电流输入。

3 工作模式通过配置寄存器可将n RF241L01配置为发射、接收、空闲及掉电四种工作模式,如表1所示。

空闲模式1主要用于降低电流损耗,在该模式下晶体振荡器仍然是工作的;空闲模式2则是在当发射堆栈为空且CE=1时发生(用在PTX设备);在空闲模式下,配置字仍然保留。

在掉电模式下电流损耗最小,同时n RF24L01也不工作,但其所有配置寄存器的值仍然保留。

nRF24L01P_Datasheet数据手册

All rights reserved.Reproduction in whole or in part is prohibited without the prior written permission of the copyright holder.September 2008nRF24L01+Single Chip 2.4GHz TransceiverProduct Specification v1.0Key Features•Worldwide 2.4GHz ISM band operation •250kbps, 1Mbps and 2Mbps on air data rates•Ultra low power operation•11.3mA TX at 0dBm output power •13.5mA RX at 2Mbps air data rate •900nA in power down •26µA in standby-I•On chip voltage regulator • 1.9 to 3.6V supply range •Enhanced ShockBurst™ •Automatic packet handling•Auto packet transaction handling • 6 data pipe MultiCeiver™•Drop-in compatibility with nRF24L01•On-air compatible in 250kbps and 1Mbps with nRF2401A, nRF2402, nRF24E1 and nRF24E2•Low cost BOM•±60ppm 16MHz crystal •5V tolerant inputs•Compact 20-pin 4x4mm QFN packageApplications•Wireless PC Peripherals•Mouse, keyboards and remotes •3-in-1 desktop bundles•Advanced Media center remote controls •VoIP headsets •Game controllers•Sports watches and sensors•RF remote controls for consumer electronics •Home and commercial automation •Ultra low power sensor networks •Active RFID•Asset tracking systems •ToysnRF24L01+ Product SpecificationLiability disclaimerNordic Semiconductor ASA reserves the right to make changes without further notice to the product to improve reliability, function or design. Nordic Semiconductor ASA does not assume any liability arising out of the application or use of any product or circuits described herein.All application information is advisory and does not form part of the specification.Limiting valuesStress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the specifications are not implied. Exposure to limiting values for extended periods may affect device reliability.Life support applicationsThese products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Nordic Semiconductor ASA cus-tomers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Nordic Semiconductor ASA for any damages resulting from such improper use or sale.Contact detailsVisit www.nordicsemi.no for Nordic Semiconductor sales offices and distributors worldwideMain office:Otto Nielsens vei 127004 TrondheimPhone: +47 72 89 89 00 Fax: +47 72 89 89 89www.nordicsemi.noData sheet statusObjective product specificationThis product specification contains target specifications for product development.Preliminary product specification This product specification contains preliminary data; supplementarydata may be published from Nordic Semiconductor ASA later.Product specification This product specification contains final product specifications. NordicSemiconductor ASA reserves the right to make changes at any time without notice in order to improve design and supply the best possibleproduct.nRF24L01+ Product Specification Writing ConventionsThis product specification follows a set of typographic rules that makes the document consistent and easy to read. The following writing conventions are used:•Commands, bit state conditions, and register names are written in Courier .•Pin names and pin signal conditions are written in Courier bold .•Cross references are underlined and highlighted in blue .Revision HistoryAttention!DateVersion DescriptionSeptember 2008 1.0Observe precaution for handling Electrostatic Sensitive Device. HBM (Human Body Model) > 1Kv MM (Machine Model) > 200VnRF24L01+ Product Specification Contents1Introduction (7)1.1Features (8)1.2Block diagram (9)2Pin Information (10)2.1Pin assignment (10)2.2Pin functions (11)3Absolute maximum ratings (12)4Operating conditions (13)5Electrical specifications (14)5.1Power consumption (14)5.2General RF conditions (15)5.3Transmitter operation (15)5.4Receiver operation (16)5.5Crystal specifications (19)5.6DC characteristics (20)5.7Power on reset (20)6Radio Control (21)6.1Operational Modes (21)6.1.1State diagram (21)6.1.2Power Down Mode (22)6.1.3Standby Modes (22)6.1.4RX mode (23)6.1.5TX mode (23)6.1.6Operational modes configuration (24)6.1.7Timing Information (24)6.2Air data rate (25)6.3RF channel frequency (25)6.4Received Power Detector measurements (25)6.5PA control (26)6.6RX/TX control (26)7Enhanced ShockBurst™ (27)7.1Features (27)7.2Enhanced ShockBurst™ overview (27)7.3Enhanced Shockburst™ packet format (28)7.3.1Preamble (28)7.3.2Address (28)7.3.3Packet control field (28)7.3.4Payload (29)7.3.5CRC (Cyclic Redundancy Check) (30)7.3.6Automatic packet assembly (31)7.3.7Automatic packet disassembly (32)7.4Automatic packet transaction handling (33)7.4.1Auto acknowledgement (33)7.4.2Auto Retransmission (ART) (33)nRF24L01+ Product Specification7.5Enhanced ShockBurst flowcharts (35)7.5.1PTX operation (35)7.5.2PRX operation (37)7.6MultiCeiver™ (39)7.7Enhanced ShockBurst™ timing (42)7.8Enhanced ShockBurst™ transaction diagram (45)7.8.1Single transaction with ACK packet and interrupts (45)7.8.2Single transaction with a lost packet (46)7.8.3Single transaction with a lost ACK packet (46)7.8.4Single transaction with ACK payload packet (47)7.8.5Single transaction with ACK payload packet and lost packet (47)7.8.6Two transactions with ACK payload packet and the firstACK packet lost (48)7.8.7Two transactions where max retransmissions is reached (48)7.9Compatibility with ShockBurst™ (49)7.9.1ShockBurst™ packet format (49)8Data and Control Interface (50)8.1Features (50)8.2Functional description (50)8.3SPI operation (50)8.3.1SPI commands (50)8.3.2SPI timing (52)8.4Data FIFO (55)8.5Interrupt (56)9Register Map (57)9.1Register map table (57)10Peripheral RF Information (64)10.1Antenna output (64)10.2Crystal oscillator (64)10.3nRF24L01+ crystal sharing with an MCU (64)10.3.1Crystal parameters (64)10.3.2Input crystal amplitude and current consumption (64)10.4PCB layout and decoupling guidelines (65)11Application example (66)11.1PCB layout examples (67)12Mechanical specifications (71)13Ordering information (73)13.1Package marking (73)13.2Abbreviations (73)13.3Product options (73)13.3.1RF silicon (73)13.3.2Development tools (73)14Glossary of Terms (74)Appendix A - Enhanced ShockBurst™ - Configuration and communication example (75)Enhanced ShockBurst™ transmitting payload (75)nRF24L01+ Product Specification Enhanced ShockBurst™ receive payload (76)Appendix B - Configuration for compatibility with nRF24XX (77)Appendix C - Constant carrier wave output for testing (78)Configuration (78)nRF24L01+ Product Specification1 IntroductionThe nRF24L01+ is a single chip 2.4GHz transceiver with an embedded baseband protocol engine (Enhanced ShockBurst™), suitable for ultra low power wireless applications. The nRF24L01+ is designed for operation in the world wide ISM frequency band at 2.400 - 2.4835GHz.To design a radio system with the nRF24L01+, you simply need an MCU (microcontroller) and a few exter-nal passive components.You can operate and configure the nRF24L01+ through a Serial Peripheral Interface (SPI). The register map, which is accessible through the SPI, contains all configuration registers in the nRF24L01+ and is accessible in all operation modes of the chip.The embedded baseband protocol engine (Enhanced ShockBurst™) is based on packet communication and supports various modes from manual operation to advanced autonomous protocol operation. Internal FIFOs ensure a smooth data flow between the radio front end and the system’s MCU. Enhanced Shock-Burst™ reduces system cost by handling all the high speed link layer operations.The radio front end uses GFSK modulation. It has user configurable parameters like frequency channel, output power and air data rate. nRF24L01+ supports an air data rate of 250 kbps, 1 Mbps and 2Mbps. The high air data rate combined with two power saving modes make the nRF24L01+ very suitable for ultra low power designs.nRF24L01+ is drop-in compatible with nRF24L01 and on-air compatible with nRF2401A, nRF2402,nRF24E1 and nRF24E2. Intermodulation and wideband blocking values in nRF24L01+ are much improved in comparison to the nRF24L01 and the addition of internal filtering to nRF24L01+ has improved the margins for meeting RF regulatory standards.Internal voltage regulators ensure a high Power Supply Rejection Ratio (PSRR) and a wide power supply range.nRF24L01+ Product Specification 1.1 FeaturesFeatures of the nRF24L01+ include:•RadioX Worldwide 2.4GHz ISM band operationX126 RF channelsX Common RX and TX interfaceX GFSK modulationX250kbps, 1 and 2Mbps air data rateX1MHz non-overlapping channel spacing at 1MbpsX2MHz non-overlapping channel spacing at 2Mbps•TransmitterX Programmable output power: 0, -6, -12 or -18dBmX11.3mA at 0dBm output power•ReceiverX Fast AGC for improved dynamic rangeX Integrated channel filtersX13.5mA at 2MbpsX-82dBm sensitivity at 2MbpsX-85dBm sensitivity at 1MbpsX-94dBm sensitivity at 250kbps•RF SynthesizerX Fully integrated synthesizerX No external loop filer, VCO varactor diode or resonatorX Accepts low cost ±60ppm 16MHz crystal•Enhanced ShockBurst™X1 to 32 bytes dynamic payload lengthX Automatic packet handlingX Auto packet transaction handlingX6 data pipe MultiCeiver™ for 1:6 star networks•Power ManagementX Integrated voltage regulatorX1.9 to 3.6V supply rangeX Idle modes with fast start-up times for advanced power managementX26µA Standby-I mode, 900nA power down modeX Max 1.5ms start-up from power down modeX Max 130us start-up from standby-I mode•Host InterfaceX4-pin hardware SPIX Max 10MbpsX3 separate 32 bytes TX and RX FIFOsX5V tolerant inputs•Compact 20-pin 4x4mm QFN packagenRF24L01+ Product Specification1.2 Block diagram ArrayFigure 1. nRF24L01+ block diagramnRF24L01+ Product Specification 2 Pin Information2.1 Pin assignment ArrayFigure 2. nRF24L01+ pin assignment (top view) for the QFN20 4x4 package2.2 Pin functionsPin Name Pin function Description1CE Digital Input Chip Enable Activates RX or TX mode2CSN Digital Input SPI Chip Select3 SCK Digital Input SPI Clock4MOSI Digital Input SPI Slave Data Input5 MISO Digital Output SPI Slave Data Output, with tri-state option6IRQ Digital Output Maskable interrupt pin. Active low7 VDD Power Power Supply (+1.9V - +3.6V DC)8VSS Power Ground (0V)9XC2Analog Output Crystal Pin 210XC1Analog Input Crystal Pin 111VDD_PA Power Output Power Supply Output (+1.8V) for the internalnRF24L01+ Power Amplifier. Must be connectedto ANT1 and ANT2 as shown in Figure 32.12ANT1RF Antenna interface 113ANT2RF Antenna interface 214VSS Power Ground (0V)15VDD Power Power Supply (+1.9V - +3.6V DC)16IREF Analog Input Reference current. Connect a 22kΩ resistor toground. See Figure 32.17VSS Power Ground (0V)18VDD Power Power Supply (+1.9V - +3.6V DC)19DVDD Power Output Internal digital supply output for de-coupling pur-poses. See Figure 32.20VSS Power Ground (0V)Table 1. nRF24L01+ pin function3 Absolute maximum ratingsNote: Exceeding one or more of the limiting values may cause permanent damage to nRF24L01+.Operating conditions Minimum Maximum Units Supply voltagesVDD-0.3 3.6V VSS0V Input voltageV I-0.3 5.25V Output voltageV O VSS to VDD VSS to VDDTotal Power DissipationP D (T A=85°C)60mW TemperaturesOperating Temperature-40+85°C Storage Temperature-40+125°CTable 2. Absolute maximum ratings4 Operating conditionsSymbol Parameter (condition)Notes Min.Typ.Max.Units VDD Supply voltage 1.9 3.0 3.6V VDD Supply voltage if input signals >3.6V 2.7 3.0 3.3V TEMP Operating Temperature -40+27+85ºCTable 3. Operating conditionsConditions: VDD = +3V, VSS = 0V, T A = - 40ºC to + 85ºC5.1 Power consumptionTable 4. Power consumptionSymbol Parameter (condition)NotesMin.Typ.Max.Units Idle modesI VDD_PD Supply current in power down900nA I VDD_ST1Supply current in standby-I modea a.This current is for a 12pF crystal. Current when using external clock is dependent on signal swing.26µA I VDD_ST2Supply current in standby-II mode 320µA I VDD_SU Average current during 1.5ms crystal oscillator startup 400µATransmitI VDD_TX0Supply current @ 0dBm output powerb b.Antenna load impedance = 15Ω+j88Ω..11.3mA I VDD_TX6Supply current @ -6dBm outputpowerb 9.0mA I VDD_TX12Supply current @ -12dBm outputpowerb 7.5mA I VDD_TX18Supply current @ -18dBm outputpowerb 7.0mA I VDD_AVG Average Supply current @ -6dBm out-put power, ShockBurst™c c.Antenna load impedance = 15Ω+j88Ω. Average data rate 10kbps and max. payload length packets.0.12mA I VDD_TXS Average current during TX settlingd d.Average current consumption during TX startup (130µs) and when changing mode from RX to TX (130µs).8.0mA ReceiveI VDD_2M Supply current 2Mbps 13.5mA I VDD_1M Supply current 1Mbps 13.1mA I VDD_250Supply current 250kbps12.6mA I VDD_RXSAverage current during RX settlinge e.Average current consumption during RX startup (130µs) and when changing mode from TX to RX (130µs).8.9mATable 5. General RF conditions5.3 Transmitter operationTable 6. Transmitter operationSymbol Parameter (condition)NotesMin.Typ.Max.Units f OP Operating frequencya a.Regulatory standards determine the band range you can use.24002525MHz PLL res PLL Programming resolution 1MHz f XTAL Crystal frequency16MHz Δf 250Frequency deviation @ 250kbps ±160kHz Δf 1M Frequency deviation @ 1Mbps ±160kHz Δf 2M Frequency deviation @ 2Mbps±320kHz R GFSKAir Data rateb b.Data rate in each burst on-air2502000kbps F CHANNEL 1M Non-overlapping channel spacing @ 250kbps/1Mbpsc c.The minimum channel spacing is 1MHz1MHz F CHANNEL 2M Non-overlapping channel spacing @ 2Mbpsc 2MHzSymbol Parameter (condition)Notes Min.Typ.Max.Units P RF Maximum Output Powera a.Antenna load impedance = 15Ω+j88Ω0+4dBm P RFC RF Power Control Range 161820dB P RFCR RF Power Accuracy±4dB P BW220dB Bandwidth for Modulated Carrier (2Mbps)18002000kHz P BW120dB Bandwidth for Modulated Carrier (1Mbps)9001000kHz P BW25020dB Bandwidth for Modulated Carrier (250kbps)700800kHz P RF1.21st Adjacent Channel Transmit Power 2MHz (2Mbps)-20dBc P RF2.22nd Adjacent Channel Transmit Power 4MHz (2Mbps)-50dBc P RF1.11st Adjacent Channel Transmit Power 1MHz (1Mbps)-20dBc P RF2.12nd Adjacent Channel Transmit Power 2MHz (1Mbps)-45dBc P RF1.2501st Adjacent Channel Transmit Power 1MHz (250kbps)-30dBc P RF2.2502nd Adjacent Channel Transmit Power 2MHz (250kbps)-45dBc5.4 Receiver operationTable 7. RX SensitivityTable 8. RX selectivity according to ETSI EN 300 440-1 V1.3.1 (2001-09) page 27Datarate Symbol Parameter (condition)Notes Min.Typ.Max.Units RX max Maximum received signal at <0.1% BER 0dBm 2Mbps RX SENS Sensitivity (0.1%BER) @2Mbps -82dBm 1Mbps RX SENS Sensitivity (0.1%BER) @1Mbps -85dBm 250kbpsRX SENSSensitivity (0.1%BER) @250kbps-94dBmDatarate Symbol Parameter (condition)Notes Min.Typ.Max.Units 2Mbps C/I CO C/I Co-channel7dBc C/I 1ST 1st ACS (Adjacent Channel Selectivity) C/I 2MHz 3dBc C/I 2ND 2nd ACS C/I 4MHz -17dBc C/I 3RD 3rd ACS C/I 6MHz-21dBc C/I Nth N th ACS C/I, f i> 12MHz-40dBc C/I Nth N th ACS C/I, f i> 36MHzaa.Narrow Band (In Band) Blocking measurements: 0 to ±40MHz; 1MHz step sizeFor Interferer frequency offsets n*2*fxtal, blocking performance is degraded by approximately 5dB com-pared to adjacent figures.-48dBc 1MbpsC/I CO C/I Co-channel 9dBc C/I 1ST 1st ACS C/I 1MHz 8dBc C/I 2ND 2nd ACS C/I 2MHz -20dBc C/I 3RD 3rd ACS C/I 3MHz -30dBc C/I Nth N th ACS C/I, f i> 6MHz-40dBc C/I Nth N th ACS C/I, f i> 25MHza-47dBc 250kbps C/I CO C/I Co-channel12dBc C/I 1ST 1st ACS C/I 1MHz -12dBc C/I 2ND 2nd ACS C/I 2MHz -33dBc C/I 3RD 3rd ACS C/I 3MHz -38dBc C/I Nth N th ACS C/I, f i> 6MHz-50dBc C/I Nth N th ACS C/I, f i> 25MHza-60dBcTable 9. RX selectivity with nRF24L01+ equal modulation on interfering signal. Measured usingPin = -67dBm for wanted signal.2MbpsC/I CO C/I Co-channel (Modulated carrier)11dBc C/I 1ST 1st ACS C/I 2MHz 4dBc C/I 2ND 2nd ACS C/I 4MHz -18dBc C/I 3RD 3rd ACS C/I 6MHz-24dBc C/I Nth N th ACS C/I, f i > 12MHz -40dBc C/I NthN th ACS C/I, f i > 36MHz a-48dBc 1MbpsC/I CO C/I Co-channel 12dBc C/I 1ST 1st ACS C/I 1MHz 8dBc C/I 2ND 2nd ACS C/I 2MHz -21dBc C/I 3RD 3rd ACS C/I 3MHz -30dBc C/I Nth N th ACS C/I, f i > 6MHz -40dBc C/I NthN th ACS C/I, f i > 25MHz a -50dBc 250kbpsC/I CO C/I Co-channel 7dBc C/I 1ST 1st ACS C/I 1MHz -12dBc C/I 2ND 2nd ACS C/I 2MHz -34dBc C/I 3RD 3rd ACS C/I 3MHz -39dBc C/I Nth N th ACS C/I, f i >6MHz -50dBc C/I NthN th ACS C/I, f i >25MHza -60dBca.Narrow Band (In Band) Blocking measurements: 0 to ±40MHz; 1MHz step sizeWide Band Blocking measurements: 30MHz to 2000MHz; 10MHz step size 2000MHz to 2399MHz; 3MHz step size 2484MHz to 3000MHz; 3MHz step size 3GHz to 12.75GHz; 25MHz step sizeWanted signal for wideband blocking measurements: -67dBm in 1Mbps and 2Mbps mode -77dBm in 250kbps modeFor Interferer frequency offsets n*2*fxtal, blocking performance are degraded by approximately 5dB compared to adjacent figures.If the wanted signal is 3dB or more above the sensitivity level then, the carrier/interferer ratio is indepen-dent of the wanted signal level for a given frequency offset.Note: Wanted signal level at Pin = -64 dBm. Two interferers with equal input power are used. Theinterferer closest in frequency is unmodulated, the other interferer is modulated equal with the wanted signal. The input power of interferers where the sensitivity equals BER = 0.1% is pre-sented. Table 10. RX intermodulation test performed according to Bluetooth Specification version 2.02Mbps P_IM(6Input power of IM interferers at 6 and 12MHz offset from wanted signal-42dBmP_IM(8)Input power of IM interferers at 8 and 16MHz offset from wanted signal-38dBmP_IM(10)Input power of IM interferers at 10 and 20MHz offset from wanted signal-37dBm1Mbps P_IM(3)Input power of IM interferers at 3 and 6MHz offset from wanted signal-36dBmP_IM(4)Input power of IM interferers at 4 and 8MHz offset from wanted signal-36dBmP_IM(5)Input power of IM interferers at 5 and 10MHz offset from wanted signal-36dBm250kbps P_IM(3)Input power of IM interferers at 3 and 6MHz offset from wanted signal-36dBmP_IM(4)Input power of IM interferers at 4 and 8MHz offset from wanted signal-36dBmP_IM(5)Input power of IM interferers at 5 and 10MHz offset from wanted signal-36dBm5.5 Crystal specificationsTable 11. Crystal specificationsThe crystal oscillator startup time is proportional to the crystal equivalent inductance. The trend in crystal design is to reduce the physical outline. An effect of a small outline is an increase in equivalent serialinductance Ls, which gives a longer startup time. The maximum crystal oscillator startup time, Tpd2stby = 1.5 ms, is set using a crystal with equivalent serial inductance of maximum 30mH. An application specific worst case startup time can be calculated as :Tpd2stby= Ls/30mH *1.5ms if Ls exceeds 30mH.Note: In some crystal datasheets Ls is called L1 or Lm and Cs is called C1 or Cm.Figure 3. Equivalent crystal componentsSymbol Parameter (condition)NotesMin.Typ.Max.Units Fxo Crystal Frequency 16MHz ΔF Tolerancea ba. Frequency accuracy including; tolerance at 25ºC , temperature drift, aging and crystal loading.b. Frequency regulations in certain regions set tighter requirements for frequency tolerance (For example, Japan and South Korea specify max. +/- 50ppm).±60ppm C 0Equivalent parallel capacitance 1.57.0pF Ls Equivalent serial inductance cc.Startup time from power down to standby mode is dependant on the Ls parameter. See Table 16. on page 24 for details.30mH C L Load capacitance81216pF ESREquivalent Series Resistance100ΩCoCs LsESR5.6 DC characteristicsTable 12. Digital input pinTable 13. Digital output pin5.7 Power on resetTable 14. Power on resetSymbol Parameter (condition)NotesMin.Typ.Max.Units V IH HIGH level input voltage 0.7VDD 5.25aa.If the input signal >3.6V, the VDD of the nRF24L01+ must be between 2.7V and 3.3V (3.0V±10%)V V ILLOW level input voltageVSS0.3VDD V SymbolParameter (condition)NotesMin.Typ.Max.Units V OH HIGH level output voltage (I OH =-0.25mA)VDD -0.3VDD V V OLLOW level output voltage (I OL =0.25mA)0.3VSymbol Parameter (condition)NotesMin.Typ.Max.Units T PUP Power ramp up time a a.From 0V to 1.9V.100ms T PORPower on resetbb.Measured from when the VDD reaches 1.9V to when the reset finishes.1100ms6 Radio ControlThis chapter describes the nRF24L01+ radio transceiver’s operating modes and the parameters used to control the radio.The nRF24L01+ has a built-in state machine that controls the transitions between the chip’s operating modes. The state machine takes input from user defined register values and internal signals.6.1 Operational ModesYou can configure the nRF24L01+ in power down, standby, RX or TX mode. This section describes these modes in detail.6.1.1 State diagramThe state diagram in Figure 4. shows the operating modes and how they function. There are three types of distinct states highlighted in the state diagram:•Recommended operating mode: is a recommended state used during normal operation.•Possible operating mode: is a possible operating state, but is not used during normal operation.•Transition state: is a time limited state used during start up of the oscillator and settling of the PLL. When the VDD reaches 1.9V or higher nRF24L01+ enters the Power on reset state where it remains in reset until entering the Power Down mode..Figure 4. Radio control state diagram6.1.2 Power Down ModeIn power down mode nRF24L01+ is disabled using minimal current consumption. All register values avail-able are maintained and the SPI is kept active, enabling change of configuration and the uploading/down-loading of data registers. For start up times see Table 16. on page 24. Power down mode is entered by setting the PWR_UP bit in the CONFIG register low.6.1.3 Standby Modes6.1.3.1 Standby-I modeBy setting the PWR_UP bit in the CONFIG register to 1, the device enters standby-I mode. Standby-I mode is used to minimize average current consumption while maintaining short start up times. In this mode only part of the crystal oscillator is active. Change to active modes only happens if CE is set high and when CE is set low, the nRF24L01 returns to standby-I mode from both the TX and RX modes.6.1.3.2 Standby-II modeIn standby-II mode extra clock buffers are active and more current is used compared to standby-I mode. nRF24L01+ enters standby-II mode if CE is held high on a PTX device with an empty TX FIFO. If a new packet is uploaded to the TX FIFO, the PLL immediately starts and the packet is transmitted after the nor-mal PLL settling delay (130µs).Register values are maintained and the SPI can be activated during both standby modes. For start up times see Table 16. on page 24.6.1.4 RX modeThe RX mode is an active mode where the nRF24L01+ radio is used as a receiver. To enter this mode, the nRF24L01+ must have the PWR_UP bit, PRIM_RX bit and the CE pin set high.In RX mode the receiver demodulates the signals from the RF channel, constantly presenting the demodu-lated data to the baseband protocol engine. The baseband protocol engine constantly searches for a valid packet. If a valid packet is found (by a matching address and a valid CRC) the payload of the packet is pre-sented in a vacant slot in the RX FIFOs. If the RX FIFOs are full, the received packet is discarded.The nRF24L01+ remains in RX mode until the MCU configures it to standby-I mode or power down mode. However, if the automatic protocol features (Enhanced ShockBurst™) in the baseband protocol engine are enabled, the nRF24L01+ can enter other modes in order to execute the protocol.In RX mode a Received Power Detector (RPD) signal is available. The RPD is a signal that is set high when a RF signal higher than -64 dBm is detected inside the receiving frequency channel. The internal RPD signal is filtered before presented to the RPD register. The RF signal must be present for at least 40µs before the RPD is set high. How to use the RPD is described in Section 6.4 on page 25.6.1.5 TX modeThe TX mode is an active mode for transmitting packets. To enter this mode, the nRF24L01+ must have the PWR_UP bit set high, PRIM_RX bit set low, a payload in the TX FIFO and a high pulse on the CE for more than 10µs.The nRF24L01+ stays in TX mode until it finishes transmitting a packet. If CE = 0, nRF24L01+ returns to standby-I mode. If CE = 1, the status of the TX FIFO determines the next action. If the TX FIFO is not empty the nRF24L01+ remains in TX mode and transmits the next packet. If the TX FIFO is empty the nRF24L01+ goes into standby-II mode. The nRF24L01+ transmitter PLL operates in open loop when in TX mode. It is important never to keep the nRF24L01+ in TX mode for more than 4ms at a time. If the Enhanced ShockBurst™ features are enabled, nRF24L01+ is never in TX mode longer than 4ms.6.1.6 Operational modes configurationThe following table (Table 15.) describes how to configure the operational modes.Table 15. nRF24L01+ main modes6.1.7 Timing InformationThe timing information in this section relates to the transitions between modes and the timing for the CE pin. The transition from TX mode to RX mode or vice versa is the same as the transition from the standby modes to TX mode or RX mode (max. 130µs), as described in Table 16.Table 16. Operational timing of nRF24L01+For nRF24L01+ to go from power down mode to TX or RX mode it must first pass through stand-by mode. There must be a delay of Tpd2stby (see Table 16.) after the nRF24L01+ leaves power down mode before the CE is set high.Note: If VDD is turned off the register value is lost and you must configure nRF24L01+ before enter-ing the TX or RX modes. ModePWR_UP register PRIM_RX register CE input pin FIFO state RX mode111-TX mode101Data in TX FIFOs. Will empty all levels in TX FIFOs a .a.If CE is held high all TX FIFOs are emptied and all necessary ACK and possible retransmits are car-ried out. The transmission continues as long as the TX FIFO is refilled. If the TX FIFO is empty whenthe CE is still high, nRF24L01+ enters standby-II mode. In this mode the transmission of a packet isstarted as soon as the CSN is set high after an upload (UL) of a packet to TX FIFO.TX mode10Minimum 10µs high pulse Data in TX FIFOs.Will empty one level in TX FIFOs b .b.This operating mode pulses the CE high for at least 10µs. This allows one packet to be transmitted.This is the normal operating mode. After the packet is transmitted, the nRF24L01+ enters standby-Imode.Standby-II101TX FIFO empty.Standby-I1-0No ongoing packet transmission.Power Down 0---Name nRF24L01+Notes Max.ments Tpd2stby Power Down Î Standby mode 150µsWith external clock a a.See Table 11. on page 19 for crystal specifications.1.5msExternal crystal, Ls < 30mH 3msExternal crystal, Ls = 60mH 4.5msExternal crystal, Ls = 90mH Tstby2a Standby modes Î TX/RX mode130µs Thce Minimum CE high10µs Tpece2csn Delay from CE positive edge to CSNlow 4µs。

nRF24L01调试经典

nRF24L01应用笔记(一)2011-03-3111:15最近百度上一些朋友都在为nRF24L01头疼,我这段时间又比较忙不能花太多时间一个一个去帮忙调试,干脆今天抽点儿时间写个应用笔记,希望能给大家提供一些方法和帮助。

有问题可以跟帖留言,我看到会尽量帮大家。

nRF24L01是Nordic公司生产的一个单芯片射频收发器件,是目前应用比较广泛的一款无线通讯芯片,具体手册资料网上大把,我就不再重复它的特性什么的了,直接说说它的调试方法,供大家参考。

24L01是收发双方都需要编程的器件,这就对调试方法产生了一定的要求,如果两块一起调,那么通讯不成功,根本不知道是发的问题还是收的问题,不隐晦的说,我当时也是没理清调试思路才浪费了大半天时间看着模块干瞪眼。

正确的方法应该是先调试发送方,能保证发送正确,再去调接收,这样就可以有针对性的解决问题。

至于怎么去调发送方,先说下发送方的工作流程:·配置寄存器使芯片工作于发送模式后拉高CE端至少10us·读状态寄存器STATUS·判断是否是发送完成标志位置位·清标志·清数据缓冲网上的程序我也看过,大多都是成品,发送方发送-等应答-(自动重发)-触发中断。

可是这样的流程就已经把接收方给牵涉进来了,就是说一定要接收方正确收到数据并且回送应答信号之后发送方才能触发中断,结束一次完整的发送。

可是这跟我们的初衷不相符,我们想单独调试发送,完全抛开接收,这样就要去配置一些参数来取消自动应答,取消自动重发,让发送方达到发出数据就算成功的目的。

SPI_RW_Reg(WRITE_REG + EN_AA, 0x00); //失能通道0自动应答SPI_RW_Reg(WRITE_REG + EN_RXADDR, 0x00); //失能接收通道0 SPI_RW_Reg(WRITE_REG + SETUP_RETR, 0x00); //失能自动重发(注:以下贴出的寄存器描述由于中文资料上有一个错误,故贴出原版英文资料)有了以上这三个配置,发送方的流程就变成了发送-触发中断。