SI3993DV-T1-GE3;中文规格书,Datasheet资料

SUD19P06-60-GE3;SUD19P06-60-E3;中文规格书,Datasheet资料

VDS - Drain-to-Source Voltage (V)

Qg - Total Gate Charge (nC)

Capacitance

Gate Charge

Document Number: 69253 S11-2132 Rev. B, 31-Oct-11 This document is subject to change without notice.

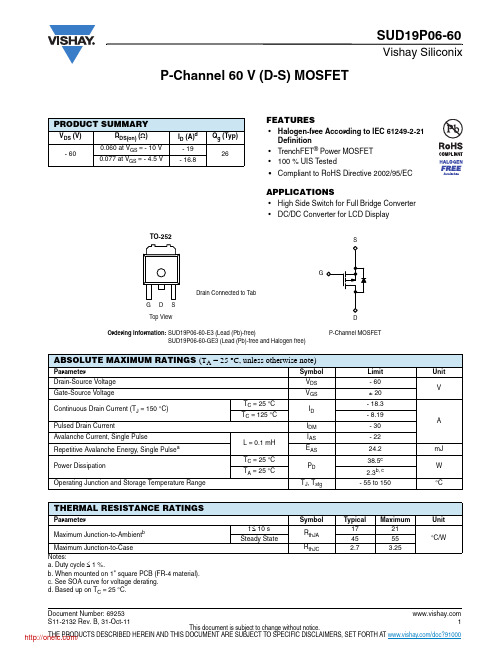

SUD19P06-60

Vishay Siliconix

TYPICAL CHARACTERISTICS (25 °C, unless otherwise noted)

30 VGS = 10 thru 5 V 25 ID - Drain Current (A) 4V ID - Drain Current (A) 25 30

3

THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT /doc?91000 /

• High Side Switch for Full Bridge Converter • DC/DC Converter for LCD Display

TO-252

S

G Drain Connected to Tab G D S D P-Channel MOSFET

Top View Ordering Information: SUD19P06-60-E3 (Lead (Pb)-free) SUD19P06-60-GE3 (Lead (Pb)-free and Halogen free)

FEATURES

• Halogen-free According to IEC 61249-2-21 Definition • TrenchFET® Power MOSFET • 100 % UIS Tested

SI7489DP-T1-GE3;中文规格书,Datasheet资料

Vishay SiliconixSi7489DPP-Channel 100-V (D-S) MOSFETFEATURES•Halogen-free According to IEC 61249-2-21Available•TrenchFET ® Power MOSFETPRODUCT SUMMARYV DS (V)R DS(on) (Ω)I D (A)a Q g (Typ.)- 1000.041 at V GS = - 10 V - 2854 nC0.047 at V GS = - 4.5 V- 28Notes:a.Package Limited.b.Surface Mounted on 1" x 1" FR4 board.c.t = 10 s.d.See Solder Profile (/ppg?73257). The PowerPAK SO-8 is a leadless package. The end of the lead terminal is exposed copper (not plated) as a result of the singulation process in manufacturing. A solder fillet at the exposed copper tip cannot be guaranteed and is not required to ensure adequate bottom side solder interconnection.e.Rework Conditions: manual soldering with a soldering iron is not recommended for leadless components.f.Maximum under Steady State conditions is 65 °C/W. ABSOLUTE MAXIMUM RATINGS T A = 25 °C, unless otherwise notedarameter Symbol Limit Unit Drain-Source Voltage V DS - 100VGate-Source Voltage V GS ± 20Continuous Drain Current (T J = 150 °C)T C = 25 °C I D - 28a AT C = 70 °C - 24.9a T A = 25 °C - 7.8b, c T A = 70 °C - 6.2b, cPulsed Drain Current I DM - 40Continuous Source-Drain Diode CurrentT C = 25 °C I S - 28a T A = 25 °C - 4.3b, cAvalanche Current L = 0.1 mHI AS - 35Single-Pulse Avalanche Energy E AS 61mJMaximum Power Dissipation T C = 25 °C P D 83WT C = 70 °C 53T A = 25 °C 5.2b, c T A = 70 °C 3.3b, cOperating Junction and Storage T emperature Range T J , T stg - 55 to 150°C Soldering Recommendations (Peak Temperature)d, e 260THERMAL RESISTANCE RATINGSarameter Symbol Typical Maximum UnitMaximum Junction-to-Ambientb, f t ≤ 10 s R thJA 1924°C/WMaximum Junction-to-Case (Drain)Steady State R thJC1.2 1.5Vishay SiliconixSi7489DPNotes:a. Pulse test; pulse width ≤ 300 µs, duty cycle ≤ 2 %.b. Guaranteed by design, not subject to production testing.Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.SPECIFICATIONS T J = 25 °C, unless otherwise notedarameter Symbol Test Conditions Min.Typ.Max.UnitStaticDrain-Source Breakdown Voltage V DS V GS = 0 V , I D = - 250 µA- 100V V DS Temperature Coefficient ΔV DS /T J I D = - 250 µA - 113mV/°C V GS(th) Temperature Coefficient ΔV GS(th)/T J 5.5Gate-Source Threshold Voltage V GS(th) V DS = V GS , I D = - 250 µA - 1- 3V Gate-Source LeakageI GSS V DS = 0 V , V GS = ± 20 V ± 100nA Zero Gate Voltage Drain Current I DSS V DS = - 100 V , V GS = 0 V - 1µA V DS = - 100 V , V GS = 0 V , T J = 55 °C- 10On-State Drain Current aI D(on) V DS ≥ 5 V , V GS = - 10 V - 40A Drain-Source On-State Resistance a R DS(on) V GS = - 10 V , I D = - 7.8 A 0.0330.041ΩV GS = - 4.5 V , I D = - 7.3 A 0.0380.047Forward T ransconductance a g fsV DS = - 15 V , I D = - 7.8 A38SDynamic bInput Capacitance C iss V DS = - 50 V , V GS = 0 V , f = 1 MHz4600pFOutput CapacitanceC oss 230Reverse Transfer Capacitance C rss 175Total Gate Charge Q g V DS = - 50 V , V GS = - 10 V , ID = - 7.8 A 106160nC V DS = - 50 V , V GS = - 4.5 V , I D = - 7.8 A 5481Gate-Source Charge Q gs 14Gate-Drain Charge Q gd 26Gate Resistance R g f = 1 MHz4ΩTurn-On Delay Time t d(on) V DD = - 50 V , R L = 8.1 ΩI D ≅ - 6.2 A, V GEN = - 10 V, R g = 1 Ω1525ns Rise Timet r 2030Turn-Off Delay Time t d(off) 110165Fall Timet f 100150Turn-On Delay Time t d(on) V DD = - 50 V , R L = 8.1 ΩI D ≅ - 6.2 A, V GEN = - 4.5 V , R g = 1 Ω4265Rise Timet r 160240Turn-Off Delay Time t d(off) 100150Fall Timet f100150Drain-Source Body Diode Characteristics Continuous Source-Drain Diode Current I S T C = 25 °C- 28A Pulse Diode Forward Current a I SM - 40Body Diode VoltageV SD I S = - 6.2 A- 0.8- 1.2V Body Diode Reverse Recovery Time t rr I F = - 6.2 A, dI/dt = 100 A/µs, T J = 25 °C6090ns Body Diode Reverse Recovery Charge Q rr 150225nC Reverse Recovery Fall Time t a 46nsReverse Recovery Rise Timet b14Single Pulse Power, Junction-to-AmbientVishay SiliconixSi7489DPTYPICAL CHARACTERISTICS 25°C, unless otherwise noted* The power dissipation P D is based on T J(max) = 150 °C, using junction-to-case thermal resistance, and is more useful in settling the upper dissipation limit for cases where additional heatsinking is used. It is used to determine the current rating, when this rating falls below the package limit.Current Derating*Single Pulse Avalanche CapabilityPower DeratingVishay SiliconixSi7489DPTYPICAL CHARACTERISTICS 25°C, unless otherwise notedVishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see /ppg?73436.Normalized Thermal Transient Impedance, Junction-to-AmbientNormalized Thermal Transient Impedance, Junction-to-CasePackage InformationVishay Siliconix PowerPAK® SO-8, (SINGLE/DUAL)MILLIMETERS INCHES DIM.MIN.NOM.MAX.MIN.NOM.MAX.A0.97 1.04 1.120.0380.0410.044A10.00-0.050.000-0.002b0.330.410.510.0130.0160.020c0.230.280.330.0090.0110.013D 5.05 5.15 5.260.1990.2030.207D1 4.80 4.90 5.000.1890.1930.197D2 3.56 3.76 3.910.1400.1480.154D3 1.32 1.50 1.680.0520.0590.066D40.57 TYP.0.0225 TYP.D5 3.98 TYP.0.157 TYP.E 6.05 6.15 6.250.2380.2420.246E1 5.79 5.89 5.990.2280.2320.236E2 3.48 3.66 3.840.1370.1440.151E3 3.68 3.78 3.910.1450.1490.154E40.75 TYP.0.030 TYP.e 1.27 BSC0.050 BSCK 1.27 TYP.0.050 TYP.K10.56--0.022--H0.510.610.710.0200.0240.028L0.510.610.710.0200.0240.028L10.060.130.200.0020.0050.008θ0°-12°0°-12°W0.150.250.360.0060.0100.014M0.125 TYP.0.005 TYP.ECN: T10-0055-Rev. J, 15-Feb-10DWG: 5881Vishay SiliconixAN821PowerPAK ® SO-8 Mounting and Thermal ConsiderationsWharton McDanielMOSFETs for switching applications are now available with die on resistances around 1 m Ω and with the capability to handle 85 A. While these die capabilities represent a major advance over what was available just a few years ago, it is important for power MOSFET packaging technology to keep pace. It should be obvi-ous that degradation of a high performance die by the package is undesirable. PowerPAK is a new package technology that addresses these issues. In this appli-cation note, PowerPAK’s construction is described.Following this mounting information is presented including land patterns and soldering profiles for max-imum reliability. Finally, thermal and electrical perfor-mance is discussed.THE PowerPAK PACKAGEThe PowerPAK package was developed around the SO-8 package (Figure 1). The PowerPAK SO-8 uti-lizes the same footprint and the same pin-outs as the standard SO-8. This allows PowerPAK to be substi-tuted directly for a standard SO-8 package. Being a leadless package, PowerPAK SO-8 utilizes the entire SO-8 footprint, freeing space normally occupied by the leads, and thus allowing it to hold a larger die than a standard SO-8. In fact, this larger die is slightly larger than a full sized DPAK die. The bottom of the die attach pad is exposed for the purpose of providing a direct,low resistance thermal path to the substrate the device is mounted on. Finally, the package height is lower than the standard SO-8, making it an excellent choice for applications with space constraints.PowerPAK SO-8 SINGLE MOUNTINGThe PowerPAK single is simple to use. The pin arrangement (drain, source, gate pins) and the pin dimensions are the same as standard SO-8 devices (see Figure 2). Therefore, the PowerPAK connection pads match directly to those of the SO-8. The only dif-ference is the extended drain connection area. To take immediate advantage of the PowerPAK SO-8 single devices, they can be mounted to existing SO-8 land patterns.The minimum land pattern recommended to take full advantage of the PowerPAK thermal performance see Application Note 826, Recommended Minimum Pad Patterns With Outline Drawing Access for Vishay Sili-conix MOSFETs . Click on the PowerPAK SO-8 single in the index of this document.In this figure, the drain land pattern is given to make full contact to the drain pad on the PowerPAK package.This land pattern can be extended to the left, right, and top of the drawn pattern. This extension will serve to increase the heat dissipation by decreasing the ther-mal resistance from the foot of the PowerPAK to the PC board and therefore to the ambient. Note that increasing the drain land area beyond a certain point will yield little decrease in foot-to-board and foot-to-ambient thermal resistance. Under specific conditions of board configuration, copper weight and layer stack,experiments have found that more than about 0.25 to 0.5 in 2 of additional copper (in addition to the drain land) will yield little improvement in thermal perfor-mance.Figure 1.PowerPAK 1212 DevicesFigure 2.Standard SO-8Pow erPAK SO-8Vishay SiliconixAN821PowerPAK SO-8 DUALThe pin arrangement (drain, source, gate pins) and the pin dimensions of the PowerPAK SO-8 dual are the same as standard SO-8 dual devices. Therefore, the PowerPAK device connection pads match directly to those of the SO-8. As in the single-channel package,the only exception is the extended drain connection area. Manufacturers can likewise take immediate advantage of the PowerPAK SO-8 dual devices by mounting them to existing SO-8 dual land patterns.To take the advantage of the dual PowerPAK SO-8’s thermal performance, the minimum recommended land pattern can be found in Application Note 826,Recommended Minimum Pad Patterns With Outline Drawing Access for Vishay Siliconix MOSFETs . Click on the PowerPAK 1212-8 dual in the index of this doc-ument.The gap between the two drain pads is 24 mils. This matches the spacing of the two drain pads on the Pow-erPAK SO-8 dual package.REFLOW SOLDERINGVishay Siliconix surface-mount packages meet solder reflow reliability requirements. Devices are subjected to solder reflow as a test preconditioning and are then reliability-tested using temperature cycle, bias humid-ity, HAST, or pressure pot. The solder reflow tempera-ture profile used, and the temperatures and time duration, are shown in Figures 3 and 4.For the lead (Pb)-free solder profile, see /doc?73257.Ramp-Up Rate+ 6 °C /Second Maximum Temperature at 155 ± 15 °C 120 Seconds Maximum Temperature Above 180 °C 70 - 180 Seconds Maximum T emperature 240 + 5/- 0 °CTime at Maximum T emperature 20 - 40 SecondsRamp-Down Rate+ 6 °C/Second MaximumFigure 3. Solder Reflow Temperature ProfileFigure 3.Solder Reflow Temperatures and Time DurationsVishay SiliconixAN821THERMAL PERFORMANCE IntroductionA basic measure of a device’s thermal performance is the junction-to-case thermal resistance, R θjc , or the junction-to-foot thermal resistance, R θjf . This parameter is measured for the device mounted to an infinite heat sink and is therefore a characterization of the device only, in other words, independent of the properties of the object to which the device is mounted. Table 1 shows a comparison of the DPAK, PowerPAK SO-8, and stan-dard SO-8. The PowerPAK has thermal performance equivalent to the DPAK, while having an order of magni-tude better thermal performance over the SO-8. Thermal Performance on Standard SO-8 Pad Pattern Because of the common footprint, a PowerPAK SO-8can be mounted on an existing standard SO-8 pad pat-tern. The question then arises as to the thermal perfor-mance of the PowerPAK device under these conditions.A characterization was made comparing a standard SO-8and a PowerPAK device on a board with a trough cut out underneath the PowerPAK drain pad. This configuration restricted the heat flow to the SO-8 land pads. The results are shown in Figure 5.Because of the presence of the trough, this result sug-gests a minimum performance improvement of 10 °C/W by using a PowerPAK SO-8 in a standard SO-8 PC board mount.The only concern when mounting a PowerPAK on a standard SO-8 pad pattern is that there should be no traces running between the body of the MOSFET.Where the standard SO-8 body is spaced away from the pc board, allowing traces to run underneath, the Power-PAK sits directly on the pc board.Thermal Performance - Spreading CopperDesigners may add additional copper, spreading cop-per, to the drain pad to aid in conducting heat from a device. It is helpful to have some information about the thermal performance for a given area of spreading cop-per.Figure 6 shows the thermal resistance of a PowerPAK SO-8 device mounted on a 2-in. 2-in., four-layer FR-4PC board. The two internal layers and the backside layer are solid copper. The internal layers were chosen as solid copper to model the large power and ground planes common in many applications. The top layer was cut back to a smaller area and at each step junction-to-ambient thermal resistance measurements were taken.The results indicate that an area above 0.3 to 0.4 square inches of spreading copper gives no additional thermal performance improvement. A subsequent experiment was run where the copper on the back-side was reduced, first to 50 % in stripes to mimic circuit traces,and then totally removed. No significant effect was observed.TABLE 1.DPAK and PowerPAK SO-8Equivalent Steady State PerformanceDPAKPowerPAKSO-8 Standard SO-8 Thermal Resistance R θjc1.2 °C/W1.0 °C/W16 °C/WFigure 5. PowerPAK SO-8 and Standard SO-0 Land Pad Thermal PathFigure 6. Spreading Copper Junction-to-Ambient PerformanceR th v s. Spreading Copper (0 %, 50 %, 100 % Back Copper))s t t a w /C ( e c n a d e p m I 0.0056514641360.250.500.751.001.251.501.752.000 %50 %100 %分销商库存信息: VISHAYSI7489DP-T1-GE3。

SI2301CDS-T1-GE3中文资料

Vishay SiliconixSi2301CDSP-Channel 20-V (D-S) MOSFET FEATURES•Halogen-free Option Available•TrenchFET ® Power MOSFETAPPLICATIONS •Load SwitchMOSFET PRODUCT SUMMARYV DS (V)R DS(on) (Ω)I D (A)a Q g (Typ.)- 200.112 at V GS = - 4.5 V - 3.1 3.3 nC0.142 at V GS = - 2.5 V- 2.7Notes:a. Based on T C = 25 °C.b. Surface Mounted on 1" x 1" FR4 board.c. t = 5 s.d. Maximum under Steady State conditions is 175 °C/W.ABSOLUTE MAXIMUM RATINGS T A = 25°C, unless otherwise notedParameter Symbol Limit U nitDrain-Source Voltage V DS - 20VGate-Source Voltage V GS ± 8Continuous Drain Current (T J = 150 °C)T C = 25 °C I D- 3.1A T C = 70 °C - 2.5T A = 25 °C - 2.3b, c T A = 70 °C - 1.8b, cPulsed Drain Current I DM - 10Continuous Source-Drain Diode CurrentT C = 25 °C I S - 1.3T A = 25 °C - 0.72b, c Maximum Power Dissipation T C = 25 °C P D 1.6WT C = 70 °C 1.0T A = 25 °C 0.86b, c T A = 70 °C 0.55b, cOperating Junction and Storage T emperature Range T J , T stg - 55 to 150°C THERMAL RESISTANCE RATINGSParameter Symbol Typical Maximum UnitMaximum Junction-to-Ambient b, d ≤ 5 s R thJA 120145°C/WMaximum Junction-to-Foot (Drain)Steady State R thJF 6278Vishay SiliconixSi2301CDSNotes:a. Pulse test; pulse width ≤ 300 µs, duty cycle ≤ 2 %.b. Guaranteed by design, not subject to production testing.Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.MOSFET SPECIFICATIONS T J = 25°C, unless otherwise notedParameter Symbol Test Conditions Min.Typ.Max.U nit StaticDrain-Source Breakdown Voltage V DS V DS = 0 V, I D = - 250 µA- 20VV DS Temperature Coefficient ΔV DS /T J I D = - 250 µA - 18mV/°C V GS(th) T emperature Coefficient ΔV GS(th)/T J 2.2Gate-Source Threshold Voltage V GS(th) V DS = V GS , I D = - 250 µA - 0.4- 1V Gate-Source LeakageI GSS V DS = 0 V , V GS = ± 8 V ± 100nA Zero Gate Voltage Drain Current I DSS V DS = - 20 V , V GS = 0 V - 1µA V DS = - 20 V, V GS = 0 V , T J = 55 °C- 10On-State Drain Current aI D(on) V DS ≤ - 5 V , V GS = - 4.5 V - 6A Drain-Source On-State Resistance aR DS(on) V GS = - 4.5 V, I D = - 2.8 A 0.0900.112ΩV GS = - 2.5 V, I D = - 2.0 A 0.1100.142Forward T ransconductance a g fsV DS = - 5 V , I D = - 2.8 A2.0SDynamic bInput Capacitance C iss V DS = - 10 V , V GS = 0 V , f = 1 MHz405pFOutput CapacitanceC oss 75Reverse Transfer Capacitance C rss 55Total Gate Charge Q g V DS = - 10 V , V GS = - 4.5 V , ID = - 3 A 5.510nC V DS = - 10 V , V GS = - 2.5 V , I D = - 3 A 3.36Gate-Source Charge Q gs 0.7Gate-Drain Charge Q gd 1.3Gate Resistance R g f = 1 MHz6.0ΩTurn-On Delay Time t d(on) V DD = - 10 V, R L = 10 ΩI D = - 1 A, V GEN = - 4.5 V , R G = 1 Ω1120ns Rise Timet r 3560Turn-Off Delay Time t d(off) 3050Fall Timet f1020Drain-Source Body Diode Characteristics Continuous Source-Drain Diode Current I S T C = 25 °C- 1.3A Pulse Diode Forward Current a I SM - 10Body Diode VoltageV SD I S = - 0.7 A- 0.8- 1.2V Body Diode Reverse Recovery Time t rr I F = - 3.0 A, dI/dt = 100 A/µs, T J = 25 °C3050ns Body Diode Reverse Recovery Charge Q rr 2550nC Reverse Recovery Fall Time t a 15nsReverse Recovery Rise Timet b15Output CharacteristicsOn-Resistance vs. Drain Current and Gate VoltageTransfer CharacteristicsCapacitanceOn-Resistance vs. Junction TemperatureThreshold VoltageSingle Pulse PowerVishay SiliconixSi2301CDSTYPICAL CHARACTERISTICS 25°C, unless otherwise notedVishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see /ppg?68741.Normalized Thermal Transient Impedance, Junction-to-FootDisclaimer Legal Disclaimer NoticeVishayAll product specifications and data are subject to change without notice.Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, “Vishay”), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay’s terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.Product names and markings noted herein may be trademarks of their respective owners.元器件交易网。

SQ4940AEY-T1-GE技术资料

Automotive Dual N-Channel 40 V (D-S) 175 °C MOSFETFEATURES•TrenchFET ® power MOSFET •100 % R g and UIS tested •AEC-Q101 qualified d•Material categorization:For definitions of compliance please seeNotesa.Package limited.b.Pulse test; pulse width ≤ 300 μs, duty cycle ≤ 2 %.c.When mounted on 1" square PCB (FR-4 material).d.Parametric verification ongoing.PRODUCT SUMMARYV DS (V)40R DS(on) (Ω) at V GS = 10 V 0.024R DS(on) (Ω) at V GS = 4.5 V 0.029I D (A)8ConfigurationDualTop ViewS O-8 Dual1S 12G 13S 24G 2D 17D 26D 25D 18ORDERING INFORMATIONPackageSO-8Lead (Pb)-free and Halogen-freeSQ4940AEY-T1-GE3ABSOLUTE MAXIMUM RATINGS (T C = 25 °C, unless otherwise noted)PA AMETE SYMBOL LIMIT UNIT Drain-Source Voltage V DS40VGate-Source Voltage V GS ± 20Continuous Drain CurrentT C = 25 °C a I D 8A T C = 125 °C5.3Continuous Source Current (Diode Conduction)I S 3.6Pulsed Drain Current bI DM 32Single Pulse Avalanche Current L = 0.1 mH I AS 17Single Pulse Avalanche Energy E AS 15mJ Maximum Power Dissipation bT C = 25 °C P D 4W T C = 125 °C 1.3Operating Junction and Storage Temperature RangeT J , T stg-55 to +175°C THERMAL RESISTANCE RATINGSPA AMETE SYMBOL LIMIT UNIT Junction-to-Ambient PCB Mount cR thJA 112°C/WJunction-to-Foot (Drain)R thJF38Notesa. Pulse test; pulse width ≤ 300 μs, duty cycle ≤ 2 %.b. Guaranteed by design, not subject to production testing.c. Independent of operating temperature.Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.SPECIFICATIONS (T C = 25 °C, unless otherwise noted)PA AMETE R SYMBOLTEST CONDITIONS MIN.TYP.MAX.UNITStaticDrain-Source Breakdown Voltage V DS V GS = 0 V, I D = 250 μA 40--V Gate-Source Threshold Voltage V GS(th)V DS = V GS , I D = 250 μA 1.52 2.5Gate-Source LeakageI GSS V DS = 0 V, V GS = ± 20 V--± 100nAZero Gate Voltage Drain Current I DSS V GS = 0 V V DS = 40 V --1μA V GS = 0 V V DS = 40 V, T J = 55 °C --50V GS = 0 V V DS = 40 V, T J = 175 °C--150On-State Drain Current aI D(on)V GS = 10 V V DS ≥ 5 V 30--A Drain-Source On-State Resistance aR DS(on)V GS = 10 VI D = 5.3 A -0.0200.024ΩV GS = 10 V I D = 5.3 A, T J = 125 °C --0.036V GS = 10 V I D = 5.3 A, T J = 175 °C--0.043V GS = 4.5 VI D = 4.9 A-0.0240.029Forward Transconductance b g fsV DS = 15 V, I D = 5.3 A-33-S Dynamic bInput Capacitance C issV GS = 0 V V DS = 20 V, f = 1 MHz -593741pFOutput CapacitanceC oss -103129Reverse Transfer Capacitance C rss -4455Total Gate Charge c Q gV GS = 10 V V DS = 20 V, I D = 5.7 A -28.443nC Gate-Source Charge c Q gs -4-Gate-Drain Charge c Q gd -6-Gate Resistance R g f = 1 MHz0.5-2ΩTurn-On Delay Time c t d(on)V DD = 20 V, R L = 3.5 ΩI D ≅ 5.7 A, V GEN = 10 V, R g = 1 Ω-812ns Rise Time ct r-1320Turn-Off Delay Time c t d(off) -2030Fall Time c t f -914Source-Drain Diode Ratings and Characteristics bPulsed Current a I SM --32A Forward VoltageV SDI F = 3.6 A, V GS = 0 V-0.751.1VTransfer CharacteristicsOn-Resistance vs. Drain Current Transconductance CapacitanceSource Drain Diode Forward VoltageThreshold VoltageOn-Resistance vs. Gate-to-Source Voltage Drain Source Breakdown vs. Junction TemperatureTHERMAL RATINGS (T A = 25 °C, unless otherwise noted)Safe Operating AreaTHERMAL RATINGS (T A = 25 °C, unless otherwise noted)Normalized Thermal Transient Impedance, Junction-to-FootNote•The characteristics shown in the two graphs- Normalized Transient Thermal Impedance Junction-to-Ambient (25 °C)- Normalized Transient Thermal Impedance Junction-to-Foot (25 °C)are given for general guidelines only to enable the user to get a “ball park” indication of part capabilities. The data are extracted from single pulse transient thermal impedance characteristics which are developed from empirical measurements. The latter is valid for the part mounted on printed circuit board - FR4, size 1" x 1" x 0.062", double sided with 2 oz. copper, 100 % on both sides. The part capabilities can widely vary depending on actual application parameters and operating conditions.Vishay Silico nix maintains wo rldwide manufacturing capability. Pro ducts may be manufactured at o ne o f several qualified lo catio ns. Reliability data fo r Silico n Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, seeOrdering InformationVishay SiliconixSO-8Ordering codes for the SQ rugged series power MOSFETs in the SO-8 package:DATASHEET PART NUMBER OLD ORDERING CODE a NEW ORDERING CODE SQ4005EY-SQ4005EY-T1_GE3SQ4050EY SQ4050EY-T1-GE3SQ4050EY-T1_GE3SQ4182EY SQ4182EY-T1-GE3SQ4182EY-T1_GE3SQ4184EY SQ4184EY-T1-GE3SQ4184EY-T1_GE3SQ4282EY SQ4282EY-T1-GE3SQ4282EY-T1_GE3SQ4284EY SQ4284EY-T1-GE3SQ4284EY-T1_GE3SQ4401EY SQ4401EY-T1-GE3SQ4401EY-T1_GE3SQ4410EY SQ4410EY-T1-GE3SQ4410EY-T1_GE3SQ4425EY SQ4425EY-T1-GE3SQ4425EY-T1_GE3SQ4431EY SQ4431EY-T1-GE3SQ4431EY-T1_GE3SQ4435EY SQ4435EY-T1-GE3SQ4435EY-T1_GE3SQ4470EY SQ4470EY-T1-GE3SQ4470EY-T1_GE3SQ4483BEEY SQ4483BEEY-T1-GE3SQ4483BEEY-T1_GE3SQ4483EY-SQ4483EY-T1_GE3SQ4532AEY-SQ4532AEY-T1_GE3SQ4840EY SQ4840EY-T1-GE3SQ4840EY-T1_GE3SQ4850EY SQ4850EY-T1-GE3SQ4850EY-T1_GE3SQ4917EY SQ4917EY-T1-GE3SQ4917EY-T1_GE3SQ4920EY SQ4920EY-T1-GE3SQ4920EY-T1_GE3SQ4937EY SQ4937EY-T1-GE3SQ4937EY-T1_GE3SQ4940AEY SQ4940AEY-T1-GE3SQ4940AEY-T1_GE3SQ4946AEY SQ4946AEY-T1-GE3SQ4946AEY-T1_GE3SQ4949EY SQ4949EY-T1-GE3SQ4949EY-T1_GE3SQ4961EY SQ4961EY-T1-GE3SQ4961EY-T1_GE3SQ9407EY SQ9407EY-T1-GE3SQ9407EY-T1_GE3SQ9945BEY SQ9945BEY-T1-GE3SQ9945BEY-T1_GE3Notea.Old ordering code is obsolete and no longer valid for new ordersVishay SiliconixPackage InformationDIM MILLIMETERSINCHESMin Max Min Max A 1.35 1.750.0530.069A 10.100.200.0040.008B 0.350.510.0140.020C 0.190.250.00750.010D 4.80 5.000.1890.196E 3.804.000.1500.157e 1.27 BSC0.050 BSCH 5.80 6.200.2280.244h 0.250.500.0100.020L 0.500.930.0200.037q 0°8°0°8°S0.440.640.0180.026ECN: C-06527-Rev. I, 11-Sep-06DWG: 5498Application Note 826Vishay SiliconixP P L I C A T I O N N O T ERECOMMENDED MINIMUM PADS FOR SO-8Legal Disclaimer Notice 创泰芯电子 只做原装3266606846VishayDisclaimerALL PRODUCT, PRODUCT SPECIFICAT IONS AND DAT A ARE SUBJECT T O CHANGE WIT HOUT NOT ICE T O IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, “Vishay”), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.Statements regarding the suitability of products for certain types of applications are based on Vishay’s knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer’s responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and / or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer’s technical experts. Product specifications do not expand or otherwise modify Vishay’s terms and conditions of purchase, including but not limited to the warranty expressed therein.Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.。

SI7116DN-T1-GE3;中文规格书,Datasheet资料

Vishay SiliconixSi7116DNN-Channel 40-V (D-S) Fast Switching MOSFETFEATURES•Halogen-free Option Available •TrenchFET ® Power MOSFET•New Low Thermal Resistance PowerPAK ®Package with Low 1.07 mm Profile •PWM Optimized •100 % R g TestedAPPLICATIONS•Synchronous Rectification •Intermediate Switch •Synchronous BuckPRODUCT SUMMARYV DS (V)R DS(on) (Ω)I D (A)Q g (Typ.)400.0078 at V GS = 10 V 16.415 nC0.010 at V GS = 4.5 V14.5Notes:a.Surface Mounted on 1" x 1" FR4 board.b.See Solder Profile (/ppg?73257). The PowerPAK 1212-8 is a leadless package. The end of the lead terminal is exposed copper (not plated) as a result of the singulation process in manufacturing. A solder fillet at the exposed copper tip cannot be guaranteed and is not required to ensure adequate bottom side solder interconnection.c.Rework Conditions: manual soldering with a soldering iron is not recommended for leadless components. ABSOLUTE MAXIMUM RATINGS T A = 25 °C, unless otherwise notedParameterSymbol 10 sSteady StateUnit Drain-Source Voltage V DS 40VGate-Source VoltageV GS ± 20Continuous Drain Current (T J = 150 °C)a T A = 25 °C I D16.410.5AT A = 70 °C13.18.4Pulsed Drain CurrentI DM 60Continuous Source Current (Diode Conduction)a I S 3.21.3Avalanche Current L = 0 1 mH I AS 15Avalanche EnergyE AS 11mJ Maximum Power Dissipation aT A = 25 °C P D 3.8 1.5W T A = 70 °C 2.00.8Operating Junction and Storage T emperature Range T J , T stg- 55 to 150°CSoldering Recommendations (Peak Temperature)b, c260THERMAL RESISTANCE RATINGSParameter Symbol T ypical Maximum UnitMaximum Junction-to-Ambient a t ≤ 10 s R thJA 2433°C/WSteady State 6581Maximum Junction-to-Case (Drain)Steady StateR thJC1.92.4Vishay SiliconixSi7116DNNotes:a. Pulse test; pulse width ≤ 300 µs, duty cycle ≤ 2 %.b. Guaranteed by design, not subject to production testing.Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.MOSFET SPECIFICATIONS T J = 25 °C, unless otherwise notedParameter Symbol T est Conditions Min.T yp.Max.UnitStaticGate Threshold Voltage V GS(th) V DS = V GS , I D = 250 µA 1.52.5VGate-Body LeakageI GSS V DS = 0 V , V GS = ± 20 V ± 100 nAZero Gate Voltage Drain Current I DSS V DS = 40 V , V GS = 0 V 1µA V DS = 40 V, V GS = 0 V , T J = 55 °C5On-State Drain Current aI D(on) V DS ≥ 5 V , V GS = 10 V 40A Drain-Source On-State Resistance a R DS(on) V GS = 10 V , I D = 16.4 A 0.00650.0078ΩV GS = 4.5 V, I D = 14.5 A 0.00830.010Forward T ransconductance a g fs V DS = 15 V , I D = 16.4 A 68S Diode Forward Voltage a V SDI S = 3.2 A, V GS = 0 V0.81.2VDynamic bTotal Gate Charge Q g V DS = 20 V , V GS = 4.5 V , I D = 16.4 A1523nCGate-Source Charge Q gs 6.7Gate-Drain Charge Q gd 5.1Gate Resistance R g f = 1 MHz0.71.42.1ΩTurn-On Delay Time t d(on) V DD = 20 V , R L = 20 ΩI D ≅ 1 A, V GEN = 10 V , R g = 6 Ω1015ns Rise Timet r 1015Turn-Off Delay Time t d(off) 3655Fall Timet f 1015Source-Drain Reverse Recovery Time t rr I F = 3.2 A, di/dt = 100 A/µs 3060Body Diode Reverse Recovery ChargeQ rrI F = 3.2 A, di/dt = 100 A/µs 2652nc Output Characteristics Transfer CharacteristicsVishay SiliconixSi7116DNTYPICAL CHARACTERISTICS 25°C, unless otherwise notedGate ChargeSource-Drain Diode Forward VoltageCapacitanceOn-Resistance vs. Gate-to-Source VoltageSafe Operating AreaVishay SiliconixSi7116DNTYPICAL CHARACTERISTICS 25°C, unless otherwise notedVishay Sil iconix maintains worl dwide manufacturing capabil ity. Products may be manufactured at one of several qual ified l ocations. Rel iabil ity data for Sil icon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see /ppg?73139.Normalized Thermal Transient Impedance, Junction-to-CaseVishay SiliconixAN822PowerPAK ® 1212 Mounting and Thermal ConsiderationsJohnson ZhaoMOSFETs for switching applications are now available with die on resistances around 1 m Ω and with the capability to handle 85 A. While these die capabilities represent a major advance over what was available just a few years ago, it is important for power MOSFET packaging technology to keep pace. It should be obvi-ous that degradation of a high performance die by the package is undesirable. PowerPAK is a new package technology that addresses these issues. The PowerPAK 1212-8 provides ultra-low thermal impedance in a small package that is ideal for space-constrained applications. In this application note, the PowerPAK 1212-8’s construction is described. Following this,mounting information is presented. Finally, thermal and electrical performance is discussed.THE PowerPAK PACKAGEThe PowerPAK 1212-8 package (Figure 1) is a deriva-tive of PowerPAK SO-8. It utilizes the same packaging technology, maximizing the die area. The bottom of the die attach pad is exposed to provide a direct, low resis-tance thermal path to the substrate the device is mounted on. The PowerPAK 1212-8 thus translates the benefits of the PowerPAK SO-8 into a smaller package, with the same level of thermal performance.(Please refer to application note “PowerPAK SO-8Mounting and Thermal Considerations.”)The PowerPAK 1212-8 has a footprint area compara-ble to TSOP-6. It is over 40 % smaller than standard TSSOP-8. Its die capacity is more than twice the size of the standard TSOP-6’s. It has thermal performance an order of magnitude better than the SO-8, and 20times better than TSSOP-8. Its thermal performance is better than all current SMT packages in the market. It will take the advantage of any PC board heat sink capability. Bringing the junction temperature down also increases the die efficiency by around 20 % compared with TSSOP-8. For applications where bigger pack-ages are typically required solely for thermal consider-ation, the PowerPAK 1212-8 is a good option.Both the single and dual PowerPAK 1212-8 utilize the same pin-outs as the single and dual PowerPAK SO-8.The low 1.05 mm PowerPAK height profile makes both versions an excellent choice for applications with space constraints.PowerPAK 1212 SINGLE MOUNTINGTo take the advantage of the single PowerPAK 1212-8’s thermal performance see Application Note 826,Recommended Minimum Pad Patterns With Outline Drawing Access for Vishay Siliconix MOSFETs. Click on the PowerPAK 1212-8 single in the index of this document.In this figure, the drain land pattern is given to make full contact to the drain pad on the PowerPAK package.This land pattern can be extended to the left, right, and top of the drawn pattern. This extension will serve to increase the heat dissipation by decreasing the ther-mal resistance from the foot of the PowerPAK to the PC board and therefore to the ambient. Note that increasing the drain land area beyond a certain point will yield little decrease in foot-to-board and foot-to-ambient thermal resistance. Under specific conditions of board configuration, copper weight, and layer stack,experiments have found that adding copper beyond an area of about 0.3 to 0.5 in 2 of will yield little improve-ment in thermal performance.Figure 1.PowerPAK 1212 DevicesVishay SiliconixAN822PowerPAK 1212 DUALTo take the advantage of the dual PowerPAK 1212-8’s thermal performance, the minimum recommended land pattern can be found in Application Note 826,Recommended Minimum Pad Patterns With Outline Drawing Access for Vishay Siliconix MOSFETs . Click on the PowerPAK 1212-8 dual in the index of this doc-ument.The gap between the two drain pads is 10 mils. This matches the spacing of the two drain pads on the Pow-erPAK 1212-8 dual package.This land pattern can be extended to the left, right, and top of the drawn pattern. This extension will serve to increase the heat dissipation by decreasing the ther-mal resistance from the foot of the PowerPAK to the PC board and therefore to the ambient. Note that increasing the drain land area beyond a certain point will yield little decrease in foot-to-board and foot-to-ambient thermal resistance. Under specific conditions of board configuration, copper weight, and layer stack,experiments have found that adding copper beyond an area of about 0.3 to 0.5 in 2 of will yield little improve-ment in thermal performance.REFLOW SOLDERINGVishay Siliconix surface-mount packages meet solder reflow reliability requirements. Devices are subjected to solder reflow as a preconditioning test and are then reliability-tested using temperature cycle, bias humid-ity, HAST, or pressure pot. The solder reflow tempera-ture profile used, and the temperatures and time duration, are shown in Figures 2 and 3. For the lead (Pb)-free solder profile, see /doc?73257.Ramp-Up Rate+ 6°C /Second Maximum Temperature at 155 ± 15 °C 120 Seconds Maximum Temperature Above 180 °C 70 - 180 Seconds Maximum T emperature240 + 5/- 0 °CTime at Maximum T emperature 20 - 40 Seconds Ramp-Down Rate+ 6 °C/Second MaximumFigure 2. Solder Reflow Temperature ProfileFigure 3.Solder Reflow Temperatures and Time DurationsVishay SiliconixAN822THERMAL PERFORMANCE IntroductionA basic measure of a device’s thermal performance is the junction-to-case thermal resistance, R θjc, or the junction to- foot thermal resistance, R θjf. This parameter is measured for the device mounted to an infinite heat sink and is therefore a characterization of the device only, in other words, independent of the properties of the object to which the device is mounted. Table 1 shows a comparison of the PowerPAK 1212-8, PowerPAK SO-8,standard TSSOP-8 and SO-8 equivalent steady state performance.By minimizing the junction-to-foot thermal resistance, the MOSFET die temperature is very close to the tempera-ture of the PC board. Consider four devices mounted on a PC board with a board temperature of 45 °C (Figure 4). Suppose each device is dissipating 2 W. Using the junc-tion-to-foot thermal resistance characteristics of the PowerPAK 1212-8 and the other SMT packages, die temperatures are determined to be 49.8 °C for the Pow-erPAK 1212-8, 85 °C for the standard SO-8, 149 °C for standard TSSOP-8, and 125 °C for TSOP-6. This is a 4.8 °C rise above the board temperature for the Power-PAK 1212-8, and over 40 °C for other SMT packages. A 4.8 °C rise has minimal effect on r DS(ON) whereas a rise of over 40 °C will cause an increase in r DS(ON) as high as 20 %.Spreading CopperDesigners add additional copper, spreading copper, to the drain pad to aid in conducting heat from a device. It is helpful to have some information about the thermal performance for a given area of spreading copper.Figure 5 and Figure 6 show the thermal resistance of a PowerPAK 1212-8 single and dual devices mounted on a 2-in. x 2-in., four-layer FR-4 PC boards. The two inter-nal layers and the backside layer are solid copper. The internal layers were chosen as solid copper to model the large power and ground planes common in many appli-cations. The top layer was cut back to a smaller area and at each step junction-to-ambient thermal resistance measurements were taken. The results indicate that an area above 0.2 to 0.3 square inches of spreading copper gives no additional thermal performance improvement.A subsequent experiment was run where the copper on the back-side was reduced, first to 50 % in stripes to mimic circuit traces, and then totally removed. No signif-icant effect was observed.TABLE 1: EQIVALENT STEADY STATE PERFORMANCEPackage SO-8TSSOP-8TSOP-8PPAK 1212PPAK SO-8ConfigurationSingleDual Single Dual Single Dual Single Dual Single Dual Thermal Resiatance R thJC (C/W)2040528340902.45.51.85.5Figure 4. Temperature of Devices on a PC BoardVishay SiliconixAN822CONCLUSIONSAs a derivative of the PowerPAK SO-8, the PowerPAK 1212-8 uses the same packaging technology and has been shown to have the same level of thermal perfor-mance while having a footprint that is more than 40 %smaller than the standard TSSOP-8.Recommended PowerPAK 1212-8 land patterns are provided to aid in PC board layout for designs using this new package.The PowerPAK 1212-8 combines small size with attrac-tive thermal characteristics. By minimizing the thermal rise above the board temperature, PowerPAK simplifies thermal design considerations, allows the device to run cooler, keeps r DS(ON) low, and permits the device to handle more current than a same- or larger-size MOS-FET die in the standard TSSOP-8 or SO-8 packages.Figure 5. Spreading Copper - Si7401DNFigure 6. Spreading Copper - Junction-to-Ambient Performance分销商库存信息: VISHAYSI7116DN-T1-GE3。

SI4459ADY-T1-GE3;中文规格书,Datasheet资料

3600

1800 Crss

Coss

0.003 0 14 28 42 ID - Drain Current (A) 56 70

0 0 6 12 18 24 VDS - Drain-to-Source Voltage (V) 30

A

mJ

Maximum Power Dissipation

PD

W

Operating Junction and Storage Temperature Range

TJ, Tstg

°C

THERMAL RESISTANCE RATINGS

Parameter Maximum Junction-to-Ambienta, c Maximum Junction-to-Foot Notes: a. Surface mounted on 1" x 1" FR4 board. b. t = 10 s. c. Maximum under steady state conditions is 80 °C/W. d. Based on TC = 25 °C. Document Number: 69979 S11-1813-Rev. B, 12-Sep-11 This document is subject to change without notice. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT /doc?91000 / 1 t 10 s Steady State Symbol RthJA RthJF Typical 29 13 Maximum 35 16 Unit °C/W

SI7439DP-T1-GE3;中文规格书,Datasheet资料

Min. - 2.0

Typ.

Max. - 4.0 ± 100 -1 - 10

Unit V nA µA A

- 30 0.073 0.077 19 - 0.78 88 - 1.2 135 0.090 0.095

S V

Total Gate Charge Gate-Source Charge Gate-Drain Charge Gate Resistance Turn-On Delay Time Rise Time Turn-Off Delay Time Fall Time Source-Drain Reverse Recovery Time

FEATURES

• Halogen-free According to IEC 61249-2-21 Definition • TrenchFET® Power MOSFETs • Ultra-Low On-Resistance Critical for Application • Low Thermal Resistance PowerPAK®Package with Low 1.07 mm Profile • 100 % Rg and Avalanche Tested • Compliant to RoHS Directive 2002/95/EC

Notes: a. Surface mounted on 1" x 1" FR4 board. b. See solder profile (/ppg?73257). The PowerPAK SO-8 is a leadless package. The end of the lead terminal is exposed copper (not plated) as a result of the singulation process in manufacturing. A solder fillet at the exposed copper tip cannot be guaranteed and is not required to ensure adequate bottom side solder interconnection. c. Rework conditions: manual soldering with a soldering iron is not recommended for leadless components. Document Number: 73106 S10-2246-Rev. E, 04-Oct-10 1

SI2302CDS-T1-E3中文资料

Vishay SiliconixSi2302CDSN-Channel 20-V (D-S) MOSFETFEATURES•Halogen-free Option Available •TrenchFET ® Power MOSFETAPPLICATIONS•Load Switching for Portable Devices •DC/DC ConverterPRODUCT SUMMARYV DS (V)R DS(on) (Ω)I D (A)Q g (Typ.)200.057 at V GS = 4.5 V 2.9 3.50.075 at V GS = 2.5 V2.6Notes:a. Surface Mounted on 1" x 1" FR4 board.b. Pulse width limited by maximum junction temperature.ABSOLUTE MAXIMUM RATINGS T A = 25 °C, unless otherwise notedParameterSymbol 5 sSteady StateUnit Drain-Source Voltage V DS 20VGate-Source VoltageV GS ± 8Continuous Drain Current (T J = 150 °C)a T A = 25 °C I D 2.9 2.6AT A = 70 °C2.32.1Pulsed Drain Current bI DM 10Continuous Source Current (Diode Conduction)a I S 0.720.6Power Dissipation aT A = 25 °C P D 0.860.71W T A = 70 °C 0.550.46Operating Junction and Storage T emperature RangeT J , T stg- 55 to 150°CTHERMAL RESISTANCE RATINGSParameter Symbol Typical Maximum UnitMaximum Junction-to-Ambient a t ≤ 5 s R thJA 120145°C/WSteady State 140175Maximum Junction-to-FootSteady StateR thJF6278Vishay SiliconixSi2302CDSNotes:a. Pulse test: Pulse width ≤ 300 µs, duty cycle ≤ 2 %.b. Guaranteed by design, not subject to production testing.Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximumSPECIFICATIONS T A = 25 °C, unless otherwise notedParameter Symbol Test Conditions LimitsUnitMin.Typ.Max.StaticDrain-Source Breakdown Voltage V DS V GS = 0 V , I D = 250 µA 20VGate-Threshold Voltage V GS(th) V DS = V GS , I D = 250 µA 0.400.85Gate-Body LeakageI GSS V DS = 0 V, V GS = ± 8 V ± 100nAZero Gate Voltage Drain Current I DSS V DS = 20 V , V GS = 0 V 1µA V DS = 20 V , V GS = 0 V , T J = 70 °C75On-State Drain Current a I D(on) V DS ≥ 10 V , V GS = 4.5 V 6A Drain-Source On-Resistance aR DS(on) V GS = 4.5 V, I D = 3.6 A 0.0450.057ΩV GS = 2.5 V, I D = 3.1 A 0.0560.075Forward T ransconductance a g fs V DS = 5 V, I D = 3.6 A 13S Diode Forward Voltage V SDI S = 0.95 A, V GS = 0 V0.71.2VDynamic bTotal Gate Charge Q g V DS = 10 V , V GS = 4.5 V, I D = 3.6 A3.5 5.5nCGate-Source Charge Q gs 0.6Gate-Drain Charge Q gd 0.45Gate Resistance R gf = 1.0 MHz2.04.08.0ΩSwitchingTurn-On Delay Time t d(on) V DD = 10 V , R L = 2.78 ΩI D ≅ 3.6 A, V GEN = 4.5 V , R g = 1 Ω815nsRise Timet r 715Turn-Off Delay Time t d(off) 3045Fall Timet f 715Source-Drain Reverse Recovery Time t rr I F = 3.6 A, dI/dt = 100 A/µs 8.515Body Diode Reverse Recovery ChargeQ rr2.04.0nCTransfer CharacteristicsCapacitanceOn-Resistance vs. Junction TemperatureOn-Resistance vs. Drain CurrentGate ChargeSource-Drain Diode Forward VoltageVishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see /ppg?68645.Disclaimer Legal Disclaimer NoticeVishayAll product specifications and data are subject to change without notice.Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, “Vishay”), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay’s terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.Product names and markings noted herein may be trademarks of their respective owners.元器件交易网。

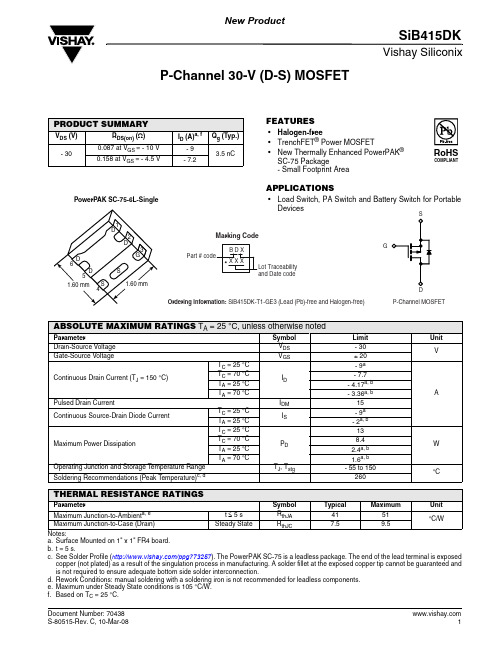

SIB433EDK-T1-GE3;中文规格书,Datasheet资料

Min. - 20

Typ.

Max.

Unit V

- 13 2.5 - 0.4 -1 ±6 ± 0.5 -1 - 10 - 15 0.047 0.064 0.085 12 0.058 0.077 0.105

mV/°C V

µA

A S

Drain-Source On-State Resistance Forward Transconductancea Dynamic

°C

THERMAL RESISTANCE RATINGS

Parameter Maximum Junction-to-Ambientb, f Maximum Junction-to-Case (Drain) t5s Steady State Symbol RthJA RthJC Typical 41 7.5 Maximum 51 9.5 Unit °C/W

G R

1.60 mm

D

Ordering Information: SiB433EDK-T1-GE3 (Lead (Pb)-free and Halogen-free)

P-Channel MOSFET

ABSOLUTE MAXIMUM RATINGS (TA = 25 °C, unless otherwise noted)

SiB433EDK

Vishay Siliconix

P-Channel 20-V (D-S) MOSFET

FEATURES PRODUCT SUMMARY

VDS (V) - 20 RDS(on) () 0.058 at VGS = - 4.5 V 0.077 at VGS = - 2.5 V 0.105 at VGS = - 1.8 V ID (A) - 9a - 9a -5 7.6 nC Qg (Typ.)

SI3981DV-T1-GE3;中文规格书,Datasheet资料

Vishay SiliconixSi3981DVDual P-Channel 20-V (D-S) MOSFETFEATURES•Halogen-free According to IEC 61249-2-21Definition•TrenchFET ® Power MOSFET•Compliant to RoHS Directive 2002/95/ECAPPLICATIONS•Battery Switch for Portable Devices •Computers- Bus Switch - Load SwitchPRODUCT SUMMARYV DS (V)R DS(on) (Ω)I D (A)- 200.185 at V GS = - 4.5 V - 1.90.260 at V GS = - 2.5 V - 1.60.385 at V GS = - 1.8 V- 0.7Notes:a. Surface Mounted on 1" x 1" FR4 board.ABSOLUTE MAXIMUM RATINGS T A = 25 °C, unless otherwise notedParameterSymbol 5 sSteady State Unit Drain-Source Voltage V DS - 20VGate-Source VoltageV GS± 8Continuous Drain Current (T J = 150 °C)a T A = 25 °C I D - 1.9- 1.6AT A = 70 °C- 1.5- 1.3Pulsed Drain CurrentI DM - 8Continuous Source Current (Diode Conduction)a I S- 1.0- 0.72Maximum Power DissipationaT A = 25 °C P D 1.080.80W T A = 70 °C0.690.51Operating Junction and Storage T emperature RangeT J , T stg- 55 to 150°CTHERMAL RESISTANCE RATINGSParameter Symbol T ypical Maximum UnitMaximum Junction-to-Ambient a t ≤ 5 s R thJA 97115°C/WSteady State 132155Maximum Junction-to-Foot (Drain)Steady StateR thJF7895Vishay SiliconixSi3981DVNotes:a. Pulse test; pulse width ≤ 300 µs, duty cycle ≤ 2 %.b. Guaranteed by design, not subject to production testing.Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.TYPICAL CHARACTERISTICS 25°C, unless otherwise notedSPECIFICATIONS T J = 25 °C, unless otherwise notedParameter Symbol T est Conditions Min.T yp.Max.UnitStaticGate Threshold Voltage V GS(th) V DS = V GS , I D = - 250 µA - 0.40- 1.1VGate-Body LeakageI GSS V DS = 0 V, V GS = ± 8 V ± 100 nAZero Gate Voltage Drain Current I DSS V DS = - 20 V, V GS = 0 V - 1µA V DS = - 20 V , V GS = 0 V , T J= 85 °C- 10On-State Drain Current aI D(on) V DS = - 5 V, V GS = - 4.5 V - 5ADrain-Source On-State Resistance a R DS(on) V GS = - 4.5 V , I D = - 1.9 A 0.1460.185ΩV GS = - 2.5 V , I D = - 1.6 A 0.2100.260V GS = - 1.8 V , I D = - 0.7 A 0.3060.385Forward T ransconductance a g fs V DS = - 5 V, I D = - 1.9 A 4S Diode Forward Voltage a V SDI S = - 1.0 A, V GS = 0 V- 0.84- 1.1V Dynamic bTotal Gate Charge Q g V DS = - 10 V , V GS = - 4.5 V , I D = - 1.9 A3.25nCGate-Source Charge Q gs 0.42Gate-Drain Charge Q gd 0.84Gate Resistance R g f = 1 MHz6ΩTurn-On Delay Time t d(on) V DD = - 10 V, R L = 10 ΩI D ≅ - 1 A, V GEN = - 4.5 V , R g = 6 Ω3045ns Rise Timet r 5085Turn-Off Delay Time t d(off) 4585Fall Timet f 2150Source-Drain Reverse Recovery Timet rrI F = - 1.00 A, dI/dt = 100 A/µs 2040Transfer CharacteristicsVishay SiliconixSi3981DVTYPICAL CHARACTERISTICS 25°C, unless otherwise notedOn-Resistance vs. Drain CurrentGate ChargeOn-Resistance vs. Junction TemperatureOn-Resistance vs. Gate-to-Source VoltageSi3981DVVishay SiliconixTYPICAL CHARACTERISTICS 25°C, unless otherwise notedSingle Pulse Power, Junction-to-AmbientNormalized Thermal Transient Impedance, Junction-to-AmbientSi3981DVVishay Siliconix TYPICAL CHARACTERISTICS 25°C, unless otherwise notedNormalized Thermal Transient Impedance, Junction-to-FootVishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see /ppg?72502.Vishay SiliconixPackage InformationAN823Vishay SiliconixMounting LITTLE FOOT R TSOP-6 Power MOSFETsSurface mounted power MOSFET packaging has been based on integrated circuit and small signal packages. Those packages have been modified to provide the improvements in heat transfer required by power MOSFET s. Leadframe materials and design,molding compounds, and die attach materials have been changed. What has remained the same is the footprint of the packages.The basis of the pad design for surface mounted power MOSFET is the basic footprint for the package. For the TSOP-6 package outline drawing see /doc?71200 and see /doc?72610 for the minimum pad footprint.In converting the footprint to the pad set for a power MOSFET , you must remember that not only do you want to make electrical connection to the package, but you must made thermal connection and provide a means to draw heat from the package, and move it away from the package.In the case of the TSOP-6 package, the electrical connections are very simple. Pins 1, 2, 5, and 6 are the drain of the MOSFET and are connected together. For a small signal device or integrated circuit, typical connections would be made with traces that are 0.020 inches wide. Since the drain pins serve the additional function of providing the thermal connection to the package, this level of connection is inadequate. The total cross section of the copper may be adequate to carry the current required for the application, but it presents a large thermal impedance. Also, heat spreads in a circular fashion from the heat source. In this case the drain pins are the heat sources when looking at heat spread on the PC board.Figure 1 shows the copper spreading recommended footprint for the TSOP-6 package. This pattern shows the starting point for utilizing the board area available for the heat spreading copper. T o create this pattern, a plane of copper overlays the basic pattern on pins 1,2,5, and 6. The copper plane connects the drain pins electrically, but more importantly provides planar copper to draw heat from the drain leads and start the process of spreading the heat so it can be dissipated into the ambient air. Notice that the planar copper is shaped like a “T” to move heat away from the drain leads in all directions. This pattern uses all the available area underneath the body for this purpose.FIGURE 1. Recommended Copper Spreading Footprint0.0491.250.0100.250.1674.250.0491.25Since surface mounted packages are small, and reflow soldering is the most common form of soldering for surface mount components, “thermal” connections from the planar copper to the pads have not been used. Even if additional planar copper area is used, there should be no problems in the soldering process. The actual solder connections are defined by the solder mask openings. By combining the basic footprint with the copper plane on the drain pins, the solder mask generation occurs automatically.A final item to keep in mind is the width of the power traces. The absolute minimum power trace width must be determined by the amount of current it has to carry. For thermal reasons, this minimum width should be at least 0.020 inches. The use of wide traces connected to the drain plane provides a low impedance path for heat to move away from the device.REFLOW SOLDERINGVishay Siliconix surface-mount packages meet solder reflow reliability requirements. Devices are subjected to solder reflow as a test preconditioning and are then reliability-tested using temperature cycle, bias humidity, HAST , or pressure pot. The solder reflow temperature profile used, and the temperatures and time duration, are shown in Figures 2 and 3.Ramp-Up Rate+6_C/Second Maximum Temperature @ 155 " 15_C 120 Seconds Maximum Temperature Above 180_C 70 − 180 Seconds Maximum Temperature 240 +5/−0_C Time at Maximum Temperature20 − 40 Seconds Ramp-Down Rate+6_C/Second MaximumFIGURE 2. Solder Reflow Temperature ProfileAN823Vishay Siliconix_C/s (max)3_C/s (max)140 −THERMAL PERFORMANCEA basic measure of a device’s thermal performance is the junction-to-case thermal resistance, R q jc , or the junction-to-foot thermal resistance, R q jf . This parameter is measured for the device mounted to an infinite heat sink and is therefore a characterization of the device only, in other words, independent of the properties of the object to which the device is mounted. T able 1 shows the thermal performance of the TSOP-6.TABLE 1.Equivalent Steady State Performance—TSOP-6Thermal Resistance R q jf30_C/WSYSTEM AND ELECTRICAL IMPACT OF TSOP-6In any design, one must take into account the change in MOSFET r DS(on) with temperature (Figure 4).0.60.81.01.21.41.6−50−250255075100125150On-Resistance vs. Junction TemperatureT J − Junction Temperature (_C)FIGURE 4.Si3434DVr D S (o n ) − O n -R e s i i s t a n c e (N o r m a l i z e d )Application Note 826Vishay SiliconixP P L I C A T I O N N O T ERECOMMENDED MINIMUM PADS FOR TSOP-6Legal Disclaimer Notice VishayDisclaimerALL PRODU CT, PRODU CT SPECIFICATIONS AND DATA ARE SU BJECT TO CHANGE WITHOU T NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively,“Vishay”), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.Statements regarding the suitability of products for certain types of applications are based on Vishay’s knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer’s responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and/or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer’s technical experts. Product specifications do not expand or otherwise modify Vishay’s terms and conditions of purchase, including but not limited to the warranty expressed therein.Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk and agree to fully indemnify and hold Vishay and its distributors harmless from and against any and all claims, liabilities, expenses and damages arising or resulting in connection with such use or sale, including attorneys fees, even if such claim alleges that Vishay or its distributor was negligent regarding the design or manufacture of the part. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.Material Category PolicyVishay Intertechnology, Inc. hereb y certifies that all its products that are identified as RoHS-Compliant fulfill the definitions and restrictions defined under Directive 2011/65/EU of The European Parliament and of the Council of June 8, 2011 on the restriction of the use of certain hazardous substances in electrical and electronic equipment (EEE) - recast, unless otherwise specified as non-compliant.Please note that some Vishay documentation may still make reference to RoHS Directive 2002/95/EC. We confirm that all the products identified as being compliant to Directive 2002/95/EC conform to Directive 2011/65/EU.分销商库存信息: VISHAYSI3981DV-T1-GE3。

SI4532CDY-T1-GE3;中文规格书,Datasheet资料

THERMAL RESISTANCE RATINGS

N-Channel Parameter Maximum Junction-to-Ambient

b, d

P-Channel Typ. 57 37 Max. 70 45 Unit °C/W

Symbol t 10 s Steady State RthJA RthJF

Min.

Typ.a 7 5.5 12 13 14 17 6 7.7 16 40 16 40 9 20 9 17

Max. 11 10 18 25 25 30 10 15 30 60 30 60 18 40 18 30 2.3 - 2.3 24 - 12

Unit

Turn-On Delay Time Rise Time Turn-Off Delay Time Fall Time Turn-On Delay Time Rise Time Turn-Off Delay Time Fall Time

Si4532CDY

Vishay Siliconix

N- and P-Channel 30 V (D-S) MOSFET

PRODUCT SUMMARY

VDS (V) N-Channel 30 RDS(on) () 0.047 at VGS = 10 V 0.065 at VGS = 4.5 V 0.089 at VGS = - 10 V 0.140 at VGS = - 4.5 V ID (A)a 6.0 5.2 - 4.3 - 3.4 Qg (Typ.) 2.75

Si4532CDY

Vishay Siliconix

SPECIFICATIONS (TJ = 25 °C, unless otherwise noted)

Vishay Siliconix Si7404DN 芯片说明书