阻抗板工程设计规范

PCBEMC设计规范

PCB--EMC设计规范PCB EMC设计规范目录第一部分布局1 层的设置1.1 合理的层数1.1.1 Vcc、GND的层数1.1.2 信号层数1.2 单板的性能指标与成本要求1.3 电源层、地层、信号层的相对位置1.3.1 Vcc、GND 平面的阻抗以及电源、地之间的EMC环境问题1.3.2 Vcc、GND 作为参考平面,两者的作用与区别1.3.3 电源层、地层、信号层的相对位置2 模块划分及特殊器件的布局2.1 模块划分2.1 .1 按功能划分2 .1.2 按频率划分2.1.3 按信号类型分2.1.4 综合布局2.2 特殊器件的布局2.2.1 电源部分2.2.2 时钟部分2.2.3 电感线圈2.2.4 总线驱动部分2.2.5 滤波器件3 滤波3.1 概述3.2 滤波器件3.2.1 电阻3.2.2 电感3.2.3 电容3.2.4 铁氧体磁珠3.2.5 共模电感3.3 滤波电路3.3.1 滤波电路的形式3.3.2 滤波电路的布局与布线3.4 电容在PCB的EMC设计中的应用3.4.1 滤波电容的种类3.4.2 电容自谐振问题3.4.3 ESR对并联电容幅频特性的影响3.4.4 ESL对并联电容幅频特性的影响3.4.5 电容器的选择3.4.6 去耦电容与旁路电容的设计建议3.4.7 储能电容的设计4 地的分割与汇接4.1 接地的含义4.2 接地的目的4.3 基本的接地方式4.3.1 单点接地4.3.2 多点接地4.3.3 浮地4.3.4 以上各种方式组成的混合接地方式4.4 关于接地方式的一般选取原则4.4.2 背板接地方式4.4.3 单板接地方式第二部分布线1 传输线模型及反射、串扰1.1 概述:1.2 传输线模型1.3 传输线的种类1.3.1 微带线(microstrip)1.3.2 带状线(Stripline)1.3.3嵌入式微带线1.4 传输线的反射1.5 串扰2 优选布线层2.1 表层与内层走线的比较2.1.1 微带线(Microstrip)2.1.3 微带线与带状线的比较2.2 布线层的优先级别3 阻抗控制3.1 特征阻抗的物理意义3.1.1 输入阻抗:3.1.2 特征阻抗3.1.3 偶模阻抗、奇模阻抗、差分阻抗3.2 生产工艺对对阻抗控制的影响3.3 差分阻抗控制3.3.1 当介质厚度为5mil时的差分阻抗随差分线间距的变化趋势3.3.2 当介质厚度为13 mil时的差分阻抗随差分线间距的变化趋势3.3.3 当介质厚度为25 mil时的差分阻抗随差分线间距的变化趋势3.4 屏蔽地线对阻抗的影响3.4.1 地线与信号线之间的间距对信号线阻抗的影响3.4.2 屏蔽地线线宽对阻抗的影响3.5 阻抗控制案例4 特殊信号的处理5 过孔5.1 过孔模型5.1.1 过孔的数学模型5.1.2 对过孔模型的影响因素5.2 过孔对信号传导与辐射发射影响5.2.1 过孔对阻抗控制的影响5.2.2 过孔数量对信号质量的影响6 跨分割区及开槽的处理6.1 开槽的产生6.1.1 对电源/地平面分割造成的开槽6.2 开槽对PCB板EMC性能的影响6.2.1 高速信号与低速信号的面电流分布6.2.2 分地”的概念6.2.3 信号跨越电源平面或地平面上的开槽的问题6.3 对开槽的处理6.3.1 需要严格的阻抗控制的高速信号线,其轨线严禁跨分割走线6.3.2 当PCB板上存在不相容电路时,应该进行分地的处理6.3.3 当跨开槽走线不可避免时,应该进行桥接6.3.4 接插件(对外)不应放置在地层隔逢上6.3.5 高密度接插件的处理6.3.6 跨“静地”分割的处理7 信号质量与EMC 7.1 EMC简介7.2 信号质量简介7.3 EMC与信号质量的相同点7.4 EMC与信号质量的不同点7.5 EMC与信号质量关系小结第三部分背板的EMC设计1 背板槽位的排列1.1 单板信号的互连要求1.2 单板板位结构1.2.1 板位结构影响;1.2.2 板间互连电平、驱动器件的选择2 背板的EMC设计2.1 接插件的信号排布与EMC设计2.1.1 接插件的选型2.1.2 接插件模型与针信号排布2.2 阻抗匹配2.3 电源、地分配2.3.1 电源分割及热插拔对电源的影响2.3.2 地分割与各种地的连接2.3.3屏蔽层第四部分射频PCB的EMC设计1 板材1.1 普通板材1.2 射频专用板材2 隔离与屏蔽2.1 隔离2.2 器件布局2.3 敏感电路和强辐射电路2.4 屏蔽材料和方法2.5 屏蔽腔的尺寸3 滤波3.1 电源和控制线的滤波3.2 频率合成器数据线、时钟线、使能线的滤波4 接地4.1 接地分类4.2 大面积接地4.3 分组就近接地4.4 射频器件接地4.4 接地时应注意的问题4.5 接地平面的分布5 布线5.1 阻抗控制5.2 转角5.3 微带线布线5.4 微带线耦合器5.5 微带线功分器5.6 微带线基本元件5.7 带状线布线5.8 射频信号走线两边包地铜皮6 其它设计考虑第一部分布局1 层的设置在PCB的EMC设计考虑中,首先涉及的便是层的设置;单板的层数由电源、地的层数和信号层数组成;电源层、地层、信号层的相对位置以及电源、地平面的分割对单板的EMC指标至关重要。

6层板 阻抗 参考面

6层板阻抗参考面

6层板阻抗参考面是PCB设计中非常重要的概念,特别是在高速数字电路和射

频电路设计中。

在6层板中,为了确保信号完整性和电磁兼容性,我们需要正确地设计阻抗匹配,同时考虑参考面的布局。

首先,让我们了解一下6层板的结构。

6层板通常由两层信号层、两层参考层

和两层地层组成。

其中,信号层用于布置信号线,参考层则用于提供参考电平,地层则用于提供良好的接地。

在6层板中,参考面的布局非常重要,因为它直接影响到阻抗的稳定性和信号传输质量。

为了正确设计阻抗,首先需要确定信号线的宽度和间距,然后根据介质常数和

板厚计算出阻抗值。

在6层板中,参考面的选择也是至关重要的。

参考面应尽量靠近信号层,以减小阻抗的变化。

在布局参考面时,需要注意尽量减小参考面之间的距离,以减小互相干扰的可能性。

另外,6层板的参考面也需要考虑到地层的布局。

地层应该尽可能贴近参考层,以减小回流路径,从而减小电磁辐射和互相干扰的可能性。

在布局地层时,需要考虑到不同信号层之间的层间耦合,尽量减小地层之间的交叉。

总的来说,正确设计6层板的阻抗参考面是确保信号完整性和电磁兼容性的关键。

通过合理的阻抗匹配和参考面布局,可以有效减小信号传输中的失真和干扰,提高电路的性能和稳定性。

希望以上内容能帮助您更好地理解6层板的阻抗参考面设计原则。

浅谈特性阻抗板之工程设计与制程控制要点

镀层 均匀 , 使线 路 的厚 度平 衡及 孔

内 镀 铜 均

37 .。从 图2 知 ,介 电常数 是 随着频 率 的增 加 而减 小 , 可

并 且 从 1 z 1 H 的 频 率 增 大 表 现 出 略 微 下 降 的 趋 MH 到 G z

导 线 宽 度 ( w

匀 ,以确保

阻 抗 的 要

阻抗 要 求设计 阻 抗C U O ( 片 ) 如 图4 响及 控 制

从 公 式 可 以看 出 导 线 宽 度 及厚 度也 是 影 响特 ・ l 生阻 抗 的 另 一 个重 要 因素 。导 线 宽 度 越大 ,其Z 就 越 小 , O

化 ,所 以工 程 人 员 在 设 计 阻 抗板 的层 压 结 构 时 需 考 虑

度取 最 小 值 ,则使 用 CT 件 计 算 的理 论 值 应 大 于阻 抗 I 软

上 9 艮 4Q) 半 固化片 的 型 号 、数量 、胶含 量 及P B C 内层 线 路的 铜皮 要 求 的下 限 ( 述 的例 子 . 值 为 5 ,相 反 若 导 线 宽 分 布情 况 ,保 证 叠 加 后 的介 电层 理 论 值 厚 度 与 压合 后 度 、导 线 厚 度 、介 电 常 数 取 最 小值 ,同 时介 电层 厚 度 的实 际介 电层厚 度基 本相 符 。 取 最 大 值 ,I CT 件 计 算 的理 论 值 应 小 于 阻抗 要 求 的 l I . 软 1 1 i 上 限 ( 的例 子, 限值为6 ;第三步 是 根据客 户 的 上述 上 6 Q)

求。 图3导线 宽度 、介 电层厚 度与 特性阻 抗的 关系

从 以 上 可 知 实 际 生 产 中 绝 缘 材 料 的 相 对 介 电 常 数 、导 线 与基 准 面 的 介 电层 厚 度 ( 间厚 度 )、导 线 层 宽 度 及 导 线 的 厚 度 都 会 引 起 特 性 阻 抗 值 发 生 较 大 变 化 。由 于 介 电 层 厚 度 和 导线 宽 度对 阻 抗 值 影 响 最 大 , 工 程 设 计 首 先 要 根 据客 户的 要 求 设 计 出 合 理 的 叠层 结

设计规范

(1)公差< 6 mil ==> 上限之孔径+ 2 mil镀铜厚.EX:0.039” + 0.003”/-002”0.042” + 0.002” = 0.044” = 1.1176mm(用1.1∮钻头).P.S.若为中间值,则取偏下限之钻头.(2)公差≧6 mil ==> 中间值孔径+ 2 mil公差+ 2 mil镀铜厚.EX:0.040” + 0.005”/- 002”0.0415” + 0.002” + 0.002” = 0.0455” = 1.1557mm(用1.15∮钻头).P.S.若为中间值,则取偏下限之钻头.C.NPTH钻孔孔径设计:(公差比±2 mil严格时,另议)(1)中间值+1MIL.(2)以选用可采用钻头直径之中心钻头为最佳.7.1.3.除了下列状况外,N PTH须采用后钻外,其余N PTH须前钻.C面或S面有锡边且内缘必须露铜者.工单注明”二钻时C面或S面朝上”7.1.4.SLOT之两端须加钻导屑孔.(1)CNC成型时为SLOT直径减6MILS.(2)PUNCH成型时为SLOT直径加2MILS.P.S.金手指板成型外之SLOT不加导屑孔.7.1.5.孔径>0.256"/6.5mm时(1)须加钻导孔(通常为0.125”/3.175mm)(2)如公差为>±0.005"时,以Routing制作(3)如公差<±0.005"时,尽可能要求客户放宽规格;如客户仍不同意放宽时,则以钻头扩孔制作or以Punch方式处理.7.1.6.成型PIN孔:(1) NPTH孔,直径0.080"/2mm以上;且表面不可有钖环.(2) 每PCS(或Spnl)三颗,位于三个角落,不可过度集中;且以不对称为原则以达防呆之作用.(3)如无NPTH孔时,必须与客户洽谈在板内增设PIN孔或在板外加折断边及PIN孔(0.125"/3.175mm).若客户不同意于板内或加折断边来增设PIN孔,则可选择1个贯孔做为辅助用定位PIN,PIN 钉SIZE须比钻孔孔径小6~8 mil.7.1.7.测试pin孔:(同成型pin孔)(1)NPTH,直径0.080"/2mm以上.(2)每PCS(或STEP)四颗位于四个角落,不可过度集中.7.1.8.最小钻孔孔径为10 mil/0.254mm,最大钻孔孔径为256 mil/6.5mm,;有超过者须反应主管.允许孔位公差为±3 mil7.1.9.孔边缘离成型边须大于10mil(含).7.1.10.目前厂内固定将靶位孔、pin孔之钻头放在T1(3.175mm).靶孔防呆点作法:(1)设于短靶处(如下图),起始靶距为4”.(样品固定为4”)(3)各层制作说明标于该层图标下面.COMP → PAD RING 單邊比1ST 單邊大8 mil CMASK → RING 單邊比外層PAD大3 mil.線寬依MI 裁板圖上標示製作.標示:孔位導通層別、料號、阻抗值及阻抗公差線寬依MI 裁板圖上標示製作.邊比鉆孔大12 mil .邊比鉆孔大12 mil .8.4 《板边工具孔及板框资料》8.5 《钻孔叠板参数表》8.6 《冲孔机底片设计规格》8.7 《内二课自动曝光机底片设计规格》。

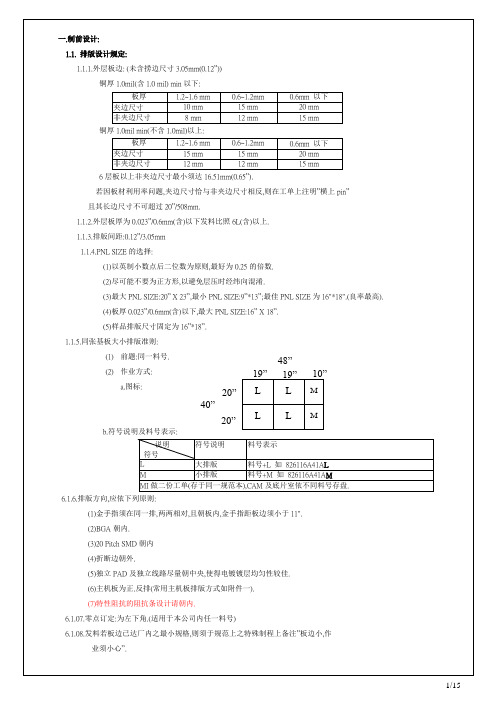

阻抗制作规范操作指引

1、目的:为规范制作阻抗PCB的阻抗计算和阻抗图形设计方法,确保成品的阻抗符合规定,使阻抗制作标准化,简单化。

2、范围:适用于本厂客户要求阻抗控制的PCB阻抗设计及CAM制作的阻抗图形设计。

3、参考文件无4、定义4.1特性阻抗(Characteristic Impedance)当一条导线与大地绝缘后,导线与大地彼此之间的阻抗。

4.2 差分阻抗(Differential Impedance)二条平行导线与大地绝缘后的阻抗,两条导线与大地彼此之间的阻抗。

5、职责5.1 PE工程部:负责客户阻抗资料的确认和设计制作;5.2 PROD生产部:按照操作指示和制作指示进行生产;5.3 QA品保部:阻抗板在制作过程中的品质监控及确认;5.4 ME工艺部:为阻抗板在制作中提供技术支持。

6、作业内容6.1 客户资料确认6.1.1确认客户压合结构可否满足阻抗控制要求。

6.1.2确认阻抗控制范围是否合理,一般情况下公差标准为±10%。

6.1.3阻抗层控制阻抗线粗设计是否合理,无阻抗线层尽量不做阻抗控制,以降低制作难度。

6.1.4评估客户阻抗控制有否特殊要求,厂内能力能否满足客户要求。

6.2阻抗设计基本原则6.2.1抗设计计算采阻抗计算软件进行计算,根据客户阻抗要求,分别输入介电常数、铜厚、线宽、线距、介电层厚度等相关参数,然后根据我司生产能力制作我司生产工作指示(MI),以指导现场生产。

6.2.2压合结构的确认根据客户要求设计压合结构,除客户指定的压合结构外,压合结构设计的一般原则如下: 6.2.1优先选用厚度较大的基板(尺寸稳定性较好);6.2.2优先选用低成本(或低成本组合)PP;备注:对于同种玻璃布型prepreg,树脂含量高低基本不影响价格,pp厚度与价格无必然联系,特殊PP(如2113,2112,3113,1506,106)价格一般较普通PP(7628, 7630,1080,2116)贵30%以上,为节约成本,在保证压合品质的前提下,PP张数尽量少用,尽量避免使用特殊PP。

阻抗制作规范

规范制作阻抗PCB的阻抗计算和阻抗图形设计方法,确保成品的阻抗符合规定。

2、适用范围:

适用于本厂客户要求阻抗控制的PCB的阻抗设计及之CAM制作的阻抗图形设计。

3、名词解释:

3.1特性阻抗(Characteristic Impedance):当一条导线与大地绝缘后,导线与大地彼此之间的阻抗。

7.2.9外层方形PAD对应接地层为Thermal Pad或直接与铜面导通。

7.2.10线宽/线距必须符合流程单要求。

7.2.11两层板设计如下:

6.2.12四层板设计如下:

7.2.13六层板设计如下:

7.2.14八层板设计如下:

ቤተ መጻሕፍቲ ባይዱ7.3特殊阻抗设计:

特殊阻抗设计时除了一般注意事项以外须根据实际情况进行修改。

4.3.3特性阻抗:成品60欧姆±10%

4.3.3.1要求理论值计算特性阻抗控制的范围为60欧姆±8%:

4.3.3.2产品的制作参数要求如下:

1)客户原本设计的特性阻抗线线宽:150um,

2)客户原本设计的与特性阻抗线相邻的线距最小为:100um

3)与特性阻抗线相邻的介层的厚度要求为:105um±15um

RC% 68压合后的介质厚度为71±8UM,RC%62压合后的介质厚度为65±8UM

5)当选用几种Prepreg同时压合时,则采用最高的介电常数与最低的介电常数的平均值进行计算。

6)内层板材铜厚计算数据:

板材铜厚是70um用62um计算,板材铜厚是35um用30um计算,板材铜厚是18um用16um计算.

3) 2116 Prepreg

A、介电常数为4.3±0.2

B、压合后的介质厚度为(内层100%残铜理论值):

阻抗板工程设计规范

1.0 工程设计阻抗值应保证在阻抗要求值的+/-5%之内,不在公差范围之内的均不合格。

2.0阻抗板最终测试合格标准:

2.0.1阻抗要求值50以下,则其允许公差为+/-5欧姆;

2.0.2阻抗要求值50以上,则其允许公差为+/-10%;

3.0.1 不在公差范围之内的均判定为不合格;

3.0.2阻抗设计合格标准+/-5%。

4.0.制作程序:

4.0.1 计算阻抗时,对参数调整的顺序:优先调整介质厚度,其次线宽/间距。

介质厚度调整2mil

以内可不与客户确认,阻抗线调整0.5mil可不用确认;

5.0 规范内容:

5.1阻抗设计相关参数:

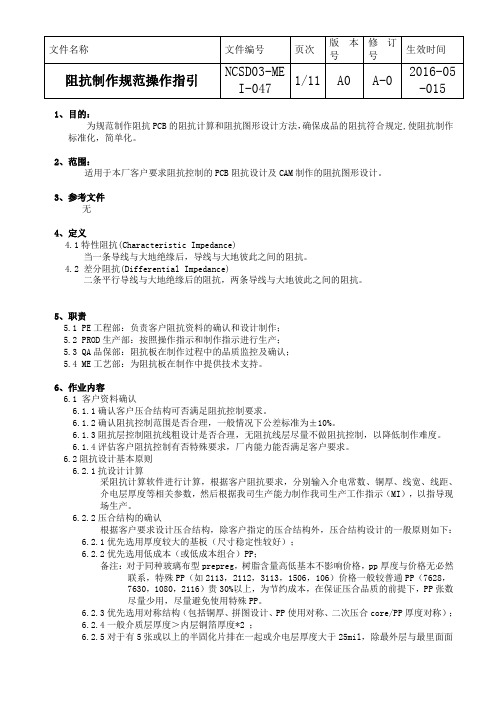

5.1.1.3介电常数:

:

对介电常数的取值,要关键看其介质的厚度来对应查找其对应的介电常数,可以按最接近的原则进行选择;如果计算的介质厚度位于列表中的两个介质厚度中间,则介电常数取列表相应两个介电常数的平均值;如果顾客提供板材,则按顾客提供板材的介电常数取值。

5.1.2线宽/线距

常规下侧蚀因子在2.0-2.5左右。

为了方便计算,在常规板制作计算时,使用计算线宽如下表:(对于非常规铜厚时则需要参考侧蚀因子进行计算及与工艺人员进行确认)。

使用计算间距(S)为顾客设计间距。

=顾客设计线宽)

(注:W

5.1.3铜厚

常规下,内层基铜厚为1OZ、0.5OZ、2OZ,外层基铜铜厚为HOZ、1OZ、2OZ。

常规情况下内层的基铜厚就是其成品的计算厚度。

以上仅供参考。

工程制作精简规范

工程制作精简规范1、钻孔制作:A.在客户没有要求孔径公差的情况下,表面处理是有铅喷锡或无铅喷锡时金属化孔加放0.15MM,表面处理是沉金、化银、化锡、OSP时金属化孔加放0.1MM,非金属化孔一律加放0.05MM,压接孔加放0.1MM.压接孔要求在刀具表上备注使用新的钻咀,注意有的订单有偏公差要求,例如:+0.2/-0,要求将成品孔径加大0.1,再保证+/-0.1MM。

B.分析钻孔,不得有重孔、近孔、少孔、多孔现象,孔到孔边距≥0.15MM,盘、孔等大或盘比孔小的无连接定位孔在客户没有孔属性要求时一律做成非金属化孔。

过孔可适当减小,以保证焊环。

如果槽孔不是很多,一律采用钻孔方式,条孔要在刀具表上注明,钻孔时使用槽刀。

如遇到连孔,不允许删除其中一个时,将连孔中大的一个孔单独做成一种孔径,以区分其它孔,在刀具表上注明此孔和哪种孔相连,让钻孔人员注意,以免造成断刀。

C.邮票孔一律按照0.5-0.6MM钻孔,孔边到边距离为0.3MM。

塞孔的孔径比钻孔孔径大0.2MM,塞孔铝片只钻需要塞的孔,≤0.6MM的孔要求塞孔,大于0.6MM的孔不用塞,是指钻孔孔径。

SET中在没有客户要求的情况下,工艺边上添加的定位孔为成品3.0MM,共计4个。

D.对于长/宽小于2倍的条孔,要求添加预钻孔,使用自动添加脚本,在条孔的两边各添加一个。

E.将钻孔自动导出之后,必须重新回调钻孔,确认是否一致,使用自动导出脚本时可能会出现丢槽孔,要特别注意。

2、内层制作:A.内层隔离正常情况下最小10mil ,内层隔离带最小8mil,内层孔距线最小0.15MM,内层外形内缩0.4MM,所有的非金属化圆孔、槽孔在内层均做成隔离、做在外形上的金属化槽孔,在内层也要做成隔离。

内层孔距线六层板≤6MIL,八层板≤7MIL,十层板≤8.5MIL,十二层及以上的板子≤10MIL,此种情况下在压合备注外发铆合,公司的制程不能实现。

B.过孔隔离及花盘可以适当调整,保证连接。

{5S6S现场管理}6S项目之板内阻抗板件质量改进

{5S6S现场管理}6S项目之板内阻抗板件质量改进经过一段时间的分析、总结,在接下来的一段时间内,板内阻抗过程控制勉强可以达到Cpk≥1.33,但板内阻抗控制中值极不理想(Av实测值平均与客户要求中值相差7%左右),阻抗超差问题仍不容乐观。

一、分析(A)选择变量,鱼骨图分析如下:二、改善(I)5.1方法方面➢板内阻抗和板边Coupon区别经分析,尽管测试coupon具有和主PCB相同的叠层和迹线构造,可以反映线路板的阻抗是否合格,但不能非常精确地忠实代表板内阻抗。

图1为典型的PCB测试用Coupon和板内阻抗真实走线。

可以看出Coupon和板内阻抗二者间存在较大的差别:A)虽二者走线间距、走线宽度一致,但coupon测试点的间距一般固定为100mil(即最初的双列直插式IC接脚间距),而板内真实走线的末端(即芯片接脚)间距是不同的,随着QFP、PLCC、BGA封装的出现,芯片接脚间距远小于双列直插式IC封装间距。

这种差分走线末端间距与走线间距差别引起阻抗不连续,带来不同的阻抗测试结果。

B)Coupon走线是理想化的直线,而PCB板内阻抗线因各种因素导致走线设计不规则,如下图所示:这种不断拐弯的传输线本身就构成了一个复杂的滤波器,由于滤波作用使得高速信号不断损耗、反射而衰减,测试阻抗值在走线弯折处变得不连续。

C)Coupon与板内阻抗走线在整个PCB上的位置不同。

Coupon一般位于PCB边缘,在PCB出厂时往往会被生产商去掉。

而板内阻抗真实走线的位置则相当多样,有的靠近电路板边缘,有的位于板中央。

针对这种差别,从方法设计方面加以系统改善板内阻抗:➢优化板内阻抗线宽补偿。

相对于板边Coupon,位于板中央的板内阻抗线蚀刻药水交换较慢,存在一定的“水池效应”;且板内阻抗线容易受图形本身影响、钻孔影响,线宽补偿难度远远高于板边Coupon。

按目前正常的线宽补偿,双线板内阻抗一般都要超出控制下限3-4Ω。

阻抗设计规范

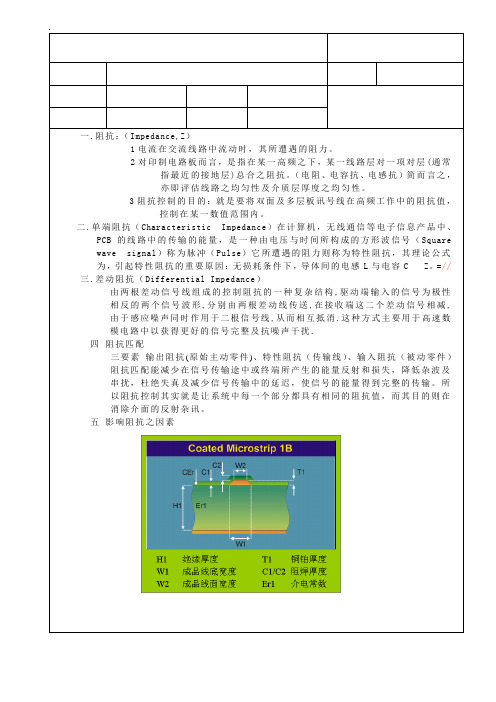

一.阻抗:(Impedance,Z)1电流在交流线路中流动时,其所遭遇的阻力。

2对印制电路板而言,是指在某一高频之下,某一线路层对一项对层(通常指最近的接地层)总合之阻抗。

(电阻、电容抗、电感抗)简而言之,亦即评估线路之均匀性及介质层厚度之均匀性。

3阻抗控制的目的:就是要将双面及多层板讯号线在高频工作中的阻抗值,控制在某一数值范围内。

二.单端阻抗(Characteristic Impedance)在计算机,无线通信等电子信息产品中、PCB的线路中的传输的能量,是一种由电压与时间所构成的方形波信号(Square wave signal)称为脉冲(Pulse)它所遭遇的阻力则称为特性阻抗,其理论公式为,引起特性阻抗的重要原因:无损耗条件下,导体间的电感L与电容C Z。

=//三.差动阻抗(Differential Impedance)由两根差动信号线组成的控制阻抗的一种复杂结构,驱动端输入的信号为极性相反的两个信号波形,分别由两根差动线传送,在接收端这二个差动信号相减,由于感应噪声同时作用于二根信号线,从而相互抵消.这种方式主要用于高速数模电路中以获得更好的信号完整及抗噪声干扰.四阻抗匹配三要素输出阻抗(原始主动零件)、特性阻抗(传输线)、输入阻抗(被动零件)阻抗匹配能减少在信号传输途中或终端所产生的能量反射和损失,降低杂波及串扰,杜绝失真及减少信号传输中的延迟,使信号的能量得到完整的传输。

所以阻抗控制其实就是让系统中每一个部分都具有相同的阻抗值,而其目的则在消除介面的反射杂讯。

五影响阻抗之因素2:阻抗COUPON设计单端阻抗:信号线设计长度为6 Inch差分阻抗: 信号线设计长度为6 Inch单端与差分的COUPON设计模块相同,只是一个为单线一个为双线.无论是单端模块还是差分模块,测试孔的位置必须与以上模块相同,否则将造成无法测试.3 COUPON的放置方式1.依据客户原稿设计2.设在折断边上(工艺边上)3.另设阻抗条(见以上附图所示)4 屏蔽层的判定5.Polar SI8000阻抗计算软件的应用.外层单端阻抗计算模块H1 绝缘层的厚度(对阻抗影响极大)Er1 介电常数值(普通FR-4板材一般在4.2-4.8之间)W1 成品线底宽度W2 成品线面宽度(线面宽度一般会比线底宽度小1mil左右)T1 成品铜铂厚度(成品铜铂厚度一般在1.2-1.4mil)C1 基材部分阻焊厚度(阻焊厚度一般在0.4-0.8mil)C2 信号线部分阻焊厚度CEr 阻焊介电常数Impedence 最终理论阻抗值(计算出来的理论值与客户要求的实际值不得相差2 ohm以内) 注:1.阻焊越厚阻值越低,影响值会在3ohm以内,如成品板实测阻值偏高,可多盖两次阻焊膜,以降低阻值2.阻值控制范围:单端35-75 ohm差分90-140 ohm外层差分计算模块H1 绝缘层的厚度(对阻抗影响极大)Er1 介电常数值(普通FR-4板材一般在4.2-4.8之间)W1 成品线底宽度W2 成品线面宽度(线面宽度一般会比线底宽度小1mil左右)S1 成品线间距T1 成品铜铂厚度(成品铜铂厚度一般在1.2-1.4mil)C1 基材部分阻焊厚度(阻焊厚度一般在0.4-0.8mil)C2 信号线部分阻焊厚度C3 基材部分阻焊厚度CEr 阻焊介电常数Impedence 最终理论阻抗值(计算出来的理论值与客户要求的实际值不得相差2 ohm以内)内层差分阻抗计算模块H1 绝缘层的厚度(与对应屏蔽层间的厚度)Er1 介电常数值(普通FR-4板材一般在4.2-4.8之间)H2绝缘层的厚度(与对应屏蔽层间的厚度)Er2介电常数值(普通FR-4板材一般在4.2-4.8之间)W1 成品线底宽度W2 成品线面宽度(线面宽度一般会比线底宽度小1mil左右)S1 成品线间距T1 成品铜铂厚度(成品铜铂厚度一般在1.2-1.4mil)Impedence 最终理论阻抗值(计算出来的理论值与客户要求的实际值不得相差2 ohm以内)差分阻抗与周围铜皮有间距,计算模块.H1 绝缘层的厚度(对阻抗影响极大)Er1 介电常数值(普通FR-4板材一般在4.2-4.8之间)W1 成品线底宽度W2 成品线面宽度(线面宽度一般会比线底宽度小1mil左右)S1 成品线间距G1信号线周围铜皮的大小(按101输入)G2信号线周围铜皮的大小(按100输入)D1信号线与周围铜皮的间距T1 成品铜铂厚度(成品铜铂厚度一般在1.2-1.4mil)C1 基材部分阻焊厚度(阻焊厚度一般在0.4-0.8mil)C2 信号线部分阻焊厚度C3 基材部分阻焊厚度CEr 阻焊介电常数Impedence 最终理论阻抗值(计算出来的理论值与客户要求的实际值不得相差2 ohm以内)。

阻抗制作规范 CAM

保证特性阻抗板工程设计和制作质量。

2.0 适用范围:适用于特性阻抗板的工程设计和制作。

3.0 职责:3.1 工程设计人员采用CITS25或SI6000软件进行辅助设计;3.2 工程设计阻抗值应保证在阻抗要求值的+/-5%之内,不在公差范围之内的均不合格;3.3 工程人员负责阻抗板工程制作处理;3.4 工程QA人员负责对阻抗设计和制作的检查;3.5 资料室人员负责菲林的检查。

4.0 阻抗测试合格标准:4.1阻抗要求值50以下,则其允许公差为+/-5欧姆;4.2阻抗要求值50以上,则其允许公差为+/-10%;4.3不在公差范围之内的均判定为不合格;4.4测试有效位置为测试附连片的3-7 INCH处,单点均在范围内视为合格。

5.0 制作程序:5.1工程人员根据顾客资料中提供的设计参数,采用CITS25或SI6000进行阻抗值计算,确定能否满足顾客阻抗值要求,若能满足其要求,按正常制作程序进行即可;若不能满足顾客阻抗值要求,则需要考虑重新设计及与顾客沟通确认设计参数,其具体的操作参照《非常规合同评审规范》;5.2工程人员确定好各参数,则在制作工程文件时按顾客要求的参数或经顾客确认的参数和《工程MI制作规范》制作工程资料,并填写《制造说明》、《特性阻抗制造说明》中的相应项目。

6.0 规范内容:6.1阻抗设计相关参数:6.1.1介质层厚度与介电常数(生益材料):6.1.1.1半固化片的厚度参数表:介质厚度HOZCopper/Gnd Gnd/Gnd Copper/Signal Gnd/Signal Signal/Signal1080 2.8 2.6 2.5 2.4 2.22116 4.6 4.4 4.2 4.0 3.87628 7.3 7.0 6.8 6.7 6.61OZ1080 2.8 2.6 2.5 2.4 2.22116 4.5 4.3 4.1 3.9 3.77628 7.1 6.8 6.6 6.5 6.4如果介质在HOZ和1OZ铜箔之间,其厚度按HOZ情况计算。

阻抗板的制作培训

阻抗板的制作培训1.线宽/线距常规下侧蚀因子在2.0-2.5左右。

为了方便计算,在常规板制作计算时,使用计算线宽如下表:(对于非常规铜厚时则需要参考侧蚀因子进行计算及与工艺人员进行确认)。

使用计算间距(S )为顾客设计间距。

(注:W 0=顾客设计线宽)铜厚常规下,内层基铜厚为1OZ 、0.5OZ 、2OZ ,外层基铜铜厚为HOZ 、1OZ 、2OZ 。

常规情况下内层的基铜厚就是其成品的计算厚度。

阻焊的厚度与对阻抗值的影响阻焊厚度为10um 对单端的阻抗值影响为1-3ohm (4%-6%),计算时定为减小2ohm ,外层设计计算时采用不盖阻焊的方法进行软件计算,再减去阻焊对阻抗值的影响而得到设计阻抗值。

阻焊厚度对差分阻抗影响较大,减小为5-12ohm ,计算时采用盖阻焊的模式来进行计算。

制作阻抗附连片用于阻抗测试:1阻抗附连片设计在板边,方向与阻抗线布方向平行,若阻抗线两个方向,原则上选用短边,但若短边长度不足9英寸或出现特殊情况如金手指等则将其设计在长边。

如图示。

100mil2 阻抗附连片与板平行,距离成品板间距100mil 。

3 测试线设计不小于7.5英寸,测试孔为PTH 孔,成品孔径要求1.25mm ,一般线路焊盘为80mil,而其阻焊盘为88mil,内层隔离焊盘和花焊盘按相关规范设定,要求阻抗最靠近板边的测试焊盘距离板边距离为30mil 左右,设计最小开料尺寸为佳。

4在开料尺寸比较小的情况下,为满足阻抗线的长度的情况下,往往需要另外加大开料,在阻抗线对不是很多情况下,可以将阻抗线做为曲线。

如下图示d=100mil 。

5 对于每组测试线,只需要一端有测试焊盘(孔)即可,另一端为悬空。

如下图所示:L1 6 从减小附连边角度出发,相邻对阻抗线的间距越小越好,但太近,会产生耦合干扰,所以同层相邻阻抗线对的间距需保证有100mil 。

L17单端测试要求:测试线对应的测试的孔与PLANE 层对应测试的孔间距为X 和Y 方向上均为100MIL 。

PCB线路板常用阻抗设计及叠层结构

PCB阻抗设计及叠层结构目录第四章六层板设计...........................................................................................................................6.20. SGSGSGGSGS || 50 75 || 150 || 2.4mm ...................................................................前言随着信号传输速度的迅猛提高以及高频电路的广泛应用,对印刷电路板也提出了更高的要求?要得到完整?可靠?精确?无干扰?噪音的传输信号?就必须保证印刷电路板提供的电路性能保证信号在传输过程中不发生反射现象,信号完整,传输损耗低,起到匹配阻抗的作用?为了使信号,低失真﹑低干扰?低串音及消除电磁干扰EMI?阻抗设计在PCB设计中显得越来越重要?对我们而言,除了要保证PCB板的短、断路合格外,还要保证阻抗值在规定的范围内,只有这两方向都合格了印刷板才符合客户的要求。

牧泰莱电路技术有限公司作为快速响应市场的PCB制造服务商,在建厂以来我们就对阻抗进行了大量的研究和开发?并且该类产品已成为公司的特色产品,在pcb业界留下很好的口碑?随着“阻抗”的进一步扩展和延伸,我们作为专业的PCB制造服务商,为能向客户提供优质的产品和高质的服务,对该类PCB的合作方面做如下建议:对于PCB 的阻抗控制而言,其所涉及的面是比较广泛的,但在具体的加工和设计时我们一般控制主要四个因素:Er--介电常数H---介质厚度W---走线宽度T---走线厚度Er(介电常数)大多数板料选用FR-4,该种材料的Er特性为随着加载频率的不同而变化,一般情况下Er的分水岭默认为1GHZ(高频)?目前材料厂商能够承诺的指标<5.4(1MHz)根据实际加工的经验,在使用频率为1GHZ以下的其Er认为4.2左右1.5—2.0GHZ的使用频率其仍有下降的空间?故设计时如有阻抗的要求则须考虑该产品的当时的使用频率? 我们在长期的加工和研发的过程中针对不同的厂商已经摸索出一定的规律和计算公式?我们全部采用行业内最好的生益板料,其各项参数都比较稳定。

阻抗控制

CAD

按阻抗线补偿

生 产 菲 林

内层图形转移 内层蚀刻 阻抗线控制

褪 资料传递

膜

自动光学检查 棕化/黑化 压 板

23

流程

Meadville Group

東莞生益電子有限公司

CAD

切

板

锣板边 钻 钻 带 磨批锋 孔

去钻污 沉 铜

正片做板

负片做板

流程

24

Meadville Group

東莞生益電子有限公司

概述

3

Meadville Group

東莞生益電子有限公司

而且当工作电压越低及频率越高时,线路太长超过了其逻辑临 界长度(Critical length)而成为distributed系统者,各种 不良效应将越加容易出现,而造成的多样噪声也愈难处理。 PCB制造中所提到的阻抗控制,就是对线路的宽度、高度、介质 层厚度、介质层的介电常数等等加以严格控制,从而达到对某 段线路的阻抗值Z0进行控制,使其能与该段线路之组件的阻抗 匹配,能够更好的实现讯号传输的目的。 由于阻抗值的计算颇为复杂,目前绝大多数PCB设计人员与PCB 制造厂家都采用一定的模拟软件进行模拟。我们采用的是POLAR 这一软件对PCB阻抗控制中不同的情况进行模拟计算然后与实际 值比较并加以修订。

阻抗计算

15

Meadville Group

東莞生益電子有限公司

三.流程:

1.内部首板IFA(inner first article)

对于阻抗控制要求较多,较为复杂批量较大的线路板,我们需要做内 部首板。就是将所有的阻抗要求设计在一条测试条内(特殊情况可能需要 多条)。然后将线宽为计算值的置于板中间。两边的线宽等差排列各四条。 比如:一阻抗要求为50欧姆。计算线宽为0.15毫米。我们将如下排列:

EMC十三条设计参考规则

《PCB Layout EMC 设计参考规则》1、 概述经验告诉我们,修改PCB layout 成功解决EMI 的案例很多, PCB 已成为EMI 设计的关键。

总结多年的经验,得出13条经典的设计规则。

希望通过理解和运用13条经典 EMI 规则,并在PCB layout 过程中进行控制,减少PCB 修改次数,提高研发效率。

本规则针对高速数字信号PCB 设计,适用于双面板、四层板及多层板。

2、 EMI 噪声模型差模计算公式:E=1.316×10-14(f 2·A·I)/rf ,差模电流的频率,单位是Hz ; A ,差模电流的环路面积,单位是m 2;I ,差模电流强度,单位是A ;r,观察点到差模电流环路的距离,单位是m。

共模计算公式:E=1.26×10-6(f ·I·l)/rf,共模电流频率,单位是Hz;I,共模电流,单位是A;l,电缆长度,单位是m;r ,测量天线到电缆的距离,单位是m 。

3、抑制共模辐射设计共模辐射是 EMI 最主要的干扰,通常是由于电路板地的“不平整”导致的,或者连接 Cable 线两端地电位的高低差而导致连接线变成辐射天线。

线路板则是由于地阻抗而引起电位高低不平,从而能量由高到低有了辐射的条件。

所以PCB 排版时要特别注意 PCB 地阻抗问题,从而减小其产生的干扰。

减小共模辐射常用的方法:(1)降低地阻抗以减小地电位差;(2)使用去耦电容 ;(3)使用铁氧体磁环 ;(4)使用共模滤波器(电源/信号)3.1 抑制共模辐射的PCB设计①、双面板尽量减少Bottom层走线,保证信号流向的地平面连续,不产生明显的地平面分割;②、四层及多层板应有完整的地网络平面层;③、良好的螺丝孔接地设计,保证螺丝孔与整机的系统地良好接触;④、高速信号的Cable线端的地平面尽量完整并与系统地良好接触,比如增加接地泡棉、增加接地片(建议深入了解整机结构,了解整机接地设计)⑤、保证IC每个供电管脚都有退藕电容设计;⑥、四层板及多层板电源分区四周增加退藕电容,避免电源平面与地平面产生谐振;4、抑制差模辐射设计信号流出至信号流入形成信号环路,每个环路都相当于一个天线,这是差模干扰发生原因,也是PCB 设计中EMI 控制的关键。

PCB设计规范V1.0

PCB设计规范版本号V1.0文档修改情况版本状态修订内容实施日期编制审核1.0 起草 2011-4-151 概述本文档的目的在于说明当使用ORCAD完成原理图设计后,使用Candence公司的Allegro完成PCB布线设计时,在使用Allegro设计PCB时的流程和一些注意事项,为一个工作组的设计人员提供设计规范,方便设计人员之间进行交流和相互检查。

本规范归定了我司PCB 设计的流程和设计原则,主要目的是为PCB 设计者提供必须遵循的规则和约定。

提高PCB 设计质量和设计效率。

提高PCB 的可生产性、可测试、可维护性。

2 专业术语PCB(Print circuit Board):印刷电路板。

原理图:电路原理图,用原理图设计工具绘制的、表达硬件电路中各种器件之间的连接关系的图。

网络表:由原理图设计工具自动生成的、表达元器件电气连接关系的文本文件,一般包含元器件封装、网络列表和属性定义等组成部分。

布局:PCB设计过程中,按照设计要求,把元器件放置到板上的过程仿真:在器件的IBIS MODEL或SPICE MODEL支持下,利用EDA 设计工具对PCB的布局、布线效果进行仿真分析,从而在单板的物理实现之前发现设计中存在的EMC问题、时序问题和信号完整性问题,并找出适当的解决方案。

3 设计流程PCB设计流程分为:PCB封装设计,创建网络表, PCB布局设计,设置布线约束条件,PCB布线设计,PCB检查,提交设计文件。

4 确定PCB封装打开网络表(可以利用一些编辑器辅助编辑),将所有封装浏览一遍,确保所有元件的封装都正确无误并且元件库中包含所有元件的封装,元件具体命名规则详见《PCB生产工艺规范电装规范》。

标准元件全部采用公司统一元件库中的封装。

元件库中不存在的封装,由专人建库。

详见《PCB生产工艺规范电装规范》5 结构设计建立PCB 结构图:根据结构图设置板框尺寸,按结构要素布置安装孔、接插件等需要定位的器件,并给这些器件赋予不可移动属性。

PCB设计规范大全

PCB设计规范大全PCB设计规范大全1,目的规范印制电路板(以下简称PCB)设计流程和设计原则,提高PCB设计质量和设计效率,保证PCB 的可制造性、可测试、可维护性。

2,范围所有PCB 均适用。

3,名词定义3.1原理图:电路原理图,用原理图设计工具绘制的、表达硬件电路中各种器件之间的连接关系的图。

3.2网络表:由原理图设计工具自动生成的、表达元器件电气连接关系的文本文件,一般包含元器件封装、网络列表和属性定义等组成部分。

3.3布局:PCB 设计过程中,按照设计要求,把元器件放置到板上的过程。

3.4模拟:在器件的IBIS MODEL 或SPICE MODEL 支持下,利用EDA 设计工具对PCB 的布局、布线效果进行模拟分析,从而在单板的物理实现之前发现设计中存在的EMC 问题、时序问题和信号完整性问题,并找出适当的解决方案。

3.5 SDRAM :SDRAM 是Synchronous Dynamic Random Access Memory(同步动态随机内存)的简称,同步是指时钟频率与CPU 前端总线的系统时钟频率相同,并且内部的命令的发送数据和数据的传输都以它为准;动态是指存储数组需要不断刷新来保证数据不丢失;随机是指数据不是线性一次存储,而是自由指定地址进行数据的读写。

3.6 DDR :DDR SDRAM 全称为Double Data Rate SDRAM ,DDR SDRAM 在原有的SDRAM 基础上改进而来。

DDR SDRAM 可在一个时钟周期内传送两次数据。

3.7 RDRAM :RDRAM 是Rambus 公司开发的具有系统带宽的新型DRAM ,它能在很高的频率范围内通过一个简单的总线传输数据。

RDRAM 更像是系统级的设计,它包括下面三个关键部分:3.7.1 基于DRAM 的Rambus(RDRAM );3.7.2 Rambus ASIC cells (专用集成电路单元);3.7.3 内部互连的电路,称为Rambus Channel(Rambus 通道);3.8 容性耦合:即电场耦合,引发耦合电流,干扰源上的电压变化在被干扰对象上引起感应电流而导致电磁干扰。

50欧姆,100欧姆板厚2.0MM4层板阻抗设计

备注: 我公司将严格按照客户确认的参数和结构生产加工,对影响阻抗的线宽、线距、铜箔厚度和介质厚度的控制 负责。 影响阻抗的因素是多方面的,敬请客户充分考虑资料的线路设计、电地布局及元器件匹配等因素。 特别需要说明的是:对于客户文件本身设计中存在的阻抗屏蔽层混乱、屏蔽不完全,差分线线长不等、间距不等、不 平行,阻抗线与铜皮之间距离不一致等情况我们会提出修改建议,但是不能代客户调整。如客户认为勿需调整,我司 只能对符合理论数据的阻抗设计负责。

L1 L4 L1 L4

特性 特性 差分 差分

9 9 6 6

5 5

top 18um

1 1 1 1

50 50 100 100

推 荐 参 数

线宽 MIL

9 9 6 6

5 5

1 1 1 1

50 50 100 100

+/-10% +/-10% +/-10% +/-10%

二、推荐层压结构

5mil 60.24mil 5mil PP L2/L3 35/35um PP bot 18um ER ER ER 4.2 4.2 4.2

铜厚(成 品)OZ 要求阻抗 值OHM

电话: 电话:

层数: 建议板厚: 参考层 L2 L3 L2 L3

传真: 传真:

4 2.0mm 线距 MIL 铜皮 间距 板厚公差:

铜厚(成 建议阻抗 品)OZ 值OHM

+/-0.18mm

阻抗值公 差范围

设 计 参 数

阻抗 线宽 线距 铜皮 属性 MIL MIL 间距

PCB制程能力尺寸公差设计规范_相互

21

22

23

限制:原稿線路PAD與PAD之間距至少0.25mm(不足0.25時需建議客戶開天窗不作隔線 下墨)

單邊 0.065mm 單邊 0.065mm 單邊 0.1mm 0.08mm 0.08mm 0.1mm 0.13

24

25

26

限制:原稿線路PAD與PAD之間距至少0.3mm(不足0.3時需建議客戶開天窗不作隔線下 墨)

Laser 孔之 底銅要求

16

All Types

COB金線拉力保證 線寬/線距 pitch (min) PAD 大小 底銅 Annular Ring (Min) 底銅 Annular Ring (最佳值)

5g以上 Min. 0.1mm

限制:客戶原稿設計至少線寬線距5mil/5mil--如COB面有盲孔設計者客戶原稿設計至少線寬線距 5.5mil/5.5mil 限制 1:蝕刻銅厚 1oz以下之產品 , 限制 2:當 pitch=0.5mm其線路 pad只能設 0.32,mask0.37故 成品 BGA之 pad為 0.24mm(min)--需告知客戶 避免 Laser孔偏移 ,需增加管制站做技術管控

能力

+/-20% +/-20% +/-20% +/-20% +/-20% +/-20% +/-10% 單邊 0.1mm 單邊 0.1mm 單邊 0.15mm 單邊 0.075mm 單邊 0.075mm 單邊 0.1mm 0.08mm 0.08mm 0.1mm 0.1mm

備註

當客戶原稿設計已無補線寬之補償空間時須 另外協定規格(工程問題回饋單)

19

當客戶原稿設計已無補線寬之補償空間時須 反應客戶修改Layout(工程問題回饋單)

PCBEMC设计规范方案

PCB EMC设计规范目录第一部分布局1 层的设置1.1 合理的层数1.1.1 Vcc、GND的层数1.1.2 信号层数1.2 单板的性能指标与成本要求1.3 电源层、地层、信号层的相对位置1.3.1 Vcc、GND 平面的阻抗以及电源、地之间的EMC环境问题1.3.2 Vcc、GND 作为参考平面,两者的作用与区别1.3.3 电源层、地层、信号层的相对位置2 模块划分及特殊器件的布局2.1 模块划分2.1 .1 按功能划分2 .1.2 按频率划分2.1.3 按信号类型分2.1.4 综合布局2.2 特殊器件的布局2.2.1 电源部分2.2.2 时钟部分2.2.3 电感线圈2.2.4 总线驱动部分2.2.5 滤波器件3 滤波3.1 概述3.2 滤波器件3.2.1 电阻3.2.2 电感3.2.3 电容3.2.4 铁氧体磁珠3.2.5 共模电感3.3 滤波电路3.3.1 滤波电路的形式3.3.2 滤波电路的布局与布线3.4 电容在PCB的EMC设计中的应用3.4.1 滤波电容的种类3.4.2 电容自谐振问题3.4.3 ESR对并联电容幅频特性的影响3.4.4 ESL对并联电容幅频特性的影响3.4.5 电容器的选择3.4.6 去耦电容与旁路电容的设计建议3.4.7 储能电容的设计4 地的分割与汇接4.1 接地的含义4.2 接地的目的4.3 基本的接地方式4.3.1 单点接地4.3.2 多点接地4.3.3 浮地4.3.4 以上各种方式组成的混合接地方式4.4 关于接地方式的一般选取原则4.4.2 背板接地方式4.4.3 单板接地方式第二部分布线1 传输线模型及反射、串扰1.1 概述:1.2 传输线模型1.3 传输线的种类1.3.1 微带线(microstrip)1.3.2 带状线(Stripline)1.3.3嵌入式微带线1.4 传输线的反射1.5 串扰2 优选布线层2.1 表层与内层走线的比较2.1.1 微带线(Microstrip)2.1.3 微带线与带状线的比较2.2 布线层的优先级别3 阻抗控制3.1 特征阻抗的物理意义3.1.1 输入阻抗:3.1.2 特征阻抗3.1.3 偶模阻抗、奇模阻抗、差分阻抗3.2 生产工艺对对阻抗控制的影响3.3 差分阻抗控制3.3.1 当介质厚度为5mil时的差分阻抗随差分线间距的变化趋势3.3.2 当介质厚度为13 mil时的差分阻抗随差分线间距的变化趋势3.3.3 当介质厚度为25 mil时的差分阻抗随差分线间距的变化趋势3.4 屏蔽地线对阻抗的影响3.4.1 地线与信号线之间的间距对信号线阻抗的影响3.4.2 屏蔽地线线宽对阻抗的影响3.5 阻抗控制案例4 特殊信号的处理5 过孔5.1 过孔模型5.1.1 过孔的数学模型5.1.2 对过孔模型的影响因素5.2 过孔对信号传导与辐射发射影响5.2.1 过孔对阻抗控制的影响5.2.2 过孔数量对信号质量的影响6 跨分割区及开槽的处理6.1 开槽的产生6.1.1 对电源/地平面分割造成的开槽6.2 开槽对PCB板EMC性能的影响6.2.1 高速信号与低速信号的面电流分布6.2.2 分地”的概念6.2.3 信号跨越电源平面或地平面上的开槽的问题6.3 对开槽的处理6.3.1 需要严格的阻抗控制的高速信号线,其轨线严禁跨分割走线6.3.2 当PCB板上存在不相容电路时,应该进行分地的处理6.3.3 当跨开槽走线不可避免时,应该进行桥接6.3.4 接插件(对外)不应放置在地层隔逢上6.3.5 高密度接插件的处理6.3.6 跨“静地”分割的处理7 信号质量与EMC 7.1 EMC简介7.2 信号质量简介7.3 EMC与信号质量的相同点7.4 EMC与信号质量的不同点7.5 EMC与信号质量关系小结第三部分背板的EMC设计1 背板槽位的排列1.1 单板信号的互连要求1.2 单板板位结构1.2.1 板位结构影响;1.2.2 板间互连电平、驱动器件的选择2 背板的EMC设计2.1 接插件的信号排布与EMC设计2.1.1 接插件的选型2.1.2 接插件模型与针信号排布2.2 阻抗匹配2.3 电源、地分配2.3.1 电源分割及热插拔对电源的影响2.3.2 地分割与各种地的连接2.3.3屏蔽层第四部分射频PCB的EMC设计1 板材1.1 普通板材1.2 射频专用板材2 隔离与屏蔽2.1 隔离2.2 器件布局2.3 敏感电路和强辐射电路2.4 屏蔽材料和方法2.5 屏蔽腔的尺寸3 滤波3.1 电源和控制线的滤波3.2 频率合成器数据线、时钟线、使能线的滤波4 接地4.1 接地分类4.2 大面积接地4.3 分组就近接地4.4 射频器件接地4.4 接地时应注意的问题4.5 接地平面的分布5 布线5.1 阻抗控制5.2 转角5.3 微带线布线5.4 微带线耦合器5.5 微带线功分器5.6 微带线基本元件5.7 带状线布线5.8 射频信号走线两边包地铜皮6 其它设计考虑第一部分布局1 层的设置在PCB的EMC设计考虑中,首先涉及的便是层的设置;单板的层数由电源、地的层数和信号层数组成;电源层、地层、信号层的相对位置以及电源、地平面的分割对单板的EMC指标至关重要。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1.0 目的:保证特性阻抗板工程设计和制作质量。

2.0 适用范围:适用于特性阻抗板的工程设计和制作。

3.0 职责:

3.1 工程设计人员采用CITS25软件进行辅助设计;

3.2 工程设计阻抗值应保证在阻抗要求值的+/-5%之内,不在公差范围之内的均不合格。

3.3 工程人员负责阻抗板工程制作处理;

3.4 工程QA人员负责对阻抗设计和制作的检查;

3.5 资料室人员负责菲林的检查。

4.0 规范说明

4.1阻抗板最终测试合格标准:

4.1.1阻抗要求值50以下,则其允许公差为+/-5欧姆;

4.1.2阻抗要求值50以上,则其允许公差为+/-10%;

4.1.3不在公差范围之内的均判定为不合格;

4.1.4其中测试有效位置为测试附连片的3-7INCH处,单点均在范围内视为合格。

4.2阻抗设计合格标准+/-5%。

4.3 制作程序:

4.3.1工程人员根据顾客资料确定阻抗设计阻抗值要求及提供的参数要求;

4.3.2工程人员采用CITS25进行阻抗设计计算,根据要求确定各对应参数;若有参数与顾客提供

参数要求有所到之处不符则需要重新考虑设计或与顾客沟通确认设计参数;

4.3.3工程人员确定好各参数则在制作工程文件时按顾客要求参数和《工程MI制作规范》制作工

程资料,并填写《特性阻抗制作说明》。

5.0 规范内容:

5.1阻抗设计相关参数:

5.1.1介质层厚度与介电常数(生益材料):

如果介质在内层HOZ和1OZ铜箔之间,其厚度按HOZ情况计算。

对于相邻外层的半固化片的厚度取值,以对内层的铜箔为准;对于光板情况,在计算其相邻半固化片厚度时,将光面看作Copper。

5.1.1.3介电常数:

对介电常数的取值,要关键看其介质的厚度来对应查找其对应的介电常数,可以按最接近的原则进行选择;如果计算的介质厚度位于列表中的两个介质厚度中间,则介电常数取列表相应两个介电常数的平均值;如果顾客提供板材,则按顾客提供板材的介电常数取值。

5.1.2线宽/线距

常规下侧蚀因子在2.0-2.5左右。

为了方便计算,在常规板制作计算时,使用计算线宽如下表:(对于非常规铜厚时则需要参考侧蚀因子进行计算及与工艺人员进行确认)。

使用计算间距(S)为顾客设计间距。

=顾客设计线宽)

(注:W

5.1.3铜厚

常规下,内层基铜厚为1OZ、0.5OZ、2OZ,外层基铜铜厚为HOZ、1OZ、2OZ。

常规情况下内层的基铜厚就是其成品的计算厚度。

5.1.4阻焊的厚度与对阻抗值的影响

阻焊厚度为10um对单端的阻抗值影响为1-3ohm(4%-6%),计算时定为减小2ohm,外层设计计算时采用不盖阻焊的方法进行软件计算,再减去阻焊对阻抗值的影响而得到设计阻抗值。

阻焊厚度对差分阻抗影响较大,减小为5-12ohm,计算时采用盖阻焊的模式来进行计算。

5.2 制作阻抗附连片用于阻抗测试:

5.2.1阻抗附连片设计在板边,方向与阻抗线布方向平行,若阻抗线两个方向,原则上选用短边,

但若短边长度不足9英寸或出现特殊情况如金手指等则将其设计在长边。

如图示。

100mil

5.2.2 阻抗附连片与板平行,距离成品板间距100mil 。

5.2.3 测试线设计不小于7.5英寸,测试孔为PTH 孔,成品孔径要求1.25mm ,一般线路焊盘为80mil,

而其阻焊盘为88mil,内层隔离焊盘和花焊盘按相关规范设定,要求阻抗最靠近板边的测试 焊盘距离板边距离为30mil 左右,设计最小开料尺寸为佳。

5.2.4在开料尺寸比较小的情况下,为满足阻抗线的长度的情况下,往往需要另外加大开料,在

阻抗线对不是很多情况下,可以将阻抗线做为曲线。

如下图示d=100mil 。

5.2.5 对于每组测试线,只需要一端有测试焊盘(孔)即可,另一端为悬空。

如下图所示: L1 5.2.6 从减小附连边角度出发,相邻对阻抗线的间距越小越好,但太近,会产生耦合干扰,所以

同层相邻阻抗线对的间距需保证有100mil 。

L1

5.2.7单端测试要求:测试线对应的测试的孔与PLANE 层对应测试的孔间距为X 和Y 方向上均为

100MIL 。

不可使用差分测试上的一组来设计成为单端测试线。

如图示:

5.2.8差分测试要求:测试线对应的孔与PLANE 层对应的孔间距在X 和Y 方向上均为100MIL ,两

差动线间距为200MIL 如图示:

5.2.9 一般将外层阻抗线设计靠近板内,单端与差分线的阻抗测试线要分开设计。

5.2.10要求将阻抗设计线和焊盘所对应的层次标注在相应的线路层,并将其对应要求阻抗线的线

宽也标注在线路旁,方便工序控制及阻抗测试。

5.2.11附连片上的线宽补偿比板内多0.2mil ,资料室检查底片线宽保证+/-0.5mil 公差范围内。

5.2.12附连片上外层线路在不影响阻抗电性能的基材区加入分流块,建议采用80mil 大小与间距,

但各分流块之间不可互相连接。

但对于次外层只有一个屏蔽PLANE 层控制阻抗情况,即(Embedded Microstrip )和(Edge-coupled Embedded Microstrip )模式,附连片外层不允许铺分流块,其对阻抗测试的影响较大。

5.2.13附连片上内层线路需要有测试要求的孔对应焊盘设计并对应测试线连接,而其他位置均设计焊盘及可,而接屏蔽PLANE 层的孔应与相邻的两个PLANE 层都应相连,在其余各PLANE 层均应隔离。

对于接参考PLANE 层的孔由于共用地层情况会造成与多个PLANE 层相连,可以不予理会,其对阻抗测试结果不会造成影响。

5.2.14 对于单端外层共面线(Surface Coplanar Line )情况,附连片设计应与板内情况一致,

即阻抗线周围需铺铜,线到铜面间距与板内注意保持一致,阻抗线周围的铜皮可以不接屏蔽地层。

5.2.15附连片的设计注意与板内一致原则,特别是内层正片、外层大铜面的效果以及双面板屏蔽

地层的制作(不能将屏蔽地层制作成分流块形式)。

5.2.16附连片上字符层上应注明各测试孔所对应的层数,各层阻抗线的线宽,板的产品编号,以

方便测试,并加上字符块,大小一般为200mil*100mil,用于测试记录理论值与实际测量值。

5.2.17单端的附连片其只做一个接屏蔽层接口,以减小附连片尺寸。

5.2.18对附连片的标注要清楚,将各组测试线交叉错开排放,其测试端接口不要全放在同一位置

上,其做标记要紧靠测试点处,使其清楚。

5.2.19附连片与板有效图形的间距不能大于120mil ,在板上位置要与内外层的大铜面区保持在同

一方向,防止其层压因树脂填充不好,铜箔延展性受阻,板起皱,不能将附连片放在基材空白区多的位置。