FPGA VHDL4位全加器

FPGA 4位全加器的设计

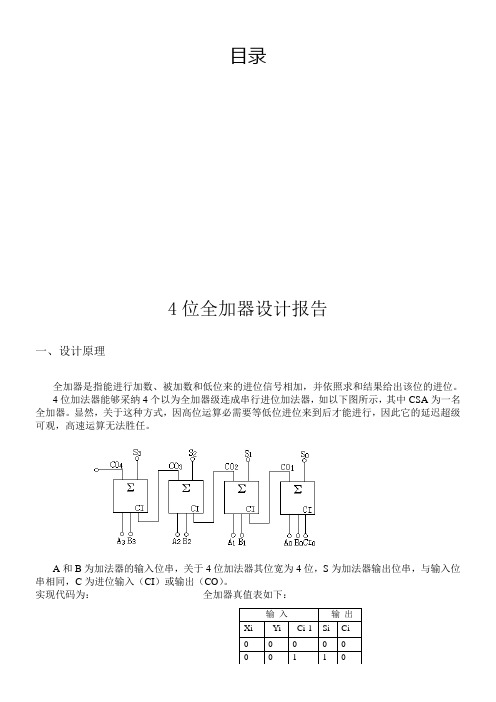

目录4位全加器设计报告一、设计原理全加器是指能进行加数、被加数和低位来的进位信号相加,并依照求和结果给出该位的进位。

4位加法器能够采纳4个以为全加器级连成串行进位加法器,如以下图所示,其中CSA为一名全加器。

显然,关于这种方式,因高位运算必需要等低位进位来到后才能进行,因此它的延迟超级可观,高速运算无法胜任。

A和B为加法器的输入位串,关于4位加法器其位宽为4位,S为加法器输出位串,与输入位串相同,C为进位输入(CI)或输出(CO)。

实现代码为:全加器真值表如下:输入输出Xi Yi Ci-1 Si Ci0 0 0 0 00 0 1 1 0output[3:0]sum;output cout;input[3:0]ina,inb;input cin;assign {count,sum}=ina+inb+cin;endmodule二、设计目的⑴熟悉开发环境,把握工程的生成方式。

⑵熟悉SEED-XDTK XUPV2Pro实验环境。

⑶了解Verilog HDL语言在FPGA中的利用。

⑷了解4位全加器的Verilog HDL语言实现。

三、设计内容用Verilog HDL语言设计4位全加器,进行功能仿真演示。

四、设计步骤1、创建工程及设计输入。

⑴在E:\progect\目录下,新建名为count8的新工程。

⑵器件族类型(Device Family)选择“Virtex2P”器件型号(Device)选“XC2VP30 ff896-7”综合工具(Synthesis Tool)选“XST(VHDL/Verilog)”仿真器(Simulator)选“ISE Simulator”⑶下面一直next和确信。

⑷设计输入:在源代码窗口中单击右键,在弹出的菜单被选择“New Source”,在弹出的对话框被选择“Verilog Moudle”,在右端的“File name”中输入源文件名adder4,下面各步单击“Next”按钮。

VHDL全加器的设计

实验四全加器的设计一、实验目的通过VHDL语言设计4位全加器,掌握加法器的设计方法;学习利用软件工具的模块封装(1位全加器)及连接使用方法,在软件工具的原理图输入法下完成4位全加器的设计。

二、实验原理根据数字电路全加器的理论知识,按图1所示的1位全加器的管脚图进行设计。

图 1 1位全加器管脚图三、实验内容用VHDL语言设计1位全加器,进行编译、波形仿真及器件编程。

代码一见附录,仿真图如下图 2 1位全加器功能仿真图使用原理图设计4位全加器进行编译、波形仿真及器件编程。

原理图如下仿真图如下用VHDL语言设计4位全加器,进行编译、波形仿真及器件编程,代码二见附录,仿真图如下图 5 4位全加器功能仿真图附录代码一、library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity swqjq isport (a,b:in std_logic;ci:in std_logic;co:out std_logic;s:out std_logic);end swqjq;architecture zhang of swqjq isbeginprocess (a,b,ci)beginif(a='0'and b='0'and ci='0') thens<='0';co<='0';elsif(a='1'and b='0'and ci='0') thens<='1';co<='0';elsif(a='0'and b='1'and ci='0') thens<='1';co<='0';elsif(a='1'and b='1'and ci='0') thens<='0';co<='1';elsif(a='0'and b='0'and ci='1') thens<='1';co<='0';elsif(a='0'and b='1'and ci='1') thens<='0';co<='1';elsif(a='1'and b='0'and ci='1') thens<='0';co<='1';elses<='1';co<='1';end if;end process;end zhang;代码二、library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity adder4b isport ( ci:in std_logic;a,b:in std_logic_vector(3 downto 0);s:out std_logic_vector(3 downto 0);co:out std_logic);end adder4b;architecture zhang of adder4b issignal sint:std_logic_vector(4 downto 0); signal aa,bb:std_logic_vector(4 downto 0); beginaa<='0'&a(3 downto 0);bb<='0'&b(3 downto 0);sint<=aa+bb+ci;s(3 downto 0)<=sint(3 downto 0);co<=sint(4);end zhang;。

VHDL语言完成4位十进制计数器、4位锁存器、测频控制器的设计.docx

电子设计自动化实验实验名称综合性实验二、硬件描述语言的层次化设计实验设备(1) EDA实验箱 ( 型号 ), ( 2)计算机 , ( 3) EDA软件( QuartusII )实验目的1、熟悉 EDA软件( QuartusII)的硬件描述语言输入设计方法;2、掌握 VHDL语言的层次化设计方法和仿真分析方法;3、了解功能仿真、时序仿真和时序参数分析的意义。

实验内容1、用 VHDL语言完成 4 位十进制计数器、 4 位锁存器、测频控制器的设计,包括编译、综合、仿真;**2、采用层次化设计的方法,用VHDL语言的元件例化语句写出 4 位十进制频率计的顶层文件,并分别给出其测频功能和时序仿真分析波形图,并加以分析;**3、用 EDA实验箱进行硬件验证,并分析测量结果; 建议硬件测试实验电路采用电路结构,待测信号F_IN 接 clock0 ;测频控制时钟CLK接 clock2 ; **4、在 2 基础上将其扩展为8 位十进制频率计,或带译码输出的 4 位十进制频率计。

实验报告要求根据以上实验内容写出实验报告:1、简述 4 位频率计模块的工作原理及其设计、编译、仿真分析过程;2、给出模块设计文件、仿真测试文件、仿真结果波形图及其分析报告;3、简述硬件验证过程和验证结果。

1、简述 4 位频率计模块的工作原理根据频率的定义和频率测量的基本原理,测定信号的频率必须有一个脉宽为 1 秒的对输入信号脉冲计数允许的信号; 1 秒计数结束后,计数值锁入锁存器的锁存信号和为下一测频计数周期作准备的计数器清0 信号。

这 3 个信号可以由一个测频控制信号发生器产生,即TESTCTL,它的设计要求是,TESTCTL的计数使能信号CNT_EN能产生一个1 秒脉宽的周期信号,并对频率计的每一计数器 CNT10的 ENA使能端进行同步控制。

当CNT_EN高电平时,允许计数;低电平时停止计数,并保持其所计的脉冲数。

在停止计数期间,首先需要产生一个锁存信号LOAD,在该信号上升沿时,将计数器在前1 秒钟的计数值锁存进各锁存器REG4B中,并由外部的7 段译码器译出,显示计数值。

四位全加器实验报告

武汉轻工大学数学与计算机学院《计算机组成原理》实验报告题目:4位二进制计数器实验专业:软件工程班级:130X班学号:XXX姓名:XX指导老师:郭峰林2015年11月3日【实验环境】1. Win 72. QuartusII9.1计算机组成原理教学实验系统一台。

【实验目的】1、熟悉VHDL 语言的编写。

2、验证计数器的计数功能。

【实验要求】本实验要求设计一个4位二进制计数器。

要求在时钟脉冲的作用下,完成计数功能,能在输出端看到0-9,A-F 的数据显示。

(其次要求下载到实验版实现显示)【实验原理】计数器是一种用来实现计数功能的时序部件,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能。

计数器由基本的计数单元和一些控制门所组成,计数单元则由一系列具有存储信息功能的各类触发器构成,这些触发器有RS 触发器、T 触发器、D 触发器及JK 触发器等。

计数器在数字系统中应用广泛,如在电子计算机的控制器中对指令地址进行计数,以便顺序取出下一条指令,在运算器中作乘法、除法运算时记下加法、减法次数,又如在数字仪器中对脉冲的计数等等。

计数器按计数进制不同,可分为二进制计数器、十进制计数器、其他进制计数器和可变进制计数器,若按计数单元中各触发器所接收计数脉冲和翻转顺序或计数功能来划分,则有异步计数器和同步计数器两大类,以及加法计数器、减法计数器、加/减计数器等,如按预置和清除方式来分,则有并行预置、直接预置、异步清除和同步清除等差别,按权码来分,则有“8421”码,“5421”码、余“3”码等计数器,按集成度来分,有单、双位计数器等等,其最基本的分类如下:计数器的种类⎪⎪⎪⎪⎪⎪⎩⎪⎪⎪⎪⎪⎪⎨⎧⎪⎩⎪⎨⎧⎪⎩⎪⎨⎧⎩⎨⎧进制计数器十进制计数器二进制计数器进制可逆计数器减法计数器加法计数器功能异步计数器同步计数器结构N 、、、321 下面对同步二进制加法计数器做一些介绍。

同步计数器中,所有触发器的CP 端是相连的,CP 的每一个触发沿都会使所有的触发器状态更新。

四位全加器

1.C机一台;

2.Altera Blaster下载器一根;

3.KHF-5实验箱一台。

三、实验原理

全加器是由两个加数Xi和Yi以及低位来的进位Ci-1作为输入,产生本位和Si以及向高位的进位Ci的逻辑电路。它不但要完成本位二进制码Xi和Yi相加,而且还要考虑到低一位进位Ci-1的逻辑。对于输入为Xi、Yi和Ci-1,输出为Si和Ci的情况,根据二进制加法法则可以得到全加器的真值表如下表9-1所示:

五、实验过程

1.打开QUARTUSII软件,新建一个工程。

2.建完工程之后,再新建一个VHDL File,打开VHDL编辑器对话框。

3.按照实验原理和自己的想法,在VHDL编辑窗口编写VHDL程序,用户可参照光盘中提供的示例程序。

4.编写完VHDL程序后,保存起来。方法同实验一。

5.对编写的VHDL程序进行编译并仿真,对程序的错误进行修改。

BEGIN

abc <= a & b ; --a相并b,即a与b并置操作

PROCESS(abc)

BEGIN

CASE abc IS --类似于真值表的CASE语句

WHEN "00" => so<='0'; co<='0' ;

WHEN "01" => so<='1'; co<='0' ;

WHEN "10" => so<='1'; co<='0' ;

ENTITY h_adder IS

PORT (a, b : IN STD_LOGIC;

1数电实验6PLD VHDL 四位串行二进制加法器 樊1

用Quartus II 软件原理图与VHDL 混合编程编写:樊伟敏1. 用Quartus II 软件原理图与VHDL 混合编写四位串行全加器四位串行全加器电路图如图1所示。

图1 四位串行全加器电路2. 新建原理图文件新建项目add4a ,出现如图2所示的界面。

执行【File\New ...】菜单命令,进入如图3所示的新建文件类型选择对话框。

选择Design Files 中的Block Diagram/Schematic file 项。

点击【OK 】按钮,进入如图4所示的新建原理图窗口。

图2 新建项目add4a 界面图3 新建文件类型选择对话框图4 新建原理图窗口3. 顶层原理图绘制3.1绘制图形块符号点击绘图图形块工具图标,在原理图窗口中拖动鼠标绘制出如图5所示的图形块符号。

3.2 图形块属性设置鼠标右键点击图5所示的图形块,弹出的如图6所示的快捷菜单。

选择Block Properties项,弹出模块属性对话框。

在如图7所示的General标签页中输入自定义的模块名,由于串行四位全加器是由4个一位全加器构成,所以在Name栏中输入自定义的一位全加器的名称,例如:add1a。

然后点击I/Os标签页,在该标签页中设置电路模块的输入输出端口的名称和类型,其中BIDIR为双向端口,INPUT为输入端口,OUTPUT为输出端口。

按如图8所示建立三个输入端a(加数)、b(被加数)、c0(低位进位)和两个输出端s(和)、c1(进位)。

在输入第一个名称和类型后点击【OK】,然后输入下一个名称和类型,直至全部输入以上五个端口的名称和类型后点击【OK】,完成图形块属性设置。

图5 在原理图窗口中绘制图形块符号图6 右键快捷菜单图7 在General标签页中输入自定义的模块名add1a图8 建立五个端口的名称和类型。

3.2 复制自定义的图形块符号在原理图窗口中激活自定义的图形块符号,使用右键快捷菜单中选择复制项,然后选择粘贴项,复制符号块,完成后的原理图编辑窗口的显示如图9所示。

完整四位全加全减器设计

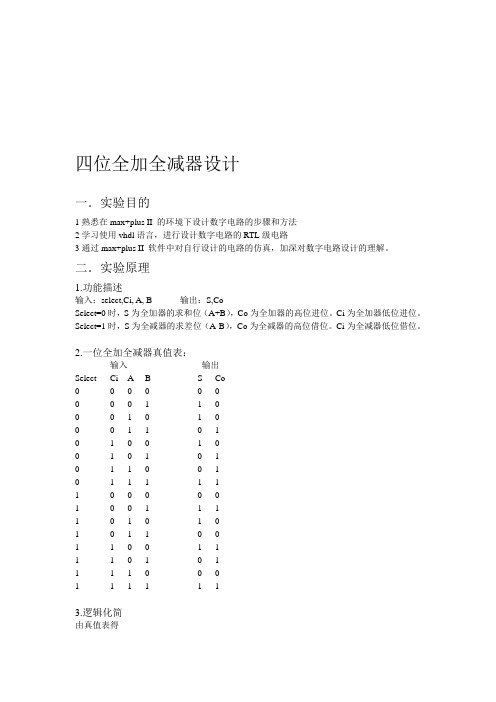

四位全加全减器设计一.实验目的1熟悉在max+plus II 的环境下设计数字电路的步骤和方法2学习使用vhdl语言,进行设计数字电路的RTL级电路3通过max+plus II 软件中对自行设计的电路的仿真,加深对数字电路设计的理解。

二.实验原理1.功能描述输入:select,Ci, A, B 输出:S,CoSelect=0时,S为全加器的求和位(A+B),Co为全加器的高位进位。

Ci为全加器低位进位。

Select=1时,S为全减器的求差位(A-B),Co为全减器的高位借位。

Ci为全减器低位借位。

2.一位全加全减器真值表:输入输出Select Ci A B S Co0 0 0 0 0 00 0 0 1 1 00 0 1 0 1 00 0 1 1 0 10 1 0 0 1 00 1 0 1 0 10 1 1 0 0 10 1 1 1 1 11 0 0 0 0 01 0 0 1 1 11 0 1 0 1 01 0 1 1 0 01 1 0 0 1 11 1 0 1 0 11 1 1 0 0 01 1 1 1 1 13.逻辑化简由真值表得S=A○十B○十Ci=((A○十Select)○十B○十Ci)○十SelectCo=(A○十Select)B+Ci((A○十Select)+B)=((A○十Select)○十B)Ci+(A○十Select)B对于半加器的逻辑表达式为:S=A○十B Co=AB综上,一位全加全减器可由两个半加器,两个异或门和一个或门组成。

4.毛刺的产生与消除组合逻辑电路由于输入到输出各端的延时不同,在输出端稳定之前会产生错误的输出。

在本电路中,由于低位的进位或借位传输到输出的时间比其他信号传输的延时要长,因此当低位产生进位或借位时会出现错误的输出。

一种常见的方法是利用D触发器的D输入端对毛刺信号不敏感的特点,在输出信号的保持时间内,用触发器读取组合逻辑的输入输出信号。

由组合逻辑电路的最大延时Td为16.7ns,D触发器的时钟周期T应略大于Td,取20ns。

采用VHDL层次化文件设计一个四位全加器

采用VHDL层次化文件设计一个四位全加器一、实训目的1.巩固VHDL层次化文件设计方法。

2.培养应用VHDL层次化文件设计法的技能。

二、实训器材计算机与Quartus Ⅱ工具软件。

三、实训指导(一)实训原理4位二进制加法器由4个全加器构成,而全加器又由一个半加器和一个或门构成,半加器的真值表如表5-1所示:表5-1 半加器的真值表半加器的逻辑表达式为:so=NOT(a XOR(NOT b))co=a AND b一位全加器的真值表如表5-2所示:表5-2 一位全加器的真值表(二)实训步骤1.电路模块划分根据算法分析,4位二进制加法器可由4个全加器构成,画出其原理方框图。

全加器原理方框图如图5-1所示。

而每个全加器又可划分为一个半加器和一个或门这两个更小的模块,画出其原理方框图。

4位二进制加法器原理方框图如图5-2所示。

图5-1 一位全加器原理方框图图5-2 4位二进制加法器原理框图2.设计底层设计文件(1)设计半减器文件halfadd.vhd。

(2)设计或门电路文件orgate.vhd。

(3)设计全加器电路文件fulladd.vhd,其中把半加器和或门电路文件作为元件调用。

3.设计顶层设计文件设计顶层设计文件add4.vhd,其中把全加器文件作为元件调用。

VHDL代码如下:halfadd.vhd文件代码如下:ENTITY halfadd ISPORT(a,b:IN BIT;so,co:OUT BIT);END halfadd;ARCHITECTURE a OF halfadd ISBEGINPROCESS(a,b)BEGINso<=NOT(a XOR(NOT b)) AFTER 10ns; co<=a AND b AFTER 10 ns;END PROCESS;END a;orgate.vhd文件代码如下:ENTITY orgate ISPORT(a1,b1:IN BIT;o:OUT BIT);END orgate;ARCHITECTURE a OF orgate ISBEGINo<=a1 OR b1;END a;fulladd.vhd文件代码如下:ENTITY fulladd ISPORT(i1,i2,c_in:IN BIT;fs,c_out:OUT BIT);END fulladd;ARCHITECTURE a OF fulladd ISSIGNAL temp_s,temp_c1,temp_c2:BIT; COMPONENT halfaddPORT(a,b:IN BIT;so,co:OUT BIT);END COMPONENT;COMPONENT orgatePORT(a1,b1:IN BIT;o:OUT BIT);END COMPONENT;BEGINU0:halfadd PORT MAP(i1,i2,temp_s,temp_c1);U1:halfadd PORT MAP(temp_s,c_in,fs,temp_c2);U2:orgate PORT MAP(temp_c1,temp_c2,c_out);END a;add4.vhd文件代码如下:ENTITY add4 ISPORT(a,b:IN BIT_VECTOR(3 DOWNTO 0);cin:IN BIT;so:OUT BIT_VECTOR(3 DOWNTO 0);co:OUT BIT);END add4;ARCHITECTURE a OF add4 ISSIGNAL temp_co0,temp_co1,temp_co2:BIT;COMPONENT fulladd ISPORT(i1,i2,c_in:IN BIT;fs,c_out:OUT BIT);END COMPONENT;BEGINU0:fulladd PORT MAP(a(0),b(0),cin,so(0),temp_co0);U1:fulladd PORT MAP(a(1),b(1),temp_co0,so(1),temp_co1); U2:fulladd PORT MAP(a(2),b(2),temp_co1,so(2),temp_co2); U3:fulladd PORT MAP(a(3),b(3),temp_co2,so(3),co);END a;1.编译顶层设计文件把以上各个模块的VHDL设计文件放入同一个文件夹中,以顶层文件建立工程,直接编译顶层文件同时也就编译各个底层模块文件。

基于VHDL4位加法器的设计

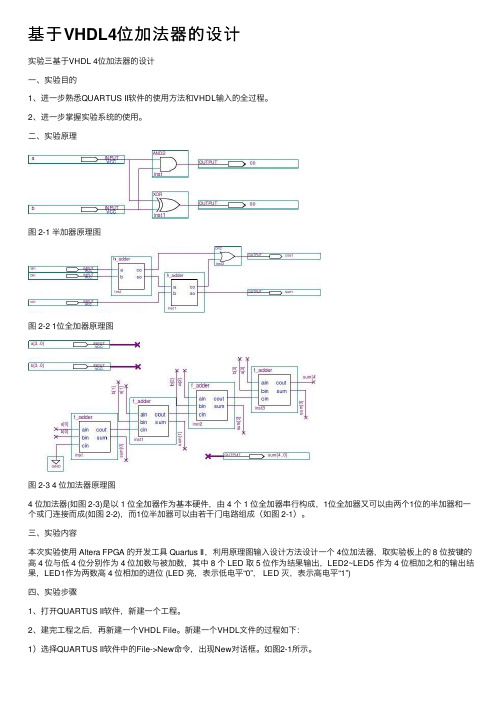

基于VHDL4位加法器的设计实验三基于VHDL 4位加法器的设计⼀、实验⽬的1、进⼀步熟悉QUARTUS II软件的使⽤⽅法和VHDL输⼊的全过程。

2、进⼀步掌握实验系统的使⽤。

⼆、实验原理图 2-1 半加器原理图图 2-2 1位全加器原理图图 2-3 4 位加法器原理图4 位加法器(如图 2-3)是以 1 位全加器作为基本硬件,由 4 个 1 位全加器串⾏构成,1位全加器⼜可以由两个1位的半加器和⼀个或门连接⽽成(如图 2-2),⽽1位半加器可以由若⼲门电路组成(如图 2-1)。

三、实验内容本次实验使⽤ Altera FPGA 的开发⼯具 Quartus Ⅱ,利⽤原理图输⼊设计⽅法设计⼀个 4位加法器,取实验板上的 8 位按键的⾼ 4 位与低 4 位分别作为 4 位加数与被加数,其中 8 个 LED 取 5 位作为结果输出,LED2~LED5 作为 4 位相加之和的输出结果,LED1作为两数⾼ 4 位相加的进位 (LED 亮,表⽰低电平“0”, LED 灭,表⽰⾼电平“1”)四、实验步骤1、打开QUARTUS II软件,新建⼀个⼯程。

2、建完⼯程之后,再新建⼀个VHDL File。

新建⼀个VHDL⽂件的过程如下:1)选择QUARTUS II软件中的File->New命令,出现New对话框。

如图2-1所⽰。

图2-1 新建设计⽂件选择窗⼝2)在New对话框(图2-1)中选择Design Files页下的VHDL File,点击OK按钮,打开VHDL编辑器对话框,如图2-2所⽰。

图2-2 VHDL编辑窗⼝3、按照实验原理和⾃⼰的想法,在VHDL编辑窗⼝编写1位半加器的VHDL程序。

如图2-3所⽰。

图2-3 1位半加器VHDL程序4、编写完半加器VHDL程序后,保存,⽂件名为h_adder.vhd(注意⽂件名要与实体名保持⼀致),再将半加器⽂件设置为顶层⽂件,然后进⾏编译并仿真,对程序的错误进⾏修改。

4位加法计数器的VHDL描述

0

十进制整数

35

十进制整数

10E3

十进制整数

16#D9#

十六进制整数

8#720#

八进制整数

2#11010010# 二进制整数

1.3 4位加法计数器的另一种表达方式

【例5-2】 LIBRARY IEEE ; USE IEEE.STD_LOGIC_1164.ALL ; USE IEEE.STD_LOGIC_UNSIGNED.ALL ; ENTITY CNT4 IS PORT ( CLK : IN STD_LOGIC ; Q : OUT STD_LOGIC_VECTOR(3 DOWNTO 0) ) ; END ; ARCHITECTURE bhv OF CNT4 IS

BEGIN PROCESS (CLK)

BEGIN IF CLK'EVENT AND CLK = '1' THEN Q <= Q + 1 ; END IF;

END PROCESS ; END bhv;

4位加法计数器的VHDL描述

1.2 整数、自然数和正整数数据类型

整数常量的书写方式示例如下:

1

十进制整数

1.3 4位加法计数器的另一种表达方式 4位加法计数器由两大部分组成:

图5-1 4位加法计数器RTL电路

4位加法计数器的VHDL描述

1.3 4位加法计数器的另一种表达方式

图5-2 4位加法计数器工作时序

4位加法计数器的VHDL描述

1.3 4位加法计数器的另一种表达方式

数据类型: 整数类型INTEGER、自然数类型、正整数类型POSITIVE。

EDA技术实用教程

4位加法计数器的VHDL描述

1.1 4位加法计数器

vhdl编程实例

vhdl编程实例VHDL编程实例- 设计与实现一个4位的全加器在本篇文章中,我们将一步一步地回答如何设计和实现一个4位的全加器。

VHDL编程语言将是我们用于描述和模拟这个电路的工具。

第一步:理解全加器的原理在编写代码之前,我们首先需要理解全加器的原理。

全加器是一种用于对两个二进制数字进行相加的电路。

它接收三个输入信号:两个位的输入(A 和B)以及一个进位输入(C_in)。

全加器的输出结果为一个位的和(S)和一个进位输出(C_out)。

我们可以使用如下的真值表来描述全加器的输出结果:输入信号输出结果A B C_in S C_out0 0 0 0 00 0 1 1 00 1 0 1 00 1 1 0 11 0 0 1 01 0 1 0 11 1 0 0 11 1 1 1 1了解了全加器的工作原理后,我们可以开始编写代码了。

第二步:编写全加器的VHDL代码我们将使用VHDL语言来描述和模拟全加器。

下面是一个简单的4位全加器的VHDL代码实现:vhdlEntity声明entity full_adder isport (A, B : in std_logic_vector(3 downto 0);C_in : in std_logic;S : out std_logic_vector(3 downto 0);C_out : out std_logic);end full_adder;Architecture声明architecture Behavioral of full_adder isbeginprocess(A, B, C_in)variable carry : std_logic;begincarry := C_in;for i in 0 to 3 loopS(i) <= A(i) xor B(i) xor carry;carry := (A(i) and B(i)) or (carry and (A(i) xor B(i)));end loop;C_out <= carry;end process;end Behavioral;在此代码中,我们首先声明了一个实体(entity)和一个架构(architecture)。

层次化4位加法器设计 VHDL

课程设计说明书学院专业题目学号姓名同组人员报告完成日期成绩指导教师实验一层次化4位加法器设计一.实验目的1、掌握用 VHDL 设计全加器的方法并实现。

2、熟悉设计平台及VHDL层次化设计。

二.实验仪器1、硬件:计算机Gxsoc/sops-Dev-LabCycloneII EP2C35F672C8 核心板2、软件:正版Quartus8.0三.实验设计要求学习用VHDL或原理图设计方法,掌握全加器的设计方式及表示方式,极其与二进制表示的转换方法,完成编译、综合、适配、仿真和实验箱上的硬件测试,通过数码管观察结果。

采用层次化方法实现4位加法器,完成编译,仿真,引脚锁定,下载。

四.实验原理通过动态扫描两组4BIT的二进制数据,同时还有一个单BIT 的进位,把三者按照二进制加法原理进行加,求出和及进位,并通过电路显示出各部分数据(输入,输出)。

加数、被加数、“和”显示在共阳数码管上,进位输出显示在LED上。

五.程序代码1、半加器Hadder代码LIBRARY Ieee;USE Ieee.Std_Logic_1164.all;ENTITY HADDER ISPort (a,b: In Bit;Co, So: Out Bit);END HADDER;ARCHITECTURE fh1 Of HADDER Is BEGINSo <= (a Xor b);Co <= (a And b);END fh1;2、或门ora代码LIBRARY Ieee;USE Ieee.Std_Logic_1164.all;ENTITY ora ISPort ( a: in Std_Logic;b: in Std_Logic;c: out Std_Logic);END ora;ARCHITECTURE org OF ora ISBEGINc <= a Or b;END org;3、1位全加器f_hadder代码LIBRARY Ieee;USE Ieee.Std_Logic_1164.all;ENTITY f_ADDER ISPort (x: In Std_Logic;y: In Std_Logic;cin: In Std_Logic;cout: Out Std_Logic;sum: Out Std_Logic);END f_ADDER;ARCHITECTURE fd1 Of f_ADDER Is Component HADDERPort( a,b: In Std_Logic;co,so: Out Std_Logic);END Component;Component oraPort(a,b: In Std_Logic;c: Out Std_Logic);END Component;Signal d,e,f: Std_Logic;BeginU1: HADDERPort Map(a=>X,b=>Y,Co=>d,so=>e);U2:HADDERPort Map(a=>e,b=>cin,Co=>f,so=>sum);U3:ora Port Map(a=>d,b=>f,c=>cout);END ARCHITECTURE fd1;4、4位全加器Qadd:Library ieee;Use ieee.std_logic_1164.all;Entity Qadd isPort (a:in std_logic_VECTOR(3 DOWNTO 0);b:in std_logic_VECTOR(3 DOWNTO 0);--cin:in std_logic;s:out std_logic_VECTOR(3 DOWNTO 0)); End Qadd;Architecture one of Qadd isSignal c0,c1,c2,c3 : std_logic;Component f_ADDERPort (x: In Std_Logic;y: In Std_Logic;cin: In Std_Logic;cout: Out Std_Logic;sum: Out Std_Logic);END Component;Beginu1 :F_ADDERPort map(sum=>s(0),cout=>c0,X=>a(0),Y=>b(0),cin=>'0');u2 :F_ADDERPort map(sum=>s(1),cout=>c1,X=>a(1),Y=>b(1),cin=>c0 );u3 : F_ADDERPort map(sum=>s(2),cout=>c2,X=>a(2),Y=>b(2),cin=>c1 );u4 : F_ADDERPort map(sum=>s(3),cout=>c3,X=>a(3),Y=>b(3),cin=>c2 ); END;六.仿真结果程序代码进行编译后,建立waveform文件,设定输入输出端口进行仿真,仿真结果如图1-1所示。

四位全加器实验报告格式

实验二 使用VHDL 语言设计语言设计四位全加器四位全加器 实验报告专业班级专业班级:: 学号学号:: 姓名姓名::一、实验目的1. 了解四位全加器的工作原理。

2. 掌握基本组合逻辑电路的设计方法。

3. 熟悉应用Quartus II 进行FPGA 开发过程和开发方法。

4. 掌握VHDL 语言程序的基本结构,初步熟悉VHDL 语言设计方法。

二、实验原理全加器是由两个加数A i 和B i 以及低位来的进位C i 作为输入,产生本位和Si 以及向高位的进位C O 的逻辑电路。

它不但要完成本位二进制码A i 和B i 相加,而且还要考虑到低一位进位C i 的逻辑。

对于输入为A i 、B i 和C i ,输出为S i 和C O 的情况,根据二进制加法法则可以得到全加器的真值表:A iB iC i S i C O 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1 1 111由真值表得到Si 和Ci 的逻辑表达式为:S i =A i ⊕B i ⊕C iC O =(A i ⊕B i )C i +A i B i这是一位的二进制全加器,要完成一个四位的二进制全加器,只需要把四个级联起来即可。

四位全加器可以看作是4个1位全加器串行构成。

三、实验内容实验内容1.根据逻辑表达式设计一个四位二进制全加器,考虑最低位的进位输入信号。

2.写出四位全加器的VHDL 语言源代码,并下载验证。

四、预习要求1.了解VHDL 语言程序的基本结构一个VHDL 语言程序必须包含 和 两个部分,除这两个部分外,多数程序还包含 和 。

• 实体:定义电路实体的外观,电路的外部输入和输出端口,即模块的外部特征。

实体使用关键字 来定义,用 关键字来定义输入输出端口, 以 关键字结束。

• 结构体:用来描述电路的内部结构和逻辑功能。

结构体是有一个或多个并行语句构结构体是有一个或多个并行语句构成的成的,,他们的书写顺序并不代表执行顺序,这一点与其他高级语言有所不同。

VHDL硬件描述语言四位加法器实验报告

题目:硬件描述语言实验四:四位加法器姓名:***** 学号: ******地点:主楼402 时间: 3月21日一、实验目的:进一步练习VHDL语言设计工程的建立与仿真的步骤和方法、熟悉VHDL语言基本设计实体的编写方法。

二、实验环境:PC个人计算机、Windows XP操作系统、Quartus II集成开发环境软件。

三、设计要求:采用三种方式设计一个四位加法器,实体名称分别为“adder4”、“adder4_2”、和“adder_3”,四位加法器的引脚与功能如下表。

端口模式端口名数据类型说明in (输入)astd_logic_vector(3 downto 0)加数b 加数ci std_logic 低位进位out (输出)s std_logic_vector(3 downto 0) 和co std_logic 高位进位四、实验步骤:1、采用寄存器传输的描述方式:首先新建一个工程,命名为“adder4”,然后编辑代码。

注意在模块内部(构造体说明部分)需要定义三个连接线,定义语句为:signal c0,c1,c2 : std_logic代码如下:library ieee;use ieee.std_logic_1164.all;entity adder4 isport(a,b : in std_logic_vector (3 downto 0);ci : in std_logic;s : out std_logic_vector (3 downto 0);co : out std_logic);end entity;architecture rtl of adder4 issignal c0,c1,c2 : std_logic;begins(0) <= a(0) xor b(0) xor ci;c0<= (a(0) and b(0)) or (a(0) and ci) or (b(0) and ci);s(1)<= a(1) xor b(1) xor c0;c1<= (a(1) and b(1)) or (a(1) and c0) or (b(1) and c0);s(2)<= a(2) xor b(2) xor c1;c2<= (a(2) and b(2)) or (a(2) and c1) or (b(2) and c1);s(3)<= a(3) xor b(3) xor c2;co<= (a(3) and b(3)) or (a(3) and c2) or (b(3) and c2); end rtl;仿真波形图如下:仿真电路图如下:s~1c0~0c0~1c0~3c0s~3c1~0c1~1c1~3c1s~5c2~0c2~1c2~3c2s~7co~0co~1co~3co~4cicoa[3..0]b[3..0]s[3..0]由上图可知设计是正确的。

太原理工大学 EDA实验 VHDL方式设计4位加法计数器

本科实验报告课程名称:CPLD/FPGA应用设计实验名称: VHDL方式设计4位加法计数器实验二VHDL方式设计4位加法计数器一、实验目的1、学习时序电路的VHDL描述方法。

2、掌握时序进程中同步、异步控制信号的设计。

3、熟悉EDA的仿真分析和硬件测试技术。

二、实验原理设计一个含计数使能、异步复位和并行预置功能的4位加法计数器,RST是异步复位信号,高电平有效;CLK是时钟信号;当使能信号ENA为“1”时,加法计数,COUT为计数进位输出,OUTY为计数输出。

三、实验仪器Windows xp操作系统;ispDesignEXPERT System软件;1016E开发板。

四、实验任务1、编写4位二进制加法计数器的VHDL程序。

2、在ispDesignEXPERT System上对编码器进行仿真。

3、将输入引脚连接到拨码开关,时钟输入锁定到相应频率的时钟信号,输出连接到发光二极管,下载后在实验板上验证其功能,记录实验结果。

五、实验步骤1、VHDL文本编辑在MUX+PLUS集成环境下,执行“file”中的“new”命令,弹出编辑文本类型的对话框,选择“text edior file”后单击“OK”。

先采用VHDL文本输入设计法实现4位二进制加法计数器的数字逻辑电路,并将文件cnt4.vhd保存到创建的目录下。

library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt4 isport(clk : in std_logic;rst : in std_logic;ena : in std_logic;outy :out std_logic_vector(3 downto 0);cout :out std_logic);end cnt4;architecture behav of cnt4 issignal cqi : std_logic_vector(3 downto 0);beginp_reg : process(clk,rst,ena)beginif rst ='1'then cqi <="0000";elsif clk'event and clk ='1'thenif ena='1' thencqi<=cqi+1;end if;end if;outy <= cqi;end process p_reg;cout <=cqi(0) and cqi(1) and cqi(2) and cqi(3);end behav;2、编译文件对cnt4.vhd设计文件进行编译,进而实现四位同步二进制加法计数器的数字逻辑电路3、功能时序仿真4位加法计数器功能仿真图4位加法计数器时序仿真图4、引脚锁定5、器件适配在ispDesignEXPERT System Project Navigator主窗口中选中左侧的ispLSI1016E器件,双击右侧的Compile Design选项,进行器件适配。

FPGA四位加法器实验报告

题目:含异步清0和同步使能的4位加法计数器一. 实验目的.学习时序电路的设计、仿真和硬件测试,进一步熟悉VHDL技术。

二.实验原理.如图是一含计数使能、异步复位和计数值并行预置功能4位加法计数器,4位锁存器;rst是异步清0信号,高电平有效;clk是锁存信号;D[3..0]是4位数据输入端。

ENA是使能信号,当ENA为'1'时,多路选择器将加1器的输出值加载于锁存器的数据端;当ENA为'0'时将"0000"加载于锁存器。

三.实验内容.设计一个含异步清0和同步使能的4位加法计数器;实现对输入时钟(clk)的计数。

任务分析:在RST=1,ENA=1时,系统对输入时钟进行计数,所计数值输出至OUTY(3 DOWNTO 0),当计数满15时,产生一个进位,输出至COUT,同时OUTY溢出归零;如果RST=1,ENA=0时,保持原来的计数值不变。

如果RST=0,置输出信号为0;1)异步复位,则输入信号有复位信号RST2)同步使能, 则输入信号有使能信号ENA3)要求同步的时序,则输入信号有时钟CLK在QuartusII上对下列程序进行编辑、编译、综合、适配、仿真。

module CNT4B(CLK,RST,ENA,CLK_1,RST_1,ENA_1,OUTY,COUT);input CLK,RST,ENA;output CLK_1,RST_1,ENA_1;output[3:0] OUTY;output COUT;reg[3:0] OUTY;reg COUT;wire CLK_1; wire RST_1; wire ENA_1;assign CLK_1 = CLK; assign RST_1 = RST; assign ENA_1 = ENA;always@(posedge CLK or negedge RST)begin if(!RST)begin OUTY<=4'b0000;COUT<=1'b0; endelse if(ENA)Begin OUTY<=OUTY+1;COUT<=OUTY[0] & OUTY[1] & OUTY[2] & OUTY[3]; end end endmodule四.实验步骤.1.在QUARTUSII软件下创建一工程,工程名为CNT4B,芯片名为EP2C35F672C6;2.新建Verilog语言文件,输入以上Verilog语言源程序,并将程序命名为CNT4B.vhd,保存在与工程相同的文件夹中;3.进行功能仿真、全编译、时序仿真,如出现错误请按照错误提示进行修改,保证设计的正确性。

利用原理图输入法实现4位串行进位加法器

VHDL(一)模拟部分电子线路仿真实验报告实验名称:软件和实验箱介绍姓名:申红霞学号: 080404108班级: 08通信一班时间: 10.02南京理工大学紫金学院电光系一、实验目的1.讲解QuartusⅡ软件和实验箱的使用。

2.利用原理图输入法实现4位串行进位加法器。

3.重点掌握软件使用过程中工程建立、原理图输入方法、编译、仿真、管脚配置等。

二、实验原理1.加法器原理全加器真值表如图1所示:加法器真值表全加器表达式为:Si=Ai⊕Bi⊕Ci-1Ci=(Ai⊕Bi)Ci-1+AiBi全加器逻辑符号如图2所示:全加器逻辑符号2.利用全加器可以构成4位串行进位加法器,逻辑符号如图3所示:4位串行进位加法器逻辑符号图三、实验内容1.新建文件夹,在所新建的文件夹中利用QuartusⅡ软件建立新工程,设计原理图输入的一位全加器电路,如图4所示:图4、一位全加器电路2.对该图进行全编译,编译成功后,建立矢量波形文件,验证所设计的一位全加器电路的正确性,时序仿真结果和功能仿真结果如下图所示:图5、时序仿真结果图6、功能仿真结果由仿真波形分析可知,该全加器设计正确。

3.将设计好的全加器生成一个模块,如图7所示:图7、一位全加器器件4.将4个全加器串联,再添加相应的管脚和原件构成四位串行进位加法器,如图8所示:图8、四位串行进位加法器电路图5.将此文件设置为顶层文件,对该图进行全编译,编译成功后,建立矢量波形文件,添加相应的节点,为输入信号赋初值,功能仿真结果和时序仿真结果如下图:图9、功能仿真结果图10、时序仿真结果由仿真波形可知,电路设计正确。

6.利用模式实验箱来验证设计电路的正确性,设置管脚,管脚配置图如图11所示:图11、管脚配置图配置好使用管脚后,器件上未使用管脚也需进行设置,将它们设置为高阻状态。

7.管脚配置完,一定要重新编译一次。

编译后如图12所示:图12、配置管脚后电路图8.下载到实验箱中,对实验箱进行操作,验证电路是否正确。

vhdl 4位累加器

ACC4, 8, 164-, 8-, 16-Bit Loadable Cascadable Accumulators with Carry-In, Carry-Out, and Synchronous ResetArchitectures SupportedACC4, ACC8, ACC16 can add or subtract a 4-, 8-, 16-bit unsigned-binary, respectively or twos-complement word to or from the contents of a 4-, 8-, 16-bit data register and store the results in the register. The register can be loaded with the 4-, 8-, 16-bit word. The synchronous reset (R) has priority over all other inputs, and when High, causes all outputs to go to logic level zero during the Low-to-High clock (C) transition. Clock (C) transitions are ignored when clock enable (CE) is Low.The accumulator is asynchronously cleared, outputs Low, when power is applied. For XC9500/XV/XL, CoolRunner XPLA3, and CoolRunner-II, the power-oncondition can be simulated by applying a High-level pulse on the PRLD global net.Spartan-II, Spartan-IIE, Spartan-3, Virtex, Virtex-E, Virtex-II, Virtex-II Pro and Virtex-II Pro X simulate power-on when global set/reset (GSR) is active.GSR defaults to active-High but can be inverted by adding an inverter in front of the GSR input of the STARTUP_SPARTAN2, STARTUP_SPARTAN3, STARTUP_VIRTEX, or STARTUP_VIRTEX2 symbol.LoadWhen the load input (L) is High, CE is ignored and the data on the D inputs is loaded into the register during the Low-to-High clock (C) transition. ACC4 loads the data on inputs D3 – D0 into the 4-bit register. ACC8 loads the data on D7 – D0 into the 8-bit register. ACC16 loads the data on inputs D15 – D0 into the 16-bit register.Unsigned Binary Versus Twos ComplementACC4, ACC8, ACC16 can operate, respectively, on either 4-, 8-, 16-bit unsigned binary numbers or 4-, 8-, 16-bit twos-complement numbers. If the inputs are interpreted as unsigned binary, the result can be interpreted as unsigned binary. If the inputs are interpreted as twos complement, the output can be interpreted as twos complement. The only functional difference between an unsigned binary operation and a twos-complement operation is how they determine when “overflow” occurs. UnsignedACC4, ACC8, ACC16Spartan-II, Spartan-IIE Macro Spartan-3Macro Virtex, Virtex-EMacro Virtex-II, Virtex-II Pro, Virtex-II Pro X MacroXC9500, XC9500XV , XC9500XL Primitive CoolRunner XPLA3Primitive CoolRunner-IIPrimitivebinary uses CO, while twos complement uses OFL to determine when “overflow”occurs.Unsigned Binary OperationFor unsigned binary operation, ACC4 can represent numbers between 0 and 15,inclusive; ACC8 between 0 and 255, inclusive; and ACC16 between 0 and 65535,inclusive. In add mode, CO is active (High) when the sum exceeds the bounds of theadder/subtracter. In subtract mode, CO is an active-Low borrow-out and goes Lowwhen the difference exceeds the bounds. The carry-out (CO) is not registeredsynchronously with the data outputs. CO always reflects the accumulation of the Binputs (B3 – B0 for ACC4, B7 – B0 for ACC8, B15 – B0 for ACC16) and the contents ofthe register. This allows cascading of ACC4s, ACC8s, or ACC16s by connecting CO ofone stage to CI of the next stage. An unsigned binary “overflow” that is always active-High can be generated by gating the ADD signal and CO as follows.unsigned overflow = CO XOR ADDIgnore OFL in unsigned binary operation.T wos-Complement OperationFor twos-complement operation, ACC4 can represent numbers between -8 and +7,inclusive; ACC8 between -128 and +127, inclusive; ACC16 between -32768 and+32767, inclusive. If an addition or subtraction operation result exceeds this range, theOFL output goes High. The overflow (OFL) is not registered synchronously with thedata outputs. OFL always reflects the accumulation of the B inputs (B3 – B0 for ACC4,B7 – B0 for ACC8, B15 – B0 for ACC16) and the contents of the register, which allowscascading of ACC4s, ACC8s, or ACC16s by connecting OFL of one stage to CI of thenext stage.Ignore CO in twos-complement operation. Libraries GuideACC8 Implementation Spartan-II, Spartan-IIE, Virtex, Virtex-EACC8 Implementation Spartan-3, Virtex-II, Virtex-II Pro, Virtex-II Pro X Libraries GuideACC4 Implementation XC9500/XV/XL, CoolRunner XPLA3, and CoolRunner-IIACC8 Implementation XC9500/XV/XL, CoolRunner XPLA3, and CoolRunner-IIUsageACC is schematic and inference only -- not instantiated.VHDL Inference Code (ACC4)Following is some "basic" code for inference of the ACC modules.architecture Behavioral of acc4 isbeginprocess(C)beginif (R = '1') thenQ <= (others => '0');elsif (C'event and C = '1') thenif (L = '1') thenQ <= D;elsif (CE = '1') thenif (ADD = '1') thenQ <= Q + B;elseQ <= Q - B;end if;end if;end if; Libraries Guideend process;end Behavioral; Verilog Inference Code always @ (posedge C)beginif (R)Q <= 0;else if (L)Q <= D;else if (CE)endif (ADD)Q <= Q + B;elseQ <= Q - B;end Libraries Guide。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

《FPGA原理及应用》

实验报告书

(4)

用例化语句设计4位全加器题目

学院专业

姓名学号

指导教师

2015年 10-12月

1.实验目的

(1)进一步熟悉和掌握Qartus II的使用方法;

(2)进一步掌握FPGA实验箱使用方法;

(3)学习和掌握电路原理图的设计流程;

(4)深化理解顶层设计的概念和构建电路的方法

2.实验内容

使用Qartus II的元件库,通过元件图的方式设计具有4位全加器功能的程序,并使用FPGA实验箱对程序进行硬件下载,验证。

3.实验条件

开发软件:Qartus II 8.0

实验设备:FPGA实验箱

拟用芯片:Altera EP3C55F484C8

4.实验设计

1)系统原理

多位加法器的构成有两种方式:并行进位和串行进位方式。

并行进位加法器设有并行进位产生逻辑,运算速度快;串行进位方式是将全加器级联构成多位加法器。

通常,并行加法器比串行级联加法器占用更多的资源,并且随着位数的增加,相同位数的并行加法器比串行加法器的资源占用差距也会越来越大。

四位全加器可对两个多位二进制数进行加法运算,同时产生进位。

当两个二进制数相加时,较高位相加时必须加入较低位的进位项(Ci),以得到输出为和(S)和进位(C0)。

其中CIN表示输入进位位,COUT表示输出进位位,输入A和B分别表示加数和被加数。

输出SUM=A+B+CIN,当SUM大于255时,COUT置‘1’。

图4-1 4位全加器原理图

2)程序代码

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY adder1 IS --1位全加器设计

PORT(a,b,cin:IN STD_LOGIC;

s,cout:OUT STD_LOGIC);

END adder1;

ARCHITECTURE dataflow OF adder1 IS --用数据流方式设计1位全加器SIGNAL tmp:STD_LOGIC; --用tmp表示a⊕b

BEGIN

tmp<=a XOR b AFTER 10 ns;

s<=tmp XOR cin AFTER 10 ns;

cout<=(a AND b)OR(tmp AND cin) AFTER 20 ns;

END dataflow;

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY adder4 IS --4位全加器设计

PORT(a,b:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

cin:IN STD_LOGIC;

s:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

cout:OUT STD_LOGIC);

END adder4;

ARCHITECTURE structural OF adder4 IS --用结构化描述风格设计4位全加器COMPONENT adder1

PORT(a,b,cin:IN STD_LOGIC;

s,cout:OUT STD_LOGIC);

END COMPONENT;

SIGNAL x,y,z:STD_LOGIC;

FOR u1,u2,u3,u4:adder1 USE ENTITY WORK.adder1(dataflow);

BEGIN

u1:adder1 PORT MAP(a(0),b(0),cin,s(0),x);

u2:adder1 PORT MAP(a(1),b(1),x,s(1),y);

u3:adder1 PORT MAP(a(2),b(2),y,s(2),z);

u4:adder1 PORT MAP(a(3),b(3),z,s(3),cout);

END structural;

3)电路波形图

工程编译完成后,必须对其功能和时序性质进行仿真测试。

下图就是实现仿真后的波形,满足原设计要求。

如图3-4所示。

图4-2 4位全加器仿真后的波形

4)引脚锁定和硬件测试

为了能够对全加器进行硬件验证,应将其输入信号锁定在芯片确定的引脚上,编译下载。

其锁定输入信号、输出信号。

图3-5 全加器器引脚锁定

5)编译文件下载

编译文件下载结果如图3-6所示。

图3-6 全加器编译文件下载

5. 实验结果

使用实验箱L8~L1八个开关做输入信号的高低电平,通过FPGA实验箱上的LED显示模块的1个二极管的明灭来测试进位信号,LED数码管显示个位加法最终值。

实验箱演示示意图如图3-7所示。

图3-7 实验箱进行试验

6.心得体会

通过这次实验,让我学习到了如何在Qartus II中使用原理图的方式做出所需要的功能器件,以及顶层设计的方法与优点。

也学会了如何使用FPGA实验箱。