系统结构实验与硬件设计 实验报告

系统设计方法实验报告

实验名称:系统设计方法实验实验日期:2023年4月10日实验地点:XX大学计算机实验室实验目的:1. 理解系统设计的基本原理和方法。

2. 掌握系统需求分析、系统设计、系统实施和系统评估等步骤。

3. 培养团队协作能力和系统设计实践能力。

实验内容:一、实验背景随着信息技术的快速发展,系统设计在各个领域都发挥着越来越重要的作用。

为了提高系统设计的质量和效率,本实验采用系统设计方法,对XX项目进行设计。

二、实验步骤1. 系统需求分析(1)明确项目目标:XX项目旨在提高公司内部信息共享和协作效率。

(2)收集需求信息:通过与项目相关人员沟通,了解用户需求、功能需求、性能需求、安全性需求等。

(3)整理需求文档:将收集到的需求信息整理成需求规格说明书。

2. 系统设计(1)系统架构设计:根据需求规格说明书,确定系统架构,包括硬件架构、软件架构、网络架构等。

(2)模块设计:将系统划分为若干模块,明确每个模块的功能和接口。

(3)数据库设计:根据系统需求,设计数据库结构,包括数据表、字段、关系等。

(4)界面设计:设计用户界面,包括界面布局、颜色搭配、字体大小等。

3. 系统实施(1)硬件采购与安装:根据系统架构设计,采购服务器、存储设备、网络设备等硬件,并进行安装。

(2)软件开发:根据系统设计,开发软件模块,包括前端界面、后端业务逻辑、数据库等。

(3)系统集成:将各个模块进行集成,确保系统正常运行。

4. 系统评估(1)功能测试:测试系统功能是否满足需求规格说明书中的要求。

(2)性能测试:测试系统性能,包括响应时间、并发用户数等。

(3)安全性测试:测试系统安全性,包括用户权限、数据加密等。

三、实验结果与分析1. 系统功能实现经过系统实施,XX项目已成功上线,实现了信息共享和协作功能,满足了用户需求。

2. 系统性能表现经过性能测试,系统响应时间在1秒以内,可支持1000个并发用户同时访问。

3. 系统安全性经过安全性测试,系统符合相关安全规范,能够有效保障用户数据安全。

智能硬件设计实验报告

智能硬件设计实验报告一、引言智能硬件是近年来兴起的一种新型产品,它结合了传统硬件与智能技术的优势,能够提供更加智能化、便捷化的服务。

本次实验旨在设计并制作一款智能硬件产品,通过实践操作了解智能硬件的设计过程和原理。

二、实验目的1. 了解智能硬件的概念和发展历程。

2. 掌握智能硬件设计的基本原理与方法。

3. 进行智能硬件产品的设计、制作与测试。

4. 分析实验结果,总结经验教训。

三、实验内容1. 硬件选择:选择合适的单片机芯片、传感器和其他元件。

2. 硬件设计:进行硬件电路的设计和连线。

3. 程序编写:编写单片机程序,实现智能功能。

4. 调试测试:对硬件和软件进行调试测试,确保产品正常运行。

四、实验步骤1. 硬件选择:根据设计需求选择适合的单片机芯片和传感器。

2. 硬件设计:根据电路原理图,进行硬件的连线和焊接。

3. 程序编写:使用合适的开发工具编写单片机程序。

4. 调试测试:将程序下载到单片机中,对硬件进行测试和调试。

五、实验结果经过一段时间的设计和调试,我们成功制作出一款智能硬件产品。

该产品集成了多种传感器和功能模块,能够实现智能控制和反馈功能。

经过实验测试,产品运行稳定,各项功能正常。

六、实验总结通过本次实验,我们深刻认识到了智能硬件设计的复杂性和挑战性。

在设计过程中,我们充分发挥团队协作的优势,克服了许多困难,取得了成功。

同时,我们也发现了一些不足之处,可以为今后的设计工作提供借鉴和改进方向。

七、展望与建议在未来的学习和实践中,我们将进一步深化对智能硬件设计原理的理解,提升设计能力和创新水平。

同时,也希望不断开拓创新,为智能硬件领域的发展做出更大的贡献。

结语:本次实验让我们深刻体会到了智能硬件设计的魅力和未来发展的潜力,希望通过不断努力和学习,为智能硬件行业的发展贡献自己的力量。

愿智能硬件设计之路越走越宽广,谱写属于自己的辉煌篇章。

计算机系统结构实验报告

计算机系统结构实验报告实验目的:掌握计算机系统的基本结构和工作原理,了解计算机系统的组成部分及其相互关系。

实验仪器和材料:计算机硬件设备(主机、硬盘、内存、显卡等)、操作系统、实验指导书、实验报告模板。

实验原理:实验步骤:1.搭建计算机硬件设备,将主机、硬盘、内存、显卡等组装连接好。

2. 安装操作系统,如Windows、Linux等。

3.启动计算机,进入操作系统界面。

4.打开任务管理器,查看CPU的使用情况。

5.打开任务管理器,查看内存的使用情况。

6.运行一些应用程序,观察CPU和内存的使用情况。

7.尝试使用输入输出设备,如键盘、鼠标等。

实验结果:通过实验,我们可以观察到计算机系统的硬件部分和软件部分的工作情况。

通过任务管理器,我们可以查看到CPU的使用情况和内存的使用情况。

在运行应用程序时,我们可以观察到CPU和内存的使用情况的变化。

通过使用输入输出设备,我们可以与计算机进行交互操作。

实验分析:从实验结果可以看出,计算机系统的硬件部分和软件部分都是相互关联的。

CPU作为计算机的核心部件,负责执行各种指令,通过数据传输和计算来完成各种操作。

而内存则用于存储数据和程序,通过读写操作来完成对数据的处理。

硬盘则用于长期存储数据。

操作系统则是计算机系统的管理者,通过调度CPU和内存的使用来实现对计算机资源的分配。

结论:计算机系统是由硬件和软件部分组成的,其中硬件部分包括CPU、内存、硬盘等,软件部分包括操作系统、应用程序等。

计算机系统通过CPU 的运算和数据传输来实现各种操作。

通过实验,我们可以观察到计算机系统的工作情况,并深入了解计算机系统的组成和工作原理。

实验总结:通过本次实验,我们对计算机系统的基本结构和工作原理有了更深入的了解。

实验中,我们搭建了计算机硬件设备,安装了操作系统,并通过观察和分析实验结果,进一步认识到计算机系统的组成部分和各部分之间的相互关系。

通过操作输入输出设备,我们还实践了与计算机进行交互操作的过程。

计算机硬件实习报告

计算机硬件实习报告一、实习单位概况我所实习的单位是一家知名的计算机硬件公司,总部位于中国的主要城市之一。

该公司是一家专注于计算机硬件设计和制造的企业,拥有先进的研发设施和先进的制造工艺。

公司成立多年来一直致力于为客户提供高品质的计算机硬件产品,并在行业内享有很高的声誉。

二、实习岗位及任务我在实习期间担任的岗位是硬件工程师助理,主要负责协助高级硬件工程师完成各种任务。

我的主要任务包括:1. 参与硬件设计和开发项目,负责制定设计方案和进行相关的实验和测试。

2. 协助高级硬件工程师进行硬件性能测试和故障排除,并提供解决方案。

3. 参与硬件产品的生产和测试,确保产品的质量符合标准。

4. 跟踪和记录硬件设计和开发过程中的问题和进展,并向高级硬件工程师汇报。

三、实习过程及收获在实习期间,我通过参与实际的硬件设计和开发项目,深入了解了计算机硬件的工作原理和设计方法。

我学会了使用各种硬件设计和测试工具,并在实践中不断提升自己的技能。

在参与硬件设计和开发项目时,我学会了如何制定设计方案并进行实验和测试。

我通过自己的实践,掌握了硬件设计的常用原理和方法,如布线、电路设计和封装等。

我还学会了如何分析硬件设计中的问题,并提出解决方案。

在协助高级硬件工程师进行硬件性能测试和故障排除时,我学会了如何使用各种硬件测试工具和设备,并进行数据分析和处理。

通过这一过程,我对硬件的性能和故障排除方法有了更深入的了解。

在参与硬件产品的生产和测试时,我学会了如何进行产品的组装和测试,并确保产品的质量符合标准。

我通过实践中的不断调试和改进,提高了自己的组装和测试技巧。

在跟踪和记录硬件设计和开发过程中的问题和进展的过程中,我锻炼了自己的沟通和汇报能力。

我学会了如何向高级硬件工程师汇报问题和进展,并获得他们的指导和建议。

通过这次实习,我不仅加深了对计算机硬件的了解,还提高了自己的硬件设计和开发能力。

我学会了如何分析和解决硬件设计和开发中的问题,并在实践中不断提升自己的技能。

计算机导论-实验1-硬件组装实验报告

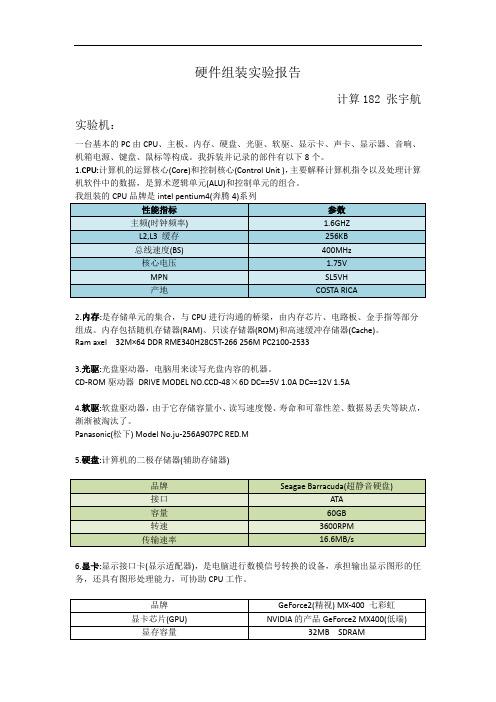

硬件组装实验报告计算182 张宇航实验机:一台基本的PC由CPU、主板、内存、硬盘、光驱、软驱、显示卡、声卡、显示器、音响、机箱电源、键盘、鼠标等构成。

我拆装并记录的部件有以下8个。

1.CPU:计算机的运算核心(Core)和控制核心(Control Unit ),主要解释计算机指令以及处理计算机软件中的数据,是算术逻辑单元(ALU)和控制单元的组合。

我组装的CPU品牌是intel pentium4(奔腾4)系列2.内存:是存储单元的集合,与CPU进行沟通的桥梁,由内存芯片、电路板、金手指等部分组成。

内存包括随机存储器(RAM)、只读存储器(ROM)和高速缓冲存储器(Cache)。

Ram axel 32M×64 DDR RME340H28C5T-266 256M PC2100-25333.光驱:光盘驱动器,电脑用来读写光盘内容的机器。

CD-ROM驱动器DRIVE MODEL D-48×6D DC==5V 1.0A DC==12V 1.5A4.软驱:软盘驱动器,由于它存储容量小、读写速度慢、寿命和可靠性差、数据易丢失等缺点,渐渐被淘汰了。

Panasonic(松下) Model No.ju-256A907PC RED.M5.硬盘:计箅机的二极存储器(辅助存储器)6.显卡:显示接口卡(显示适配器),是电脑进行数模信号转换的设备,承担输出显示图形的任务,还具有图形处理能力,可协助CPU工作。

7.北桥:用来处理高速信号,通常处理CPU、RAM、AGP端口或PCI Express和南桥芯片之间的通信。

它是主板上的一块芯片,位于CPU插座边,起连接作用。

由于数据处理量较大,一般有覆盖散热片。

8.南桥:负责I/O总线之间的通信,一般位于主板上离CPU插槽较远的下方,PCI插槽的附近,因为它所连接的I/O总线较多,离处理器远一点有利于布线。

观察机:我的电脑:1.型号:华硕VivoBook 15 ASUS Laptop X570UD 笔记本电脑2.操作系统:Windows 10 64位(DirectX 12)3.CPU:英特尔Core i5-8250U 1.60GHZ 四核4.主板:华硕X570UD(英特尔Xeon E3 - 1200 v6/7th Gen Intel Core/DRAM Registers – 5914- 7th Generation Intel)5.内存:8GB(三星DDR4 2400MHz)6.主硬盘:SK HYYNIX HFS128G39TND-N210A(128GB/固态硬盘)7.显卡:Nvidia GeForce GTX 1050(4GB)8.显示器:友达AUO61ED(15.5英寸)9.声卡:瑞昱Audio @英特尔High Definition Audio 控制器10.网卡:瑞昱RTL8168/8111/8112 Gigabit Ethernet Controller/华硕计算机硬件的组装[教学安排]:2课时(实验)[教学目标]:知识与技能:1、熟练掌握计算机的组装顺序。

计算机组成原理实验报告_存储系统设计实验

实验四存储系统设计实验一、实验目的本实训项目帮助大家理解计算机中重要部件—存储器,要求同学们掌握存储扩展的基本方法,能设计MIPS 寄存器堆、MIPS RAM 存储器。

能够利用所学习的cache 的基本原理设计直接相联、全相联,组相联映射的硬件cache。

二、实验原理、内容与步骤实验原理、实验内容参考:1、汉字字库存储芯片扩展设计实验1)设计原理该实验本质上是8个16K×32b 的ROM 存储系统。

现在需要把其中一个(1 号)16K×32b 的ROM 芯片用4个4K×32b 的芯片来替代,实际上就是存储器的字扩展问题。

a) 需要4 片4个4K×32b 芯片才可以扩展成16K×32b 的芯片。

b) 目标芯片16K个地址,地址线共14 条,备用芯片12 条地址线,高两位(分线器分开)用作片选,可以接到2-4 译码器的输入端。

c) 低12 位地址直接连4K×32b 的ROM 芯片的地址线。

4个芯片的32 位输出直接连到D1,因为同时只有一个芯片工作,因此不会冲突。

芯片内数据如何分配:a) 16K×32b 的ROM 的内部各自存储16K个地址,每个地址里存放4个字节数据。

地址范围都一样:0x0000~0x3FFF。

b) 4个4K×32b 的ROM,地址范围分别是也都一样:0x000~0xFFF,每个共有4K个地址,现在需要把16K×32b 的ROM 中的数据按照顺序每4个为一组分为三组,分别放到4个4K×32b 的ROM 中去。

HZK16_1 .txt 中的1~4096个数据放到0 号4K 的ROM 中,4097~8192 个数据放到 1 号4K 的ROM 中,8193~12288 个数据放到2 号4K 的ROM 中,12289~16384个数据放到3 号4K 的ROM 中。

c) 注意实际给的16K 数据,倒数第二个4K(8193~12288 个数据)中部分是0,最后4K(12289~16384 数据)全都是0。

实验报告硬件电路设计

实验报告硬件电路设计一、引言本实验旨在通过设计硬件电路来实现特定功能,并验证电路设计的正确性和可行性。

本实验选择了某款电子产品的核心功能进行设计与实现。

二、设计原理本实验设计的硬件电路包括输入接口、中央处理器、输出接口等多个模块,其工作原理如下:1. 输入接口:负责接收用户输入的指令或数据,例如按钮、触摸屏等。

2. 中央处理器:接收输入接口传入的指令或数据,根据预设的算法进行计算、逻辑判断等操作,将计算结果保存到存储器中,并控制输出接口的工作状态。

3. 存储器:用于存放中央处理器计算的结果以及其他需要保存的数据。

4. 输出接口:负责将存储器中的数据进行输出,例如显示屏、声音输出器等。

三、设计步骤1. 根据电子产品的需求和功能,确定硬件电路的整体架构和模块划分。

2. 选择合适的元器件,例如电阻、电容、晶体管等,并进行元器件的布线和连线设计。

3. 按照设计的电路原理图,进行电路板的布局设计,确保各个元器件的位置合理,以及连线的长度、走向等因素。

4. 制作电路板原型,喷锡、焊接元器件,并进行连接测试。

5. 调试并修改电路设计中的问题,确保硬件电路的正确和可靠性。

6. 验证设计的电路是否满足预期功能,检查电路的功耗、稳定性等指标,以及其与其他系统的兼容性。

7. 进行电路板的大规模生产,并进行质检,保证产品的质量和可靠性。

四、实验结果经过多次调试和修改,本实验设计的硬件电路稳定运行,成功实现了特定功能。

根据测试结果显示,电路运行良好,没有出现异常情况。

同时,电路设计满足了产品的要求,功能达到预期。

五、总结与展望本实验通过设计硬件电路,成功实现了特定功能,并验证了电路设计的正确性和可行性。

电路设计经过多次调试和修改,达到了预期效果。

然而,仍有一些改进的空间,如进一步优化电路的功耗、增加系统的稳定性等。

在未来的研究中,可以考虑使用更先进的元器件,提升电路的性能,以及进一步优化电路布局,减小电路的体积。

六、参考文献1. 电路设计与实践,XXX,XXX出版社,XXXX年。

智能硬件设计实验报告

智能硬件设计实验报告1. 引言智能硬件是指通过集成计算能力和通信能力的装置,能够感知周围环境并做出一定反应的硬件设备。

本实验旨在探索智能硬件的设计和制作过程,并验证其在实际应用中的可行性和效果。

本报告将详细介绍实验的背景、目的、设计方法、实验结果和分析,以及对实验过程中遇到的问题和解决方法的探讨。

2. 背景随着人工智能和物联网技术的不断发展,智能硬件逐渐成为日常生活中的重要组成部分。

智能硬件可以应用于各个领域,如智能家居、智能医疗、智能交通等,为人们提供更加便捷、高效、智能化的生活方式。

因此,了解智能硬件的基本设计原理和制作方法具有重要的意义。

3. 目的本实验旨在通过设计和制作一个智能硬件系统,以探索智能硬件的设计过程和开发流程,加深对智能硬件的理解。

同时,通过实验验证所设计的智能硬件系统的可行性和效果,并评估其在实际应用中的性能。

4. 设计方法本实验的智能硬件系统由以下几个部分组成:1. 感知模块:利用传感器获取周围环境的数据,如温度、湿度、光照强度等。

2. 处理模块:通过微控制器对感知模块采集的数据进行处理和分析,并做出相应的反应和决策。

3. 通信模块:实现与外部设备的通信,如通过无线网络与手机或电脑进行数据传输和远程控制。

4. 控制模块:根据处理模块的决策结果,控制执行器的动作,如控制灯光、音乐播放等。

在设计过程中,我们首先进行了需求分析和系统架构的设计,在硬件选型和软件开发环节,我们选择了适合实验目的的感知模块、处理模块、通信模块和控制模块,并进行了模块的集成和测试。

最后,对整个系统进行了功能测试和性能评估。

5. 实验结果和分析经过实验,我们成功设计和制作了一个智能硬件系统,并取得了以下结果:1. 感知模块能够准确地获取周围环境的数据,并将数据传输给处理模块进行处理和分析。

2. 处理模块能够根据感知模块采集的数据做出相应的决策,并控制执行器的动作。

3. 通信模块能够实现与外部设备的通信,如通过无线网络传输数据和接收远程控制指令。

计算机硬件实习报告

计算机硬件实习报告一、引言计算机硬件是现代计算机系统中不可或缺的重要组成部分。

通过参与计算机硬件实习,我对计算机硬件的组成原理、工作原理以及性能优化等方面有了更深入的了解。

本文将对我在计算机硬件实习中的所学所感进行总结和回顾。

二、实习背景与目的在实习过程中,我加入了一家计算机硬件研发公司,并参与了他们的硬件产品开发与测试。

实习的目的是熟悉计算机硬件的工作原理,掌握相关测试方法和技术,并通过实践提升自己的实践能力和团队合作意识。

三、实习内容与收获在实习期间,我主要参与了以下几个方面的工作:1. 硬件原型设计与制作:与团队成员合作,根据产品需求进行硬件原型设计,包括电路设计、PCB制作以及硬件组装调试等。

通过这一过程,我深入了解了硬件设计流程以及各种电子元器件的工作原理。

2. 硬件测试与性能优化:通过使用各种专业的测试仪器和设备,对硬件产品进行功能测试和性能评估。

针对测试结果,我与团队成员一起进行性能优化,提高产品的稳定性和性能。

3. 问题排查与解决:在硬件测试的过程中,经常会遇到一些问题和故障。

我需要通过分析硬件电路和信号调试,找出问题的根源并提出解决方案。

这个过程让我锻炼了自己的问题解决能力和逻辑思维能力。

4. 文档撰写与技术交流:在实习期间,我积极参与团队内部的技术交流会议,并撰写了一些技术文档,记录了硬件的设计思路、测试方法及结果等内容。

这不仅提升了自己的沟通表达能力,还加深了对所学知识的理解。

通过这些实习内容,我对计算机硬件的工作原理与设计流程有了更深入的认识与掌握,并提升了自己的动手能力和问题解决能力。

四、实习心得与体会在实习期间,我深切体会到了计算机硬件实践的重要性。

理论知识只是我们学习的基础,只有通过实际动手操作和实践,才能真正理解计算机硬件的运作原理。

而且,在团队中的合作也是十分重要的,只有良好的协作能力才能完成复杂的硬件开发工作。

实习过程中,我也遇到了一些挑战与问题。

例如,在硬件测试和性能优化过程中,有时候会遇到较为复杂的问题,需要耐心和细心进行排查和解决。

硬件综合设计实验报告

一、实验目的1. 理解和掌握数字电路设计的基本原理和方法。

2. 学会使用FPGA(现场可编程门阵列)进行硬件设计。

3. 提高实际动手能力和问题解决能力。

4. 熟悉硬件描述语言(HDL)VHDL或Verilog的使用。

二、实验环境1. 开发平台:Xilinx Vivado 2022.22. 硬件设备:Xilinx Zynq-7000 SoC 开发板3. 软件工具:VHDL/Verilog 编辑器、仿真工具ModelSim、FPGA 编译器三、实验内容本次实验以设计一个简单的数字信号处理系统为例,包括以下模块:1. 数据输入模块2. 数据处理模块3. 数据输出模块四、实验步骤1. 需求分析根据实验要求,设计一个能够对输入数据进行简单处理的数字信号处理系统。

具体要求如下:- 输入数据为8位二进制数。

- 处理模块为简单的加法运算。

- 输出数据为处理后的结果。

2. 模块设计根据需求分析,将系统分为三个模块:- 数据输入模块:负责读取输入数据。

- 数据处理模块:负责执行加法运算。

- 数据输出模块:负责输出处理后的数据。

3. 代码编写使用VHDL或Verilog语言编写各模块代码。

```verilog// 数据输入模块module data_input(input clk, // 时钟信号input reset, // 复位信号output reg [7:0] data_in // 输入数据);always @(posedge clk or posedge reset) begin if (reset) begindata_in <= 8'b0;end else begin// 读取输入数据,此处省略具体实现endendendmodule// 数据处理模块module data_process(input [7:0] data_in, // 输入数据output reg [7:0] data_out // 输出数据);always @(data_in) begindata_out = data_in + 8'b1; // 简单的加法运算 endendmodule// 数据输出模块module data_output(input clk,input reset,input [7:0] data_out,output reg [7:0] data_display // 显示输出数据);always @(posedge clk or posedge reset) beginif (reset) begindata_display <= 8'b0;end else begindata_display <= data_out;endendendmodule```4. 仿真验证使用ModelSim进行仿真,验证各模块功能。

计算机系统结构实验报告

计算机系统结构实验报告计算机系统结构实验报告引言:计算机系统结构是计算机科学领域中的重要课题,它研究计算机硬件和软件之间的关系,以及如何优化计算机系统的性能和效率。

本实验报告旨在介绍我们小组在计算机系统结构实验中的设计和实现过程,以及所获得的实验结果和经验。

一、实验目的计算机系统结构实验的目的是通过设计和实现一个简单的计算机系统,加深对计算机硬件和软件之间关系的理解,以及掌握计算机系统的组成和工作原理。

具体目标包括:1. 理解计算机系统的层次结构和组成部分。

2. 理解指令集架构和微指令集架构的区别。

3. 设计和实现一个简单的计算机系统,包括处理器、存储器和输入输出设备。

4. 测试和验证计算机系统的功能和性能。

二、实验设计与实现1. 计算机系统结构设计我们设计了一个基于冯·诺依曼体系结构的计算机系统,包括中央处理器(CPU)、存储器和输入输出设备。

CPU由控制单元和算术逻辑单元组成,控制单元负责指令的解码和执行,算术逻辑单元负责数据的运算和逻辑操作。

存储器用于存储指令和数据,我们选择了静态随机存储器(SRAM)作为主存储器。

输入输出设备包括键盘、显示器和磁盘。

2. 指令集架构设计我们选择了经典的冯·诺依曼指令集架构作为基础,定义了一套简单的指令集,包括算术运算、逻辑运算和数据传输等指令。

我们还设计了一套微指令集架构,用于实现指令的执行过程。

微指令集中包含了各种控制信号和操作码,用于控制CPU的工作。

3. 硬件设计与实现我们使用硬件描述语言(HDL)进行硬件设计和实现。

通过使用HDL,我们可以描述和模拟计算机系统的各个组成部分,并进行功能验证和性能分析。

我们使用Verilog HDL进行设计和实现,借助Verilog仿真器进行功能验证。

4. 软件设计与实现除了硬件设计和实现,我们还编写了一些软件程序,用于测试和验证计算机系统的功能和性能。

我们编写了一些简单的程序,包括算术运算、逻辑运算和数据传输等,用于测试CPU的指令执行和数据处理能力。

计算机硬件系统及组装实验报告PPT课件

编辑版pppt

12

• 高速缓冲存储器(Cache)

• Cache也是我们经常遇到的概念,也就是平常看到的一级 缓存(L1 Cache)、二级缓存(L2 Cache)、三级缓存(L3 Cache)这些数据,它位于CPU与内存之间,是一个读写 速度比内存更快的存储器。当CPU向内存中写入或读出数 据时,这个数据也被存储进高速缓冲存储器中。当CPU再 次需要这些数据时,CPU就从高速缓冲存储器读取数据, 而不是访问较慢的内存,当然,如需要的数据在Cache中 没有,CPU会再去读取内存中的数据。

• 随机存储器(RAM)

• 随机存储器(Random Access Memory)表示既可以从中 读取数据,也可以写入数据。当机器电源关闭时,存于其 中的数据就会丢失。我们通常购买或升级的内存条就是用 作电脑的内存,内存条(SIMM)就是将RAM集成块集中 在一起的一小块电路板,它插在计算机中的内存插槽上, 以减少RAM集成块占用的空间。目前市场上常见的内存条

• 升技(ABIT):历来都是把超频作为第一要务,做工用料 方面丝毫不逊色于一线品牌,所以受到诸多DIYER的青睐。 在国外知名媒体的调查中,升技都是位列华硕之后而居于 次席。由于升技只做DIY市场,主板出货量不算大,在国 内名气还差那么一点,所以只能暂居准一线这个位置了。

• 磐正(EPOX):原名磐英,因为在国内被抢注而更名磐 正。与升技的风格类似,超频能力同样有口皆碑,而且附 件更加齐全,价格相对也更为低廉,因此同样拥有众多的 Fans。

• 缓存是硬盘控制器上的一块内存芯片,具有极快的存取速 度,它是硬盘内部存储和外界接口之间的缓冲器。由于硬 盘的内部数据传输速度和外界介面传输速度不同,缓存在 其中起到一个缓冲的作用。缓存的大小与速度是直接关系 到硬盘的传输速度的重要因素,能够大幅度地提高硬盘整 体性能。当硬盘存取零碎数据时需要不断地在硬盘与内存 之间交换数据,有大缓存,则可以将那些零碎数据暂存在 缓存中,减小外系统的负编荷辑版,ppp也t 提高了数据的传输速度。15

计算机硬件及组装实验报告

计算机硬件系统及组装预习实验报告目录一计算机的硬件系统的主要组成部分说明 (1)1.计算机的硬件系统的组成 (1)2.计算机的基本结构 (2)1.2.1 运算器 (2)1.2.2 控制器 (2)1.2.3 存储器 (3)1.2.4 输入设备 (3)1.2.5 输出设备(Output Device) (3)二计算机系统的安装和配置 (4)2.1 组装计算机的主要部件及其说明 (4)2.1.1CPU (4)2.1.2主板 (4)2.1.3内存 (4)2.1.4硬盘 (4)2.1.5光驱 (5)2.1.6 显示卡 (5)2.1.7 声卡 (5)2.1.8 显示器 (5)2.1.9 机箱电源 (5)2.2计算机的组装步骤 (6)2.2.1组装工具 (6)2.2.2注意问题 (6)2.2.3安装步骤 (6)一计算机的硬件系统的主要组成部分说明1.计算机的硬件系统的组成计算机硬件系统分为主机和外部设备两大部分。

通常把内存储器、运算器和控制器合称为计算机主机。

而把运算器、控制器做在一个大规模集成电路块上称为中央处理器,又称CPU。

而主机以外的装置称为外部设备,外部设备包括输入、输出设备,外存储器等。

2.计算机的基本结构计算机硬件系统由运算器、控制器、存储器、输入设备和输出设备等五大部件组成。

图(2)计算机基本结构1.2.1 运算器运算器是一个“信息加工厂”。

数据的运算和处理工作就是在运算器中进行的。

这里的“运算”,不仅是加、减、乘、除等基本算术运算,还包括若干基本逻辑运算。

1.2.2 控制器控制器是整个计算机的指挥中心,它取出程序中的控制信息,经分析后,便按要求发出操作控制信号,使各部分协调一致地工作。

1.2.3 存储器存放程序和数据的地方,并根据命令提供存储器是计算机中给有关部分使用。

1) 存储器的主要技术参数:存储容量、存取速度和位价格(即一个二进制位的价格)。

2)存储器容量:表示计算机存储信息的能力,并以字节(byte)为单位。

计算机体系结构实验报告3篇

计算机体系结构实验报告第一篇:计算机体系结构概述计算机体系结构是计算机学科中的一个重要分支,它研究的是计算机的硬件组成和工作原理,包括计算机的处理器、存储器、输入输出设备、总线等。

计算机体系结构的研究可以帮助我们理解计算机的工作原理,优化计算机的性能,提升计算机的能力。

计算机体系结构可以分为两个方面:指令集体系结构和微体系结构。

其中,指令集体系结构是指计算机的操作系统能够直接识别和执行的指令集合,它们是应用程序的编程接口;而微体系结构是指通过硬件实现指令集合中的指令,在底层支持指令集合的操作。

指令集体系结构和微体系结构是密切相关的,因为指令集体系结构会影响微体系结构的设计和实现。

目前,计算机体系结构主要有三种类型:单处理器体系结构、多处理器体系结构和分布式计算体系结构。

其中,单处理器体系结构是指所有的指令和数据都存放在同一台计算机中,这种体系结构的优点是操作简单、易于管理,但是主频存在瓶颈,无法很好地发掘多核的性能优势;多处理器体系结构是指多个计算机共享同一块物理内存,因此可以方便地实现负载均衡和任务协作,但是存在通信延迟和数据一致性问题;分布式计算体系结构则是指通过互联网将多个计算机连接成一个网络,可以在全球范围内共享计算资源,但是通信成本和数据安全问题需要考虑。

总之,计算机体系结构是计算机学科中的重要分支,它研究计算机的硬件组成和工作原理,帮助我们理解计算机的工作原理,优化计算机性能,提升计算机能力。

第二篇:计算机指令集体系结构计算机指令集体系结构,简称ISA(Instruction Set Architecture),是指计算机能够识别和执行的指令集合。

ISA是计算机指令的编程接口,定义了一组指令和地址模式,以及寄存器和内存的组织方式,它是计算机软件和硬件协同工作的关键接口之一。

ISA可以分为两类:精简指令集体系结构(RISC,Reduced Instruction Set Computer)和复杂指令集体系结构(CISC,Complex Instruction Set Computer)。

计算机组成原理实验报告

计算机组成原理实验报告计算机组成原理实验报告引言:计算机组成原理是计算机科学与技术专业的重要课程之一,通过实验可以更好地理解和掌握计算机的组成原理。

本篇实验报告将介绍我们在计算机组成原理实验中所进行的实验内容和实验结果。

实验一:逻辑门电路设计在这个实验中,我们学习了逻辑门电路的设计和实现。

通过使用门电路,我们可以实现与门、或门、非门等基本逻辑运算。

我们首先学习了逻辑门电路的真值表和逻辑代数的基本运算规则,然后根据实验要求,使用逻辑门电路设计了一个简单的加法器电路,并通过仿真软件进行了验证。

实验结果表明,我们设计的加法器电路能够正确地进行二进制数的加法运算。

实验二:数字逻辑电路实现在这个实验中,我们进一步学习了数字逻辑电路的实现。

通过使用多路选择器、触发器等数字逻辑元件,我们可以实现更复杂的逻辑功能。

我们首先学习了多路选择器的原理和使用方法,然后根据实验要求,设计了一个4位二进制加法器电路,并通过数字逻辑实验板进行了搭建和测试。

实验结果表明,我们设计的4位二进制加法器能够正确地进行二进制数的加法运算。

实验三:存储器设计与实现在这个实验中,我们学习了存储器的设计和实现。

存储器是计算机中用于存储和读取数据的重要组成部分。

我们首先学习了存储器的基本原理和组成结构,然后根据实验要求,设计了一个简单的8位存储器电路,并通过实验板进行了搭建和测试。

实验结果表明,我们设计的8位存储器能够正确地存储和读取数据。

实验四:计算机硬件系统设计与实现在这个实验中,我们学习了计算机硬件系统的设计和实现。

计算机硬件系统是计算机的核心部分,包括中央处理器、存储器、输入输出设备等。

我们首先学习了计算机硬件系统的基本原理和组成结构,然后根据实验要求,设计了一个简单的计算机硬件系统,并通过实验板进行了搭建和测试。

实验结果表明,我们设计的计算机硬件系统能够正确地进行指令的执行和数据的处理。

结论:通过这些实验,我们深入学习了计算机组成原理的相关知识,并通过实践掌握了计算机组成原理的基本原理和实现方法。

计算机系统结构专业实习报告

计算机系统结构专业实习报告一、实习背景与目的随着信息技术的快速发展,计算机系统结构作为一门涵盖了计算机硬件和软件等多个方面的学科,在我国的高等教育体系中占据了重要的地位。

为了更好地将理论知识与实践相结合,提高自身综合素质和实际操作能力,我选择了计算机系统结构专业实习,以便为今后的学术研究和职业生涯打下坚实基础。

本次实习的主要目的是:1. 深入了解计算机系统结构的基本原理和组成部件;2. 熟悉各类计算机硬件设备的工作原理和性能指标;3. 掌握计算机系统组装、维护和调试的基本技能;4. 提高团队协作能力和沟通交流能力。

二、实习内容与过程1. 实习前的准备在实习开始前,我们参加了由指导老师举办的实习动员大会,了解了实习的要求、内容以及注意事项。

同时,我们还自学了相关教材和资料,为实习打下了理论知识基础。

2. 实习过程中的主要任务与收获实习过程中,我们主要完成了以下任务:1. 参观实验室和机房,了解各类计算机硬件设备及其功能;2. 学习计算机系统组装、维护和调试的基本技能;3. 参与实验室科研项目,协助导师进行数据分析和实验验证;4. 撰写实习日记和总结报告,记录实习过程中的所学所得。

具体收获如下:1. 熟悉了计算机系统结构的基本原理和组成部件,如CPU、内存、硬盘、显卡等;2. 掌握了计算机系统组装、维护和调试的基本技能,如安装操作系统、配置网络、排查故障等;3. 了解了实验室科研项目的工作流程,提高了科研素养;4. 增强了团队协作能力和沟通交流能力。

3. 实习中遇到的困难与解决方案在实习过程中,我们遇到了一些困难,如:1. 部分硬件设备的原理和操作较为复杂,一开始难以掌握;2. 实验室科研项目中的某些技术问题需要花费较长时间解决;3. 实习任务较重,时间紧张,难以兼顾学业与实习。

针对上述困难,我们采取了以下解决方案:1. 请教老师和同学,共同探讨,逐步掌握硬件设备的原理和操作;2. 利用课余时间深入学习相关技术,提高解决问题的能力;3. 合理安排时间,加强与团队成员的沟通,提高团队协作效率。

熟悉计算机硬件实验报告

熟悉计算机硬件实验报告

计算机硬件实验报告通常涉及对计算机硬件组件的实际操作和

观察。

这些组件可能包括中央处理器(CPU)、内存、硬盘、显卡、

主板等。

在撰写这样的实验报告时,需要包括以下几个方面的内容:

1. 实验目的,明确实验的目的,例如是测试硬件性能、比较不

同硬件的性能差异或者观察硬件工作原理。

2. 实验环境,描述实验所用的计算机硬件设备及其配置,包括CPU型号、内存容量、硬盘类型等。

3. 实验方法,详细描述实验的步骤和操作过程,包括对硬件的

安装、连接和设置。

4. 实验结果,记录实验过程中观察到的现象和数据,例如不同

硬件配置下的性能表现、温度变化等。

5. 结果分析,对实验结果进行分析,解释观察到的现象,比较

不同硬件配置的优劣势,并提出可能的原因。

6. 实验总结,总结实验的主要内容和结果,讨论实验中遇到的问题和解决方法,提出改进建议,并指出实验的局限性。

在撰写实验报告时,需要准确记录实验过程中的数据和观察结果,尽量使用量化的数据进行分析,同时注意描述实验中遇到的困难和解决方法。

此外,报告应当清晰、简练,图表应当配有清晰的标注和说明。

最后,对于实验中的任何偏差或异常情况,也需要进行充分的解释和讨论。

计算机组成原理课程设计的实验报告

计算机组成原理课程设计的实验报告实验报告:计算机组成原理课程设计摘要:本实验报告旨在介绍计算机组成原理课程设计的实验过程和结果。

该实验旨在深入理解计算机的组成和工作原理,并通过设计和实现一个简单的计算机系统来加深对计算机组成原理的理解。

本实验报告将包括实验的目的、实验环境、实验步骤、实验结果以及实验的分析和讨论。

1. 实验目的:本实验的目的是通过设计和实现一个简单的计算机系统,加深对计算机组成原理的理解。

具体目标包括:- 理解计算机的基本组成和工作原理;- 掌握计算机硬件的设计和实现方法;- 学习使用计算机组成原理相关的软件工具。

2. 实验环境:本实验所需的硬件和软件环境如下:- 硬件环境:一台支持计算机组成原理课程设计的计算机;- 软件环境:计算机组成原理相关的软件工具,如Xilinx ISE、ModelSim等。

3. 实验步骤:本实验的步骤主要包括以下几个部分:3.1 系统需求分析在设计计算机系统之前,首先需要明确系统的需求和功能。

根据实验要求,我们需要设计一个简单的计算机系统,包括指令集、寄存器、运算单元等。

3.2 系统设计根据系统需求分析的结果,进行系统设计。

设计包括指令集的设计、寄存器的设计、运算单元的设计等。

3.3 系统实现在系统设计完成后,需要进行系统的实现。

具体步骤包括使用硬件描述语言(如VHDL)进行电路设计,使用Xilinx ISE进行逻辑综合和布局布线,最终生成bit文件。

3.4 系统测试在系统实现完成后,需要进行系统的测试。

测试包括功能测试和性能测试。

功能测试主要是验证系统是否按照设计要求正常工作;性能测试主要是测试系统的性能指标,如运行速度、吞吐量等。

4. 实验结果:经过实验,我们成功设计和实现了一个简单的计算机系统。

该系统具有以下特点:- 指令集:支持基本的算术运算和逻辑运算;- 寄存器:包括通用寄存器、程序计数器、指令寄存器等;- 运算单元:包括算术逻辑单元(ALU)和控制单元。

智能家居系统设计实验报告

智能家居系统设计实验报告一、引言智能家居系统是一种集成了现代科技与家居设备的新型房屋系统。

它通过网络连接和智能控制,使得家庭设备更加智能化、便利化和节能环保化。

本实验报告旨在介绍智能家居系统的设计及实验结果。

二、背景以往的家居系统主要通过物理开关进行控制,效率低且缺乏智能化。

然而,随着科技的发展,智能家居系统应运而生,为人们提供了更加便捷、安全、舒适的生活方式。

三、系统设计1. 系统结构智能家居系统由以下几个关键组件构成:(1) 传感器:用于感知家居环境,例如温度、湿度、光照等。

(2) 控制器:负责接收传感器信息并进行处理和分析。

(3) 执行器:根据控制器的指令,对家居设备进行控制,如开启灯光、调节温度等。

(4) 通信网络:连接传感器、控制器和执行器,实现信息传输与控制命令传递。

2. 功能设计智能家居系统的功能设计需要根据实际需求进行定制,常见的功能包括:(1) 照明控制:根据光照强度自动调节灯光亮度。

(2) 温度控制:根据温度传感器反馈,智能调节空调或暖气温度。

(3) 安防控制:通过监控摄像头和门锁传感器实时监测家居安全,并进行远程控制。

(4) 家电控制:通过智能插座和电视、音响等设备的连接,实现远程控制和定时操作。

四、实验过程与结果1. 实验准备(1) 购买所需设备和材料,包括传感器、控制器、执行器等。

(2) 搭建实验环境,确保各组件能够正常连接并供电。

2. 硬件连接按照系统设计,将传感器、控制器和执行器按照指定方法进行连接。

确保连接正确并稳定。

3. 软件程序编写(1) 选择适合的开发平台,如Arduino、树莓派等,并下载相关开发软件。

(2) 编写程序代码,包括传感器数据采集与处理、控制指令生成和执行器控制等功能。

4. 实验操作(1) 将系统部署到实验环境中,并确认各组件正常运行。

(2) 进行各项功能测试,如温度控制、照明控制、安防控制等。

5. 实验结果与分析根据实验操作,记录各功能的测试结果,并分析其准确性和稳定性。

计算机组成ALU实验报告

计算机组成与系统结构实验报告院(系):计算机科学与技术学院专业班级:学号:姓名:同组者:指导教师:实验时间: 2012 年 3 月 28 日实验目的:1.进一步熟悉Altebra QuartusII 开发环境(包括各种输入方法、功能仿真、综合实现等)。

2.进一步熟悉运用Verilog HDL语言进行编程。

3.熟悉算术逻辑部件的设计,实现11条指令中运算的ALU。

实验仪器:PC机(安装Altebra 公司的开发软件 QuartusII)一台实验原理:11条目标指令的ALU,输入为两个32位操作数A和B,其中核心部件是能够进行加减运算的加法器,加法器除了输出和/差Add_Result以外,还有进位标志Add_carry、零标志Zero、溢出标志Add_Overflow 和符号标志Add_Sign。

ALU的操作由一个ALU操作控制信号生成部件产生的控制信号来控制,该控制信号的输入是ALUctr信号,输出有4个控制信号:SUBctr、Opct、Ovctr、SIGctr。

ALUctr的三位编码及其对应的操作类型和ALU控制信号ALU<2:0> 操作类型SUBctr OVctr SIGctr Opctr<1:0> Opctr的含义0 0 0 addu 0 0 X 0 0 加法器的输出结果0 0 1 add 0 1 X 0 0 加法器的输出结果0 1 0 or X 0 X 0 1 “按位或”输出结果0 1 1 未用1 0 0 subu 1 0 X 0 0 加法器的输出结果1 0 1 sub 1 1 X 0 0 加法器的输出结果1 1 0 sltu 1 0 0 1 0 小于置位结果输出1 1 1 slt 1 0 1 1 0 小于置位结果输出实验过程及实验记录:1 完成代码的编写,并调试运行。

Alu模块module alu(A,B,ALUctr,Zero,Overflow,Result);parameter n=32;input [n-1:0] A,B;input [2:0] ALUctr;output Zero,Overflow;output [n-1:0] Result;wire SUBctr,OVctr,SIGctr,SignA,SignB,Cin;wire [1:0] OPctr;wire [n-1:0] X,Y,Z,Less,M,N,Add_Result;wire Add_Carry,Add_Overflow,Add_Sign;assign M={n{1'b0}};assign N={n{1'b1}};assign SUBctr=ALUctr[2];assign OVctr=!ALUctr[1]&ALUctr[0];assign SIGctr=ALUctr[0];assign OPctr[1]=ALUctr[2]&ALUctr[1];assign OPctr[0]=!ALUctr[2]&ALUctr[1]&!ALUctr[0];assign Cin=SUBctr;assign X=B^{n{SUBctr}};assign Y=A|B;assign SignA=Cin^Add_Carry;assign SignB=Add_Overflow^Add_Sign;assign Overflow=Add_Overflow&OVctr;Adderad(Cin,A,X,Add_Carry,Add_Overflow,Add_Sign,Add_Result,Zero );MUX2to1 m1(SignA,SignB,Less,SIGctr);defparam m1.k=1;MUX2to1 m2(N,M,Z,Less);MUX3to1 m3(Add_Result,Y,Z,Result,OPctr);endmodule2选1模块module MUX2to1(X,Y,Z,ctr); parameter k=32;input [k-1:0] X,Y;output reg [k-1:0] Z;input ctr;always @(X or Y or ctr)if(ctr) Z<=X;else Z<=Y;endmodule3选1模块module MUX3to1(A,B,C,D,ctr); parameter k=32;input [k-1:0] A,B,C;output reg [k-1:0] D;input [1:0] ctr;always @(A or B or C or ctr) if(ctr==2'b00) D=A;elseif(ctr==2'b01) D=B;elseif(ctr==2'b10) D=C; endmodule加法器模块moduleAdder(Cin,X,Y,Add_Carry,Add_Overflow,Add_Sign,Add_Result,Z ero);parameter k=32;input [k-1:0] X,Y;input Cin;output reg [k-1:0] Add_Result;output Add_Carry,Add_Overflow,Add_Sign,Zero;reg Add_Carry;assign Zero=~|Add_Result;assign Add_Sign=Add_Result[31];assignAdd_Overflow=Add_Carry^Add_Result[k-1]^X[k-1]^Y[k-1];always @(X or Y or Cin){Add_Carry,Add_Result}=X+Y+Cin;endmodule2.进行仿真并验证其正确性:总结与思考: 通过此次试验,对算术逻辑部件有了较为深入的了解,掌握了11条目标指令的ALU 实现的方法,锻炼了自己的硬件设计能力和编程技巧。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

END ARCHITECTURE ART;

六、设计步骤

1、打开QuartusⅡ,选择File→New Project Wizard,输入目标路径,工程名及顶层设计实体名,区分大小写。

2、输入工程中包含的设计文件

3、确定设计使用的器件,MAXII→

R0_B<=RS_B OR I3 OR I2;

R1_B<=RS_B OR I3 OR( NOT I2);

R2_B<=RS_B OR( NOT I3) OR I2;

LDAC<=LDRiAND I1 AND I0;

LDR0<=LDRiAND (NOT I1) AND (NOT I0);

LDR1<=LDRiAND (NOT I1) AND I0;

五、VHDL程序

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY RISC IS

PORT(T1,T2,T3,T4,I7,I6,I5,I4,I3,I2,I1,I0,CLR,Q:IN STD_LOGIC;

LD<=NOT(T3 AND JMP AND (NOT F));

IOM<=NOT( T2 OR (T1 AND (LOAD OR STA) AND F)OR (T3 AND STA AND F) );

LDPC<=(M3 AND (NOT F))OR (M3 AND (LOAD OR STA)AND F );

SS2: PROCESS(CLR,T1,T2,T3,LOAD,F,STA)

BEGIN

IF CLR='0' THEN RD<='0';WR<='0';

ELSE RD<=(T2 AND(NOT F)) OR ( T1 AND( LOAD OR STA)AND F)OR (T2 AND LOAD AND F);

三、设计内容

设计一台基于RISC技术的模型计算机,包含五条常用指令,并编写一段验证程序检验指令功能。

四、设计原理

1.指令系统设计

本实验采用RISC思想设计的模型机选用常用的五条指令:MOV、ADD、LOAD、STORE和JMP作为指令系统,寻址方式采用寄存器寻址及直接寻址两种方式。指令格式采用单字节及双字节两种格式:

系统结构实验与硬件设计Ⅱ

基于Leabharlann 实验报告1.实验目的1.了解精简指令系统计算机(RISC)和复杂指令系统计算机(CISC)的体系结构特点和区别。前面组成原理部分的“复杂模型机”是基于复杂指令系统设计的模型机。本书中所提到的复杂指令系统计算机可参照组成原理部分的“复杂模型机”来理解。

2.实验设备

PC机一台,TD-CMA实验系统一套。

WR<=T3 AND STA AND F;

END IF;

END PROCESS;

PC_B<=NOT( (T1 AND (NOT F) )OR ((LOAD OR STA)AND T4 AND (NOT F)));

ALU_B<=NOT(ADD AND T4);

RS_B<=NOT(((MOV OR ADD OR JMP)AND T3 AND (NOT F)) OR (STA AND T3 AND F));

SIGNAL MOV,ADD,JMP,LOAD,STA,RS_B,LDRi,F,CLK,CLK11,M1,M2,M3,M4:STD_LOGIC;

BEGIN

M1<=Q AND T1;

M2<=Q AND T2;

M3<=Q AND T3;

M4<=Q AND T4;

MOV <= (not i7) and (not i6) and (not i5) and (not i4);

单字节指令(MOV、ADD、JMP)格式如下:

7654

32

10

OP-CODE

RS

RD

其中,OP-CODE为操作码,RS为源寄存器,RD为目的寄存器,并规定:

RS或RD

选定的寄存器

00

01

10

11

R0

R1

R2

A

双字节指令(LOAD、SAVE)格式如下:

7654(1)

32(1)

10(1)

7—0(2)

OP-CODE

RS

RD

P

其中括号中的1表示指令的第一字节,2表示指令的第二字节,OP-CODE为操作码,RS为源寄存器,RD为目的寄存器,P为操作目标的地址,占用一个字节。

2.RISC处理器的模型计算机系统设计

数据通路图

指令周期流程图

3.控制器设计

(1)数据通路图中的控制器部分需要在CPLD中设计。

(2)用VHDL语言设计RISC子模块的功能描述程序,顶层原理图如下图所示

进来,启动Start按钮完成下载

12、打开CMA软件,编写验证程序,运行通路图,观察并记录程序执行流程及各寄存器的变化。

13、完成实验报告,内容包括:实验目的、实验设备、实验内容、实验原理图、VHDL程序、实验步骤、验证程序、实验数据及实验心得。

七、验证程序

LOADR0 ,R1

MOVR1,R2

ADDR2,R1

ADD <= (not i7) and (not i6) and (not i5) and (i4);

JMP <= (not i7) and (noti6) and (i5) and (not i4);

LOAD <= (not i7) and (not i6) and (i5) and (i4);

STA <= (not i7) and (i6) and (not i5) and (not i4);

4、选择EDA工具:综合、仿真和时序分析

5、检查工程中的各项设置

6、建立新文件。File→New,选择VHDL,输入程序,保存

7、File→Creat/Update→CreatSymbol Files For Current File,产生一个类型为电原理图的新文件。

8、重复6、7,产生所有模块,完成VHDL语言输入及原理图绘制。

LDDR<=ADD AND M3 AND (NOT F);

LDIR<=M2 AND (NOT F);

LDAR<=M1 OR ((LOAD OR STA)AND (NOT F)AND M4) OR(M1 AND(LOAD OR STA)AND F);

LDRi<=(ADD AND M4 AND (NOT F))OR (LOAD AND M2 AND F) OR (MOV AND M3 AND (NOT F));

S<="1001";

CLK11<=(LOAD OR STA)AND T4;

SS1: PROCESS(CLK11,CLR)

BEGIN

IF CLR='0' THEN F<='0';

ELSIF (CLK11'EVENT AND CLK11='0') THEN F<=NOT F;

END IF;

END PROCESS;

LDR0,LDR1,LDR2,R0_B,R1_B,LD,R2_B,PC_B,LDAR,IOM,RD,WR,LDIR,LDPC,LDAC,LDDR,ALU_B: OUT STD_LOGIC;

S:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END ENTITY RISC;

ARCHITECTURE ART OF RISC IS

9、分配引脚。执行Assignments→Pins命令,启动分配引脚功能.

10、编译源文件,Processing→Start Compilation

11、用下载电缆将PC机和CPLD的下载电路连接起来,执行

Tool→Programmer命令,在框中选择默认的JTAG下载方式,

选中Program/Configure框,Add File将生成的pof文件添加

SUBR2,R0

STORE R1,R0

JMPR0

八、实验数据截图