Virtuoso Layout 版图基本知识

版图绘制及Virtuoso工具软件

GDS文件操作

28/ 103

Display Control Window

工艺流程

Design Rule

Virtuoso软件

PDK简介

版图设计

GDS文件操作

29/ 103

Virtuoso下快捷键的使用

• • • • • • • • • • • • • Ctrl+A 全选 Shift + X,进入子模块 Shift + B,升到上一级视图 Ctrl + C 中断某个命令,一般用 ESC代替 Shift + C 裁切(chop) C 复制,复制某个图形 Ctrl + D 取消选择。亦可点击空白 处实现。 Ctrl + F显示上层等级 Shift + F显示所有等级 F fit,显示你画的所有图形 K 标尺工具 Shift + K清除所有标尺 L 标签工具 Design Rule Virtuoso软件 M 移动工具 Shift + M 合并工具,Merge N 斜45对角+正交 Shift + O 旋转工具, Rotate O 插入接触孔 Ctrl + P 插入引脚, Pin Shift + P 多边形工具, Polygon P 插入Path(路径) Q 图形对象属性(选中一个图形先) R 矩形工具, 绘制矩形图形 S 拉伸工具, 可以拉伸一个边,也可 以选择要拉伸的组一起拉伸 • U 撤销, Undo • Shift + U重复, Redo, 撤销后反悔 • • • • • • • • • • •

工艺流程

Design Rule

Virtuoso软件

PDK简介

版图设计

GDS文件操作

40/ 103

Virtuoso_Layout_版图基本知识课件

工具介绍

• 我们现阶段主要使用的版图软件有基于 PC的 chiplogic 、 Tanner 公 司 的 L-edit 、 基 于 Cadence的Virtuoso

Virtuoso_Layout_版图基本知识

virtuoso 使用流程

• 登录到工作站 • 创建版图库、版图单元 • 确立相关技术文件以及配置

版图基本知识

MOS器件简介

2009年11月25日

市场IDEA 结构定义 系统设计仿真 电路设计仿真 版图设计 原型&测试 大规模生产

Virtuoso_Layout_版图基本知识

目录

• 工艺简介 • 工艺流程介绍 • 工具介绍 • 版图设计规则 • 版图设计流程 • 小结

Virtuoso_Layout_版图基本知识

S/D

Gate

D/S PSG

Poly

N-imp

P-sub

The cross section of mos

Virtuoso_Layout_版图基本知识

Layout

Layout of cmos transistors

Pwell P-imp Active Poly

N-imp contact

Virtuoso_Layout_版图基本知识

工艺简介

• 现有的IC工艺主要分为两大类,分为模拟工艺 和数字工艺。

• 模拟工艺主要以双极器件为主,它的做法是在 晶元上生长外延,在外延上制作双极器件完成 电路功能,可以称为BIPOLAR工艺。另外由CMOS 工艺也可以制造模拟电路。

• 数字工艺主要以CMOS器件为主,它的做法是在 衬底上直接做出MOS管,和在衬底上扩散出阱, 在阱内做出MOS管,完成电路功能。

实验三 Virtuoso版图编辑器的基本使用

实验三Virtuoso版图编辑器的基本使用目录1.实验目的2.使用Virtuoso版图编辑器绘制反相器版图3.设计规则检查(D esign R ule C heck)4.版图网表和参数提取(L ayout and P arameter E xtraction)5.版图与原理图网表对比检查(L ayout v s. S chematic Check)1.实验目的本实验主要目的是通过绘制反相器版图的详细过程初步介绍Virtuoso版图编辑器的使用,同时也介绍了设计规则检查(DRC)、版图提取(LPE)、以及版图原理图网表对比检查(LVS)的基本操作步骤。

2.使用Virtuoso版图编辑器绘制反相器版图通过用版图编辑器创建反相器版图的例子来熟悉版图编辑器的使用。

在Library Manager窗口中选中IClab1库,然后点击File-->New-->Cell View,输入Cell Name为inverter,Tool选Virtuoso,View Name会自动变成layout,见图1。

图1. 用Virtuoso创建layout对话框在此需要特别注意的是,我们创建的版图是为实验一反相器原理图而创建的,因此自定义元件库名称必须与原理图所在库名称一致,特别是Cell Name也必须与原理图的Cell Name一致,即为inverter,有些同学在做此实验时在新创建的元件库中做,而且取了一个与原理图不同名的版图名称,这就给后面的版图提取和后端仿真带来了很大麻烦,所以请严格遵守上述命名规则。

点击OK会打开Virtuoso版图编辑器,同时启动的还有Layer Select Window,即LSW。

因绘制版图时一定先要与某一工艺库关联,而LSW将与关联的工艺库联动,所以不同的工艺库会有不同的LSW窗口出现。

本实验中的IClab1自定义库是与NCSU_TechLib_ami06工艺库关联的,所以该工艺库的名称会显示在LSW窗口的上面。

Virtuoso_Layout_版图基本知识课件

Oxide/Iso Substrate

Al

注:我们在这里指出各个层次说明是为了更好的对下面的实例进行分析

Virtuoso_Layout_版图基本知识

CMOS Transistor Introduction

Virtuoso_Layout_版图基本知识

MOS(Cross section)

Virtuoso_Layout_版图基本知识

virtuoso 常用快捷键

放大

ctrl + z

• 缩小

shift + z

• 画线

p

• 画矩形 r

• 画多边形 shift + p

• 插入单元 i

• 显示属性 q

• 拉伸

s

Virtuoso_Layout_版图基本知识

virtuoso 常用快捷键

• 复制

Virtuoso_Layout_版图基本知识

工艺简介

• 随着设计的要求和发展,数模混合电路大量应 用 , BiCMOS 工 艺 被 开 发 出 来 并 大 量 应 用 。 BiCMOS 工 艺 顾 名 思 义 , 这 种 工 艺 中 既 包 含 Bipolar器件,也包含CMOS器件。常见的BiCMOS 工艺一般都基于CMOS工艺,利用CMOS工艺中存 在的阱、有源等,寄生出电路所需的的双极管 来。

设计规则

• 设计规则主要包括最小宽度,层与层之间的最小间距等等。

Virtuoso_Layout_版图基本知识

版图设计流程

项目下达

资料准备

解剖并照片

照片分析

工艺确认

器件分析整理

工艺选择

方案评估 可行

版图绘制

Cadence IC版图工具Virtuso的使用简介

建立一个库(续)

3.在CIW窗口中点击file/ new/ library….. 给库任意取名字(如:lib_1),在右侧选 compile a new techfile. (如图) 点击OK,填入工艺文件的路径和名称。

DRC检查(续)

DRC检查(续)

• 在CIW窗口中查找错误

• 回到layout中改正错误,并重新做DRC。反复修改,直到所 有错误都被修改。

LVS检查

• DRC保证了版图能够在流片中没有违规 • LVS则保证了流片出来逻辑功能的正确性。 • LVS=layout versus schematic • 步骤:

建立一个库(续)

4.在CIW窗口中点击tools/ library manager 我们就看到了新建的库lib_1 在下拉菜单中选择new/ cell view,取一个cell name:INV。 在该窗口中点击tool选择Virtuoso。 OK!这样就建立了一个画版图的平台。

如何调入版图的层

• N-Well

N-Well的规则(续)

Island and Poly

Island and Poly(续)

Poly

PLUS

PLUS(续)

Contact and Metal-1

Contact

Metal-1

Via-1

Metal-2 and Via

Metal-3

Cadence 版图工具Virtuoso简介

作者:卢俊 2006-7-5

内容安排

• 本次上机实验的任务 • 使用Virtuoso设计版图的步骤简介 • 电子58所0.5um工艺设计规则介绍

layout 基础知识介绍

沟道长 金属布 (μm) 线层数

多晶 硅布 线层 数

电源 电压

(V)

W/L

阀值电压 (V)

NMOS PMOS

31级环 行振荡 器频率

(MHz)

0.35

3

0.6/0.40 0.54 -0.77

2 3.3

196.17

3.6/0.40 0.58 -0.76

MOSIS为TSMC 0.35mCMOS工艺定义的全部工艺层

集成电路设计基础

第七章 集成电路版图设计

华南理工大学 电子与信息学院 广州集成电路设计中心 殷瑞祥 教授

版图设计概述

• 版图(Layout)是集成电路设计者将设计并模拟优化后的电路转 化成的一系列几何图形,包含了集成电路尺寸大小、各层拓扑 定义等有关器件的所有物理信息。

• 集成电路制造厂家根据 版图 来制造掩膜。版图的设计有特定的 规则,这些规则是集成电路制造厂家根据自己的工艺特点而制 定的。不同的工艺,有不同的设计规则。

电阻的可变参数:电阻宽度(width)、电阻值(R)。

多晶硅电阻

多晶硅通过接触孔与第一层金属连接,该金属构成电阻的两

个电极,图中所示电阻最小宽度为2 λ=0.4μm。

第一层多晶硅的方块电阻值为7.4欧姆,每接触孔形成的电

阻为5.6欧姆。该多晶硅电阻一般为几十欧姆。

2.0

Poly

2.0 2.0

Metal1

1. 工艺参数:如每一层的厚度,深度…等。 2. 工艺流程:如每一步骤所需的时间。 3. 设计指导 (Design guide):如告诉你如何加contact,如何用

library,如何用避免Latch Up…等 4. SPICE Parameters:SPICE的参数。一般还有分是那一种

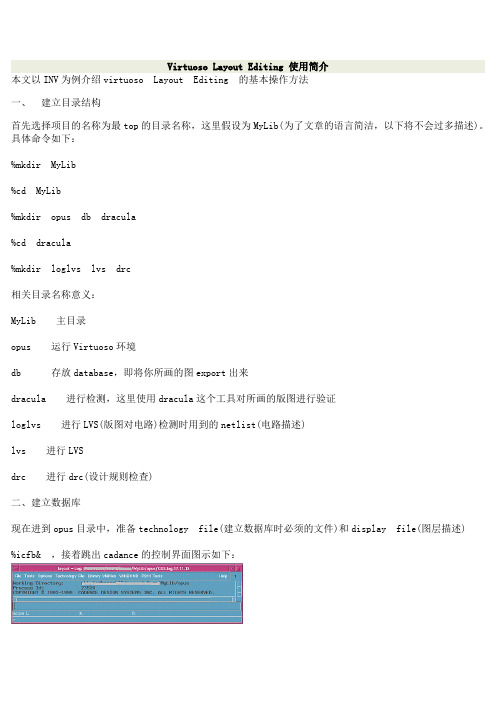

Virtuoso Layout Editing 使用简介

Virtuoso Layout Editing 使用简介本文以INV为例介绍virtuoso Layout Editing 的基本操作方法一、建立目录结构首先选择项目的名称为最top的目录名称,这里假设为MyLib(为了文章的语言简洁,以下将不会过多描述)。

具体命令如下:%mkdir MyLib%cd MyLib%mkdir opus db dracula%cd dracula%mkdir loglvs lvs drc相关目录名称意义:MyLib 主目录opus 运行Virtuoso环境db 存放database,即将你所画的图export出来dracula 进行检测,这里使用dracula这个工具对所画的版图进行验证loglvs 进行LVS(版图对电路)检测时用到的netlist(电路描述)lvs 进行LVSdrc 进行drc(设计规则检查)二、建立数据库现在进到opus目录中,准备technology file(建立数据库时必须的文件)和display file(图层描述)%icfb& ,接着跳出cadance的控制界面图示如下:点击File-->New-->Library ,在跳出的对话框中Name填入MyLib,选中Compile a new techfile,点击ok在ASCII Technology file 里填入准备好的tech file,点击ok,库便建好了。

三、建立新的版图inv点击File-->New-->Cellview在跳出的对话框中Library Name选择MyLib,Cell Name填入inv,View Name选择layout,点击ok接着就是版图inv的工作区了图为layout工作区,所进行的layout都在些工作区内完成。

工具框中介绍几个常用的工具,为保存,点击保存当前工作区的内容。

这三个图标依次为fit全部显示,zoom in放大视图,zoom out缩小视图。

layout常用基本操作

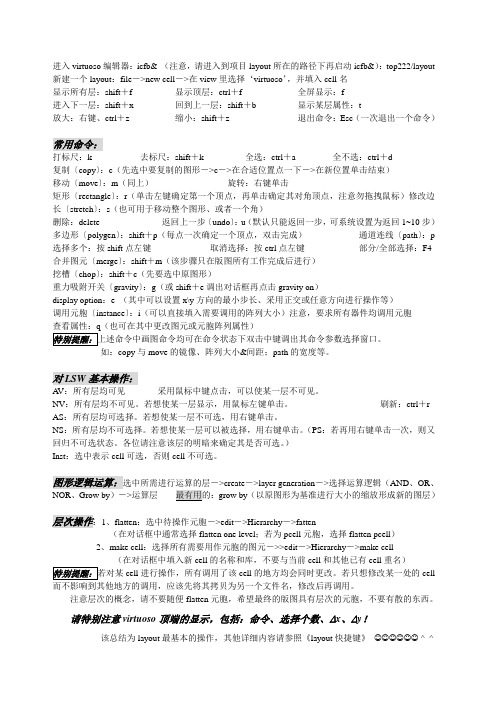

进入virtuoso编辑器:icfb& (注意,请进入到项目layout所在的路径下再启动icfb&):top222/layout 新建一个layout:file->new cell->在view里选择‘virtuoso’,并填入cell名显示所有层:shift+f 显示顶层:ctrl+f 全屏显示:f进入下一层:shift+x 回到上一层:shift+b 显示某层属性:t放大:右键、ctrl+z 缩小:shift+z 退出命令:Esc(一次退出一个命令)常用命令:打标尺:k 去标尺:shift+k 全选:ctrl+a 全不选:ctrl+d复制〔copy〕:c(先选中要复制的图形->c->在合适位置点一下->在新位置单击结束)移动〔move〕:m(同上)旋转:右键单击矩形〔rectangle〕:r(单击左键确定第一个顶点,再单击确定其对角顶点,注意勿拖拽鼠标)修改边长〔stretch〕:s(也可用于移动整个图形、或者一个角)删除:delete 返回上一步〔undo〕:u(默认只能返回一步,可系统设置为返回1~10步)多边形〔polygen〕:shift+p(每点一次确定一个顶点,双击完成)通道连线〔path〕:p 选择多个:按shift点左键取消选择:按ctrl点左键部分/全部选择:F4 合并图元〔merge〕:shift+m(该步骤只在版图所有工作完成后进行)挖槽〔chop〕:shift+c(先要选中原图形)重力吸附开关〔gravity〕:g(或shift+e调出对话框再点击gravity on)display option:e (其中可以设置x\y方向的最小步长、采用正交或任意方向进行操作等)调用元胞〔instance〕:i(可以直接填入需要调用的阵列大小)注意,要求所有器件均调用元胞查看属性:q(也可在其中更改图元或元胞阵列属性)如:copy与move的镜像、阵列大小&间距;path的宽度等。

Virtuoso软件的使用技巧

Tools →Library Manager

新建库: File→New →Library

File→New →Cell View

Tool:Composer-Schematic

主要内容

1、Virtuoso简介 2、如何正确进入Virtuoso 3、电路图的绘制 4、电路图的仿真与分析 5、版图的绘制 6、版图的验证DRC/LVS 7、版图后仿真

主要内容

1、Virtuoso简介 2、如何进入Virtuoso 3、电路图的绘制 4、电路图的仿真与分析 5、版图的绘制 6、版图的验证DRC/LVS 7、版图后仿真

Calibre →Run PEX

128

129 # add layout topcell name to replace xxx

130 setenv LAYOUT_PRIMARY "OP_CL_3p"

131 #setenv LAYOUT_PRIMARY "mpw_08"

132 #setenv LAYOUT_PRIMARY "HDPWM_top_with_buffer"

调用生成的模块

常用的快捷键

i (instance):插入元件 f (full screen):全屏幕 w (wire) :连线 p (pin):加管脚 q (quality):编辑属性

e:进入下一层模块 ctrl+e:返回上一层模

块

[ : 缩小两倍 ] :放大两倍

主要内容

1、Virtuoso简介 2、如何进入Virtuoso 3、电路图的绘制 4、电路图的仿真与分析 5、版图的绘制 6、版图的验证DRC/LVS 7、版图后仿真

关于Cadence virtuoso Layout Editer的一些实用技巧

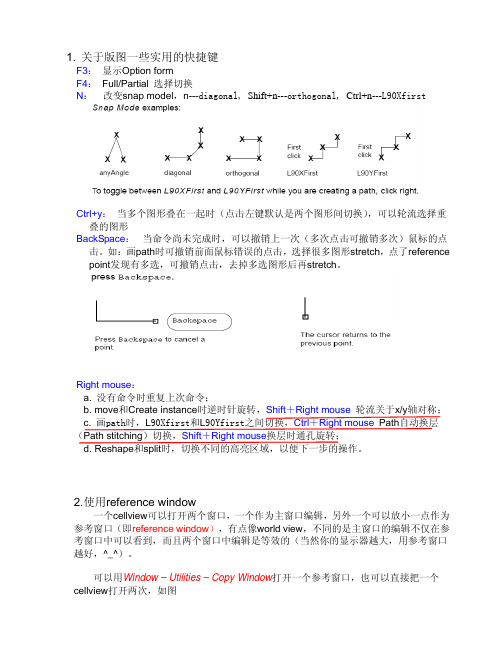

Right mouse: a. 没有命令时重复上次命令; b. move和Create instance时逆时针旋转,Shift+Right mouse 轮流关于x/y轴对称; c. 画path时,L90Xfirst和L90Yfirst之间切换,Ctrl+Right mouse Path自动换层

6. 关于Tap的使用

Tap是用来快速捕捉任意一个图形的相关属性,捕捉到的信息会自动赋给将要生成的 Object上包括Layer信息,Net的名字,其它属性(如path的width,endtype等等)

a. 用Tap来快速选择entry Layer

选择Edit – Tap [t],默认的是选择的Layer是边界最接近鼠标指针(或者边界与指针 重合)的图形的Layer,如果两层完全重合,则有一层可能一直也选不中。

②在Change To Layer 栏里选择你要换的layer,也可以通过Control+right mouse 键来选择需要换的层。

ห้องสมุดไป่ตู้

如果Change To Layer栏里没有层可选,那是因为在technology file 中没有关于这层 的contact(或者cdsVia的定义)定义,只有定义了之后才能使用path stitching功能。

因此可以设置环境变量 layerTapCycle为 t or nil, 可以改变捕捉的方法 在CIW敲入命令(只对这个icfb窗口适用): envSetVal("layout" "layerTapCycle" 'boolean t ) 或者在根目录下的.cdsenv文件中加入一行,每次启动icfb就会调用这个环境变量 layout layerTapCycle boolean t 设成 nil 时(默认值)选择的Layer是边界最接近鼠标指针(或者边界与指针重合) 的图形的Layer 设成 t 时,在重复的图形上连续点击,可以依次轮流的选择不同的Layer,直到选 到你想要的为止。

CadenceVirtuoso讲义

• • •

版图设计工具-Virtuoso LE 版图验证工具-Diva 版图验证工具-Dracula

1

系统启动

环境设置

1 .cshrc 文件设置

.cshrc文件中指定 Cadence 软件和 licence 文件所在的路 径

2 .cdsenv 文件设置

.cdsenv 文件包含了 Cadence 软件的一些初始设置,该 文件用 SKILL 语言写,Cadence 可直接执行

48

版图验证工具-DIVA

49

版图验证工具-DIVA

分析错误(Explain)

50

版图验证工具-DIVA

51

版图验证工具-DIVA

Extractor

52

版图验证工具-DIVA

Extractor 功能

提取器件和互联信息用于 ERC 或 LVS 提取网表 提取有寄生参数的版图网表用于模拟

DRC 界面

45

版图验证工具-DIVA

Checking Method指的是要检查的版图的类型:

Flat 表示检查版图中所有的图形,对子版图块不检查。 Hierarchical利用层次之间的结构关系和模式识别优化,检查电路 中每个单元块内部是否正确。 hier w/o optimization 利用层次之间的结构关系而不用模式识别 优化,来检查电路中每个单元块 。

版图编辑环境

13

版图设计工具-Virtuoso LE

Virtuoso Layout Editing

14

版图设计工具-Virtuoso LE

LSW-层选择窗口

15

版图设计工具-Virtuoso LE

设置有效 Drawing 层

最新实验一-Virtuoso原理图和图标编辑器的基本使用

最新实验一-Virtuoso原理图和图标编辑器的基本使用实验一Virtuoso原理图和图标编辑器的基本使用目录1.实验目的2.创建一个新的自定义单元库3.使用 Cadence Virtuoso 原理图编辑器构建一个反相器4.创建一个自定义元器件图标1.实验目的本实验采用AMI06工艺设计一个反相器,以此使学生达到熟悉Cadence Virtuoso 原理图和图标编辑器使用,记住常用热键组合以及掌握与特定工艺库关联之目的。

2.创建一个新的自定义单元库启动 Cadence,调用 CIW(Command Interpreter Window)首先启动计算机,在用户名处键入 cdsusr, 密码处键入123456,进入Linux操作系统桌面,在cdsusr’s Home文件夹中创建iclabs 子文件夹。

请记住一定要创建这个子文件夹,这样才不会影响到cdsusr根目录下的cds.lib文件。

操作如下:File --> Create Folder, 在新创建的文件夹名称处键入iclabs(可取不同名字,学号和本人名字拼音等)。

进入Linux桌面,单击鼠标右键打开终端。

见图1。

图1. Linux桌面操作在打开的终端中执行下列命令:见图2的红色框线内。

图2. Linux终端执行第二个命令后你就可看见Cadence软件的CIW窗口出现。

见图3所示。

图3. Cadence软件的CIW窗口在CIW窗口中点击Tools-->Library Manager..., 将打开库管理器(图4)。

图4. 库管理器你可看到NCSU提供的库已显示在Library栏目中,有NCSU_Analog_Parts,...等。

点击库管理器中的File-->New-->Library..., 将打开New Library 对话窗口, 现创建一个新库取名为IClab1。

见图5。

图5. 创建一个自定义元件库点击OK弹出关联工艺库对话框(图6),选择Attach to an existing techfile。

使用Virtuoso设计全定制版图

使用Virtuoso设计全定制版图本文介绍利用virtuoso layout editor(以后简称le)创建全定制版图,以及vituoso le 的一些使用说明。

全文将用一个贯穿始终的例子来说明如何绘制全定制版图,一个最简单的反相器的版图.设计过程采用chartered(csm25rf)库—标准CMOS工艺库。

具体内容包括:1)如何打开virtuoso le和le 的一些设置;2)使用LSW窗口;3)使用le 创建一个版图;4)使用快捷键—bindkey;5)使用diva验证版图;6)使用diva 进行LVS;登陆以后,首先要先创建自己的工作目录,比如Work, cd Work.从csm25rf库所在文件夹下拷贝文件到自己的工作目录下,你的工作目录下必须有文件,不然在LSW窗无法显示绘制版图需要的各个图层。

从/CDS_ROOT/tools/dfII/cdsuser目录下拷贝 .cdsinit文件到自己的目录下,该文件是Cadence 自带的软件相关设置的文件,里面有相关字体的设置,Bindkey设置等,这里主要考虑Bindkey的设置,也可以设置自己的Bindkey,不过 Cadence默认的设置是足够的。

当然也可以单单靠鼠标来进行操作,virtuoso le 窗口有常用命令的工具栏,不过就我自己的感觉,用快捷键比鼠标要快很多。

如果要运行Diva LVS 还得有.simrc文件。

(不过这里有一个问题,服务器上的.simrc文件的设置跟csm25rf库有不一致的地方,运行Diva LVS 会出现目录LVS非法的错误。

运行vituoso le要打开virtuoso le ,首先要打开CIW窗口。

在shell 命令行下输入:icfb& 进入CIW 窗口,字符&使得cadence 在后台工作(即可以在shell命令行执行其它命令),也可以在shell 提示符下输入其它的命令来打开CIW窗口,如下图:(在这里也可以输入layout& 或者 layoutPlus&)检查设计需要的相关库是否存在。

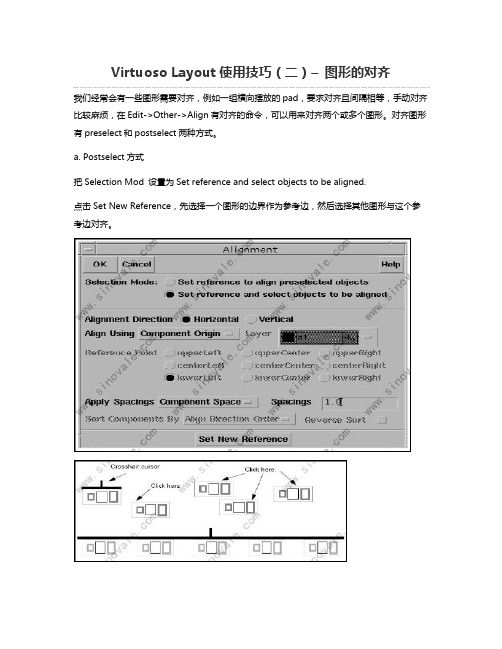

Virtuoso Layout使用技巧(二)– 图形的对齐

Virtuoso Layout使用技巧(二)–图形的对齐

我们经常会有一些图形需要对齐,例如一组横向摆放的pad,要求对齐且间隔相等,手动对齐比较麻烦,在Edit->Other->Align有对齐的命令,可以用来对齐两个或多个图形。

对齐图形有preselect和postselect两种方式。

a. Postselect方式

把Selection Mod 设置为Set reference and select objects to be aligned.

点击Set New Reference,先选择一个图形的边界作为参考边,然后选择其他图形与这个参考边对齐。

b. Preselect方式

设置Selection Mod为Set reference to align preselected objects.

先选择未对齐的图形,然后点击Set New Reference and 在layout窗口选择一个对齐点,所有选择的图形就会对齐。

当然对齐还有其他的一些设置,但要注意这里的对齐操作是对一个整体而言(如一个instance,polygon等),如果几个图形需要组合在一起,参与与其他单元的对齐,先将这几个图形make cell或者用attatch(而且被attatch的图形不能被选中),否则这几个图形将被拆开。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Layout

Pwell

P-imp

Active

Poly

N-imp contact

Layout of cmos transistors

工具介绍

我们现阶段主要使用的版图软件有基于 PC 的 chiplogic、 Tanner 公司的 L-edit 、 PC的 chiplogic 、 公司的L 基于Cadence的 基于Cadence的Virtuoso

复制 c 取消操作 u 撤销取消操作 shift + u 移动 m 标尺 k 合并 shift + m 剪切 shift + c 取消选中 ctrl + d 标注label 标注label l

版图设计规则

版图设计规则概念 设计规则种类

版图设计规则概述

集成电路的制造收到工艺水平的限制, 受到器件物理参数的制约,为了保证器 件正确工作和提高芯片的成品率,要求 设计者在版图设计时遵循一定的设计规 则(design rule),这些设计规则直接 则(design rule),这些设计规则直接 由流片厂家提供。 设计规则是版图设计与工艺之间的接口。

设计规则

设计规则主要包括最小宽度,层与层之间的最小间距等等。

版图设计流程

项目下达 照片分析 工艺选择 方案评估 可行 版图绘制 数据出代 资料准备 工艺确认 文件确认 不可行 项目终止 环境配置 模块分配 绘制 验证 解剖并照片 器件分析整理 适用性评估

P-imp

S u b strate

Active

Poly

Al

N-imp contact

注:我们在这里指出各个层次说明是为了更好的对下面的实例进行分析

CMOS Transistor Introduction

MOS(Cross section)

S/D

Gate Poly

D/S

PSG

N-imp

P-sub

The cross section of mos

virtuoso 使用流程

登录到工作站 创建版图库、 创建版图库、版图单元 确立相关技术文件以及配置

virtuoso 常用快捷键

放大 ctrl + z 缩小 shift + z 画线 p 画矩形 r 画多边形 shift + p 插入单元 i 显示属性 q 拉伸 s

virtuoso 常用快捷键

分为: 现有的IC工艺主要分为: * CMOS工艺 CMOS工艺 * BIPOLAR工艺 BIPOLAR工艺 * BICMOS工艺 BICMOS工艺 下面简单介绍CMOS工艺 下面简单介绍CMOS工艺

层次申明: 层次申明:

well/NBL

O x id e /Iso

工艺简介

随着设计的要求和发展, 随着设计的要求和发展 , 数模混合电路 大量应用, BiCMOS 工艺被开发出来并大 大量应用 , BiCMOS工艺被开发出来并大 量应用。 BiCMOS 工艺顾名思义, 量应用 。 BiCMOS工艺顾名思义 , 这种工 艺中既包含Bipolar器件,也包含CMOS器 艺中既包含Bipolar器件,也包含CMOS器 件 。 常见的 BiCMOS工艺一般都基于 CMOS 常见的BiCMOS 工艺一般都基于CMOS 工艺, 利用 CMOS工艺中存在的阱 、 工艺 , 利用CMOS 工艺中存在的阱、 有源 等,寄生出电路所需的的双极管来。 寄生出电路所需的的双极管来。

版图基本知识

MOS器件简介 MOS器件简介

2009 11月25日 2009年11月25日

市场IDEA 结构定义 系统设计仿真 电路设计仿真 版图设计 原型&测试 大规模生产

目录

工艺简介 工艺流程介绍 工具介绍 版图设计规则 版图设计流程 小结

工艺简介

现有的IC工艺主要分为两大类, 现有的IC工艺主要分为两大类,分为模拟工艺 和数字工艺。 和数字工艺。 模拟工艺主要以双极器件为主, 模拟工艺主要以双极器件为主,它的做法是在 晶元上生长外延, 晶元上生长外延,在外延上制作双极器件完成 电 路 功 能 , 可 以 称 为 BIPOLAR 工 艺 。 另 外 由 CMOS工艺也可以制造模拟电路。 CMOS工艺也可以制造模拟电路。 数字工艺主要以CMOS器件为主, 数字工艺主要以CMOS器件为主,它的做法是在 衬底上直接做出MOS 管 和在衬底上扩散出阱, 衬底上直接做出 MOS管 , 和在衬底上扩散出阱 , 在阱内做出MOS管 完成电路功能。 在阱内做出MOS管,完成电路功能。