JTAG与SWD接口的.ppt

STM32F103的SWD、JTAG接口remap禁止后

手贱将STM32F103的SWD、JTAG接口remap禁止后单片机:stm32f103开发环境:keil uvision4烧写器:J-link,SWD接口使用STM32F103的PB3引脚作为GPIO口,但其默认功能为JTDO,需要remap。

Remap 中,使能GPIO_Remap_SWJ_JTAGDisable就可以了,这样是禁止JTAG,但保留SWD,因为板子设计用的是使用SWD接口进行烧写。

结果手贱,尝试了GPIO_Remap_SWJ_Disable,将整个SWD和JTAG都禁止了。

好吧,接下来就是程序运行完毕remap后,keiluvision4就不能再读取stm32的寄存器内容了,变量窗口的变量不能再查看了;想再重新烧写下、擦除下,提示错误,no cortex-m device,断电再上电,也不行,因为flash中的程序上电后自动运行,将SWD口禁止了。

网上查,解决方法是“将BOOT0脚和BOOT1脚接3.3V,这种方法是由RAM启动,所以之前你烧进去的程序是不会运行的,也就不存在JTAG被禁止”。

如果你的板子上做了BOOT 启动选择电路,那你就可以不用往下看了。

但略坑的是我的板子上的BOOT0已经直接接到GND了,总不能割线再飞线吧。

然后想到的就是NRST复位了。

但是,再次略坑的是板子上没有做手动复位电路,NRST 悬空在。

好吧,还好,NRST复位脚悬空在,而不是直接拉高。

比较幸运的是板子上焊接了一个拨码开关模块,开关ON时,接GND,开关OFF时,悬空。

接下来使用NRST来实现重新烧写。

飞线将NRST接到该开关,打到ON档,将NRST接GND。

板子上电,烧写时提示错误:cpudid not halt after reset(类似于这样,记不清)。

这是因为NRST一直为低,CPU一直为复位。

比较幸运的是,keil+J-Link还是比较执着,尝试一次不成功后,还尝试了第2、第3次等(具体几次不记得了,从output消息窗口可看出J-Link尝试了好几次)。

B52-2.5-JTAG-SWD-调试接口

• 芯片内嵌 (JTAG/SWD)调试接口

典型调试系统:ARM7TDMI处理器的高级调试特性使 应用程序、操作系统和硬件的开发变得更加容易。

调试主机: 一台运行调试软件 的计算机。 ADS1.2+AXD1.2 MDK-Keil for ARM

协议转换器: 将调试主机发出的 高级命令转换到处 理器JTAG接口的 低级命令。有3种:

14/20PIN JTAG接口电缆

较新的基于USB接口接口转换器(USB←→SWD) 仅有4根联线:VCC、SWDIO、SWCLK、GND

调试目标: 具体的硬件目标板。 调试接口有2种 JTAG、SWD

1.LPT←→JTAG B←→JTAG B←→SWD

STM32F103核心板

早期(2000年前后) 基于IEE488并行打印口的 JTAG协议转换器 电路原理图

USB←→JTAG(14/20PIN)

并行打印机接口信号

STLINK和JLINK使用 SWD四线 调试 下载STM32

For my breadboarded test rig, I used a four pin Harwin M20 connector. Even on a half size micromouse, this will not take up much room and I may use it as the only debug/programming connector.The pins on the 20-pin standard JTAG connector to use are:Pin 1 – VCC:This is the traget board Vcc. It is used by the STLINK/V2Pin 7 – TMS/SWDIO:The SWD Data signalPin 8 – GND:Be sure there is a common groundPin 9 – TCK/SWCLKThe SWD Clock SignalPin 15 – nSRST/RESETSystem reset – probably optional(你可以不要这个复位pin,直接关电源再上电来复位)ST-Link/V2 JTAG/SWD接口定义:可以自己做一些转接PCB板子,现在USB四线的可以用起来。

做一个现在智能手机usb接口,接四根线就好SWD不单单可以下载还可以单步调试,速度比JTAG快。

有人问,那为什么要发明JTAG这个20pin 的接口呢?因为JTAG标准制定不是为了下载程序调试程序用的,它用来做“边界扫描”用的,什么是边界扫描不知道的可以搜搜一些,在国内谷歌需要翻墙软件才好用。

百度搜索专业术语类不好用,最近我发现好多东西搜搜比百度好用不少。

JTAG接口

JTAG接口

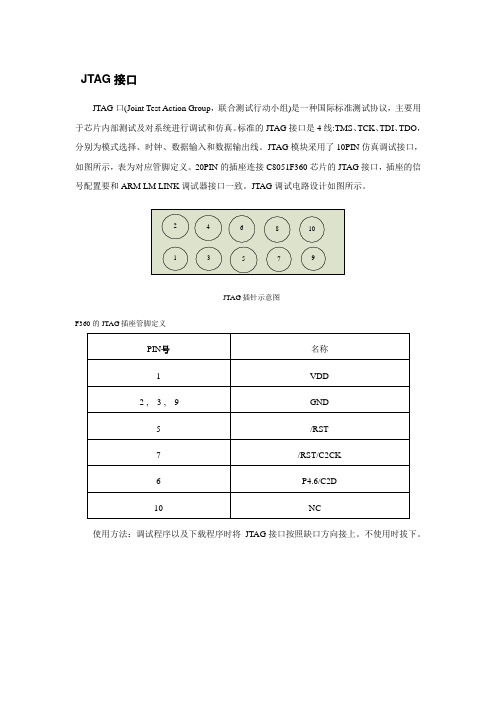

JTAG口(Joint Test Action Group,联合测试行动小组)是一种国际标准测试协议,主要用于芯片内部测试及对系统进行调试和仿真。

标准的JTAG接口是4线:TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。

JTAG模块采用了10PIN仿真调试接口,如图所示,表为对应管脚定义。

20PIN的插座连接C8051F360芯片的JTAG接口,插座的信号配置要和ARM LM LINK调试器接口一致。

JTAG调试电路设计如图所示。

136

79

248

5

10

JTAG插针示意图

F360的JTAG插座管脚定义

PIN号名称

1 VDD

2 ,

3 , 9 GND

5 /RST

7 /RST/C2CK

6 P4.6/C2D

10 NC

使用方法:调试程序以及下载程序时将JTAG接口按照缺口方向接上。

不使用时拔下。

JTAG与SWD接口的工作原理

何宾 2011.12

本章内容

本章主要介绍PSoC3的编程和调试接口功能,其 内容主要包括:

测试控制器的模块结构和连接器接口; JTAG和SWD接口的工作原理; PSoC3的JTAG和SWD接口的工作原理; 8051的片上调试模块(DoC); 非易失性存储器的编程。

位代码 0101

1010 1011 1000

1100

指令

PSoC3功能

CLASMP

DPACC APACC

将TDI和TDO连接到BYPASS寄存器,设置引脚到边界扫描 寄存器的当前内容

连接TDI和TDO到DP/AP寄存器,用于访问调试端口寄存器 连接TDI和TDO到DP/AP寄存器,用于访问访问端口寄存器

PSoC3 JTAG接口与IEEE1149.1-2001规范兼容,同 时提供了额外的指令。指令寄存器为4比特宽度。下表给 出了PSoC3额外的JTAG指令。

JTAG与SWD接口的工作原理 --PSoC3的JTAG和SWD接口的工作原理

位代码 1111 1110 0010

0000 0100

表 PSoC3额外的JTAG指令

2.10针连接器 如下图所示,10针连接器配置成双排,每针之间间隔

为50mil。

图 10针连接器

测试控制器

--连接器接口

表 不同通信协议的引脚分配

协议

信号

5针

10针

ISSP

SCLK

4

SDAT

5

XRES

3

JTAG

TMS

2

TCK

4

TDO

6

TDI

8

XRES

10

SWD/SWV

JTAG与SWD引脚对比

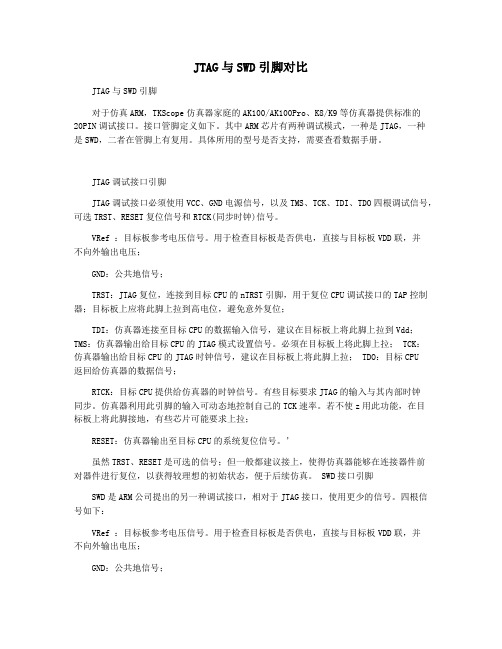

JTAG与SWD引脚对比JTAG与SWD引脚对于仿真ARM,TKScope仿真器家庭的AK100/AK100Pro、K8/K9等仿真器提供标准的20PIN调试接口。

接口管脚定义如下。

其中ARM芯片有两种调试模式,一种是JTAG,一种是SWD,二者在管脚上有复用。

具体所用的型号是否支持,需要查看数据手册。

JTAG调试接口引脚JTAG调试接口必须使用VCC、GND电源信号,以及TMS、TCK、TDI、TDO四根调试信号,可选TRST、RESET复位信号和RTCK(同步时钟)信号。

VRef :目标板参考电压信号。

用于检查目标板是否供电,直接与目标板VDD联,并不向外输出电压;GND:公共地信号;TRST:JTAG复位,连接到目标CPU的nTRST引脚,用于复位CPU调试接口的TAP控制器;目标板上应将此脚上拉到高电位,避免意外复位;TDI:仿真器连接至目标CPU的数据输入信号,建议在目标板上将此脚上拉到Vdd;TMS:仿真器输出给目标CPU的JTAG模式设置信号。

必须在目标板上将此脚上拉; TCK:仿真器输出给目标CPU的JTAG时钟信号,建议在目标板上将此脚上拉; TDO:目标CPU返回给仿真器的数据信号;RTCK:目标CPU提供给仿真器的时钟信号。

有些目标要求JTAG的输入与其内部时钟同步。

仿真器利用此引脚的输入可动态地控制自己的TCK速率。

若不使z用此功能,在目标板上将此脚接地,有些芯片可能要求上拉;RESET:仿真器输出至目标CPU的系统复位信号。

’虽然TRST、RESET是可选的信号;但一般都建议接上,使得仿真器能够在连接器件前对器件进行复位,以获得较理想的初始状态,便于后续仿真。

SWD接口引脚SWD是ARM公司提出的另一种调试接口,相对于JTAG接口,使用更少的信号。

四根信号如下:VRef :目标板参考电压信号。

用于检查目标板是否供电,直接与目标板VDD联,并不向外输出电压;GND:公共地信号;SWDIO:串行数据输入输出,作为仿真信号的双向数据信号线,建议上拉;SWCLK:串行时钟输入,作为仿真信号的时钟信号线,建议下拉;SWO:串行数据输出引脚,CPU调试接口可通过SWO引脚输出一些调试信息。

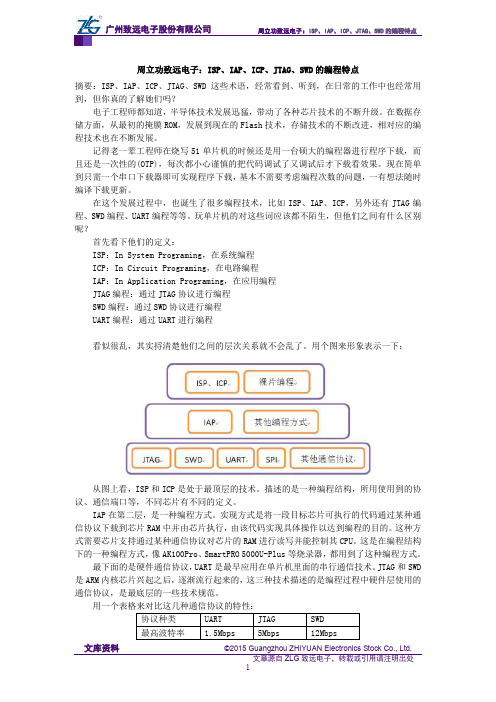

周立功致远电子:ISP、IAP、ICP、JTAG、SWD的编程特点

周立功致远电子:ISP、IAP、ICP、JTAG、SWD的编程特点摘要:ISP、IAP、ICP、JTAG、SWD这些术语,经常看到、听到,在日常的工作中也经常用到,但你真的了解她们吗?电子工程师都知道,半导体技术发展迅猛,带动了各种芯片技术的不断升级。

在数据存储方面,从最初的掩膜ROM,发展到现在的Flash技术,存储技术的不断改进,相对应的编程技术也在不断发展。

记得老一辈工程师在烧写51单片机的时候还是用一台硕大的编程器进行程序下载,而且还是一次性的(OTP),每次都小心谨慎的把代码调试了又调试后才下载看效果。

现在简单到只需一个串口下载器即可实现程序下载,基本不需要考虑编程次数的问题,一有想法随时编译下载更新。

在这个发展过程中,也诞生了很多编程技术,比如ISP、IAP、ICP,另外还有JTAG编程、SWD编程、UART编程等等。

玩单片机的对这些词应该都不陌生,但他们之间有什么区别呢?首先看下他们的定义:ISP:In System Programing,在系统编程ICP:In Circuit Programing,在电路编程IAP:In Application Programing,在应用编程JTAG编程:通过JTAG协议进行编程SWD编程:通过SWD协议进行编程UART编程:通过UART进行编程看似很乱,其实捋清楚他们之间的层次关系就不会乱了。

用个图来形象表示一下:从图上看,ISP和ICP是处于最顶层的技术。

描述的是一种编程结构,所用使用到的协议、通信端口等,不同芯片有不同的定义。

IAP在第二层,是一种编程方式。

实现方式是将一段目标芯片可执行的代码通过某种通信协议下载到芯片RAM中并由芯片执行,由该代码实现具体操作以达到编程的目的。

这种方式需要芯片支持通过某种通信协议对芯片的RAM进行读写并能控制其CPU。

这是在编程结构下的一种编程方式,像AK100Pro、SmartPRO 5000U-Plus等烧录器,都用到了这种编程方式。

Jtag的各种引脚定义

使用过ARM芯片的人肯定都听过一个仿真器————JLINK,为什么ARM芯片现在能够这么流行?其中恐怕就有一个原因就是很多的ARM芯片都支持使用Jlink进行调试和仿真。

所以你只要有一个Jlink,不管是ARM7、ARM9、ARM11还是最新的ARM Cortex 系统都能下载和调试了。

以前的嵌入式开发者,可能使用什么公司的芯片就得买一个对应芯片的下载和仿真器,这样如果你只使用一种芯片,可能还好,不过恐怕没有那种芯片能够一直引领市场。

Jlink使用的是一种叫做JTAG的协议,JTAG原本是用于芯片内部测试的,现在大多用于芯片的程序下载和调试仿真。

由于现在Jlink用的比较多,所以有些人可能把Jlink就等同于JTAG了,实际上,JTAG是一种协议,只要满足这种协议的就可以叫做JTAG,比如H—JTAG、OpenJTAG、OSJTAG等等。

正版的Jlink是卖的很贵的。

大概是1000到2000RMB吧。

不过,中国的山寨能力是很强的,而且你硬件卖给别人了,你也没办法控制别人说你不许拆开我的东西看里面的电路是怎么样的。

所以Jlink就被破解了,破解之后的Jlink很便宜,网上五六十块钱就能买到一个能用的Jlink。

除了商业版的Jlink和H—JTAG,网上还有一些电子爱好者,他们参照开源软件的模式,设计了开源硬件,比如arduino。

还有人制作了开源版本的JTAG仿真器——OpenJTAG。

而一些芯片的开发商不像那些软件厂商,会给软件做很多的限制,他们对于开源硬件还是比较开明的,所以他们也支持了一些开源硬件。

比如TI公司的MSP430 LaunchPad、ST公司的STM Discovery 等等板子。

还有飞思卡尔公司的USBDM和OSJTAG。

他们把这些硬件的原理图、PCB还有固件都放在了网络上供人自由下载和制作,你也可以根据他的资料进行改进。

这样能使大家对于他们家的芯片有更多的了解,所以,他们也乐于开源一些评估板。

ARM仿真器JLINK、ULINK使用SWD调试时的接线方式

ARM仿真器JLINK、ULINK使用SWD调试时的接线

方式

手头的仿真器是JLINK V8,连接STM32F103 时,使用SWD 方式。

JTAG 引脚示意图:

一、SWD 和传统的调试方式区别

1. SWD 模式比JTAG 在高速模式下面更加可靠

2. GPIO 刚好缺一个的时候, 可以使用SWD 仿真, 这种模式支持更少的引脚

3. 在板子的体积有限的时候推荐使用SWD 模式

二、仿真器对SWD 模式支持情况

1. 市面上的常用仿真器对SWD 模式支持情况

JLINKV8 非常好的支持SWD 仿真模式, 速度可以到10M

ULINK2 非常好的支持SWD 模式,速度可以达到10M

2. SWD 硬件接口上的不同

(1) JLINKV7 需要的硬件接口为: GND, RST, SWDIO, SWDCLK(2) JLINKV8 需要的硬件接口为: VCC, GND, RST, SWDIO, SWDCLK (注:下面有我自己用JLINKV8 的实际连线及相应实验结果)(3) ULINK1 不支持SWD 模式(4) ULINK2 需要的硬件接口为: GND, RST, SWDIO, SWDCLK

三、在MDK 中SWD 模式的设置

正常的JTAG 需要20 管脚,而J-Link 的SWD 只需要2 根线(PA13/JTMS/SWDIO、PA14/JTCK/SWCLK)就够了(加上电源线也就4 根),这样就节省了3 个I/O 口(PA15/JTDI、PB3/JTDO、PB4/JNTRST)为其它所用,并且可节省一部分板子的空间(只需4 个口就可以了)。

jtag接口

JTAG接口1. 简介JTAG(Joint Test Action Group,联合测试行动小组)接口是一种用于测试和调试电子设备的标准接口。

它可以提供对设备内部的信号和状态进行非侵入性访问,方便测试和调试工作的进行。

2. JTAG接口的原理JTAG接口基于IEEE 1149.1标准而设计,通常由以下几个主要部分组成:2.1 TAP控制器TAP(Test Access Port,测试访问端口)控制器是JTAG接口的核心部分,它负责控制JTAG链上的各个设备进行测试和调试操作。

TAP控制器包含四个主要状态:Test-Logic-Reset (测试逻辑复位)、Run-Test/Idle(运行测试/空闲)、Select-DR-Scan(选择数据寄存器扫描)和 Select-IR-Scan(选择指令寄存器扫描)。

2.2 数据寄存器和指令寄存器JTAG接口通过数据寄存器和指令寄存器实现对设备内部信息的读取和写入。

数据寄存器用于存储设备内部的数据,指令寄存器用于存储控制设备的指令。

2.3 JTAG链JTAG链是由多个设备连接在一起形成的链路,每个设备都有一个JTAG接口用于进行测试和调试操作。

通过JTAG链,可以对所有设备进行统一的控制和访问。

3. JTAG接口的应用JTAG接口广泛应用于电子设备的测试和调试领域。

它可以用于以下几个主要方面:3.1 片上自检(BIST)JTAG接口可以用于进行片上自检(Built-In Self-Test,BIST)操作,通过读取和分析测试模式下设备内部的信号和状态,检测设备是否正常工作。

3.2 调试模式JTAG接口可以进入设备的调试模式,可以对设备进行单步调试、断点调试等操作,方便开发人员进行程序调试和故障排查。

3.3 仿真和验证JTAG接口还可以用于仿真和验证工作。

通过JTAG接口,可以将外部测试模式下的信号加载到设备内部进行仿真和验证工作。

4. JTAG接口的优势与其他调试和测试接口相比,JTAG接口具有以下几个显著的优势:4.1 非侵入性访问JTAG接口可以在不破坏原有电路功能的情况下,对设备内部信号进行读取和分析。

下载调试接口JTAGvsSWD

下载调试接口JTAGvsSWD作为嵌入式工程师,下载调试器都应该知道,但你真正了解其SWD 和 JTAG接口的含义和区别吗?什么是下载调试器简单来说,下载调试器是将PC(例如通过USB协议)发送的命令转换为MCU(负责MCU内部外围设备)理解的语言(例如SWD或JTAG协议)的设备,加载代码并精确控制执行。

调试器协议标准1.什么是标准?简单来说,标准是一组规则和协议,特定行业中的每个参与者都同意遵循并执行。

2.调试器协议混乱现象在SWD和JTAG之类的协议出现之前,调试器及其协议一片混乱,每个MCU制造商都提出了自己的专有方法,将代码加载到他们的MCU上。

制造商每次发布MCU时,嵌入式软件工程师都需要了解其专有协议,以将代码加载到微控制器中。

而且,调试适配器很昂贵,因为制造商实际上并没有竞争者可以使调试适配器与他们的协议相匹配,因为协议是专有的。

它们昂贵的另一个原因是由于体积不足,因为它们只能将调试适配器出售给使用它们制造的MCU的公司(工程师)。

不同协议还会导致开发成本增加,比如:你在设计的板上有来自4个不同制造商的4种芯片,并且希望对其进行一些自动化测试以提高生产过程的效率。

但是,由于所有电路板都有自己的协议,因此您需要制作一个能适应复杂性的超级复杂的生产代码,并且需要在电路板上的测试点安装4个不同的调试器,从而增加了成本,生产时间和编程时间。

3.制定协议各种下载调试不同会导致几个问题:•投入更多的学习时间•增加购买下载调试的成本•生成测试效率低下为了解决这一问题,各大MCU制造和生产商的工程师们就针对调试制定了一些规范协议。

JTAG标准JTAG:Joint Test Action Group,即联合测试行动小组。

该小组于1980年后期开始讨论,并于1990年正式发布了解释IEEE标准的文档。

(IEEE代表电气与电子工程师协会,是一个国际组织,其中发布了所有标准,如WiFi,蓝牙等)。

他们提出的协议在1990年被记录在IEEE 1149.1中。

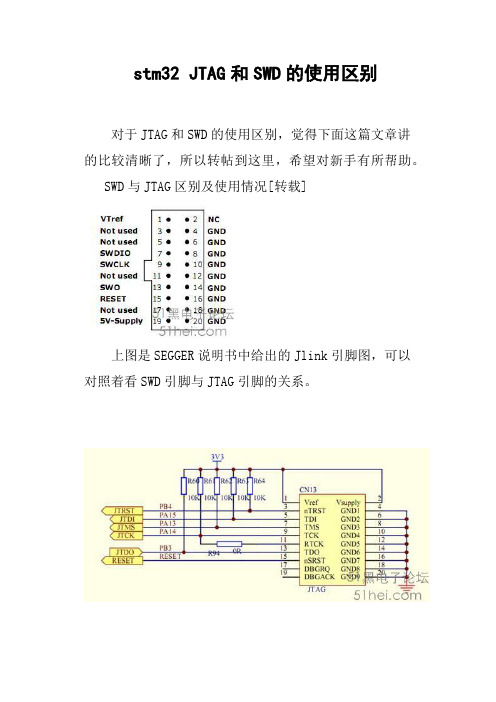

stm32JTAG和SWD的使用区别

stm32 JTAG和SWD的使用区别对于JTAG和SWD的使用区别,觉得下面这篇文章讲的比较清晰了,所以转帖到这里,希望对新手有所帮助。

SWD与JTAG区别及使用情况[转载]上图是SEGGER说明书中给出的Jlink引脚图,可以对照着看SWD引脚与JTAG引脚的关系。

这是我手边开发板上的JTAG连接图,这个肯定是能用的。

这个是从网上找来的标准的JTAG连接图,供对照参考。

调试方式既可以用JTAG,也可以用SWD。

以下是一段转自:(showvi)SWD 仿真模式概念简述一、SWD 和传统的调试方式区别1. SWD 模式比 JTAG 在高速模式下面更加可靠。

在大数据量的情况下面 JTAG 下载程序会失败, 但是SWD 发生的几率会小很多。

基本使用 JTAG 仿真模式的情况下是可以直接使用 SWD 模式的, 只要你的仿真器支持。

所以推荐大家使用这个模式。

2. 在大家 GPIO 刚好缺一个的时候, 可以使用 SWD 仿真, 这种模式支持更少的引脚。

3. 在大家板子的体积有限的时候推荐使用 SWD 模式, 它需要的引脚少, 当然需要的 PCB 空间就小啦!比如你可以选择一个很小的 2.54 间距的 5 芯端子做仿真接口。

二、仿真器对 SWD 模式支持情况1. 市面上的常用仿真器对 SWD 模式支持情况(1) JTAGV6 支持 SWD 仿真模式,速度较慢。

(2) JTAGV7 比较好的支持 SWD 仿真模式, 速度有了明显的提高,速度是 JTAGV6 的 6 倍。

(3) JTAGV8 非常好的支持 SWD 仿真模式, 速度可以到10M。

(4) ULINK1 不支持 SWD 模式。

(5) 盗版 ULINK2 非常好的支持 SWD 模式,速度可以达到 10M。

(6) 正版 ULINK2 非常好的支持 SWD 模式,速度可以达到 10M。

2. SWD 硬件接口上的不同(1) JTAGV6 需要的硬件接口为: GND, RST, SWDIO, SWDCLK(2) JTAGV7 需要的硬件接口为: GND, RST, SWDIO, SWDCLK(3) JTAGV8 需要的硬件接口为: VCC, GND, RST, SWDIO, SWDCLK (注:下面有我自己用JTAGV8的实际连线及相应实验结果)(4) ULINK1 不支持 SWD 模式(5) 盗版 ULINK2 需要的硬件接口为: GND, RST, SWDIO, SWDCLK(6) 正版 ULINK2 需要的硬件接口为: GND, RST, SWDIO, SWDCLK由此可以看到只有 JTAGV8 需要 5 个引脚,即多了一个VCC引脚,其好处是: 仿真器对目标板子的仿真需要用到 RST 引脚, 使用仿真器内部的 VCC 作这个功能其实并不是非常美妙。

SWD协议学习

SWD协议学习协议名称:SWD协议学习一、引言SWD(Serial Wire Debug)协议是一种用于嵌入式系统调试的串行通信协议。

本协议旨在提供详细的学习指南,帮助初学者了解SWD协议的基本原理、通信流程以及相关的技术细节。

二、背景在嵌入式系统开发过程中,调试是一个重要的环节。

SWD协议作为一种调试接口,为开发人员提供了一种快速、高效的调试方式。

通过SWD协议,开发人员可以在目标芯片上进行非侵入式的调试操作,包括读取寄存器、修改内存值、单步执行等。

三、SWD协议基本原理1. SWD接口SWD接口由两根线组成,分别是SWDIO(Serial Wire Data Input/Output)和SWCLK(Serial Wire Clock)。

SWDIO用于数据传输,SWCLK用于时钟同步。

2. 通信模式SWD协议支持两种通信模式:JTAG模式和SWD模式。

其中,SWD模式是一种简化的模式,占用的引脚更少,速度更快。

3. 通信流程SWD协议的通信流程如下:- 初始化:主机发送初始化序列,包括发送复位信号和读取IDCODE等操作。

- 读写操作:主机发送读写请求,包括读取寄存器、修改内存值等操作。

- 时钟同步:主机通过SWCLK信号与目标芯片进行时钟同步。

- 数据传输:主机通过SWDIO信号与目标芯片进行数据传输。

四、SWD协议技术细节1. 帧结构SWD协议的数据传输以帧为单位,每个帧包含一个起始位、一个数据位和一个校验位。

2. 时序要求SWD协议的时序要求包括时钟周期、数据传输时序和状态转换时序等。

在实际应用中,需要根据目标芯片的规格书来确定具体的时序要求。

3. 错误处理SWD协议中定义了多种错误码,用于表示通信过程中可能出现的错误情况。

在实际应用中,需要根据错误码来进行相应的错误处理。

五、SWD协议学习方法1. 学习资料学习SWD协议可以参考以下资料:- ARM Debug Interface Architecture Specification- Cortex-M系列处理器技术参考手册- 目标芯片的调试接口规格书2. 实践操作通过实践操作,可以更好地理解SWD协议的工作原理。

jtag各类接口针脚定义含义以及swd接线方式

JTAG各类接口针脚定义、含义以及SWD接线方式JTAG有10pin的、14pin的和20pin的,尽管引脚数和引脚的排列顺序不同,但是其中有一些引脚是一样的,各个引脚的定义如下。

一、引脚定义Test Clock Input (TCK) -----强制要求1TCK在IEEE1149.1标准里是强制要求的。

TCK为TAP的操作提供了一个独立的、基本的时钟信号,TAP的所有操作都是通过这个时钟信号来驱动的。

Test Mode Selection Input (TMS) -----强制要求2TMS信号在TCK的上升沿有效。

TMS在IEEE1149.1标准里是强制要求的。

TMS信号用来控制TAP状态机的转换。

通过TMS信号,可以控制TAP在不同的状态间相互转换。

Test Data Input (TDI) -----强制要求3TDI在IEEE1149.1标准里是强制要求的。

TDI是数据输入的接口。

所有要输入到特定寄存器的数据都是通过TDI接口一位一位串行输入的(由TCK驱动)。

Test Data Output (TDO) -----强制要求4TDO在IEEE1149.1标准里是强制要求的。

TDO是数据输出的接口。

所有要从特定的寄存器中输出的数据都是通过TDO接口一位一位串行输出的(由TCK驱动)。

Test Reset Input (TRST) ----可选项1这个信号接口在IEEE 1149.1标准里是可选的,并不是强制要求的。

TRST可以用来对TAPController进行复位(初始化)。

因为通过TMS也可以对TAP Controll进行复位(初始化)。

所以有四线JTAG与五线JTAG之分。

(VTREF) -----强制要求5接口信号电平参考电压一般直接连接Vsupply。

这个可以用来确定ARM的JTAG接口使用的逻辑电平(比如3.3V还是5.0V?)Return Test Clock ( RTCK) ----可选项2可选项,由目标端反馈给仿真器的时钟信号,用来同步TCK 信号的产生,不使用时直接接地。

JTAG接口

在Debug模式下,ARM内核的时钟从系统的主时钟 (MCLK)被替换成跟踪时钟(DCLK)。

跟踪时钟(DCLK)是通过在JTAG的状态机的 Run-test/Idle状态的TCK来控制的。

28

3.4.7 ARM7TDMI断点的设置

横 向

I2

0 X0

I 待测装置 O

0 X0

Pin

Logic

Logic

O1

Pin

O2

Pin

I3

Pin

0 X0

I

Logic

输入数据 输出数据

TCK TDI

101010

扫描前的输入数据

O

Logic

0 X0

O3

Pin

TDO

XXXXXX

扫描后的输出数据

18

JTAG处于挂起状态

I1

1 X1

DUT

0 X0

O1

(测试器件)

29

硬件断点和软件断点

在ARM7TDMI处理器的内核中,有两种断点的设置方式: 硬件断点和软件断点

硬件断点 通过设置EmbeddedICE中的Watchpoint寄存器中的地 址相关的寄存器,来实现断点。 通过这种方式设置断点,断点数目受EmbeddedICE中 的Watchpoint数目的限制(在ARM7TDMI处理器的内 核中,只有两组Watchpoint寄存器,最多只能设置两 个硬件断点)。 硬件断点可以在任何地方设置。不受存储器类型的限 制。

Channel)。

26

Watchpoint寄存器的使用

EmbeddedICE的一个主要作用就是可以在ARM的程序 中设置软件或者硬件的断点。

JTAG调试接口与Silicon IDE【精选】

• 串口选择

– EC2选RS232 – EC5选USB

• 调试接口

– F3xx、F4xx等选C2 – F00x、F02x等选JTAG

设置通信接口

• 在菜单栏中点击“Options” 选项,在其下拉子菜单中点击 “Connection Options …” 选 项,出现如图对话框,进行如下 设置:

JTAG调试接口

• C8051Fxxx 单片机具有片内 JTAG接口 和调试电 路

• 通过 4 脚 JTAG (或两脚C2)接口经JTAG仿真 器可对应用系统进行程序下载和非侵入式、全速 的在系统调试。

• 调试系统支持观察和修改存储器和寄存器,支持 断点、观察点、堆栈指示器和单步执行。

• 调试时不需要额外的目标 RAM、程序存储器、定 时器或通信通道,并且所有的模拟和数字外设都 正常工作。

硬件连接及通信接口配置

• 用串行电缆连接PC 机和EC5 • 用JTAG 扁平电缆连接EC5 和目标硬件 • 在IDE (Options/Connection Options…) 菜单选项卡中选

择适当的串行口

– RS232 Serial Adapter (EC2)

• COMPORT: COM1,COM2,COM3,COM4

• 集成了代码编写功能、编译功能、调试功 能的一体化开发软件包。

Silicon IDE

• Silicon集成开发环境(IDE)是一套完整独立 的软件程序它为设计者提供了用于开发和 测试项目的所有工具。

• Silicon集成开发环境(IDE)本身不带汇编器、 编译器和链接器使用外部汇编器、编译器 和链接器(keil51)。

置程序。 • 将生成的程序粘贴到源程序中。

JLink、JTAG接口详细图解

JLink、JTAG接口详细图解DBGACK-This pin is connected in the RVI run control unit, but is not supported in the current release of the software. It is reserved for compatibility with other equipment to be used as a debug acknowledge signal from the target system. It is recommended that this signal is pulled LOW on the target.DBGRQ-This pin is connected in the RVI run control unit, but is not supported in the current release of the software. It is reserved for compatibility with other equipment to be used as a debug request signal to the target system. The RVI software maintains this signal as LOW.When applicable,RVI uses the scan chain 2 of the processor to put the processor in debug state. It is recommended that this signal is pulled LOW on the target.GND-Ground.nSRSTInput/outputActive Low output from RVI to the target system reset, with a 4.7kΩ pull-up resistor for de-asserted state. This is also an input to RVI so that a reset initiated on the target can be reported to the debugger.This pin must be pulled HIGH on the target to avoid unintentional resets when there is no connection.nTRSTOutputActive Low output from RVI to the Reset signal on the target JTAG port, driven to the VTref voltage for de-asserted state. This pin must be pulled HIGH on the target to avoid unintentional resets when there is no connection.RTCKInputReturn Test Clock signal from the target JTAG port to RVI. Some targets must synchronize the JTAG inputs to internal clocks. To assist in meeting this requirement, you can use a returned, and retimed, TCK to dynamically control the TCK rate. RVI provides Adaptive Clock Timing, that waits for TCK changes to be echoed correctly before making more changes. Targets that do not have to process TCK can ground this pin.RTCK is not supported in Serial Wire Debug (SWD) mode.TCKOutputTest Clock signal from RVI to the target JTAG port. It is recommended that this pin is pulled LOW on the target.TDIOutputTest Data In signal from RVI to the target JTAG port. It is recommended that this pin is pulled HIGH on the target.TDOInputTest Data Out from the target JTAG port to RVI. It is recommended that this pin is pulled HIGH on the target.TMSOutputTest Mode signal from RVI to the target JTAG port. This pin must be pulled HIGH on the target so that the effect of any spurious TCK s when there is no connection is benign.VsupplyInputThis pin is not connected in the RVI unit. It is reserved for compatibility with other equipment to be used as a power feed from the target system.VTrefInputThis is the target reference voltage. It indicates that the target has power, and It must be at least 0.628V. VTref is normally fed from V dd on the target hardware and might have a series resistor (though this is not recommended). There is a 10kΩ pull-down resistor on VTref in RVI.。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

JTAG接口由:

测试数据输入(TDI); 测试数据输出(TDO); 测试模式选择(TMS); 测试时钟信号(TCK)和其它信号构成。

下图给出了JTAG连接多个IC芯片的结构。

第5章 PSoC编程和调试接口功能

何宾 2011.12

本章内容

本章主要介绍PSoC3的编程和调试接口功能,其 内容主要包括:

测试控制器的模块结构和连接器接口; JTAG和SWD接口的工作原理; PSoC3的JTAG和SWD接口的工作原理; 8051的片上调试模块(DoC); 非易失性存储器的编程。

JTAG与SWD接口的工作原理 --JTAG工作原理

下图给出了JTAG接口的内部结构。

图 JTAG内部结构

JTAG与SWD接口的工作原理 --JTAG工作原理

如下图,TMS信号控制TAP的状态机,状态机控制 哪个寄存器(包括边界扫描通路)在TDI-TDO移位通 路上。

图 TAP状态机

JTAG与SWD接口的工作原理 --JTAG工作原理

这个解决方案就是后来的IEEE1149.1-2001标准, 这个标准基于一个概念,即使用一个布线贯穿所有IC引 脚的移位寄存器(这也叫做边界扫描)。每个引脚上都 有一个边界扫描单元。在PSoC3中,大部分的GPIO和 SIO端口引脚都有边界扫描单元。

JTAG与SWD接口的工作原理 --JTAG工作原理

TAP内的寄存器包含:

1)Instruction:2-4位宽,存放当前指令,该指令定义了在 TDI-TDO移位通道上的数据寄存器,引起设备被旁路用于 JTAG模式;

2)Bypass:1位宽度,TDI和TDO直接连接; 3)ID:32位宽,用于读JTAG的制造商/芯片的ID号; 4)Boundary Scan Path(BSR):宽度等于I/O引脚(有边

调试操作;

测试控制器 --测试控制器模块结构

如下图,PSoC3测试控制器将JTAG或者SWD访问转 换成DoC模块内寄存器的访问。

图 PSoC3测试控制器模块图

测试控制器 --连接器接口

1.5针连接器 如下图所示,5针连接器配置成单排,每针之间间隔

为100mil。

图 5针连接器

测试控制器 --连接器接口

支持到调试主机的JTAG或者SWD接口; SWD接口可以使用GPIO或者USB引脚; 支持边界扫描IEEE标准1149.1-2001“Test Access Port and

Boundary-Scan Architecture”; 支持额外的JTAG指令/寄存器,用于访问芯片的剩余部分; 与PSoC3的调试模块接口用于访问芯片的剩余部分用于编程和

界扫描单元)的数量,用于设置或者读写这些I/O引脚的状 态;

JTAG与SWD接口的工作原理 --JTAG工作原理

在IEEE1149中,给出了标准的指令集: 1)EXTEST:该指令将使得TDI和TDO连接到边界扫

描通路上(BSR),芯片将从普通操作模式改变为测试模 式。芯片引脚的状态可以使用capture dr的JTAG状态进行 采样,使用updata dr状态新的值可以用于芯片引脚上。

JTAG与SWD接口的工作原理 --SWD工作原理

SWD接口是由ARM公司开发出来的,目的是减少 调试接口所使用的引脚数。SWD接口使用两个信号 线:双向的数据线(SWDIO)和用于数据线的时钟信 号(SWDCK)。

JTAG与SWD接口的工作原理 --JTAG工作原理

2)SAMPLE:该指令将使得TDI和TDO连接到边 界扫描通路上(BSR),但是芯片仍然处于普通操作模 式。使用该指令,BSR可以使用capture dr的JTAG状态进 行读取,对进入的功能数据进行采样,然后移出芯片。 3)PERLOAD:该指令将使得TDI和TDO连接到边 界扫描通路上(BSR),但是芯片仍然处于普通操作模 式。该指令用于在加载EXTEST指令前,预加载测试数 据到BSR。

JTAG与SWD接口的工作原理 --JTAG工作原理

下面给出了可选的指令: 1)IDCODE:该指令使得TDI和TDO线连接到

IDCODE寄存器。 2)INTEST:该指令将使得TDI和TDO连接到边界

扫描通路上(BSR)。当EXTEST指令允许访问芯片引脚 时,INTEST能访问芯片内核逻辑的信号。

6

XRES

3

10

I2C

SCK

4

SDA

5

JTAG与SWD接口的工作原理 --JTAG工作原理

为了应对IC芯片日益增加的高引脚密度,联合行 动测试小组(Joint Test Action Group,JTAG)提供了一 个用于测试电路板的方法,这个方法就是通过一个独立 的测试接口来控制IC的引脚(和读取它们的值)。

测试控制器 --测试控制器模块结构

PSoC3结构包括一个测试控制器,主要用于下面 的目的:

用于边界扫描测试访问I/O引脚; 通过PSoC3的片上调试DoC模块来访问芯片的存储器和寄存

器。

测试控制器 --测试控制器模块结构

测试控制器通过边界扫描端口(Joint Test Action Group,JTAG)或者串行调试(Serial Wire Debug, SWD)接口连接到片外设备。测试控制器包含下面的特 性:

其中:

1)ir:是指令寄存器; 2)dr:其它寄存器中的一个(包括边界扫描路径),由指

令寄存器的内容确定; 3)capture:将dr寄存器的内容传输到移位寄存器中,然后

移出TDO; 4)update:传输移位寄存器的内容,从TDI移入到一个dr;

JTAG与SWD接口的工作原理 --JTAG工作原理

2.10针连接器 如下图所示,10针连接器配置成双排,每针之间间隔

为50mil。

图同通信协议的引脚分配

协议

信号

5针

10针

ISSP

SCLK

4

SDAT

5

XRES

3

JTAG

TMS

2

TCK

4

TDO

6

TDI

8

XRES

10

SWD/SWV

SDIO

5

2

SCK

4

4

SWV