数电仿真实验报告

数字电路仿真实验实验报告

表(1)逻辑与门输入输出关系

A

B

Y

0

00Biblioteka 1101

1

所以逻辑与门的输入输出关系如式(1)所示。

式(1)

2.测试逻辑与非门的输入输出关系

……

3.测试XXX的输入输出关系

……

数字电路仿真实验实验报告

实验名称

基本逻辑门的使用

学生姓名

学生学号

一、实验目的

1.使用Tina软件测试基本逻辑门电路的输入输出关系,掌握与门、与非门、或门、或非门、非门等常用逻辑门的逻辑关系。

2.熟悉Tina软件的操作环境,掌握逻辑电路的画图和功能测试方法。

二、实验内容

1.测试逻辑与门的输入输出关系

测试电路如图(1)所示,测试结果如表(1)所示。

数电仿真实验报告

数电仿真实验报告数字电路仿真实验报告引言:数字电路仿真实验是电子信息类专业学生在学习数字电路原理与设计课程中的一项重要实践环节。

通过仿真实验,学生可以进一步加深对数字电路的理解,掌握数字电路的设计方法和仿真工具的使用。

本文将结合具体的实验案例,介绍数字电路仿真实验的目的、原理、实验步骤和实验结果。

一、实验目的本次实验的目的是通过使用仿真软件,设计并验证一个简单的数字电路电路原理图,了解数字电路仿真的基本流程,掌握仿真软件的使用方法,并通过仿真结果验证设计的正确性。

二、实验原理数字电路仿真实验是通过计算机软件模拟电路的运行过程,以验证电路设计的正确性。

仿真软件可以模拟电路的输入和输出波形,以及电路中各个元件的工作状态。

在数字电路仿真实验中,我们主要使用Verilog HDL(硬件描述语言)来描述电路结构和功能,并通过仿真软件进行仿真。

三、实验步骤1. 确定实验电路的功能和结构,绘制电路原理图;2. 使用Verilog HDL编写电路的结构描述和功能描述;3. 使用仿真软件加载Verilog HDL代码,并设置仿真参数;4. 运行仿真软件,观察并分析仿真结果;5. 根据仿真结果,对电路进行调试和优化,直至达到预期的功能和性能。

四、实验案例以设计一个4位二进制加法器为例,介绍数字电路仿真实验的具体步骤和过程。

1. 确定实验电路的功能和结构:4位二进制加法器是由4个全加器组成的,每个全加器有两个输入和两个输出。

输入包括两个4位二进制数和一个进位信号,输出为一个4位二进制数和一个进位信号。

2. 绘制电路原理图:根据功能和结构确定电路原理图,将4个全加器按照一定的连接方式组合在一起,形成4位二进制加法器的电路原理图。

3. 使用Verilog HDL编写电路的结构描述和功能描述:根据电路原理图,使用Verilog HDL编写电路的结构描述和功能描述。

结构描述包括各个元件的连接方式和引脚定义,功能描述包括各个元件的逻辑运算和信号传递。

数字逻辑 数字电路仿真实验报告

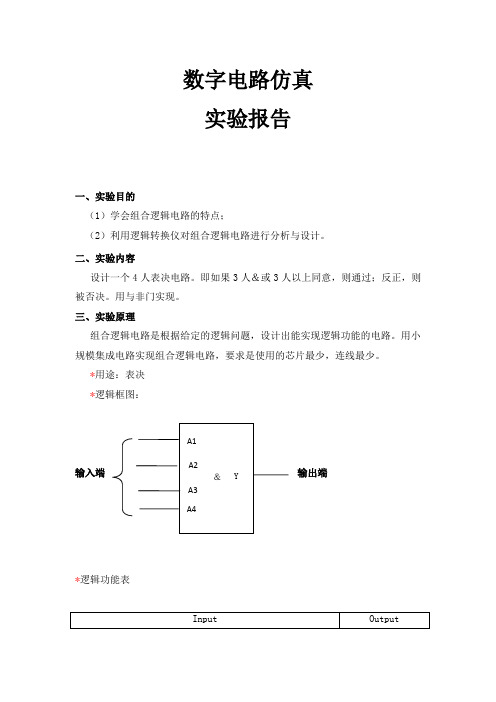

数字电路仿真 实验报告一、实验目的(1)学会组合逻辑电路的特点;(2)利用逻辑转换仪对组合逻辑电路进行分析与设计。

二、实验内容设计一个4人表决电路。

即如果3人&或3人以上同意,则通过;反正,则被否决。

用与非门实现。

三、实验原理组合逻辑电路是根据给定的逻辑问题,设计出能实现逻辑功能的电路。

用小规模集成电路实现组合逻辑电路,要求是使用的芯片最少,连线最少。

*用途:表决 *逻辑框图: 输入端 输出端*逻辑功能表InputOutputA1A2A3 A4 & YA1 A2 A3 A4Sum 1000 (任意顺序,只在乎最后结果) >30 1100(任意顺序,只在乎最后结果) 1110(任意顺序,只在乎最后结果) >=311111(任意顺序,只在乎最后结果)电平的个数之和,其和小于3则输出0,表决不成功,其和大于或者等于3则输出1,表决成功。

*逻辑框图:*逻辑功能表inputs and sum output A1 sum A2 sum A3 sumA4 sum 1112 1314 1输入端0 3 10 2 1 3 1 0 2 00 1 1 21 3 10 2 00 11 2 00 1 00 0 1 11 21 3 10 2 00 11 2 00 1 00 01 11 2 00 1 00 01 1 00 0 0输入的数据依次相加,若最后和的结果大于等于3则输出1,否则输出0四、实验步棸1、编写源代码。

(1)打开QuartusⅡ软件平台,点击File中得New Project新建工程,将工程名称建得跟文件夹名称一样为ren。

在File 中New建立一个VHDL文件。

VHDL语言设计如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY ren ISPORT (A1,A2,A3,A4:IN STD_LOGIC;Y:OUT STD_LOGIC);END;ARCHITECTURE bhv OF ren ISBEGINPROCESS(A1,A2,A3,A4)VARIABLE SUM:INTEGER RANGE 0 TO 4;BEGINSUM:=0;IF A1='1'THEN SUM:=SUM+1;END IF;IF A2='1'THEN SUM:=SUM+1;END IF;IF A3='1'THEN SUM:=SUM+1;END IF;IF A4='1'THEN SUM:=SUM+1;END IF;IF SUM>=3 THEN Y<='1';ELSE Y<='0';END IF;END PROCESS;END;(2)点击File/Save as以“.vhd”为扩展名存盘文件,命名为“ren.vhd”,保存时勾选“Add file to current file”选项。

数字电路仿真实训实验报告

课程设计(大作业)报告课程名称:数字电子技术课程设计设计题目:多功能数字时钟的设计、仿真院系:信息技术学院班级:二班设计者:张三学号:79523指导教师:张延设计时间:2011年12月19日至12月23日信息技术学院昆明学院课程设计(大作业)任务书一、设计目的为了熟悉数字电路课程,学习proteus软件的使用,能够熟练用它进行数字电路的仿真设计,以及锻炼我们平时独立思考、善于动手操作的能力,培养应对问题的实战能力,提高实验技能,熟悉复杂数字电路的安装、测试方法,掌握关于多功能数字时钟的工作原理,掌握基本逻辑们电路、译码器、数据分配器、数据选择器、数值比较器、触发器、计数器、锁存器、555定时器等方面已经学过的知识,并能够将这些熟练应用于实际问题中,我认真的动手学习了数字时钟的基本原理,从实际中再次熟悉了关于本学期数字电路课程中学习的知识,更重要的是熟练掌握了关于proteus软件的使用,收获颇多,增强了自己的工程实践能力。

另外,数字钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更更长的使用寿命,因此得到了广泛的使用。

数字钟从原理上讲是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。

因此,我们此次设计数字钟就是为了了解数字钟的原理,从而学会制作数字钟。

而且通过数字钟的制作进一步的了解各种在制作中用到的中小规模集成电路的作用及实用方法。

且由于数字钟包括组合逻辑电路和时叙电路。

通过它可以进一步学习与掌握各种组合逻辑电路与时序电路的原理与使用方法。

二、设计要求和设计指标设计一个数字时钟,具有“秒”、“分”、“时”计时和显示功能。

小时以24小时计时制计时;具有校时功能,能够对“分”、“时”进行调整;能够进行整点报时,报时规则为:在59Min51s后隔秒发出500Hz的低音报时信号,在59min59s时发出1kHz的高音报时信号,声响持续1s。

数电仿真实验报告

数电仿真实验报告

《数电仿真实验报告》

实验目的:

本次实验的目的是通过数电仿真软件进行数字电路的设计和仿真,以加深对数字电路原理的理解,并掌握数字电路设计和仿真的基本方法。

实验内容:

本次实验分为两个部分:第一部分是基本逻辑门的设计和仿真,包括与门、或门、非门等;第二部分是组合逻辑电路的设计和仿真,包括多路选择器、加法器等。

实验步骤:

1. 打开数电仿真软件,创建新的仿真项目。

2. 依次设计并仿真与门、或门、非门等基本逻辑门,观察输入输出关系。

3. 设计并仿真多路选择器、加法器等组合逻辑电路,验证其功能和正确性。

4. 对仿真结果进行分析和总结,发现问题并进行修正。

实验结果:

通过数电仿真软件的实验,我们成功设计和仿真了各种基本逻辑门和组合逻辑电路,并且验证了其功能和正确性。

在实验过程中,我们发现了一些问题并进行了修正,最终得到了满意的结果。

实验总结:

本次实验通过数电仿真软件进行数字电路的设计和仿真,使我们对数字电路原理有了更深入的理解,并掌握了数字电路设计和仿真的基本方法。

同时,也锻炼了我们的动手能力和分析问题的能力。

相信通过这次实验,我们对数字电路

的理解会更加深入,为以后的学习和工作打下坚实的基础。

通过这次实验,我们不仅学会了如何使用数电仿真软件进行数字电路的设计和仿真,还加深了对数字电路原理的理解,为以后的学习和工作打下了坚实的基础。

希望通过不断的实践和学习,我们能够更加深入地理解数字电路的原理,并能够应用到实际的工程项目中去。

数字电路仿真报告

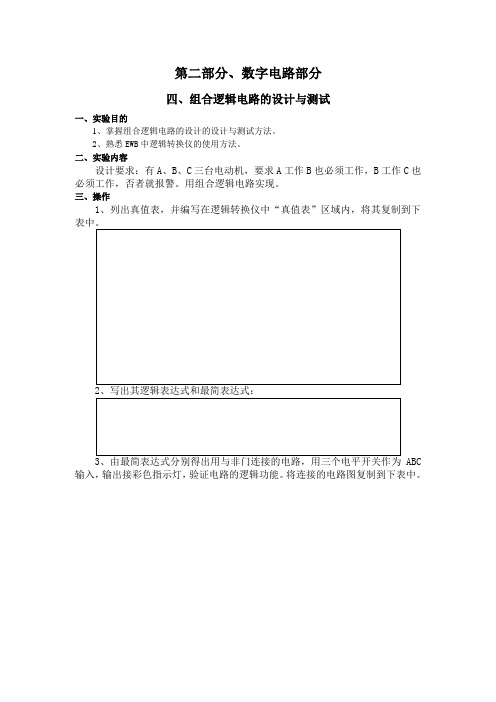

第二部分、数字电路部分四、组合逻辑电路的设计与测试一、实验目的1、掌握组合逻辑电路的设计的设计与测试方法。

2、熟悉EWB中逻辑转换仪的使用方法。

二、实验内容设计要求:有A、B、C三台电动机,要求A工作B也必须工作,B工作C也必须工作,否者就报警。

用组合逻辑电路实现。

三、操作1、列出真值表,并编写在逻辑转换仪中“真值表”区域内,将其复制到下ABC 输入,输出接彩色指示灯,验证电路的逻辑功能。

将连接的电路图复制到下表中。

五、触发器及其应用一、实验目的1、掌握基本JK、D等触发器的逻辑功能的测试方法。

2、熟悉EWB中逻辑分析仪的使用方法。

二、实验内容1、测试D触发器的逻辑功能。

2、触发器之间的相互转换。

3、用JK触发器组成双向时钟脉冲电路,并测试其波形。

三、操作1、D触发器在输入信号为单端的情况下,D触发器用起来最为方便,其状态方程为nn D+1Q=其输出状态的更新发生在CP脉冲的上升沿,故又称为上升沿触发的边沿触发器。

图2.5.1为双D 74LS74的引脚排列及逻辑符号。

图2.5.1 74LS74的引脚排列及逻辑符号在EWB中连接电路如图2.5.2所示,记录表2.5.1的功能表。

图2.5.2在集成触发器的产品中,每一种触发器都有自己固定的逻辑功能。

但可以利用转换的方法获得具有其它功能的触发器。

在T ′触发器的CP 端每来一个CP 脉冲信号,触发器的状态就翻转一次,故称之为反转触发器,广泛用于计数电路中,其状态方程为:1nn Q Q +=。

同样,若将D 触发器Q 端与D 端相连,便转成T ′触发器。

如图2.5.3所示。

QQ图2.5.3 D 转成T ′在EWB 中连接电路如图2.5.4所示,测试其功能。

图2.5.4 D 转成T ′触发器3、双向时钟脉冲电路的测试。

①、按图2.5.5用JK 触发器和与非门组成双向时钟脉冲电路。

图2.5.5Q、CPA、CPB接入逻辑分析仪的输入端,把设②、CP用10Hz时钟源,将CP、Q、③、在逻辑分析仪面板中设置内时钟频率为100Hz,把逻辑分析仪显示波形复制到下六计数器和译码显示电路的应用一、实验验目的1、掌握中规模集成计数器的使用及其功能测试方法。

数字电路实训报告

一、设计目的及要求:(一)实验目的:1. 通过实验培养学生的市场素质,工艺素质,自主学习的能力,分析问题解决问题的能力以及团队精神。

2. 通过本实验要求学生熟悉各种常用中规模集成电路组合逻辑电路的功能与使用方法,学会组装和调试各种中规模集成电路组合逻辑电路,掌握多片中小规模集成电路组合逻辑电路的级联、功能扩展及综合设计技术,使学生具有数字系统外围电路、接口电路方面的综合设计能力。

(二)实验要求1. 数字显示电路操作面板:左侧有16个按键,编号为0到15数字,面板右侧有2个共阳7段显示器。

2. 设计要求:当按下小于10的按键后,右侧低位7段显示器显示数字,左侧7段显示器显示0;当按下大于9的按键后,右侧低位7段显示器显示个位数字,左侧7段显示器显示1。

若同时按下几个按键,优先级别的顺序是15到0。

二、电路框图及原理图原理图概要:数字显示电路由键盘、编码、码制转换、译码显示组成。

各部分作用:1. 键盘:用于0~15数字的输入。

可以由16个自锁定式的按键来排列成4×4键盘。

2.编码:采用两片74ls148级联来完成对0~15的编码,并且是具有优先级的编码。

3.码制转换:本电路采用了2个74ls00、1个74ls04、1个74ls283来完成对0~15出事编码的码制转换,转换成个位与十位的8421bcd码,为下一步的解码做准备。

4.译码显示:本电路采用了两个74ls47分别对码制转换后的bcd码进行译码,并且由这两个芯片分别驱动两片七段共阳极数码管。

原理图:三、设计思想及基本原理分析:篇二:数电实验实验报告数字电路实验报告院系:电气工程学院专业:电气工程极其自动化班级:09级7班姓名:王哲伟学号:2009302540221 实验一组合逻辑电路分析一.试验用集成电路引脚图74ls00集成电路 74ls20集成电路四2输入与非门双4输入与非门二.实验内容 1.实验一x1abdabcd按逻辑开关,“1”表示高电平,“0”表示低电平2.5 vc示灯:灯亮表示“1”,灯灭表示“0”自拟表格并记录: 2.实验二密码锁的开锁条件是:拨对密码,钥匙插入锁眼将电源接通,当两个条件同时满足时,开锁信号为“1”,将锁打开。

数电实验仿真报告

数电实验仿真报告实验一 组合逻辑电路设计与分析 一、实验目的(1)学会组合逻辑的特点(2)利用逻辑转换仪对组合逻辑电路进行分析与设计 二、实验原理组合逻辑电路是一种重要的数字逻辑电路:特点是任何时候的输出仅仅取决于同一时刻输入信号的取值组合。

根据电路确定功能,是分析组合逻辑电路的过程。

三、实验内容 (1)、利用逻辑转换仪对已知逻辑电路进行分析。

XLC1A BU1A 74LS136DU2A 74LS136DU3A 74LS04DU4A 74LS04DU5B 74LS04DU6C 74LS136D所以这是一个四位输入信号的奇偶校验电路。

(2)、根据要求利用逻辑转换仪进行逻辑电路分析。

火灾报警系统分析如下:生成的报警控制信号电路如下:A B C44454647484950四、思考题设计一个4人表决器,3人或3人以上同意则通过。

利用逻辑转换仪得真值表和表达式如下:根据真值表和表达式得逻辑电路如下:A B C D6566676869 7071727374757677787980818283 84利用逻辑转换仪对下图所示逻辑电路进行分析。

XLC1A BU1A 74LS04DU2B74LS04D U3C 74LS04DU4A 74LS00D U6B 74LS00DU7B74LS10D U8A74LS10D5623478910分析如下 实验二 编码器、译码器电路仿真实验 一、实验目的(1)掌握编码器、译码器的工作原理。

(2)常见编码器、译码器的作用。

二、实验原理(1)编码是指在选定的一系列二进制数码中,赋予每个二进制数码以某一固定含义。

能完成编码功能的电路统称为编码器。

(2)译码是编码的逆过程,将输入的每个二进制代码赋予的含义翻译出来,给出相应的输出信号。

三、实验内容 (1)、8-3线优先译码器(2)、1型冒险电路仿真实验V11kHz 5 VXSC1A BExt Trig++__+_U2A74LS04DU1A74LS08D(3)、多输入信号同时变化时的冒险电路V11MHz5 VXSC1A B Ext Trig++_ _+_U1A 74LS04DU2B74LS09DU3C74LS09DU4B74LS32DGNDVDD 5V(4)、多输入信号同时变化时的冒险消除电路V11MHz5 V XSC1A B Ext Trig++_ _+_U1A 74LS04DU2B74LS09DU3C74LS09DU4B74LS32DGNDVDD5VU5A74LS09DU6A74LS32D四、思考题如图3-5所示电路是否存在竞争冒险现象,若存在如何消除?U1A74LS04D U2A74LS02D U2B74LS02DU2C74LS02D2341567ABCF图表 1 思考题电路做出该电路所对应的卡诺图如下BC A 00 01 11 10 0 0 1 1 0 111因为卡诺图中填1的格所形成的卡诺图有两个相邻的圈相切,故可知电路存在竞争冒险的可能。

Multisim数字电路仿真实验报告

基于Multisim数字电路仿真实验一、实验目的1.掌握虚拟仪器库中关于测试数字电路仪器的使用方法,入网数字信号发生器和逻辑分析仪的使用。

2.进一步了解Multisim仿真软件基本操作和分析方法。

二、实验内容用数字信号发生器和逻辑分析仪测试74LS138译码器逻辑功能。

三、实验原理实验原理图如图所示:四、实验步骤1.在Multisim软件中选择逻辑分析仪,字发生器和74LS138译码器;2.数字信号发生器接138译码器地址端,逻辑分析仪接138译码器输出端。

并按规定连好译码器的其他端口。

3.点击字发生器,控制方式为循环,设置为加计数,频率设为1KHz,并设置显示为二进制;点击逻辑分析仪设置频率为1KHz。

相关设置如下图五、实验数据及结果逻辑分析仪显示图下图实验结果分析:由逻辑分析仪可以看到在同一个时序74LS138译码器的八个输出端口只有一个输出为低电平,其余为高电平.结合字发生器的输入,可知.在译码器的G1=1,G2A=0,G2B=0的情况下,输出与输入的关系如下表所示当G1=1,G2A=0,G2B=0中任何一个输入不满足时,八个输出都为1六、实验总结通过本次实验,对Multisim的基本操作方法有了一个简单的了解。

同时分析了38译码器的功能,结果与我们在数字电路中学到的结论完全一致。

实验二基于Multisim的仪器放大器设计一、实验目的1.掌握仪器放大器的实际方法;2.理解仪器放大器对共模信号的抑制能力;3.熟悉仪器放大器的调试方法;4.掌握虚拟仪器库中关于测试模拟电路仪器的使用方法,如示波器、毫伏表、信号发生器等虚拟仪器的使用方法。

二、实验内容1.采用运算放大器设计并构建仪器放大器,具体指标为:(1)输入信号Ui=2mv时,要求输出电压信号Uo=0.4V,Avd=200,f=1KHz;(2)输入阻抗要求Ri》1MΩ2.用虚拟仪器库中关于测试模拟电路仪器,按设计指标进行调试;3.测量所构建的测量放大器的共模抑制比(选做)4.记录实验数据进行整理分析。

数字电路仿真实验报告材料

数字逻辑与CPU 仿真实验报告姓名:班级:学号:仿真实验摘要:Multisim是Interactive Image Technologies公司推出的以Windows为基础的仿真工具,具有丰富的仿真分析能力。

本次仿真实验便是基于Multisim软件平台对数字逻辑电路的深入研究,包括了对组合逻辑电路、时序逻辑电路中各集成元件的功能仿真与验证、对各电路的功能分析以及自行设计等等。

一、组合逻辑电路的分析与设计1、实验目的(1)掌握用逻辑转换器进行逻辑电路分析与设计的方法。

(2)熟悉数字逻辑功能的显示方法以及单刀双掷开关的应用。

(3)熟悉字信号发生器、逻辑分析仪的使用方法。

2、实验内容和步骤(1)采用逻辑分析仪进行四舍五入电路的设计①运行Multisim,新建一个电路文件,保存为四舍五入电路设计。

②在仪表工具栏中跳出逻辑变换器XLC1。

图1-1 逻辑变换器以及其面板③双击图标XLC1,其出现面板如图1-1所示④依次点击输入变量,并分别列出实现四舍五入功能所对应的输出状态(点击输出依次得到0、1、x状态)。

⑤点击右侧不同的按钮,得到输出变量与输入变量之间的函数关系式、简化的表达式、电路图及非门实现的逻辑电路。

⑥记录不同的转换结果。

(2)分析图1-2所示代码转换电路的逻辑功能①运行Multisim,新建一个电路文件,保存为代码转换电路。

②从元器件库中选取所需元器件,放置在电路工作区。

•从TTL工具栏选取74LS83D放置在电路图编辑窗口中。

•从Source库取电源Vcc和数字地。

•从Indictors库选取字符显示器。

•从Basic库Switch按钮选取单刀双掷开关SPD1,双击开关,开关的键盘控制设置改为A。

后面同理,分别改为B、C、D。

图1-2 代码转换电路③将元件连接成图1-2所示的电路。

④闭合仿真开关,分别按键盘A、B、C、D改变输入变量状态,将显示器件的结果填入表1-1中。

⑤说明该电路的逻辑功能。

大学_数电仿真实验报告

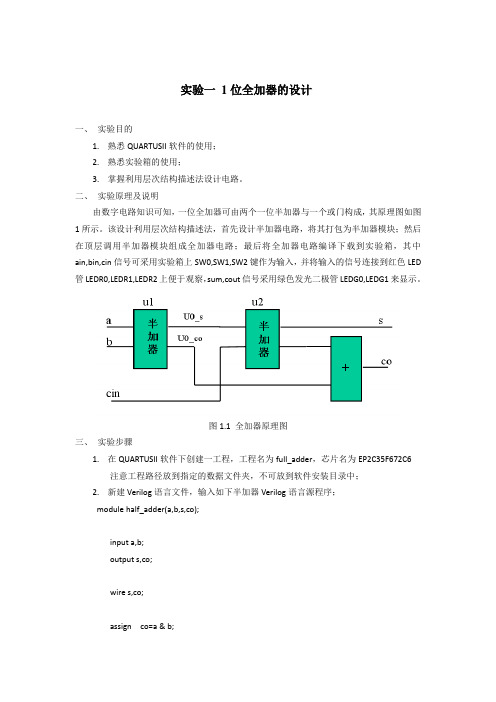

实验一1位全加器的设计一、实验目的1.熟悉QUARTUSII软件的使用;2.熟悉实验箱的使用;3.掌握利用层次结构描述法设计电路。

二、实验原理及说明由数字电路知识可知,一位全加器可由两个一位半加器与一个或门构成,其原理图如图1所示。

该设计利用层次结构描述法,首先设计半加器电路,将其打包为半加器模块;然后在顶层调用半加器模块组成全加器电路;最后将全加器电路编译下载到实验箱,其中ain,bin,cin信号可采用实验箱上SW0,SW1,SW2键作为输入,并将输入的信号连接到红色LED 管LEDR0,LEDR1,LEDR2上便于观察,sum,cout信号采用绿色发光二极管LEDG0,LEDG1来显示。

图1.1 全加器原理图三、实验步骤1.在QUARTUSII软件下创建一工程,工程名为full_adder,芯片名为EP2C35F672C6注意工程路径放到指定的数据文件夹,不可放到软件安装目录中;2.新建Verilog语言文件,输入如下半加器Verilog语言源程序;module half_adder(a,b,s,co);input a,b;output s,co;wire s,co;assign co=a & b;assign s=a ^ b;endmodule3.保存半加器程序为half_adder.v,进行功能仿真、时序仿真,验证设计的正确性。

4.选择菜单Fil e→Create/Update→Create Symbol Files for current file,创建半加器模块。

5.新建一原理图文件,在原理图中调用半加器、或门模块和输入,输出引脚,按照图1所示连接电路。

并将输入ain,bin,cin连接到FPGA的输出端,便于观察。

完成后另保存full_adder。

6.对设计进行全编译,如出现错误请按照错误提示进行修改。

7.分别进行功能与时序仿真,验证全加器的逻辑功能。

8.锁定引脚采用JATG方式进行下载,通过SW0,SW1,SW2输入,观察的LEDR[0],LEDR[1],LEDR[2],LEDG[0],LEDG[1]亮灭验证全加器的逻辑功能。

数电项目实验报告(3篇)

第1篇一、实验目的1. 理解数字电路的基本概念和组成原理。

2. 掌握常用数字电路的分析方法。

3. 培养动手能力和实验技能。

4. 提高对数字电路应用的认识。

二、实验器材1. 数字电路实验箱2. 数字信号发生器3. 示波器4. 短路线5. 电阻、电容等元器件6. 连接线三、实验原理数字电路是利用数字信号进行信息处理的电路,主要包括逻辑门、触发器、计数器、寄存器等基本单元。

本实验通过搭建简单的数字电路,验证其功能,并学习数字电路的分析方法。

四、实验内容及步骤1. 逻辑门实验(1)搭建与门、或门、非门等基本逻辑门电路。

(2)使用数字信号发生器产生不同逻辑电平的信号,通过示波器观察输出波形。

(3)分析输出波形,验证逻辑门电路的正确性。

2. 触发器实验(1)搭建D触发器、JK触发器、T触发器等基本触发器电路。

(2)使用数字信号发生器产生时钟信号,通过示波器观察触发器的输出波形。

(3)分析输出波形,验证触发器电路的正确性。

3. 计数器实验(1)搭建异步计数器、同步计数器等基本计数器电路。

(2)使用数字信号发生器产生时钟信号,通过示波器观察计数器的输出波形。

(3)分析输出波形,验证计数器电路的正确性。

4. 寄存器实验(1)搭建移位寄存器、同步寄存器等基本寄存器电路。

(2)使用数字信号发生器产生时钟信号和输入信号,通过示波器观察寄存器的输出波形。

(3)分析输出波形,验证寄存器电路的正确性。

五、实验结果与分析1. 逻辑门实验通过实验,验证了与门、或门、非门等基本逻辑门电路的正确性。

实验结果表明,当输入信号满足逻辑关系时,输出信号符合预期。

2. 触发器实验通过实验,验证了D触发器、JK触发器、T触发器等基本触发器电路的正确性。

实验结果表明,触发器电路能够根据输入信号和时钟信号产生稳定的输出波形。

3. 计数器实验通过实验,验证了异步计数器、同步计数器等基本计数器电路的正确性。

实验结果表明,计数器电路能够根据输入时钟信号进行计数,并输出相应的输出波形。

multisim仿真数电实验报告

实验报告课程名称:数字电子技术实验姓名:学号:专业:开课学期:指导教师:实验课安全知识须知1.须知1:规范着装。

为保证实验操作过程安全、避免实验过程中意外发生,学生禁止穿拖鞋进入实验室,女生尽量避免穿裙子参加实验。

2.须知2:实验前必须熟悉实验设备参数、掌握设备的技术性能以及操作规程。

3.须知3:实验时人体不可接触带电线路,接线或拆线都必须在切断电源的情况下进行。

4.须知4:学生独立完成接线或改接线路后必须经指导教师检查和允许,并使组内其他同学引起注意后方可接通电源。

实验中如设备发生故障,应立即切断电源,经查清问题和妥善处理故障后,才能继续进行实验。

5.须知5:接通电源前应先检查功率表及电流表的电流量程是否符合要求,有否短路回路存在,以免损坏仪表或电源。

特别提醒:实验过程中违反以上任一须知,需再次进行预习后方可再来参加实验;课程中违反三次及以上,直接重修。

实验报告撰写要求1.要求1:预习报告部分列出该次实验使用组件名称或者设备额定参数;绘制实验线路图,并注明仪表量程、电阻器阻值、电源端编号等。

绘制数据记录表格,并注明相关的实验环境参数与要求。

2.要求2:分析报告部分一方面参考思考题要求,对实验数据进行分析和整理,说明实验结果与理论是否符合;另一方面根据实测数据和在实验中观察和发现的问题,经过自己研究或分析讨论后写出的心得体会。

3.要求3:在数据处理中,曲线的绘制必须用坐标纸画出曲线,曲线要用曲线尺或曲线板连成光滑曲线,不在曲线上的点仍按实际数据标出其具体坐标。

4.要求4:本课程实验结束后,将各次的实验报告按要求装订,并在首页写上序号(实验课上签到表对应的序号)。

请班长按照序号排序,并在课程结束后按要求上交实验报告。

温馨提示:实验报告撰写过程中如遇预留空白不足,请在该页背面空白接续。

实验报告课程名称:数字电子技术实验实验 5 : multisim多位计数器仿真实验日期:年月日地点:实验台号:专业班级:学号:姓名:评分:教师评语:教师签字:日期:一、实验目的二、实验设备及元器件Multisim仿真洁面三、实验原理(简述实验原理,画出原理图)这一部分的实验主要涉及改变计数进制的问题,我分为以下几个部分预习一、首先需要明确各个芯片的计数最大进制 161系列为16进制,160系列的为10进制。

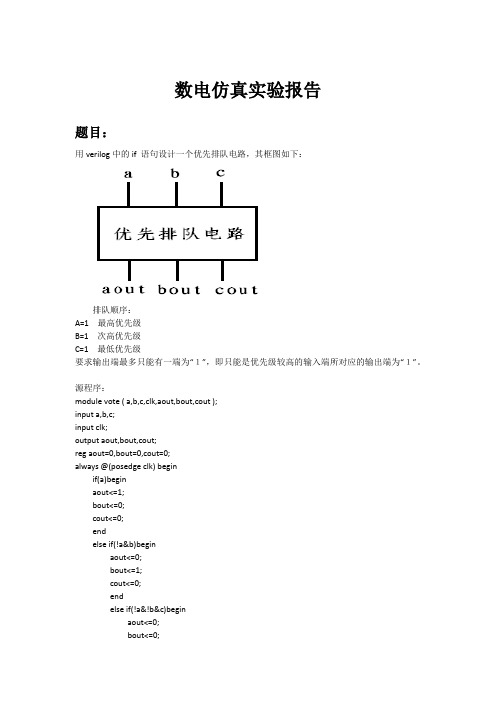

数电仿真实验报告 优先排队电路

数电仿真实验报告题目:用verilog中的if 语句设计一个优先排队电路,其框图如下:排队顺序:A=1 最高优先级B=1 次高优先级C=1 最低优先级要求输出端最多只能有一端为“1”,即只能是优先级较高的输入端所对应的输出端为“1”。

源程序:module vote ( a,b,c,clk,aout,bout,cout );input a,b,c;input clk;output aout,bout,cout;reg aout=0,bout=0,cout=0;always @(posedge clk) beginif(a)beginaout<=1;bout<=0;cout<=0;endelse if(!a&b)beginaout<=0;bout<=1;cout<=0;endelse if(!a&!b&c)beginaout<=0;bout<=0;cout<=1;endelse beginaout<=0;bout<=0;cout<=0;endendendmodule仿真结果:电路需要时钟信号,每次时钟上升沿进行判定,并且电路有延迟,对于数字电路来说,几ns 的延迟是正常的,输入a,b,c从000到111,可以看到,当a=1时,无论b,c为何值,aout=1,bout=0,cout=0,a=0且b=1时,无论c为何值,aout=0,bout=1,cout=0,a,b都为0时,c=1,则aout=0,bout=0,cout=1,a,b,c都为0时,aout=0,bout=0,cout=0。

数电仿真实验报告_2008302540289_修改

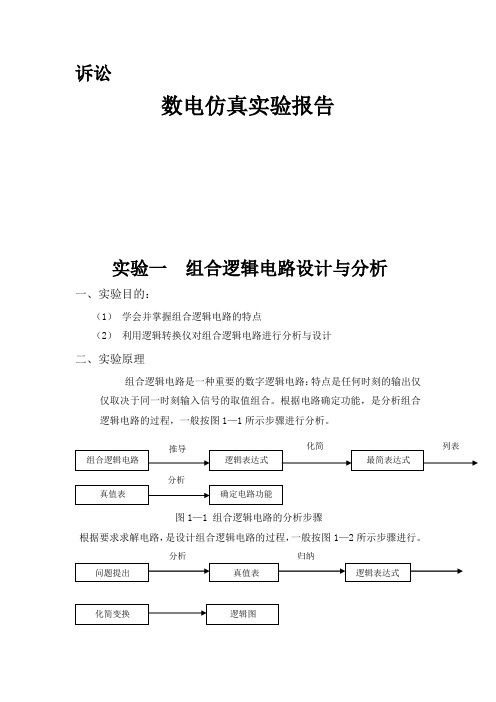

诉讼数电仿真实验报告实验一组合逻辑电路设计与分析一、实验目的:(1)学会并掌握组合逻辑电路的特点(2)利用逻辑转换仪对组合逻辑电路进行分析与设计二、实验原理组合逻辑电路是一种重要的数字逻辑电路:特点是任何时刻的输出仅仅取决于同一时刻输入信号的取值组合。

根据电路确定功能,是分析组合逻辑电路的过程,一般按图1—1所示步骤进行分析。

图1—1 组合逻辑电路的分析步骤根据要求求解电路,是设计组合逻辑电路的过程,一般按图1—2所示步骤进行。

图1—2 组合逻辑电路的设计步骤逻辑转换仪是在Multisim 软件中常用的数字逻辑电路设计和分析的仪器使用方便、简洁。

逻辑转换仪的图标和面板如图1—3所示。

三、实验内容:(1) 利用逻辑转换仪对已知逻辑电路进行分析。

经分析得到的真值表和表达式:在逻辑转换仪面板上单击由逻辑电路转换为真值表的按钮和由真值表导出简化表达式后,得到如图1-5所示结果。

观察真值表,我们发现:当四个输入变量A,B,C,D中1的个数为奇数时,输出为0,而当四个输入变量A,B,C,D中1的个数为偶数时,输出为1。

因此这是一个四位输入信号的奇偶校验电路。

(2)根据要求利用逻辑转换仪进行逻辑电路的设计。

a.问题提出:有一火灾报警系统,设有烟感、温感和紫外线三种类型不同的火灾探测器。

为了防止误报警,只有当其中有两种或两种以上的探测器发出火灾探测信号时,报警系统才产生报警控制信号,试设计报警控制信号的电路。

b.在逻辑转换仪面板上根据下列分析出真值表如图1-6所示:由于探测器发出的火灾探测信号也只有两种可能,一种是高电平(1),表示有火灾报警;一种是低电平(0),表示正常无火灾报警。

因此,令A、B、C分别表示烟感、温感、紫外线三种探测器的探测输出信号,为报警控制电路的输入、令F为报警控制电路的输出。

(3)在逻辑转换仪面板上单击由真值表到处简化表达式的按钮后得到如图1-7所示的最简化表达式。

(4)在图1-8的基础上单击由逻辑表达式得到逻辑电路的按钮后得到如图1-8所示的逻辑电路。

数电综合实验报告(3篇)

第1篇一、实验目的1. 巩固和加深对数字电路基本原理和电路分析方法的理解。

2. 掌握数字电路仿真工具的使用,提高设计能力和问题解决能力。

3. 通过综合实验,培养团队合作精神和实践操作能力。

二、实验内容本次实验主要分为以下几个部分:1. 组合逻辑电路设计:设计一个4位二进制加法器,并使用仿真软件进行验证。

2. 时序逻辑电路设计:设计一个4位计数器,并使用仿真软件进行验证。

3. 数字电路综合应用:设计一个数字时钟,包括秒、分、时显示,并使用仿真软件进行验证。

三、实验步骤1. 组合逻辑电路设计:(1)根据题目要求,设计一个4位二进制加法器。

(2)使用Verilog HDL语言编写代码,实现4位二进制加法器。

(3)使用ModelSim软件对加法器进行仿真,验证其功能。

2. 时序逻辑电路设计:(1)根据题目要求,设计一个4位计数器。

(2)使用Verilog HDL语言编写代码,实现4位计数器。

(3)使用ModelSim软件对计数器进行仿真,验证其功能。

3. 数字电路综合应用:(1)根据题目要求,设计一个数字时钟,包括秒、分、时显示。

(2)使用Verilog HDL语言编写代码,实现数字时钟功能。

(3)使用ModelSim软件对数字时钟进行仿真,验证其功能。

四、实验结果与分析1. 组合逻辑电路设计:通过仿真验证,所设计的4位二进制加法器能够正确实现4位二进制加法运算。

2. 时序逻辑电路设计:通过仿真验证,所设计的4位计数器能够正确实现4位计数功能。

3. 数字电路综合应用:通过仿真验证,所设计的数字时钟能够正确实现秒、分、时显示功能。

五、实验心得1. 通过本次实验,加深了对数字电路基本原理和电路分析方法的理解。

2. 掌握了数字电路仿真工具的使用,提高了设计能力和问题解决能力。

3. 培养了团队合作精神和实践操作能力。

六、实验改进建议1. 在设计组合逻辑电路时,可以考虑使用更优的电路结构,以降低功耗。

2. 在设计时序逻辑电路时,可以尝试使用不同的时序电路结构,以实现更复杂的逻辑功能。

数电仿真Modelsim设计实验报告-Verilog-HDL语言

¥《Verilog HDL程序设计与仿真实验报告》1、实验名称:Verilog HDL程序设计与仿真实验2、实验设计要求以及内容:利用Verilog HDL语言和描述下列芯片的功能,编写激励测试程序并在Modelsim软件中仿真运行、记录相关波形。

芯片包括:CD4532、74X138、74HC4511、74HC151、74HC85、74HC283、74HC194、74LVC161。

3、实验软件:Modelsim软件。

4、?5、芯片功能与真值表:!74HC85:4位数值比较器:、74HC283:4位二进制全加器:6、实验具体设计:CD4532-8位优先编码器:模块设计代码:moduleCD4532(EI,I,Y,GS,EO);I(EI_in),.I(D_in),.Y(Q_result),.GS(GS_result),.EO(EO_result));、endmodule74X138-3 线-8线译码器:模块设计代码:module _74X138(A,EN,Y);(A_in),.EN(EI_in),.Y(Y_result));endmodule74HC4511-七段显示译码器:《模块设计代码:module _74HC4511(D,LE,BL,LT,a,b,c,d,e,f,g);reg F000,F001,F002,F110,F111,F112,F220,F221,F222,F330,F331,F332;//中间节点,依次对应Ai=Bi,Ai<Bi,Ai>为位数(0~3)always@(A,B,I0,I1,I2)beginif(A[3]>B[3])//比较第4位begin F330=0; F331=0; F332=1; endelse if(A[3]<B[3])begin F330=0; F331=1; F332=0; end)elsebegin F330=1; F331=0; F332=0; endif(A[2]>B[2])//比较第3位begin F220=0; F221=0; F222=1; endelse if(A[2]<B[2])begin F220=0; F221=1; F222=0; endelsebegin F220=1; F221=0; F222=0; end*if(A[1]>B[1])//比较第2位begin F110=0; F111=0; F112=1; endelse if(A[1]<B[1])begin F110=0; F111=1; F112=0; endelsebegin F110=1; F111=0; F112=0; endif(A[0]>B[0])//比较第1位begin F000=0; F001=0; F002=1; end%else if(A[0]<B[0])begin F000=0; F001=1; F002=0; endelsebegin F000=1; F001=0; F002=0; end//输出结果如下if((F000&&F110&&F220&&F330)&&I0)//低位进位信号出错begin Fab2=0; Fab1=0; Fab0=1; endelse if((F000&&F110&&F220&&F330)&&(~I0&&I1&&I2))//低位进位信号出错}begin Fab2=0; Fab1=0; Fab0=0; endelse if((F000&&F110&&F220&&F330)&&(~I0&&~I1&&~I2))//低位进位信号出错begin Fab2=1; Fab1=1; Fab0=0; endelse//低位进位信号正常beginFab2=F332||F330&&F222||F330&&F220&&F112||F330&&F220&&F110&&F002||F330&&F220&&F110&&F000&&I2;Fab1=F331||F330&&F221||F330&&F220&&F111||F330&&F220&&F110&&F001||F330&&F220&&F110&&F000&&I1;Fab0=F330&&F220&&F110&&F000&&I0;end>endendmodule对应testbench设计代码:`timescale 1ns/1nsmodule _74HC85_tb;reg [3:0] A_in,B_in;reg I0_in,I1_in,I2_in;wire Fab0_result,Fab1_result,Fab2_result;¥initialbeginI0_in=0;I1_in=0;I2_in=0;A_in=4'b1010;B_in=4'b0111;#10 begin I0_in=1; I1_in=0; I2_in=0; end//低位A=B、#10 begin I0_in=0; I1_in=1; I2_in=0; end//低位A<B#10 begin I0_in=0; I1_in=0; I2_in=1; end//低位A>B#10 begin I0_in=0; I1_in=0; I2_in=0; //低位归位A_in=4'b0100; B_in=4'b1001; end#10 begin I0_in=1; I1_in=0; I2_in=0; end//低位A=B#10 begin I0_in=0; I1_in=1; I2_in=0; end//低位A<B#10 begin I0_in=0; I1_in=0; I2_in=1; end//低位A>B#10 begin I0_in=0; I1_in=0; I2_in=0; //低位归位~A_in=4'b0010; B_in=4'b0010; end#10 begin I0_in=1; I1_in=0; I2_in=0; end//低位A=B#10 begin I0_in=0; I1_in=1; I2_in=0; end//低位A<B#10 begin I0_in=0; I1_in=0; I2_in=1; end//低位A>B#10 $stop();end_74HC85 U1(A_in,B_in,I0_in,I1_in,I2_in,Fab0_result,Fab1_result,Fab2_result); endmodule—74HC283-4位二进制全加器:模块设计代码:module _74HC283(A,B,Ci,Co,S);//4位二进制全加器input Ci;//低位进位信号input [3:0] A,B;//输入信号output reg [3:0] S;//输出结果output reg Co;//高位进位信号Co=C[3]>reg [3:0] C,G,P;integer k;always@(A,B,Ci)beginfor(k=0;k<4;k=k+1)beginG[k]=A[k]&&B[k];P[k]=A[k]&&~B[k]||~A[k]&&B[k];]endC[0]=G[0]||P[0]&&Ci;C[1]=G[1]||P[1]&&C[0];C[2]=G[2]||P[2]&&C[1];C[3]=G[3]||P[3]&&C[2];S[0]=P[0]&&~Ci||~P[0]&&Ci;S[1]=P[1]&&~C[0]||~P[1]&&C[0];S[2]=P[2]&&~C[1]||~P[2]&&C[1];~S[3]=P[3]&&~C[2]||~P[3]&&C[2];Co=C[3];endendmodule对应testbench设计代码:`timescale 1ns/1nsmodule _74HC283_tb;reg [3:0] A_in,B_in;【reg Ci_in;//低位进位信号wire [3:0] S_out;//本位相加结果wire Co_out;//高位进位信号initialbeginCi_in=0;A_in=4'b1010;B_in=4'b0111;(#10 begin A_in=4'b0011; B_in=4'b1111; end#10 begin A_in=4'b0101; B_in=4'b1001; end#10 begin A_in=4'b1111; B_in=4'b0010; end #10 $stop();endalways #5beginCi_in=~Ci_in;//循环改变低位进位信号{end_74HC283 U1(A_in,B_in,Ci_in,Co_out,S_out);endmodule74HC194-4位双向移位寄存器:模块设计代码:module _74HC194(S0,S1,Dsl,Dsr,CP,CR,D,Q);//4位双向移位寄存器_P339 input S0,S1;//输入端口,input Dsr,Dsl;//串行数据输入input CP,CR;//时钟和清零input [3:0] D;//并行数据输入output reg [3:0] Q;//输出结果always@(posedge CP, negedge CR)beginif(~CR) Q<=4'b0000;//异步清零else<case({S1,S0})2'b00:Q<=Q;//输出保持不变2'b01:Q<={Q[2:0],Dsr};//右移,低位移向高位2'b10:Q<={Dsl,Q[3:1]};//左移,高位移向低位2'b11:Q<=D;//并行置数endcaseendendmodule?对应testbench设计代码:`timescale 1ns/1nsmodule _74HC194_tb;reg [3:0] D_in;//并行数据输入reg S0_in,S1_in;//控制信号输入端口reg Dsr_in,Dsl_in;//串行数据输入reg CP_in,CR_in;//时钟和清零,清零为低电平有效wire [3:0] Q_out;//输出结果¥initialbeginCP_in=1;CR_in=1;S0_in=1;S1_in=1;//开始先输入串行数据Dsr_in=0;Dsl_in=0;&D_in=4'b0110;#243 CR_in=~CR_in;#20 $stop();endalways #5beginCP_in=~CP_in;//周期为10ns的时钟信号end)always #15//循环调整控制输入信号,周期60nsbegincase({S1_in,S0_in})2'b00:begin S1_in=0; S0_in=1; end2'b01:begin S1_in=1; S0_in=0; end2'b10:begin S1_in=1; S0_in=1; end2'b11:begin S1_in=0; S0_in=0; endendcase(endalways #10//循环调整串行数据输入信号,周期40nsbegincase({Dsr_in,Dsl_in})2'b00:begin Dsr_in=0; Dsl_in=1; end2'b01:begin Dsr_in=1; Dsl_in=0; end2'b10:begin Dsr_in=1; Dsl_in=1; end2'b11:begin Dsr_in=0; Dsl_in=0; end|endcaseend_74HC194 U1(S0_in,S1_in,Dsl_in,Dsr_in,CP_in,CR_in,D_in,Q_out);endmodule74LVC161-4位二进制同步计数器:模块设计代码:module _74LVC161(CEP,CET,PE,CP,CR,D,TC,Q);//4位二进制同步计数器_P340 ]input CEP,CET,PE,CP,CR;//输入端口input [3:0] D;//并行数据输入output TC;//进位输出output reg [3:0] Q;//输出结果wire CE;assign CE=CEP&CET;//CE=1时计数器计数assign TC=CET&PE&(Q==4'b1111);//产生进位输出信号always@(posedge CP, negedge CR)beginif(~CR) Q<=4'b0000;//异步清零else if(~PE) Q<=D;//PE=0,同步输入数据else if(CE)beginif((TC==1)&&(Q==4'b1111))Q<=4'b0000;//计数器计满后自动归零elseQ<=Q+1'b1;//加1计数endelse Q<=Q;//保持输出不变endendmodule对应testbench设计代码:`timescale 1ns/1nsmodule _74LVC161_tb;reg CEP_in,CET_in,PE_in,CP_in,CR_in;//输入端口reg [3:0] D_in;//并行数据输入wire TC_out;//进位输出wire [3:0] Q_out;//输出结果initialbeginCEP_in=0;CET_in=1;PE_in=0;CP_in=1;CR_in=1;D_in=4'b1101;#10 begin PE_in=1;D_in=4'b1001; end#20 begin CEP_in=1; CET_in=1; end#220 begin PE_in=0; end#23 CR_in=~CR_in;#20 $stop();endalways #5beginCP_in=~CP_in;//周期为10ns的时钟信号end_74LVC161 U1(CEP_in,CET_in,PE_in,CP_in,CR_in,D_in,TC_out,Q_out);endmodule7、输出仿真波形以及相关数据:CD4532-8位优先编码器:以下波形由上至下依次是:D_in, EI_in, Q_result, GS_result, EO_result;74X138-3 线-8线译码器:以下波形由上至下依次是:A_in, EI_in, Y_result;74HC4511-七段显示译码器:以下波形由上至下依次是:D_in, LE_in, LT_in, A, B, C, D, E, F, G;74HC151-八选一数据选择器:以下波形由上至下依次是:S_in, D_in, E_in, Y0_result, Y1_result;74HC85-4位数值比较器:以下波形由上至下依次是:A_in, B_in, I0_in, I1_in, I2_in, Fab0_result, Fab1_result, Fab2_result;74HC283-4位二进制全加器:以下波形由上至下依次是:A_in, B_in, S_out, Co_out;74HC194-4位双向移位寄存器:以下波形由上至下依次是:D_in, S0_in, S1_in,Dsr_in, Dsl_in, CP_in, CR_in, Q_out;74LVC161-4位二进制同步计数器:以下波形由上至下依次是:CEP_in, CET_in, PE_in, CP_in, CR_in, D_in, T_out, Q_out;8、仿真结果分析:仿真输出波形符合预期,与芯片的功能表描述的功能相符。

数电仿真实验报告 (2)

数电仿真Multisim实验报告班级:学号:姓名:学院:实验一组合逻辑电路设计与分析一、实验目的1、掌握组合逻辑电路的特点2、利用逻辑转换仪对组合逻辑电路进行分析与设计二、实验原理组合逻辑电路是一种重要的数字逻辑电路:特点是任何时候的输出仅仅取决于同一时刻的输入信号的取值组合。

根据电路确定功能,是分析组合逻辑电路的过程,其步骤如下:组合逻辑电路→推导→逻辑表达式→化简→最简表达式→列表→真值表→分析→确定电路功能。

根据要求求解电路,是设计组合逻辑电路的过程,其步骤如下:问题提出→分析→真值表→归纳→逻辑表达式→化简变换→逻辑图。

逻辑转换仪是Multisim中常用的数字逻辑电路分析和设计仪器。

三、仿真例题1、利用逻辑转换仪对已知逻辑电路进行分析电路图如下:图1.1 待分析逻辑电路分析结果如下:图1.2 逻辑分析仪输出结果2、根据要求利用逻辑转换仪进行逻辑电路设计问题:有一火灾报警系统,设有烟感、温感和紫外线三种类型的火灾探测器。

为了防止误报警,只有当其中的两种或两种以上的探测器发出火灾探测信号时,报警系统才产生报警控制信号,试设计报警控制信号的电路。

利用逻辑分析仪分析:图1.3 经分析得到的真值表和表达式则可以得到如下电路图:A B C141310912118图1.4 最终得到的逻辑电路图四、思考题1、设计一个四人表决电路,即如果3人或3人以上同意,则通过;否则被否决。

用与非门实现。

解:用ABCD 分别表示四人的表决结果,1表示同意,0表示不同意。

则利用逻辑分析仪可以输入如下真值表,并得到如下表达式:L=ACD+ABD+ABC+BCD图1.5 逻辑分析仪得到的真值表和表达式得到如下电路图:A B C1411131123210968754图1.6 利用逻辑分析仪得到的与非门设计的表决电路2、利用逻辑转换仪对下图所示电路进行分析。

XLC1A BU1A74LS04DU1B 74LS04DU1C 74LS04DU2A 74LS00DU2B74LS00D2U3A74LS10DU3B74LS10D1436578910图1.7 待分析的逻辑电路解:通过逻辑分析仪可以得到如下结果:图1.8 逻辑分析仪输出结果=++得到逻辑表达式为:L AC BC ABC实验二 编码器、译码器电路仿真实验一、实验目的1、掌握编码器、译码器的工作原理2、常见编码器、译码器的应用 二、实验原理数字信号既可以表示数,也可以用来表示指令和信息。

数字电路实验的实验报告(3篇)

第1篇一、实验目的1. 理解和掌握数字电路的基本原理和组成。

2. 熟悉数字电路实验设备和仪器的基本操作。

3. 培养实际动手能力和解决问题的能力。

4. 提高对数字电路设计和调试的实践能力。

二、实验器材1. 数字电路实验箱一台2. 74LS00若干3. 74LS74若干4. 74LS138若干5. 74LS20若干6. 74LS32若干7. 电阻、电容、二极管等元器件若干8. 万用表、示波器等实验仪器三、实验内容1. 基本门电路实验(1)验证与非门、或非门、异或门等基本逻辑门的功能。

(2)设计简单的组合逻辑电路,如全加器、译码器等。

2. 触发器实验(1)验证D触发器、JK触发器、T触发器等基本触发器的功能。

(2)设计简单的时序逻辑电路,如计数器、分频器等。

3. 组合逻辑电路实验(1)设计一个简单的组合逻辑电路,如4位二进制加法器。

(2)分析电路的输入输出关系,验证电路的正确性。

4. 时序逻辑电路实验(1)设计一个简单的时序逻辑电路,如3位二进制计数器。

(2)分析电路的输入输出关系,验证电路的正确性。

5. 数字电路仿真实验(1)利用Multisim等仿真软件,设计并仿真上述实验电路。

(2)对比实际实验结果和仿真结果,分析误差原因。

四、实验步骤1. 实验前准备(1)熟悉实验内容和要求。

(2)了解实验器材的性能和操作方法。

(3)准备好实验报告所需的表格和图纸。

2. 基本门电路实验(1)搭建与非门、或非门、异或门等基本逻辑电路。

(2)使用万用表测试电路的输入输出关系,验证电路的功能。

(3)记录实验数据,分析实验结果。

3. 触发器实验(1)搭建D触发器、JK触发器、T触发器等基本触发电路。

(2)使用示波器观察触发器的输出波形,验证电路的功能。

(3)记录实验数据,分析实验结果。

4. 组合逻辑电路实验(1)设计4位二进制加法器电路。

(2)搭建电路,使用万用表测试电路的输入输出关系,验证电路的正确性。

(3)记录实验数据,分析实验结果。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验一 :组合逻辑电路设计与分析一、 实验目的(1) 掌握组合逻辑电路的特点;(2) 利用组合逻辑转换仪对组合逻辑电路进行分析。

二、 实验原理组合逻辑电路是一种重要的数字逻辑电路:特点是任何时刻的输出仅仅取决于同一时刻的输入信号的取值组合。

根据电路的特定功能,分析组合逻辑电路的过程。

三、 实验电路及步骤(1) 利用逻辑转换仪对已知电路进行分析 实验连接图如下:U1A74LS136DU1B74LS136DU1C 74LS136DU2A 74LS04DU2B 74LS04DU2C 74LS04DXLC1A B真值表和逻辑表达式如下:(2) 根据要求利用逻辑转换仪进行逻辑电路分析。

问题的提出:火灾报警器只有在烟感、温感和紫外线三种不同类型的火灾探测器中两种或两种以上的探测器发出火灾探测信号时,报警系统才产生报警控制信号。

四、 思考题(1) 设计一个四人表决电路。

如果3人或者3人以上同意,则通过;反之,则被否决。

用与非门实现。

(2) 利用逻辑转换仪对下图所示逻辑电路进行分析U1A 74LS04D U2A74LS00D U1B 74LS04DU1C 74LS04DU2B74LS00DU3A74LS10D U3B74LS10D 24XLC1A B135678910五、实验体会实验二:编码器、译码器电路仿真实验一、实验目的(1)掌握编码器、译码器的工作原理。

(2)常见编码器、译码器的作用。

二、 实验原理数字信号不仅可以用来表示数,还可以用来表示各种指令和信息。

通过编码和译码来实现。

(1)编码是指在选定的一系列二进制数码中,赋予每个二进制数码以某一固定含义。

能完成编码功能的电路统称为编码器。

(2)译码是编码的逆过程,将输入的每个二进制代码赋予的含义翻译出来,给出相应的输出信号。

U174LS148DA 09A 17A 26G S14D 313D 41D 52D 212D 111D 010D 74D 63E I 5E O 15U274LS138DY 015Y 114Y 213Y 312Y 411Y 510Y 69Y 77A1B 2C 3G 16~G 2A 4~G 2B 5图2-1 编码器74LS148D 和译码器74LS138D三、实验电路(1)8-3线优先编码器 实验电路图如下:J1Key = 0J2Key = 1J3Key = 2J4Key = 3J5Key = 4J6Key = 5J7Key = 6J8 Key = 7U174LS148DA09A17A26GS14D313D41D52D212D111D010D74D63EI5EO15J9Key = SpaceA25 VA05 VGS5 VEO5 VVDD5V A15 V利用九个单刀双掷开关切换8位信号输入端和选通输入端输入的高低电平状态。

利用5个探测器观察3位信号输入端、选通输入端、优先标志输出信号的高低电平状态。

8-3线优先编码器真值表如下:输入端输出端EI Y7 Y6 Y5 Y4 Y3 Y2 Y1 Y0 A2 A1 A0 GS E0(2)3-8线译码器实验图如下:U174LS138D Y015Y114Y213Y312Y411Y510Y69Y77A 1B 2C 3G16~G2A 4~G2B5J1Key = SpaceVCC5VR11kΩY05 VR21kΩR31kΩJ2Key = SpaceJ3Key = SpaceY15 VY25 VY35 VY45 VY55 VY65 VY75 V123456VCC7891011121314利用三个单刀双掷开关切换二路输入端输入的高低电平的状态。

利用8个探测器观察8路输出端输出信号的高低电平状态。

使能端G1接高电平,G2A 、G2B 接低电平。

3-8译码器真值表如下:输入端输出端 G1 G2A G2B A2 A1 A0 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7四、思考题(1)利用两块8-3线优先编码器74LS148D 设计16-4线优先编码器,然后仿真验证16-4线优先编码器的逻辑功能。

(2)利用两块3-8线译码器74LS38D设计4—16线译码器,然后仿真验证4—16线译码的逻辑功能。

五、实验体会实验三:触发器带电路仿真实验一、实验目的(1) 掌握边沿触发器的逻辑功能;(2) 逻辑不同边沿触发器逻辑功能之间的相互切换。

二、实验原理触发器是构成时序逻辑电路的基本逻辑单元,具有记忆、存储二进制信息的功能。

从逻辑功能上将触发器分为RS 、D 、JK 、T 、T ’等几种类型,对于逻辑功能的描述又真值表、波形图、特征方程等几种方法。

边沿触发器指只在CP 上升或下降沿到来时接收此刻的输入信号,进行状态转换,而其他时刻的输入信号的变化对其没有影响的电路。

集成触发器异步置位、复位功能。

三、实验电路及步骤(1)D 触发器仿真电路,接线图如图所示:XSC1ABCDGTU1A74LS74D1D21Q5~1Q6~1CLR11CLK 3~1PR4VDD5VV11kHz 5 VJ1Key = SpaceJ2Key = SpaceJ3Key = SpaceJ4Key = SpaceX12.5 V真值表如下(输入1表示高电平,0表示低电平;输出1表示灯亮,0表示灯灭):输入端现态次态 CP ~CLR ~PR D Qn Qn+1分析结果:通过上述真值表,我们可以看到,~CLR 和~PR 两个端子的工作不受时钟脉冲的牵制,二者为无效电平时,该触发器才实现正常的D 触发器功能,即D Q n =+1,输出状态始终与脉冲上升沿到来前的瞬间D 的状态保持一致。

通过示波器的观察,也可以证明这一点,~CLR 和~PR 为无效电平时,次态Q 的变化始终在脉冲的上升沿处;而由~CLR 和~PR 引起的变化却可以出现在任何时候,不必非在时钟变化之处。

在仿真中我发现,当~CLR 和~PR 同时为低电平时,输出信号是与D 保持一致的。

应该说,这种工作状态并不是我们所希望的。

虽然于功能没影响,但是~CLR 和~PR 同时为有效电平仍是不被允许的。

(2)JK 触发器仿真电路图如图所示:XSC1ABCDG TU1A74LS112D1Q5~1Q6~1PR41K2~1CLR151J 31CLK 1V11kHz 5 VVDD5VJ1Key = SpaceJ2Key = SpaceJ3Key = SpaceJ4Key = SpaceJ5Key = SpaceX12.5 V真值表如下:CP ~CLR ~PR J K Qn Qn+1分析结果:通过上述真值表,我们可以看到,~CLR和~PR两个端子的工作不受时钟脉冲的牵制,当二者为无效电平时,该触发器才实现正常的JK触发器功能,即nnn QKQJQ+=+1,输出状态始终与脉冲下降沿到来前的瞬间J、K及nQ的状态相关。

通过示波器的观察,也可以证明,当JK触发器在正常实现其功能时,次态Q的变化始终在脉冲的下降沿处,而由~CLR和~PR引起的变化却可以出现在任何时候,不必非在时钟变化之处,二者的控制是异步的。

在仿真中我发现,当~CLR和~PR同时为低电平时,输出信号为1。

应该说,这种工作状态也不是我们所希望的。

虽然影响不会影响到JK触发器的功能,但是~CLR和~PR还是不要同时为有效电平的好。

四、思考题由于D触发器器方便,JK触发器功能最完善,怎样将JK触发器和D触发器分别转换为T触发器。

五、实验体会实验四:计数器电路仿真实验一、实验目的(1)了解计数器的日常应用和分类。

(2)熟悉集成计数器逻辑功能和其各控制端作用。

(3)掌握计数器的使用方法。

二、实验原理统计输入脉冲个数的过程叫计数。

能够完成计数工作的电路称做计数器。

计数器的基本功能是统计时钟脉冲的个数,即实现技术操作,也可由于分频、定时、产生节拍脉冲等。

二进制计数器是构成其他计数器的基础。

74LS161D 是常见的二进制加法同步计数器,74LS191D 是常见的二进制加/减同步计数器。

若一计数器的计数长度(模)为10,则该计数器称为十进制计数器。

三、实验电路及步骤(1)74LS161D 构成的二进制加法同步计数器,电路图如下: VCC5VU174LS161DQA 14QB 13QC 12QD 11RCO15A 3B 4C 5D6ENP 7ENT 10~LOAD 9~CLR 1CLK2GNDV11kHz 5 VJ1Key = AJ2Key = BJ3Key = CJ4Key = DU2DCD_HEXX1 2.5 VXLA1C Q T1FBusBusLn1Ln2Ln3Ln4Ln1Ln2Ln3Ln4BusL n 4L n 3L n 2L n 1该电路采用总线方式进行连接利用J1~4四个单刀双掷开关可切换74LS161D 第7、10、9、1脚输入的高低电平状态。

74LS161D 第3、4、5、6脚同时接高电平,第15脚接探测器。

V1为时钟信号,利用逻辑分析仪观察四位二进制输出端,进位端和时钟信号端的波形。

利用J1、J2、J3、J4四个单刀双掷开关进行切换,同时观察数码管U2的输出信号,实验表明,当~LOAD端和~CLR端为高电平时,数码管依次显示0—9—A—F。

观察探测器X1,发现当该计数器记满时,探测器X1亮,表明进位输出端有进位且高电平有效。

逻辑分析观察仪的结果如图5-2,它的6—9端子依次对应161上的QA—QD四个端子。

可以看出,以6端为最低位、9端为最高位的四位二进制数的变化恰是由0000—1111的依次递增。

其结果与表给定的功能是相吻合的。

改变时钟信号V1的幅度,若减小得过多,则数码管和逻辑分析仪显示将没有结果,因为电平太低而不能产生有效的脉冲;若增大时钟信号V1的频率,数码管上显示的数字的的循环频率加大,逻辑分析仪若不作调整,其上6—9端子上的波形变化将变慢。

(2)2.74LS191D构成的二进制加/减同步计数器实验步骤四、实验体会10。