32位MIPS处理器设计实验报告

单周期CPU实验报告

MIPS-CPU设计实验报告实验名称:32位单周期MIPS-CPU设计姓名学号:刘高斯11072205实验日期:2014年12月19日目录前言MIPS简介------------------------------------------------------------- 3 实验目的------------------------------------------------------------- 3第一部分VERILOG HDL 语言实现部分实验内容------------------------------------------------------------- 4 试验环境------------------------------------------------------------- 4 模块简介------------------------------------------------------------- 4 实验截图------------------------------------------------------------- 5 实验感想------------------------------------------------------------- 5 实验代码------------------------------------------------------------- 6第二部分LOGISIM 语言实现部分实验内容------------------------------------------------------------- 16 实验环境------------------------------------------------------------- 16模块设计------------------------------------------------------------- 16 试验感想------------------------------------------------------------- 23前言一、MIPS简介MIPS是世界上很流行的一种RISC处理器。

单周期CPU实验报告

MIPS-CPU设计实验报告实验名称:32位单周期MIPS-CPU设计姓名学号:刘高斯11072205实验日期:2014年12月19日目录前言MIPS简介------------------------------------------------------------- 3 实验目的------------------------------------------------------------- 3第一部分VERILOG HDL 语言实现部分实验内容------------------------------------------------------------- 4 试验环境------------------------------------------------------------- 4 模块简介------------------------------------------------------------- 4 实验截图------------------------------------------------------------- 5 实验感想------------------------------------------------------------- 5 实验代码------------------------------------------------------------- 6第二部分LOGISIM 语言实现部分实验内容------------------------------------------------------------- 16 实验环境------------------------------------------------------------- 16模块设计------------------------------------------------------------- 16 试验感想------------------------------------------------------------- 23前言一、MIPS简介MIPS是世界上很流行的一种RISC处理器。

基于MIPS 32位处理器的简易智能家居控制系统设计详解

基于MIPS 32位处理器的简易智能家居控制系统设计详解一.研究背景与意义随着智能电网理念的提出,基于家庭智能交互终端的电能计量和营销方案已逐步形成,这意味着家居控制将迈向智能化。

智能家居是近几年产生并迅速崛起的一种新型家居住宅,家居的智能化为住户提供了一种更加安全、舒适、方便、快捷和开放的智能化、信息化的生活空间,极大的方便了用户。

因此,组建一套以家庭交互终端为核心的家居控制系统,对智能电网的改造和实施有重大的意义。

但目前的家居智能化系统存在一个很大的局限,即只是实现了局部的智能化。

而真正意义上的家居智能化则应该是拥有一个集中的终端控制系统,通过该终端对家居的所有设备进行智能化的控制和监控,这也将是智能家居系统未来的发展方向。

本设计以MIPS公司的32位处理器为核心来组建智能显示终端,并以具备无线通讯的智能插座为被控节点,搭建了一套简易的智能家居控制系统。

该系统可通过远程(手机短信),和本地(智能显示终端)两种方式进行控制。

下面将对本系统的构成和实现方案,以及各模块中涉及的关键问题进行分析。

二.系统的构成与工作原理1 系统构成与原理本系统由手机,智能显示终端,智能插座构成。

手机与智能显示终端之间通过GSM模块进行通讯,智能显示终端和智能插座之间采用Zigbee进行通讯。

智能插座作为基本的控制单元,能够实时采集每个房间的用电信息,并将信息实时传送到智能显示终端。

当发现用电异常时,智能插座自动断电并将执行结果发送到智能显示终端。

智能显示终端也将这一结果发送到用户手机。

手机实现用户的远程控制和信息接收。

用户外出时,通过手机发送的指令(如预启动,预关闭,限时供电等)将被智能终端接收并下发到智能插座。

另外,智能插座的所有执行动作都将通过智能显示终端发送到手机。

智能显示终端既能够接收手机发送的指令,也能够接收智能插座发送的数据。

智能显示终。

32位MIPS CPU设计

实验四32位MIPS CPU设计实验

1设计要求

使用Logisim 软件依次完成4 个子电路的设计,如下:

1. 指令译码器

2. 时序发生器状态机(定长指令周期)

3. 时序发生器输出函数(定长指令周期)

4. 硬布线控制器

在此基础上完成对“单总线CPU(3 级时序)”的联合调试,使之可以运行

简单的冒泡排序算法MIPS 汇编程序,实现排序功能。

2方案设计

2.1 指令译码器

原理:

根据MIPS指令格式表中各个指令的op字段,和IR送来的指令op字段比较,若相同则是该指令,注意SLT 指令还需要判断funct字段为101010,用异或门判断OtherInstr

电路:

图1指令译码器

2.2 时序发生器状态机(定长指令周期)

原理:

由于是定长指令周期,所以次态只和现态有关,Si->Si+1 (0<=i<=10),S11->S0

电路:

图2状态机

2.3 时序发生器输出函数(定长指令周期)

原理:

定长指令周期分为3个机器周期(取指,计算,执行)每个机器周期分为4个节拍S0~S3取指周期,S4~S7计算周期,S8~S11执行周期

每个机器周期内节拍递增

电路:

图3输出函数

2.4 硬布线控制器

原理:

状态暂存器输出到状态机计算出次态再返回状态寄存器,同时现态送到输出函数电路:

图4硬布线控制器

3实验步骤

按照设计连接电路,在电路图中“单总线CPU(3 级时序)”子电路中进行调试,测试CPU 是否可以正确执行冒泡排序程序

4测试与分析

发现数据6,5,4,3,2,1,-1按递减排序

实验结果符合预期。

32位MIPS处理器说明

32位MIPS处理器说明一、实验目的熟悉现代处理器的基本工作原理;掌握单周期和流水线处理器的设计方法。

二、实验原理及实验内容该32位MIPS处理器主要需要设计ALU、单周期、流水线。

下面分别讲述这三个部分的设计原理及实验内容。

1.ALUALU即算数逻辑单元,要求设计一个32位的ALU,实现基本的算术、逻辑、关系、位与移位运算。

输入32bit的A和B作为操作数,5bit的控制输入ALUFun和一位控制输入Sign,输出32bit的结果Z。

其功能表如下图所示:根据功能表和要求,我们在顶层模块中设计了32bit输入ALUSrc1和ALUSrc2,以及5bit控制ALUFunc,1bit控制Sign,32bit输出ALUOut。

设计了四个主要模块:ALU_ADD_SUB,ALU_CMP,ALU_Logic,ALU_Shift,并根据ALUFunc的值来确定使用的模块。

设计框图思路如下:(1)ALU_ADD_SUB这部分是ALU设计中最重要的一部分。

采用了8位超前进位级联,用与门来实现32位全加器。

减法由加法实现,在运算的开始由ALUFunc判断进行的是加法还是减法,如果是加法则直接将两个操作数输入全加器,最低进位为0,如果是减法则取ALUSrc2的反码之后再做加法运算,最低进位是1。

需要注意的是运算结束之后需要判断结果是否为0(这个在branch指令中尤为重要),是否为负数,还有是否溢出。

是否为溢出还需要检查控制符号,如果控制符号为有效(即有符号计算)则两正数相加得负或两负数相加得正则溢出,溢出则结果符号位反了,再进而判断是否为负。

若为无符号运算,加法结果溢出则最高进位为1,且结果不为负;减法结果溢出等价于结果为负,即最高进位为0。

而结果为0等价于全部位都取0。

(2)ALU_Shift移位运算分别有逻辑左移,逻辑右移,算术右移三种情况。

首先判断是逻辑移位还是算术移位来决定填充0还是填充逻辑位。

之后采取先将操作数根据左移还是右移的判断做出32位扩充,再根据shamt从最高位到最低位判断是否为0来决定取那几位操作数,最后得到移位的结果。

mips运算器设计的实验报告

mips运算器设计的实验报告MIPS运算器设计的实验报告在计算机科学领域,MIPS(Microprocessor without Interlocked Pipeline Stages)是一种常见的指令集架构,被广泛用于教学和研究。

MIPS运算器设计实验旨在通过实际操作,加深对MIPS指令集的理解,提高学生的计算机系统设计能力。

实验开始前需要明确设计的目标和功能需求。

在设计MIPS运算器时,需要考虑指令的执行流程、寄存器的设计、ALU的功能等关键要素。

设计者应该清楚每条指令的操作码、操作数及操作结果的存储位置,确保整个运算器的功能正常实现。

根据设计要求,搭建MIPS运算器的硬件结构。

在硬件设计中,需要考虑到时钟频率、数据通路的连接、控制信号的传输等方面。

合理的硬件设计是保证运算器正常运行的基础,需要对各个模块进行充分测试和调试,确保整个系统的稳定性和可靠性。

接着,进行指令集的编码和解码工作。

MIPS指令集包括常见的算术运算指令、逻辑运算指令、分支跳转指令等,设计者需要为每条指令赋予唯一的操作码,并实现指令的编码和解码功能。

编码和解码的准确性直接影响到指令的执行结果,需要仔细检查和验证每条指令的功能和操作。

进行仿真和调试工作。

通过仿真软件模拟MIPS运算器的运行过程,检查指令执行的正确性和时序的准确性。

在调试过程中,需要重点关注指令执行的过程中是否存在冲突和错误,及时修改和优化设计方案,确保运算器的功能完整和稳定。

总的来说,通过设计MIPS运算器的实验,可以帮助学生深入理解计算机系统的结构和工作原理,提高他们的设计和调试能力,培养他们的团队合作和问题解决能力。

同时,这也是一个很好的实践机会,让学生将理论知识应用到实际项目中,提升他们的综合素质和创新能力。

希望通过这样的实验,能够激发学生对计算机科学的兴趣,培养他们对技术研究的热情,为未来的科技发展做出贡献。

华中科技大学HUST类MIPS单周期微处理器设计实验报告

类MIPS单周期微处理器设计实验报告专业:班级:学号:姓名:一、微处理器各模块设计各模块的框图结构如上图所示。

由图可知,该处理器包含指令存储器、数据存储器、寄存器组、ALU单元、符号数扩张、控制器、ALU控制译码以及多路复用器等。

图中还忽略了一个单元:时钟信号产生器,而且以上各个部件必须在时钟信号的控制下协调工作。

1.指令存储器的设计指令寄存器为ROM类型的存储器,为单一输出指令的存储器。

因此其对外的接口为clk、存储器地址输入信号(指令指针)以及数据输出信号(指令)。

(1)在IP wizard 中配置ROM,分配128个字的存储空间,字长为32位宽。

(2)选择输入具有地址寄存功能,只有当时钟上升沿有效时,才进行数据的输出。

(3)配置ROM内存空间的初始化COE文件。

最后单击Generate按钮生成IROM模块。

2.数据存储器的设计数据存储器为RAM类型的存储器,并且需要独立的读写控制信号。

因此其对外的接口输入信号为clk、we、datain、addr;输出信号为dataout。

数据存储器基本建立过程同ROM的建立。

3.寄存器组设计寄存器组是指令操作的主要对象,MIPS中一共有32个32位寄存器。

在指令的操作过程中需要区分Rs、Rt、Rd的地址和数据,并且Rd的数据只有在寄存器写信号有效时才能写入,因此该模块的输入为clk、RegWriteAddr、RegWriteData、RegWriteEn、RsAddr、RtAddr、reset;输出信号为RsData、RtData。

由于$0一直输出0,因此当RsAddr、RtAddr为0时,RsData以及RtData 必须输出0,否则输出相应地址寄存器的值。

另外,当RegWriteEn有效时,数据应该写入RegWriteAddr寄存器。

并且每次复位时所有寄存器都清零。

代码如下:module regFile(input clk,input reset,input [31:0] regWriteData,input [4:0] regWriteAddr,input regWriteEn,output [31:0] RsData,output [31:0] RtData,input [4:0] RsAddr,input [4:0] RtAddr);reg[31:0] regs[0:31];assign RsData = (RsAddr == 5'b0)?32'b0:regs[RsAddr];assign RtData = (RtAddr == 5'b0)?32'b0:regs[RtAddr];integer i;always @(posedge clk)beginif(!reset)beginif(regWriteEn==1)beginregs[regWriteAddr]=regWriteData;endendelsebeginfor(i=0;i<31;i=i+1)regs[i]=0;regs[31]=32'hffffffff;endendendmodule4.ALU设计在这个简单的MIPS指令集中,微处理器支持add、sub、and、or、slt运算指令,需要利用ALU单元实现运算,同时数据存储指令sw、lw也需要ALU单元计算存储器地址,条件跳转指令beq需要ALU来比较两个寄存器是否相等。

mips控制器设计实验原理

mips控制器设计实验原理MIPS(Microprocessor without Interlocked Pipelined Stages)是一种32位的RISC (Reduced Instruction Set Computing)处理器架构,旨在提高处理器效率和性能。

MIPS 架构的处理器被广泛应用于各种领域,包括计算机、嵌入式系统、网络设备、数字信号处理等需要高性能的应用中。

在本实验中,我们将学习如何设计一个基于MIPS控制器的处理器。

控制器是一个能够控制处理器各个子系统如存储器、算术逻辑单元(ALU)、输入/输出设备等的模块。

MIPS控制器的设计是关键,因为它可以决定处理器的运行效率和性能。

MIPS控制器的设计需要考虑以下几个方面:1. 指令解码MIPS指令集包含了大量的指令,但是由于指令采用RISC架构,指令集中的每一个指令都很简单,只有少量的寄存器、立即数和内存操作。

控制器需要能够识别每一个指令,并正确地解码指令中的操作数。

为了实现这个目标,控制器需要包含适当的译码电路和其他必要的逻辑门电路。

2. 流水线控制流水线是一种增加处理器效率和性能的技术,通过将指令的执行拆分为多个阶段,多个指令可以在同一时刻被处理。

MIPS架构使用了5级流水线结构,即取指令、指令译码、执行、访问存储器和写回结果。

控制器需要能够控制流水线的各个阶段,确保它们按照正确的顺序执行。

3. 异常处理处理器在执行指令时可能会出现各种错误,如未定义的指令、内存访问冲突、算术溢出等。

这些错误称作异常。

处理器需要能够捕获异常并采取适当的措施,如停止当前指令的执行、中断指令流并处理异常。

控制器需要包含适当的硬件和逻辑电路来处理异常。

4. 输入/输出一个处理器需要有输入/输出接口来连接外部设备,如键盘、鼠标、显示器、网络等。

这些设备通过输入输出端口(I/O端口)与处理器相连。

控制器需要能够控制I/O端口的数据传输,并确保数据在正确的时刻被传输。

位MIPS处理器设计实验报告

数字逻辑与处理器基础实验32位MIPS处理器设计实验报告王晗(2013011076)July26,2015Date Performed:July15,2015Partners:耿天毅(2012011119)陈志杰withdrawn1实验目的熟悉现代处理器的基本工作原理;掌握单周期和流水线处理器的设计方法。

2设计方案2.1总体结构由于这次实验涉及的功能较多,我们将完整的CPU分成多个模块。

指令存储器、寄存器堆、控制器、ALU控制器、ALU、数据存储器、UART等功能单元均在单独的Module中实现。

其中指令存储器、寄存器堆、控制器、ALU控制器、ALU等单元在Single Cycle Core中实例化,作为单周期处理器的核心;数据存储器、UART和定时器、LED、七段数码管、开关在Peripheral中实现,作为处理器的外设。

处理器核心和外设在顶层模块中实例化,互相通信。

单周期CPU模块的结构关系如Figure1所示:Figure1:单周期处理器结构对于流水线CPU,我们还在Pipeline Core中加入了流水线寄存器、冒险检测单元、数据转发单元:Figure2:流水线处理器结构2.2ALU1ALU模块的结构如图所示,输入两个操作数A、B和控制信号ALUFun、Signed,在ARITH子模块中做加减法运算,CMP子模块根据ARITH模块的输出进行比较判断,LOGIC和SHIFT模块分别进行逻辑运算和移位运算,ALUFun的最高两位用于控制多路选择器的输出。

Figure3:ALU结构ARITH模块ARITH模块中包括减法和加法两个模块,加法模块直接通过+号运算,减法模块先对第二个操作数取补码,再调用加法模块做加法运算。

Overflow和Negative信号的产生是ALU中的难点:Figure4:ADD中的Overflow和Negative1原作者:陈志杰;修改:王晗其中pos为正数,neg为负数,big为MSB=1的无符号数,small为MSB=0的无符号数。

基于32位MIPS指令集的ALU及CP0模块的设计的开题报告

基于32位MIPS指令集的ALU及CP0模块的设计的开题报告一、选题背景嵌入式系统是指通过计算机技术将计算机系统嵌入到各种电子设备中,以完成特定的控制、测量、表示等功能的系统。

这种嵌入范围包含了很多领域,如汽车、航空航天、医疗、机器人等。

嵌入式系统要求硬件的体积小、功耗低、性能高,因此需要采用一种紧凑的指令集架构,即RISC(精简指令集计算机)。

RISC是一种基于硬件的优化技术,能够提高芯片的性能。

为了实现高效的嵌入式系统,需要对硬件进行优化,其中又尤为重要的是CPU,特别是ALU和CP0模块。

二、选题意义该选题的目的是设计基于32位MIPS指令集的ALU及CP0模块,优化CPU的执行效率,提高嵌入式系统的性能。

ALU模块是处理器中的一个基本硬件模块,负责运算操作,可以实现基本的算术、逻辑运算,而CP0模块是状态寄存器模块,控制着计算机系统的各种状态和异常处理,能够提高系统的可靠性。

优化ALU和CP0模块的设计可以提高MIPS处理器的性能和效率,使得嵌入式系统具有更好的性能和稳定性,具有重要的应用意义。

三、选题内容本文将涵盖以下内容:1. MIPS指令集概述2. ALU模块的设计与实现3. CP0模块的设计与实现4. 模块的集成与测试5. 优化策略与性能测试四、预期成果1. 实现一个基于32位MIPS指令集的ALU模块,实现基本的算术、逻辑运算。

2. 实现一个可靠的CP0模块,可以进行状态寄存器的读写操作,能够控制系统状态和异常处理。

3. 对两个模块进行集成和测试,考虑到延迟和吞吐量等因素,在保证正确性的前提下尽量提高系统的性能。

4. 对模块进行优化,优化策略包括流水线和并行处理等,通过性能测试获得优化后的实验结果。

五、研究方法选题基于MIPS指令集的ALU及CP0模块的设计,方法主要有:1. 对MIPS指令集进行分析,了解指令的类型、格式和执行过程。

2. 设计ALU模块并实现各种运算操作。

3. 设计CP0模块完成状态寄存器的读写操作。

湘潭大学计算机原理实验四多周期MIPSCPU+存储器实验预习报告

实验四多周期MIPS CPU +存储器实验一.实验目的1、深入理解MIPS—CPU指令系统的功能和工作原理;2、掌握多周期CPU的工作原理和逻辑功能实现;3、熟练掌握用Verilog HDL语言设计多周期存储器的方法;4、熟练掌握对多周期存储器的仿真实验验证和硬件测试两种调试方法;5、通过对多周期CPU的运行情况进行观察和分析,进一步加深理解。

二.实验设备硬件:现代计算机组成原理实验系统(兼)Nios 32位嵌入式系统实验开发平台EP1C12Q240Core(TM)i3-3240 CPU@3.40GHz 3.39GHz 1.91GB的内存软件:QuartusII 13.0sp1Microsoft Windows xp三.实验内容1、设计一个32位MIPS多周期CPU具体的要求如下:至少运行下列的6类32条MIPS指令。

(1)算术逻辑指令and、sub、addi(2)逻辑运算指令and、0r、xor、andi、ori、xori(3)位移指令sll、srl、sra(4)条件分支指令beq、bne、(5)无条件跳转指令j、jr(6)数据传送指令lw、sw2.设计一个存储器四.实验原理与步骤实现上述原理框图根据功能将其分划分为控制单元(cunit)、执行单元(eunit)、指令单元(iunit)以及存储单元(munit)四大模块。

(1).控制单元(cunit)是多周期微处理器的核心控制微处理器取指令、指令译码和指令执行等工作。

主要由指令译码器控制器(outputs control)、算术逻辑运算控制器(ALU control)两个子模块组成。

(2).执行单元(eunit)主要由寄存器堆(registers)和算术逻辑单元(ALU)两个子模块组成。

其中寄存器是微处理器最基本的元素MIPS系统的寄存器堆由32个32位寄存器组成而ALU则是微处理器的主要功能部件执行加、减、比较等算术运算和与、或、或非、异或等逻辑运算。

数字系统设计实验流水线MIPS微处理器设计

数字系统设计实验流水线MIPS微处理器设计一、实验目的(1)了解提高CPU性能的方法。

(2)理解数据冒险、控制冒险的概念以及流水线冲突的解决方法。

(3)掌握流水线MIPS微处理器的工作原理。

(4)掌握流水线MIPS微处理器的测试方法。

二、实验任务设计一个32位流水线MIPS微处理器,具体要求如下设计要求:(1)至少执行下列MIPS32指令。

①算数运算指令:ADD ADDU SUB SUBU ADDI ADDU②逻辑运算指令:AND OR NOR XOR ANDI ORI XORI SLT SLTISLTU SLTIU③移位指令:SLL SLLV SRL SRLV SRA④条件分支指令:BEQ BNE BGEZ BGTZ BLEZ BLTZ⑤无条件跳转指令:J JR⑥数据传输指令:LW SW⑦空指令:NOP(2)在用5级流水线技术,对数据冒险实现转发或阻塞功能。

(3)在XUP Vietex-II Pro开发系统中实现MIPS微处理器,要求CPU的运行速度大于25MHz.三、实验原理1.流水线MIPS CPU总体设计流水线是数字系统中一种提高系统稳定性和工作速度的方法,广泛应用在高档CPU的构建中。

根据MIPS处理器指令的特点,将整体的处理过程分为取指令(IF)、指令译码、执行、存储器访问和寄存器写回五级,对应多周期CPU的五个处理阶段。

如图1所示,一个指令的执行需要五个时钟周期,每个时钟周期上升沿来临时,此指令所代表的一系列数据和控制信息转移到下一级处理。

图1 流水线流水作业示意图一条MIPS指令分为五个处理步骤,即五级流水线,的具体执行过程如图2所示。

图2 五级流水线MIPS CPU初步原理框图流水线寄存器:为了在其它四级流水线中各条指令保持各自的值,从指令存储器中读出的指令必须保存在寄存器中。

同样的方法应用到每个流水线步骤中,需要在上图中各级之间加入寄存器,如图3所示。

图3.在各级分割线添加寄存器后的框图由于在流水线中,数据和控制信息将在时钟上升沿转移到下一级,所以规定流水线转移的变量命名遵守如下格式:名称_流水线级名称。

mips文档

mips文档MIPS(子集)CPU设计报告在本学期,我们学习了微处理设计这门课程,在学习过程中我们选用的是MIPS指令集,它是一个32位的精简指令集。

鉴于时间和自己设计水平的考虑,在本设计中,只采用了MIPS中的若干指令,主要是要掌握好设计的整个流程。

对处理器的整体架构的把握,数据通路的搭建以及控制逻辑设计是本设计的主要目的。

一、MIPS设计整体架构及设计要求1. 采用32 位的指令长度,所有的数据总线宽度为32位,地址总线为8位。

这是因为在设计当中,存储器的设计是采用寄存器文件的形式,加上指令数目比较少,因此8位的地址总线是可以达到设计的要求。

2.搭建一个多周期的数据通路,一是为了提高设计的主频,另外一个就是为搭建流水线的数据通路提供一个平台。

3.存储器结构采用哈佛结构,即指令存储器和数据存储器分开。

尽管在指令的执行过程中,计算得到的地址都是32位,但是在本设计中,只取其中的低8位。

4.指令集的选取。

在本设计中,选用的一个算法是:对n个数进行求和,然后把最大的那个数找出来。

(1)C语言的实现:int a[5];int i, mux,sum;sum=0;for(i=0;i<5; i++){ if(a[i]>=mux)mux=a[i];elsemux=mux;sum=sum+a[i];};(2) MIPS汇编语言的实现:Fact: LW $t0,0($zero);LW $t1,1($zero);LW $t2,2($zero);LW $t3,3($zero);LW $t4,4($zero);ADD $s1,$t0,$t1;COMP $s0,$t0,$t1;ADD $s1,$s1,$t2;COMP $s0,$s0,$t2;ADD $s1,$s1,$t3;COMP $s0,$s0,$t3;ADD $s1,$s1,$t4;COMP $s0,$s0,$t4;SW $S0,5($zero);SW $s1,6($zero);JUMP fact;有上面的算法分析,可以得知,在本设计中只用到了五种指令,但是这五种指令却包括了MIPS指令的三大类型:R型,J型,I型。

CPU实验——单周期MIPS处理器设计

单周期MIPS处理器设计实验报告完成人:笪腾飞2012011263一、实验目的1、设计一个32位的单周期MIPS处理器,具备定时器、数码管等外设;2、编写一个编译器,可以将mips代码编译为二进制机器码;3、编写一个计算两个整数的最大公约数的汇编程序。

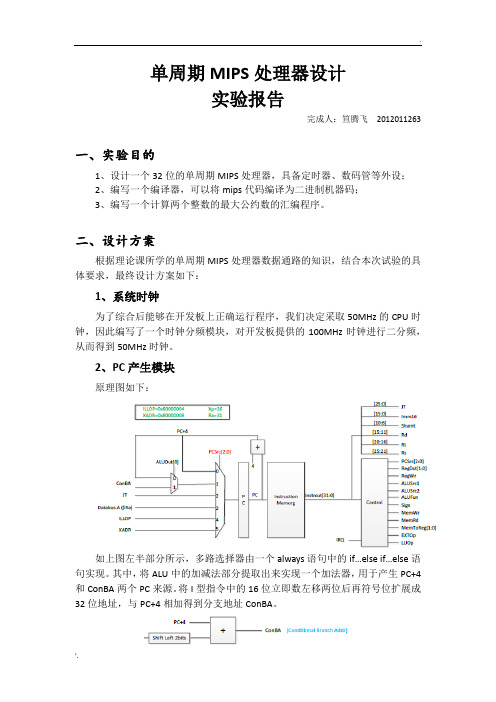

二、设计方案根据理论课所学的单周期MIPS处理器数据通路的知识,结合本次试验的具体要求,最终设计方案如下:1、系统时钟为了综合后能够在开发板上正确运行程序,我们决定采取50MHz的CPU时钟,因此编写了一个时钟分频模块,对开发板提供的100MHz时钟进行二分频,从而得到50MHz时钟。

2、PC产生模块原理图如下:如上图左半部分所示,多路选择器由一个always语句中的if…else if…else语句实现。

其中,将ALU中的加减法部分提取出来实现一个加法器,用于产生PC+4和ConBA两个PC来源。

将I型指令中的16位立即数左移两位后再符号位扩展成32位地址,与PC+4相加得到分支地址ConBA。

将跳转指令中的26位目标地址左移两位后,与当前PC的高四位拼接得到跳转地址JT。

将第一个操作数寄存器中的值取出作为PC的一个输入,这是为了实现jr和jalr指令,从$Xp和$Ra寄存器中读取跳转地址。

ILLOP和XADR分别是发生中断和异常时的跳转地址。

下一指令地址的选择由PCSrc决定,而PCSrc是译码后由控制信号模块根据每条指令的操作码(opcode)和函数码(funct)产生。

3、译码模块原理图如上图右半部分所示,将PC作为ROM模块的地址输入,输出即为PC所对应的指令。

分别取出指令中的某些片段,得到$Rs,$Rt,$Rd,shamt,funct,16位立即数和26位跳转地址。

4、控制模块控制模块即控制信号产生模块,六位操作码OpCode,六位函数码[5:0] Funct,定时器中断信号irq和PC最高位PC31作为输入,输出为以下控制信号:(1) R型指令指示信号IsR,值为1表示当前指令为R型指令,否则非R型指令;(2) PC产生的选择信号[2:0] PCSrc,取值0,1,2,3,4及其它,分别选择下一指令不同的PC;(3) 目的寄存器选择信号[1:0]RegDst,被写入的寄存器有四种选择:$Rd,$Rt,$Ra,$Xp,分别由RegDst不同取值完成选择;(4) 写寄存器使能信号RegWr,值为1表示允许对寄存器进行写操作;(5) ALU第一个操作数选择信号ALUSrc1,值为1表示选择将移位量shamt进行0扩展后作为输入,值为0表示将$Rs寄存器中的值作为输入;(6) ALU第一个操作数选择信号ALUSrc1,值为1表示选择将扩展后的32位立即数作为输入,值为0表示将$Rt寄存器中的值作为输入;(7) ALU运算控制信号[5:0] ALUFunc,作为ALU的输入选择不同的运算操作;(8) 有无符号数指示信号Sign,值为1表示有符号数,值为0表示无符号数;(9) 写存储器使能信号MemWr,值为1表示允许对存储器进行写操作;(10) 读存储器使能信号MemRd,值为1表示允许对存储器进行读操作;(11) 写寄存器值的选择信号[1:0] MemToReg,选择ALU结果,存储器读取结果和PC+4其中之一作为写入目的寄存器的值;(12) 符号位扩展指示信号EXTOp,值为1表示对16位立即数进行符号位扩展,值为0表示0扩展;(13) 立即数高位取指令指示信号LUOp,值为1表示当前指令为lui指令,选择将立即数载入高16位低位填0的32位立即数作为ALU输入,值为0表示将正常扩展后的32位立即数作为ALU输入;控制信号的具体产生过程此处略去,在控制信号说明文件中进行详述。

32位MIPS处理器设计实验报告

数字逻辑与处理器基础实验32位MIPS处理器设计实验报告王晗(2013011076)July26,2015Date Performed:July15,2015 Partners:耿天毅(2012011119)陈志杰withdrawn1实验目的熟悉现代处理器的基本工作原理;掌握单周期和流水线处理器的设计方法。

2设计方案2.1总体结构由于这次实验涉及的功能较多,我们将完整的CPU分成多个模块。

指令存储器、寄存器堆、控制器、ALU控制器、ALU、数据存储器、UART等功能单元均在单独的Module中实现。

其中指令存储器、寄存器堆、控制器、ALU控制器、ALU等单元在Single Cycle Core中实例化,作为单周期处理器的核心;数据存储器、UART和定时器、LED、七段数码管、开关在Peripheral中实现,作为处理器的外设。

处理器核心和外设在顶层模块中实例化,互相通信。

单周期CPU模块的结构关系如Figure1所示:1Figure1:单周期处理器结构对于流水线CPU,我们还在Pipeline Core中加入了流水线寄存器、冒险检测单元、数据转发单元:Figure2:流水线处理器结构22.2ALU1ALU模块的结构如图所示,输入两个操作数A、B和控制信号ALUFun、Signed,在ARITH子模块中做加减法运算,CMP子模块根据ARITH模块的输出进行比较判断,LOGIC和SHIFT模块分别进行逻辑运算和移位运算,ALUFun的最高两位用于控制多路选择器的输出。

Figure3:ALU结构ARITH模块ARITH模块中包括减法和加法两个模块,加法模块直接通过+号运算,减法模块先对第二个操作数取补码,再调用加法模块做加法运算。

Overflow和Negative信号的产生是ALU中的难点:Figure4:ADD中的Overflow和Negative1原作者:陈志杰;修改:王晗3其中pos为正数,neg为负数,big为MSB=1的无符号数,small为MSB=0的无符号数。

32位MIPS CPU 设计 实验报告详解

数字逻辑与处理器基础实验32位MIPS CPU设计综述:我们的最后验收结果时钟频率是84.9MHz。

本实验报告主要分为实验设计说明与实验收获总结两个部分。

附件中有CPU工程文档与模块代码。

第一部分实验设计一、ALU设计1、设计思路实现基本的算术、逻辑、关系、位与移位运算,尽量优化以达到最小的面积延时积。

结构图如下:主要设计思想:A. 加法运算实现可以采用逐次进位、超前进位等结构,减法可以通过加法实现(参见见面理论课讲义或者前面实验);同时输出Z(结果为零)、V(结果溢出)、N(结果为负)等标志位,注意有符号数和无符号数标志产生的不同。

B. 比较运算根据减法运算的结果(Z/V/N)产生,自行分析比较操作与算术运算之间的关系。

C. 移位运算可以考虑将移位操作拆分为16 位移位、8 位移位、4 位移位、2 位移位、1位移位等几个子运算的组合,然后级联形成最后的运算结果。

D. 逻辑运算可以根据要求直接产生。

功能表接口说明2、主要模块a)32bit加法器采用8个4bit超前进位加法器极连的方式,构成32bit加法器。

对于逸出位v的处理如下:由有符号数的性质可知,对最高位32和次高位31位取抑或,输出信号则为是否逸出。

对32位运算结果取反后,再对相邻两位反复取与,最终得到结果是否为零的输出z.如果是有符号数,则符号位=n。

由于这一方法部分程度上减弱了高位计算对低位计算的依赖程度,因此可以实现延时的降低。

同时,由于其超前进位网络的大量逻辑运算,较大程度上提升了电路的面积,造成最终的面积延时积特性恶化。

关键代码见附录1b)32bit减法器对加法器按位取反,再加一。

关键代码见附录1c)32bit 右移32bit 左移32bit 算术右移将移位操作拆分为16 位移位、8 位移位、4 位移位、2 位移位、1位移位等几个子运算的组合,然后级联得到最后的运算结果。

关键代码见附录1d)32bit 逻辑比较单元采用行为级语句直实现逻辑比较功能。

西安交通大学组成专题实验报告

西安交通大学组成专题实验报告计算机组织与结构专题实验报告 MIPS单周期处理器的设计学生姓名赵荣建专业班级计算机45班学号2140505119 指导教师姜欣宁完成日期 2021-05-09一.实验目的根据所学的CPU组成原理,自主设计一个MIPS32位的单周期处理器。

二.设计方案参照计算机组成原理教材上的MIPS32位处理器的工作原理。

1.构建数据通路取指令指令译码指令执行存储器访问结果写回取指周期:a.从指令寄存器PC输出端得到地址b.送地址到指令存储器IM地址端Ac.从指令存储器IM的数据端RD得到指令d.计算下地址:通过运算器,PC+4形成下地址,送回到PC。

2. .MIPS 寄存器集:定义了32个32位的寄存器3.MIPS三种指令格式:R-类型、I-类型和J-类型R-类型格式:* 所有指令操作吗OP都是0;特定操作由funct决定。

* 机器语言指令中,字段分配格式如上图;前两个寄存器rs、 rt是源寄存器,rd是目的寄存器。

而在汇编语言格式中,第一个寄存器是目的寄存器。

如:add $t0,$s4,$s5 #[rd]=[rs]+[rt],[t0]=[s4]+[s5]; I-类型格式:* 指令含4个字段;op, rs, rt 和 imm* 有两个寄存器操作数和一个16位立即数操作数,一些指令中,rt也可作为源寄存器。

J-类型格式:* 有一个26位立即数操作数,扩展后形成目的地址。

4.算逻单元ALU的设计<<210Add<<2JumpMemToReg4Add01ControlMemReadMemWriteBranchALUopALUsrcRegWriteIn structionMemoryPC0R1Rdata132R21RegisterFileW1WdataALU32zeroResult32AddrRdata20212DataData0321Memory3Wdata{15~0}sign32 extend2ALUcontrol6{5~0}ALU工作原理图BA321zeroALU3232Result* 两级控制:通过系统控制器(Control)3ALUoperFunc6ALUcontrol2ALUop 和运算器控制器(ALU Control)产生 ALU的控制信号:ALUoper* ALU控制信号对照表:ALUop Func(来自R型指令的func字段)操作 ALUop1 ALUop2 F5 0 0 1 1 1 1 1 0 1 × × × × × × × × × × × × F4 × × × × × × × F3 × × 0 0 0 0 1 F2 × × 0 0 1 1 0 F1 × × 0 1 0 0 1 F0 × × 0 0 0 1 0 010:ADD 110:SUB 010:ADD 110:SUB 000:AND 001: OR 111:SLT 5.单周期数据通路的构建1)构件:PC、指令存储器、寄存器文件RF和数据存储器; 2)取指令的过程:PC→IM: A/RD3)取源操作数的过程:IM:RD→RF:A1/RD1。

基于MIPS指令集的32位RISC处理器逻辑设计

本科生毕业论文题目:基于MIPS指令集的32位RISC处理器逻辑设计院系:信息科学与技术学院专业:计算机科学与技术学生姓名:***学号:********指导教师:李国桢副教授二〇〇九年四月摘要CPU是计算机系统的核心部件,在各类信息终端中得到了广泛的应用。

处理器的设计及制造技术也是计算机技术的核心之一。

MIPS是世界上很流行的一种RISC 处理器。

MIPS的意思是“无内部互锁流水级的微处理器”(Microprocessor without interlocked piped stages),其机制是尽量利用软件办法避免流水线中的数据相关问题。

本文在详细研究32位MIPS处理器体系结构的基础之上,在Quartus II 7.2环境中,完全依靠自己的研发设计能力,采用硬件描述语言VHDL完成了拥有自主知识产权的基于MIPS指令集的32位RISC处理器的逻辑设计。

共开发出单周期、多周期、五级流水线等3个不同版本的32位RISC处理器,均通过Quartus II进行了时序仿真和性能比较分析。

本文的首先概述了MIPS指令集的重要特征,为讨论CPU的具体设计奠定基础。

本文设计的3个版本的CPU均实现了一个共包含59条指令的32位MIPS指令子集。

本文的主体部分首先详细描述了处理器各个独立功能模块的设计,为后续的整体设计实现提供逻辑功能支持。

随后按照单周期、多周期、流水线的顺序,循序渐进的围绕着指令执行过程中需经历的五个阶段,详细描述了3个版本的处理器中各阶段的逻辑设计。

在完成了各个版本的CPU的整体逻辑设计后,通过Quartus II时序仿真软件在所设计的CPU上运行了测试程序,测试输出波形表明了处理器逻辑设计的正确性。

本文还通过Quartus II 7.2中的Quartus II Time Quest Timing Analyzer软件,基于Altra公司的FPGA器件比较分析了所设计的3个版本CPU的性能。

mips实验报告

mips实验报告MIPS实验报告引言:计算机体系结构是计算机科学中的重要研究领域,而MIPS(Microprocessor without Interlocked Pipeline Stages)是一种经典的RISC(Reduced Instruction Set Computer)体系结构。

本实验报告将介绍我对MIPS实验的理解和实践,包括MIPS指令集的基本特点、实验环境的搭建、以及在MIPS架构下编写和运行程序的过程。

一、MIPS指令集的基本特点MIPS指令集是一种精简的指令集,其特点主要包括以下几点:1. 定长指令格式:MIPS指令采用32位定长指令格式,使得指令解码和执行过程更加高效。

2. 延迟槽:MIPS指令集中的延迟槽是指在分支指令后的一条指令,它总是会被执行,无论分支是否发生。

这种设计可以提高指令流水线的效率。

3. 五种指令格式:MIPS指令集包括R格式、I格式、J格式、COP0格式和COP1格式,分别用于处理寄存器相关操作、立即数操作、跳转操作、协处理器0操作和协处理器1操作。

4. 寄存器:MIPS体系结构中有32个通用寄存器,可以进行高速数据传递和操作。

二、实验环境的搭建为了进行MIPS实验,我们需要搭建相应的实验环境。

在本次实验中,我选择使用MARS(MIPS Assembler and Runtime Simulator)作为MIPS实验的模拟器。

MARS提供了一个图形化界面,可以方便地进行MIPS程序的编写、调试和运行。

搭建实验环境的步骤如下:1. 下载和安装MARS:从MARS官方网站上下载最新版本的MARS软件,并按照提示进行安装。

2. 配置MARS:打开MARS软件后,点击“Settings”菜单,选择“MIPS Assembler”选项卡。

在这里,我们可以设置MIPS汇编程序的语言类型、字符集和显示格式等。

3. 编写MIPS程序:在MARS的编辑器中,我们可以编写MIPS程序。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字逻辑与处理器基础实验32位MIPS处理器设计实验报告王晗(2013011076)July26,2015Date Performed:July15,2015Partners:耿天毅(2012011119)陈志杰withdrawn1实验目的熟悉现代处理器的基本工作原理;掌握单周期和流水线处理器的设计方法。

2设计方案2.1总体结构由于这次实验涉及的功能较多,我们将完整的CPU分成多个模块。

指令存储器、寄存器堆、控制器、ALU控制器、ALU、数据存储器、UART等功能单元均在单独的Module中实现。

其中指令存储器、寄存器堆、控制器、ALU控制器、ALU等单元在Single Cycle Core中实例化,作为单周期处理器的核心;数据存储器、UART和定时器、LED、七段数码管、开关在Peripheral中实现,作为处理器的外设。

处理器核心和外设在顶层模块中实例化,互相通信。

单周期CPU模块的结构关系如Figure1所示:Figure1:单周期处理器结构对于流水线CPU,我们还在Pipeline Core中加入了流水线寄存器、冒险检测单元、数据转发单元:Figure2:流水线处理器结构2.2ALU1ALU模块的结构如图所示,输入两个操作数A、B和控制信号ALUFun、Signed,在ARITH子模块中做加减法运算,CMP子模块根据ARITH模块的输出进行比较判断,LOGIC和SHIFT模块分别进行逻辑运算和移位运算,ALUFun的最高两位用于控制多路选择器的输出。

Figure3:ALU结构ARITH模块ARITH模块中包括减法和加法两个模块,加法模块直接通过+号运算,减法模块先对第二个操作数取补码,再调用加法模块做加法运算。

Overflow和Negative信号的产生是ALU中的难点:Figure4:ADD中的Overflow和Negative1原作者:陈志杰;修改:王晗其中pos为正数,neg为负数,big为MSB=1的无符号数,small为MSB=0的无符号数。

Figure5:SUB中的Overflow和Negative图中的缩写含义同上。

CMP模块CMP模块直接根据ARITH模块产生的Zero,Overflow,Negative进行关系判断。

LOGIC模块LOGIC模块直接根据ALUFun[3:0]指定的逻辑运算进行运算。

SHIFT模块将移位操作拆分为16位移位、8位移位、4位移位、2位移位、1位移位,分别用Shamt 的每一个bit位控制,组合产生最后的运算结果。

2.3寄存器堆、指令存储器、数据存储器和外设2寄存器堆直接采用reg[31:0]RF_DATA[31:1]实现,注意RF_DATA[0]不存在,读取时直接返回0。

指令存储器将机器码以十六进制文本的形式存放在.rom文件中,使用$readmemh系统任务初始化一个大小为256words的只读存储器。

数据存储器由于数据存储器容量设计为256words,因此寻址时只根据address[9:2]寻址。

另外,0x40000000开始的地址用于外设编址,因此数据存储器不对0x40000000开始的地址进行读写操作。

其他外设定时器、LED、Switch参考老师提供的样例代码直接在Peripheral.v中实现,UART使用春季学期第四次实验的UART发送和接收模块,将发送模块中Tx_Status的定义取反,即1表示发送端忙碌。

UART的控制同样在Peripheral.v中实现,当0x40000018写入要发送的数据时,串口控制器自动产生一个发送使能信号。

2作者:王晗2.4控制器和ALU控制器3控制单元采用两级控制的实现方法,在主控制器中根据OpCode和Funct产生PCSrc、RegWrite、RegDst、MemRead、MemWrite、MemToReg、ALUSrc1、ALUSrc2、ExtOp、LuOp、ALUOp等控制信号,其中ALUOp经过ALU控制器进一步解码生成ALUFunc、Signed信号,控制ALU的运算,其余信号控制数据通路中的多路选择器。

控制器还产生了UndefinedInst信号,用于识别未定义指令的异常。

在单周期CPU中,PCSrc信号位宽为2,分别指示从PC+4、Branch Target、Jump Target、Jump Register取出下一个指令地址,当发生中断或异常时,由Single-Cycle Core直接跳转至中断或异常服务程序入口。

在流水线CPU中,为了方便流水线寄存器操作,将PCSrc信号位宽扩展至3,当发生中断或异常,PCSrc变为100或101,指示中断或异常服务程序入口。

2.5单周期数据通路4Figure6:单周期数据通路3作者:王晗4作者:王晗a.当没有中断或异常时,根据PCSrc取出下一个PC地址,并读取指令;否则跳转至中断或异常服务程序。

b.RegDst控制写入的目标寄存器:R型指令写入Rd;I型指令写入Rt;jal/jalr指令写入$31;中断或异常写入$26。

c.ExtOp控制立即数的符号扩展或无符号扩展。

d.LuOp控制立即数左移16位,用于lui指令。

e.ALUSrc1用于选择RegReadData1或Shamt作为ALU的第一个操作数,ALUSrc2用于选择RegReadData2或立即数作为ALU的第二个操作数。

f.MemRead、MemWrite控制外设和数据存储器的读写。

g.MemToReg用于选择写入寄存器的数据来源:运算指令来源为ALU输出,lw指令来源为Mem-ReadData,jal/jalr/中断/异常来源为PC+4。

h.PC的最高位为监督位,不用于寻址。

当PC[31]=1时为内核态,禁止中断请求;当PC[31]=0时为正常态,允许中断请求。

Reset、异常、中断可以将PC[31]置1,jr、jalr可以将PC[31]清零。

2.6流水线数据通路5Figure7:流水线数据通路5a.在单周期数据通路的基础上添加流水线寄存器。

b.添加数据转发单元,从EX/MEM或MEM/WB寄存器转发数据,解决ALU运算中的数据关联问题。

c.完善数据转发单元,从ALUOut、MemReadData、RegWriteData转发数据,解决jr指令的数据关联问题。

d.添加冒险检测单元,对存在load-use竞争的指令阻塞一个周期,禁止PC寄存器写入、清空ID/EX寄存器。

e.完善冒险检测单元,在EX阶段进行分支时,需要清空IF/ID和ID/EX寄存器。

f.完善冒险检测单元,在ID阶段进行跳转时,需要清空IF/ID寄存器。

2.7汇编代码6Supplementary report will be submitted separately.2.8汇编器7Supplementary report will be submitted separately.3关键代码及文件清单3.1寄存器堆的读写8寄存器堆在同一周期对同一个寄存器先写再读不会引起数据冒险,为了实现这个目的,先对读取的寄存器地址做判断,如果读取地址为0,则返回0;如果读取地址和写入地址相同,则返回写入的值;其他情况返回寄存器堆中相应寄存器的值。

regfile.vassign data1=(addr1==5'b0)?32'b0:(addr1==addr3)?data3:RF_DATA[addr1];3.2数据转发单元9对于ALU运算的指令,输入数据来自寄存器堆时,可能存在数据冒险。

为了解决这个问题,可以从EX/MEM或MEM/WB寄存器转发数据到ALU输入端。

从EX/MEM转发的条件是前一条指令需要写非$0寄存器,且写入地址和欲读取地址相等;从MEM/WB转发的条件是前两条指令需要写非$0寄存器,欲读取的地址和写入地址相等,并且不能从前EX/MEM就近转发。

6作者:耿天毅7作者:耿天毅8作者:王晗9ForwardUnit.vif(EX_MEM_RegWrite==1'b1&&EX_MEM_RegWriteAddr!=5'h00&&EX_MEM_RegWriteAddr==ID_EX_InstRs)ForwardA=2'b10;5else if(MEM_WB_RegWrite==1'b1&&MEM_WB_RegWriteAddr!=5'h00&&MEM_WB_RegWriteAddr==ID_EX_InstRs)ForwardA=2'b01;else10ForwardA=2'b00;//ForwardB is similar to this.对于jr指令,同样存在数据冒险。

由于跳转操作在ID阶段完成,如果检测到jr的目标寄存器和ID_EX段写入寄存器相同,需要从ALUOut转发数据;如果目标寄存器和EX_MEM段写入寄存器相同,需要从MemReadData转发数据;如果目标寄存器和MEM_WB段写入寄存器相同,则需要从RegWriteData转发数据。

ForwardUnit.vif(ID_PCSrc==3'b011&&IF_ID_InstRs==ID_EX_RegWriteAddr&&ID_EX_RegWriteAddr!=0&&ID_EX_RegWrite)ForwardJr=2'b01;else if(ID_PCSrc==3'b011&&5IF_ID_InstRs!=ID_EX_RegWriteAddr&&IF_ID_InstRs==EX_MEM_RegWriteAddr&&EX_MEM_RegWrite&&EX_MEM_RegWriteAddr!=0)ForwardJr=2'b10;10else if(ID_PCSrc==3'b011&&IF_ID_InstRs!=ID_EX_RegWriteAddr&&IF_ID_InstRs!=EX_MEM_RegWriteAddr&&IF_ID_InstRs==MEM_WB_RegWriteAddr&&MEM_WB_RegWriteAddr!=0&&15MEM_WB_RegWrite)ForwardJr=2'b11;elseForwardJr=2'b00;3.3冒险检测单元10对于load指令,需要阻塞一个周期,即在禁止PC寄存器、IF_ID流水线寄存器写入,并清空ID_EX流水线寄存器;对于跳转指令,在ID段完成正确的跳转,因此IF段的指令是错误的,需要清空IF_ID流水线寄存器;对于分支指令,在EX段完成分支判断,因此如果成功跳转,IF、ID段的指令均是错误的,需要清空IF_ID和ID_EX流水线寄存器。