超结器件

一种900 V超结VDMOSFET器件的设计与仿真

一种900 V超结VDMOSFET器件的设计与仿真杨永念【摘要】功率MOSFET在现代电子工业中已经得到了广泛的运用,然而在高压功率MOSFET器件中,如何平衡功率MOSFET的击穿电压与导通电阻的冲突一直是研究热点。

结合超结理论和传统功率VDMOSFET的生产工艺设计了一款高压超结VDMOSFET器件,运用半导体器件仿真软件对器件结构进行优化,得到P柱区和N柱区掺杂浓度和厚度的最优值和工艺参数。

仿真结果表明,设计的超结VDMOSFET器件击穿电压和导通电阻分别为946 V和0.83Ω,很好地平衡了功率MOSFET击穿电压与导通电阻的冲突。

%Power MOSFET in modern times has been widely used in electronic industry. In high-voltage power MOSFET device, it’s still not solved that how to balance the contradiction of the breakdown voltage and the on resistance of power MOSFET. The article combine with super-junction theory and manufacturing process of the traditional power VDMOSFET to design a high voltage super-junction MOSFET, and using the semiconductor device simulation software to optimize the structure of device. Get column P and N column of doping concentration and thickness of the optimal value and process parameters. The simulation results show that the S-J VDMOSFET with breakdown voltage of 946 V and on resistance of 0.83 Ω. It solved the conlfict of balance between the breakdown voltage and on resistance of the power MOSFET perfectly.【期刊名称】《电子与封装》【年(卷),期】2015(000)003【总页数】6页(P29-34)【关键词】功率MOSFET;超结VDMOSFET;导通电阻;击穿电压【作者】杨永念【作者单位】重庆邮电大学光电工程学院,重庆 400065【正文语种】中文【中图分类】TN305功率MOSFET器件在低压环境中的运用已经占据主导地位,然而在高频高压环境中,由于击穿电压和导通电阻之间的矛盾一直未被很好地解决,功率MOSFET在高频高压环境中的运用受到很大限制[1]。

超结MOSFET及其发展

超结MOSFET及其发展超结MOSFET是一种优化的金属-氧化物-半导体场效应晶体管,被广泛应用于功率电子设备中。

它的结构和工作原理使其具有更低的开关损耗和更高的开关速度,因此在高频率应用和高功率应用中表现出色。

本文将对超结MOSFET的发展历程进行介绍,并讨论其在电力应用领域中的重要性。

超结MOSFET最早于20世纪80年代末被提出,并在1990年代初开始商业化生产。

与传统的DMOS(双扩散金属-氧化物-半导体场效应晶体管)相比,超结MOSFET引入了超结二极管结构。

这个结构通过在储存电荷区域引入掺杂浅的p-n结,减少了二极管的正向电压降低,从而有效降低了开关电路中的反向恢复电流。

这一点对于高频开关应用和高功率开关应用尤为重要。

超结MOSFET的发展主要集中在两个方向:压降和开关损耗的降低和开关速度的提高。

为了降低压降和开关损耗,一项关键技术是减小超结二极管结区域的电阻。

通过合理的超结二极管结设计和优化的材料选择,可以降低电阻,提高效率。

另外,一些新型材料的引入,例如硅碳(SiC)和氮化镓(GaN),使超结MOSFET具备了更高的工作电压和温度范围。

这使得其在高功率应用中更具优势。

另一方面,为了提高开关速度,超结MOSFET的一种常用技术是减小储存电荷区域的尺寸。

这可以通过减小栅极长度和厚度,以及优化栅氧化层等手段实现。

此外,改变流道材料的特性,例如引入高移动性衬底或引入纳米线流道结构,也可以提高开关速度。

这些技术的发展使得超结MOSFET在高频开关应用中具有良好的性能。

超结MOSFET在电力应用领域中发挥着重要作用。

首先,它可以用于直流-直流(DC-DC)转换器,用于电源管理和电能转换。

其低压降和低开关损耗特性使得它在高效率要求的应用中具备优势。

其次,超结MOSFET也可以用于交流-直流(AC-DC)变换器,例如无线充电器和电动汽车充电器。

由于其高开关速度和高工作电压能力,使其适用于高功率应用和高频应用,为电网负载的需求提供了强大的支持。

超级结mos的外延厚度和衬底厚度

超级结mos的外延厚度和衬底厚度随着半导体技术的不断发展,超级结MOS(Metal-Oxide-Semiconductor)器件在现代电子设备中扮演着越来越重要的角色。

超级结MOS器件具有低功耗、高速度和高可靠性等优点,因此在智能手机、平板电脑、电视机和笔记本电脑等设备中得到广泛应用。

而超级结mos的外延厚度和衬底厚度是两个关键参数,直接影响器件的性能和稳定性。

1. 超级结MOS器件概述超级结MOS器件是一种特殊的MOS场效应晶体管,其特点是在金属-氧化物-半导体结构中引入了具有超晶格结构的p型半导体。

这种超晶格结构可以显著减小形成在结界面的势能垒,从而克服传统结构中形成的PN结开启电压较高的问题,从而降低了开启电压和开启电流。

超级结MOS器件具有较低的导通压降和开启电流,适用于高频、高速多器件应用。

2. 外延厚度的影响外延层是指在衬底上沉积的材料层,它直接影响着器件的结构和性能。

对于超级结MOS器件来说,外延厚度是一个重要参数,它决定了超结区域的形成和性能。

外延层的厚度越大,PN结的形成对电压的影响就越小,导通压降就越低,器件的性能就越好。

除了外延厚度外,外延层的掺杂浓度也是一个重要参数,对器件的性能影响也非常显著。

3. 衬底厚度的影响衬底厚度是指衬底的厚度,对超级结MOS器件的性能同样有着重要的影响。

衬底的厚度越大,可以有效减小PN结的电容,从而提高器件的高频性能。

另外,在深亚微米及纳米器件中,衬底的厚度还可以影响器件的电压承受能力和漏电流。

在超级结MOS器件的制备中,合理选择衬底厚度是至关重要的。

4. 外延厚度和衬底厚度的匹配对于超级结MOS器件来说,外延厚度和衬底厚度的匹配是非常重要的。

过大或过小的外延厚度都会导致器件性能的下降,过薄的衬底厚度也会使得器件的高频性能受到限制。

制备超级结MOS器件时,需要综合考虑外延厚度和衬底厚度,并进行优化设计。

5. 结论在现代电子器件中,超级结MOS器件因其优良的性能和稳定性受到了广泛关注。

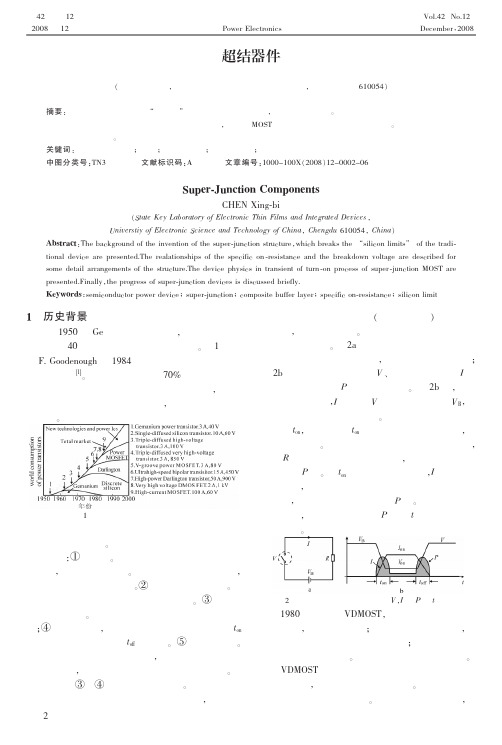

超结器件

摘要 : 简要地介绍 了突破传统 “ 硅极限” 的超结器件发明的背景 , 以及产生的来由。描述 了既用作漂移区又用 作耐压 区的各种超结结构的导通 电阻与击穿电压 的关系, 及超结 M S O T瞬态特性 中导通过程 的器件物理。最后简要地介绍

了超 结器 件 的进 展 。 关 键 词 : 导体 功 率 器件 ; 结 ;复 合缓 冲 层 ;比导 通 电阻 ; 极 限 半 超 , 硅 中图 分 类号 :N T3 文 献标 识码 : A 文 章 编 号 :0 0 10 20 )2 0 0 — 6 10 — 0 X(0 8 1 — 0 2 0

亿美 元

Ge n u p we Wa sso . .0 V ma i m o r n i r A 4 t 3 S n e d fu e … c n t sso 0A. OV i gl. i s d s o r it rl 6 l an l i l - il dli} o t g ' p e d fu e g 卜v ia e r s 1 ta ss o A 0 V r n it r3 l0 T i e df le e yh g — o tge rpi— If s d v r j h v la i ta ssor . 5 r n it A 8 0V 3 V— o vep w e O S gr o o r M FET 3A . 0V 8 Ul a i h s e d bpoa ta sstrl A 0 V t h g -p e i lr r n ii , 5 45 r o

t n l d vc r r s n e .h e l t n h p ft e s e i c o —e itn e a d t e b e k o ot g r e c i e o i a e ie a e p e e tdT e r a ai sቤተ መጻሕፍቲ ባይዱi s o h p cf n r ss c n h ra d wn v l e a e d s rb d fr o o i a a

超结 器件 原理 概述

超结VDMOS概述目录1.高压器件演变史2.超结理论精髓3.超结VDMOS概念4.超结VDMOS指标5.超结VDMOS工艺1.高压器件演变史现代电力电子技术的发展使功率器件多数情形下是用作一种开关。

对功率器件性能的要求大致有如下几条:①耐压高导通时电流密度大②导通时器件上压降低③开关速度高④驱动功率小。

1980年出现了VDMOS,相对于传统功率器件有很多优势,是功率器件的一大进步,但导通压降问题却一直没有解决。

随后发展起来的超结概念与理论,解决了这一问题。

1998年德国西门子的英飞凌(Infineon)公司推出的COOLMOS 器件。

至此,高压功率器件迈入了群雄逐鹿的超结时代。

2.超结理论精髓超结理论的精髓在于电荷平衡原理,或者说电荷互补原理。

相对于传统的耐压结构,由于其交替排列的pn 区域相互耗尽而导致的电荷平衡,使得电场强度在穿越超结时基本保持不变。

3.超结VDMOS 概念将超结结构应用到传统的VDMOS 中,即构成了超结VDMOS 。

这种概念的独到之处在于不折损器件电压阻塞能力的情况下n-漂移区的掺杂浓度可以提高一个数量级,彼此耗尽的pn 区域内将产生横向的内建电场,同时还存在着源自漏源压降的纵向电场,电子和空穴在这1980V D M OS 1998SJ Device 1990G a te -trench DMOS 1975V V M OS p +n +SJ Strucrure SJ Strucrure--Composite buffer layer p n p n p n p np +n -n +Conventional Structure两个方向电场的联合驱使下沿着各自的路径流向电极。

+。

超结mos 和 氮化镓

超结MOSFET(Super Junction MOSFET)和氮化镓(GaN)都是高性能的功率半导体器件,主要用于电源转换、电机驱动等高效率电力电子应用中。

它们各自具有独特的结构与优势:

1. 超结MOSFET (Super Junction MOSFET):

- 结构特点:超结MOSFET采用了一种创新的垂直双扩散型结构,通过在P型和N型硅层之间形成交替排列的非常薄且均匀的掺杂层,从而极大地降低了导通电阻Rds(on),同时保持了较高的击穿电压。

- 优点:相比于传统的平面型MOSFET,超结MOSFET具有更低的导通损耗,适合于高压大电流的应用场合,如开关电源、电动汽车充电器、工业变频器等。

2. 氮化镓(GaN) MOSFET:

- 结构特点:氮化镓是一种宽禁带半导体材料,基于氮化镓材料制作的MOSFET拥有更高的禁带宽度,使得其在高温下能保持良好的性能,并且允许使用更小的晶片尺寸来实现同样的阻断电压,因而可以制造出更高频率、更低导通电阻的晶体管。

- 优点:氮化镓MOSFET的开关速度更快,导通

电阻更低,栅极电荷低,开关损耗显著减少,因此特别适用于高频开关电源、数据中心电源供应、射频功率放大器以及需要高效能密度和高速开关的其他先进应用。

总结来说,超结MOSFET主要是在传统硅基技术上进行优化,提高了硅器件的性能;而氮化镓MOSFET则是利用新型半导体材料实现了更为先进的特性,尤其是在高频、高功率密度和低损耗方面表现突出。

两种器件各有优劣,应用场景不同,根据具体需求选择合适的器件类型。

超结MOSFET

超结MOSFET超结MOSFET(MetalOxideSemiconductorField-EffectTransistor)是一种重要的半导体器件,能够实现两个电路之间的导通、阻断、放大以及稳压等功能。

它的特点是提供了低端噪声、小尺寸、低主输入电流、输出级少功耗和良好的热响应性能,而且可以在超小尺寸的空间中实现良好的性能。

因此,它已经广泛应用于当今的集成电路中,主要应用于电源控制、静态芯片和电源线路保护等。

超结MOSFET所用的半导体器件是MOSFET,它由金属氧化物半导体结构构成,其中金属层为硅,氧化物层为硅氧化物,半导体层通常为硅晶体。

由于金属氧化物半导体的结构,电子便能够从源极区域进入漏极区域,也能够从漏极区域回到源极区域,因此超结MOSFET具有良好的阻抗特性,能够实现低功耗、高精度、高可靠性和高效率的电子电路。

另外,由于它的自激电路性能,可以用它来构建复杂的电子电路和控制电路。

除了上述特性外,超结MOSFET还具有很高的抗电磁干扰性能,可以有效抑制电磁波对电路的影响,从而使得电路性能得到最大的优化。

另外,它具有很高的切换速率,使用它来构建多层次的数字信号处理电路能够更加精确,更少的延时,从而提高系统的数字处理速度和精度。

综上所述,超结MOSFET在电子电路设计中具有重要的意义,因为它具有良好的导通和阻断性能,低主输入电流,良好的热响应性能,可以有效抑制电磁波对电路的影响,提高系统的数字处理速度和精度,高切换速率等优点,并且还可以通过自激电路实现复杂的电子电路和控制电路的设计。

因此,超结MOSFET已经在当前的数字电子电路中广泛应用,且应用范围正在不断扩大,成为电子电路设计中不可或缺的重要器件。

未来,随着半导体技术的发展,超结MOSFET将可以得到更精细的调节,从而使它在电子电路设计中起到更大的作用。

例如,超结MOSFET可以被调节为更小尺寸,因此可以有效减少电路组件的体积,减少芯片的功耗。

超结器件

如下几条:①耐压高。即功率器件加反向电压而处于 关断时,其击穿电压要高。 这个要求比较容易理解, 而要实现此要求并非易事。②导通时电流密度大。这 使得处理一定电流时所需芯片面积不大。 ③导通时 器件上压降低。 意即导通时器件单位面积的电阻很 小;④开关速度高,意即器件从关断到导通的时间 ton 及从导通到关断的时间 toff 都很小。 ⑤驱动功率小。 意即要使得驱动功率器件运作, 开关输入端所需要 的能耗较小,否则需要多个前级放大器才能控制。

3

第 42 卷第 12 期 2008 年 12 月

电力电子技术 Power Electronics

Vol.42 No.12 December,2008

基区变薄, 故这时 IGBT 的电流就是这时双极型晶

体管的电流。这个电流并不太小,但毕竟述快速的下降过程的第 1 阶段 (电容

在 VDMOST 出现后的不到两年时间内,出现了 IGBT,它的结构如图 4a 所示。 可见,IGBT 的开关特 性也是由只需很小的驱动功率的 MOST 的栅电压来 控制的。 图 4a 和 VDMOST 的图 3a 的差别只是在 n 外延层下不是 n+型而是 p+衬底。 但就是这点差别却 带来了一个重要的效果。 当 n-MOST 中的源有电子 向下流、会经过外延层 n 和衬底 p+形成的 p-n 结。 这 个 p-n 结在电子进入衬底 p+的同时, 也把空穴注入 到 n-外延层中去。 使得 n-外延区充满了非平衡电子 与空穴,其浓度可以远超于平衡时电子的浓度,使得 耐压区在导通时电导受到强烈调制, 导通时电压大 大下降。

超结mosfet的特点

超结mosfet的特点超结型金属氧化物半导体场效应晶体管(Super Junction MOSFET)是一种新型的功率半导体器件,具有许多优越的特点。

超结MOSFET具有低导通电阻。

这是由于器件的结构设计,采用了超结的形式,使得电流在导通状态下可以沿着多个通道流动,从而有效降低了导通电阻。

相比传统的MOSFET,超结MOSFET的导通电阻更低,可以承受更大的电流。

超结MOSFET具有快速开关速度。

由于超结MOSFET的结构设计合理,使得器件的电容分布均匀,电流在开关过程中能够得到快速地控制。

因此,超结MOSFET具有较快的开关速度,可以实现高频率的开关操作。

超结MOSFET还具有较低的开关损耗。

由于器件的结构设计合理,使得超结MOSFET在开关过程中可以实现较低的开关损耗。

这是由于在关断状态下,电流能够通过超结区域流动,而不被阻碍。

相比传统的MOSFET,超结MOSFET的开关损耗更低,能够提高器件的效率。

超结MOSFET还具有较高的击穿电压。

由于器件的结构设计合理,使得超结MOSFET能够承受较高的击穿电压。

这是由于超结区域的设计使得电场分布均匀,能够有效地抵抗高电压的作用。

相比传统的MOSFET,超结MOSFET的击穿电压更高,能够适应更复杂的工作环境。

超结MOSFET还具有良好的温度特性。

由于器件的结构设计合理,使得超结MOSFET在高温环境下能够保持较低的导通电阻和开关损耗。

这是由于超结区域的设计使得电流能够得到良好的控制,不受温度的影响。

相比传统的MOSFET,超结MOSFET在高温环境下具有更好的性能表现。

超结MOSFET具有低导通电阻、快速开关速度、较低的开关损耗、较高的击穿电压和良好的温度特性。

这些特点使得超结MOSFET在功率电子领域具有广泛的应用前景。

它可以用于电力变换、电动汽车、太阳能发电系统等领域,提高系统的效率和可靠性。

随着技术的不断进步,超结MOSFET将会越来越成熟,并在各个领域得到更广泛的应用。

超结VDMOS器件及其制备方法[发明专利]

![超结VDMOS器件及其制备方法[发明专利]](https://img.taocdn.com/s3/m/106465fe14791711cd79175b.png)

专利名称:超结VDMOS器件及其制备方法专利类型:发明专利

发明人:钟圣荣,张新

申请号:CN201710136588.7

申请日:20170308

公开号:CN108574012A

公开日:

20180925

专利内容由知识产权出版社提供

摘要:本发明提供一种超结VDMOS器件及其制备方法。

本发明中超结VDMOS器件,分为原胞区、位于原胞区外周的终端区以及位于终端区外周的截止区,其包括具有第一导电类型的衬底;具有第一导电类型的第一外延层,作为漂移区;第二导电类型柱,位于原胞区的第一外延层中以及终端区的第一外延层中;具有第一导电类型的第一注入区,位于原胞区的第一外延层上;第一注入区的掺杂浓度比漂移区的掺杂浓度高;具有第一导电类型的第二外延层,位于终端区的第一外延层上;第二外延层的掺杂浓度比漂移区的掺杂浓度低;具有第一导电类型的第二注入区,位于截止区的第一外延层上;第二注入区的掺杂浓度比漂移区的掺杂浓度高。

本发明的技术方案可以缩短开发时间,降低成本。

申请人:无锡华润华晶微电子有限公司

地址:214028 江苏省无锡市太湖国际科技园菱湖大道180号-22

国籍:CN

代理机构:北京博思佳知识产权代理有限公司

代理人:林祥

更多信息请下载全文后查看。

一种集成电流采样功能的超结器件[发明专利]

![一种集成电流采样功能的超结器件[发明专利]](https://img.taocdn.com/s3/m/003d6d1759fb770bf78a6529647d27284b7337f6.png)

(19)国家知识产权局(12)发明专利申请(10)申请公布号 (43)申请公布日 (21)申请号 202210357125.4(22)申请日 2022.04.07(71)申请人 江苏长晶科技股份有限公司地址 210000 江苏省南京市中国(江苏)自由贸易试验区南京片区研创园腾飞大厦C座13楼申请人 江苏长晶浦联功率半导体有限公司(72)发明人 杨国江 于世珩 (74)专利代理机构 南京天翼专利代理有限责任公司 32112专利代理师 奚铭(51)Int.Cl.H01L 23/544(2006.01)H01L 29/06(2006.01)H01L 29/78(2006.01)(54)发明名称一种集成电流采样功能的超结器件(57)摘要一种集成电流采样功能的超结器件,器件从内到外依次为超结元胞区、过渡区和终端区,所述过渡区同时充当电流采样区,过渡区的第一导电类型半导体外延层中设有两个第二导电类型半导体柱且顶部分别具有第二导电类型半导体区,两个第二导电类型半导体区顶部分别与源极电位和栅极电位相连,两个第二导电类型半导体区之间为第一导电类型半导体导电通道,用于与超结器件外接的过流保护电路的电流采样端相连。

本发明利用超结DMOS的过渡区实现电流采样功能,无需新增采样元胞,有效的减小了芯片面积,且采样区的制备工艺和常规超结DMOS工艺完全兼容,不增加工艺难度和工艺成本。

权利要求书1页 说明书4页 附图3页CN 114496994 A 2022.05.13C N 114496994A1.一种集成电流采样功能的超结器件,器件从内到外依次为元胞区(201)、过渡区(202)和终端区(203),元胞区(201)、过渡区(202)和终端区(203)共用重掺杂第一导电类型半导体衬底(101)及第一导电类型半导体外延层(102),重掺杂第一导电类型半导体衬底(101)的底部与超结器件的漏电极相连,其特征在于:所述过渡区(202)同时充当电流采样区,过渡区(202)的第一导电类型半导体外延层(102)中设有第二导电类型半导体柱A(103‑1)和第二导电类型半导体柱B(103‑2),两者的位置相比之下,第二导电类型半导体柱A (103‑1)靠近元胞区(201),第二导电类型半导体柱B(103‑2)靠近终端区(203);所述第二导电类型半导体柱A(103‑1)和第二导电类型半导体柱B(103‑2)的顶部分别具有第二导电类型半导体区A(105‑1)和第二导电类型半导体区B(105‑2),第二导电类型半导体区A(105‑1)顶部与源极电位相连,第二导电类型半导体区B(105‑2)顶部与栅极电位相连,第二导电类型半导体区A(105‑1)和第二导电类型半导体区B(105‑2)之间为第一导电类型半导体导电通道(108),所述第一导电类型半导体导电通道(108)用于与超结器件外接的过流保护电路的电流采样端相连。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1 历史背景

自 1950 年 Ge 功率管问世以来,它很快就取代 了上世纪 40 年代采用的电子管及离子管。图 1 示出 了 F. Goodenough 在 1984 年发表的功率器件的年销 售额及预测[1]。 由于现在世界上 70%以上的电能都 是经过半导体功率器件变换其形式而应用的, 功率 器件的年销售额仅次于集成电路, 现在每年约二百 亿美元。

为现在称为超结(super-junction)的耐压层。 他提出

了超结的多种结构,并作了理论计算,发现在一定的

图形的基本单元的尺度 b 的值下,Ron 与 VB 的 1.3 次 方成正比:

Ron=c10-7bVB1.3

一个不断扩展的情形,进一步求优化分布。得到的结

果是在同样 VB 下,Ron 大约可再降低 10%[4]。 这 两 篇 论 文 虽 然 都 比 较 短 , 但 在 IEEE

Transaction 这 样 重 要 的 刊 物 上 却 很 快 接 受 作 为

Regular Paper 发 表 , 这 本 身 足 以 说 明 当 时 人 们 对 Ron-VB 关系的重视程度。

图 3 VDMOST 一个单元结构和耐压区电场分布

电场线对 y 的斜率与 n-区掺杂浓度 ND 成正比。 电场线与 y 轴所包围的面积为 VDS。 当 VDS 增加时, 面积的增加是靠了斜率不变的直线向右移动。 这时

靠近 p+区的电场增加。 当此电场增加到击穿的临界

电场 Ecrit 时,会发生雪崩击穿。 这时的外加电压就是 击穿电压 VB。 通常 EC 之值为 2.5×105 V/cm 上下。 显 然,外延层厚度 W 愈大,电场线的斜率愈小,即外延

C 的充电为主导的 阶 段 ),IGBT 的 关 断 面 临 缓 慢 下

降过程的第 2 阶段。 在该阶段,由于 J2 发射结两旁 的非平衡载流子并不为零,该结仍是正偏压。非平衡

载流子 的 消 失 是 由 J2 结 的 一 边 的 基 区 及 另 一 边 的 发射区内复合而逐渐消失的。 这个速度主要决定于

上述的③和④两点值得特别注意。 电力电子技 术要求在变换电能时尽量提高变换的频率, 这样可

2

使外围电路中的储能元件(电感及电容)的体积大 为缩小,重量减轻许多。 但是开关频率高就遇到开 关损耗大的问题。 图 2a 示出一个功率器件通过一个 纯电阻性负载在直流供电下,在开关运用的示意图; 图 2b 示出器件上的电压降 V、通过器件的电流 I 及 两者的乘积即功率 P 与时间的关系。 图 2b 中,在功 率器件被关断时,I 很小而 V 接近于外加电压 VB,因 此器件上损耗的功率也很小。 从关断到导通有一个 时间段 ton, 这里假设 ton 内电流随时间逐渐增加,而 电压逐渐减小。当电流增加到完全导通时的一半时, 负载 R 上有接近一半的外加电压,这对应着一个很 大的功率 P 值。 在 ton 之后的导通时间内,I 达到了一 个稳定值, 由于功率器件在一定电流下总有一定的 电压降,因此有一个一定的功耗 P 值。在周期性的开 关操作下, 平均功耗是图中 P 线和 t 轴所围绕面积 的平均值。

非平衡载流子的寿命, 因此表现为关段过程中的电

流有较长的拖尾。

2 超结的发明

作者从 1981 年开始研究功率 MOST 导通电阻[4],

此后从事多方面结边缘终端技术的工作, 发现各种

结边缘技术的要害都在于在边缘引入了电荷。 这些

电荷产生的电场能降低原来的最大电场。 1989 年作

者想出了在体内引入电场的几种方法。 其中包括作

比较厚,而导通时的 Ron 也就相应的增加。 只不过在 双极型及别的器件中, 开关速度这个主要矛盾未解

决之前,Ron 与 VB 的矛盾关系是次要矛盾,并不突出。 比导通电阻能否进一步下降是当时业内关注的

问题。 1979 年胡正明用外延层杂质浓度在纵向非均

匀而得到一个优化的分布[3]。 但结果表明,在同样 VB 下,Ron 只能再下降约 10%。 1982 年陈星弼与胡正明 考虑到电流从外延层顶部向下流时其流动路径存在

第 42 卷第 12 期 2008 年 12 月

电力电子技术 Power Electronics

Vol.42 No.12 December,2008

超结器件

陈星弼 ห้องสมุดไป่ตู้电子科技大学,电子薄膜与集成器件国家重点实验室, 四川 成都 610054)

摘要:简要地介绍了突破传统“硅极限”的超结器件发明的背景,以及产生的来由。 描述了既用作漂移区又用作耐压

应当注意, 这个充电电流并不能使 n-型区中的 非平衡空穴的总数有显著的变化[5]。 事实上,由于电 流的连续性及衬底 p+对 n-型区的注射效率应接近于 1 这两个条件,n-型每经过 J1 结流出一个空穴,就相 应地有空穴从衬底 p+区流入到 n-型区。

但是,由于这个充电电流毕竟使 J1 结两边电荷 变化,耗尽区从几乎没有变为伸展到一定程度。 n-的 中性区有一定的减薄,从而少子渡越时间降低。该过 程的时间很短,到其结束时,可近似地把结上两边电 荷的变化率忽略,即近似地当作不再充电。而且双极 型晶体管的非平衡载流子的总量也不变。 由于中性

超结器件

问题常被误会为不存在。事实上,传统器件也有这个 问题,只是被速度低这个更重要的缺点所掩盖了。

图 3a 示出 VDMOST 的一个单元结构。 当漏源 两端加有电压 VDS,而栅源电压 VGS 低于 MOST 的阈 电压时,器件 无 电 流 ,耐 住 VDS 的 是 n-外 延 层 ,即 耐 压层。 耐压区的电场分布示意图如图 3b 所示。

Super-Junction Components

CHEN Xing-bi

(State Key Laboratory of Electronic Thin Films and Integrated Devices, Universtiy of Electronic Science and Technology of China, Chengdu 610054, China) Abstract:The background of the invention of the super-junction structure,which breaks the “silicon limits” of the traditional device are presented.The realationships of the specific on -resistance and the breakdown voltage are described for some detail arrangements of the structure.The device physics in transient of turn -on process of super-junction MOST are presented.Finally,the progress of super-junction devices is discussed briefly. Keywords:semiconductor power device; super-junction; composite buffer layer; specific on-resistance; silicon limit

3

第 42 卷第 12 期 2008 年 12 月

电力电子技术 Power Electronics

Vol.42 No.12 December,2008

基区变薄, 故这时 IGBT 的电流就是这时双极型晶

体管的电流。这个电流并不太小,但毕竟是比开始时

还有电容 C 的充电电流小一些。

在经历上述快速的下降过程的第 1 阶段 (电容

Ron=0.83×10-8×VB2.5(Ω·cm2)

(1)

这是一个可怕的关系,称为“硅极限”。设想一个

耐压为 200 V 的器件,根据上述理论公式,每平方毫

米有 0.47 Ω,那么对耐压为 500 V 的器件,每平方毫

米的电阻会增加近 10 倍。

式(1)的关系在别的器件中也存在。 例如对双极

型晶体管,要求集电极耐压高,则集电区要轻掺杂且

在 VDMOST 出现后的不到两年时间内,出现了 IGBT,它的结构如图 4a 所示。 可见,IGBT 的开关特 性也是由只需很小的驱动功率的 MOST 的栅电压来 控制的。 图 4a 和 VDMOST 的图 3a 的差别只是在 n 外延层下不是 n+型而是 p+衬底。 但就是这点差别却 带来了一个重要的效果。 当 n-MOST 中的源有电子 向下流、会经过外延层 n 和衬底 p+形成的 p-n 结。 这 个 p-n 结在电子进入衬底 p+的同时, 也把空穴注入 到 n-外延层中去。 使得 n-外延区充满了非平衡电子 与空穴,其浓度可以远超于平衡时电子的浓度,使得 耐压区在导通时电导受到强烈调制, 导通时电压大 大下降。

图 1 功率器件的年销售额及预测 现代电力电子技术的发展使功率器件多数情形 下是用作一种开关。 对功率器件性能的要求大致有

如下几条:①耐压高。即功率器件加反向电压而处于 关断时,其击穿电压要高。 这个要求比较容易理解, 而要实现此要求并非易事。②导通时电流密度大。这 使得处理一定电流时所需芯片面积不大。 ③导通时 器件上压降低。 意即导通时器件单位面积的电阻很 小;④开关速度高,意即器件从关断到导通的时间 ton 及从导通到关断的时间 toff 都很小。 ⑤驱动功率小。 意即要使得驱动功率器件运作, 开关输入端所需要 的能耗较小,否则需要多个前级放大器才能控制。

区的各种超结结构的导通电阻与击穿电压的关系,及超结 MOST 瞬态特性中导通过程的器件物理。 最后简要地介绍

了超结器件的进展。

关键词:半导体功率器件; 超结; 复合缓冲层; 比导通电阻; 硅极限