IC封装基础资料

IC封装制程介绍基本

電 鍍 設 備

20

➢切筋/成型

傳統IC封裝製程

利用機械模具,將引腳間金屬連接桿和引線框切除,使 外腳與內部線路成單一通路。將已切筋后的料件引腳, 以連續沖模的方式將之彎曲成所要求之形狀。

成型機

Trim & Form

引腳形狀

海鷗型 插入型

J型

21

傳統IC封裝製程

➢電性測試

22

傳統IC封裝製程

➢印碼

在產品的表面刻(印)上廠商LOGO,產品名稱,生產日期,生產批次等.

鐳射刻字 (laser)

油墨印碼 (ink)

23

傳統IC封裝製程

➢包裝-出貨

Tray 盤

管 裝

卷 帶

24

Thank You

25

粘 片前

點膠

粘片

粘片完成

15

➢焊線

傳統IC封裝製程

用金線、銅線、或鋁線把 Pad和 Lead通過焊接的方法連接起來。

焊線前

焊線

焊線后

實物圖

16

傳統IC封裝製程

➢焊線過程分解

瓷嘴Capillary

EFO打火桿烧球

Cap在芯片的Pad上 Cap牽引金線上升 加力和超聲波焊球

Cap運動軌跡形 成弧度

Cap下降到Lead 焊接

基片型封裝(高級):BGA

6

常見IC封裝結構

➢Lead frame封裝

Die 晶片

Bonding wire 焊線

Molding compound 封膠

Leadframe 引綫架

Plating 鍍層

Die attach material (silver paste) 贴晶材料(銀膠)

ic的封装方式

ic的封装方式【原创版】目录1.IC 封装方式的概述2.常见的 IC 封装类型3.各种 IC 封装类型的特点及应用4.IC 封装方式的选择正文【1.IC 封装方式的概述】IC 封装方式,指的是将集成电路(Integrated Circuit,简称 IC)芯片安装在电路板上的方法。

它不仅影响着电路板的性能,而且还关乎到设备的稳定性、可靠性和使用寿命。

因此,合适的 IC 封装方式对于电子产品的性能和品质至关重要。

【2.常见的 IC 封装类型】常见的 IC 封装类型主要有以下几种:(1)DIP(Dual In-Line Package,双列直插式封装):这是最古老的一种封装方式,主要应用于低密度的 IC 芯片。

其特点是引脚排列在两条平行的直线上,易于焊接和插入电路板。

(2)SOP(Small Outline Package,小型外型封装):这是一种较为常见的 IC 封装方式,具有体积小、可靠性高的特点。

SOP 封装的引脚一般分布在四周,间距较小。

(3)QFP(Quad Flat Package,四侧扁平封装):QFP 封装是一种高密度的 IC 封装方式,引脚数量较多且分布在四个侧面。

它具有体积小、焊接方便等优点,但缺点是引脚容易弯曲。

(4)BGA(Ball Grid Array,球栅阵列封装):BGA 封装是一种先进的 IC 封装技术,引脚以微小的球状焊接在芯片底部,间距非常小。

它具有体积小、可靠性高、I/O 引脚数多等优点,但焊接难度较高。

(5)CSP(Chip Scale Package,芯片级封装):CSP 封装是一种新型的 IC 封装方式,引脚与芯片尺寸相当,可以实现真正的芯片级封装。

它具有体积小、散热性好、信号延迟短等优点,但焊接和组装难度较大。

【3.各种 IC 封装类型的特点及应用】(1)DIP 封装:适用于低密度 IC 芯片,如数字电路、模拟电路等,常用于较为简单的电子设备。

(2)SOP 封装:适用于中低密度 IC 芯片,如存储器、微处理器等,广泛应用于各类电子产品。

ic的封装方式

ic的封装方式摘要:一、IC 封装方式简介1.IC 封装的定义和作用2.常见的IC 封装类型二、IC 封装技术的发展历程1.传统封装技术2.先进封装技术三、各种封装技术的特点和应用1.DIP 封装2.QFP 封装3.BGA 封装4.CSP 封装5.Fan-Out Wafer-Level Packaging (FOWLP)四、我国IC 封装产业的发展现状及挑战1.我国IC 封装产业的发展历程2.我国IC 封装产业的现状3.我国IC 封装产业面临的挑战五、我国IC 封装产业的未来发展趋势1.技术创新和发展2.产业政策的支持3.国际合作与市场竞争正文:一、IC 封装方式简介集成电路(IC)封装是将集成电路裸片(Die)与引线框架以及外部电路连接,从而实现芯片功能的一种技术。

封装不仅可以保护芯片免受物理损伤,还可以提高芯片的性能、可靠性和稳定性。

常见的IC 封装类型包括DIP 封装、QFP 封装、BGA 封装、CSP 封装等。

二、IC 封装技术的发展历程传统封装技术主要包括DIP 封装和QFP 封装,具有制程成熟、成本较低的优点。

随着电子产品的轻薄化和高性能需求,先进封装技术逐渐成为主流,如BGA 封装、CSP 封装等。

三、各种封装技术的特点和应用1.DIP 封装(双列直插式封装):是一种通用的封装技术,适用于低速、低功耗的数字和模拟电路。

2.QFP 封装(四侧引脚扁平封装):具有较高的引脚数量和密度,适用于高速、高密度的数字电路。

3.BGA 封装(球栅阵列封装):具有高集成度、低寄生电容、高散热性能等特点,适用于高性能、高密度的处理器、显卡等芯片。

4.CSP 封装(芯片级封装):尺寸最小,厚度最薄,适用于手机、便携式电子设备等对体积要求较高的产品。

5.Fan-Out Wafer-Level Packaging (FOWLP):一种先进的封装技术,具有高集成度、高散热性能和低成本等优点,适用于高性能、低功耗的电子设备。

IC 封装的知识

一些IC工艺的专业词汇:1 Active Area 主动区(工作区)主动晶体管(ACTIVE TRANSISTOR)被制造的区域即所谓的主动区(ACTIVE AREA)。

在标准之MOS制造过程中ACTIVE AREA是由一层氮化硅光罩即等接氮化硅蚀刻之后的局部场区氧化所形成的,而由于利用到局部场氧化之步骤,所以ACTIVE AREA会受到鸟嘴(BIRD’S BEAK)之影响而比原先之氮化硅光罩所定义的区域来的小,以长0.6UM之场区氧化而言,大概会有0.5UM之BIRD’S BEAK存在,也就是说ACTIVE AREA比原在之氮化硅光罩所定义的区域小0.5UM。

2 ACTONE 丙酮 1. 丙酮是有机溶剂的一种,分子式为CH3COCH3。

2. 性质为无色,具刺激性及薄荷臭味之液体。

3. 在FAB内之用途,主要在于黄光室内正光阻之清洗、擦拭。

4. 对神经中枢具中度麻醉性,对皮肤黏膜具轻微毒性,长期接触会引起皮肤炎,吸入过量之丙酮蒸汽会刺激鼻、眼结膜及咽喉黏膜,甚至引起头痛、恶心、呕吐、目眩、意识不明等。

5. 允许浓度1000PPM。

3 ADI 显影后检查 1.定义:After Developing Inspection 之缩写2.目的:检查黄光室制程;光阻覆盖→对准→曝光→显影。

发现缺点后,如覆盖不良、显影不良…等即予修改,以维护产品良率、品质。

3.方法:利用目检、显微镜为之。

4 AEI 蚀刻后检查 1. 定义:AEI即After Etching Inspection,在蚀刻制程光阻去除前及光阻去除后,分别对产品实施全检或抽样检查。

2.目的:2-1提高产品良率,避免不良品外流。

2-2达到品质的一致性和制程之重复性。

2-3显示制程能力之指针2-4阻止异常扩大,节省成本3.通常AEI检查出来之不良品,非必要时很少作修改,因为重去氧化层或重长氧化层可能造成组件特性改变可靠性变差、缺点密度增加,生产成本增高,以及良率降低之缺点。

先进芯片封装知识介绍

先进芯片封装知识介绍芯片封装是将半导体芯片封装成具有特定功能和形状的封装组件的过程。

芯片封装在实际应用中起着至关重要的作用,它不仅保护芯片免受外部环境的干扰和损害,同时也为芯片提供了良好的导热特性和机械强度。

本文将介绍先进芯片封装的知识,包括封装技术、封装材料和封装工艺等方面。

一、芯片封装技术芯片封装技术主要包括无引线封装(Wafer-Level Package,简称WLP)、翻装封装(Flip-Chip Package,简称FCP)和探针封装(Probe Card Package,简称PCP)等。

1.无引线封装(WLP):无引线封装是在芯片表面直接封装焊盘,实现对芯片进行封装和连接。

它可以使芯片的封装密度更高,并且具有优秀的热传导和电性能。

无引线封装技术广泛应用于移动设备和无线通信领域。

2.翻装封装(FCP):翻装封装是将芯片颠倒翻转后通过导电焊球连接到基板上的封装技术。

它可以提供更好的电路性能和更高的封装密度,适用于高性能芯片的封装。

3.探针封装(PCP):探针封装是通过探针头将芯片连接到测试设备进行测试和封装的技术。

它可以快速进行芯片测试和封装,适用于小批量和多品种的芯片生产。

二、芯片封装材料芯片封装材料是指用于封装过程中的材料,包括基板、封装胶料和焊盘等。

1.基板:基板是芯片封装的重要组成部分,主要用于支撑和连接芯片和其他封装组件。

常用的基板材料包括陶瓷基板、有机基板和金属基板等。

2.封装胶料:封装胶料用于固定和保护芯片,防止芯片受损。

常见的封装胶料包括环氧树脂、硅胶、聚酰亚胺等。

3.焊盘:焊盘是连接芯片和基板的关键部分,用于传递信号和电力。

常见的焊盘材料包括无铅焊料、焊接球和金属焊点等。

三、芯片封装工艺芯片封装工艺是指在封装过程中实施的一系列工艺步骤,主要包括胶黏、焊接和封装等。

1.胶黏:胶黏是将芯片和其他封装组件固定在基板上的工艺步骤。

它通常使用封装胶料将芯片和基板粘接在一起,并通过加热或压力处理来保证粘结的强度。

24.IC封装基本知识介绍

4.3.3 MCM应用领域 作为一个完整的电子系统,常常由许多功能块组成, 如复杂的运算单元像MCU和DSP、小信号放大、射频 电路、低频功放和光电器件等。这些功能电路往往用 不同的工艺实现,如要用同一工艺制在一片芯片上是 十分困难的,有时甚至是不可能的。 ——多芯片封装的集成电路组件

4.3.4 MCM的基板 多芯片封装的基板主要有以下一些类型 L(Laminate)型,即叠层型 C(Ceramic)型即原膜陶瓷型 D(Deposited Thin Film)型即淀积薄膜型 Si (Silicon)型,即硅型

SOP封装外形图

(3) QFP(Quad Flat Package) 四边引脚扁平封装

QFP封装结构 QFP的分类: QFP的分类:塑(Plastic)封 QFP(PQFP) 薄型QFP(TQFP) 窄(Fine)节距 QFP(FQFP)

4.3 集成电路多芯片组件(MCM)封装技术 集成电路多芯片组件( )

一种六芯片MCM

4.3.2 多芯片封装的好处 多芯片封装的好处是可将不同工艺的芯片组合在 一起在单片集成电路上实现较为完整的系统功能。还 在于可以利用现有成熟而较为复杂的芯片附加自己设 计的较简单的ASIC组成应用系统,降低产品开发风险, 提高芯片性能和经济效益。多芯片封装提高系统的保 密性和可靠性也是很显然的。多芯片封装是21世纪新 型封装的一个重要方向。

6. 按芯片功能分类 模拟集成电路(Analog IC):它是指处理模拟信号 (连续变化的信号)的集成电路 线性集成电路:又叫做放大集成电路,如运算 放大器、电压比较器、跟随器等 非线性集成电路:如振荡器、定时器等电路 数模混合集成电路(Digital - Analog IC) :例如数 模(D/A)转换器和模数(A/D)转换器等

《IC封装技术》课件

TQFP

薄型方形平面封装,厚度更薄, 适用于要求更小封装尺寸的应 用。

BGA

球栅阵列封装,引脚以焊球形式存在,适用于高速 和高密度的应用。

CSP

芯片级封装,芯片表面直接焊接,尺寸更小,适用 于小型化的应用。

封装材料

1 塑封料

用于封装芯片的塑料材料,具有良好的绝缘和保护性能。

通过精确的手工焊接过程, 将芯片和基板连接,确保稳 定的电连接。

制备小型焊球,用于连接焊球上形成保护层,确保电连接的稳定性和可 靠性。

将焊球与芯片焊接在一起,实现稳定的电连接并 保护芯片。

封装种类

DIP

双列直插封装,适用于连接较 粗的引脚。

QFP

2 金属材料

用于封装芯片的金属材料,具有良好的散热性能和电导性。

应用领域

通讯

IC封装技术在通信设备中的应 用广泛,包括移动通信和网络 设备。

汽车电子

汽车电子领域对封装技术的要 求越来越高,应用于车载电子 控制系统和安全系统等。

多媒体

音视频设备和娱乐系统广泛采 用IC封装技术,实现高质量的 音视频处理和输出。

工艺流程

1

热压封装工艺流程

通过热压技术将芯片与封装基板结合,实现电连接和封装保护。

2

焊球压装工艺流程

使用焊球将芯片与基板连接,提供稳定的电连接并实现封装保护。

3

直立式封装工艺流程

将芯片直立安装在基板上,实现更高的功率密度和封装效果。

主要工艺

1 脱模

2 人工对焊

3 焊球制备

从封装模具中取出芯片,准 备封装过程。

动力电子

动力电子设备中常用的电源模块封装技术可以提供 高效率和高可靠性的电能转换。

ic的封装方式

ic的封装方式【实用版】目录1.IC 封装方式的定义与重要性2.常见 IC 封装类型及其特点3.IC 封装方式的选择4.未来 IC 封装技术的发展趋势正文一、IC 封装方式的定义与重要性IC 封装,即集成电路封装,是指将集成电路芯片安装在电路板上并保护起来的过程。

封装方式对于 IC 的稳定性、可靠性和使用寿命具有重要影响。

合适的封装方式可以提高 IC 的性能,使其在不同的环境中都能保持稳定的工作状态。

二、常见 IC 封装类型及其特点1.DIP(Double In-Line Package):双列直插式封装,是 IC 封装中最常见的一种类型。

它具有引脚数量多、插入方便等优点,但体积较大,不适用于高密度电路板。

2.SOP(Small Out-Line Package):小型外引线封装,具有体积小、外观美观等优点,适用于高密度电路板。

但引脚数量较少,插拔较为困难。

3.QFP(Quad Flat Package):四侧引脚扁平封装,具有体积小、引脚数量多等优点,适用于高密度电路板。

但其引脚容易弯曲,需要特别注意。

4.BGA(Ball Grid Array Package):球栅阵列封装,具有体积小、引脚数量多、可靠性高等优点,适用于高密度电路板。

但焊接难度较高,需要专用设备。

5.CSP(Chip Scale Package):芯片级封装,引脚与芯片尺寸相近,具有体积小、引脚数量多等优点,适用于高密度电路板。

但焊接难度较高,需要专用设备。

三、IC 封装方式的选择在选择 IC 封装方式时,需要综合考虑以下几个方面:1.应用场景:根据不同的应用场景选择合适的封装类型,如高密度电路板适用 SOP、QFP、BGA、CSP 等封装方式。

2.性能要求:对于性能要求较高的 IC,应选择具有良好散热性能、抗干扰性能的封装方式。

3.成本考虑:在满足性能要求的前提下,选择成本较低的封装方式。

4.兼容性:考虑 IC 封装与电路板的兼容性,选择易于焊接、插拔的封装方式。

14.IC封装基本知识介绍

半導體材料發展

元素半導體: IV族Si, Ge 化合物半導體 :

III-V族:GaAs, InP, GaN, AlP…. II-VI族:ZnO,ZnS, CdS… IV-IV族:SiC IV-VI族:PbS,PbSe

合金半導體:

二元素:SiGe 三元素:AlGaAs, GaMnTe, HgCdTe 四元素:AlGaAsSb, GaInAsP

(5) 提供准确的检验测试数据,为提高集成电路封装的性能 和可靠性提供有力的保证。

集成電路設計考慮

集成电路设计中的封装考虑:

(1)划片槽与焊盘:

在一个晶圆上分布着许多块 集成电路,在封装时要将各 块集成电路切开。这个切口 就叫划片槽。

划片槽示意图

集成電路設計考慮

集成电路设计中的封装考虑 :

(2)芯片散热问题:

集成電路測試方法

集成电路测试信号联接方法 :

集成电路测试所要做的工作,一是要将芯片与测试系统的各 种联接线正确联接;二是要对芯片施加各种信号,通过分析 芯片的输出信号,来得到芯片的功能和性能指标。芯片与测 试系统的联接 分为两种:

(1)芯片在晶圆测试的联接方法 (2)芯片成品测试的联接方法

集成電路測試方法

TAB : Flip Chip :

優點 : 可得細微腳間隙,並可一次加壓完成。 缺點 : 平行度調整困難。 優點 : IC封裝面積可大大降低。 缺點 : 需調整晶體與封裝基板接合,程序複雜。

封裝方法優缺點

( 4 ) 外部引線接合方式 :

IC與PCB基板的連接方式 : a.插入式 b. 表面黏度。 依腳的形狀又可分為 I 形腳, J 形腳,翼形腳…等。

Foxconn Technology Group

SMT Technology Center

IC封装相关的一些基础材料

IC封装相关的一些基础材料

液态封装树酯

液态封装树酯具有可靠性佳、内应力极低、颗粒极细小等特性,用于涂

布于芯片四周以保护组件。

常用于BGA、CSP、覆晶等封装应用。

介面散热材料

介面散热材料分为有jel 材质(无黏性)与rubber 材质(高黏性),用作IC 原件(device) 与散射片(heat spreader)之间的介质,可以提升散热功能。

可广泛使用于封装散热应用。

黑胶

黑胶成分为环氧树脂,是高分子热固性材料,主要用于IC 与被动原件

封装,用来保护内部芯片不受环境破坏并具绝缘效果,具有低应力,高散热

等特性。

聚醯亚胺

用于半导体芯片的表面涂层,具有很高的绝缘性能,可以保护芯片电气

特性,提升防潮性能,避免机械性冲击,隔离污染物质。

LED 涂布保护材料

用于LED 芯片的表面涂布,具有高透光性,有利于LED 电气特性的维

持和对芯片的防潮保护。

tips:感谢大家的阅读,本文由我司收集整编。

仅供参阅!。

ic的封装方式

ic的封装方式(原创实用版)目录1.IC 封装方式的概述2.常见的 IC 封装类型及其特点3.IC 封装方式的选择因素4.IC 封装对电子产品性能的影响5.未来 IC 封装技术的发展趋势正文一、IC 封装方式的概述IC 封装,即集成电路封装,是指将集成电路芯片安装在电路板上并进行保护的过程。

IC 封装方式是电子产品制造中至关重要的一环,它直接影响到产品的性能、可靠性和使用寿命。

本文将对 IC 封装的常见方式及其特点进行介绍,并探讨 IC 封装方式的选择因素以及对电子产品性能的影响。

二、常见的 IC 封装类型及其特点1.SMD(表面贴装器件):SMD 封装是将 IC 芯片贴装在电路板上,并通过焊接方式进行连接。

具有体积小、重量轻、自动化生产程度高等优点,广泛应用于智能手机、平板电脑等消费电子产品中。

2.DIP(双列直插式封装):DIP 封装是一种传统的 IC 封装方式,采用焊接或插拔方式将 IC 芯片安装在电路板上。

具有成本低、可靠性高、易于维修等优点,但体积较大,不太适用于小型化电子产品。

3.QFP(四侧引脚扁平封装):QFP 封装是一种高密度 IC 封装方式,具有体积小、引脚数量多等优点,适用于对空间要求较高的电子产品。

4.BGA(球栅阵列封装):BGA 封装是一种先进的 IC 封装技术,采用微小球形焊料将 IC 芯片与电路板焊接在一起。

具有体积小、散热性好等优点,但焊接难度较高,对生产工艺要求严格。

5.FC(倒装芯片封装):FC 封装是将 IC 芯片的电极倒装在电路板上,通过焊接方式进行连接。

具有体积小、可靠性高、散热性好等优点,但成本较高,不太适用于低端电子产品。

三、IC 封装方式的选择因素1.电子产品的性能要求:不同的 IC 封装方式对电子产品的性能影响不同,需要根据产品的性能要求进行选择。

2.成本因素:IC 封装方式的成本直接影响到电子产品的制造成本,需要在性能和成本之间进行权衡。

3.生产工艺:IC 封装方式的生产工艺对电子产品的生产效率和质量具有重要影响,需要选择适合生产工艺的 IC 封装方式。

IC先进封装简介介绍

04

IC先进封装在产业界的应用案 例

案例一:高性能计算芯片的封装解决方案

解决方案概述

针对高性能计算芯片的高功耗、高热流密度等挑战,采用 先进的2.5D/3D封装技术,实现更高集成度和更优性能。

技术特点

利用硅通孔(TSV)技术,实现芯片内部垂直互联;采用 多层布线技术,大幅提升互连密度;引入高效热管理技术 ,降低芯片工作温度。

应用优势

提升计算性能,满足高性能计算需求;减小芯片尺寸,降 低功耗,提高能源利用效率;优化散热设计,提高系统稳 定性。

案例二:智能手机中的超微型封装技术

01

解决方案概述

为满足智能手机对轻薄、高性能的需求,采用超微型封装技术,将多种

功能芯片集成于极小空间内。

02 03

技术特点

运用晶圆级封装(WLP)技术,减小芯片封装尺寸;采用扇出型封装( Fan-out)结构,提高I/O接口数量及布线灵活性;利用高精度组装技 术,确保微型组件的可靠连接。

装行业的发展。

IC先进封装的技术特点

01

02

03

04

高集成度

IC先进封装技术能够实现更高 密度的集成,减小封装体积,

提高产品便携性。

优异的电气性能

采用先进的互连技术,降低寄 生参数影响,提高信号传输速

度和可靠性。

高效的散热设计

通过优化散热结构,提高散热 效率,确保芯片在高功率密度

下的可靠工作。

灵活的生产工艺

IC先进封装简介介绍

汇报人: 日期:

contents

目录

• IC先进封装概述 • IC先进封装的主要类型 • IC先进封装的技术挑战与发展趋势 • IC先封装定义和作用

定义

IC封装,也称为集成电路封装,是指将集成电路芯片封装在封装体中,以保护芯片、提供电气连接、散热等功能 ,并使得芯片能够方便地安装在电路板上。

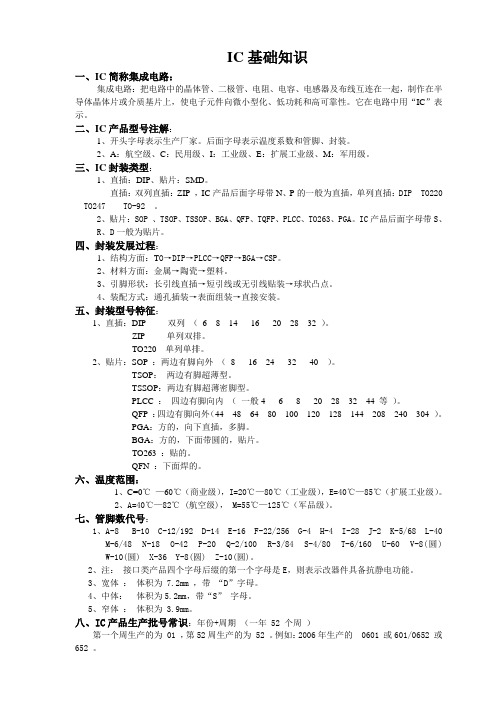

IC基础知识

IC基础知识一、IC简称集成电路:集成电路:把电路中的晶体管、二极管、电阻、电容、电感器及布线互连在一起,制作在半导体晶体片或介质基片上,使电子元件向微小型化、低功耗和高可靠性。

它在电路中用“IC”表示。

二、IC产品型号注解:1、开头字母表示生产厂家。

后面字母表示温度系数和管脚、封装。

2、A:航空级、C:民用级、I:工业级、E:扩展工业级、M:军用级。

三、IC封装类型:1、直插:DIP、贴片:SMD。

直插:双列直插:ZIP ,IC产品后面字母带N、P的一般为直插,单列直插:DIP TO220 TO247 TO-92 。

2、贴片:SOP 、TSOP、TSSOP、BGA、QFP、TQFP、PLCC、TO263、PGA。

IC产品后面字母带S、R、D一般为贴片。

四、封装发展过程:1、结构方面:T O→DIP→PLCC→QFP→BGA→CSP。

2、材料方面:金属→陶瓷→塑料。

3、引脚形状:长引线直插→短引线或无引线贴装→球状凸点。

4、装配方式:通孔插装→表面组装→直接安装。

五、封装型号特征:1、直插:DIP 双列(6 8 14 16 20 28 32 )。

ZIP 单列双排。

TO220 单列单排。

2、贴片:SOP :两边有脚向外(8 16 24 32 40 )。

TSOP:两边有脚超薄型。

TSSOP:两边有脚超薄密脚型。

PLCC :四边有脚向内(一般4 6 8 20 28 32 44 等)。

QFP :四边有脚向外(44 48 64 80 100 120 128 144 208 240 304 )。

PGA:方的,向下直插,多脚。

BGA:方的,下面带圆的,贴片。

TO263 :贴的。

QFN :下面焊的。

六、温度范围:1、C=0℃—60℃(商业级),I=20℃—80℃(工业级),E=40℃—85℃(扩展工业级)。

2、A=40℃—82℃ (航空级), M=55℃—125℃(军品级)。

七、管脚数代号:1、A-8 B-10 C-12/192 D-14 E-16 F-22/256 G-4 H-4 I-28 J-2 K-5/68 L-40M-6/48 N-18 O-42 P-20 Q-2/100 R-3/84 S-4/80 T-6/160 U-60 V-8(圆) W-10(圆) X-36 Y-8(圆) Z-10(圆)。

IC芯片封装常识

5、Cerdip

用玻璃密封的陶瓷双列直插式封装,用于ECL RAM,DSP(数字信号处理器)等电路。带有

玻璃窗口的Cerdip 用于紫外线擦除型EPROM 以及内部带有EPROM 的微机电路等。引脚中心

距2.54mm,引脚数从8 到42。在日本,此封装表示为DIP-G(G 即玻璃密封的意思)。

美国Motorola 公司对BGA 的别称(见BGA)。

20、CQFP(quad fiat package with guard ring)

带保护环的四侧引脚扁平封装。塑料QFP 之一,引脚用树脂保护环掩蔽,以防止弯曲变形。

在把LSI 组装在印刷基板上之前,从保护环处切断引脚并使其成为海鸥翼状(L 形状)。这种封装

和10.16mm 的封装分别称为skinny DIP 和slim DIP(窄体型DIP)。但多数情况下并不加区分,

只简单地统称为DIP。另外,用低熔点玻璃密封的陶瓷DIP 也称为cerdip(见cerdip)。

13、DSO(dual small out-lint)

双侧引脚小外形封装。SOP 的别称(见SOP)。部分半导体厂家采用此名称。

LSI 电路。

LGA 与QFP 相比,能够以比较小的封装容纳更多的输入输出引脚。另外,由于引线的阻抗

小,对于高速LSI 是很适用的。但由于插座制作复杂,成本高,现在基本上不怎么使用。预计

今后对其需求会有所增加。

26、LOC(lead on chip)

芯片上引线封装。LSI 封装技术之一,引线框架的前端处于芯片上方的一种结构,芯片的

6、Cerquad

表面贴装型封装之一,即用下密封的陶瓷QFP,用于封装DSP 等的逻辑LSI 电路。带有窗

IC封装资料大全

1、BGA(ball grid array)球形触点陈列,表面贴装型封装之一。

在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配LSI 芯片,然后用模压树脂或灌封方法进行密封。

也称为凸点陈列载体(PAC)。

引脚可超过200,是多引脚LSI用的一种封装。

封装本体也可做得比QFP(四侧引脚扁平封装)小。

例如,引脚中心距为1.5mm 的360 引脚BGA 仅为31mm 见方;而引脚中心距为0.5mm 的304 引脚QFP 为40mm 见方。

而且BGA 不用担心QFP 那样的引脚变形问题。

该封装是美国Motorola 公司开发的,首先在便携式电话等设备中被采用,今后在美国有可能在个人计算机中普及。

最初,BGA 的引脚(凸点)中心距为1.5mm,引脚数为225。

现在也有一些LSI 厂家正在开发500 引脚的BGA。

BGA 的问题是回流焊后的外观检查。

现在尚不清楚是否有效的外观检查方法。

有的认为,由于焊接的中心距较大,连接可以看作是稳定的,只能通过功能检查来处理。

美国Motorola 公司把用模压树脂密封的封装称为OMPAC,而把灌封方法密封的封装称为GPAC(见OMPAC 和GPAC)。

2、BQFP(quad flat package with bumper)带缓冲垫的四侧引脚扁平封装。

QFP 封装之一,在封装本体的四个角设置突起(缓冲垫) 以防止在运送过程中引脚发生弯曲变形。

美国半导体厂家主要在微处理器和ASIC 等电路中采用此封装。

引脚中心距0.635mm,引脚数从84 到196 左右(见QFP)。

3、碰焊PGA(butt joint pin grid array) 表面贴装型PGA 的别称(见表面贴装型PGA)。

4、C-(ceramic)表示陶瓷封装的记号。

例如,CDIP 表示的是陶瓷DIP。

是在实际中经常使用的记号。

5、Cerdip用玻璃密封的陶瓷双列直插式封装,用于ECL RAM,DSP(数字信号处理器)等电路。

IC封装基本知识介绍

外部引線的應力為

a. IC重量造成應力 b. 焊接殘留應力 c. 熱循環應力

外部引線的應力,依EIAJ建議QFP最好邊長不大於40mm 。

集成電路封裝內容

集成电路封装的内容:

(1) 通过一定的结构设计、工艺设计、电设计、热设计和 可靠性设计制造出合格的外壳或引线框架等主要零部 件;

Foxconn Technology Group

SMT Technology Center

SMT 技術中心

SMT Technology Development Committee

一.半導體材料發展 二.半導體應用分類 三.封裝方法優缺點 四.集成電路封裝內容 五.集成電路設計考慮 六.集成電路測試方法

集成電路測試方法

集成电路测试信号联接方法 :

集成电路测试所要做的工作,一是要将芯片与测试系统的各 种联接线正确联接;二是要对芯片施加各种信号,通过分析 芯片的输出信号,来得到芯片的功能和性能指标。芯片与测 试系统的联接 分为两种:

(1)芯片在晶圆测试的联接方法 (2)芯片成品测试的联接方法

集成電路測試方法

半導體材料發展

元素半導體: IV族Si, Ge 化合物半導體 :

III-V族:GaAs, InP, GaN, AlP…. II-VI族:ZnO,ZnS, CdS… IV-IV族:SiC IV-VI族:PbS,PbSe

合金半導體:

二元素:SiGe 三元素:AlGaAs, GaMnTe, HgCdTe 四元素:AlGaAsSb, GaInAsP

另一目的是希望通过测试,确定电路失效的原 因以及失效所发生的具体部位,以便改进设计 和修正错误。

集成電路測試方法

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Tail length

PDF created with pdfFactory trial version

Wire Bቤተ መጻሕፍቲ ባይዱnding Cycle (7)

Ø

Disconnection of the tail bond

W/C close CAP rise Cut off G/W

Bond Time Ultrasonic

• Frequency (60KHz, 120KHz, 138KHz) • Power

Force Temperature Looping

PDF created with pdfFactory trial version

Materials

Breaking load

low

Wire sweep after molding 2nd bondability Bigger better

high

lower worse

HAZ length

short

Loop height Loop height stability in low loop lower better

2nd Optical Inspection 2nd Optical Inspection

Die Bond & Cure Die Bond & Cure Substrate Baking Substrate Baking

Wire Bond Wire Bond Chip Attach Chip Attach

ワイヤの比抵抗

4N系 合金系 (G1) 〃 (R1) 2.30 2.98 3.20

電気抵抗/Ωm

100

50

0 10 20

線径/μm

30

40

測定方法は4端子法を用いています。

PDF created with pdfFactory trial version

Characteristic of gold wire (3)

Wire Bond Process

Prepared by : Jerry Hsu Rev. : O

PDF created with pdfFactory trial version

Assembly Process Flow -- Front-end

Lead frame , Substrate & FC

PDF created with pdfFactory trial version

Wire Bonder

Wire Feeder

Loader

Unloader

PDF created with pdfFactory trial version

Dejunk/ Trim Dejunk/ Trim Ball Attach Ball Attach

Solder Plating Solder Plating (L/F type only) (L/F type only)

Solder Plating Solder Plating Inspection (L/F) Inspection (L/F)

Type (relate electrical properties)

• 4N • Au alloy

HAZ (Heat Affected Zone)

PDF created with pdfFactory trial version

Characteristic of gold wire (2)

Characteristic of SBT

Finger top width Finger pitch Au plating thickness (0.5~1um) Ni plating thickness (5~15um)

Finger top width

PDF created with pdfFactory trial version

long

Higher Worse

PDF created with pdfFactory trial version

Gold Wire Electrical Resistance

合金系ボンディング ワイヤの電気抵抗

200

verj.002

150

4N系 G1(合金) R1(合金)

PDF created with pdfFactory trial version

Wire bond

1st Bond

2nd Bond

PDF created with pdfFactory trial version

Bonding Parameter

Direct Material:

• Gold wire • SBT(L/F)

Indirect Material:

• Capillary

PDF created with pdfFactory trial version

Characteristic of gold wire (1)

PDF created with pdfFactory trial version

Wire Bonding Cycle (8)

Ø

Formation of a new FAB

Wire clamp close

High voltage Low Electricity

Working Area

Bond Head

Transducer

Feeder Heater

PDF created with pdfFactory trial version

Motion Principle

Loading P.R.S. Wire Bonding Unloader

Assembly Process Flow -- Back-end

Lead frame , Substrate & FC

Molding Molding Underfill Underfill Post Mold Cure Post Mold Cure Underfill Cure Underfill Cure Laser Marking Laser Marking or Ink Marking or Ink Marking

Mechanical properties

• Breaking Load • Elongation

Type of spool

• Conductive • Non conductive

PDF created with pdfFactory trial version

High temperature(180°c)

PDF created with pdfFactory trial version

Wire Bonding Cycle (3)

Ø

Capillary rises to loop height position

W/C Open 依照 Loop parameter CAP上升到 Loop height position

Wafer Incoming Wafer Incoming Wafer Taping Wafer Taping

Wafer Back Grinding Wafer Back Grinding

Wafer De-taping Wafer De-taping

Wafer Mount Wafer Mount

Wafer Saw Wafer Saw

Die

Lead

PDF created with pdfFactory trial version

Wire Bonding Cycle (5)

Ø

Formation of the 2nd bond

W/C close 等速度下降 Ultrasonic

L/F:金銀共金 SBT:金金共金

PDF created with pdfFactory trial version

Wire Bonding Cycle (1)

Ø

Step 1. FAB (Free Air Ball) formation

Wire clamp close

High voltage Low Electricity

Forming/Singulation Forming/Singulation Singulation/Saw Singulation/Saw

Open/Short Test Open/Short Test (option) (option)

Lead Scan Lead Scan

Final Visual Final Visual

金球和鋁墊相粘

PDF created with pdfFactory trial version

Wire Bonding Cycle (4)

Formation of the loop

W/C close 依照 Loop parameter, CAP以機械動作折出弧形

High temperature(180°c)

PDF created with pdfFactory trial version

Wire Bonding Cycle (6)

Ø

Creation of the tail length

W/C Open 依照 EFO parameter CAP上升到tail height position

The Basic Gold Ball Wire Bonding Cycle ¶ Free air ball is captured in the chamfer · Formation of a first bond ¸ Formation of a loop ¹ Formation of a second bond º Disconnection of the tail » Formation of a new free air ball. Ready for a new cycle