单片机音乐彩灯设计说明

基于89c51单片机控制的LED音乐彩灯控制器的设计说明

基于89c51单片机控制的LED音乐彩灯控制器的设计随着人们对房屋的装饰需要彩灯,在许多城市可以看到彩色霓虹灯。

LED彩灯由于其丰富的灯光色彩,便宜的造价以及简单等特点而得到了广泛的应用,用彩灯来装饰街道和城市建础物已经成为一种时尚。

但目前市场上各种各样的LED彩灯控制器大多数用全硬件电路实现,电路结构复杂、电路复杂、功率损耗大等缺点。

此外从功能效果上看,亮灯模式少而且样式单调,缺乏用户可操作性……本方案提出一种基于8951单片机的彩灯控制方案,实现对LED 彩灯的控制。

本方案以8951单片机作为主控核心,在主控模块上设有3个按键和8个LED显示灯,根据需要可以编写若干种亮灯模式,利用其部定时器T0实现一个基本单位时间为1ms的定时中断,根据各种亮灯时间的不同需要,在不同时刻输出灯亮或灯灭的控制信号,然后驱动各种颜色的灯亮或灭。

与普通LED彩灯相比,具有体积小、价格低、功耗低等优点。

2系统功能LED彩灯用软件控制硬件的方式来控制彩灯闪烁,即彩灯控制器和管LED模块。

彩灯采用8951提供+5V电压工作,经过电源变换,输出直流工作电压,一方面为管LED模块提供+5V工作电源,另一方面为主控模块单片机系统彩灯控制器提供5V工作电源。

整个系统工作由软件程序控制运行,根据需要用户可以在LED彩灯工作时通过主控模块上的按键来设定亮灯时间和灯光闪动频率。

上电后系统经过初始化,查询是否有功能切换键按下:有,则进入设定模式状态;无,则进入默认工作状态。

在设定模式状态下,可以根据个人爱好及不同场合的需要来指定调用哪种模式,并且可以改变每种模式的时间T1、频率F1参数,在工作状态下,LED彩灯控制器按照程序设定好的若干亮灯花样模式程序顺序调用往下走,开始工作,依次8个等亮完为一个亮灯周期,然后再回主循环继续工作,同样如果想进入其它设定模式状态,只需按下功能切换键即可。

整个3种亮灯模式时间可以看作一个大周期T,对于每一个模式编写一个独立工作子程序,其中设定了从左到右点亮LED,从右到左点亮LED,还有自己定义的LED点亮方式。

51单片机彩灯控制器的设计

51单片机彩灯控制器的设计一、设计目的单片机彩灯控制器是一种能够通过控制程序实现RGBLED灯光颜色和亮度变化的设备。

其设计目的是实现LED的多彩灯光效果,丰富室内环境,提高生活品质。

二、硬件设计1.单片机选择在设计彩灯控制器时,我们选择了常用的8051单片机作为控制芯片。

8051单片机拥有丰富的外设资源,易于编程控制,并且具有较高的稳定性和可靠性。

2.RGBLEDRGBLED是一种由红、绿和蓝三个LED灯组成的组合灯,可以通过控制不同颜色的LED来实现丰富多彩的灯光效果。

在设计中,我们选用了高亮度的RGBLED,以确保灯光效果的良好。

3.驱动电路为了驱动RGBLED,我们设计了一套驱动电路,其中包括三个恒流驱动电路和三个PWM调光电路。

恒流驱动电路可以确保LED的电流稳定,而PWM调光电路可以实现LED的亮度调节。

4.控制电路控制电路主要由单片机、按键、显示屏等组成。

通过单片机控制按键输入,并根据用户需求调整LED的颜色和亮度。

同时,显示屏可以实时显示LED的参数信息,方便用户操作。

5.电源彩灯控制器的电源一般采用直流5V供电,可以通过USB接口或者外部电源适配器来供电,以满足不同环境下的使用需求。

三、软件设计1.系统架构我们将彩灯控制器的软件设计分为三个模块:按键输入模块、LED控制模块和显示模块。

按键输入模块负责接收用户的按键输入,LED控制模块根据用户输入控制LED的颜色和亮度,显示模块实时显示LED的参数信息。

2.按键输入模块按键输入模块主要负责检测用户按键的状态,并根据按键的状态进行相应的处理。

例如,当用户按下“颜色+/颜色-”按键时,按键输入模块会向LED控制模块发送指令,控制LED颜色的变化。

3.LED控制模块LED控制模块负责控制RGBLED的颜色和亮度。

当接收到按键输入模块发送的指令时,LED控制模块会根据指令调节LED的PWM值,实现LED 颜色的变化和亮度的调节。

4.显示模块显示模块通过显示屏实时显示LED的参数信息,包括LED的颜色、亮度等参数。

毕业设计(论文)-基于51单片机的音乐彩灯设计-毕业设计

毕业设计(论文)-基于51单片机的音乐彩灯设计-毕业设计扬州工业职业技术学院毕业论文扬州工业职业技术学院2009 2010 学年第二学期毕业设计课题名称:基于51 单片机的音乐彩灯设计设计时间: 2009 年12 月系部:电子信息工程系班级:姓名:指导教师:1 扬州工业职业技术学院毕业论文总目录第一部分任务书第二部分开题报告第三部分毕业设计正文2扬州工业职业技术学院毕业论文第一部分任务书3扬州工业职业技术学院毕业论文扬州工业职业技术学院毕业设计任务书电子信息系部指导老师职称工程系学生姓名班级学号设计题目基于51 单片机的音乐彩灯设计1、主要内容本毕业设计是以单片机AT89C52 为基础,通过LED,数码管,喇叭等进行展示,然后用Keil 软件编写单片机端通信程序,实现多模式彩灯和音乐的结合。

通过本设计旨在让学生要将单片机的硬件知识与软件知识融会贯通,设计出实用的系统。

培养学生独立分析问题,综合运用知识解决实际问题的能力。

通过本题的设计和调试,使学生巩固所学的理论知识,增强设计动手能力,提高学生的创新能力和工程素质。

内容 2、主要技术指标1)系统电源电压:+5V±5%目标2)单片机及外围芯片工作电压:+5V±5%和 3)单片机选型:MCS-51 系列单片机4)软件开发环境:Keil uvision2要求5)计时时间产生方式:定时器中断方式获取二、毕业设计的基本要求1 收集、整理与毕业设计有关领域的信息资料2 完成本毕业设计方案和结构框图的设计;3 完成本毕业设计电路原理图设计。

4 完成本毕业设计程序流程图和汇编语言源程序设计5 完成软件和硬件系统的调试,功能指标达到技术要求;4扬州工业职业技术学院毕业论文6 程序清单和图样资料;7 作品及照片;8)形成符合学校规定的毕业设计书面文档;三、毕业论文(设计)进度安排第一阶段 2009 11 月21 日 - 2010 1月 20 日选题、调研、收集资料、论证、开题第二阶段 2010 2 月20 日 - 20104 月 20 日方案、电路、硬件、软件设计第三阶段2010 4 月21 日- 2010 5 月 10 日软硬件调试、写作初稿第四阶段2010 5 月10 日- 2010 6 月 15 日修改、定稿、打印、答辩四、毕业设计提交的成果1 开题报告2 设计说明书3 图样资料a 系统原理图;b 硬件电路图;c 软件流程图;4 中、英文摘要(中文摘要约200 字,3―5 个关键词)查阅文献不少于8 篇教研室系部审核审核5扬州工业职业技术学院毕业论文第二部分开题报告扬州工业职业技术学院电子信息工程系 10届6扬州工业职业技术学院毕业论文毕业设计(论文)开题报告书(表 1)毕业设计(论文)开题报告书(表 1)学生姓专业应用电子班级学号名题基于51 单片机的音乐彩灯设计目指导教职称教师学位师题目类□工程设计□基础研究□应用研究□其它别【题的内容与要求】以单片机AT89C52 为基础,通过LED,数码管,喇叭等进行展示,然后用Keil软件编写单片机端通信程序,实现多模式彩灯和音乐的结合。

单片机音乐彩灯课程设计

单片机音乐彩灯课程设计一、课程目标知识目标:1. 理解单片机的基本原理,掌握其编程方法。

2. 学习并掌握音乐彩灯电路的设计与制作,理解其工作原理。

3. 了解并掌握音符、节奏与灯光效果之间的关系,能运用单片机进行控制。

技能目标:1. 能够运用所学知识,独立设计并制作出具有音乐节奏控制功能的彩灯。

2. 培养学生的动手实践能力,提高问题解决能力和创新思维。

3. 学会使用相关软件(如Keil、Proteus等)进行单片机程序设计和电路仿真。

情感态度价值观目标:1. 培养学生对单片机及电子制作的兴趣,激发学生的学习热情和求知欲。

2. 培养学生的团队协作精神,提高沟通与交流能力。

3. 增强学生的自信心,培养克服困难、勇于创新的品质。

课程性质:本课程为实践性较强的课程,以项目为导向,注重培养学生的动手能力和创新能力。

学生特点:学生具备一定的电子基础知识,对单片机有一定了解,喜欢动手实践。

教学要求:结合学生特点,以学生为主体,教师为主导,采用任务驱动法、分组讨论法等教学策略,引导学生主动探索、实践和思考。

同时,注重个别辅导,关注学生的个体差异,使每位学生都能在原有基础上得到提高。

通过本课程的学习,使学生能够将所学知识应用于实际项目中,提高综合运用能力。

二、教学内容1. 单片机基础原理回顾:C51单片机的结构、工作原理,I/O口编程,中断系统,定时器/计数器应用。

2. 音乐基础:音符与节奏的基本知识,MIDI音乐文件格式解析,音符与单片机编程的关联。

3. 硬件设计:彩灯电路设计原理,LED灯的驱动方式,电阻、电容的选择与计算,电源管理。

4. 软件编程:使用Keil C编写单片机程序,实现音符播放与彩灯控制,程序调试与优化。

5. 电路仿真:利用Proteus进行电路仿真,验证程序与硬件设计的正确性。

6. 实践制作:分组进行音乐彩灯的设计与制作,包括电路搭建、程序烧写、功能测试。

7. 项目展示:每组展示自己的作品,介绍设计思路、制作过程和解决的关键问题。

单片机课程设计-基于单片机音乐彩灯电子控制器设计

提供全套毕业论文,各专业都有物理与电子工程学院《单片机》课程设计报告书设计题目:基于单片机音乐彩灯电子控制器设计专业:自动化班级: 14接本学生姓名:学号: 20140343112指导教师:2014年11 月16 日物理与电子工程学院课程设计任务书专业:自动化班级: 2014接本摘要随着人们生活环境的不断改善和美化,在许多场合可以看到彩色霓虹灯。

LED彩灯由于其丰富的灯光色彩,低廉的造价以及控制简单等特点而得到了广泛的应用。

本篇设计为基于单片机的音乐彩灯控制器,它是指彩灯能随着音乐信号地变化而变化的一种控制电路。

本文详细论述了音乐彩灯控制器的硬件原理电路,包括振荡、时钟、复位等模块电路。

以及如何在硬件电路的基础上通过单片机进行软件编程最终实现音乐彩灯的同步控制。

关键词:音乐;彩灯;同步控制目录1 引言 (4)2.1 设计任务与要求 (5)2.2 方案的论证和选取 (5)3 硬件电路的设计 (7)3.1 单片机系统设计框图 (7)3.2 单片机外围电路 (8)3.3 时钟电路 (9)3.5 按键电路 (11)3.6 ISP下载口电路 (11)3.7LED彩灯显示电路 (12)3.8 12864液晶电路 (12)3.9 音乐播放电路 (14)3.10 直流稳压电源电路 (15)4 系统软件设计 (16)4.1 单片机系统设计主程序流程图 (16)4.2 音乐产生程序 (20)4.3 定时器子程序设计序 (21)4.4 液晶显示子程序 (29)参考文献 (32)1 引言目前,基于彩灯控制器的设计的方法很多,有利用单片机控制的、有利用传感器控制的,还有利用EDA控制的等等。

在简化设计步骤和节约实验器材的情况下,为了简化硬件电路,也可采用PLC S7-20CN控制的,虽然硬件电路比较简便,但是实验程序更复杂,实验步奏更繁琐;对于编写程序是个比较困难的问题。

通常采用单片机控制的方法,即利用单片机的端口来控制彩灯以及音乐播放,在程序编写上更容易编写,程序的可编译性更强。

单片机音乐彩灯设计

艺术彩灯控制系统设计一.概述1.1 艺术彩灯的设计背景及意义彩灯是人们日常生活中的一种装饰用品,它美观大方,尤其在节日期间,倍增节日气氛。

它蕴涵着丰富的文化底蕴,被广泛地应用于各种店面的装饰。

变换无穷的彩灯样式,给城市增添活力,吸引着人们的注意力,深受人民的喜爱。

在日常生活中,人们还将彩灯摆放成各种图案,增添美感。

随着电子技术的发展,应用系统向着小型化、快速化、大容量、重量轻的方向发展。

科学技术更加贴近人们的生活,向着满足人们需求的方向发展。

节日彩灯的设计与制作工艺也一步一步的走向成熟。

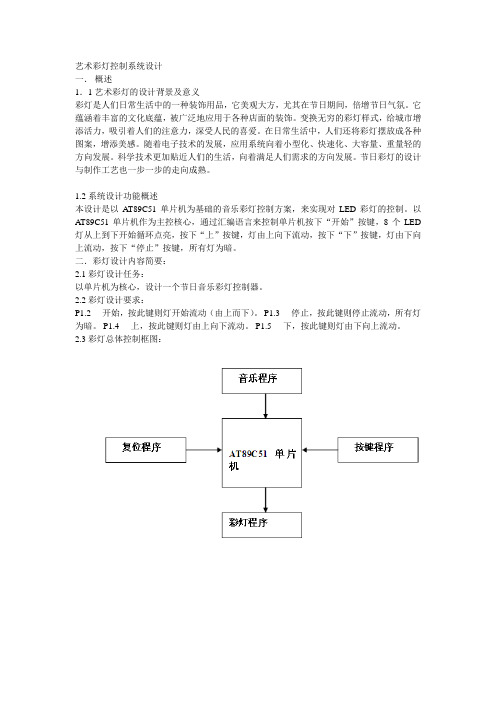

1.2 系统设计功能概述本设计是以AT89C51单片机为基础的音乐彩灯控制方案,来实现对LED彩灯的控制。

以AT89C51单片机作为主控核心,通过汇编语言来控制单片机按下“开始”按键,8个LED 灯从上到下开始循环点亮,按下“上”按键,灯由上向下流动,按下“下”按键,灯由下向上流动,按下“停止”按键,所有灯为暗。

二.彩灯设计内容简要:2.1彩灯设计任务:以单片机为核心,设计一个节日音乐彩灯控制器。

2.2彩灯设计要求:P1.2----开始,按此键则灯开始流动(由上而下)。

P1.3----停止,按此键则停止流动,所有灯为暗。

P1.4----上,按此键则灯由上向下流动。

P1.5----下,按此键则灯由下向上流动。

2.3彩灯总体控制框图:3.2 A T89C51单片机硬件结构:AT89C51是一种带4K字节闪存可编程可擦除只读存储器(FPEROM—Flash Programmable and Erasable Read Only Memory)的单片机芯片,它采用静态CMOS 工艺制造8位微处理器,最高工作频率位24MHZ。

AT89C5外形及引脚排列如图所示:管脚说明:RST:复位输入。

当振荡器复位器件时,要保持RST脚两个机器周期的高电平时间。

P0口:P0口为一个8位漏级开路双向I/O口,每脚可吸收8TTL门电流。

单片机课程设计+音乐彩灯开关控制

微机原理及接口技术课程设计设计题目:开关控制音乐彩灯闪烁设计指导老师:学生姓名:学院:班级:学号:设计时间:一.课程设计题目开关控制音乐彩灯闪烁系统设计二.设计功能说明用实验系统中的LED来代替彩灯,用定时器T1,工作方式1,通过8031的P1.0驱动LED 亮500ms,灭500ms闪烁。

利用定时器0 实现音阶的振荡频率,定时器1 实现音值的基本节拍控制,两者均工作于定时方式1 状态。

对于一般乐曲来讲,一拍的时间约占 0.5秒左右,且以1/4拍作为基本节拍,通过程序输入基本节拍的倍数,而实现音值的节拍时间控制。

程序设计中音乐的播放用接口P1.4输出,最后通过开关K1控制P1.0,开关K2控制P1.4,从而实现音乐的播放和停止,彩灯的亮灭。

三.设计内容1. 定时器T1,工作方式1产生500ms的定时程序驱动LED闪烁,设定时25ms的初值为X,则有(216-X)*0.000002 =0.025,X=53036=CF2C,在程序中给出TH,TL的赋值。

2.奏歌曲《两只蝴蝶》,乐谱为图一,其中每一音符占两个字节,第一个字节用于存放音阶代码,第二个字节用于存放节拍代码。

另外规定音阶代码00H表示休止符,80H表示反复演奏。

振荡频率的计算公式为:f=f0×2(i+j)/12其中f0=233.08188Hz(C调6.#)。

i音调修正值j音阶修正值歌曲《两只蝴蝶》乐谱图一 (G调)四.程序流程图五.程序清单ORG 0000H ;程序开始AJMP LP0 ;跳转乐曲信息表首地址ORG 000BHAJMP LP6 ;跳转至音阶代码ORG 001BHAJMP PTIINT ;中断彩灯闪烁服务程序MOV DPTR, #0F0H ;送外部端口地址MOVX A,@DPTR ;读入开关状态MOVX @DPTR,A ;根据开关状态,驱动发光二极管 MOV P1,A ;开关控制接口P1START:MOV R7,#14H ;R7=14MOV TMOD,#10H ;中断方式MOV TL1,#2CHMOV TH1,#CFHSETB EA ;开放总中断SETB ET1 ;开放T1中断SETB TR1 ;启动定时器T1SJMP $PTIINT:MOV TL1,#2CH ;恢复计算初值MOV TH1,#CFHDJNZ R7,PEND ;判断是否循环发生了20次MOV R7,#05HCPL P1.0 ;500ms后取反LP0:MOV DPTR,#TABLE ;乐曲音符信息表首地址MAIN:CLR AMOVC A,@A+DPTR ;读音阶代码MOV R5,AMOV R0,ACLR AINC DPTRMOVC A,@A+DPTR ;读节拍代码MOV R4,AMOV A,R5 ;重读音阶代码DEC ARL A ;以两个字节为单位查表MOV R5,A ;代码转存ADD A,#41H ;与TABLE0间的偏移量MOVC A,@A+PC ;查得音阶定时初值高8位MOV TH0,AMOV R3,A ;初值高8位转存MOV A,R5 ;重新装入音阶代码ADD A,#3BHMOVC A,@A+PCMOV TL0,AMOV R2,AMOV TMOD,#11HMOV A,#05HMOV B,R4MUL ABMOV R4,AMOV TH1,#0CFHMOV TL1,#2CHSETB TR1CJNE R0,#80H,LP1 ;若没有结束,转至LP1AJMP LP0 ;否侧重新开始LP1: CJNE R0,#00H,LP2 ;不为休止符,转至LP2,否则转至LP4 AJMP LP4LP2: SETB TR0 ;所读音阶不是休止符,启动定时器T0SETB EASETB ET0LP3: JNB TF1,$ ;TF1不为0,则原地执行CLR TF1 ;当发生中断时,重设TF1为0DJNZ R4,LP5INC DPTRAJMP MAINLP4:CLR TR0CLR EAAJMP LP3LP5: MOV TH1,#0CFHMOV TL1,#2CHAJMP LP3 ;跳至LP3重新判断TABLE0:DW 0FCADH ;音阶对应的定时初值表DW 0FD0AHDW 0FD5DHDW 0FD82HDW 0FDC8HDW 0FE06HDW 0FE22HDW 0FE57HDW 0FE85HDW 0FEAEHDW 0FEC1HDW 0FEE4HDW 0FF03HLP6: MOV TH0,R3MOV TL0,R2CPL P1.4 ;取反得到方波RETTABLE: DW 0602H,0502H,0604H,0602H ;乐曲对应的音阶和节拍代码DW 0502H,0602H,0502H,0404HDW 0202H,0402H,0504H,0502H,0602HDW 0502H,0402H,0202H,0402H,0804HDW 0602H,0502H,0604H,0602H,0502HDW 0602H,0502H,0404H,0202H,0402HDW 0504H,0502H,0602H,0502H,0402H,0202H,0402H,0504HDW 0602H,0502H,0604H,0602H,0502HDW 0602H,0502H,0404H,0202H,0402HDW 0504H,0502H,0602H,0502H,0402H,0202H,0402H,0804HDW 0602H,0802H,0804H,0802H,0802HDW 0902H,0802H,0604H,0502H,0602HDW 0504H,0502H,0602H,0502H,0402H,0201H,0201H,0402HDW 0402H,0402H,0404H,0004H,0804HDW 0802H,0902H,0B02H,0A02H,0A02H,0902HDW 0606H,0502H,0502H,0602H,0604HDW 0002H,0602H,0602H,0802H,0904H,0906H,0204H,0502H,0202H,0204H DW 0602H,0802H,0802H,0602H,0804H,0004H,0B04H,0A04HDW 0902H,0A02H,0604H,0002H,0902H,0902H,0A02HDW 0902H,0802H,0604H,0504H,0604H,0502H,0602H,0804HDW 0002H,0802H,0802H,0902H,0902H,0802H,0604H,0504H,0604H,0504H DW 0104H,0102H,0202H,0404HDB 8OHEND音乐彩灯控制原理图七.设计中遇到的问题及解决方法由于该门知识涉及面太广,又有些艰涩难懂,所以该不免有些不足之处,在我们设计和调试的过程中,也发现了一些问题,出现联机失败提示,结束运行,重新进行操作,并在写程序之前按下通讯键PCDBG。

单片机的四开关循环彩灯的设计课程设计

单片机的四开关循环彩灯的设计课程设计一、引言在现代电子技术领域中,单片机是一种功能强大且应用广泛的微处理器。

它具有体积小、功耗低、成本低廉等优点,因此被广泛应用于各种电子设备中。

其中,单片机的四开关循环彩灯设计是一项常见且有趣的课程设计项目。

本文将详细介绍该课程设计的步骤和要点。

二、设计目标本次课程设计旨在通过使用单片机和四个开关来实现一个循环彩灯系统。

具体目标如下:1. 使用四个开关控制不同颜色的LED灯的亮灭;2. 实现循环播放不同颜色的灯光效果;3. 设计简洁、易于理解和操作的系统。

三、硬件设计1. 单片机选择根据设计目标,我们可以选择适合该项目的单片机。

常见的单片机有PIC系列、AVR系列等,这里我们选择使用AVR系列的ATmega16单片机。

2. LED灯和电阻为了实现彩灯效果,我们需要准备四个不同颜色(红色、绿色、蓝色和黄色)的LED灯,并且每个LED都需要连接一个合适的电阻以限制电流。

3. 开关我们需要准备四个开关,每个开关对应一个LED灯。

这些开关用于控制LED灯的亮灭。

四、软件设计1. 系统初始化在程序开始时,我们需要初始化单片机的引脚和寄存器。

具体步骤如下:- 设置引脚方向:将LED灯所连接的引脚设置为输出,将开关所连接的引脚设置为输入。

- 设置初始状态:将所有LED灯关闭。

2. 主循环主循环是整个系统的核心部分,它负责读取开关状态并控制LED灯的亮灭。

具体步骤如下:- 读取开关状态:通过读取每个开关所连接引脚的电平来确定其状态(高电平表示按下,低电平表示未按下)。

- 根据开关状态控制LED灯:根据不同的开关状态来控制对应LED 灯的亮灭。

当按下第一个开关时,打开红色LED;当按下第二个开关时,打开绿色LED;以此类推。

- 实现循环播放效果:在每次循环中依次点亮不同颜色的LED灯,并保持一段时间后熄灭。

五、系统测试在完成硬件和软件设计后,我们需要进行系统测试以验证其功能和稳定性。

单片机下的音乐节奏彩灯控制系统设计

单片机下的音乐节奏彩灯控制系统设计提纲:一、设计背景及意义二、设计原理及方案三、系统实现方式四、硬件设计及调试五、软件设计及调试一、设计背景及意义近年来,随着单片机技术的不断发展和应用,越来越多的人开始将其应用于各个领域,尤其是在音乐和灯光控制领域中。

因而,设计一种基于单片机的音乐节奏彩灯控制系统具有重要的现实意义和实际价值。

该系统主要目的是实现对彩灯亮度、颜色、模式等进行调节,同时根据音乐的不同节奏和速度实现灯光的变化,增加彩灯的艺术性和观赏性。

因此,基于该系统可以为演出、KTV、酒吧等提供更加丰富的灯光效果,从而增强现场气氛。

二、设计原理及方案该系统主要原理是通过单片机控制和调节彩灯的亮度、颜色和模式,同时根据音乐的不同节奏和速度实现灯光的变化,从而实现音乐节奏彩灯的控制。

具体方案如下:1. 彩灯选择采用RGB LED灯光作为彩灯,通过控制不同的灯珠来实现不同的颜色和亮度。

2. 技术选型选择STM32F103C8T6作为单片机主控芯片,并使用脉宽调制(PWM)技术控制灯光亮度和颜色。

3. 灯光控制设计灯光控制电路,通过单片机控制开关来选择不同的彩灯效果,并通过PWM技术控制灯光的亮度。

4. 音乐节奏检测采用LM393声音传感器实现音频信号的检测和分析,通过单片机控制来实现不同的灯光效果。

三、系统实现方式该系统的实现方式主要包括硬件和软件两个方面。

硬件方面,需要进行电路设计和调试,包括STM32F103C8T6控制器、RGB LED灯光、LM393声音传感器、电容、电阻等元器件的连接和调试。

软件方面,需要进行程序设计和调试,包括音乐节奏分析算法、PWM控制算法、灯光选择算法、彩灯颜色变换算法等,同时需要根据实际应用需求不断进行优化和改进。

四、硬件设计及调试硬件设计主要包括选型、电路设计、零件选择和调试等步骤。

具体步骤如下:1. 选型根据系统需求选择合适的芯片、传感器、LED灯珠等元器件。

2. 电路设计根据系统需求设计电路图并进行电路布局。

基于单片机的音乐彩灯控制器的设计——任务书

要求将音乐分成四个不同的频段,将彩灯分为四组,各组彩灯颜色不同,每组彩灯包含两个颜色相同的彩灯。

1、实现音乐彩灯同步控制

2、当音乐出于高频段2000-4000HZ时第一组彩灯根据音乐幅度强弱不同产生不同的亮度;

3、当音乐出于中频段500-1200HZ时第二组彩灯根据音乐幅度强弱不同产生不同的亮度;

2012届毕业论文(设计)题目申报表

申报题目名称

基于单片机的音乐彩灯控制器的设计

题目来源

教师自选

课题类型

工程设计

题

目

简

介

包括研究的目的、内容和意义,预计题目难易程度、工作量大小等

在当今这个社会,音乐彩灯的发展非常广泛,各种娱乐场所,酒店,广场等都采用了彩灯烘托环境的美好。而音乐彩灯能在音乐的节奏下闪耀,更能给客人以全新的感觉。随着电子技术的发展,对音乐彩灯的控制也就相当的容易了,无论是从技术上讲还是从需求上讲,音乐彩灯都有很高的发展前景。相比传统的中小规模集成电路和计算机控制,采用单片机来设计彩灯控制器具有体积小、功耗低、可靠性高、调节灵活等优点。

学生开始执行任务书日期:

学生完成毕业论文(设计)日期:

指导教师(签名):二级学院院长(签名):

年月日年月日

2011-7-11~2011-8-31收集资料,撰写开题报告

2011-9-1~2011-9-11提交开题报告

2011-9-12~2011-9-30方案比较论证,撰写论文初稿

2011-10-1~2011-10-15中期检查,提交论文初稿

2011-10-16~2011-10-29修改论文,提交论文定稿

2011-10-30~2011-11-5准备答辩

基于单片机的音乐彩灯控制系统

毕业设计(论文)题目基于单片机音乐彩灯控制器的设计系部电子信息工程系专业电子信息工程姓名学号指导教师2016 年 3 月31 日基于单片机的音乐彩灯控制器设计[摘要]本设计是一种基于AT89C51单片机音乐控制彩灯的方案,实现单片机演奏音乐,并且对LED彩灯随音符频率的不同而闪烁发光。

本方案以AT89C51单片机作为主控核心,通过三极管放大电流使用蜂鸣器播放音乐,利用编程实现亮灯循环模式,在有8个LED彩灯, 根据用户需求可以编写若干种亮灯模式. 例如左右闪烁,隔几个亮灭,蜂鸣器可以根据用户需求改写编程播放各种音乐。

本方案具有设计简单、体积小、元器件少、电路结构简单等优点。

该设计方案设计及其简单,典型的AT89C51单片机,亮灯模式多,播放各种类型的音乐,具有体积小、价格低、低能耗等优点。

在美丽的都市夜晚,彩灯的循环亮灭,播放动人的音乐,衬托出美丽的氛围。

[关键词]AT89C51 LED 彩灯音乐Music lights controller design based on SCM[Abstract]this design is based on the AT89C51 microcontroller music programme control lights, single-chip computer to play music and to note the frequency of the LED lights but without flashing. The programme with AT89C51 microcontroller as the main control core, by transistor amplifier current using a buzzer to play music, using programmed light cycle mode 8 LED lights, can prepare several kinds of lighting patterns according to user needs. For example about Flash, a few on or off, the buzzer can be based on user demand overwrite the programmed play all kinds of music. The programme has a simple design, small size, less components and advantages of simple circuits. The scheme design and simple, typical AT89C51 microcontroller, lighting models, play various types of music, has the advantages of small size, low price and low energy consumption. In the beautiful city of night lights cycle on or off, playing lovely music, bring out the beautiful atmosphere.[Key words] AT89C51 LED lights music目录绪论 (3)1 音乐彩灯方案设计与选择 (5)1. 1 设计要求 (5)1. 2 基本原理 (5)1. 3 设计电源 (6)1. 4 频率音符 (6)2 音乐彩灯设计过程 (7)2. 1 元器件选取 (7)2. 2 电路设计 (7)2. 2. 1 元器件介绍 (7)2. 2. 2 音乐彩灯构思 (10)2. 3 软件设计 (13)2. 3. 1 编程介绍 (13)2. 3. 2 设计程序 (16)3 心得体会 (18)3. 1 课程设计总结 (18)3. 2 收获与体会 (19)参考文献 (20)绪论单片机诞生于 1971 年,经历了 SCM、 MCU、 SoC 三大阶段,早期的 SCM 单片机都是 8 位或 4位的。

单片机彩灯控制器设计

单片机彩灯控制器设计一、硬件设计1.主控单元选择:主控单元选用常用的单片机芯片,如STC89C52、AT89C52等,这种芯片具有成本低、可靠性高、易于编程等特点。

2.彩灯控制电路:彩灯控制电路可以采用常见的PWM(脉宽调制)电路,其中使用光电隔离器将主控单元与触摸开关进行电气隔离,以提高安全性。

通过PWM电路可以调整RGB(红绿蓝)三种基本颜色的亮度,从而实现多种颜色的组合。

3.连接器和线缆:为了方便安装和更好地布局,可以在控制器外壳上设置合适的连接器,如插头或插座。

使用高质量的线缆连接控制器和彩灯,以确保信号的稳定传输。

二、软件设计1.硬件初始化:在程序开始时,需要对单片机的各个端口进行初始化设置。

如设置I/O口接收和发送数据,设置定时器等。

2.触摸开关控制:通过读取触摸开关状态,可以实现对彩灯的开关、颜色切换等控制。

在触摸开关按下时,单片机可以通过读取触摸开关对应的I/O口电平变化来实现相应的功能。

3.调整亮度:可以通过按下触摸开关不同的次数或按下不同的触摸区域来调整彩灯的亮度。

单片机可以通过改变PWM的占空比来控制彩灯的亮度。

4.调整颜色:通过触摸开关可以实现彩灯颜色的切换。

根据按下的次数或按下的区域,单片机可以改变RGB三个通道的PWM占空比,从而实现不同颜色的混合。

5.模式切换:可以通过触摸开关实现不同的彩灯模式切换,如渐变、闪烁、呼吸等。

单片机可以通过改变PWM的频率和占空比来控制彩灯的亮度和变化速度。

三、应用场景举例1.室内装饰照明:单片机彩灯控制器可以用于室内的装饰照明,如客厅、卧室、书房等。

通过控制器可以实现不同颜色和亮度的灯光效果,营造出不同的氛围。

2.室外建筑照明:单片机彩灯控制器可以用于室外建筑照明,如大楼、桥梁、喷泉等。

可以通过控制器实现彩灯颜色的切换和模式的变化,为夜晚的城市增添美丽的景观。

3.舞台灯光:单片机彩灯控制器可以用于舞台灯光的控制。

可以根据音乐的节奏和舞蹈的动作,通过控制器实现灯光的闪烁、渐变等效果,增加舞台表演的视觉效果。

基于单片机的彩灯设计

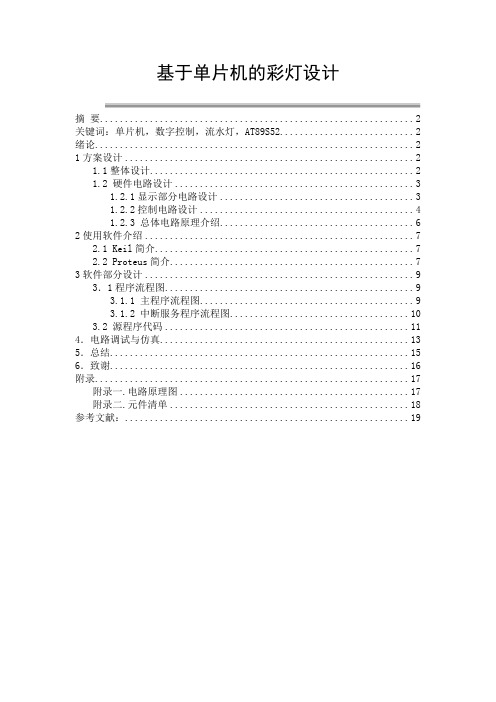

基于单片机的彩灯设计摘要 (2)关键词:单片机,数字控制,流水灯,AT89S52 (2)绪论 (2)1方案设计 (2)1.1整体设计 (2)1.2 硬件电路设计 (3)1.2.1显示部分电路设计 (3)1.2.2控制电路设计 (4)1.2.3 总体电路原理介绍 (6)2使用软件介绍 (7)2.1 Keil简介 (7)2.2 Proteus简介 (7)3软件部分设计 (9)3.1程序流程图 (9)3.1.1 主程序流程图 (9)3.1.2 中断服务程序流程图 (10)3.2 源程序代码 (11)4.电路调试与仿真 (13)5.总结 (15)6.致谢 (16)附录 (17)附录一.电路原理图 (17)附录二.元件清单 (18)参考文献: (19)摘要本文设计了一种基于单片机的简易流水等的控制系统。

系统由AT89S52、LED 发光二极管、按键,可以实现彩灯的不同类型显示切换。

其硬件电路主要有主控制器,LED显示电路,复位电路,晶振电路。

系统程序的设计包括主程序的设计,中断服务程序等等本系统以单片机汇编语言进行软件设计,由于汇编语言与单片机底层结合,使程序设计的逻辑关系更加简洁明了。

此程序直接在Keil软件编译程序,利用Proteus进行仿真调试,方便修改程序。

关键词:单片机,数字控制,流水灯,AT89S52绪论当今时代是一个新技术层出不穷的时代,在电子领域尤其是自动化智能控制领域,传统的分立元件或数字逻辑电路构成的控制系统,正以前所未见的速度被单片机智能控制系统所取代。

随着人们生活水平的不断提高,单片机控制无疑是人们追求的目标之一,它所给人带来的方便也是不可否定的。

单片机具有体积小、功能强、成本低、应用面广等优点,可以说,智能控制与自动控制的核心就是单片机。

目前,一个学习与应用单片机的高潮正在工厂、学校及企事业单位大规模地兴起。

学习单片机的最有效方法就是理论与实践并重,本文用AT89C52单片机自制了一款可实现多种循环显示状态的流水灯,重点介绍了其软件编程方法。

音乐彩灯控制器课程设计说明书

学号:0121111360104题目音乐数字彩灯控制器设计学院自动化专业自动化班级1101姓名温志伟指导教师李彬、林伟2013 年7 月 5 日课程设计任务书学生姓名:温志伟专业班级:自动化1101指导教师:李彬、林伟工作单位:武汉理工大学题目: 音乐数字彩灯控制器设计初始条件:1)运用所学的模拟电路和数字电路等知识;2)用到的元件:实验板、电源、连接导线、74系列芯片、555芯片或微处理器等。

要求完成的主要任务:1)数码管自动依次显示数字队列0,1,2,3,4,5,6,7,8,9(自然数列);1,3,5,7,9(奇数列);0,2,4,6,8(偶数列);0,1,2,3,4,5,6,7,0,1(音乐数列)。

然后又依次显示同上数列,不断循环;2)打开电源开关,自动清零,即通电后最先显示出自然数列的0,再显示出1,然后按上述规律变化;3)每个数字的一次显示时间(从数码管显示之时起到消失之时止)基本相等。

4)严格按照课程设计说明书要求撰写课程设计说明书。

时间安排:第1天下达课程设计任务书,根据任务书查找资料;第2~4天进行方案论证,软件模拟仿真并确定设计方案;第5天提交电路图,经审查后领取元器件;第6~8天组装电路并调试,检查错误并提出问题;第9~11天结果分析整理,撰写课程设计报告,验收调试结果;第12~14天补充完成课程设计报告和答辩。

指导教师签名: 2013年 6月24日系主任(或责任教师)签名: 2013年 6月24日目录引言 (1)1设计意义及要求 (2)1.1设计意义 (2)1.2设计要求 (2)2方案设计 (3)2.1设计思路 (3)2.2设计方案 (3)2.2.1方案一(个人设计方案) (3)2.2.2方案二(小组设计方案) (4)2.3方案比较 (5)3部分电路设计 (6)3.1脉冲产生电路 (6)3.2自然数列、奇偶数列、音乐数列产生电路 (7)3.2.1自然数列的产生 (7)3.2.2奇偶数列的产生 (8)3.2.3音乐数列的产生 (9)3.3选通电路的实现 (10)3.4数码显示电路 (11)4调试与检测 (13)4.1调试中故障及解决办法 (13)4.2调试与运行结果 (13)5仿真操作步骤及使用说明 (14)6体会与总结 (15)参考文献 (16)引言随着基础理论课程的结束,课程设计也即将开始。

单片机课程设计_音乐彩灯控制器设计

《音乐彩灯控制器设计》课程设计说明书专业班级:电信四班姓名:印筱峰080212145姓名:岳信080212162姓名:王亮080212138指导教师:纪娟娟老师设计时间: 2014年5月27-6月6号物理与电气工程学院2014年6月6日目录一绪论1.1 引言.................................................................. 错误!未定义书签。

二方案论证 (2)2.1设计原理 (2)2.2引脚说明 (2)三系统硬件电路设计 (5)3.1彩灯总体框图 (5)3.2设计要求 (5)四系统软件设计 (6)4.1 彩灯总体控制框图 (6)4.2 设计说明 (6)4.3 元器件清单 (6)4.4 音乐彩灯程序流程图 (7)4.5音乐彩灯系统程序部分 (7)五调试及性能分析 (12)六总结 (13)参考文献 (13)一绪论1引言彩灯是人们日常生活中的一种装饰用品,它美观大方,尤其在节日期间,倍增节日气氛。

它蕴涵着丰富的文化底蕴,被广泛地应用于各种店面的装饰。

变换无穷的彩灯样式,给城市增添活力,吸引着人们的注意力,深受人民的喜爱。

在日常生活中,人们还将彩灯摆放成各种图案,增添美感。

随着电子技术的发展,应用系统向着小型化、快速化、大容量、重量轻的方向发展。

科学技术更加贴近人们的生活,向着满足人们需求的方向发展。

节日彩灯的设计与制作工艺也一步一步的走向成熟。

随着人们生活环境的不断改善和美化,在许多场合可以看到彩色霓虹灯。

LED 彩灯由于其丰富的灯光色彩,低廉的造价以及控制简单等特点而得到了广泛的应用,用彩灯来装饰已经成为一种时尚。

但目前市场上各式样的LED 彩灯控制器大多数用全硬件电路实现,电路结构复杂、功能单一,这样一旦制作成品只能按照固定的模式闪亮,不能根据不同场合、不同时间段的需要来调节亮灯时间、模式、闪烁频率等动态参数。

这种彩灯控制器结构往往有芯片过多、电路复杂、功率损耗大等缺点。

单片机彩灯的设计报告

单片机彩灯的设计报告1. 引言彩灯是一种能够发出丰富多彩的光线的装饰灯具,在各种场合中广泛应用,如家庭聚会、商业展示和舞台演出等。

为了实现不同颜色和灯光效果之间的切换,我们设计了一套基于单片机的彩灯系统。

2. 设计目标本彩灯系统的设计目标是实现以下功能:1. 支持多种颜色的灯光发射;2. 可以自动进行颜色切换;3. 可以通过外部设备进行手动控制;4. 方便灵活的系统扩展。

3. 系统硬件设计3.1 主控芯片我们选择了一种适合彩灯控制的低成本、低功耗的单片机作为主控芯片。

该单片机具有丰富的IO端口和较大的存储空间,可以满足我们的需求。

3.2 灯光发射模块我们选用了RGB三色LED作为彩灯的光源,可通过调节各个颜色的亮度来混合得到不同的颜色效果。

使用三个单向可控硅(Triac)对三色LED 进行调光控制。

3.3 控制电路主控芯片与灯光发射模块之间通过一个适配电路进行联接。

适配电路可以将单片机输出的数字控制信号转换为模拟控制信号,控制灯光发射模块的亮度和颜色。

3.4 电源系统彩灯系统需要一个可靠的电源系统,我们使用稳压电源模块来提供稳定的电压。

同时,考虑到系统扩展和方便性,我们为每个模块设计了独立的电源接口。

4. 系统软件设计4.1 系统初始化系统上电时,单片机进行初始化,设置各个IO口的工作模式和初始状态。

同时,初始化控制寄存器以设置定时器、启用中断等必要操作。

4.2 彩灯控制算法彩灯的控制算法分为手动模式和自动模式。

在手动模式下,系统会通过读取外部设备输入的信号来控制灯光的亮度和颜色。

根据输入信号的不同,单片机会相应地改变各个颜色的输出占空比来实现灯光的调控。

在自动模式下,系统会周期性地进行颜色切换。

通过定时器和中断机制,单片机按照预设的时间来自动改变各个颜色的输出占空比,实现灯光的渐变效果。

4.3 扩展性设计为了方便系统的扩展,我们在设计过程中考虑了一些扩展性问题。

例如,我们通过引入外部传感器接口,可以实现灯光与环境亮度、音乐节奏等外部因素的联动控制。

基于单片机的音乐流水灯设计

单片机原理及系统课程设计专业:电气工程及其自动化班级:电气1003班*名:***学号:指导教师:兰州交通大学自动化与电气工程学院2013 年 3 月 7 日基于单片机的音乐流水灯设计摘要本设计是一种基于AT89C52单片机音乐控制彩灯的方案,实现单片机演奏音乐,并且对LED彩灯随音符频率的不同而闪烁发光。

本方案以AT89C52单片机作为主控核心,通过三极管放大电流使蜂鸣器播放音乐,利用编程实现循环点亮24个太极图案的LED彩灯,根据用户需求可以编写若干种亮灯模式.,蜂鸣器可以根据用户需求改写编程播放各种音乐。

本方案具有电路结构简单、体积小、元器件少、能耗低等优点。

在美丽的都市夜晚音乐彩灯为我们的生活增添了无限光彩。

音乐彩灯具有更广阔的发展天地。

关键字:AT89C51;LED彩灯;音乐AbstractThe design is based on AT89C52 microcontroller music control lantern program microcontroller playing music, and note the frequency of different flashing light LED Lantern with. Program AT89C52 microcontroller as the master core through the transistor amplifier to the current buzzer play music programming cycle LED lantern lit 24 Taiji patterns can write certain kinds of lighting modes according to user needs, beep can rewrite the program play a variety of music based on user demand. The program has a simple circuit structure, small size, fewer components and lower energy consumption. Add unlimited glory for our lives in the beautiful city night music Lantern. Music lantern has a broader development world.Keywords: AT89C51,LED Lantern,music1引言1.1设计目的:设计是学生理论联系实际的重要实践教学环节,是对学生进行的一次综合性专业设计训练。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

艺术彩灯控制系统设计一.概述1.1 艺术彩灯的设计背景及意义彩灯是人们日常生活中的一种装饰用品,它美观大方,尤其在节日期间,倍增节日气氛。

它蕴涵着丰富的文化底蕴,被广泛地应用于各种店面的装饰。

变换无穷的彩灯样式,给城市增添活力,吸引着人们的注意力,深受人民的喜爱。

在日常生活中,人们还将彩灯摆放成各种图案,增添美感。

随着电子技术的发展,应用系统向着小型化、快速化、大容量、重量轻的方向发展。

科学技术更加贴近人们的生活,向着满足人们需求的方向发展。

节日彩灯的设计与制作工艺也一步一步的走向成熟。

1.2 系统设计功能概述本设计是以AT89C51单片机为基础的音乐彩灯控制方案,来实现对LED彩灯的控制。

以AT89C51单片机作为主控核心,通过汇编语言来控制单片机按下“开始”按键,8个LED灯从上到下开始循环点亮,按下“上”按键,灯由上向下流动,按下“下”按键,灯由下向上流动,按下“停止”按键,所有灯为暗。

二.彩灯设计容简要:2.1彩灯设计任务:以单片机为核心,设计一个节日音乐彩灯控制器。

2.2彩灯设计要求:P1.2----开始,按此键则灯开始流动(由上而下)。

P1.3----停止,按此键则停止流动,所有灯为暗。

P1.4----上,按此键则灯由上向下流动。

P1.5----下,按此键则灯由下向上流动。

2.3彩灯总体控制框图:3.2 AT89C51单片机硬件结构:AT89C51是一种带4K字节闪存可编程可擦除只读存储器(FPEROM—Flash Programmable and Erasable Read Only Memory)的单片机芯片,它采用静态CMOS 工艺制造8位微处理器,最高工作频率位24MHZ。

AT89C5外形及引脚排列如图所示:管脚说明:RST:复位输入。

当振荡器复位器件时,要保持RST脚两个机器周期的高电平时间。

P0口:P0口为一个8位漏级开路双向I/O口,每脚可吸收8TTL门电流。

当P1口的管脚第一次写1时,被定义为高阻输入。

P0能够用于外部程序数据存储器,它可以被定义为数据/地址的第八位。

在FIASH编程时,P0 口作为原码输入口,当FIASH进行校验时,P0输出原码,此时P0外部必须被拉高。

P1口:P1口是一个部提供上拉电阻的8位双向I/O口,P1口缓冲器能接收输出4TTL 门电流。

P1口管脚写入1后,被部上拉为高,可用作输入,P1口被外部下拉为低电平时,将输出电流,这是由于部上拉的缘故。

在FLASH编程和校验时,P1口作为第八位地址接收。

P2口:P2口为一个部上拉电阻的8位双向I/O口,P2口缓冲器可接收,输出4个TTL 门电流,当P2口被写“1”时,其管脚被部上拉电阻拉高,且作为输入。

并因此作为输入时,P2口的管脚被外部拉低,将输出电流。

这是由于部上拉的缘故。

P2口当用于外部程序存储器或16位地址外部数据存储器进行存取时,P2口输出地址的高八位。

在给出地址“1”时,它利用部上拉优势,当对外部八位地址数据存储器进行读写时,P2口输出其特殊功能寄存器的容。

P2口在FLASH编程和校验时接收高八位地址信号和控制信号。

P3口:P3口管脚是8个带部上拉电阻的双向I/O口,可接收输出4个TTL门电流。

当P3口写入“1”后,它们被部上拉为高电平,并用作输入。

作为输入,由于外部下拉为低电平,P3口将输出电流(ILL)这是由于上拉的缘故。

ALE/PROG:当访问外部存储器时,地址锁存允许的输出电平用于锁存地址的地位字节。

在FLASH编程期间,此引脚用于输入编程脉冲。

在平时,ALE端以不变的频率周期输出正脉冲信号,此频率为振荡器频率的1/6。

因此它可用作对外部输出的脉冲或用于定时目的。

然而要注意的是:每当用作外部数据存储器时,将跳过一个ALE脉冲。

如想禁止ALE的输出可在SFR8EH地址上置0。

此时,ALE只有在执行MOVX,MOVC指令是ALE才起作用。

另外,该引脚被略微拉高。

如果微处理器在外部执行状态ALE禁止,置位无效。

PSEN:外部程序存储器的选通信号。

在由外部程序存储器取指期间,每个机器周期两次PSEN有效。

但在访问外部数据存储器时,这两次有效的PSEN信号将不出现。

EA/VPP:当EA保持低电平时,则在此期间外部程序存储器(0000H-FFFFH),不管是否有部程序存储器。

注意加密方式1时,EA将部锁定为RESET;当EA端保持高电平时,此间部程序存储器。

XTAL1和XTAL2:反向振荡放大器的输入及部时钟工作电路的输入。

3.3系统的硬件构成及功能描述:控制系统硬件设计电路图如图所示:四.系统的软件设计ORG 0000HAJMP MAINORG 000BHAJMP INTORG 0020HMAIN: JNB P1.2,START ;判断按键P1.2(开始键)为0时转MAIN程序JMP MAIN ;否则返回START: MOV 50H,#HIGH TABLE10 ;开始(默认情况下上到下)MOV 51H,#LOW TABLE10ACALL BOFANG ;音乐播放初始设置LJMP DOWNLIGHTSTOP: MOV P0,#0FFH ;停止SETB P3.5JNB P1.2,STARTAJMP STOPDOWN: MOV 50H,#HIGH TABLE10 ;上到下MOV 51H,#LOW TABLE10ACALL BOFANG ;音乐播放初始设置DOWNLIGHT: MOV DPTR,#TABLE1 ;将TABLE1首地址赋数据指针 AJMP GETDATAUP: MOV 50H,#HIGH TABLE10 ;下到上MOV 51H,#LOW TABLE10ACALL BOFANG ;音乐播放初始设置UPLIGHT: MOV DPTR,#TABLE2 ;将TABLE2首地址赋数据指针GETDATA: MOV R0,#08HMOV R6,DPH ;暂存指针值MOV R7,DPLLOOP: CLR A ;A清零MOV DPH,R6MOV DPL,R7MOVC A,A+DPTR ;表数据送AMOV P0,A ;将A值送P0端口INC DPTR ;数据指针加1,指向表中的下一数据MOV R6,DPHMOV R7,DPLJNB P1.2,START ;P1.2口低电平则转START程序执行JNB P1.3,STOP ;P1.3口低电平则转STOP程序执行JNB P1.4,DOWN ;P1.4口低电平则转DOWN执行JNB P1.5,UP ;P1.5口低电平则转UP左循环程序执行LJMP MUSIC ;跳转音乐程序BACK: DJNZ R0,LOOPCLR A ;判断是上还是下MOV DPH,R6MOV DPL,R7MOVC A,A+DPTRJNZ DOWNLIGHTLJMP UPLIGHT BOFANG:MOV TMOD,#11H ;音乐播放初始设置MOV IE,#82HMOV 40H,#00HRETMUSIC: MOV A,40H ;音乐播放处理MOV DPH,50H ;取表地址MOV DPL,51HMOVC A,A+DPTR ;将表数据送累加器AJZ STOP2 ;累加器A为0则转移(说明歌曲播放完得重新播放) MOV R1,AANL A,#0FHRL AMOV R2,AMOV A,R1SWAP AANL A,#0FHJNZ SINGCLR TR0LJMP W1SING: DEC AMOV 22H,ARL AMOV DPTR,#TABLE00MOVC A,A+DPTRMOV TH0,AMOV 21H,AMOV A,22HRL AINC AMOVC A,A+DPTRMOV TL0,AMOV 20H,ASETB TR0W1: LCALL DELAYINC 40HJNZ STOP1 ;A不为0则转移LJMP BACKSTOP1: CLR TR0 ;音符结束重新播放处理LJMP BACKSTOP2: CLR TR0 ;整首歌曲播放结束处理MOV R2,#03HLCALL DELAYLCALL BOFANGLJMP BACKTABLE00: DW 64580,64684,64777,64820DW 64898,64968,65030,64260DW 64400,64524,65058,63835,64021INT: PUSH PSWPUSH ACCMOV TH0,21HMOV TL0,20HCPL P3.5POP ACCPOP PSWRETIDELAY: MOV R4,#100 ;延时100msLOOP3: MOV R5,#0FFHLOOP4: DJNZ R5,$DJNZ R4,LOOP3DJNZ R2,DELAYRETTABLE1:DB 0FEH,0FDH,0FBH,0F7H,0EFH,0DFH,0BFH,7FH,01H TABLE2:DB 7FH,0BFH,0DFH,0EFH,0F7H,0FBH,0FDH,0FEH,00H TABLE10:DB 0d4H,84H,94H,82H,92HDB 12H,22H,82H,92H,02H,92H,82H,0d2HDB 82H,92H,14H,84H,02H,0d1H,0d1HDB 0c2H,0d2H,84H,0d2H,0d2H,82H,82HDB 84H,82H,82H,94H,82H,0d2HDB 82H,82H,82H,92H,02H,82H,82H,0d2HDB 0c4H,84H,0d4H,92H,0d2HDB 82H,0d2H,82H,92H,98HDB 04H,94H,88HDB 04H,94H,88HDB 04H,94H,88HDB 04H,94H,88H,04HDB 32H,32H,22H,12H,02H,92H,12H,92HDB 32H,32H,22H,12H,02H,92H,12H,92HDB 32H,32H,22H,12H,02H,92H,12H,22HDB 54H,44H,34H,12H,22HDB 34H,22H,12H,02H,92H,12H,92HDB 32H,32H,22H,12H,02H,92H,12H,92HDB 32H,32H,22H,12H,02H,92H,12H,22HDB 54H,44H,32H,22H,12H,92HDB 00HEND4.1程序流程图:四.系统的软件设计4.1程序流程图:程序如下:ORG 0000H AJMP MAIN ORG 000BH AJMP INT ORG 002 0H MAIN:JNB P1.2,START ;判断按键P1.2(开始键)为0时转MAIN程序JMP MAIN ;否则返回START:MOV 50H,#HIGH TABLE10 开始(默认情况下上到下)MOV 51H,#LOW TABLE10 ACALL BOFANG ;音乐播放初始设置LJMP DOWNLIGHTSTOP:MOV P0,#0FFH 停止SETB P3.5JNB P1.2,START AJMP STOPDOWN:MOV 50H,#HIGH TABLE10 ;上到下MOV 51H,#LOW TABLE10 ACALL BOFANG ;音乐播放初始设置DOWNLIGHT:MOV DPTR,#TABLE1 ;将TABLE1首地址赋数据指针AJMP GETDATAUP:MOV 50H,#HIGH TABLE10 ;下到上MOV 51H,#LOW TABLE10 ACALL BOFANG ;音乐播放初始设置UPLIGHT:MOV DPTR,#TABLE2 ;将TABLE2首地址赋数据指针GETDATA:MOV R0,#08H MOV R6,DPH ;暂存指针值MOV R7,DPL LOOP:CLR A ;A清零MOV DPH,R6 MOV DPL,R7 MOVC A,A+DPTR ;表数据送A MOV P0,A ;将A值送P0端口INC DPTR ;数据指针加1,指向表中的下一数据MOV R6,DPH MOV R7,DPL JNB P1.2,START ;P1.2口低电平则转START程序执行JNB P1.3,STOP ;P1.3口低电平则转STOP程序执行JNB P1.4,DOWN ;P1.4口低电平则转DOWN执行JNB P1.5,UP ;P1.5口低电平则转UP左循环程序执行LJMP MUSIC ;跳转音乐程序BACK: DJNZ R0,LOOP CLR A ;判断是上还是下MOV DPH,R6 MOV DPL,R7 MOVC A,A+DPTR JNZ DOWNLIGHT LJMP UPLIGHT BOFANG:MOV TMOD,#11H ;音乐播放初始设置MOV IE,#82H MOV 40H,#00H RETMUSIC: MOV A,40H ;音乐播放处理MOV DPH,50H ;取表地址MOV DPL,51HMOVC A,A+DPTR ;将表数据送累加器A JZ STOP2 ;累加器A为0则转移(说明歌曲播放完得重新播放) MOV R1,A ANL A,#0FH RL A MOV R2,A MOV A,R1 SWAP A ANL A,#0FH JNZ SING CLR TR0 LJMP W1 SING : DEC A MOV 22H,A RL A MOV DPTR,#TABLE00 MOVC A,A+DPTR MOV TH0,A MOV 21H,A MOV A,22H RL A INC A MOVC A,A+DPTR MOV TL0,A MOV 20H,A SET B TR0 W1: LCALL DELAY INC 40H JNZ STOP1 ;A 不为0则转移LJMP BACK STOP1: CLR TR0 ;音符结束重新播放处理LJMP BACK STOP2: CLR TR0 ;整首歌曲播放结束处理MOV R2,#03H LCALL DELAY LCALL BOFANG LJMP BACK TABLE00: DW 64580,64684,64777,64820 DW 64898,64968,65030,64260 DW 64400,64524,65058,63835,64021 INT: PUSH PSW PUSH ACC MOV TH0,21HMOV TL0,20H CPL P3.5 POP ACC POP PSW RETI DELAY: MOV R4,#100 ;延时100ms LOOP3: MOV R5,#0FFH LOOP4: DJNZ R5,$ DJNZ R4,LOOP3 DJNZ R2,DELAY RET TABLE1:DB 0FEH,0FDH,0FBH,0F7H,0EFH,0DFH,0BFH,7FH,01H TABLE2:DB 7FH,0BFH,0DFH,0EFH,0F7H,0FBH,0FDH,0FEH,00H ;-------------------------------------------------------------------- TABLE10: DB 0d4H,84H,94H, 82H,92HDB 12H,22H,82H,92H,02H,92H,82H,0d2H DB 82H,92H,14H,84H,02H,0d1H,0d1H DB 0c2H,0d2H,84H,0d2H,0d2H,82H,82H DB 84H,82H,82H,94H,82H,0d2HDB 82H,82H,82H,92H,02H,82H,82H,0d2H DB 0c4H,84H,0d4H,92H,0d2H DB 82H ,0d2H,82H,92H,98H DB 04H,94H,88H DB 04H,94H,88H DB 04H,94H,88H D B 04H,94H,88H,04HDB 32H,32H,22H,12H,02H,92H,12H,92H DB 32H,32H,22H,12H,02H,92H,12H,92H DB 32H,32H,22H,12H,02H,92H,12H,22H DB 54H,44H,34H,12H,22HDB 34H,22H,12H,02H,92H,12H,92H DB 32H,32H,22H,12H,02H,92H,12H,92H DB 32H,32H,22H,12H,02H,92H,12H,22H DB 54H,44H,32H,22H,12H,92H DB 00HEND五.设计体会:历时2个星期的单片机课程设计,我从中受益匪浅。