Intel CPU架构解析2020

intel 核心代号

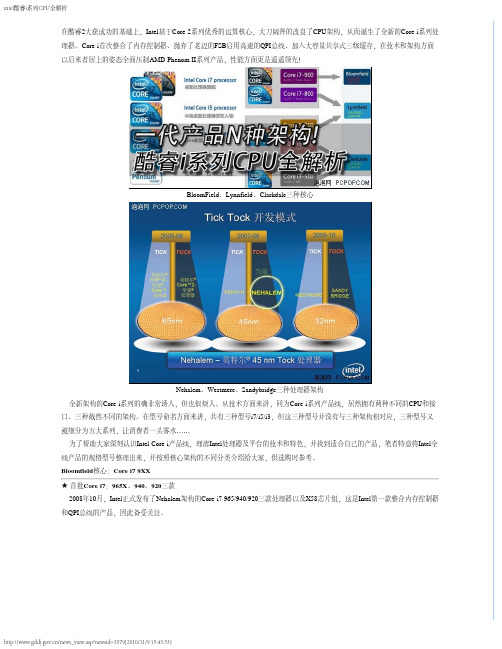

Intel处理器微架构和核心代号解析Bloomfield,Lynnfield,Clarkdale,SandyBridge一、Bloomfield核心:首次整合内存控制器Intel将新一代的SandyBridge处理器称作是第二代Core架构微处理器,因此在详细介绍SandyBridge处理器的核心架构之前,我们有必要对第一代Core 架构微处理器做一个详细的回顾,这样才能深入了解Intel近年来是如何改良处理器微架构的。

第一代Core架构微处理器分为三个版本:Bloomfield、Lynnfield、Clarkdale(六核心版的Gulftown与Bloomfield没有本质不同,因此不做介绍),这三颗CPU核心一颗比一颗的集成度高,下面我们就一一解读:回顾:Bloomfield核心首次整合内存控制器2008年10月,Intel正式发布了Nehalem架构的Core i7 965/940/920三款处理器以及X58芯片组,这是Intel第一款整合内存控制器和QPI总线的产品,因此备受关注。

i7 9XX系列处理器是基于Nehalem架构的首款产品,核心研发代号是Bloomfield,采用了45nm工艺制造,是原生四核心设计,集众多先进技术于一身:1. 超线程技术回归,四核八线程大幅提升CPU的多任务和多线程计算能力;2. 整合三通道DDR3内存控制器,带宽大幅提升、延迟大大下降,从此内存不再是瓶颈;3. QPI总线取代FSB总线,用以连接北桥芯片,Core 2架构最大的瓶颈被消除;4. 采用大容量共享式三级缓存设计,较少数据等待延迟,多核应用效率提升。

i7 9XX系列的主要特点:四核心、八线程、三通道、三级缓存★ Bloomfield核心Core i7 9XX系列CPU的特点总结:四核八线程、三通道内存还有可以支持多显卡互联的X58芯片组,这些就是Bloomfield核心Core i7 9XX系列CPU的主要特点。

CPU架构讲解 X86、ARM、RISC、MIPS

CPU架构讲解X86、ARM、RISC、MIPS一、当前CPU的主流架构:1.X86架构采用CISC指令集(复杂指令集计算机),程序的各条指令是按顺序串行执行的,每条指令中的各个操作也是按顺序串行执行的。

2.ARM架构是一个32位的精简指令集(RISC)架构。

3.RISC-V架构是基于精简指令集计算(RISC)原理建立的开放指令集架构。

4.MIPS架构是一种采取精简指令集(RISC)的处理器架构,可支持高级语言的优化执行。

CPU架构是CPU厂商给属于同一系列的CPU产品定的一个规范,是区分不同类型CPU的重要标示。

二、目前市面上的CPU分类主要分有两大阵营:1.intel、AMD为首的复杂指令集CPU;2.IBM、ARM为首的精简指令集CPU。

两个不同品牌的CPU,其产品的架构也不相同,例如,Intel、AMD的CPU是X86架构的,而IBM的CPU是PowerPC架构,ARM是ARM架构。

三、四大主流CPU架构详解(X86、ARM、RISC、MIPS)1.X86架构X86是微处理器执行的计算机语言指令集,指一个Intel通用计算机系列的标准编号缩写,也标识一套通用的计算机指令集合。

1978年6月8日,Intel 发布了新款16位微处理器8086,也同时开创了一个新时代:X86架构诞生了。

X86指令集是Intel为其第一块16位CPU(i8086)专门开发的,IBM 1981年推出的世界第一台PC机中的CPU–i8088(i8086简化版)使用的也是X86指令。

采用CISC(Complex Instruction Set Computer,复杂指令集计算机)架构。

与采用RISC不同的是,在CISC处理器中,程序的各条指令是按顺序串行执行的,每条指令中的各个操作也是按顺序串行执行的。

顺序执行的优点是控制简单,但计算机各部分的利用率不高,执行速度慢。

随着CPU技术的不断发展,Intel陆续研制出更新型的i80386、i80486直到今天的Pentium 4系列,但为了保证电脑能继续运行以往开发的各类应用程序以保护和继承丰富的软件资源,所以Intel所生产的所有CPU仍然继续使用X86指令集。

CPU的多核心架构及计算单元详解

CPU的多核心架构及计算单元详解中央处理器(CPU)是计算机系统中的核心组件之一,它承担着执行计算和控制操作的任务。

随着计算机的快速发展,人们对于性能的要求也越来越高。

为了满足用户对于多任务处理和高性能计算的需求,CPU的多核心架构逐渐兴起。

本文将详细介绍CPU的多核心架构以及其中的计算单元。

一、CPU的多核心架构1.1 多核心概念及发展多核心是指在一个CPU芯片上集成多个独立的处理器核心。

与传统的单核心CPU相比,多核心架构能够同时处理多个线程或任务,提升计算机的整体性能。

多核心架构的发展源于摩尔定律的进展。

根据摩尔定律,集成电路中的晶体管数量每18个月翻倍,这意味着CPU的计算能力也在同期间不断提升。

然而,到了一定程度,提升频率并不能显著增加CPU的性能,因为频率增加会导致功耗和发热的问题。

因此,为了进一步提升性能,多核心架构成为了解决方案。

1.2 多核心的优势多核心架构具有如下几个优势:1.2.1 提升系统性能:多核心能够同时处理多个任务或线程,有效提高了系统的整体性能。

特别是对于多线程应用程序或者同时执行多个任务的场景,多核心能够更好地满足用户需求。

1.2.2 节能降耗:与提升频率相比,多核心架构能更好地平衡性能和功耗。

通过将任务分配到多个核心上执行,每个核心的工作频率可以降低,从而减少功耗和发热,延长电池续航时间。

1.2.3 增强并行计算能力:多核心为并行计算提供了强大的支持。

对于需要大量计算的应用程序,多个核心可以同时进行计算,加速处理过程。

1.3 多核心架构的实现方式多核心架构的实现方式主要有对称多处理(SMP)和复杂指令集计算(CISC)。

对称多处理(SMP)是指每个核心拥有相同的访问权限和权力,可以独立运行不同的任务。

SMP架构中,每个核心可以共享同一份操作系统,从而实现大部分应用程序的并行执行。

复杂指令集计算(CISC)则是在一个CPU芯片上,集成多个核心以及专用的计算单元,每个计算单元负责执行特定类型的计算任务。

Intel系列CPU的流水线结构与性能分析

Intel系列CPU的流水线结构与性能分析流水线技术早在Intel的X86芯片中均得到了实现。

流水线的使用使CPU 的性能得到了很大的提升,而Pentium系列CPU产品更是一个高级的超标量处理器。

当然CPU流水线性能是有限制,影响CPU流水线性能的因素有:1、多个任务在同一时间周期内争用同一个流水段例如,假如在指令流水线中,如果数据和指令是放在同一个储存器中,并且访问接口也只有一个,那么,两条指令就会争用储存器;在一些算数流水线中,有些运算会同时访问一个运算部件。

2、数据依赖比如,A运算必须得到B运算的结果,但是,B运算还没有开始,A运算动作就必须等待,直到A运算完成,两次运算不能同时执行。

3、条件转移的影响如果第一条指令是一个条件转移指令,那么系统就会不清楚下面应该执行那一条指令。

这时就必须等第一条指令的判断结果出来才能执行第二条指令。

条件转移所造成的流水线停顿甚至比相关还要严重的多。

越是长的流水线,相关和转移两大问题也越严重,所以,流水线并不是越长越好,超标量也不是越多越好,找到一个速度与效率的平衡点才是最重要的。

为了解决这些影响流水线性能的因素和提高CPU性能,Intel公司采取了一系列技术手段。

在Pentium III的时候主要采用的技术1.采用超标量双流水线结构超标量流水线设计是Pentium微处理器技术的核心。

所谓超标量就是处理器内部含有多个执行单元来完成多条指令的同时执行。

Pentium有两条分别称为U和V的指令流水线,各自有独立的算术逻辑单元ALU及高速缓存结构。

这种双流水线并行作业的方式,使得Pentium在每个时钟周期内可同时执行两条指令。

此外,还有一个执行单元,保证同时完成一条浮点运算指令。

在Pentium III时采用3条独立的12级超标量流水线。

2.分支预测技术为了减少由于转移导致流水线的效率损失,Pentium采用分支预测技术来动态预测指令的目标地址,从而节省了CPU的执行时间。

IntelCorei系列年最受欢迎的CPU系列

IntelCorei系列年最受欢迎的CPU系列Intel Core i系列年最受欢迎的CPU系列在当今科技快速发展的时代,电脑已经成为人们生活中不可或缺的一部分。

而作为电脑的核心部件,处理器(CPU)的选择对于电脑的性能和使用体验至关重要。

在众多处理器品牌中,英特尔(Intel)的Core i系列无疑是最受欢迎的系列之一。

本文将介绍Intel Core i系列年最受欢迎的CPU系列,并以此为例,探讨其优势和受欢迎的原因。

1. 第一代Core i系列(Nehalem架构)首先我们来介绍第一代Core i系列处理器,采用了Nehalem架构。

从当时的技术水平来看,这一架构突破了传统处理器的设计,引入了Turbo Boost等技术,提高了处理器的性能和效能。

这一系列的处理器在推出之初便受到了广泛的关注和好评,以其出色的性能表现迅速赢得了电脑用户的青睐。

2. 第二代Core i系列(Sandy Bridge架构)随后,英特尔推出了第二代Core i系列处理器,采用了Sandy Bridge架构。

这一架构进一步提升了处理器的性能和能效,具备更好的图像处理和多媒体功能。

与此同时,英特尔还引入了集成显卡,使得该系列的处理器在游戏和图形设计方面表现出色。

这一系列的处理器成为了市场上的明星产品,备受消费者瞩目。

3. 第三代Core i系列(Ivy Bridge架构)第三代Core i系列处理器采用了Ivy Bridge架构,继续改进了处理器的性能和能效。

与上一代相比,Ivy Bridge架构融入了更先进的制程技术和3D晶体管,进一步提高了处理器的集成度和计算能力。

此外,该系列处理器还引入了更多的安全功能,以保护用户的个人数据。

Ivy Bridge架构的处理器因其卓越的表现以及出色的能效而成为市场上的热门选择。

4. 第四代Core i系列(Haswell架构)接着,英特尔推出了第四代Core i系列处理器,采用了Haswell架构。

4大主流CPU处理器技术架构分析

4大主流CPU处理器技术架构分析1.x86架构:x86架构是由英特尔和AMD共同推出的一种处理器架构。

它是32位和64位处理器的主流架构,广泛用于个人电脑和服务器。

x86架构采用复杂指令集计算机(CISC)的设计思想,通过提供大量的指令集,能够直接执行复杂的操作,从而提高性能。

不过,由于复杂的指令集和多级流水线设计,x86架构的处理器功耗较高,且难以优化。

2.ARM架构:ARM架构是一种低功耗架构,广泛用于移动设备和嵌入式系统。

它采用精简指令集计算机(RISC)的设计思想,通过简化指令集和流水线设计,减少了功耗和芯片面积。

ARM架构具有高效能和低功耗的优势,在移动设备上取得了巨大成功。

它还采用了模块化的设计,可以根据需求选择不同的组件来构建处理器。

3. Power架构:Power架构由IBM开发,广泛应用于大型服务器和超级计算机。

Power架构采用RISC设计思想,通过减少指令数量和复杂度,提高了性能和效率。

Power架构也支持多线程和多处理器技术,可以实现高度的并行计算。

Power架构的处理器主要被用于高性能计算场景,如大数据分析、科学计算等。

4.RISC-V架构:RISC-V架构是一个开源的指令集架构,于2024年由加州大学伯克利分校开发。

RISC-V架构采用RISC设计思想,通过精简指令集和模块化设计,提供了灵活性和可扩展性。

RISC-V架构的指令集规范是公开的,可以任意修改和扩展,使得硬件开发者可以根据需求进行定制。

RISC-V架构对于嵌入式系统和物联网设备具有较大的潜力,也得到了学术界和开源社区的广泛支持。

这四种主流的CPU处理器技术架构各有优势和应用场景,选择合适的架构需要根据具体需求和应用来决定。

无论是个人电脑、服务器还是移动设备,处理器架构的选择都直接影响着性能、功耗和功能扩展性。

随着技术的不断发展,未来的处理器架构可能会进行更多的创新和突破,满足日益增长的计算需求。

INTEL服务器CPU参数大全

INTEL服务器CPU参数大全英特尔(Intel)是全球知名的半导体公司,其服务器CPU产品系列广泛应用于各种大型数据中心和企业服务器。

服务器CPU是指专为服务器应用而设计的处理器,具有高性能、高可靠性和较低功耗的特点。

以下是一些英特尔服务器CPU的参数介绍:1.产品系列:英特尔服务器CPU家族包括至强(Xeon)系列和至强可扩展(Xeon Scalable)系列。

至强系列是英特尔最早的服务器处理器产品线,而至强可扩展系列则是最新和最先进的产品线。

2.架构:英特尔服务器CPU采用x86架构,这意味着它们能够运行广泛的操作系统和应用程序,包括Windows、Linux和UNIX等。

3.核心数量:英特尔服务器CPU的核心数量从4核到超过70核不等。

更多的核心意味着更高的并行处理能力和更好的多任务处理性能。

4.线程数量:英特尔服务器CPU支持超线程技术,即每个物理核心能够同时处理两个线程。

这意味着一个4核心CPU能够处理8个线程,提高了处理能力和多任务处理的效率。

5.时钟频率:英特尔服务器CPU的时钟频率通常在2GHz至3GHz之间,特定型号的CPU可能会更高。

时钟频率越高,处理器的计算能力越强。

6.缓存:英特尔服务器CPU具有多级缓存,包括L1缓存、L2缓存和L3缓存。

缓存的作用是存储CPU频繁访问的数据,提高数据读取和写入的速度。

7.内存支持:英特尔服务器CPU支持大容量的内存,通常支持DDR4内存技术。

更多的内存容量可以提供更高的数据处理能力和更好的应用性能。

8.功耗:英特尔服务器CPU的功耗因型号而异,通常在60瓦至200瓦之间。

较低的功耗可以减少服务器能耗和热量产生,降低运行成本和提高服务器稳定性。

9.扩展性:英特尔至强可扩展系列CPU具有更高的扩展性,可以支持多个CPU插槽和更多的内存插槽。

这使得服务器可以随着需求的增长而扩展处理能力。

10.安全性:英特尔服务器CPU内置了各种安全功能,包括硬件加密和虚拟化技术,以保护敏感数据和提高服务器安全性。

深入了解CPU架构Intel和AMD的差异

深入了解CPU架构Intel和AMD的差异在现代计算机技术中,中央处理器(CPU)是计算机最重要的组件之一。

而在CPU市场中,Intel和AMD是两家最著名的竞争对手。

虽然它们都生产处理器,但两者之间存在一些显著的差异。

本文将深入探讨Intel和AMD的CPU架构差异。

一、历史背景Intel是全球最大的半导体芯片制造商之一,成立于1968年。

自1981年推出第一款个人电脑处理器以来,Intel一直处于市场的主导地位。

而AMD(Advanced Micro Devices)成立于1969年,是一家总部位于美国的半导体公司,长期以来与Intel保持竞争关系。

二、架构设计1. Intel架构Intel CPU的架构通常采用x86架构。

x86是一个32位架构,它最早由英特尔公司在20世纪80年代初开发,现在已经发展到了64位,如今大多数个人电脑和服务器都采用了x86架构的Intel处理器。

Intel处理器的架构追求更高的时钟频率和性能。

其处理器核心数量有限,但每个核心的性能强大。

这使得Intel处理器在单线程任务上表现优异,并且适用于对时钟速度要求较高的应用,如游戏和CAD软件。

2. AMD架构AMD的处理器架构有所不同。

AMD推出的处理器主要采用x86-64架构,也称为AMD64架构。

这种架构是扩展版的x86架构,支持64位操作系统。

AMD处理器通常具有更多的处理器核心,因此在多任务处理和多线程应用方面表现出色。

这使得AMD处理器在处理多线程工作负载时比Intel处理器更具竞争力。

三、制造工艺CPU的制造工艺对其性能和功耗有直接影响。

制造工艺的进步可以带来更小、更高效的处理器。

1. Intel制造工艺Intel在制造工艺方面一直处于领先地位。

他们推出了14纳米、10纳米、7纳米等先进的刻线工艺,并且不断推出更小、更高效的芯片。

这使得Intel在功耗和效能方面具有优势。

2. AMD制造工艺AMD在制造工艺方面相对落后于Intel。

了解电脑CPU架构

了解电脑CPU架构电脑是现代社会必不可少的工具,而CPU作为电脑的核心部件,其架构直接影响计算机的性能和使用体验。

今天,我将带您深入了解电脑CPU架构,揭开其中的奥秘。

一、什么是CPU架构CPU,全称中央处理器,是计算机的核心之一。

它负责执行计算机程序的指令,并控制计算机的各项操作。

而CPU架构,指的是CPU的内部设计和组织方式,是决定CPU性能的重要因素。

二、常见的CPU架构类型1. X86架构X86架构是目前最广泛使用的CPU架构,它是英特尔公司在上世纪70年代推出的。

X86架构的代表有英特尔的酷睿系列和AMD的锐龙系列,其特点是性能强劲,广泛兼容各种软件。

2. ARM架构ARM架构是一种低功耗的CPU架构,主要应用于移动设备和嵌入式系统。

ARM架构的代表有高通的骁龙系列和苹果的A系列,其特点是能效高,性能稳定。

3. RISC架构RISC架构,全称精简指令集计算机(Reduced Instruction Set Computing),是指指令集简单、执行速度快的CPU架构。

RISC架构的代表有IBM的POWER系列,其特点是指令简洁高效。

4. CISC架构CISC架构,全称复杂指令集计算机(Complex Instruction Set Computing),是指指令集庞大、功能丰富的CPU架构。

CISC架构的代表有英特尔的x86系列,其特点是功能全面,支持复杂的指令。

三、CPU架构的影响因素1. 主频主频是CPU运行时的时钟频率,单位是赫兹(Hz)。

主频越高,CPU的计算能力越强,但同时也会产生更多的热量和电能消耗。

2. 核心数核心数指的是CPU内部的独立处理单元个数。

核心数越多,CPU 能够同时处理的任务越多,多核心的CPU在多线程应用和多任务处理上更有优势。

3. 缓存大小缓存是CPU内部的一块高速存储器,用于暂时存储数据和指令,以提高数据读取和处理效率。

缓存大小越大,CPU的运行速度越快。

最强CPU:六核Core i7 980X架构解析

Core i7 980X架构技术解析:规格概述不知道大家发现没有,Intel在推出新品的时候,有这样一个独特的管理。

凡是上一代曾经拿来当做卖点极力宣传的新技术,新特色,在下一代新品中,如没有特别说明,都会统统支持与涵盖。

Intel Core i7 980X的情况亦是如此,在上一代Intel Core i7 975X处理器中,对于超线程,睿频加速,集成总线控制器等特色,在新一代的Intel Core i7 980X均有支持。

因此,Intel也就不会在费唇舌极力宣传一次。

那么下面我们来重新领略一下Intel Core i7 980X的一些重要的技术特色。

这里我们可以得到确认,虽然处理核心数量和制造工艺技术有着极大的提升。

但是Intel Core i7 980X 所使用的芯片组依然是X58平台。

这不仅仅保护了用户的投资,也让主板厂商可以更简单的通过BIOS升级的方式来支持新的980X。

Core i7 980X架构技术解析:超频特色英特尔在最新的采用Nehalem架构的处理器中实现一种能够自动提高CPU的时钟频率的一种“正规超频”技术,英特尔将这项技术命名为“Intel Turbo Boost Technology“,翻译过来即为英特尔智能加速技术,同时Intel也给它起了一个更好听的名字,睿频技术。

英特尔智能加速技术是一个英特尔新一代的能效管理方案,与以前一味的降低主频以达到控制能耗的想法不同,Turbo Boost的主旨在于——在不超过总TDP的前提下,尽量挖掘CPU的性能潜力。

在英特尔Nehalem架构的处理器中,每个处理核心都带有自己的PLL同步逻辑单元,每个核心的时钟频率都是独立的,而且每个处理核心都是有自己单独的核心电压,这样的好处是在深度睡眠的时候,个别的处理核心几乎可以完全被关闭。

而在之前的多核心处理器中,所有的处理核心都具备相同的核心电压,也就是说着活跃的处理核心与不活跃的处理核心都要消耗相同的功耗。

Intel CPU详解

• The instruction decode queue, which holds instructions after they have been decoded, is no longer statically partitioned between the two threads that each core can service.

Haswell New Features

• Wider core: fourth ALU, third AGU, second branch prediction unit, deeper buffers, higher cache bandwidth, improved front-end and memory controller

single die inside the processor package. In contrast, Sandy Bridge's predecessor, Clarkdale, has two separate dies (one for GMCH, one for processor) within the processor package. This tighter integration reduces memory latency even more. • A 14- to 19-stage instruction pipeline, depending on the micro-operation cache hit or miss.

intel计算机cpu芯片的封装结构

intel计算机cpu芯片的封装结构Intel计算机CPU芯片的封装结构是指将芯片(chip)封装在外壳(package)中的一种技术。

这种封装结构有助于保护芯片、提供电气连接和散热功能,并使其可以在计算机系统中使用。

本文将详细介绍Intel CPU芯片的封装结构。

首先,让我们先了解一下CPU芯片的基本组成。

CPU芯片是计算机的核心部件,负责执行各种计算和处理任务。

在基于英特尔架构的计算机系统中,CPU芯片由逻辑电路、控制电路和存储单元等组成。

为了保护这些电路及其连接,以及为其提供电源和散热,需要对芯片进行封装。

CPU芯片通常由硅在单个晶片上制成。

为了防止物理损害和污染,芯片被封装在塑料或陶瓷外壳中。

外壳的材料选择取决于芯片的用途和散热需求。

Intel CPU芯片的封装结构可以分为以下几个部分:1.片基板(substrate):芯片的底层结构,由导电材料制成。

片基板的核心功能是提供电气连接和机械支撑。

芯片上的电路和引脚通过金属线连接到片基板上的针脚(pins)。

片基板还可以提供一些附加电路,如电压调节和电流监测。

2.外包装(package):外包装是芯片保护和连接的外壳。

它由塑料或陶瓷材料制成,具有机械强度和耐热性。

外包装呈方形或长方形,其大小和形状取决于具体的芯片型号。

外包装通常包含引脚或其他电气连接接口,用于将芯片连接到计算机主板或其他电气设备上。

3.封装球栅阵列(flip-chip ball grid array,FCBGA):FCBGA是一种常用的Intel CPU芯片封装结构。

在FCBGA中,芯片的底部(面片)与片基板上的针脚直接连接,而不是通过金属线连接。

这种直接连接可以提供更快的信号传输和更低的电阻。

底部的每个针脚都覆盖着一层导电球(solder ball),用于与主板上的连接点进行电气和机械连接。

4.热解膠(heat spreader):热解膠是安装在芯片顶部的金属层,用于散热。

了解CPU架构Intel和AMD的差异与选择

了解CPU架构Intel和AMD的差异与选择随着科技的不断发展,计算机的硬件也在不断进化,CPU作为计算机的核心组件之一,其架构对计算机的性能和功能起着至关重要的作用。

在众多的CPU品牌中,Intel和AMD是两个领先的厂商。

本文将探讨Intel和AMD在CPU架构上的差异,并帮助读者了解如何选择适合自己需求的CPU。

一、架构差异1. Intel架构Intel是全球最大的半导体公司之一,自1985年开始推出自家品牌的CPU以来,一直处于行业的领先地位。

目前,Intel的产品主要包括酷睿系列、至强系列等,其架构主要分为两种:a. x86架构(主流桌面和服务器)x86架构是Intel最为广泛采用的架构,适用于主流的桌面和服务器市场。

该架构具有高性能和完善的生态系统支持,可以运行大多数的操作系统和应用软件。

在桌面市场上,Intel的酷睿系列CPU性能强劲且功耗较低,是大多数用户的首选。

b. IA-64架构(企业级服务器)IA-64架构是Intel为面向企业级服务器市场推出的架构,专注于处理海量数据和高性能计算。

其特点是支持更高的内存容量和更复杂的指令集,适用于数据中心和科学计算等领域。

2. AMD架构AMD作为Intel的主要竞争对手,也在不断创新和提升自己的CPU 架构。

目前,AMD的产品主要包括锐龙系列和Epyc系列,其架构与Intel有所不同:a. x86架构与Intel类似,AMD的x86架构也是其主要采用的架构。

不同之处在于,AMD的锐龙系列CPU在性能上与Intel酷睿系列CPU相当,而且价格更具竞争力。

同时,AMD的锐龙系列还在多核性能方面表现出色,适合需要多任务处理能力的用户。

b. x86-64架构x86-64架构是AMD在x86架构基础上的扩展版本,也被称为AMD64。

该架构支持更大的内存寻址空间和更高的处理能力,使得处理器能够处理更为复杂的计算任务。

此外,x86-64架构还可以运行以前的32位应用程序,兼容性更好。

intel酷睿i系列CPU全解析

BloomField、Lynnfield、Clarkdale三种核心Nehalem、Westmere、Sandybridge三种处理器架构系列的确非常诱人,但也很烦人。

从技术方面来讲,同为Core i系列产品线,居然拥有两种不同的系列处理器是基于Nehalem架构的首款产品,核心研发代号是Bloomfield,采用了45nm工艺制造,是原生四核心设计,集众多先进技术于一身:i7 9XX系列的主要特点:四核心、八线程、三通道、三级缓存975X、960、950、930发布三月后,Intel改进制程,依然是45nm工艺但D0比C0体制更好、功耗发热更低、超频能力更强。

的i7 975X处理器,主流价位的i7 920也跟着沾光,D0制程的新版大受欢迎。

为了进一步细分产品线,不同倍频的型号相继上市,他们是960(3.2GHz,与965X相同但960锁倍频)、950(3.06GHz)、而南桥方面使用的依然是P45芯片组当中的ICH10R,通过DMI总线与北桥相连,基本功能相信大家都比较熟悉,就不再赘述Lynnfield核心示意图Bloomfield,在处理器内核部分几乎没有任何改动,同样是45nm工艺、原生四核心设计、支持超线程Lynnfield与Bloomfield的L1/L2/L3完全相同简化成双通道之后,Lynnfield的针脚数量和封装面积缩小不少Intel官方的这张示意图让很多人产生误解核心内部,除了整合了内存控制器外,Intel连PCI-E控制器也整合了进去(因此上图显卡直接与Lynnfield内部整合了QPI总线,但已被锁定,可以通过超外频提升Lynnfield内部还是整合了QPI总线的,虽然只有一条,这一条QPI总线用以连接CPU核心部分与是单芯片设计的芯片组,其本质上就是一颗南桥,功能和ICH10R没有太大区别,既不支持SATA3.0通道是落后的1.0版本。

要知道Lynnfield核心内部整合的PCI-E 2.0通道只有16条,只能满足单显卡或者双显卡Clarkdale核心处理器封装示意图CPU和GPU两个部分,CPU部分使用了新一代32nm工艺制造,是双核心四线程设计;Clarkdale的北桥(GPU)和CPU部分示意图部分是各自独立的,微观上通过QPI总线相连,宏观上被封装在了一起,接口是与Lynnfield透过这张架构图,就可以更清楚的认识Clarkdale的互联架构实际上它的这种架构与Core 2时代的G45没有本质区别,只不过G45的北桥(GPU)在主板上,而Clarkdale Clarkdale的内存控制器并没有被真正整合在CPU核心内部,而是在北桥当中,需要透过最大的区别就是能否支持FDI,其它南桥功能上的删减都是无关紧要的。

了解CPU架构Intel和AMD的差异与选择

了解CPU架构Intel和AMD的差异与选择CPU(中央处理器)作为计算机的核心组件,扮演着至关重要的角色。

在市场上有两个主要的CPU架构供应商,分别是Intel和AMD。

本文将就这两种CPU架构的差异和选择进行详细介绍。

一、CPU的基础知识CPU是计算机的"大脑",负责处理指令、执行计算任务等关键操作。

在了解Intel和AMD的差异之前,我们需要先了解CPU的一些基础知识。

1. 架构CPU的架构是指其内部组织和运作方式。

架构的不同会直接影响到CPU的性能和功能。

目前市场上主流的CPU架构有x86和ARM,而Intel和AMD是基于x86架构的。

2. 核心和线程CPU的核心是指其独立进行计算的处理单元。

线程是指CPU同时处理多个任务的能力。

核心和线程的数量会影响到CPU的并行处理能力和性能表现。

3. 频率CPU的频率(主频)决定了CPU每秒可以执行的指令数。

高频率一般意味着更快的计算速度,但并非频率越高性能就越好,还受架构、核心数量等因素的影响。

二、Intel和AMD的差异Intel和AMD是当前市场上最主要的CPU供应商,它们在架构、性能、价格等方面存在一些差异。

1. 架构差异Intel和AMD使用的是同一架构的x86,因此在兼容性上没有太大差异。

但两家公司对架构的实现方式和优化却存在差异,这直接影响到CPU的表现。

2. 性能差异Intel一直以来都是性能的代表,其CPU在单线程性能上表现出色,适合执行单个较重的任务。

而AMD则在多线程性能上具有一定优势,适合执行多个并行的任务。

3. 价格差异相对而言,AMD的CPU价格一般较低,而Intel的CPU则相对较高。

这也是为什么在预算有限的情况下,许多用户更倾向于选择AMD。

4. 功耗和发热由于架构和制程工艺的不同,Intel CPU的功耗和发热通常较高,而AMD的CPU相对较低。

在选择CPU时需要考虑到所使用计算机的散热性能。

主流CPU处理器技术架构详解

主流CPU处理器技术架构详解CPU(中央处理器)是计算机中最重要的组件之一,负责执行计算机的指令并控制计算机的各种操作。

随着计算机技术的不断发展,CPU的技术也在不断创新和进步。

下面详细介绍几种主流CPU处理器技术架构。

1.微处理器技术架构CISC架构采用复杂的指令集,每条指令能够完成多个操作,如数据处理、内存访问等。

CISC架构的优点是能够通过一条指令完成复杂的操作,但由于指令集复杂,导致指令执行周期长,性能相对较低。

典型的CISC架构有x86架构。

RISC架构采用精简的指令集,每条指令只能完成一个操作,但通过增加寄存器和优化流水线等技术,提高了指令执行速度和性能。

RISC架构的特点是指令精简、执行速度快,适用于对性能要求较高的应用。

典型的RISC架构有ARM架构。

2.多核处理器技术架构随着计算机应用的需求越来越高,单核处理器已经不能满足需求。

多核处理器技术配备了多个并行工作的核心,能够同时处理多个任务,提高计算机的执行效率和并发能力。

多核处理器技术有两种主流架构:对称多处理(Symmetric Multi-Processing,SMP)和异步多处理(Asymmetric Multi-Processing,AMP)。

SMP架构中,每个核心具有相同的权重和功能,可以共享相同的内存和外设。

它们可以同时运行多个任务,相互独立,但又可以进行通信和协同工作。

使用SMP架构的处理器可以在多个核心之间平衡负载,提高计算机的处理能力和效率。

AMP架构中,每个核心具有不同的权重和功能,可以同时处理不同类型的任务。

AMP架构的处理器可以根据不同的任务类型和需求进行灵活分配,提供更加优化的计算能力和资源利用率。

3.高性能计算技术架构高性能计算技术架构是为了满足大规模科学计算、高性能模拟和数据处理等需求而设计的处理器架构。

它采用了许多优化和特殊的技术,以提供更高的计算性能和吞吐量。

高性能计算技术架构有两种主流架构:向量处理器(Vector Processor)和并行处理器(Parallel Processor)。

了解电脑CPUIntel和AMD的区别与性能评估

了解电脑CPUIntel和AMD的区别与性能评估电脑CPU:Intel和AMD的区别与性能评估在当今数字化时代,电脑已经成为了我们生活中不可或缺的一部分。

而电脑的性能则主要由中央处理器(CPU)决定。

在市场上,Intel和AMD是最主要的两个CPU制造商。

那么,下面我们将详细了解一下Intel和AMD的区别,并对它们的性能进行评估。

一、架构差异1. Intel架构Intel的架构主要以x86架构为主,这是一种经过多年发展的指令集架构。

x86架构较为成熟和稳定,已经被广泛应用于个人电脑领域。

此外,Intel还陆续推出了i3、i5、i7、i9等多个系列的处理器,针对不同的用户需求提供了多样化的选择。

2. AMD架构相较于Intel,AMD采用的是x86架构的改进版x86-64架构。

这种架构引入了更宽的数据通路和高速缓存,提升了处理能力。

与此同时,AMD处理器还支持AMD超线程技术,使得处理器可以同时处理更多的线程,提高了多任务处理的效率。

二、性能比较1. 单核性能在单核性能方面,Intel处理器通常更强大。

由于其架构的优势以及对指令集的精细优化,Intel处理器在单个核心上的运算性能更出色。

这使得Intel的处理器在单线程任务上表现优秀,特别适合一些对单核性能要求较高的应用场景。

2. 多核性能AMD处理器在多核性能上往往比Intel更具优势。

AMD的处理器往往拥有更多的物理核心,尤其是针对同价位级别的产品,AMD通常提供更多的核心数量。

这使得AMD处理器在多线程任务上表现出色,适合一些需要大量并发计算的场景,比如视频编辑和3D渲染等。

3. 整体性能针对整体性能的评估,需要综合考虑单核性能和多核性能的表现。

在同价位级别的处理器对比中,Intel的处理器往往在单核性能上稍占优势,而AMD处理器由于更多的物理核心优势,在多核性能上表现更突出。

因此,在不同的应用场景中,选择适合的CPU需要根据具体需求来进行。

CPU处理器架构之争系列(一):英特尔经典x86架构

CPU处理器架构之争系列(一):英特尔经典x86架构展开全文在集成电路的发展历程中,有一家公司必须被提及,那就是英特尔。

不论是其创始人诺伊斯发明了可工业化生产硅芯片的平面工艺技术,还是后来在微处理器领域引领全球数十年,英特尔在集成电路领域的成就都是令人敬重的。

Intelx86架构起源1971年英特尔发明了微处理4004,由此开启了微处理器快速发展的浪潮。

1978年,英特尔推出了首款基于x86架构的16位处理器8086 CPU。

当时英特尔与IBM合作,推出基于8086处理器的PC,在市场上获得巨大成功,这也使x86迅速发展成为PC标准平台。

早年采用x86架构的企业其实也有数家,但最后就剩AMD能够与英特尔竞争,这其中关键竞争要素不仅在芯片设计技术上,还在于领先的工艺技术。

x86架构采用CISC架构,需要向前兼容x86架构采用可变指令长度的复杂指令集(Complex Instruciton Set Computer,CISC)架构。

与精简指令集(Reduced Instruciton Set Computer,RISC)相比,CISC执行效率更低。

另外x86架构有一个重要特点就是向前兼容。

每次架构的升级一定程度上帮助英特尔建立了更高的生态壁垒,但同时这也是困扰x86架构速度提升的一个历史包袱。

为了顾全兼容性和高性能,Intel推出的x86的新架构,把x86指令转换成类似RISC的微指令,然后再执行,以此获得和RISC相当的性能,同时仍然能够前向兼容。

英特尔于1985年推出了基于32位的80386 CPU,扩展了x86架构的位数,提升了CPU的性能。

而后在32位处理器向64位处理器转移的过程中,英特尔也想尝试放弃前向兼容,采用新架构,和RISC 的ARM硬拼。

但是失败了,因为已有的软件生态不支持这样的新架构。

与此同时,老对手AMD在继承32位x86架构基础上,率先推出了64位的x86架构处理器。

并于微软操作系统形成良好互动,英特尔只能放弃原来自己的新架构,采用AMD的64位架构进行扩展。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Sunny Cove内核结构图

Sunny Cove内核微架构

缓冲区部分对比

缓存对比

可以看到Intel这次把乱序重排缓冲区(ReOrder Buffer,主要是用于乱 序执行后将执行的微指令根据原本顺序提交的指令缓冲区)大小做到 了可以容纳352条微指令,直接提升了128条/57%之多,而Haswell到 Skylake才仅仅提升了32条。同样在访存上面也进行了不小的提升, Load(加载)队列增加了56,Store(存储)队列增加了16,比Haswell 到Skylake的改变都明显要多。

Uncore部分

当 然 也 不 是 所 有 的 厂 商 都 会 给 足 四 个 TB3 接 口 , 具 体 怎 么 配 置 还 是 得 看 OEM厂商,毕竟其他的配套芯片诸如USB PD所需要的独立IC都是会增加成 本 的 , 而 TB 接 口 还 需 要 额 外 的 Retimer 芯 片 , 不 过 Intel 已 经 减 半 了 所 需 的 Retimer,两条TB3只需要1个Retimer就可以了。

Thunderblot 3

原来阻挡人们使用Thunderblot(以下简称TB)设备的一大原因就是这个接口的 使用成本略高,当TB3开始以USB Type-C接口的形式出现之后,使用率确实高上 去不少,但是还有其他的拦路虎,其中一个就是TB需要主板搭载额外的芯片来使 用,这个控制芯片并不便宜。终于在Ice Lake上面,Intel把TB控制器整合到了 处理器里面,并且再也不会占据掉处理器提供的PCI-E总线数量或者是与PCH一起 挤原本就已经拥挤不堪的DMI 3.0总线,而是在环形总线上面拥有了自己的位置 。

第11代图形架构新Fra bibliotek口版本和加强的硬件编码电路

在视频硬件编码部分,也就是Intel QuickSync特性使用的独立硬 件电路上,新核显也有比较大的改进,现在支持两条HEVC 10-bit 同时进行编码,在YUV444的情况下最高支持两条4K60帧视频流, 或者一条YUV422的8K30帧视频流。

Uncore部分

不过将TB控制器集成到CPU内部也使得整个 System Agent的IO部分更为复杂了,上面是 一张详细的原理图,一个Type-CIO路由(图 上名为CIO Router)拥有两条PCI-E 3.0 x4与CPU相连,而CPU内部的显示控制引擎( 图上的Display Engine)也要与这个TypeCIO路由相连,以控制Type-C接口所处的状 态,并决定发送的信号。同时还有USB的 xHCI也要跟Type-CIO连接,还要管理整个的 内存统一性……

复杂的结构所导致的就是整体的延迟会增加 ,Intel将原因归结在电源控制上面,原本 分离式的芯片很容易管理电源状态,但是整 合进来之后每一个部分都有自己的电源状态 需要管理,需要更为精细化的电源管理系统 ,而这就增加了总体的延迟。不过更为精细 化的电源管理还是有好处的,那就是可以提 高能耗效率,Intel方面称满载的一个TB3接 口的芯片外加链路层将使用300mW的功率, 四个加起来也只有1.2W。

3200/LPDDR4X 3733内存,原

来Skylake上面的内存控制器

顶多只能支持到DDR4 2666,

还是八代的Coffee Lake以后

的事情了。而随着DDR4内存的

发展,默频上3000的内存条也

开始出现了,内存控制器直接

支持到DDR4 3200是一件不错

的事情。而且随着处理器内核

数量的增加,内存带宽也逐渐

第11代图形架构

内部架构优化

首先通过增加单个Slice中含有的子Slice来 扩大规模,使得每周期的计算次数增加。其 次是在缓存系统上做文章,扩大了三级缓存 的容量,Intel方面公布的是EU的三级缓存 有3MB,并且还有0.5MB的本地共享内存。另 外还有通过处理器的内存控制器升级,能够 用上更高的内存带宽。

你一定想问第10代去哪里了对不对,其实还是在夭折了的 Cannon Lake上面,而且唯一一颗的核显还是被屏蔽了的 。目前在移动低压版Ice Lake处理器上面,Intel一共提 供了G1、G4和G7三种配置的核显,分别有32/48/64组EU, 低端的G1命名仍为"UHD",而G4和G7都以"Iris Plus"的品 牌出现。

04.

UNCORE部分

Uncore部分

Uncore部分指的是处理器上除了内核和GPU的其他部分,在顶上的结构示意图中 就是System Agent的那部分,自从Intel在Nehalem把内存控制器和PCI-E控制器移 入CPU内部之后就没有什么大的变化,但是这次Intel在上面加入了个新东西,还 升级了不少老部件。

CPU架构解析

总经理办公室-IT组-王旭

目录Catalog

1 Intel CPU架构介绍

3 图形架构解析 5 PCH改进

2 CPU架构解析 4 UNCORE部分 6 封装、睿频与功耗

01.

Intel CPU架构介绍

Intel Sunny Cove架构介绍

继上一次Intel更新他们的桌面级处理器的架构已经过去了将近6年的时间了,不 得不说,Skylake是一代非常成功的架构,也可能是从P6以来Intel使用时间最长的 一代处理器架构,支撑Intel走到现在还在主流和服务器市场上面占据着上风。 首先我们要理清一点,Ice Lake是整个处理器架构的代号,而现在的Intel处理器架 构中包括了内核、GPU、以及Uncore部分的其他IO单元,所以我们并不只是针对 CPU的内核微架构进行解析,而是对于整个体系结构。

03.

图形架构解析

第11代图形架构

Ice Lake的核显首次达到了 1TFlops的计算性能,还增加 了不少的功能特性,可谓改进 颇多。Intel用了"the most powerful version"来形容这代 核显的性能,怎么做到的呢?

第11代图形架构

借助10nm工艺,暴力堆叠规模

Intel的10nm工艺在晶体管密度上 的提升幅度是真的很大,14nm时 代最多配备24组EU的核显,在Ice Lake上面直接就翻了2.67倍,最 大可以达到64组EU,并且频率也 不低,最高可以跑到1100MHz,比 以前只低了50MHz,此时核显整体 的FP32计算量已经达到了 1.15TFlops。鉴于此,相比于八 代酷睿处理器上搭载的第9代核显 ,Intel官方宣称可以提供平均约 1.8倍的帧率。

可变速率着色(VRS) VRS全称Variable Rate Shading,是一种新的允许GPU根据画面 区域的重要性调整着色精度的技术,具体效果我们之前的新闻有 介绍过,可以看一下:来对比一下VRS可变速率着色技术带来的性 能提升吧 3DMark将添加该技术基准测试一文中的图片对比。

第11代图形架构

指令集与AI加速

指令集随着新单元的加入也同时进行了扩充,在加密解密、AI加速、通用计算 、特定计算等方面都新加入了不少指令,尤其是AVX-512指令集。 对于近几年大热门的人工智能,Intel一方面在Uncore部分加入了自家的“高斯网 络加速器(Gaussian Network Accelerator)”这样类似于手机SoC上面常见的AI硬 件加速电路,还通过引入AVX512VNNI指令集,使用AVX-512单元来进行AI相关的 加速计算,Intel将这种加速称为"DL(Deep Learning) Boost"。这是一种很聪明的取 巧办法,专用计算单元的引入可以保证一定的加速性能,而新指令集的加入同 时也可以更加充分地利用上新的CPU特性。 加密解密指令集上面的改动诸如AES的吞吐量加大、加入新的针对SHA算法的一 系列指令等,总之在编译器进行适当优化的前提下,Ice Lake的加密解密性能是 比Skylake强不少的。

值得一提的是,Intel已经做好了对于USB4的兼容,不过考虑到目 前USB4仍处于草案阶段,不排除未来的修改使得兼容失效。不过 目前只是针对Ice Lake的移动版本进行架构分析,当然也不排除 Intel在桌面级的Ice Lake上面同样保留内部TB控制器。

内存控制器

现在内存控制器原生支持DDR4

要开始成为处理器性能的一个

瓶颈所在了,在我们的测试中

,内存带宽对于性能的影响还 前面在讲内核的AI加速时提到了Uncore部分加入了

是比较明显的。

GNA这个针对AI的硬件加速单元,目前并不知道太多有

关于它的细节,就连具体名字都有两种说法,目前已

知的是该单元的功耗非常低,甚至会在SoC其余部分关

闭的情况下继续工作,旨在提供稳定的AI加速性能,应

Uncore部分

而且Intel大方的一下子就 提 供 了 4 个 之 多 的 TB3 接 口,每个都是PCI-E 3.0 x4 的 满 规 格 , 也 就 是 说 ,Ice Lake处理器其实一 共拥有32条PCI-E 3.0通道 ,不过其中一半都是以 TB3形式提供的,当然这 些接口是支持USB模式的 ,当运行于USB 2.0状态 时,会绕回到PCH上进行 通信。

可变速率着色(VRS)

VRS可以在不重要的画面上面节 约一定的GPU资源,使这部分 GPU资源参与更加重要的部分画 面的渲染中,从而提高了整体的 帧数,目前NVIDIA已经在Turing 核心中加入了相关的支持。而 Intel也没有落后,在第11代核显 中提供了这项特性,并且他们宣 布将与Epic合作,将这项特性加 入到虚幻引擎中去,目前文明六 已经支持了该技术,并且根据 Intel的数据,帧数最大提高了 30%。

Ice Lake处理器结构图

02.

CPU架构解析

Sunny Cove内核微架构:IPC平均提升18%

前端缓冲区:加大加大加大 x86处理器的内核主要可以简单地分成两 个部分,前端部分与后端执行部分,前端 部分主要完成“取指译码”的工作,后端 主要为指令的具体执行单元,前后端之间 有缓冲区,用于存放解译融合完毕的微指 令。Intel很早就在内核中引入了“微指令 融合”的技术来提高效率,融合过的微指 令会进入缓冲区然后被分配给后端执行部 分进行具体的执行。Intel目前认为,如今 程序更多的瓶颈位于访存和前端指令分派 上,Sunny Cove的前端部分改进就体现了 这一理念,所以这次缓冲区就被扩大了不 少。