SDXC卡协议整理学习笔记

实验一--摄像机基本操作

实验报告封面课程名称:班级:实验日期:姓名:学号:指导教师:实验名称:实验成绩:实验一摄像机基本操作一、实验目的1.了解摄像机使用的注意事项。

2.了解摄像机的基本结构与组成。

3.掌握摄像机的操作规程、调整与操作方法。

4.了解三脚架的结构与操作方法。

5.熟练掌握肩扛执机与固定执机方式。

二、实验设备和仪器索尼专业级数字摄录一体机(HXR-MC1500C)、配用电池、三角架。

三、实验内容及要求1.实验内容:(1)摄像机使用的注意事项。

(2)摄像机的构成,各功能按钮的功能与使用。

(3)摄像机的操作步骤。

(4)摄像机的执机方式。

2.实验要求:本次实验分组进行;每组成员4人。

四、实验原理及步骤1.实验原理学习电视摄像,首先要从学技术开始,即要学会如何操作摄像机,包括专业数字摄像机、家用机等。

摄像机是精密的电子仪器设备,在使用的过程中,要按照一定的规程和步骤进行使用,要注意一些使用事项,要了解摄像机的结构,以正确的姿势和操作步骤使用摄像机进行电视画面的拍摄。

2.步骤(1)介绍摄像机使用的注意事项。

(2)参照实验指导书和教师实验教案要求,熟悉专业摄像机的构成、开关按钮,了解其功用及使用方法。

(3)摄像机的操作、调整步骤与方法。

安装电池及正确开机。

摄像机的菜单及设置方法。

(部分项目的调整)设置手动或自动操作模式。

(看懂寻像器中的提示信息)调整白平衡的方法。

使用调焦环进行精确聚焦。

(认识景深)认识电子快门。

认识光圈。

进行拍摄并录制。

使用摄像机对录制的内容进行回放观看。

(4)熟悉三脚架的结构与操作方法。

(5)肩扛执机方式,掌握执机要领。

(6)练习固定执机方式,掌握执机要领。

五、使用注意事项1.摄像机是精密贵重的设备,请在使用前认真学习摄像机的使用注意事项。

2.摄像机及其附件设备,如果不会使用或者没学好,都不能乱动,需要在老师的指导下使用。

3.在老师演示讲解的过程中,需要适当地做笔记。

4.如实验机时不够,学生可与实验室联系,利用开放机时完成实验。

(完整版)SD卡协议-中文

(完整版)SD卡协议-中文一概述1. SD总线模式下CLK:时钟信号CMD:双向命令和响应信号DAT0-3:双向数据信号VDD,VSS:电源和地信号SD模式下允许有一个主机, 多个从机(即多个卡), 主机可以给从机分别地址. 主机发命令有些命令是发送给指定的从机,有些命令可以以广播形式发送.SD模式下可以选择总线宽度, 即选用几根DAT信号线, 可以在主机初始化后设置.2. SD总线协议SD模式下的命令和数据流都有一个开始位和结束位.>命令: 是在CMD上传输的用于启动一个操作的比特流. 由主机发往从机, 可以是点对点也可以是广播的.>响应: 是在CMD上传输的用于之前命令回答的比特流. 由从机发往主机.>数据: 是在DAT上传输的比特流, 双向传输.无响应模式无数据模式多块读操作模式多块写操作模式命令格式响应格式数据格式SD卡上电后会自动初始化,通过给卡发送CMD0也可以复位卡.二.SD卡命令描述.1.广播命令:给所有卡都发送, 某些命令需要响应.2.点对点命令给指定地址的卡发送, 需要响应.SD卡系统有两种工作模式:1.卡识别模式.主机上电复位后即处于此模式,它会在总线上等待卡. 卡复位后也处于此模式, 直到SEND_RCA(CMD3)命令到来.2.数据传输模式.卡收到SEND_RCA(CMD3)命令后即进入此模式. 主机识别到卡后也进入此模式.卡状态和工作模式对照表1.卡识别模式.此模式下主机复位总线所有的卡, 验证工作电压, 询问卡的地址. 这个模式下所有数据的传输都是只通过CMD线来完成.1)卡的复位.当卡上电或收到GO_IDLE_STATE (CMD0)命令后, 卡即进入Idle State状态. 此时卡将其RCA设为0, 相关寄存器设为传输稳定的最优模式.2)工作电压验证每个卡的最高和最低工作电压存储在OCR. 只有当电压比配时, CID和CSD的数据才能正常传输给主机.SD_SEND_OP_COND (ACMD41)命令用来判断卡的工作电压是否符合, 如果不符合的话, 卡应该放弃总线操作, 进入Inactive State状态. 在发送SD_SEND_OP_COND (ACMD41)命令前记得要首先发送APP_CMD (CMD55).卡的状态变换图.ACMD41命令响应中的BUSY位也用于卡表示其还没准备好, 主机此时应重发ACMD41命令,直到卡准备好.主机在这个阶段的ACMD41中不允许改变工作电压, 如果确实想改变的话, 应该先发送CMD0, 然后再发送改变后的ACMD41.GO_INACTIVE_STATE (CMD15)命令用于使指定地址的卡进入Inactive State模式.3)卡识别过程.ALL_SEND_CID (CMD2)命令用于获取卡的CID信息, 如果卡处于Ready State, 它就会在CMD线上传送它的CID信息, 然后进入Identification State模式. 紧接着发送CMD3 (SEND_RELATIVE_ADDR)命令, 用于设置卡新的地址. 卡收到新的地址后进入Stand-by State 模式.2.数据传输模式.数据传输模式下卡的状态转变图进入数据传输模式后, 主机先不停的发送SEND_CSD (CMD9)命令获取卡的CSD信息. SET_DSR (CMD4)用于设置卡的DSR寄存器, 包括数据总线宽度, 总线上卡的数目, 总线频率, 当设置成功后, 卡的工作频率也随之改变. 此步操作是可选的.CMD7命令用于使指定地址的卡进入传输模式, 任何指定时刻只能有一个卡处于传输模式.传输模式下所有的数据传输都是点对点的, 并且所有有地址的命令都需要有响应..所有读命令都可以由CMD12命令停止,之后卡进入Transfer State. 读命令包括单块读(CMD17), 多块读(CMD18), 发送写保护(CMD30), 发送scr(ACMD51)和读模式一般命令(CMD56)..所有写命令都可以由CMD12命令停止. 写命令包括单块读(CMD24), 多块读(CMD25), 写CID(CMD26), 写CSD(CMD27),锁和解锁命令(CMD42)和写模式一般命令(CMD56)..当写命令传输完成后, 卡进入Programming State(传输成功)或Transfer State(传输失败).如果一个卡写操作被停止,但其前面数据的CRC和块长度正确, 数据还是会被写入..卡要提供写缓冲, 如果写缓冲已满并且卡处于Programming State, DAT0保持低BUSY. .写CID,CSD, 写保护, 擦除命令没有缓冲, 当这些命令没完时, 不应发送其他的数据传输命令..参数设置命令在卡被编程时是不允许发送的, 这些命令包括设置块长度(CMD16), 擦除块起始(CMD32)和擦除块结束(CMD33)..当卡正编程时读命令是禁止的..用CMD7使另一个卡进入Transfer State不会终止当前卡的编程和擦除, 当前卡会进入Disconnect State并且释放DAT线.. Disconnect State模式的卡可通过CMD7重新被选中,此时卡进入Programming State 并且使能busy信号.. CMD0或CMD15会终止卡的编程操作, 造成数据混乱, 此操作应禁止.1)总线宽度选择命令ACMD6命令用于选择总线宽度, 此命令只有在Transfer State有效. 应在CMD7命令后使用.2)块读命令块是数据传输的最小单位, 在CSD (READ_BL_LEN)中定义, SD卡为固定的512B.每个块传输的后面都跟着一个CRC校验. CMD17(READ_SINGLE_BLOCK)用于传输单个块,传输完之后,卡进入Transfer State. CMD18 (READ_MULTIPLE_BLOCK)用于多个块的传输,直到收到一个CMD12命令.3)块写命令与块读命令类似, 每个块传输的后面都跟着一个CRC校验.卡写数据时会进行CRC校验.多块写比重复的单块写更能提高效率.如果CSD中的WRITE_BLK_MISALIGN没设置, 并且发送的数据不是块对齐的, 卡会设置状态寄存器中的ADDRESS_ERROR位,并且进入Receive-data-State状态等待停止命令.此时写操作也会停止, 并且卡会设置其的WP_VIOLATION位.如果写缓冲满的话, 卡会停止接受WRITE_BLOCK命令. 此时主机应发送SEND_STATUS (CMD13)命令, 卡返回数据的READY_FOR_DATA位标志卡是否准备好接受新的数据.在多块写操作中通过事先发送ACMD23命令可提高写速度. ACMD23用于定义接下来要写数据的块的数目. 每次多块写操作后, 这个值又被设为默认的1.ACMD22会使卡返回写成功的块数目.4)擦除命令擦除命令的顺序是: ERASE_WR_BLK_START(CMD32),ERASE_WR_BLK_END(CMD33)an d ERASE (CMD38).如果(CMD38或(CMD32, 33)接收到出错信息, 卡会设置状态寄存器中的ERASE_SEQ_ERROR 位并且重新等待新的命令时序.如果接收到时序错误命令, 卡会设置其ERASE_RESET位并且重新等待新的命令时序.5)写保护管理三种机制:-.写保护物理开关-.卡内部写保护通过设置CSD中的WP_GRP_ENABLE位和WP_GRP_SIZE位, SET_WRITE_PROT和CLR_WRITE_PROT命令用来设置和清除保护机制.-. 密码保护.三. 时钟控制如果主机要发送1K的数据, 但是主机缓冲区只有512B, 那么主机可以在发送完前512B 后, 可以先停止时钟, 然后把后512B填充入缓冲区, 再启动时钟, 这样卡并不会检测要两次发送之间的间隔, 认为其是一次完整的数据发送过程.四 CRC校验1.CRC7CRC7用于所有的命令, 除R3以外的响应, 以及CID和CSD寄存器.2.CRC16CRC16用于数据块的校验五. 错误类型.1. CRC错误和命令非法错误命令的CRC校验出错, 卡设置其状态寄存器的COM_CRC_ERROR 位.非法命令错误, 卡设置其状态寄存器的ILLEGAL_COMMAND位.非法命令包括:不支持的命令,未定义的命令以及当前状态不支持的命令.2. 读,写和擦除超时.卡应该在指定的时间内完成一个命令或返回移动的错误信息. 如果在指定的超时时间内主机收不到响应, 应认为卡停止工作, 应重新复位卡.六命令1. 命令类型:- bc不需要响应的广播命令.- bcr需要响应的广播命令. 每个卡都会独立的接收命令和发送响应.- ac点对点命令, DAT线上没数据- adtc点对点命令, DAT线上有数据所有命令均遵守上图中的格式, 总共48位. 首先是1个起始位0,接着是1个方向位(主机发送位1), 6个命令位( 0-63 ), 32位参数(有些命令需要), CRC7位校验, 1个停止位.2.卡命令根据不同的类型分成了不同的Class, 见下表,其中Class0,2,4,5,8是每个卡都必须支持的命令, 不同的卡所支持的命令保存在CSD中.3.命令详细描述1)基本命令Class02)读命令Class23)写命令Class43)擦除命令Class54)应用特定命令Class8下表中的所有命令使用前都应先跟一个APP_CMD(CMD55)命令七. 卡状态转换表八. 应答.所有的应答都是通过CMD发送,不同的应答长度可能不同.总共有四种类型的应答.1. R1: 长度位48位.注意每个块传输完成后有一个BUSY位.2.R1b:与R1类似, 只是将BUSY位加入响应中.3.R2(CID CSD寄存器) : 长度为136位, CID为CMD2和CMD10的应答, CSD为CMD9的应答.4.R3(OCR寄存器):长度位48位. 作为ACMD41的应答.5.R6(RCA地址应答):长度为48位九. 卡的状态SD卡支持两种状态:-卡状态:与MMC卡兼容.-SD卡状态:扩充到了512位.1.卡状态:R1应答包含一个32位的卡状态.见下表.其中Type中的含义为:E:错误位. S:状态位. R:根据命令在响应中设置.X:根据在命令执行期间设置, 必须再次读此位才能获得命令执行后的情况.Clear Condition:A: 与卡的当前状态有关B: 总是与命令有关,无效的命令会清除此位.C: 通过读此位来清除下表指明了哪些命令可能使哪些位产生变化2.SD卡状态:这些位通过DAT线传输, 并伴有CRC16校验. 其是作为ACMD13的应答.十. 卡存储器形式.-块:块是基本读写命令的单位,它可以是固定的或可变的. 关于块的大小以及其是否可变性存储在CSD中.-扇区:扇区是擦除命令的单位, 它是固定的值,保存在CSD中.十一. 时序图时序图中字母含义:1.命令和应答1)卡识别和卡工作电压确认模式:CMD2,ACMD412)地址分配模式:CMD33)数据传输模式:4)命令结束->下一个命令:5)两个命令直接1)单块读:CMD172)多块读:读过程时序.停止命令时序3.数据写1)单块写:注意Busy信号.2)多块写:多块写命令时序停止命令时序卡主动停止时的时序。

sd卡总线协议

编号:_______________本资料为word版本,可以直接编辑和打印,感谢您的下载sd卡总线协议甲方:___________________乙方:___________________日期:___________________sd卡总线协议篇一:sd卡接口的完整规范sd卡接口规范的完整翻译特性:◎容虽:32mb/64mb/128mb/256mb/512mb/1gbyte ◎兼容规范版本1.01 ◎卡上错误校正◎支持cpRm◎两个可选的通信协议:sd模式和spi模式◎可变时钟频率0— 25mh应通信电压范围:2.0-3.6V 工作电压范围:2.0-3.6V◎低电压消耗:自动断电及自动睡醒,智能电源管理◎ 无需额外编程电压◎卡片带电插拔保护◎正向兼容mmc^◎高速串行接口带随即存取----- 支持双通道闪存交叉存取----- 快写技术:一个低成本的方案,能够超高速闪存访问和高可靠数据存储---- 最大读写速率:10mbyte/s◎最大10个堆叠的卡(20mhz,Vcc=2.7-3.6V) ◎数据寿命:10万次编程/擦除◎ ce和Fcc认证◎ pip封装技术◎尺寸:24mm® x 32mn#x 1.44mm厚说明:本sd卡高度集成闪存,具备串行和随机存取能力。

可以通过专用优化速度的串行接口访问,数据传输可靠。

接口允许几个卡垛叠,通过他们的外部连接。

接口完全符合最新的消费者标准,叫做sd卡系统标准,由sd卡系统规范定义。

sd卡系统是一个新的大容虽存储系统,基于半导体技术的变革。

它的出现,提供了一个便宜的、结实的卡片式的存储媒介,为了消费多媒体应用。

sd 卡可以设计出便宜的播放器和驱动器而没有可移动的部分。

一个低耗电和广供电电压的可以满足移动电话、电池应用比如音乐播放器、个人管理器、掌上电脑、电子书、电子白科全书、电子词典等等。

使用非常有效的数据压缩比如mpeg, sd卡可以提供足够的容虽来应付多媒体数据。

中国移动WLAN业务PORTAL协议规范V2.0.0

中国移动通信企业标准 QB-D-026-2008 中国移动W L A N 业务P O R T A L 协议规范 版本号:2.0.0 中国移动通信有限公司 发布2008-4-2发布 2008-4-2实施 C M C C W L A N S e r v i c e P o r t a l S p e c i f i c a t i o n目录1. 范围 (1)2. 规范性引用文件 (1)3. 术语、定义和缩略语 (2)4. Portal协议 (2)4.1. WLAN用户类型及用户标识定义 (2)4.1.1. WLAN用户类型 (2)4.1.2. 用户标识定义 (3)4.2. 功能定义 (3)4.2.1. 认证功能 (3)4.2.2. 下线功能 (4)4.2.3. 自服务功能 (4)4.3. 系统结构 (4)5. 流程 (5)5.1. 用户上线认证流程 (5)5.2. 用户下线流程 (8)5.3. 动态密码申请流程 (9)5.4. 管理员配置个性化页面流程 (9)5.5. 用户自服务功能流程 (10)5.5.1. 静态密码修改流程 (10)5.5.2. 预付费卡用户帐户转帐流程 (12)5.5.3. 套餐信息查询流程 (13)5.5.4. 历史使用记录查询流程 (14)6. 协议 (14)6.1. 协议栈 (14)6.2. Portal与AC间的协议 (15)6.2.1. 报文格式 (15)6.2.2. 报文字段说明 (15)6.2.3. 参数 (19)6.3. Portal与Radius间的协议 (21)6.3.1. 报文格式 (21)6.3.2. 报文字段说明及参数 (21)7. 编制历史 (22)附录A详细修订历史 (22)前言本标准的目的是为了制定中国移动WLAN业务Portal规范和协议。

本标准主要包括以下几方面内容:Portal协议,系统结构,上线/下线/页面配置/自服务功能流程,协议报文字段,参数及自服务功能描述。

sd 协议

sd 协议SD协议(Secure Digital Protocol)是一种用于在存储设备和电子设备之间进行数据传输和通信的标准协议。

SD协议的发展标志着存储技术的进步和电子设备的智能化。

SD协议的最初版本是在1999年发布的,后来陆续推出了多个版本,包括SDHC协议、SDXC协议和SDUC协议等。

这些协议的不断更新和完善,使SD卡的存储容量不断扩大,同时保证数据传输的速度和稳定性。

SD协议的实现主要依靠两个要素:硬件接口和软件协议。

硬件接口是指SD卡和设备之间的物理连接,包括引脚和接口规范等。

软件协议则是指存储设备和设备间进行数据传输和通信时所需要遵循的规则和约定。

在SD协议中,数据的传输是通过指令和应答来完成的。

首先,设备发送指令给SD卡,指令可能包括读取数据、写入数据、擦除数据等操作。

SD卡接收到指令后,进行相应的处理并返回应答给设备。

设备接收到应答后,根据应答的结果进行下一步的操作。

为了保证数据的安全性和完整性,SD协议还支持数据加密和校验功能。

设备在写入数据时,可以选择进行数据加密,以防止数据泄露。

在读取数据时,设备可以对数据进行完整性校验,以确保数据的准确传输。

SD协议的应用非常广泛,几乎所有的数码设备和移动设备都支持SD卡扩展存储。

例如,相机、手机、平板电脑等设备都可以使用SD卡来进行数据存储和传输。

同时,SD卡也被广泛应用于一些特殊领域,如工业控制、车载设备等。

SD协议的优势在于其高速、高容量和可靠性。

通过不断的技术革新和发展,SD协议的存储容量从最初的几十兆字节,发展到现在的几十TB。

同时,SD协议的传输速度也从最初的几MB/s,提高到现在的几百MB/s。

这些优势使得SD卡成为了存储设备中的主流产品。

总之,SD协议是一种用于存储设备和电子设备之间进行数据传输和通信的标准协议。

通过不断的技术发展和创新,SD卡的容量和传输速度不断提升,为用户提供更高效、更可靠的数据存储和传输解决方案。

PMbus协议栈用户指南_CN

5.1 状态 1- 启动 .................................................................................................. 21 5.2 状态 2-MWA (主机写地址) ........................................................................ 21 5.3 状态 3-MWD (主机写数据) ........................................................................ 21 5.4 状态 4-MRA (主机读地址) ......................................................................... 22 5.5 状态 5-MRD (主机读数据)......................................................................... 22 5.6 状态 6- 停止 .................................................................................................. 22

本出版物中所述的器件应用信息及其他类似内容仅为您提供便

利,它们可能由更新之信息所替代。确保应用符合技术规范, 是您自身应负的责任。Microchip 对这些信息不作任何明示或 暗示、书面或口头、法定或其他形式的声明或担保,包括但不 限于针对其使用情况、质量、性能、适销性或特定用途的适用 性的声明或担保。 Microchip 对因这些信息及使用这些信息而 引起的后果不承担任何责任。如果将 Microchip 器件用于生命 维持和 / 或生命安全应用,一切风险由买方自负。买方同意在 由此引发任何一切伤害、索赔、诉讼或费用时,会维护和保障 Microchip 免于承担法律责任,并加以赔偿。在 Microchip 知识 产权保护下,不得暗中或以其他方式转让任何许可证。

SIM卡基础技术规范

SIM卡基础技术规范

6.1 SIM 卡的复位....................................................................................................................23 6.2 复位应答…........................................................................................................................25

3.1 缩略语及术语定义..............................................................................................................9 3.2 符号………........................................................................................................................12 4 物理特性...................................................................................................................................13 4.1 主要物理特性指标............................................................................................................13 4.2 格式和布局........................................................................................................................15

REF615通讯协议手册

Modbus 标准.................................................7 串行通讯.................................................7 以太网通讯...............................................7 数据应用设备 ............................................8

© 版权 2008 ABB. 版权所有

版权

未经 ABB 书面允许,不得复制本文件的任何部分,不得将其内容透露给第三 方或进行任何未经授权的应用。

本文件中所述的软件和硬件受许可证保护,任何使用、复制或公开应符合许可 证的条款。

商标 ABB 是 ABB 集团的注册商标。本文件中提及的所有其他品牌或产品名称可能 是其持有者的注册商标。

1

目录

章节 4 章节 5

时间的更新...........................................19 控制操作................................................20

控制功能.............................................21 通过 4X 寄存器结构进行的控制操作.....................21 其它的控制操作.......................................23 系统状态寄存器 .........................................24 SSR1.................................................24 SSR2 ................................................25 SSR3 ................................................25 SSR4 ................................................26 SSR5 ................................................27 SSR6 ................................................27 用户定义数据.........................................28 事件记录 ...............................................30 事件记录结构.........................................30 事件读取.............................................31 其他事件记录寄存器...................................32 多事件读取...........................................35 故障录波 ...............................................37 故障录波读取.........................................37 其他故障录波寄存器...................................39 定值组选择..............................................40 时间同步 ...............................................40 实时时钟结构.........................................40 写入实时结构.........................................40 继电保护装置信息........................................41 ASCII 字符编码.......................................42 ASCII 字符串语法.....................................42 复位时间结构............................................42

IC卡通信协议详解(7816-3)

目录第一章IC卡通信过程整体归纳 (1)第二章IC卡的电气特性 (3)1.IC卡的触点分配 (3)2.IC卡的电气特性 (3)2.1 VCC (3)2.2 I/O (3)2.3 CLK (3)2.4 RST (3)2.2 VPP (3)第三章IC卡的操作过程 (4)1、IC卡操作的一般过程 (4)2、卡激活 (4)3、冷复位 (4)4、热复位 (5)5、时钟停止 (6)6、去激活 (6)第四章复位应答 (8)1、异步字符 (8)1.1 字符结构 (8)1.2 错误信号和字符副本 (8)2、复位应答 (9)2.1 复位应答的序列配置 (9)2.2 复位应答的结构和内容 (11)第五章协议和参数选择 (14)1.PPS协议 (14)2.PPS请求的结构和内容 (14)3.成功的PPS交换 (14)第六章异步半双工字符传输协议 (16)1、命令的结构和处理 (16)2、过程字节 (16)3、NULL字节 (16)4、确认字节 (16)5、状态字节 (17)第七章异步半双工块传输 (18)1.数据块块帧结构 (18)2.起始域 (18)3.信息域 (18)4.终止域 (19)5.信息域尺寸 (19)6.等待时间 (19)7.数据链路层字符成分 (20)8.数据链路层块成分 (20)9.链接 (20)第一章IC卡通信过程整体归纳根据协议,IC卡的操作信息交互流程大概为(见图1):(1)接口设备能够控制IC卡各IO引脚使其激活。

(2)接口设备给卡发送复位信号使卡复位启动。

(3)卡要向接口设备发送复位应答信号,将通信中必要的相关信息告知接口设备。

(4)接口设备对卡进行一次热复位,卡进行复位应答。

(5)接口设备发起一个PPS交互指令,选择要与卡通信的协议和相关参数。

(6)根据选择的协议(T=0或T=1)进行数据的通信。

以后各章节将根据此流程,对IC卡协议的各部分主要内容进行归纳总结。

第二章IC卡的电气特性1.IC卡的触点分配根据ISO7816-2的规定,IC卡至少应该分配下面的几个引脚:I/O—串行输入输出CLK—时钟信号RST—复位信号VCC—供电电压,5VGND—接地引脚,电压参考点VPP—编程电压输入,可选2.IC卡的电气特性2.1 VCC在A类工作条件下,VCC的取值范围为4.5V—5.5V,最大允许电流为60mA。

C#基础知识之图解TCPIP》读书笔记

C#基础知识之图解TCPIP》读书笔记⼀、⽹络基础知识1、计算机使⽤模式的演变2、协议协议就是计算机与计算机之间通过⽹络实现通信事先达成的⼀种“约定”。

这种“约定”使那些由不同⼚商的设备、不同的CPU以及不同的操作系统组成的计算机之间,只要遵循相同的协议就能够实现通信。

反之,如果使⽤的协议不同,就⽆法通信。

3、分组交换分组交换是将⼤数据分割为⼀个个叫做包(Packet)的较⼩单位进⾏传输的⽅法。

这⾥所说的包,就如同我们平常在邮局⾥见到的邮包。

分组交换就是将⼤数据分装为⼀个个这样的邮包交给对⽅。

4、协议分层与OSI参考模型(1)协议分层就如同计算机软件中的模块化开发,OSI参考模型的建议是⽐较理想化的。

OSI是Open System Interconnection的缩写,意为开放式系统互联。

(ISO)制定了OSI模型,该模型定义了不同计算机互联的标准,是设计和描述计算机⽹络通信的基本框架。

OSI模型把的⼯作分为7层,分别是、、⽹络层、、、和。

(2)OSI参考模型中每个层的作⽤:(3)7层通信实例:假设主机A的⽤户A要给主机B的⽤户B发送⼀封电⼦邮件:发送⽅从第7层、第6层到第1层由上⾄下按照顺序传输数据,⽽接收端则从第1层、第2层到第7层由下⾄上向每个上⼀级分层传输数据。

每个分层上,在处理由上⼀层传过来的数据时可以附上当前分层的协议所必须的“⾸部”信息。

然后接收端对收到的数据进⾏数据“⾸部”与“内容”的分离,再转发给上⼀分层,并最终将发送端的数据恢复为原装。

⼆、TCP/IP基础知识TCP(Transmission Control Protocol)和IP(Internet Protocol)是互联⽹的众多通信协议中最为著名的。

1、 TCP/IP的背景及历史2、TCP/IP标准化(1)具体含义,很多⼈都会认为TCP/IP是指TCP与IP两种协议,实际⽣活中有时也确实就是指这两种协议。

但是,很多情况下,它只是利⽤IP进⾏通信时所必须使⽤到的协议群的统称。

乐鑫信息科技ESP32技术参考手册说明书

ESP32技术参考手册版本5.0乐鑫信息科技版权©2023关于本手册《ESP32技术参考手册》的目标读者群体是使用ESP32芯片的应用开发工程师。

本手册提供了关于ESP32的具体信息,包括各个功能模块的内部架构、功能描述和寄存器配置等。

芯片的管脚描述、电气特性和封装信息等可以从《ESP32技术规格书》获取。

文档版本请至乐鑫官网https:///zh-hans/support/download/documents下载最新版本文档。

修订历史请至文档最后页查看修订历史。

文档变更通知用户可以通过乐鑫官网订阅页面/zh-hans/subscribe订阅技术文档变更的电子邮件通知。

证书下载用户可以通过乐鑫官网证书下载页面/zh-hans/certificates下载产品证书。

目录1系统和存储器24 1.1概述24 1.2主要特性24 1.3功能描述261.3.1地址映射261.3.2片上存储器261.3.2.1Internal ROM0271.3.2.2Internal ROM1271.3.2.3Internal SRAM0271.3.2.4Internal SRAM1281.3.2.5Internal SRAM2281.3.2.6DMA281.3.2.7RTC FAST Memory291.3.2.8RTC SLOW Memory291.3.3片外存储器291.3.4Cache291.3.5外设301.3.5.1不对称PID Controller外设321.3.5.2不连续外设地址范围321.3.5.3存储器速度32 2中断矩阵(INTERRUPT)332.1概述33 2.2主要特性33 2.3功能描述332.3.1外部中断源332.3.2CPU中断362.3.3分配外部中断源至CPU外部中断362.3.4屏蔽CPU的NMI类型中断372.3.5查询外部中断源当前的中断状态37 3复位和时钟38 3.1System复位383.1.1概述383.1.2复位源38 3.2系统时钟393.2.1概述393.2.2时钟源403.2.3CPU时钟403.2.4外设时钟413.2.4.1APB_CLK413.2.4.2REF_TICK413.2.4.3LEDC_SCLK源423.2.4.4APLL_SCLK源423.2.4.5PLL_F160M_CLK源423.2.4.6时钟源注意事项423.2.5Wi-Fi BT时钟423.2.6RTC时钟423.2.7音频PLL42 3.3寄存器列表43 3.4寄存器434IO_MUX和GPIO交换矩阵(GPIO,IO_MUX)46 4.1概述46 4.2通过GPIO交换矩阵的外设输入474.2.1概述474.2.2功能描述474.2.3简单GPIO输入48 4.3通过GPIO交换矩阵的外设输出484.3.1概述484.3.2功能描述484.3.3简单GPIO输出49 4.4IO_MUX的直接I/O功能504.4.1概述504.4.2功能描述50 4.5RTC IO_MUX的低功耗性能和模拟I/O功能504.5.1概述504.5.2模拟功能描述50 4.6Light-sleep模式管脚功能50 4.7Pad Hold特性51 4.8I/O Pad供电514.8.1VDD_SDIO电源域52 4.9外设信号列表52 4.10IO_MUX Pad列表57 4.11RTC_MUX管脚清单58 4.12寄存器列表594.12.1GPIO交换矩阵寄存器列表594.12.2IO MUX寄存器列表604.12.3RTC IO MUX寄存器列表61 4.13寄存器634.13.1GPIO交换矩阵寄存器634.13.2IO MUX寄存器714.13.3RTC IO MUX寄存器725DPort寄存器86 5.1概述86 5.2主要特性86 5.3功能描述865.3.1系统和存储器寄存器865.3.2复位和时钟寄存器865.3.3中断矩阵寄存器865.3.4DMA寄存器865.3.5MPU/MMU寄存器865.3.6APP_CPU控制器寄存器865.3.7外设时钟门控和复位87 5.4寄存器列表88 5.5寄存器956DMA控制器(DMA)114 6.1概述114 6.2特性114 6.3功能描述1146.3.1DMA引擎的架构1146.3.2链表115 6.4UART DMA(UDMA)控制器115 6.5SPI DMA控制器117 6.6I2S DMA控制器1187SPI控制器(SPI)119 7.1概述119 7.2SPI特征119 7.3GP-SPI接口1207.3.1GP-SPI四线全双工模式1207.3.2GP-SPI四线半双工模式1217.3.3GP-SPI三线半双工模式1217.3.4GP-SPI数据缓存122 7.4GP-SPI时钟控制1227.4.1GP-SPI时钟极性和时钟相位1227.4.2GP-SPI时序123 7.5并行QSPI接口1247.5.1并行QSPI接口通信格式124 7.6GP-SPI中断硬件1257.6.1SPI中断1257.6.2DMA中断125 7.7寄存器列表126 7.8寄存器1288SDIO从机控制器149 8.1概述149 8.2主要特性149 8.3功能描述1498.3.1SDIO Slave功能块图1498.3.2SDIO总线上的数据发送和接收1498.3.3寄存器访问1508.3.4DMA1508.3.5包的发送和接收流程1518.3.5.1Slave向Host发送包1518.3.5.2Slave从Host接收包1538.3.6SDIO总线时序1548.3.7中断1558.3.7.1Host侧中断1558.3.7.2Slave侧中断155 8.4寄存器列表156 8.5SLC寄存器157 8.6SLC Host寄存器166 8.7HINF寄存器1789SD/MMC主机控制器179 9.1概述179 9.2主要特性179 9.3SD/MMC外部接口信号179 9.4功能描述1809.4.1SD/MMC架构1809.4.1.1BIU模块1819.4.1.2CIU模块1819.4.2命令通路1819.4.3数据通路1829.4.3.1数据发送1829.4.3.2数据接收183 9.5CIU操作的软件限制183 9.6收发数据RAM1849.6.1发送RAM模块1849.6.2接收RAM模块184 9.7链表环结构184 9.8链表结构185 9.9初始化1879.9.1DMAC初始化1879.9.2DMAC数据发送初始化1879.9.3DMAC数据接收初始化188 9.10时钟相位选择188 9.11中断189 9.12寄存器列表189 9.13寄存器19010以太网(MAC)210 10.1概述210 10.2EMAC_CORE21210.2.1传输操作21210.2.1.1发送流量控制21210.2.1.2冲突期间的重新发送21310.2.2接收操作21310.2.2.1接收协议21310.2.2.2接收帧控制器21410.2.2.3接收流量控制21410.2.2.4接收多帧的操作处理21410.2.2.5错误处理21410.2.2.6接收状态字214 10.3MAC中断控制器215 10.4MAC地址的过滤21510.4.1单播目标地址过滤21510.4.2多播目标地址过滤21510.4.3广播地址过滤21510.4.4单播源地址过滤21510.4.5反向过滤操作21510.4.6好的发送帧与接收帧217 10.5EMAC_MTL(MAC传输层)217 10.6PHY接口21710.6.1MII(介质独立接口)21710.6.1.1MII与PHY间的接口信号21810.6.1.2MII时钟21910.6.2RMII(精简介质独立接口)21910.6.2.1RMII接口信号描述22010.6.2.2RMII时钟22010.6.3Station Management Agent(SMA)接口22110.6.4RMII接口时序要求221 10.7以太网DMA特性222 10.8链表描述符22210.8.1发送描述符22210.8.2接收描述符226 10.9寄存器列表230 10.10寄存器23211I2C控制器(I2C)266 11.1概述266 11.2主要特性266 11.3I2C功能描述26611.3.1I2C简介26611.3.2I2C架构26711.3.3I2C总线时序26811.3.4I2C cmd结构26811.3.5I2C主机写入从机26911.3.6I2C主机读取从机27311.3.7中断275 11.4寄存器列表275 11.5寄存器27712I2S控制器(I2S)287 12.1概述287 12.2主要特性288 12.3I2S模块时钟289 12.4I2S模式29012.4.1支持的音频标准29012.4.1.1Philips标准29012.4.1.2MSB对齐标准29012.4.1.3PCM标准29112.4.2模块复位29112.4.3FIFO操作29112.4.4发送数据29112.4.5接收数据29312.4.6I2S主机/从机模式29412.4.7I2S PDM模式295 12.5Camera-LCD控制器29612.5.1LCD主机发送模式29712.5.2Camera从机接收模式29712.5.3ADC/DAC模式298 12.6I2S中断29912.6.1FIFO中断29912.6.2DMA中断300 12.7寄存器列表300 12.8寄存器30213UART控制器(UART)319 13.1概述319 13.2主要特性319 13.3功能描述31913.3.1UART简介31913.3.2UART架构32013.3.3UART RAM32113.3.4波特率检测32113.3.5UART数据帧32213.3.6AT_CMD字符格式32213.3.7流控32313.3.7.1硬件流控32313.3.7.2软件流控32413.3.8UDMA32413.3.9UART中断32413.3.10UHCI中断325 13.4寄存器列表32513.4.1UART寄存器列表32513.4.2UHCI寄存器列表326 13.5寄存器32813.5.1UART寄存器32813.5.2UHCI寄存器34414LED PWM控制器(LEDC)355 14.1概述355 14.2功能描述35514.2.1架构35514.2.2分频器35614.2.3通道35714.2.4中断358 14.3寄存器列表358 14.4寄存器36115红外遥控(RMT)370 15.1概述370 15.2功能描述37015.2.1RMT架构37015.2.2RMT RAM37115.2.3时钟37115.2.4发射器37115.2.5接收器37215.2.6中断372 15.3寄存器列表372 15.4寄存器37316电机控制脉宽调制器(PWM)378 16.1概述378 16.2主要特性378 16.3模块38016.3.1模块概述38016.3.1.1预分频器模块38016.3.1.2定时器模块38016.3.1.3操作器模块38116.3.1.4故障检测模块38316.3.1.5捕获模块38316.3.2PWM定时器模块38316.3.2.1PWM定时器模块的配置38316.3.2.2PWM定时器工作模式和定时事件生成38416.3.2.3PWM定时器影子寄存器38816.3.2.4PWM定时器同步和锁相38816.3.3PWM操作器模块38816.3.3.1PWM生成器模块38916.3.3.2死区生成器模块39916.3.3.3PWM载波模块40316.3.3.4故障处理器模块40616.3.4捕获模块40716.3.4.1介绍40716.3.4.2捕获定时器40716.3.4.3捕获通道408 16.4寄存器列表408 16.5寄存器41017脉冲计数器(PCNT)454 17.1概述454 17.2功能描述45417.2.1架构图45417.2.2计数器通道输入信号45517.2.3观察点45517.2.4举例45517.2.5溢出中断456 17.3寄存器列表456 17.4寄存器45718定时器组(TIMG)463 18.1概述463 18.2功能描述46318.2.116-bit预分频器46318.2.264-bit时基计数器46318.2.3报警产生46418.2.4MWDT46418.2.5中断464 18.3寄存器列表464 18.4寄存器46619看门狗定时器(WDT)473 19.1概述473 19.2主要特性473 19.3功能描述47319.3.1时钟47319.3.2运行过程47319.3.3写保护47419.3.4Flash启动保护47419.3.5寄存器47420eFuse控制器(eFuse)475 20.1概述475 20.2主要特性475 20.3功能描述47520.3.1结构47520.3.1.1系统参数efuse_wr_disable47620.3.1.2系统参数efuse_rd_disable47620.3.1.3系统参数coding_scheme47720.3.1.4系统参数BLK3_part_reserve47820.3.2烧写系统参数47820.3.3软件读取系统参数48120.3.4硬件模块使用系统参数48220.3.5中断482 20.4寄存器列表483 20.5寄存器48521双线汽车接口(TWAI)496 21.1概述496 21.2主要特性496 21.3功能性协议49621.3.1TWAI性能49621.3.2TWAI报文49721.3.2.1数据帧和远程帧49821.3.2.2错误帧和过载帧50021.3.2.3帧间距50121.3.3TWAI错误50221.3.3.1错误类型50221.3.3.2错误状态50221.3.3.3错误计数50221.3.4TWAI位时序50321.3.4.1名义位50321.3.4.2硬同步与再同步504 21.4结构概述50521.4.1寄存器模块50521.4.2位流处理器50621.4.3错误管理逻辑50621.4.4位时序逻辑50621.4.5接收滤波器50621.4.6接收FIFO506 21.5功能描述50621.5.1模式50621.5.1.1复位模式50721.5.1.2操作模式50721.5.2位时序50721.5.3中断管理50821.5.3.1接收中断(RXI)50821.5.3.2发送中断(TXI)50821.5.3.3错误报警中断(EWI)50821.5.3.4数据溢出中断(DOI)50921.5.3.5被动错误中断(TXI)50921.5.3.6仲裁丢失中断(ALI)50921.5.3.7总线错误中断(BEI)50921.5.4发送缓冲器与接收缓冲器50921.5.4.1缓冲器概述50921.5.4.2帧信息51021.5.4.3帧标识符51021.5.4.4帧数据51121.5.5接收FIFO和数据溢出51121.5.6接收滤波器51221.5.6.1单滤波模式51221.5.6.2双滤波模式51321.5.7错误管理51321.5.7.1错误报警限制51521.5.7.2被动错误51521.5.7.3离线状态与离线恢复51521.5.8错误捕捉51521.5.9仲裁丢失捕捉516 21.6寄存器列表517 21.7寄存器51822AES加速器(AES)530 22.1概述530 22.2主要特性530 22.3功能描述53022.3.1运算模式53022.3.2密钥、明文、密文53022.3.3字节序53022.3.4加密与解密运算53322.3.5运行效率533 22.4寄存器列表533 22.5寄存器53423SHA加速器(SHA)536 23.1概述536 23.2主要特性536 23.3功能描述53623.3.1填充解析信息53623.3.2信息摘要53623.3.3哈希运算53623.3.4运行效率537 23.4寄存器列表537 23.5寄存器53924RSA加速器(RSA)544 24.1概述544 24.2主要特性544 24.3功能描述54424.3.1初始化54424.3.2大数模幂运算54424.3.3大数模乘运算54524.3.4大数乘法运算54624.4寄存器列表547 24.5寄存器54825随机数发生器(RNG)550 25.1概述550 25.2主要特性550 25.3功能描述550 25.4编程指南550 25.5寄存器列表551 25.6寄存器55126片外存储器加密与解密(FLASH)552 26.1概述552 26.2主要特性552 26.3功能描述55226.3.1Key Generator模块55326.3.2Flash Encryption模块55326.3.3Flash Decryption模块554 26.4寄存器列表554 26.5寄存器55427存储器管理和保护单元(MMU,MPU)556 27.1概述556 27.2主要特性556 27.3功能描述55627.3.1PID控制器55627.3.2MPU/MMU55627.3.2.1嵌入式存储器55627.3.2.2片外存储器56327.3.2.3外设56828PID控制器(PID)570 28.1概述570 28.2主要特性570 28.3功能描述57028.3.1中断识别57028.3.2信息记录57128.3.3进程主动切换进程573 28.4寄存器列表574 28.5寄存器57629片上传感器与模拟信号处理581 29.1概述581 29.2电容式触摸传感器58129.2.1简介58129.2.2主要特性58129.2.3可用通用输入输出接口58229.2.4功能描述58229.2.5触发传感器的状态机583 29.3SAR ADC58429.3.1简介58429.3.2主要特性58529.3.3功能概况58529.3.4RTC SAR ADC控制器58729.3.5DIG SAR ADC控制器587 29.4数字模拟转换器58929.4.1简介58929.4.2主要特性58929.4.3结构58929.4.4余弦波形生成器59029.4.5支持DMA590 29.5寄存器列表59129.5.1传感器59129.5.2外围总线59229.5.3RTC I/O592 29.6寄存器59329.6.1传感器59329.6.2高级外围总线60229.6.3RTC I/O606 30超低功耗协处理器(ULP)607 30.1概述607 30.2主要特性607 30.3功能描述608 30.4指令集60830.4.1ALU-算数与逻辑运算60830.4.1.1对寄存器数值的运算60930.4.1.2对指令立即值的运算60930.4.1.3对阶段计数器寄存器数值的运算61030.4.2ST–存储数据至内存61130.4.3LD–从内存加载数据61130.4.4JUMP–跳转至绝对地址61230.4.5JUMPR–跳转至相对地址(基于R0寄存器判断)61230.4.6JUMPS–跳转至相对地址(基于阶段计数器寄存器判断)61330.4.7HALT–结束程序61330.4.8WAKE–唤醒芯片61330.4.9SLEEP–设置硬件计时器的唤醒周期61430.4.10WAIT–等待若干个周期61430.4.11ADC–对ADC进行测量61430.4.12I2C_RD/I2C_WR–读/写I²C61530.4.13REG_RD–从外围寄存器读取61530.4.14REG_WR–写入外围寄存器61630.5ULP协处理器程序的执行616 30.6RTC_I2C控制器61830.6.1配置RTC_I2C61830.6.2使用RTC_I2C61930.6.2.1I2C_RD-读取单个字节61930.6.2.2I2C_WR-写入单个字节61930.6.2.3检测错误条件62030.6.2.4连接I²C信号620 30.7寄存器列表62030.7.1SENS_ULP地址空间62030.7.2RTC_I2C地址空间621 30.8寄存器62130.8.1SENS_ULP地址空间62130.8.2RTC_I2C地址空间62431低功耗管理(RTC_CNTL)630 31.1概述630 31.2主要特性630 31.3功能描述63031.3.1简介63131.3.2数字内核调压器63131.3.3低功耗调压器63131.3.4Flash调压器63231.3.5欠压检测器63331.3.6RTC模块63331.3.7低功耗时钟63431.3.8电源门控的实现63631.3.9预设功耗模式63731.3.10唤醒源63931.3.11拒绝睡眠63931.3.12RTC计时器64031.3.13RTC Boot640 31.4寄存器列表642 31.5寄存器643词汇列表669外设相关词汇669寄存器相关词汇669修订历史670表格1-1地址映射26 1-2片上寄存器地址映射27 1-3具有DMA功能的模块29 1-4片外存储器地址映射29 1-5Cache memory模式30 1-6外设地址映射31 2-1PRO_CPU、APP_CPU外部中断配置寄存器、外部中断源中断状态寄存器、外部中断源34 2-2CPU中断36 3-1PRO_CPU和APP_CPU复位源38 3-2CPU_CLK源40 3-3CPU_CLK源40 3-4外设时钟用法41 3-5APB_CLK41 3-6REF_TICK41 3-7LEDC_SCLK源42 4-1IO_MUX Light-sleep管脚功能寄存器50 4-2GPIO交换矩阵外设信号52 4-3IO_MUX Pad列表57 4-4RTC_MUX管脚清单58 7-1管脚功能信号与总线信号映射关系119 7-2从机命令描述121 7-3主机模式时钟极性和相位控制寄存器值123 7-4从机模式时钟极性和相位控制寄存器值123 9-1SD/MMC管脚描述180 9-2DES0链表描述185 9-3DES1186 9-4DES2187 9-5DES3187 10-1目标地址过滤216 10-2源地址过滤216 10-3接收数据时序要求221 10-4发送数据时序要求222 10-5发送描述符0(TDES0)223 10-6发送描述符1(TDES1)225 10-7发送描述符2(TDES2)226 10-8发送描述符3(TDES3)226 10-9接收描述符0(RDES0)226 10-10接收描述符1(RDES1)228 10-11接收描述符2(RDES2)228 10-12接收描述符3(RDES3)228 10-13接收描述符4(RDES4)229 11-1SCL频率配置268 12-1I2S信号总线描述28812-2寄存器配置292 12-3发送通道模式292 12-4接收数据写入FIFO模式和对应寄存器配置293 12-54种模式对应寄存器配置294 12-6过采样率配置295 12-7下采样配置296 14-1常用配置频率及精度357 16-1操作器模块的配置参数382 16-2PWM生成器中的所有定时事件390 16-3PWM定时器递增计数时,定时事件的优先级390 16-4PWM定时器递减计数时,定时事件的优先级391 16-5控制死区时间生成器开关的寄存器400 16-6死区生成器的典型操作模式401 20-1系统参数475 20-2BLOCK1/2/3编码477 20-3烧写寄存器478 20-4时序配置480 20-5软件读取寄存器481 21-1SFF和EFF中的数据帧和远程帧499 21-2错误帧500 21-3过载帧501 21-4帧间距501 21-5名义位时序中包含的段504 21-6TWAI_CLOCK_DIVIDER_REG的bit信息;TWAI地址0x18507 21-7TWAI_BUS_TIMING_1_REG的bit信息;TWAI地址0x1c507 21-8SFF与EFF的缓冲器布局509 21-9TX/RX帧信息(SFF/EFF);TWAI地址0x40510 21-10TX/RX标识符1(SFF);TWAI地址0x44511 21-11TX/RX标识符2(SFF);TWAI地址0x48511 21-12TX/RX标识符1(EFF);TWAI地址0x44511 21-13TX/RX标识符2(EFF);TWAI地址0x48511 21-14TX/RX标识符3(EFF);TWAI地址0x4c511 21-15TX/RX标识符4(EFF);TWAI地址0x50511 21-16TWAI_ERR_CODE_CAP_REG的bit信息;TWAI地址0x30515 21-17SEG.4-SEG.0的位信息516 21-18TWAI_ARB LOST CAP_REG中的位信息;TWAI地址0x2c517 22-1运算模式530 22-2AES文本字节序531 22-3AES-128密钥字节序532 22-4AES-192密钥字节序532 22-5AES-256密钥字节序532 27-1片上存储器的MPU和MMU结构557 27-2管理RTC FAST Memory的MPU557 27-3管理RTC SLOW Memory的MPU557 27-4管理片上SRAM0和SRAM2剩余128KB的MMU页模式558 27-5SRAM0MMU页边界地址55927-6SRAM2MMU页边界地址560 27-7DPORT_DMMU_TABLE n_REG和DPORT_IMMU_TABLE n_REG561 27-8针对DMA的MPU设置562 27-9片外存储器的虚地址563 27-10PRO_CPU的MMU配置项号564 27-11APP_CPU的MMU配置项号564 27-12PRO_CPU的MMU配置项号(特殊模式)564 27-13APP_CPU的MMU配置项号(特殊模式)565 27-14片外SRAM的虚拟地址模式566 27-15片外SRAM的虚地址(正常模式)566 27-16片外SRAM的虚地址(低-高模式)566 27-17片外SRAM的虚地址(偶-奇模式)567 27-18片外RAM的MMU配置项号567 27-19管理外设的MPU568 27-20DPORT_AHBLITE_MPU_TABLE_X_REG569 28-1中断向量入口地址571 28-2PIDCTRL_LEVEL_REG571 28-3PIDCTRL_FROM_n_REG572 29-1ESP32电容式触摸传感器的管脚582 29-2SAR ADC的信号输入586 29-3ESP32的SAR ADC控制器586 29-4样式表寄存器的字段信息588 29-5I型DMA数据格式589 29-6II型DMA数据格式589 30-1对寄存器数值的ALU运算609 30-2对指令立即值的ALU运算610 30-3对阶段计数器寄存器的ALU运算610 30-4ADC指令的输入信号614 31-1RTC电源域636 31-2唤醒源639插图1-1系统结构25 1-2地址映射结构25 1-3Cache系统框图30 2-1中断矩阵结构图33 3-1系统复位38 3-2系统时钟39 4-1IO_MUX、RTC IO_MUX和GPIO交换矩阵结构框图46 4-2通过IO_MUX、GPIO交换矩阵的外设输入47 4-3通过GPIO交换矩阵输出信号49 4-4ESP32I/O Pad供电源(QFN6*6,顶视图)51 4-5ESP32I/O Pad供电源(QFN5*5,顶视图)52 6-1DMA引擎的架构114 6-2链表结构图115 6-3UDMA模式数据传输116 6-4SPI DMA117 7-1SPI系统框图119 7-2SPI四线全双工/半双工通信120 7-3SPI数据缓存122 7-4GP-SPI从机数据输出124 7-5并行QSPI接口125 7-6并行QSPI接口的通信模式125 8-1SDIO Slave功能块图149 8-2SDIO总线上数据传输150 8-3CMD53内容150 8-4SDIO Slave DMA链表结构150 8-5链表串151 8-6Slave向Host发送包的流程152 8-7Slave从Host接收包的流程153 8-8Slave CPU挂载buffer的流程154 8-9采样时序图154 8-10输出时序图155 9-1SD/MMC外设连接的拓扑结构179 9-2SD/MMC外部接口信号180 9-3SD/MMC基本架构180 9-4命令通路状态机182 9-5数据传输状态机182 9-6数据接收状态机183 9-7链表环结构185 9-8链表结构185 9-9时钟相位选择188 10-1Ethernet MAC功能概述210 10-2Ethernet功能框图212 10-3MII接口21810-4MII时钟219 10-5RMII接口220 10-6RMII时钟221 10-7接收数据时序图221 10-8发送数据时序图222 10-9发送描述符222 10-10接收链表结构226 11-1I2C Master基本架构267 11-2I2C Slave基本架构267 11-3I2C时序图268 11-4I2C命令寄存器结构269 11-5I2C Master写7-bit地址Slave270 11-6I2C Master写10-bit地址Slave271 11-7I2C Master写7-bit地址Slave的M地址RAM271 11-8I2C Master分段写7-bit地址Slave272 11-9I2C Master读7-bit地址Slave273 11-10I2C Master读10-bit地址Slave273 11-11I2C Master从7-bit地址Slave的M地址读取N个数据274 11-12I2C Master分段读7-bit地址Slave275 12-1I2S系统框图287 12-2I2S时钟289 12-3Philips标准290 12-4MSB对齐标准290 12-5PCM标准291 12-6发送FIFO数据模式292 12-7第一阶段接收数据293 12-8接收数据写入FIFO模式294 12-9PDM发送模块295 12-10PDM发送信号296 12-11PDM接收信号296 12-12PDM接收模块296 12-13LCD主机发送模式297 12-14LCD主机发送数据帧格式1297 12-15LCD主机发送数据帧格式2297 12-16Camera从机接收模式298 12-17I2S的ADC接口298 12-18I2S的DAC接口299 12-19I2S DAC接口数据输入299 13-1UART基本架构图320 13-2UART共享RAM图321 13-3UART数据帧结构322 13-4AT_CMD字符格式322 13-5硬件流控图323 14-1LED_PWM架构355 14-2LED_PWM高速通道框图355 14-3LED_PWM分频器35614-4LED_PWM输出信号图357 14-5渐变占空比输出信号图358 15-1RMT架构370 15-2数据结构371 16-1MCPWM外设概览378 16-2预分频器模块380 16-3定时器模块380 16-4操作器模块381 16-5故障检测模块383 16-6捕获模块383 16-7递增计数模式波形384 16-8递减计数模式波形385 16-9递增递减循环模式波形,同步事件后递减385 16-10递增递减循环模式波形,同步事件后递增385 16-11递增模式中生成的UTEP和UTEZ386 16-12递减模式中生成的UTEP和UTEZ387 16-13递增递减模式中生成的UTEP和UTEZ388 16-14PWM操作器的子模块389 16-15递增递减模式下的对称波形392 16-16递增计数模式,单边不对称波形,PWM x A和PWM x B独立调制–高电平393 16-17递增计数模式,脉冲位置不对称波形,PWM x A独立调制394 16-18递增递减循环计数模式,双沿对称波形,在PWM x A和PWM x B上独立调制–高电平有效395 16-19递增递减循环计数模式,双沿对称波形,在PWM x A和PWM x B上独立调制–互补396 16-20NCI在PWM x A输出上软件强制事件示例397 16-21CNTU在PWM x B输出上软件强制事件示例398 16-22死区模块的开关拓扑400 16-23高电平有效互补(AHC)死区波形401 16-24低电平有效互补(ALC)死区波形401 16-25高电平有效(AH)死区波形402 16-26低电平有效(AL)死区波形402 16-27PWM载波操作的波形示例404 16-28载波模块的第一个脉冲和之后持续的脉冲示例405 16-29PWM载波模块中持续脉冲的7种占空比设置406 17-1PULSE_CNT单元基本架构图454 17-2PULSE_CNT递增计数图456 17-3PULSE_CNT递减计数图456 21-1数据帧和远程帧中的位域498 21-2错误帧中的位域500 21-3过载帧中的位域500 21-4帧间距中的域501 21-5位时序构成504 21-6TWAI概略图505 21-7接收滤波器512 21-8单滤波模式513 21-9双滤波模式514 21-10错误状态变化514乐鑫信息科技21ESP32技术参考手册(v5.0)21-11丢失仲裁的bit位置517 25-1噪声源550 26-1Flash加解密模块架构552 27-1MMU访问示例558 28-1中断嵌套573 29-1触摸传感器581 29-2触摸传感器的内部结构582 29-3触摸传感器的工作流程583 29-4FSM的内部结构584 29-5SAR ADC的概况584 29-6SAR ADC的功能概况585 29-7RTC SAR ADC的功能概况587 29-8DIG SAR ADC控制器的概况588 29-9DAC的功能概况590 29-10余弦波形生成器的工作流程591 30-1ULP协处理器基本架构607 30-2ULP协处理器的指令格式608 30-3指令类型-对寄存器数值的ALU运算609 30-4指令类型-对指令立即值的ALU运算609 30-5指令类型-对阶段计数器寄存器的ALU运算610 30-6指令类型-ST611 30-7指令类型-LD611 30-8指令类型-JUMP612 30-9指令类型-JUMPR612 30-10指令类型-JUMPS613 30-11指令类型-HALT613 30-12指令类型-WAKE613 30-13指令类型-SLEEP614 30-14指令类型-WAIT614 30-15指令类型-ADC614 30-16指令类型-I²C615 30-17指令类型-REG_RD615 30-18指令类型-REG_WR616 30-19ULP协处理器程序框图617 30-20ULP协处理器程序流控图618 30-21I2C读操作619 30-22I²C写操作620 31-1ESP32功耗控制示意图630 31-2数字内核调压器631 31-3低功耗调压器632 31-4Flash调压器633 31-5欠压检测器633 31-6RTC结构图634 31-7RTC低功耗时钟635 31-8数字低功耗时钟635 31-9RTC状态63631-10功耗模式638 31-11ESP32启动流程图6411系统和存储器1.1概述ESP32采用两个哈佛结构Xtensa LX6CPU构成双核系统。

楼宇智能化详解

楼宇智能化详解目录1. 楼宇智能化概述 (2)1.1 楼宇智能化的定义 (3)1.2 楼宇智能化的意义 (4)1.3 楼宇智能化的发展历程 (5)2. 楼宇智能化系统架构 (7)2.1 硬件层 (8)2.1.1 传感器 (10)2.1.2 控制器 (11)2.1.3 执行器 (13)2.2 软件层 (14)2.2.1 数据采集与处理 (16)2.2.2 数据存储与分析 (17)2.2.3 控制策略与优化 (18)2.3 通信层 (20)2.3.1 有线通信 (21)2.3.2 无线通信 (24)2.4 应用层 (25)2.4.1 安防系统 (26)2.4.2 能源管理系统 (28)2.4.3 智能办公系统 (29)3. 楼宇智能化关键技术 (31)3.1 物联网技术 (32)3.2 大数据技术 (33)3.3 人工智能技术 (35)3.4 云计算技术 (36)3.5 边缘计算技术 (38)4. 楼宇智能化实施与应用案例 (39)4.1 智慧园区建设 (41)4.2 智能建筑应用 (42)4.3 智能家居案例 (44)4.4 智能交通管理实践 (45)5. 楼宇智能化发展趋势与挑战 (46)1. 楼宇智能化概述楼宇智能化是指通过现代信息技术手段,对建筑物内的各类资源进行优化配置和高效管理,提供安全、舒适、便捷、节能和环保的居住、办公和商业环境。

楼宇智能化系统主要包括楼宇自控系统(BAS)、楼宇智能安防系统、楼宇智能环境控制系统、楼宇智能能源管理系统等。

这些系统通过集成化、网络化、信息化的手段,实现对建筑物的全面感知、实时控制和智能管理,提高建筑物的使用效率和舒适度,降低运营成本,促进可持续发展。

楼宇智能化的发展经历了从简单的自动化系统到复杂的智能化的过程,随着科技的进步和人们对生活品质要求的提高,楼宇智能化已经成为现代建筑的重要组成部分。

楼宇智能化不仅提升了建筑物的功能价值,还为人们带来了更加便捷、舒适和安全的居住、办公和商业环境。

SD6.0规范(简化版)学习笔记

SD6.0规范(简化版)学习笔记目录1.概述 (1)2.系统特点SYSTEM FEATURE (1)3.SD存储卡系统概要 (2)3.1按照读写特性,可分为读写卡以及只读卡。

(2) 3.2按供电电压可分为两类 (2)3.3卡容量 (2)3.4速率等级 (2)3.5总线拓扑 (2)3.6总线协议 (2)3.6.1SD总线协议 (2)3.6.2SPI总线协议 (4)3.6.3UHS-2总线协议 (4)3.7SD存储卡的管脚和寄存器 (5)3.7.1SD 总线管脚安排 (5)3.7.2UHS-2总线管脚安排 (5)3.8ROM卡(即前面提到的只读卡) (5)3.9UHS-1卡 (5)3.9.1支持的速率 (5)3.9.2UHS-1卡的类别 (5)3.9.3UHS-1主设备类别 (5)3.9.4UHS-1总线速率模式选择流程 (5)3.9.5UHS-1系统框图 (6)3.9.6UHS-1卡总线速率模式总结 (6)3.10UHS-2卡 (6)3.10.1UHS-2卡工作模式 (6)3.10.2UHS-2卡类别 (6)3.10.3UHS-2主设备和卡配合 (7)3.10.4UHS-2接口选择时序 (7)3.10.5UHS-2卡总线速率模式总结 (8)3.11应用性能等级 APPLICATION PERFORMANCE CLASS (8)3.12C ACHE (9)3.13SELF MAINTENANCE (9)3.14COMMAND QUEUE (9)3.15LV接口 (9)3.16UHS-2更高的总线速率(UHS-3) (9)4.SD存储卡的功能描述 (9)4.1概要 (9)4.2卡识别模式 (10)4.3数据传输模式 (10)4.4时钟控制 (10)4.5CRC (10)4.6E RROR CONDITION 出现错误的情况 (10)4.7命令 (10)4.8卡状态转换表 (10)4.9响应 (10)4.10SD存储卡的三种状态信息 (10)4.11M EMORY ARRAY PARTITIONING (10)4.12时序 (10)4.13速率等级划分 (10)4.13.1SDSC和SDHC的速率等级 (11)4.13.2SDXC卡的速率等级 (13)4.13.3UHS-1和UHS-2的速率等级 (13)4.13.4Video速率等级 (14)4.14E RASE TIMEOUT CALCULATION (15)4.15S ET B LOCK C OUNT命令 (15)4.16应用性能说明 A PPLICATION P ERFORMANCE S PECIFICATION (15)4.16.1应用性能等级 (15)4.16.2应用等级测试条件 (15)4.16.3应用等级性能参数 (15)4.17C ACHE (16)4.18S ELF MAINTENANCE 自维护 (16)4.19C ONMAND QUEUE模式 (16)5.卡寄存器 (16)6.SD存储卡硬件接口 (16)6.1热插拔 (16)6.2卡检测 (16)6.3电源保护(热插拔) (16)6.4电源 (16)6.4.1SD总线接口的上电时序 (16)6.4.2UHS-2接口的上电时序 (18)6.5P ROGRAMMABLE CARD OUTPUT DRIVER(可选) (19)6.6B US OPERATING CONDITIONS FOR 3.3V SIGNALING (19)6.6.1Threshold level for high voltage range (19)6.6.2Peak voltage and leakage current (19)6.6.3Power consumption (19)6.6.4Bus signal line load (19)6.6.5Bus signal levels (19)6.6.6总线时序(默认速率模式) (19)6.6.7总线速率(高速模式) (20)6.7D RIVE STRENGTH AND BUS TIMING FOR 1.8V SIGNALING (21)6.8ESD要求 (21)7.SPI模式 (21)1. 概述除了SD存储卡之外还有SDIO卡,SDIO卡基于SD存储卡,也兼容SD存储卡接口。

5.1.13 中国移动LTE USIM卡技术规范V1_0_0. pdf

实施

中国移动通信集团公司

发布

I

目

1 2 3 4

录

5 6

7

8

9

范围 ......................................................................1 规范性引用文件 ............................................................1 术语、定义和缩略语 ........................................................3 USIM 卡产品概述 ...........................................................4 4.1. 产品概述 ..........................................................4 4.2. 单模 USIM 卡 .......................................................4 4.3. 复合 USIM 卡 .......................................................4 USIM 卡架构 ...............................................................5 5.1. USIM 卡架构 .......................................................5 物理及电气特性 ............................................................5 6.1. 物理特性 ..........................................................5 6.2. 电气特性 ..........................................................6 逻辑特性 ..................................................................6 7.1. 通信初始化建立过程 ................................................6 7.2. 传输协议 ..........................................................6 7.3. 文件结构 ..........................................................6 7.4. 安全特性 ..........................................................7 7.5. 命令结构 ..........................................................7 7.6. 命令描述 ..........................................................7 USIM 功能要求 .............................................................7 8.1. 文件内容 ..........................................................7 8.1.1. MF层下的EF文件 ................................................7 8.1.2. USIM ADF层的EF文件 ............................................8 8.1.3. USIM ADF层的DF文件 ............................................8 8.1.4. USIM ADF层的DF下的EF文件 ......................................8 8.1.5. TELECOM层的EF文件 .............................................8 8.1.6. TELECOM层的DF文件 .............................................8 8.1.7. USIM文件结构 ..................................................8 8.2. USIM 机卡接口协议..................................................8 8.2.1. USIM管理过程 ..................................................8 8.2.2. 安全相关过程 ..................................................8 8.2.3. 注册相关过程 ..................................................8 8.2.4. USAT相关过程 ..................................................9 8.3. 安全特性 ..........................................................9 8.4. USIM 命令 .........................................................9 8.4.1. 鉴权相关命令 ..................................................9 8.4.2. 返回状态字 ....................................................9 USAT 功能要求 .............................................................9 9.1. USAT 概述 .........................................................9 9.2. 概要信息下载 .....................................................10 9.3. 主动式 UICC ......................................................10

EMC VNXe 系列存储系统详细介绍

EMC VNXe 系列存储系统 详细介绍

2

目录

执行概述 ................................................................................................................ 4

目标受众 ............................................................................................................................ 4

EMC VNXe 系列存储系统 详细介绍

3

执行概述

企业对存储容量的需求持续呈指数级增长,而且还要求全天候可用性。调查显示, 企业的信息平均每年要增长 50% 以上。而这一增长中的大部分为非结构化数据, 如文件。 随着 IT 部门持续添加新的服务器和应用程序并迁移到虚拟化程度更高的环境中, 复杂性的增加是很常见的。可帮助企业更好地利用服务器虚拟化的解决方案有着 非常诱人的优势。对于企业来说,传统的存储管理通常过于复杂。对于存储管理 员来说,分配和管理存储通常需要了解复杂的存储术语,而且还要经过专门培训。 尽管 IT 环境的复杂性在持续增加,IT 用户所要求的服务级别依然很高。设备、人 员和设施方面成本的增加仍是 IT 人员面临的一个难题。 EMC® VNXe™ 系列是一个新的统一存储解决方案,它面向中小型企业、中端企 业的较低端以及大型企业中的远程 / 分支办公室 (ROBO) 。它可解决上述难题。 VNXe 系列专为存储经验有限的 IT 人员而设计,可提供高级文件和数据块功能以 及简单、应用程序驱动的共享存储管理方法,能够帮助实现全面的存储整合。 VNXe 系列在效率、简洁性和经济性上有了巨大进步。VNXe 系列存储系统的主要 好处包括: 支持文件(CIFS 和 NFS)和数据块 (iSCSI) 存储 快照和复制(本地和远程) 以应用程序为中心的资源调配和内置的最佳做法 与 VMware 和 Hyper-V 服务器集成 新的 Unisphere™ 界面简化了管理 本白皮书概括介绍了 VNXe 系列存储系统。

TNSP015C10NC接口和协议

可编辑TN_SP015_C1_0 NC接口和协议课程目标:●掌握NC接口协议模型●掌握BICC协议参考资料:●ZXWN MSCS MSC服务器技术描述●ZXWN MGW 媒体网关技术描述可编辑目录第1章 BICC协议 (1)1.1 概述 (1)1.1.1 BICC产生的原因和意义 (1)1.1.2 BICC的定义 (2)1.1.3 BICC支持的能力 (2)1.1.4 BICC的能力集 (5)1.2 BICC的基本概念 (6)1.3 BICC的协议模型 (9)1.3.1 BICC协议栈 (9)1.3.2 网络功能模型 (10)1.3.3 协议模型 (10)1.3.4 承载与控制分离 (11)1.3.5 承载控制隧道机制 (12)1.4 BICC信令消息 (13)1.5 BICC消息流程 (17)1.5.1 BICC承载建立方式 (17)1.5.2 呼叫建立流程 (17)1.6 BICC和ISUP的关系 (22)1.6.1 承载与控制分离 (22)1.6.2 CIC概念的扩充 (22)1.6.3 消息和参数的变化 (23)可编辑第1章BICC协议知识点BICC的基本概念。

BICC的协议模型。

BICC的信令流程。

1.1 概述1.1.1 BICC产生的原因和意义在过去几年,数据网络和语音网络集成的需求变得越来越明显了。

电信网络使用拨号接入WWW。

IP网络也用于提供低质量、低价钱的话音业务。

电路竞争使语音流可以和数据流都在ATM网络上传送。

尽管语音业务需要用拨号发起,WEB接入也可以对它进行管理。

ETSI和TIPHON定义了网关,使用H.323为PSTN/ISDN提供VOIP业务。

在1999年,ITU-T提出了BICC协议。

导致BICC协议发展的问题是,网络运营商在过去几年内,经历了语音业务的飞速增长。

这种增长中的很大成分归根于拨号接入WWW的大规模应用。

这就给网络运营商带来了问题。

一方面,PSTN/ISDN达到了一个伸缩极限,因此针对这种增长需要调节资金投入。

RISC-V指令集手册说明书

翻译团队 ................................................................................................................................................ 12

3.5 静态链接和动态链接 ................................................................................................................. 49

3.6 加载器 ............................................................................................................................................. 49

3.2 函数调用规范(Calling convention) ................................................................................. 41

3.3 汇编器 ............................................................................................................................................. 43

白皮书 全新EMC VNX系列简介 VNX5200 VNX5400 VNX5600 VNX5800 VNX7600 VNX8000详细介绍 20131031

I/O 模块 ................................................................................................................ 42

存储处理器的 I/O 模块 .................................................................................................... 42 Data Mover 的 I/O 模块.................................................................................................... 46

白皮书

全新 EMC VNX 系列简介

VNX5200、VNX5400、VNX5600、VNX5800、VNX7600 和 VNX8000

详细介绍

摘论了不同的 型号、新功能和改进的功能,以及主要优点。 2013 年 11 月

版权所有 © 2013 EMC Corporation。保留所有权利。 EMC 确信本出版物在发布之日内容准确无误。本出版物中的 信息可随时更改而不另行通知。 本出版物的内容按“原样”提供。EMC Corporation 对本出 版物的内容不提供任何形式的陈述或担保,明确拒绝对有特 定目的的适销性或适用性进行默示担保。 使用、复制或分发本出版物所描述的任何 EMC 软件都要有相 应的软件许可证。 有关 EMC 产品名称的最新清单,请参见 上的 EMC Corporation 商标。 VMware 是 VMware, Inc. 的注册商标。此处使用的所有其他 商标均为其各自所有者的资产。 部件号 H12145.1

射频卡协议ISO14443- 全文中文

中国金融集成电路(IC)卡与应用无关的非接触式规范中国金融集成电路(IC)卡标准修订工作组二零零四年九月目次1 范围 (1)2 参考资料 (2)3 定义 (3)3.1 集成电路Integrated circuit(s)(IC) (3)3.2 无触点的Contactless (3)3.3 无触点集成电路卡Contactless integrated circuit(s) card (3)3.4 接近式卡Proximity card(PICC) (3)3.5 接近式耦合设备Proximity coupling device(PCD) (3)3.6 位持续时间Bit duration (3)3.7 二进制移相键控Binary phase shift keying (3)3.8 调制指数Modulation index (3)3.9 不归零电平NRZ-L (3)3.10 副载波Subcarrier (3)3.11 防冲突环anticollision loop (3)3.12 比特冲突检测协议bit collision detection protocol (3)3.13 字节byte (3)3.14 冲突collision (3)3.15 基本时间单元(etu)elementary time unit(etu) (3)3.16 帧frame (3)3.17 高层higher layer (4)3.18 时间槽协议time slot protocol (4)3.19 唯一识别符Unique identifier(UID) (4)3.20 块block (4)3.21 无效块invalid block (4)4 缩略语和符号表示 (5)5 物理特性 (8)5.1 一般特性 (8)5.2 尺寸 (8)5.3 附加特性 (8)5.3.1 紫外线 (8)5.3.2 X-射线 (8)5.3.3 动态弯曲应力 (8)5.3.4 动态扭曲应力 (8)5.3.5 交变磁场 (8)5.3.6 交变电场 (8)5.3.7 静电 (8)5.3.8 静态磁场 (8)5.3.9 工作温度 (9)6 射频功率和信号接口 (9)6.1 PICC的初始对话 (9)6.2 功率传送 (9)6.2.1 频率 (9)6.2.2 工作场 (9)6.3 信号接口 (9)6.4 A类通信信号接口 (10)6.4.1 从PCD到PICC的通信 (10)6.4.2 从PICC到PCD的通信 (12)6.5 B类通信信号接口 (13)6.5.1 PCD到PICC的通信 (13)6.5.2 PICC到PCD的通信 (13)6.6 PICC最小耦合区 (14)7 初始化和防冲突 (15)7.1 轮询 (15)7.2 类型A-初始化和防冲突 (15)7.2.1 字节、帧、命令格式和定时 (15)7.2.2 PICC状态 (19)7.2.3 命令集 (20)7.2.4 选择序列 (21)7.3 类型B 初始化和防冲突 (26)7.3.1 比特、字节和帧的定时 (26)7.3.2 CRC_B (28)7.3.3 防冲突序列 (28)7.3.4 PICC状态描述 (29)7.3.5 命令集合 (31)7.3.6 ATQB和Slot-MARKER响应概率规则 (31)7.3.7 REQB命令 (31)7.3.8 Slot-MARKER命令 (33)7.3.9 ATQB(请求应答-类型B)响应 (33)7.3.10 ATTRIB命令 (34)7.3.11 对A TTRIB命令的应答 (36)7.3.12 HALT命令及应答 (36)8 传输协议 (38)8.1 类型A PICC的协议激活 (38)8.1.1 选择应答请求 (40)8.1.2 选择应答 (40)8.1.3 协议和参数选择请求 (43)8.1.4 协议和参数选择响应 (45)8.1.5 激活帧等待时间 (45)8.1.6 差错检测和恢复 (45)8.2 类型B PICC的协议激活 (46)8.3 半双工块传输协议 (46)8.3.1 块格式 (46)8.3.2 帧等待时间(FWT) (49)8.3.3 帧等待时间扩展 (49)8.3.4 功率水平指示 (50)8.3.5 协议操作 (50)8.4 类型A和类型B PICC的协议停活 (52)8.4.1 停活帧等待时间 (53)8.4.2 差错检测和恢复 (53)9 数据元和命令 (54)9.1 关闭非接触通道命令 (54)9.1.1 定义和范围 (54)9.1.2 命令报文 (54)9.1.3 命令报文数据域 (54)9.1.4 响应报文数据域 (54)9.1.5 响应报文状态码 (54)9.2 激活非接触通道命令 (55)9.2.1 定义和范围 (55)9.2.2 命令报文 (55)9.2.3 命令报文数据域 (55)9.2.4 响应报文数据域 (55)9.2.5 响应报文状态码 (55)附录 A:标准兼容性和表面质量 (56)A.1. 标准兼容性 (56)A.2. 印刷的表面质量 (56)附录 B: ISO/IEC其他卡标准参考目录 (57)附录 C:类型A的通信举例 (58)附录 D: CRC_A和CRC_B的编码 (60)D.1. CRC_A编码 (60)D.1.1. 通过标准帧发送的比特模式举例 (60)D.2. CRC_B编码 (60)D.2.1. 通过标准帧传送的比特模式实例 (60)D.2.2. 用C语言写的CRC计算的代码例子 (61)附录 E:类型A_时间槽-初始化和防冲突 (64)E.1. 术语和缩略语 (64)E.2. 比特、字节和帧格式 (64)E.2.1. 定时定义 (64)E.2.2. 帧格式 (64)E.3. PICC状态 (64)E.3.1. POWER-OFF状态 (64)E.3.2. IDLE状态 (65)E.3.3. READY状态 (65)E.3.4. ACTIVE状态 (65)E.3.5. HALT状态 (65)E.4. 命令/响应集合 (65)E.5. 时间槽防冲突序列 (65)附录 F:详细的类型A PICC状态图 (67)附录 G:使用多激活的举例 (69)附录 H:协议说明书 (70)H.1. 记法 (70)H.2. 无差错操作 (70)H.2.1. 块的交换 (70)H.2.2. 等待时间扩展请求 (70)H.2.3. DESELECT (70)H.2.4. 链接 (71)H.3. 差错处理 (71)H.3.1. 块的交换 (71)H.3.2. 等待时间扩展请求 (72)H.3.3. DESELECT (74)H.3.4. 链接 (74)附录 I:块和帧编码概览 (77)1 范围本规范包括以下主要内容:-物理特性:规定了接近式卡(PICC)的物理特性。

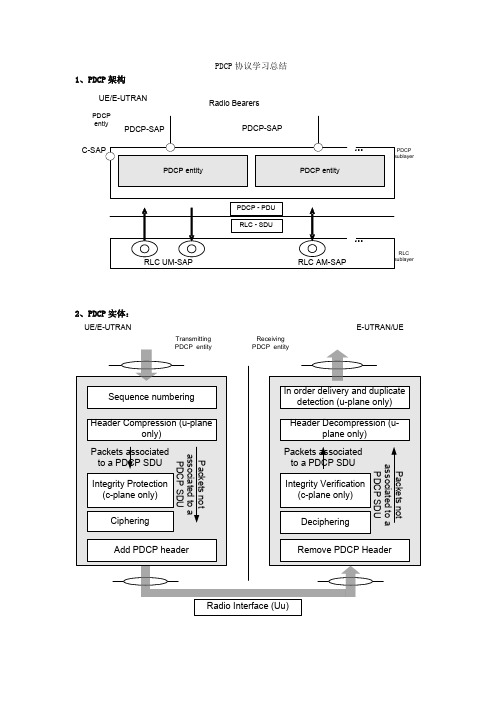

PDCP协议学习总结

PDCP 协议学习总结 1、PDCP 架构Radio BearersUE/E-UTRANPDCPRLC2、PDCP 实体:UE/E-UTRANE-UTRAN/UETransmitting Receiving一个UE可以定义多个PDCP实体,可以对携带用户面数据的每个PDCP实体进行配置,来使用头压缩。

每个PDCP实体携带一个无线承载的数据。

根据无线承载所携带的数据,PDCP实体对应于控制平面或者用户平面3、PCDP层服务向上层提供的服务:(PDCP提供服务给UE的RRC层和用户面高层)(1)数据传输(2)头压缩(3)加密(4)完整性保护从下层得到的服务:(RLC层向PDCP层提供服务)(1)确认的数据传输业务,包括PDCP PDU成功传输的指示(2)非确认的数据传输业务(3)有序传送,除了在切换时的情况(4)重复丢弃,除了在切换时的情况4、PDCP层功能(1)发送和接收实体利用ROHC协议对IP数据流进行相应的头压缩和解压缩(2)用户面数据或者控制面数据的传输(3)维护RLC AM模式下的映射的无线承载的PDCP SN(4)下层重建时,上层PDU的有序传送(5)下层重建时,RLC AM模式下的映射的无线承载的下层SDU重复消除(6)用户面数据和控制面数据的加密和解密(7)控制面数据的完整性保护与完整性验证(8)基于计时器的丢弃(9)重复丢弃5、PDCP过程(具体过程见page 3)(1)PDCP数据传输过程上行数据传输过程:每一个PDCP SDU对应一个Discard Timer,一旦由高层接收到一个PDCP SDU,即启动该SDU对应的Discard Timer。

同时,进行发送相关的状态变量更新及加密、完整性保护等,具体过程如图2所示。

下行数据传输过程:在不需重建的情况下,PDCP实体在接收到RLC AM实体提交的PDCP PDU 时,不需执行重排序过程,因为RLC AM在向PDCP实体提交PDCP PDU时,已保证顺序递交。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

SD 卡协议学习点滴(一)1.0 SD Card spec 2.0 基本特点:1.1 SD 卡基本概念首先 SD 卡有所谓操作模式(operation mode)的概念,每种操作模式又具体对应一种或 多种状态,主机通过发送命令可以使 SD 卡在不同的状态间转换,SD 卡则接受命令,并根 据自己现在所处状态做出不同的响应。

系统上电时刻或者搜寻 SD 卡时,SD 卡控制器应该处于 SD 卡识别模式;SD 卡在刚接 入系统时刻也处于这种模式,并且处于此模式下的 Idle 状态。

SD卡识别模式:在这种模式下,控制器会检验SD卡的工作电压范围,识别SD卡类型,并要 求它们发送各自的相对地址(Relative Card Address) ;这些操作在SD卡各自的CMD线上进 行。

所有的操作均使用默认的 SD卡识别时钟频率(identification clock rate) SD卡复位:发送GO_IDLE_STATE(CMD0)到SD卡后,除处于非活动状态(Inactive state) 之外的SD卡都会进入空闲状态(Idle state) ;在Idle状态,SD卡的CMD线处于输入模式,默 认相对地址为 0x0000,默认驱动寄存器设定为最低速度,最大驱动电流能力。

1.2 工作条件检测在控制器和 SD 卡进行任何通信之前,控制器不清楚 SD 卡支持的工作电压范围,故而控制 器首先使用默认的电压发送一条 reset 指令(CMD0) ,紧跟着的 CMD8 指令,用于取得 SD 卡支持工作电压范围数据。

卡通过检测 CMD8 的参数部分来检查控制器使用的工作电压, SD 控制器通过分析回传的 CMD8 参数部分来校验 SD 卡是否可以在所给电压下工作。

如果 SD 卡可以在指定电压下工作,则它回送 CMD8 的命令响应字,其中包含 check voltage, check pattern。

如果 SD 卡不支持所给电压,则 SD 卡不会给出任何响应信息,并继续处于 Idle 状 态。

在 PLV2.0(physical layer version2.0)下,在首次执行 ACMD41 之前,必须执行 CMD8 指 令,用以初始化 SDHC 卡,SDHC 卡根据是否接收到 CMD8 指令来鉴别控制器是否支持 PLV2.0 协议。

使用低电压的控制器也必须在 ACMD41 命令之前发送 CMD8,避免可以工作 在两种电压模式下的 SD 卡因为没有接收到 CMD8, 而默认工作在高电压环境下,被误认 为是只支持高电压工作模式。

SD_SEND_OP_COND(ACMD41)命令的目的是给予 SD 卡控制器一个识别 SD 卡是否可以在所给 Vdd 范围下工作的机制,如果 SD 卡无法在指定 Vdd 范围内工作,则它会进入非活动 状态 (Inactive state) 要注意的是, 。

ACMD41 是应用相关型命令, 因而, 每次发出的 ACMD41 命令都必须紧跟在一条 APP_CMD(CMD55)命令之后。

在空闲态(Idle State)下使用的 CMD55 命令使用默认的卡相对地址(RCA)0x0000。

每次控制器发送 CMD0 复位 SD 卡后,都要重新进行系列初始化操作(CMD8,ACMD41...) 。

如果 ACMD41 指令的 OCR 比特位为 0,控制器可以查询各个 SD 卡,并决定它们共同的工 作电压范围。

在作为查询的 ACMD41 指令发送之后,SD 卡并不会开始初始化过程,直到控 制器重新发送一条 ACMD41 指令。

1.3 SD卡初始化和识别过程:SD 卡的初始化开始于接收到 ACMD41 指令之后,ACMD 指令的 HCS(Host Capacity Support)位如果设定为 1 的话,表明控制器支持 SDHC 卡,否则表示不支持。

在 CMD8 命令发送之后的 ACMD41 指令其功能有所扩展,在参数里多了 HCS 部分, 在响应里面多了 CCS(Card Capacity Status)部分。

HCS 参数会被不响应 CMD8 命令的 SD 卡所抛弃。

控制器向不响应 CMD8 的卡发送 ACMD41 指令时,HCS 位应该设置为零 0。

如 果向 SDHC 卡发送 HCS 位为 0 的 ACMD41 命令,SDHC 卡返回的响应,其 busy 标识位永 远为 0,代表忙状态。

HCS 标识位用来表明 SD 卡是否已经完成初始化,如果未完成,HCS 为零,否则为 1,如果 HCS 为 0,控制器会重复发送 ACMD41 指令,SD 卡只检查首次接收 到的 ACMD41 指令的 HCS 位。

响应 CMD8 的 SD 卡发送的对于 ACMD41 指令响应会包含 CCS 部分,控制器只检查 HCS 标志位为 1 的响应所包含的 CCS 位。

CCS=1 表明其为 SDHC 卡,否则为标准 SD 卡。

控 制 器 随 后 发 送 ALL_SEND_CID(CMD2) 命 令 , 查 询 各 个 卡 的 CID ( unique card identification)值,还没有被识别的 SD 卡(处于 Ready 状态)会发送 CID 值作为响应,发 送完 CID 值之后,SD 卡进入识别状态(Identification state) ,然后控制器发送 CMD3 (SEND_RELATIVE_ADDR)命令,要求各个 SD 卡发送一个新的相对地址(RCA) ,RCA 在之后的数据传输模式中用于寻址。

RCA 发送完之后。

SD 卡进入 Stand-by 状态,在这个状 态,如果控制器想要给 SD 卡分配一个新的 RCA,它可以发送另一条 CMD3 命令给 SD 卡。

最后发布的 RCA 为 SD 卡的真实 RCA。

1.4 数据传输模式:在 SD 卡识别模式结束之前,控制器使用的时钟频率均为 Fod。

在数据传输模式,控制 器可能会使用 Fpp 频率。

控制器发送一条 SSEND_CSD(CMD9)命令来获取 SD 卡 CSD 寄存器 (Card Specific Data)里面的描述值,譬如,块长度,卡容量信息等。

广播命令 SET_DSR (CMD4)为各个已识别的 SD 卡配置驱动阶段(??)。

它会向 SD 卡的 DSR 寄存器写入相关 的信息。

控制器的时钟频率也在这个时刻从 Fod 转到 Fpp。

SET_DSR 命令是可选的。

CMD7 命令用来选择某个 SD 卡,使其进入 Transfer 状态,在指定时间段内,只有一个 卡能处于 Transfer 状态。

当某个先前被选中的处于 Transfer 状态的 SD 卡接收到 CMD7 之后, 会释放与控制器的连接,并进入 Stand-by 状态。

当 CMD7 使用保留地址 0x0000 时,所有的 SD 卡都会进入 Stand-by 状态。

1.5 数据传输模式下各个状态的转换关系总结如下:所有的数据读命令都可以被停止命令(CMD12)在任意时刻终止。

数据传输会终止,SD 卡返回 Transfer 状态。

读命令有:块读操作(CMD17)、多块读操作(CMD18)、发送写保 护(CMD30)、发送 scr(ACMD51)以及读模式下的普通命令(CMD56) 所有的数据写命令都可以被停止命令(CMD12)在任意时刻终止。

写命令也会在取消选 择命令(CMD7)之前停止。

写命令有:块写操作(CMD24,CMD25)、编程命令(CMD27)、 锁定/解锁命令(CMD42)以及写模式下的普通命令(CMD56) 数据传输一旦完成,SD 卡会退出数据写状态,进入 Programming 状态(传输成功)或者 Transfer 状态(传输失败) 如果块写操作被叫停,但是写操作包含的最终块其长度和 CRC 校验是正确的话,数据会 被编程到 SD 卡(从缓存写入到 Flash?) SD 卡可能会提供缓存模式,意思是前次写入块在编程到 Flash 的时刻,控制器可以接 着发送下一块的数据 当写缓存为满时刻,并且 SD 卡处于 Programming 状态,DAT0 会保持为低电平(BUSY), 表明其为忙状态 写 CSD,写保护,擦除这些操作没有缓存的功能,当 SD 卡正在处理这些命令的时候, 其余的数据传输命令会被忽略。

当 SD 卡为忙,并且处于 Programming 状态的时候,DAT0 也 会被 SD 卡拉低, 在 SD 卡处于 Programming 状态时候,不允许控制器发送设置参数命令。

设置参数命令 有:设置块长度(CMD16)、擦除块开始(CMD32)以及擦除块结束(CMD33) 在 SD 卡编程时刻,读命令也是不允许的 当把另一个卡从 Stand-by 状态转换为 Transfer 状态的时候,正处于 erase 和 Programming 状态的卡其操作不会终止,它会自动进入 Disconnect 状态,释放数据线。

处于 Disconnect 状态的卡可以通过发送 CMD7 命令使其脱离此状态,并进入 Programming 状态,并重新激活忙标识符 复位 SD 卡(使用 CMD0 或者 CMD15)会终止任何等待中或正在进行的 Programming 操 作。

这可能会损毁 SD 卡的数据 CMD34-37 CMD50,CMD57 保留1.6 宽总线选择/取消选择:宽总线(4bit)模式可以通过 ACMD6 选择/取消选择,默认工作模式为 1bit 模式。

为了 改变总线宽度,以下两个条件须满足: 1. SD 卡处于 Transfer 状态 2.SD 卡未被锁定 2Gbyte SD卡: 为使用 2Gbyte 的 SD 卡,Maximum Block Length(READ_BL_LEN=WRITE_BL_LEN) 参数须设置为 1024byte。

但是,由 CMD6 设置的 Block Length 须为 512byte,从而可与最大 仅可使用 512byte Block Length 的 SD 卡相兼容1.7 SD Card 读数据:DAT 线上没有数据传输时,由外部上拉电阻保持为高电平。

传输数据块由一个起始比 特(1 或者 4 个比特的低电平) ,以及紧跟着的连续数据流组成。

数据流包含有效载荷数据 (以及错误校验比特,如果有使用到 ECC) 。

数据流以数据结束标识符结束(1 或者 4 比特 的高电平)数据传输和时钟信号是同步的。

。

有效载荷数据后紧跟着 1 比特或者 4 比特的 CRC 校验码 读命令在出现 BLOCK_LEN_ERROR 或者 ADDRESS_ERROR 的情况下可以被否决, 这种情况下,不会发生数据传输过程;块读操作 块传输下,基本的数据传输单位是块,它最大为 512byte,小一些的块传输也是可以的, 如果它指向的内容其地址范围处于以 512 字节为边界的某块内(譬如 地址范围为 200~300 的传输是可以的,但是地址范围为 500~600 因为地址横跨了两个块,则不可行) 由 CMD16 设置的 Block Length 参数最大可为 512byte,而与 READ_BL_LEN 的大小无 关 块 数 据 的 结 尾 都 附 加 有 CRC 校 验 码 , 用 以 保 证 传 输 数 据 的 完 整 性 。