基于4T像素结构的CMOS图像传感器设计

有源像素CMOS图像传感器

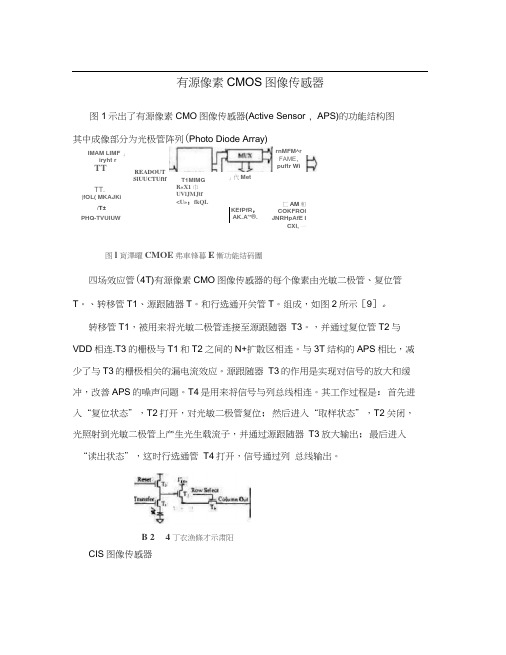

有源像素CMOS 图像传感器图1示出了有源像素CMO 图像传感器(Active Sensor , APS)的功能结构图其中成像部分为光极管阵列(Photo Diode Array)图l 肓澤曜CMOE 弗車锋暮E 慚功能结码團四场效应管(4T)有源像素CMO 图像传感器的每个像素由光敏二极管、复位管T 。

、转移管T1、源跟随器T 。

和行选通开关管T 。

组成,如图2所示[9]。

转移管T1,被用来将光敏二极管连接至源跟随器 T3。

,并通过复位管T2与VDD 相连.T3的栅极与T1和T2之间的N+扩散区相连。

与3T 结构的APS 相比,减 少了与T3的栅极相关的漏电流效应。

源跟随器 T3的作用是实现对信号的放大和缓 冲,改善APS 的噪声问题。

T4是用来将信号与列总线相连。

其工作过程是:首先进 入“复位状态”,T2打开,对光敏二极管复位;然后进入“取样状态”,T2关闭, 光照射到光敏二极管上产生光生载流子,并通过源跟随器 T3放大输出;最后进入“读出状态”,这时行选通管 T4打开,信号通过列 总线输出。

CIS 图像传感器IMAM LIMF 」iryht rTTREADOUT SlUUCTUftf TT.|fOL( MKAJKi/T±PHQ-TVUIUWKEfPfR , AK.A'*®. 匚AM 和 COKFROl JNRHpAfE I CXI, 一rnMFM^r FAME , puftr Wi 」代Met T1MIMG R«X1 巾 UVlJMJtf <U»:fkQL B 2 4丁衣漁條才示肃阳接触式图像传感器( CIS(Contact Image Sensor) 是90 年代新型图像传感器。

与电荷耦合器件(CCD相比.CIS的优点主要有a无须外加光源、光学透镜等辅助机构b具有尺寸小、重量轻、结构紧凑及便于安装c采用R a 3光源.系统功耗低d采用陶瓷基底.有良好的温度特性。

CMOS芯片原理和产品介绍

• Radiation hardness

• Color

CMOS 芯片的特性功能

Features Region of Interest: Makes it possible to address a certain area of the sensor and read this part out with a higher speed. Typically full row addressing, column addressing if required. Binning: Gives higher DR and speed with a reduced resolution. Typically 2x2 binning: +50% DR and 2.5 x more speed

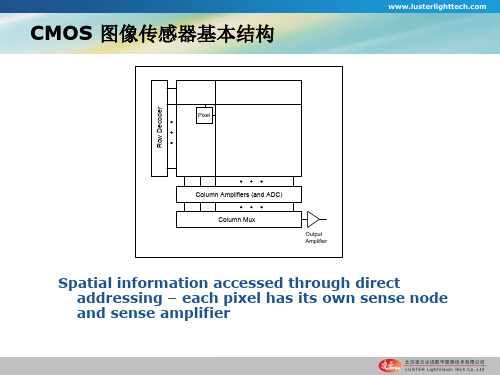

CMOS 图像传感器基本结构

Row Decoder

Pixel

Column Amplifiers (and ADC)

Column Mux

Output Amplifier

Spatial information accessed through direct addressing – each pixel has its own sense node and sense amplifier

CMOS 芯片的特性功能

Features Color: Application of on-chip color filters allows color imaging. Typically RGGB Bayer pattern.

V-CCD PD PD+amp MOS switch

Row selection

amp

CMOS图像传感器的基本原理及设计

CMOS图像传感器的基本原理及设计摘要:介绍CMOS图像传感器的基本原理、潜在优点、设计方法以及设计考虑。

关键词:互补型金属-氧化物-半导体图像传感器;无源像素传感器;有源像素传感器1引言20世纪70年代,CCD图像传感器和CMOS图像传感器同时起步。

CCD图像传感器由于灵敏度高、噪声低,逐步成为图像传感器的主流。

但由于工艺上的原因,敏感元件和信号处理电路不能集成在同一芯片上,造成由CCD图像传感器组装的摄像机体积大、功耗大。

CMOS图像传感器以其体积小、功耗低在图像传感器市场上独树一帜。

但最初市场上的CMOS图像传感器,一直没有摆脱光照灵敏度低和图像分辨率低的缺点,图像质量还无法与CCD图像传感器相比。

如果把CMOS图像传感器的光照灵敏度再提高5倍~10倍,把噪声进一步降低,CMOS图像传感器的图像质量就可以达到或略微超过CCD图像传感器的水平,同时能保持体积小、重量轻、功耗低、集成度高、价位低等优点,如此,CMOS图像传感器取代CCD图像传感器就会成为事实。

由于CMOS图像传感器的应用,新一代图像系统的开发研制得到了极大的发展,并且随着经济规模的形成,其生产成本也得到降低。

现在,CMOS图像传感器的画面质量也能与CCD图像传感器相媲美,这主要归功于图像传感器芯片设计的改进,以及亚微米和深亚微米级设计增加了像素内部的新功能。

实际上,更确切地说,CMOS图像传感器应当是一个图像系统。

一个典型的CMOS 图像传感器通常包含:一个图像传感器核心(是将离散信号电平多路传输到一个单一的输出,这与CCD图像传感器很相似),所有的时序逻辑、单一时钟及芯片内的可编程功能,比如增益调节、积分时间、窗口和模数转换器。

事实上,当一位设计者购买了CMOS图像传感器后,他得到的是一个包括图像阵列逻辑寄存器、存储器、定时脉冲发生器和转换器在内的全部系统。

与传统的CCD图像系统相比,把整个图像系统集成在一块芯片上不仅降低了功耗,而且具有重量较轻,占用空间减少以及总体价格更低的优点。

=基于CMOS图像传感器的数据采集方案设计

2012届毕业生毕业设计说明书题目: 基于CMOS图像传感器的数据采集方案设计年月日目次1 概述 (1)1.1 选题背景 (1)1.2 研究目的和意义 (1)1.3 CMOS图像传感器国内外研究现状 (2)1.4 主要研究内容 (3)2 方案论证 (3)2.1 CMOS与CCD比较 (3)2.2 CMOS图像传感器工作原理 (5)2.3图像处理芯片选择 (7)2.4 FPGA工作原理 (7)2.5 总线介绍 (8)2.6 系统总体方案设计 (9)3 图像采集系统硬件设计 (11)3.1 图像传感器外围电路设计 (12)3.2 FPGA与图像传感器连接设计 (14)3.3 数据传输电路设计 (15)3.4采集图像缓存电路 (16)3.5 电源电路设计 (16)3.6 系统稳定性设计 (17)4 系统采集方案软件设计 (18)4.1 CMOS图像传感器数据采集流程图 (19)4.2 SCCB总线接口设计 (20)4.3 FPGA程序流程设计 (20)5 总结 (22)参考文献 (24)1 概述1.1 选题背景现代社会人们对于图像的获取的要求越来越高,不仅在日常生活中存在着视频图像的应用,在现代工业生产中图像的采集程度直接影响到整个工业的自动化水平和生产效益。

因此图像传感器获得很好的应用市场和发展机会,在应用中不断得到创新。

因此图像传感器的种类繁多,能适用于不同的场合。

在图像获取与运用中,图像传感器占据着重要的位置,因此越来越多的专家学者致力于图像处理的分析研究,并且取得了非常成功的效果。

在很长一段时间中,由于技术的限制,CCD一直垄断着图像传感器市场,使得成像技术的单一化。

近年来随着CMOS的不断完善,其独特的性能优势逐渐体现出来。

并且在研究领域得到了发展,很多技术得到了攻克。

例如抑制噪声干扰、提高分辨率等方面取得了很大突破,在市场上得到了很迅速的应用,被广泛的应用到各种图像采集系统中。

本科阶段对CMOS的研究无疑会对今后的工作产生巨大的促进作用,但是CMOS图像采集技术一直被国外垄断,国内发展并不成熟。

5T结构全局曝光CMOS图像传感器的研究与设计

5T结构全局曝光CMOS图像传感器的研究与设计姚洪涛;李晓宁;田青青【摘要】阐述一种5T全局曝光像素结构的设计.通常的全局曝光CMOS图像传感器采用的是4T结构,该5T全局曝光像素结构在原有结构基础上增加一个曝光控制管,实现对曝光操作的控制,可以使曝光与积分值读出同步进行,提高图像传感器的工作效率,使其有更高的帧频,同时克服电子溢流等问题,使得其拥有更高的成像质量.【期刊名称】《现代计算机(专业版)》【年(卷),期】2018(000)031【总页数】5页(P75-79)【关键词】CMOS图像传感器;全局曝光;5T像素结构;列级ADC【作者】姚洪涛;李晓宁;田青青【作者单位】长春理工大学计算机科学技术学院,长春130022;长春理工大学计算机科学技术学院,长春130022;长春理工大学计算机科学技术学院,长春130022【正文语种】中文0 引言目前,固态图像传感器主要有两种:电荷耦合器件(Charge Couple Device,CCD)和互补金属氧化物半导体(Complementary Metal Oxide Semiconductor,CMOS)。

近年来,CMOS传感器设计技术和半导体制造技术的不断发展,使得CMOS图像传感器在数码相机、数字摄像机、安防监控、手机、汽车倒车影像、医疗影像等方面有着越来越广阔的应用前景[1]。

CMOS图像传感器主要有两种曝光方式:滚筒曝光(Rolling Shutter)和全局曝光(Global Shutter)。

在滚筒曝光模式中,一帧图像中的每一行都是在不同的时间点开始和结束曝光的,下一行的曝光开始时刻比上一行延迟一个行的读出周期,最后一行的曝光开始时刻比最早曝光的一行延迟了一个帧的读出周期[2]。

在滚筒式曝光模式下,如果被拍摄物体在曝光过程中高速运动,在进行曝光的过程中,被拍摄的物体已经发生了位移。

首先曝光的图像部分和随后曝光的图像部分已经处于不同的相对位置,导致被摄物体的图像产生形变失真。

基于CMOS图像传感器的高速相机成像电路设计与研究共3篇

基于CMOS图像传感器的高速相机成像电路设计与研究共3篇基于CMOS图像传感器的高速相机成像电路设计与研究1高速相机成像电路是指利用CMOS图像传感器的电路,能够对高速运动的目标进行拍照,并能够准确捕捉瞬间的动作。

这种相机通常用于运动学分析,以及高速目标的轨迹重建和测量。

本文将介绍高速相机成像电路的设计与研究。

1. CMOS图像传感器CMOS图像传感器是一种用于捕捉图像的半导体器件。

它由许多感光元件组成,每个像素都能够捕捉光信号并将其转化为电信号。

CMOS图像传感器具有更高的集成度,能够提供更高的灵敏度和更快的读出速度,这使得它成为高速相机的主要组成部分。

2. 负反馈放大器高速相机需要一个能够放大信号的电路。

负反馈放大器是一种经典的放大电路,它由一个放大器和一个反馈回路组成。

反馈回路能够检测放大器输出的信号,并将其与输入信号进行比较,从而能够控制放大器的增益。

这种电路具有高的放大增益,低的输入噪声和高的带宽。

3. 模数转换器高速相机需要一个能够将模拟信号转化为数字信号的电路,以便进行数字信号处理。

模数转换器是一种能够将连续的模拟信号转化为离散的数字信号的电路。

它通常采用脉冲调制技术,将连续的信号离散化为一系列的数字信号。

这种电路具有高的转换速度和高的分辨率,能够满足高速相机的要求。

4. FPGA高速相机需要一个能够进行数字信号处理的平台。

FPGA是一种可编程逻辑器件,能够根据应用的需求进行编程。

它具有高的集成度和高的实现速度,能够快速处理数字信号。

FPGA还具有低的功耗和高的可靠性,这使得它成为高速相机的优选平台。

5. 成像电路的设计与实现高速相机的成像电路需要通过软件和硬件的结合,进行设计和实现。

首先,需要进行成像算法的设计和优化,以确保能够准确捕捉高速目标的运动轨迹。

然后,需要进行电路设计和硬件优化,以保证成像电路具有高的灵敏度、高的带宽和快速的响应速度。

最后,需要通过电路模拟和实验验证,对成像电路进行评估和优化。

温度对4管像素结构CMOS图像传感器性能参数的影响

温度对4管像素结构CMOS图像传感器性能参数的影响王帆;李豫东;郭旗;汪波;张兴尧【摘要】为了对4管像素结构CMOS图像传感器的空间应用提供可靠性指导,对4管像素结构的CMOS图像传感器进行了-40~80℃的变温实验,着重分析了样品器件的转换增益、满阱容量、饱和输出和暗电流等参数随温度的变化规律。

实验结果表明,随着温度的升高,样品器件的转换增益从0.02654 DN/e 下降到0.02379 DN/e,饱和输出从4030 DN下降到3396 DN,并且暗电流从22.9 e·pixel-1·s-1增长到649 e· pixel-1·s-1。

其中器件转换增益的减小应主要归因于载流子迁移率随温度升高而下降使得像素后端读出电路增益降低;饱和输出的降低则是因为转换增益的降低,因为转换增益随温度变化对饱和输出的影响要大于满阱容量随温度变化对饱和输出的影响。

%In order to provide a reliable guidance for the spatial application of the 4 T CMOS image sensor, temperature effects on 4T active pixel sensor CMOS image sensor from -40 ℃ to 80 ℃were presented. The influences of temperature on conversion gain, full well charge, saturated output and dark current of the device were investigated. The experiment results show that the conversion gain of device decreases from 0. 026 54 DN/e to 0. 023 79 DN/e, the saturated output decreases from 4 030 DN to 3 396 DN, and the dark current increases from 22. 9 e·pixel-1 ·s-1 to 649 e· pixel-1 ·s-1 with the temperature increasing. The decrease of conversion gain should be attributed to the decrease of the carrier mobility with the temperature increasing. The decrease of saturation output is mainly because of the decrease of the conversion gainwhich the influence of the conversion gain on saturated output is greater than that of the full well capacity with the change of temperature.【期刊名称】《发光学报》【年(卷),期】2016(037)003【总页数】6页(P332-337)【关键词】CMOS图像传感器;转换增益;满阱容量;暗电流;温度【作者】王帆;李豫东;郭旗;汪波;张兴尧【作者单位】中国科学院特殊环境功能材料与器件重点实验室,新疆电子信息材料与器件重点实验室,中国科学院新疆理化技术研究所,新疆乌鲁木齐 830011; 中国科学院大学,北京100049;中国科学院特殊环境功能材料与器件重点实验室,新疆电子信息材料与器件重点实验室,中国科学院新疆理化技术研究所,新疆乌鲁木齐 830011;中国科学院特殊环境功能材料与器件重点实验室,新疆电子信息材料与器件重点实验室,中国科学院新疆理化技术研究所,新疆乌鲁木齐830011;中国科学院特殊环境功能材料与器件重点实验室,新疆电子信息材料与器件重点实验室,中国科学院新疆理化技术研究所,新疆乌鲁木齐 830011; 中国科学院大学,北京 100049;中国科学院特殊环境功能材料与器件重点实验室,新疆电子信息材料与器件重点实验室,中国科学院新疆理化技术研究所,新疆乌鲁木齐 830011; 中国科学院大学,北京 100049【正文语种】中文【中图分类】TP394.1;TH691.9相比于电荷耦合元件(Charge-coupled device,CCD)图像传感器,互补金属氧化物半导体(Complementary metal oxide semiconductor,CMOS)图像传感器有着低功耗、充足的设计资源和制造工艺成本低等优势。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于4T像素结构的CMOS图像传感器设计

发表时间:2018-07-18T16:50:27.360Z 来源:《科技新时代》2018年5期作者:陈雷

[导读] 文中介绍了基于一种4T像素结构的图像传感器的设计.

广东省深圳市深圳市华海技术有限公司 518051

摘要传统的CMOS图像传感器采用3T像素结构,但由于自身结构的关系,整体性能难以满足较高的要求,4T像素结构应运而生,它比3T像素有更小的噪声,更好的性能;同时要求控制部分更加复杂.文中介绍了基于一种4T像素结构的图像传感器的设计.

关键词3T;4T;APS;图像传感器

CMOS图像传感器是在20世纪60年代末期出现的由IBM和仙童公司开发的双极型和MOS光敏二极管阵列结构⑴.在图像传感器中最常用的光敏器件是反偏PN结光电二极管和P+/N/P埋藏光电二极管(BuriedPhotoDiode)。

其中埋藏光电二极管像素比反偏PN结像素有更好的灵敏度,另外由于M1(Tx)的存在,使像素的可控性更好,有效地降低热噪声和暗电流.但4T结构比3T多了一个管子,在同样像素尺寸条件下,填充率比3T像素小.3T像素由于自身结构的关系,暗电流不能得到很好的控制,性能难以满足较高的要求;为满足需要,4T像素结构应运而生,它比3T 像素有更小的噪声,更好的性能;同时要求控制部分更加复杂⑷

14T像素图像传感器的设计

1.14T像素与读取电路结构设计

T1时刻,完成对光敏二极管和P点连接的寄生电容Cp的复位,光电荷开始聚集;

T2时刻,再次完成P点寄生电容的复位,寄生电容Cp存入电压VDD;

T3时刻,经过源跟随器对电容CP.电压进行采样,到T4时刻,完成采样。

源跟随器增益AP,CP电压存于电容CP;电容CP上电压

Vc1=AP•VDD;

T5时刻,光信号积分完成,图像信号产生;M1管打开,光电荷流向寄生电容CP,T6时刻完成电荷转移。

寄生电容CP上电压为

Vcp=VDD-Vsignal;

T7时刻,对CP上的电压进行采样。

到T8时刻,完成采样,CP上的电压存于电容C8;C8上的电压为VC8=AP•(VDD-Vsignal);

由此可知,电容C和电容C上的电压差得到相关的图像信号电压(前文对相关双采样论述详细,这里没有再对噪声信号进行分析,因此各电容电压均为近似值).

1.2系统概述,

CMOS图像传感器的集成度高,在同一芯片上集成有模拟信号处理电路和数字信号处理电路。

描述了CIS芯片的系统模块.芯片可以通过I.c接口将用户设定保存在控制寄存器中,控制寄存器的值决定了系统的工作状况.时序与控制模块产生控制信号,控制曝光顺序,放大器增益,AD转换启止,数据流时序和数据读取.传感器模拟电路主要包括一个像素矩阵,一个方向上的寻址寄存器,2个Y方向上的寻址寄存器,校正噪声的列放大器PGA(programmable—gainamplifier),一个模拟多路开关,一个ADC模数转换器.数字电路包括时序与控制模块,控制寄存器与I2C 接口模块,色彩校正和色彩补偿模块.从像素列读出的图像信号首先经过可控增益放大器PGA,放大后的信号再由列级A/D转换器转换为数字信号并锁存,再由x寻址寄存器控制逐列读出图像数据.数字图像数据经过色彩校正和色彩补偿模块作消噪和补偿运算,最后数据输出.CMOS图像传感器的像素阵列采用列复用结构,每一列像素由列总线相连,共用—个列读出电路.

像素阵列中,每列像素共享一个列电路.在像素单元中,曝光开始后光电流产生的电子聚积起来.首先像素所在的行被选中,此行的reset产生脉冲信号将P结点电压复位,然后采样信号reset产生脉冲将复位后的col—out电压保存在电容c,然后产生脉冲选通M1管,光电子流向结点P 点的寄生电容,sig的脉冲信号将col_out的电压保存在电容C上,两个缓冲器分别输出Vres和Vaig.

CMOS图像传感器的寻址寄存器由一个同步时钟控制,用于指向正被读出或复位的行和列,由x和Y寄存器选定的行和列就可以选定一个需要的像素.工作时有2个Y方向的寻址寄存器,一个指向正在被读出的行,另一个指向正在被复位的行,这2个寻址寄存器在同一时钟频率下逐行移位并扫过整个像平面,图像传感器每行像素的积分时间相同,由2个寻址寄存器脉冲之间的时间延迟来决定.方向的寻址寄存器用来指向正被读出的列,每行数据依次被读出并复位.

CMOS图像传感器的大部分控制信号由内部时序控制器产生,如主时钟信号MAIN_CLK,帧有效信号FRAME—VALID,行有效信号LINE—VALID,像素时钟PIXEL—CLK等一些基本控制信号需要由外部控制电路产生,主要有外部时钟信号CLKIN,复位信号RESET.

2R11_HDL设计

这里以时序与控制模块为例,介绍图像传感器电路的RTL设计.

根据CMOS图像传感器工作的时序要求,控制电路采用自顶向下的设计方法,按照各功能要求划分子模块,其中,时钟分频进程负责接收外部输入的时钟信号CLKIN,产生主控进程所需的时钟信号MAIN—CLK;主控进程在外部输入的RESTART信号下启动,通过外部输入的设定判断拍照时所要求采用的快门工作方式,并向图像传感器输出相应的时序控制信号,以满足不同曝光工作模式下的时序要求;主控进程还负责产生图像传感器标志信号NEW—FRAME,NEW—COLUM,NEW_ROW,GAINC,LINEC,判断传感器所处的工作状态以完成时序控制;当传感器图像数据输出时,时序控制模块输出相应的指示信号,分别为图像数据的时钟信号PIXCLK,帧有效信号FRAME—VALID,行有效信号LINE—VALID以指示后续电路对图像数据进行存储或处理.

控制电路各子模块分别运用Verilog硬件描述语言进行程序设计.其中,主控进程采用有限状态机的设计方法产生和处理图像传感器的工作时序.完成程序设计后,使用UNIX操作平台下的SYNOPSYSVCS仿真工具对程序进行仿真。

为了便于对仿真结果的观察以验证设计的正确性,设定快门模式工作时的读取指针和复位指针之间相差2个像素行,且每行读取40个像素值.从图7给出的仿真结果可知,ay每给一个地址,读取指针完成一个像素数据的读取,与设计的工作时序一致,仿真结果证明了设计的正确性.

3实验结果

芯片使用27MHz外部时钟,输出1280*1024的10位RGB数据,最大帧速率为15帧/秒,提供可控曝光时间从1gs到20s.芯片中模拟电路部分

为全定制设计,数字电路部分使用Artisan提供的标准单元库由VerilogHDL代码综合而来,使用Magma自动布局布线工具生成版图.本设计成功流片,芯片特征概要见表1.

4结束语

介绍了一种CIS芯片的实现方案,它使用4TAPS像素结构,列级AD转换,相关双采样电路,大大减小了噪声,改善了芯片性能.芯片中集成了色彩处理单元,能够有效处理图像,完善了芯片功能.设计完成后用0.18p,m工艺流片,测试结果较好,能够采集清晰图像.

目前,国内外图像传感器芯片的研究紧锣密鼓地展开,为改善4T像素填充率低的问题,4Tjshare等新的像素结构和电路被开发出来,图像传感器的制程也不断改善,CMOS图像传感器的发展有着广阔的前景.

种乘积码译码器设计方案的研究

数据输入与输出

输人数据经过串并行转换之后,同时读人迭代译码核心模块进行迭代计算,在数据输出模块,每一次迭代完成要进行条件判别,完成所要求的4次迭代之后,强制输出数据.

FPGA实现根据乘积码并行译码方案,迭代译码器各个模块采用VI-IDL硬件描述语言编写,用)(iliIl】【公司的开发工具ISE8.1完成了设计输人和综合,硬件资源的占

有率如表1所示.采用与Xilinx公司配套的Model—simXE6.0a集成仿真工具进行了功能仿真,图5为该两维乘积码的译码陛能功能仿真波形,其中时钟信号CLK周期为10MHz,上升沿有效,启动信号START下降沿有效,为8个时钟周期.Senddata为乘积码原始信息比特,rxin为经过输人模块并行出来的8比特信息,译码后4个比特信息为:yOd,yld,y2d,y3d.从图5中可见数据的译码输出仿真测试结果波形,例如编码之前的信息为1101,则输出分别为1,1,0,1,经过800IIS完成正确译码,如此再次经过800IIS,1,0,1,1并行译码输出.

可以看出所设计的TPC码译码器具有较好的译码效果,从译码输出的功能和硬件实现的设计方案都进一步证明了设计的正确性,通过改变输人激励部分参数,可以设计出更多码型的TPC码译码器.

参考文献

[1]陈雷,韩泽耀,曹庆红.基于4T像素结构的CMOS图像传感器设计[J].电子科技,2007(10):57-60+63.

[2]杨晓亮.CMOS图像传感器像素辐射特性的仿真研究[D].哈尔滨工程大学,2014.

[3]赵秋卫,李晓宇.简化4T像素结构CMOS图像传感器设计与实现[J].固体电子学研究与进展,2014,34(02):179-183.

作者简介:陈雷(1979一),男,工程师,2007年毕业于上海交通大学微电子硕士毕业

历任中芯国际设计服务处产品高级工程师,.安捷伦科技主任工程师,现任华海技术有限公司首席技术官。

研究方向:产品工程和测试.。